# SerialLite II IP Core User Guide

## **Contents**

| SerialLite II IP Core Overview               | 1-1  |

|----------------------------------------------|------|

| General Description                          | 1-2  |

| Performance and Resource Utilization         |      |

|                                              |      |

| SerialLite II IP Core Getting Started        | 2-1  |

| Parameterize the IP Core                     | 2-1  |

| Set Up Simulation                            | 2-3  |

| Generate Files                               |      |

| Simulate the Design                          | 2-4  |

| Instantiate the IP Core                      | 2-4  |

| Compile and Program                          | 2-4  |

| Specify Constraints                          |      |

| Assign Virtual Pins                          |      |

| Fitter Constraints                           | 2-5  |

| Timing Constraints                           | 2-5  |

| SerialLite II Parameter Settings             | 2-6  |

| Link Consistency                             | 2-12 |

| Data Rate                                    | 2-12 |

| Reference Clock Frequency                    | 2-13 |

| Port Type                                    | 2-13 |

| Self Synchronized Link Up                    | 2-16 |

| Scramble                                     | 2-18 |

| Broadcast Mode                               | 2-18 |

| Lane Polarity and Order Reversal             | 2-19 |

| Data Type                                    | 2-20 |

| Packet Type                                  | 2-20 |

| Flow Control Operation                       | 2-23 |

| Transmit/Receive FIFO Buffers                | 2-28 |

| Data Integrity Protection: CRC               | 2-30 |

| Transceiver Configuration                    | 2-30 |

| Error Handling                               | 2-33 |

| Optimizing the Implementation                | 2-34 |

| SerialLite II IP Core Functional Description | 3-1  |

| Atlantic Interface                           |      |

| High-Speed Serial Interface                  |      |

| Clocks and Data Rates                        |      |

| Aggregate Bandwidth                          |      |

| External Clock Modes                         |      |

| Internal Clocking Configurations             |      |

| SerialLite II Deskew Support                 |      |

|                                              |      |

| SerialLite II Clocking Structure                                                        | 3-6         |

|-----------------------------------------------------------------------------------------|-------------|

| SerialLite II Pin-Out Diagrams                                                          | 3-12        |

| Initialization and Restart                                                              | 3-16        |

| Multiple Core Configuration                                                             | 3-17        |

| IP Core Configuration for Intel Stratix 10, Arria 10, Arria V, Cyclone V, and Stratix V | Devices3-18 |

| Design Consideration                                                                    | 3-18        |

| Parameter Settings For SerialLite II and Custom PHY IP Cores                            | 3-19        |

| Extra Signals Between SerialLite II and Custom PHY IP Cores                             | 3-21        |

| SerialLite II Signals                                                                   | 3-22        |

| IP Core Verification                                                                    |             |

|                                                                                         |             |

| SerialLite II IP Core Testbench                                                         | 4-1         |

| Testbench Files                                                                         |             |

| Testbench Specifications.                                                               |             |

| Simulation Flow                                                                         |             |

| Running a Simulation                                                                    |             |

| Simulation Pass and Fail Conditions                                                     |             |

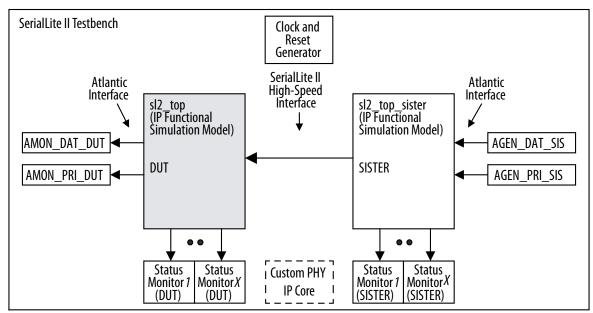

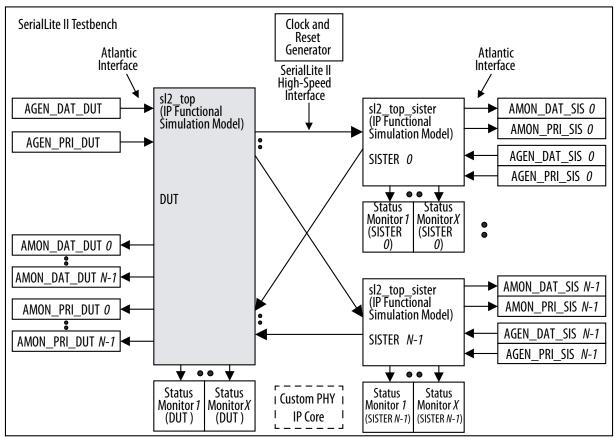

| Testbench Components                                                                    |             |

| AGEN                                                                                    |             |

| AMON                                                                                    |             |

| Status Monitors                                                                         |             |

| Clock and Reset Generator                                                               | 4-18        |

| Custom PHY IP Core                                                                      |             |

| Example Testbench – Verilog HDL                                                         |             |

|                                                                                         |             |

| SerialLite II IP Core User Guide Archives                                               | A-1         |

|                                                                                         |             |

| Revision History for SerialLite II IP Core User Guide                                   | B-1         |

### SerialLite II IP Core Overview

1

2019.01.09

UG-0705

The SerialLite II MegaCore function is a lightweight protocol suitable for packet and streaming data in chip-to-chip, board-to-board, and backplane applications.

The SerialLite II protocol offers low gate count and minimum data transfer latency. It provides reliable, high-speed transfers of packets between devices over serial links. The protocol defines packet encapsulation at the link layer and data encoding at the physical layer, and integrates transparently with existing networks without software support.

Table 1-1: SerialLite II IP Core Release Information

| Information           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Version               | 16.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Release Date          | October 2016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Ordering Code         | IP-SLITE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Device Family Support | Intel® Stratix® 10, Arria® 10, Arria V, Arria II GX, Cyclone V, Stratix V and Stratix IV device families.  Note: Intel Stratix 10 devices are indirectly supported by SerialLite II IP core version 16.1 and later. Arria 10 devices are indirectly supported by the SerialLite II IP core version 15.0 and later. If your design needs to implement SerialLite II interface in Intel Stratix 10 and Arria 10 devices, contact your local Altera representative or file a Service Request (SR) to obtain a design example, a guideline document, and a special license to enable the Quartus Prime software to generate the FPGA configuration file (.sof) for the Intel Stratix 10 and Arria 10 devices. |

Altera verifies that the current version of the Quartus Prime software compiles the previous version of each IP core. The IP Core Release Notes and Errata report any exceptions to this verification. Altera does not verify compilation with IP core versions older than one release.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

\*Other names and brands may be claimed as the property of others.

#### **Table 1-2: SerialLite II IP Core Features**

| Features                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical layer features | <ul> <li>622 Mbps to 6.375 Gbps per lane<sup>(1)</sup></li> <li>Single or multiple lane support (up to 16 lanes)</li> <li>8-, 16-, or 32-bit data path per lane</li> <li>Symmetric, asymmetric, unidirectional/simplex or broadcast mode</li> <li>Optional payload scrambling</li> <li>Full-duplex or self-synchronizing link state machine (LSM)</li> <li>Channel bonding scalable up to 16 lanes</li> <li>Synchronous or asynchronous operation</li> <li>Automatic clock rate compensation for asynchronous use: ±100 and ±300 parts per million (ppm)</li> </ul>                                                                                 |

| Link layer features     | <ul> <li>Atlantic interface compliant</li> <li>Support for two user packet types: data packet and priority packet</li> <li>Optional packet integrity protection using cyclic redundancy code (CRC-32 or CRC-16)</li> <li>Optional link management packets <ul> <li>Retry-on-error for priority packets</li> <li>Individual port (data/priority) flow control</li> </ul> </li> <li>Unrestricted data and priority packet size</li> <li>Support for TimeQuest timing analyzer</li> <li>Polarity reversal</li> <li>Lane order reversal</li> <li>IP functional simulation models for use in Altera-supported VHDL and Verilog HDL simulators</li> </ul> |

#### **Related Information**

SerialLite II IP Core User Guide Archives on page 5-1

Provides a list of user guides for previous versions of the SerialLite II IP core.

## **General Description**

**Altera Corporation**

The SerialLite II IP core is a simple, high-speed, low-latency, and low-resource point-to-point serial data communication link.

The SerialLite II IP core performs up to:

- 3.75 Gbps in Arria II GX devices

- 5 Gbps in Cyclone V devices

- 6.375 Gbps in Arria V, Stratix IV, and Stratix V devices

- More than 6.375 Gbps in Intel Stratix 10 and Arria 10 devices

SerialLite II IP Core Overview

<sup>(1)</sup> For Intel Stratix 10 and Arria 10 devices, the IP core supports higher than 6.375 Gbps per lane.

The SerialLite II IP core is highly configurable, and provides a wide range of functionality suited to moving data in many different environments.

The IP core provides a simple and lightweight way to move data from one point to another reliably at high speeds. It consists of a serial link of up to 16 bonded lanes, with logic to provide a number of basic and optional link support functions. The Atlantic interface is the primary access for delivering and receiving data.

The SerialLite II protocol specifies a link that is simple to build, uses as little logic as possible, and requires little work for a logic designer to implement. The SerialLite II MegaCore function uses all of the features available in the SerialLite II protocol. You can parameterize the IP core using the SerialLite II parameter editor.

A link built using the SerialLite II IP core operates at 622 Mbps to 6.375 Gbps per lane (or more for Intel Stratix 10 and Arria 10 devices). Link reliability is enhanced by the 8B10B encoding scheme and optional CRC capabilities. You can achieve further reductions in the bit-error rate by using the optional retry-onerror feature. Data rate and consumption mismatches can be accommodated using the optional flow-control feature to ensure that no data is lost.

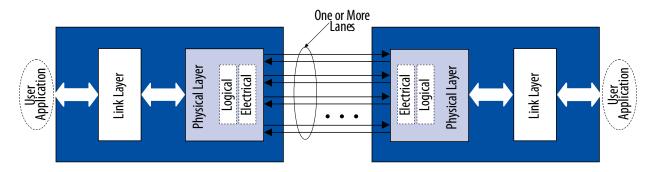

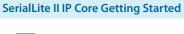

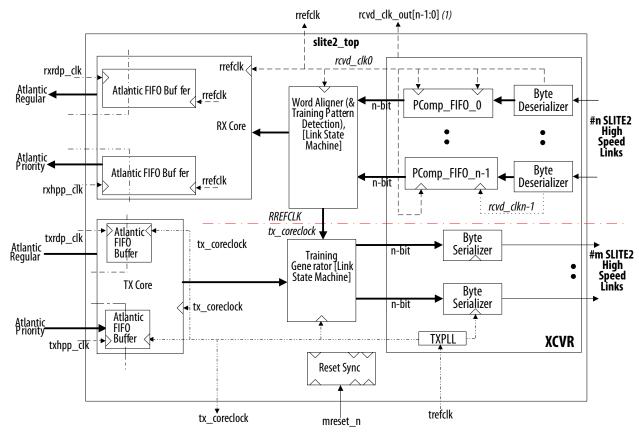

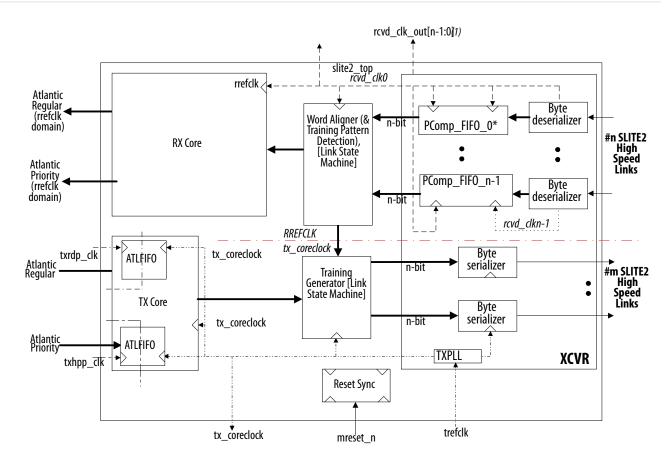

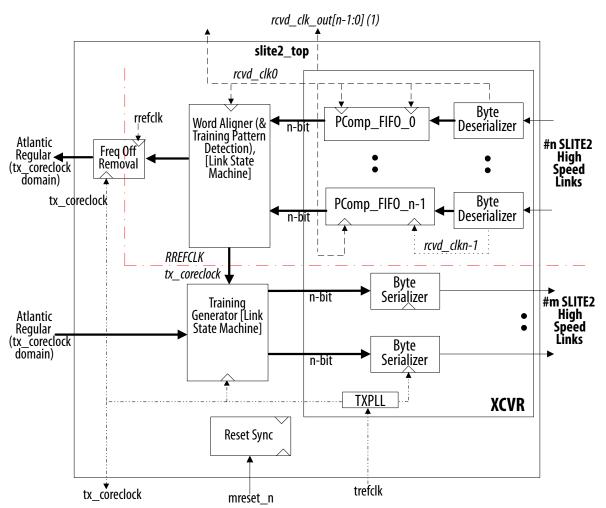

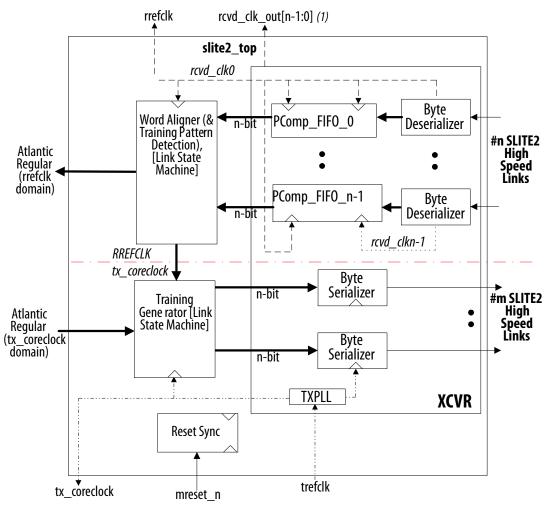

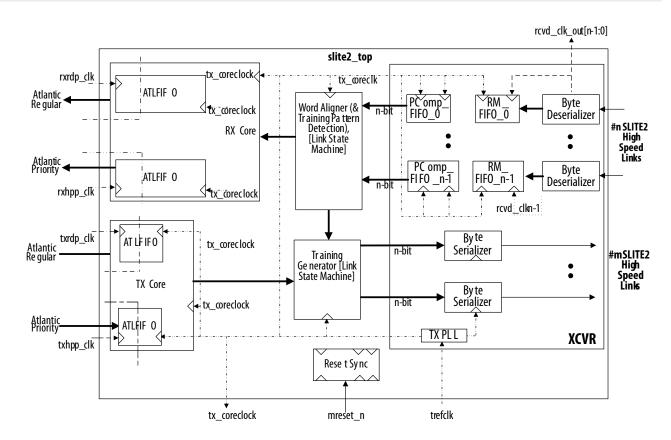

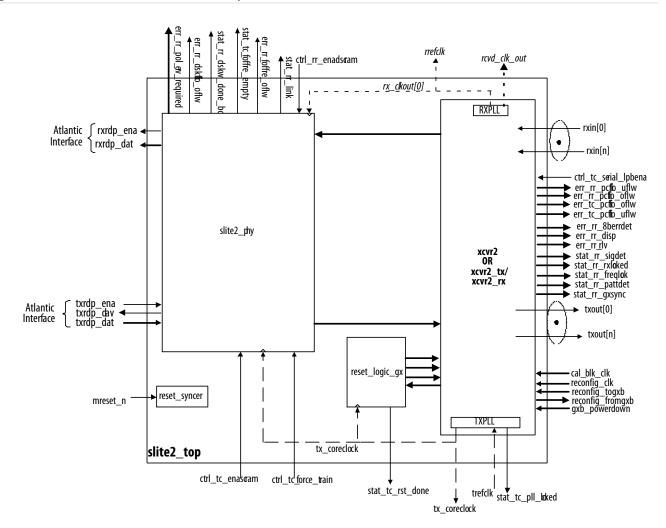

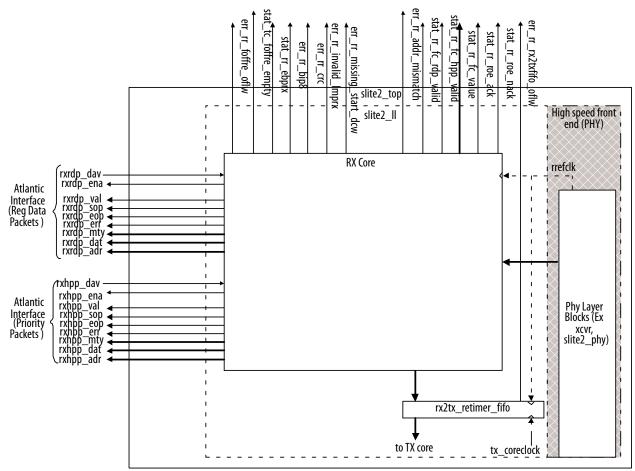

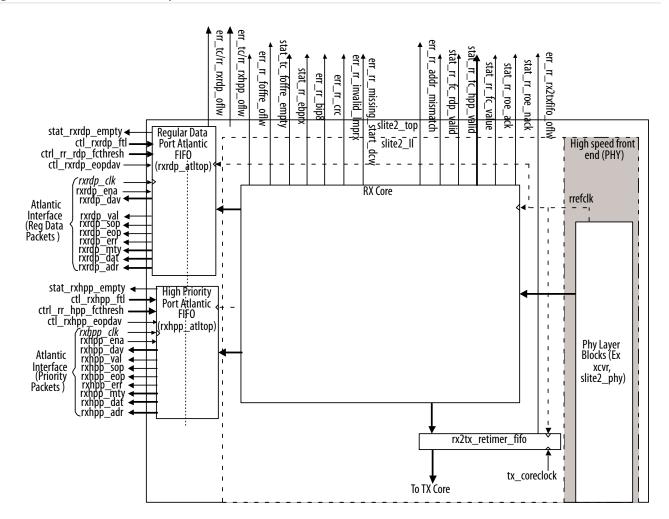

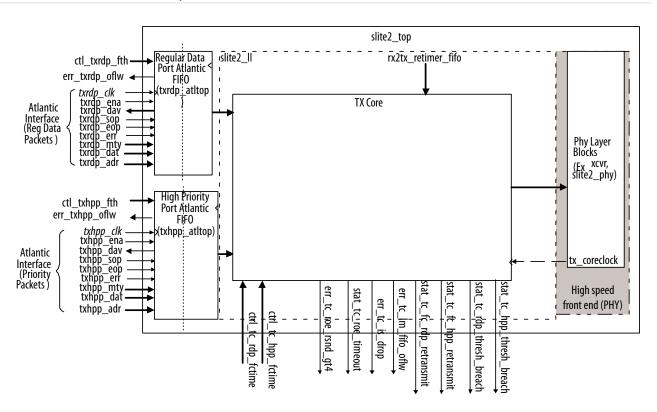

Figure 1-1: SerialLite II IP Core High-Level Block Diagram

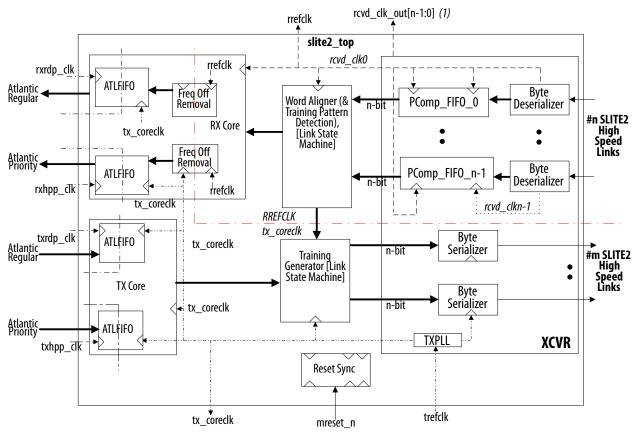

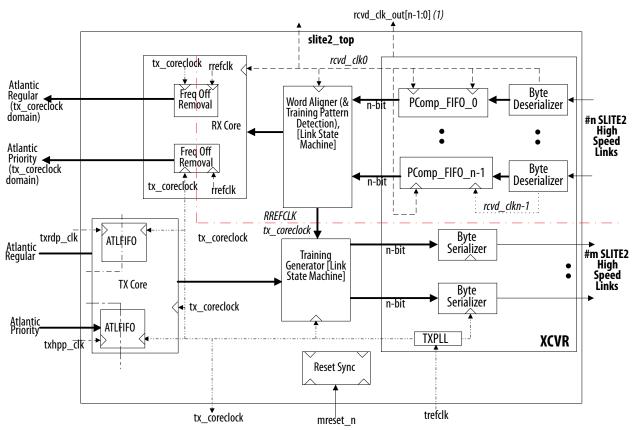

The SerialLite II IP core is divided into two main blocks: a protocol processing portion (data link layer) and a high-speed front end (physical layer).

You can use the SerialLite II IP core in the following applications:

- Chip-to-chip connectivity

- Board-to-board connectivity

- Shelf-to-shelf connectivity

- Backplane communication

- Bridging applications

- Streaming video applications

- Imaging applications

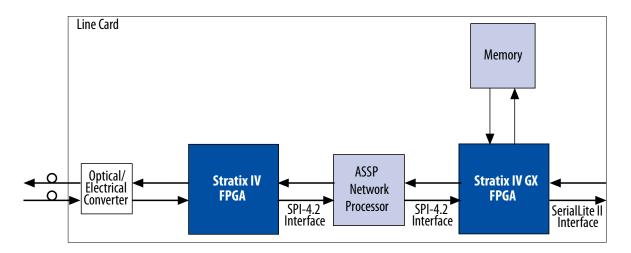

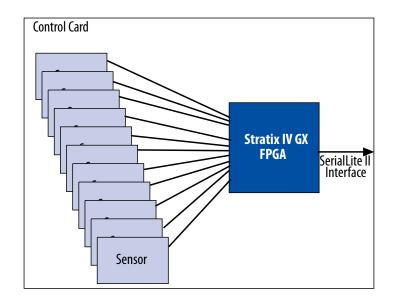

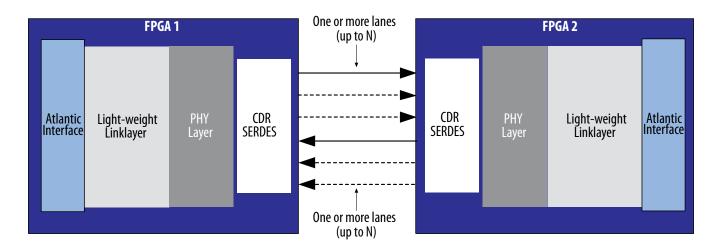

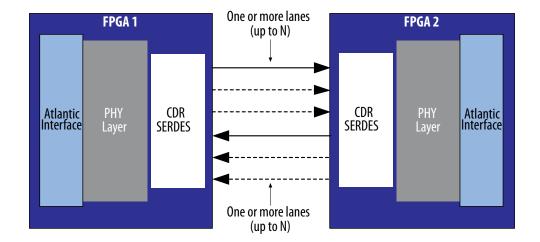

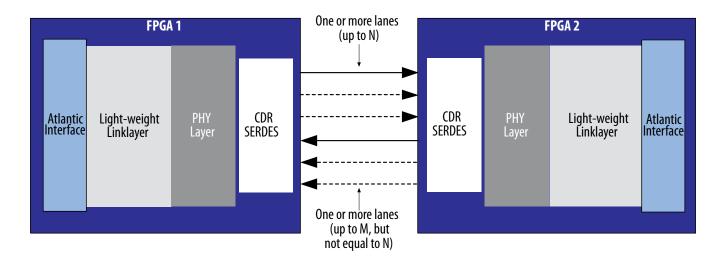

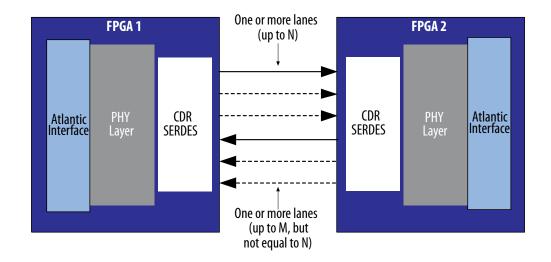

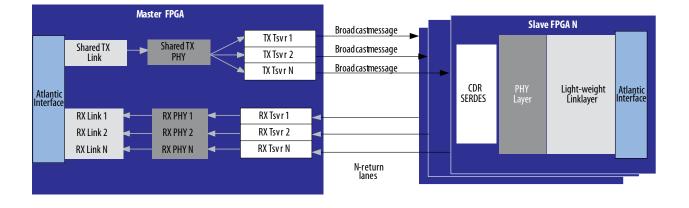

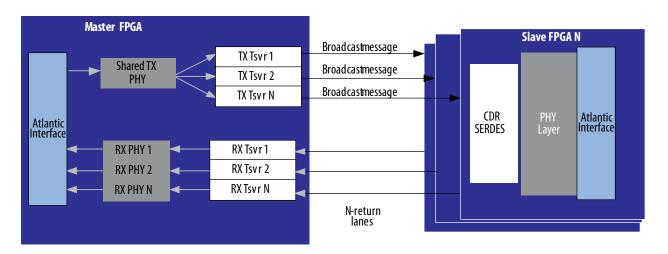

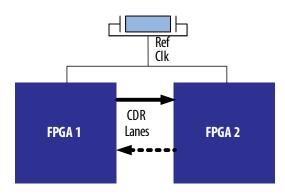

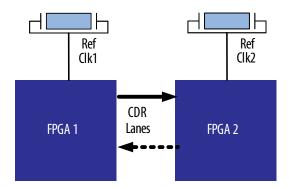

The following diagrams show two examples of bridging applications.

SerialLite II IP Core Overview Altera Corporation

#### Figure 1-2: Typical Application—Bridging Functions

Figure 1-3: Typical Application—Unidirectional Bridging Application

### **Performance and Resource Utilization**

The performance and resource utilization table lists the resources and internal core speeds for a selection of variations using a 1,024-byte FIFO buffer.

### **Table 1-3: Performance for Stratix IV Devices**

These results were obtained using the Quartus Prime software version 16.0 for the Stratix IV device (EP4SGX70HF35C2).

Altera Corporation SerialLite II IP Core Overview

| Lane | Packet<br>Type | Transfer<br>Size | CRC | ROE | FC | Through<br>-put at<br>Mbps | RX<br>Buffer<br>Size<br>(Data) | RX<br>Buffer<br>Size<br>(Prio) | Combina-<br>tional<br>ALUT | Memory<br>9K | Memory<br>ALUT | Logic<br>Register |

|------|----------------|------------------|-----|-----|----|----------------------------|--------------------------------|--------------------------------|----------------------------|--------------|----------------|-------------------|

| 1    | Data           | 1                | 0   | 0   | 0  | 1250                       | _                              | _                              | 841                        | 10           | 18             | 856               |

| 1    | Data           | 2                | 0   | 0   | 0  | 3125                       | _                              | _                              | 847                        | 11           | 0              | 820               |

| 1    | Data           | 4                | 0   | 0   | 0  | 6375                       | _                              | _                              | 935                        | 21           | 20             | 959               |

| 4    | Data           | 1                | 0   | 0   | 0  | 1250                       | _                              | _                              | 1399                       | 21           | 56             | 1291              |

| 4    | Data           | 2                | 0   | 0   | 0  | 3125                       | _                              | _                              | 1636                       | 31           | 112            | 1507              |

| 4    | Data           | 4                | 0   | 0   | 0  | 6375                       | _                              | _                              | 2184                       | 50           | 0              | 1748              |

| 16   | Data           | 2                | 0   | 0   | 0  | 3125                       | _                              | _                              | 4416                       | 87           | 308            | 3656              |

| 16   | Data           | 4                | 0   | 0   | 0  | 6375                       | _                              | _                              | 6685                       | 181          | 0              | 5066              |

| 1    | Data           | 1                | 32  | 0   | 1  | 1250                       | 1024                           | _                              | 1135                       | 11           | 35             | 1265              |

| 1    | Data           | 2                | 32  | 0   | 1  | 3125                       | 1024                           | _                              | 1189                       | 12           | 16             | 1206              |

| 1    | Data           | 4                | 32  | 0   | 1  | 6375                       | 2048                           | _                              | 1413                       | 22           | 36             | 1357              |

| 4    | Data           | 1                | 32  | 0   | 1  | 1250                       | 2048                           | _                              | 1814                       | 22           | 72             | 1675              |

| 4    | Data           | 2                | 32  | 0   | 1  | 3125                       | 4096                           | _                              | 2380                       | 32           | 128            | 1995              |

| 4    | Data           | 4                | 32  | 0   | 1  | 6375                       | 8192                           | _                              | 3402                       | 51           | 16             | 2326              |

| 1    | Priority       | 2                | 16  | 1   | 1  | 3125                       | _                              | 1024                           | 1519                       | 21           | 16             | 1396              |

| 1    | Priority       | 4                | 16  | 1   | 1  | 6375                       | _                              | 2048                           | 1745                       | 32           | 36             | 1541              |

| 4    | Priority       | 2                | 16  | 1   | 1  | 3125                       | _                              | 4096                           | 2687                       | 51           | 128            | 2165              |

| 4    | Priority       | 4                | 16  | 1   | 1  | 6375                       | _                              | 8192                           | 3661                       | 71           | 488            | 3626              |

### Table 1-4: Fmax for Stratix IV Devices

The performance results were obtained using these frequencies at 900 mV 85°C Corner.

| Lane | Packet Type | Transfer Size | Fmax<br>(txrdp_clk)<br>MHz | Fmax<br>(rxrdp_clk)<br>MHz | Fmax<br>(txhpp_clk)<br>MHz | Fmax (rxhpp_clk)<br>MHz |

|------|-------------|---------------|----------------------------|----------------------------|----------------------------|-------------------------|

| 1    | Data        | 1             | 252.78                     | 261.3                      | -                          | _                       |

| 1    | Data        | 2             | 294.38                     | 302.57                     | -                          | _                       |

| 1    | Data        | 4             | 292.06                     | 298.06                     | _                          | _                       |

| 4    | Data        | 1             | 287.77                     | 286.62                     | -                          | _                       |

| 4    | Data        | 2             | 285.47                     | 299.94                     | -                          | _                       |

| 4    | Data        | 4             | 325.31                     | 292.91                     | -                          | _                       |

SerialLite II IP Core Overview

Altera Corporation

| Lane | Packet Type | Transfer Size | Fmax<br>(txrdp_clk)<br>MHz | Fmax<br>(rxrdp_clk)<br>MHz | Fmax<br>(txhpp_clk)<br>MHz | Fmax (rxhpp_clk)<br>MHz |

|------|-------------|---------------|----------------------------|----------------------------|----------------------------|-------------------------|

| 16   | Data        | 2             | 312.99                     | 285.8                      | -                          | _                       |

| 16   | Data        | 4             | 260.35                     | 247.52                     | -                          | -                       |

| 1    | Data        | 1             | 258.67                     | 274.73                     | _                          | -                       |

| 1    | Data        | 2             | 281.61                     | 256.02                     | -                          | _                       |

| 1    | Data        | 4             | 282.97                     | 274.35                     | -                          | _                       |

| 4    | Data        | 1             | 291.12                     | 271.67                     | -                          | _                       |

| 4    | Data        | 2             | 269.61                     | 264.97                     | _                          | -                       |

| 4    | Data        | 4             | 271.67                     | 267.02                     | -                          | _                       |

| 1    | Priority    | 2             | _                          | _                          | 287.69                     | 252.33                  |

| 1    | Priority    | 4             | _                          | -                          | 271.59                     | 283.77                  |

| 4    | Priority    | 2             | _                          | -                          | 259.61                     | 288.1                   |

| 4    | Priority    | 4             | -                          | -                          | 337.5                      | 272.33                  |

Altera Corporation SerialLite II IP Core Overview

## SerialLite II IP Core Getting Started

2

2019.01.09

UG-0705

The SerialLite II IP core is installed as part of the Intel Quartus® Prime installation process.

You can select and parameterize any Altera IP core from the library. Altera provides an integrated parameter editor that allows you to customize the SerialLite II IP core to support a wide variety of applications.

#### **Related Information**

• Introduction to Altera IP Cores

Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Qsys Simulation Scripts

Create simulation scripts that do not require manual updates for software or IP version upgrades.

- Project Management Best Practices

Guidelines for efficient management and portability of your project and IP files.

### Parameterize the IP Core

The SerialLite II IP core parameter editor guides you through the setting of parameter values and selection of optional ports.

- 1. Click **Parameter Settings** in the SerialLite II parameter editor. The **Physical Layer** page appears.

- **2.** Key in a data rate in megabits per second (Mbps). The SerialLite II IP core supports data rates of 622 to 6,375 Mbps per lane.

- **Note:** For Intel Stratix 10 and Arria 10 devices, the IP core supports higher than 6.375 Gbps per lane.

- **3.** Choose a **Transfer size**. The **Transfer size** determines the number of contiguous data columns. The **Transfer size** also determines the serialization/deserialization (SERDES) factor and internal data path width.

- **4.** Specify the **Reference Clock Frequency**. This option defines the frequency of the reference clock for the Arria II GX or Stratix IV internal transceiver. You can select any frequency supported by the transceiver.

- This option is not available in Arria V, Cyclone V, and Stratix V configurations.

- 5. Select a **Port Type**. You have three choices: **Bidirectional**, **Transmitter only**, and **Receiver only**. If you choose **Transmitter only** or **Receiver only**, the **Self-Synchronized Link-Up** parameter (LSM) is enabled by default.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

\*Other names and brands may be claimed as the property of others.

- **6.** Turn on or off the **Self-Synchronized Link-Up** option. This parameter allows the receiver on the far end of the link to synchronize itself to incoming data streams, rather than on an exchange of status information with the transmitter.

- This feature is only for single lane applications.

- 7. Under **Transmitter Settings**, select the number of lanes for the transmitter.

- **8.** Turn on or off the **Scramble** and **Broadcast mode** options.

- **9.** Under **Receiver Settings**, select the number of lanes for the receiver.

**Table 2-1: Number of Transmit Lanes**

| Self-Synchronized Link-Up | Broadcast | Number of Lanes |

|---------------------------|-----------|-----------------|

| On                        | On        | 2 – 16          |

| On                        | Off       | 1               |

| Off                       | On        | 2 – 16          |

| Off                       | Off       | 2 – 16          |

- **10.**Turn on or off the **De-scramble** option.

- 11. Turn on or off the **Enable frequency offset tolerance** option.

- **12.**Click **Configure Transceiver**. Select the following parameters on the **Configure Transceiver** page to configure the ALTGX IP core for Arria II GX and Stratix IV devices.

- For the transmitter, select the Voltage Output Differential (VOD) control setting value.

- Under Pre-emphasis, select a value for Specify pre-emphasis control setting.

- In the **Bandwidth mode** list, select **high** or **low** for the Tx PLL bandwidth.

- Select a value for the **Transmitter Buffer Power (VCCH)**.

- Under Receiver Functionality, select a value for Specify equalizer control setting.

- In the **Bandwidth mode** list, select **high**, **medium** or **low** for the Rx PLL bandwidth.

- To reconfigure functionality settings, specify a **Starting channel number**.

- Click Finish.

The **Configure Transceiver** page is disabled when you select Arria V, Cyclone V, or Stratix V as the target device family. To add a transceiver, you are required to instantiate the Custom PHY IP core.

**Note:** If you want to use Intel Stratix 10, Arria 10 devices, refer to the SerialLite II IP core release information in **SerialLite II IP Core Overview** on page 1-1 for more details.

- **13.**Click **Next** to open the **Link Layer** page.

- 14. Under Data Type, select Packets or Streaming.

- 15. If you select **Packets**, select a packet type: **Priority packets and data packets**, **Priority packets**, or **Data packets**.

- **16.**If you select a packet type that includes priority packets, follow these substeps; otherwise, skip to Step 17.

- Turn on or off the Retry-on-error option.

- If you turned on **Retry-on-error**, specify a value for **Timeout** and **Segment size**.

- Under **Buffer Size**, specify a value for **Transmitter** and **Receiver**.

- Turn on or off the **Enable flow control** option.

- If you turned on **Enable flow control**, specify the values for **Pause quantum time**, **Threshold**, and **Refresh period**.

- If you selected **Priority packets only**, skip Step 17.

17. If you selected a packet type that includes data packets, follow these substeps;

- Turn on or off the **Enable flow control** option.

- If you turned on **Enable flow control**, specify the values for **Pause quantum time**, **Threshold**, and **Refresh period**.

- Under **Buffer Size**, specify a value for **Transmitter** and **Receiver**.

**18.**If your transmitter or receiver requires cyclic redundancy code (CRC) checking, turn on the **Enable CRC** option for your chosen packet type and specify a value for **CRC Type**.

#### **Related Information**

SerialLite II Parameter Settings on page 2-6

### **Set Up Simulation**

An IP functional simulation model is a cycle-accurate VHDL or Verilog HDL model produced by the Intel Quartus Prime software. The model allows for fast functional simulation of IP using industry-standard VHDL and Verilog HDL simulators.

To generate an IP functional simulation model for your IP core:

- 1. On the EDA page, under Simulation Libraries, turn on Generate Simulation Model.

- 2. Some third-party synthesis tools can use a netlist that contains only the structure of the IP core, but not detailed logic, to optimize performance of the design that contains the IP core. If your synthesis tool supports this feature, turn on **Generate netlist**.

- **3.** Click **Next** to display the **Summary** page.

**Note:** For Arria V, Cyclone V, and Stratix V devices, the generated simulation model does not come with transceiver. You need to integrate yourself. When you generate the transceiver, also include the reset controller for the respective devices. For Intel Stratix 10 and Arria 10 devices, contact your local Altera representative or file a Service Request (SR).

### **Generate Files**

You can use the check boxes on the **Summary** page to enable or disable the generation of specified files. A gray checkmark indicates a file that is automatically generated; other checkmarks indicate optional files.

Send Feedback

To generate your parameterized IP core:

- 1. Turn on the files you want to generate.

- **2.** To generate the specified files and close the SerialLite II parameter editor, click **Finish**. The generation phase can take several minutes to complete.

- 3. If you generate the IP core instance in a Quartus Prime project, you are prompted to add the Quartus Prime IP File (.qip) to the current Quartus Prime project.

The .qip file is generated by the SerialLite II parameter editor and contains information about a generated IP core. In most cases, the .qip file contains all of the necessary assignments and information required to process the IP core or system in the Quartus Prime compiler. The SerialLite II parameter editor generates a single .qip file for each IP core.

**Note:** For Arria V, Cyclone V, and Stratix V devices, you must also generate the Custom PHY and reset controller, and then add the transceiver . qip files in. You must manually integrate the transceiver to the SerialLite II IP core, and the reset controller to the transceiver. For Intel Stratix 10 and Arria 10 devices, contact your local Altera representative or file a Service Request (SR).

**4.** After your review the generation report, <*variation name*>. html, in your project directory, click **Exit** to close the SerialLite II parameter editor.

### Simulate the Design

You can simulate your design using the Quartus-generated VHDL and Verilog HDL IP functional simulation models.

Altera also provides a Verilog HDL demonstration testbench that shows you how to instantiate a model in a design for all configurations. Altera also provides a VHDL demonstration testbench for a restricted number of configurations. The testbench stimulates the inputs and checks the outputs of the interfaces of the SerialLite II IP core, allowing you to evaluate the IP core's basic functionality.

**Note:** For Arria V, Cyclone V, and Stratix V devices, the generated testbench is incorrect because the top level design has the transceiver integrated with it. The generated simulation model does not have the transceiver integrated with it, so you need to change the testbench accordingly. For these devices, you also need to modify the generated simulation script to add the Custom PHY transceiver files. For Intel Stratix 10 and Arria 10 devices, contact your local Altera representative or file a Service Request (SR).

#### **Related Information**

SerialLite II IP Core Testbench on page 4-1

### Instantiate the IP Core

You can now integrate your custom IP core variation into your design and simulate your complete design using your own custom testbench.

### **Compile and Program**

After you are done with simulating and instantiating the IP core, you can compile and program your design

- 1. Click **Start Compilation** on the **Processing** menu in the Quartus Prime software to compile your design.

- **2.** After successfully compiling your design, program the targeted Altera device with the **Programmer** in the **Tools** menu and verify the design in hardware.

### **Specify Constraints**

The SerialLite II example design applies constraints to create virtual pins and set up timing analysis.

### **Assign Virtual Pins**

If you are compiling the SerialLite II IP core variation as a standalone component, you must specify virtual pin assignments. The SerialLite II parameter editor generates a tool command language (Tcl) script that automates this task.

To run the script:

- 1. On the **Tools** menu, click **Tcl Scripts** to open the **Tcl Scripts** dialog box.

- **2.** In the project directory, select < variation name > constraints.

- 3. Click Run.

**Note:** The script assumes the default names for the virtual pins. If you have connected the pins to names other than the default names, you must edit this script and change the virtual pin names when the core is still compiled in stand-alone mode.

#### **Fitter Constraints**

The Tcl script also optimizes fitter settings to produce the best performance ( $f_{MAX}$ ). Use this script as a guide to set constraints for the SerialLite II IP core variation in your design. The timing constraints are currently set for the SerialLite II IP core variation as a standalone component, so you must update the script with hierarchy information for your own design. The Tcl script also points to the generated Synopsys Design Constraints (SDC) timing constraint script if the TimeQuest timing analyzer is enabled.

The The Fitter optimizes your design based on the requirements in the .sdc files in your project. The script uses the fitter\_effort "Standard fit" Fitter setting.

**Note:** This fitter setting may conflict with your Quartus Prime software settings.

You can now integrate your IP core variation into your design and simulate and compile.

### **Timing Constraints**

The SerialLite II IP core generates an ASCII file (with the .sdc extension) that contains design constraints and timing assignments in the industry-standard SDC format. The constraints in the .sdc file are described using the Tcl tool command language and follow Tcl syntax rules.

To specify the TimeQuest timing analyzer as the default timing analyzer:

- 1. On the Assignments menu, click Timing Analysis Settings.

- 2. In the Timing Analysis Settings page, turn on Use TimeQuest Timing Analyzer during compilation. The TimeQuest timing constraints are currently set for the SerialLite II IP core variation as a standalone component. You must update the script with hierarchy information if your own design is not a standalone component.

**Send Feedback**

Note: The .sdc generated for an Arria V, Cyclone V, or Stratix V device is incomplete. You need to change the "set\_clock\_groups" assignment which specifies "<variant\_name>\*receive| clkout" and "<variant\_name>\*transmit|clkout" to the correct name of the clkout signals coming from the transceiver. Other similar clocks from the transceiver in the generated .sdc are also incorrect and need to be replaced by the actual name and path accordingly. For Intel Stratix 10 and Arria 10 devices, contact your local Altera representative or file a Service Request (SR).

### SerialLite II Parameter Settings

You set the parameters using the SerialLite II parameter editor.

**Table 2-2: SerialLite II Parameters**

| Parameter      | Description                                                                                                                                                                                                                |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical Layer |                                                                                                                                                                                                                            |

| Device family  | Select the targeted device family.                                                                                                                                                                                         |

|                | Note: For Intel Stratix 10 and Arria 10 devices, contact your local Altera representative or file a Service Request (SR).                                                                                                  |

| Data rate      | Key in a data rate in megabits per second (Mbps). The SerialLite II IP core supports data rates of 622 to 6,375 Mbps per lane.                                                                                             |

|                | Note: The data rate must be an acceptable range for the Transfer size. The parameter editor returns a warning or an error message if you specify a data rate that is not within the range for the specified Transfer size. |

| Transfer size  | The <b>Transfer size</b> (TSIZE) parameter determines the number of contiguous data columns and the internal data path width per lane.                                                                                     |

|                | • TSIZE 1— equates to an internal data path of 8 bits (Recommended for less than 2.5 gigabits per second (Gbps))                                                                                                           |

|                | • TSIZE 2 —equates to an internal data path of 16 bits (Recommended for less than or equal to 3.125 Gbps)                                                                                                                  |

|                | TSIZE 4 —equates to an internal data path of 32 bits (Typically for greater than 3.125 Gbps, and only available for Arria V, Cyclone V, Stratix IV, and Stratix V devices)                                                 |

|                | A transfer size also determines the width of the SERDES block:                                                                                                                                                             |

|                | TSIZE 1—10 bit-wide SERDES block                                                                                                                                                                                           |

|                | <ul> <li>TSIZE 2—20 bit-wide SERDES block</li> <li>TSIZE 4—40 bit-wide SERDES block</li> </ul>                                                                                                                             |

| Parameter                                           | Description                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reference clock frequency                           | This option defines the frequency of the reference clock for the Arria II GX or Stratix IV internal transceiver. You can select any frequency supported by the transceiver.                                                                                                                |

|                                                     | Note: If you select a reference clock frequency that is not equal to the data rate/(transfer size) * 10, this option is disabled if you turned on the <b>Receiver only</b> port type option.                                                                                               |

| Port type                                           | Select a port type: Bidirectional, Transmitter only, or Receiver only.                                                                                                                                                                                                                     |

|                                                     | Note: If you choose Transmitter only or Receiver only, the self-synchronized link-up parameter (LSM) is enabled by default.                                                                                                                                                                |

| Self-synchronized link-up                           | This parameter allows the receiver on the far end of the link to synchronize itself to incoming data streams, rather than on an exchange of status information with the transmitter.                                                                                                       |

|                                                     | <b>Note:</b> This feature is only for single lane applications.                                                                                                                                                                                                                            |

| Number of lanes (Transmitter and Receiver settings) | Select the number of lanes for the transmitter and receiver. This parameter dictates the number of serial links, essentially the number of external inputs and outputs (I/Os) for the IP core. Because each lane operates at the bit rate, you can increase the bandwidth by adding lanes. |

|                                                     | Note: If adding a lane provides more bandwidth than needed, you can reduce the system clock rate, thereby mitigating possible high-speed design issues and making it easier to meet performance.                                                                                           |

| Scramble                                            | Turn on to scramble the data. Scrambling the data eliminates repeating characters that affect the EMI substantially at high data rates. This parameter applies only to the transmitter, and allows for scrambling (like CRC) to be enabled in one direction only, as required.             |

|                                                     | Scrambling is recommended for data rates greater than 3,125 Mbps, and is optional for lower data rates (622 to 3,125 Mbps).                                                                                                                                                                |

| De-scramble                                         | Turn to to descramble the data. This parameter applies only to the receiver, and allows for descrambling (like CRC) to be enabled in one direction only, as required.  Descrambling is required if the incoming data stream is scrambled.                                                  |

|                                                     | Descramoning is required if the incoming data stream is scrambled.                                                                                                                                                                                                                         |

| Parameter                         | Description                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Broadcast mode                    | Turn on to use broadcast mode. This parameter applies only to the transmitter.                                                                                                                                                                                                                                                |

|                                   | If you enable this parameter, you configure the IP core to use a single shared transmitter and multiple receivers in the master device.                                                                                                                                                                                       |

| Enable frequency offset tolerance | This parameter sets the value for the frequency offset tolerance (clock compensation). This parameter also determines whether the system is configured for synchronous or asynchronous clocking operation.                                                                                                                    |

|                                   | If you turn on this option, select an offset tolerance of $\pm 100$ or $\pm 300$ parts per million (ppm).                                                                                                                                                                                                                     |

| Link Layer                        |                                                                                                                                                                                                                                                                                                                               |

| Data type                         | Select whether to format the data as a stream or in packets. If you select <b>Streaming</b> , all link layer basic parameters, including data and priority ports, and buffering are disabled (grayed out). Streaming mode does not include link-layer functions.                                                              |

| Packet type                       | Select whether to send your packets as priority packets, data packets, or both.                                                                                                                                                                                                                                               |

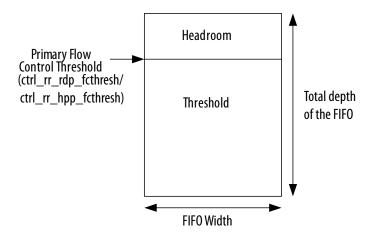

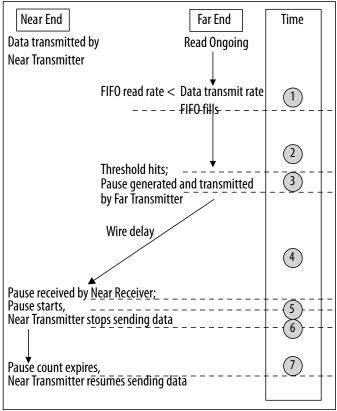

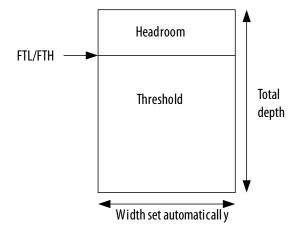

| Enable flow control               | The SerialLite II IP core provides this parameter as an optional means of exerting backpressure on a data source when data consumption is too slow. Turn on this parameter to ensure that the receive FIFO buffers do not overflow.                                                                                           |

|                                   | Note: Flow control is only needed when the system logic on the receiving end of the link is reading the data slower than the system logic on the transmitting end of the link is sending data.                                                                                                                                |

| Pause quantum time                | Activation of flow control causes a pause in transmission. Specify a pause duration from to 8 to 2,040 columns.                                                                                                                                                                                                               |

| Threshold                         | You must set the <b>Threshold</b> parameter to a value such that the FIFO does not completely empty during a flow control operation (this can cause inefficiencies in the system), and leave enough room in the FIFO to ensure any remaining data in the system can be safely stored in the FIFO without the FIFO overflowing |

| Refresh period                    | The flow control refresh period determines the number of columns before a flow control packet can be retransmitted (for example if a flow control link management packet is lost or corrupted). This period must be less than the pause quantum time. The packet is retransmitted if the FIFO buffer is still breached.       |

| Parameter                              | Description                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Retry-on-error                         | This parameter improves the bit error rate of your data.                                                                                                                                                                                                                                                                                                           |

|                                        | <ul> <li>On: Logic is created to acknowledge segments and retransmit segments when errors occur. Eight transmit segment buffers are created.</li> <li>Off: Logic is not created to acknowledge segments. This is the default setting.</li> </ul>                                                                                                                   |

|                                        | If you turn off this parameter, no segment acknowledgments are generated or expected, and all segments are transmitted without any acknowledgments from the receiver.                                                                                                                                                                                              |

|                                        | This parameter is only available for priority packets.                                                                                                                                                                                                                                                                                                             |

| Timeout                                | Set the time out value for the segment to be acknowledged. The time-out value is based primarily on the round trip latency—from the time a packet is sent to when the acknowledge signal is returned to that transmitter. The exact value of the round trip latency is undetermined, pending device characterization, but a value of 1,024 columns is recommended. |

|                                        | <ul> <li>Do not to set the time out to be too long so the system does not have to wait too long for link errors to resolve.</li> <li>Do not set the time out to be too short because then the system always times out and the link payor remains up.</li> </ul>                                                                                                    |

|                                        | always times out and the link never remains up.                                                                                                                                                                                                                                                                                                                    |

| Segment size                           | This parameter is only applicable when the <b>Retry-on-error</b> parameter is turned on. This parameter settings range from 8 to 2,048 bytes in 2 <sup>n</sup> increments, and the default value is 256 bytes.                                                                                                                                                     |

|                                        | Priority packets are broken into segments of segment size bytes and sent across the link. Priority packets less than or equal to segment size bytes and without an end marker are buffered before transmission. This buffering is required to support the <b>Retry-on-error</b> option, which is only allowed for priority packets.                                |

|                                        | If a packet is larger than a segment size, a full segment must be queued before it can be transmitted. This queuing may result in mid-packet backpressure on the priority port Atlantic interface. Segment interleaving, priority segments destined for different ports, is fully supported, as long as the address change occurs on a segment boundary.           |

| Buffer size (Transmitter and Receiver) | Specify a FIFO buffer size value for the transmitter and receiver.                                                                                                                                                                                                                                                                                                 |

| Parameter                                             | Description                                                                                                                                                           |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable CRC for priority/data packets (Transmitter and | If your transmitter or receiver requires cyclic redundancy code (CRC) checking, turn on the <b>Enable CRC</b> option for your chosen packet type.                     |

| Receiver)                                             | On: CRC logic is created. CRC usage is specified independently for each port.                                                                                         |

|                                                       | Off: CRC logic is not created. CRC usage is specified independently for each port. This is the default CRC setting.                                                   |

| CRC Type                                              | Select 16 bits or 32 bits for the CRC type.                                                                                                                           |

|                                                       | • 16 bits: Generates a two-byte CRC. Adequate for packets of around 1 KBytes or smaller. This is the default algorithm when CRC is enabled.                           |

|                                                       | 32 bits: Generates a 4-byte CRC. Should only be used for packets larger than about 1 KBytes or when extreme protection is required, because it is resource-intensive. |

| Configure Transceiver (only appl                      | icable for Arria II GX and Stratix IV devices)                                                                                                                        |

| Specify VOD control setting                           | Select the Voltage Output Differential (VOD) control setting value.                                                                                                   |

|                                                       | <b>Note:</b> This parameter is disabled when the number of lanes in the transmit direction is equal to zero.                                                          |

| Specify pre-emphasis control                          | Select pre-emphasis control setting value.                                                                                                                            |

| setting                                               | For Stratix IV devices, the pre-emphasis control values supported are 0,1,2,3,4, and 5.                                                                               |

|                                                       | • 0 = Pre-emphasis option is turned off                                                                                                                               |

|                                                       | <ul> <li>1 = Maximum negative value</li> <li>2 = Medium negative value</li> </ul>                                                                                     |

|                                                       | • 3 = Special value in which only the first post-tap is set (set to the maximum), while the other taps are off                                                        |

|                                                       | • 4 = Medium positive value                                                                                                                                           |

|                                                       | • 5 = Maximum positive value  For Arria II GY devices, the pre-emphasis setting cannot be changed.                                                                    |

|                                                       | For Arria II GX devices, the pre-emphasis setting cannot be changed.  This parameter is set to 0 by default. It is disabled when the number of                        |

|                                                       | lanes in the transmit direction is equal to zero.                                                                                                                     |

| Parameter                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bandwidth mode (Transmitter and Receiver) | The transmitter and receiver PLLs in the ALTGX IP core offer programmable bandwidth settings. The PLL bandwidth is the measure of its ability to track the input clock and jitter, determined by the -3 dB frequency of the PLL's closed-loop gain.                                                                                                                                                                                                                                                                                     |

|                                           | Select <b>low</b> or <b>high</b> bandwidth mode for the transmitter and <b>low</b> , <b>medium</b> , or <b>high</b> bandwidth mode for the receiver.                                                                                                                                                                                                                                                                                                                                                                                    |

|                                           | <ul> <li>The low bandwidth setting filters out more high frequency input clock jitter, but increases lock time. The PLL is set to the low setting by default.</li> <li>The medium setting balances the lock time and noise rejection/jitter filtering between the high and low settings.</li> <li>The high bandwidth setting provides a faster lock time and tracks more jitter on the input clock source which passes it through the PLL to help reject noise from the voltage control oscillator (VCO) and power supplies.</li> </ul> |

|                                           | If the number of lanes in the transmit or receive direction is equal to zero, the bandwidth mode for that direction is disabled.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                           | <b>Note:</b> This parameter is not applicable for Arria II GX devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Transmitter buffer power (VCCH)           | This setting is used to calculate the VOD from the buffer power supply and the transmitter termination to derive the proper VOD range.                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                           | <ul> <li>Arria II GX devices = 1.5 V</li> <li>Stratix IV devices = 1.4 V or 1.5 V</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Specify equalizer control setting         | Select the equalizer control setting value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                           | The transceiver offers an equalization circuit in each receiver channel to increase noise margins and help reduce the effects of high frequency losses. The programmable equalizer compensates for inter-symbol interference (ISI) and high frequency losses that distort the signal and reduce the noise margin of the transmission medium by equalizing the frequency response.                                                                                                                                                       |

|                                           | For Stratix IV devices, the equalization control values supported are 0, 1, 2, 3, and 4. These values correspond to lowest/off (0), between medium and lowest (1), medium (2), between medium and high (3), and high (4).                                                                                                                                                                                                                                                                                                               |

|                                           | For Arria II GX devices, the equalization cannot be changed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Parameter               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Starting channel number | To reconfigure the functionality settings, select a starting channel number. The range for the dynamic reconfiguration starting channel number setting is 0 to 380. These ranges are in multiples of four because the dynamic reconfiguration interface is per transceiver block. The range 0 to 380 is the logical channel address, based purely on the number of possible transceiver instances.  Note: This parameter is not applicable for Arria II GX devices. |

#### **Related Information**

Parameterize the IP Core on page 2-1

### **Link Consistency**

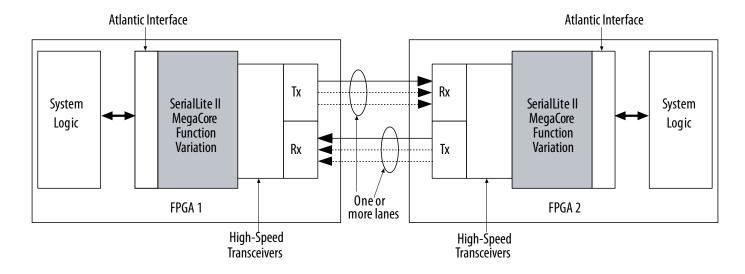

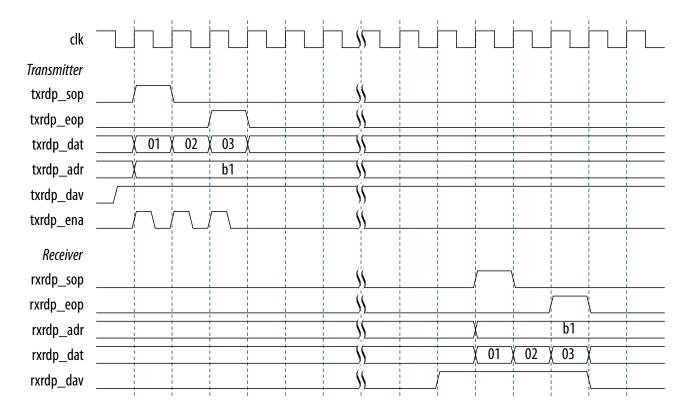

A SerialLite II link consists of two instantiations of logic implementing the SerialLite II protocol.

Each end of the link has a transmitter and a receiver.

Figure 2-1: Complete SerialLite II Link

#### **Data Rate**

The data rate range varies based on the device and the transfer size (TSIZE).

The SerialLite II IP core supports a data rate range of 622 to 6,375 Mbps per lane. In Arria II GX devices, the data rate must be less than 3,750 Mbps, and in Stratix IV devices, less than 6,375 Mbps.

Table 2-3: Data Rate Dependencies on Transfer Size

| Devices          | Data Rate   |            |           |               |               |

|------------------|-------------|------------|-----------|---------------|---------------|

| Devices          | 2.5 Gbps    | 3.125 Gbps | 3.75 Gbps | 5 Gbps        | 6.375 Gbps    |

| Arria II GX      | TSIZE= 1, 2 | TSIZE= 2   | TSIZE= 2  | Not Supported | Not Supported |

| Stratix IV<br>GX | TSIZE= 1, 2 | TSIZE= 2   | TSIZE= 4  | TSIZE= 4      | TSIZE= 4      |

| Stratix IV<br>GT | -           | TSIZE= 2   | TSIZE= 4  | TSIZE= 4      | TSIZE= 4      |

The data rates for an individual Arria II GX device are limited to the respective speed grades,

Table 2-4: Arria II GX Speed Grade-Data Rate Limits

| Device Speed Grade | Minimum Data Rate (Mbps) | Maximum Data Rate (Mbps) |

|--------------------|--------------------------|--------------------------|

| C4                 | 600                      | 3,750                    |

| C5                 | 600                      | 3,125                    |

| C6                 | 600                      | 3,125                    |

### **Reference Clock Frequency**

Valid values for reference clock frequency change with the data rate but the reference input clock frequency must be within 50 MHz and 622 MHz. Range of supported reference clock frequency is dependent on device. Please refer to the device datasheet for range of supported frequency for every device.

The general formula to determine frequency:

```

Frequency = p \times Data Rate/(2 \times m)

where p = 1 or 2, and m = 4, 5, 8, 10, 16, 20, or 25

Condition for frequency to be valid:

```

(50xp) < Frequency < 622

### **Port Type**

The **Port Type** parameter offers three options: bidirectional, transmitter only, and receiver only.

- If you set the **Number of lanes** for the transmitter and receiver settings to the same value, you configure the IP core to operate in symmetric, bidirectional mode.

- If you set the **Port Type** to **Receiver only** or **Transmitter only**, you configure the IP core to operate in unidirectional mode, transmitter, or receiver only.

- If you set the **Port Type** to **Bidirectional**, but have the number of lanes set to a value other than zero, but not equal to the other function's value, you configure the IP core to operate in asymmetric mode.

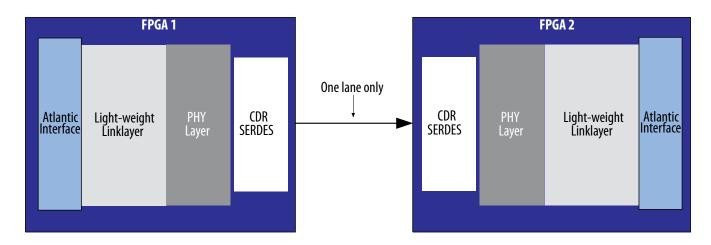

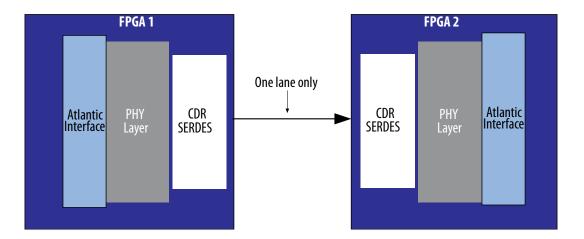

The following diagrams illustrate the symmetric and asymmetric modes.

SerialLite II IP Core Getting Started

Note: A full line indicates a mandatory lane, and a dotted line indicates an optional lane.

Figure 2-2: Symmetric Mode Block Diagram

Figure 2-3: Streaming Symmetric Mode Block Diagram

Figure 2-4: Simplex Mode Block Diagram

Figure 2-5: Streaming Simplex Mode Block Diagram

Figure 2-6: Asymmetric Mode Block Diagram

Figure 2-7: Streaming Asymmetric Mode Block Diagram

### Self Synchronized Link Up

The receiver on the far end must synchronize itself to incoming data streams. To do so, it uses the self-synchronizing LSM, a light-weight implementation that is especially useful when data is streaming.

The receiver on the far end must synchronize itself to incoming data streams. To do so, the receiver uses the self-synchronizing LSM, a light-weight implementation that is especially useful when data is streaming. Because there is no handshaking or exchange of status information between the receiver and transmitter, the **Self Synchronized Link Up** parameter uses considerably fewer logic elements than the full-duplex LSM. The self-synchronizing LSM can be used in all modes, except asymmetric mode, but this mode can only support one lane.

The **Self Synchronized Link Up** parameter is enabled by default when the IP core operates in unidirectional mode because the duplex LSM cannot be used when there is no return path.

Send Feedback

The ctrl\_tc\_force\_train signal must be asserted for the training patterns to be sent. Negate the signal in one of these two conditions:

- When the adjacent receiver has locked—if this status information can be made available.

- After a user-defined period of time when the link status of the adjacent receiver is not known or cannot be known.

The LSM links up after receiving 64 consecutive valid, error-free characters. The link goes down after receiving four consecutive errors; at this time, the <code>ctrl\_tc\_force\_train</code> signal should be reasserted until the receiver relocks. The required hold time for the <code>ctrl\_tc\_force\_train</code> signal largely depends on when the ALTGX or Custom PHY IP core completes the power-on reset cycle. The self-synchronizing link-up state machine does not look at the incoming stream until the transceiver reset is complete.

**Note:** The Arria II GX and Stratix IV devices use the ALTGX IP core. The later devices use the Custom PHY IP core.

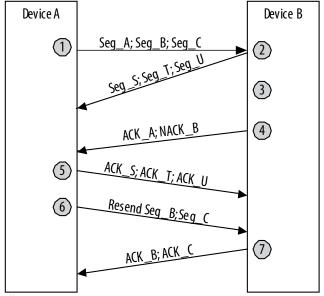

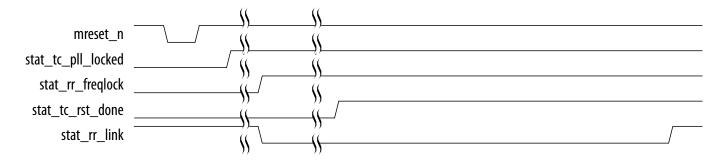

For example, the following procedure shows the transceiver reset sequence in a transceiver device: