# Intel® E8870IO Server I/O Hub (SIOH) Datasheet

## **Product Features**

- Scalability Port (SP):

- Two SPs with 3.2 GB/s peak bandwidth per direction per SP.

- Bi-directional SPs for a total bandwidth of 12.8 GB/s.

- Four Hub Interface 2.0 Ports:

- For connecting to Intel<sup>®</sup> 82870P2 PCI/ PCI-X 64-bit Hub 2 (P64H2).

- 16-bit, 533 MHz interface.

- 1 GB/s peak data rate.

- One Hub Interface 1.5 Port:

- For connecting to Intel<sup>®</sup> 82801DB.

Legacy I/O Controller Hub 4 (ICH4).

- 8-bit, 266 MHz interface.

- 266 MB/s peak data rate.

- Supports peer-to-peer write traffic between Hub Interface Ports.

- Dedicated read cache for each Hub Interface Port:

- 32 128-byte cache lines.

- Dedicated prefetch engines for Hub Interface 2.0 ports.

- Supports caching of frequently used and prefetched data residing in main memory.

- 64-line write cache.

- Aggressive prefetching algorithm optimized for PCI-X functionality supported by the 82870P2 component:

- Utilizing enhanced features such as read-streaming, and prefetch horizon.

- Supports multiple unordered inbound traffic streams:

- Two unordered streams per Hub Interface 2.0 port.

- One stream for the Hub Interface 1.5 port.

- System Management Bus (SMBus) 2.0 slave interface for server management with Packet Error Checking.

- Reliability, Availability, and Serviceability (RAS):

- Sideband access to configuration registers via SMBus SMBus or JTAG.

- End-to-end ECC for all interfaces.

- Fault detection and logging.

- Signal connectivity testing via. boundary scan.

- Packaging:

- 42.5 mm x 42.5 mm

- 1012-pin organic LAN grid array (OLGA) package-2B.

Document Number: 251111-001 August 2002

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Itanium 2 processor, E8870 chipset and E8870IO (SIOH) component may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling1-800-548-4725, or by visiting Intel's website at http://www.intel.com.

Intel, Itanium 2, E8870 and E8870IO are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries

Copyright © 2002, Intel Corporation. All rights reserved.

\*Other names and brands may be claimed as the property of others.

| 1 | Introdu                                                     | uction                                                                                                                                                                                  | 1-1                      |

|---|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|   | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9 | Overview Server I/O Hub Architectural Overview Interfaces. Scalability Port Interface. Hub Interface. SMBus Interface. JTAG Tap Port Terminology. Reference Documents. Revision History | 1-11-21-41-41-51-5       |

| 2 | Signal                                                      | Description                                                                                                                                                                             |                          |

|   | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                      | Conventions Scalability Port (SP) Interface Hub Interface 1.5 Reset and Miscellaneous Signals Clock Signals JTAG and SMBus Signals                                                      | 2-1<br>2-1<br>2-3<br>2-4 |

| 3 | Config                                                      | uration Registers                                                                                                                                                                       | 3-1                      |

|   | 3.1                                                         | Register Access Mechanisms  3.1.1 Scalability Port Initiated Register Access  3.1.2 JTAG Initiated Register Access  3.1.3 SMBus Operation                                               | 3-1<br>3-1               |

|   | 3.2                                                         | Device Mapping                                                                                                                                                                          | 3-2                      |

|   | 3.3                                                         | Register AttributesVendor ID Register (VID)                                                                                                                                             |                          |

|   | 3.4<br>3.5                                                  | Device ID Register (VID)                                                                                                                                                                |                          |

|   | 3.6                                                         | PCI Command Registers (PCICMD)                                                                                                                                                          |                          |

|   | 3.7                                                         | PCI Status Registers (PCISTS)                                                                                                                                                           | 3-6                      |

|   | 3.8                                                         | Revision ID Register (RID)                                                                                                                                                              |                          |

|   | 3.9                                                         | Class Code Registers (CCR)                                                                                                                                                              |                          |

|   | 3.10                                                        | Header Type Registers (HDR)                                                                                                                                                             |                          |

|   | 3.11                                                        | Subsystem Vendor ID Register (SVID)                                                                                                                                                     |                          |

|   | 3.12<br>3.13                                                | Subsystem ID Register (SID)                                                                                                                                                             |                          |

|   | 3.14                                                        | Hub Interface Command Control Registers (HLCMD)                                                                                                                                         |                          |

|   | 3.15                                                        | Hub Interface Recoverable Error Control Registers (RECHUB)                                                                                                                              |                          |

|   | 3.16                                                        | Hub Interface Recoverable Error Data Registers (REDHUB)                                                                                                                                 |                          |

|   | 3.17                                                        | Hub Interface Non-Recoverable Error Control Register (NRECHUB)                                                                                                                          |                          |

|   | 3.18                                                        | Hub Interface ECC Mask Register (HECCMSK)                                                                                                                                               |                          |

|   | 3.19                                                        | Hub Interface Performance Monitor Response and Control Registers (HL_PMR[1:0])                                                                                                          | 3-14                     |

|   | 3.20                                                        | Hub Interface Performance Monitor Event Registers – Low (HL_PME_LO[1:0])                                                                                                                | 3-16                     |

|   | 3.21                                                        | Hub Interface Performance Monitor Event Registers – High (HL_PME_HI[1:0])                                                                                                               | 3-18                     |

|   | 3.22                                                        | Hub Interface Performance Monitor Resource Event Registers (HL_PME_RSC[1:0]) | 3-18 |  |  |  |  |  |

|---|-------------------------------------------------------------|------------------------------------------------------------------------------|------|--|--|--|--|--|

|   | 3.23                                                        | Hub Interface Performance Monitor Data Registers (HL_PMD[1:0])               | 3-19 |  |  |  |  |  |

|   | 3.24                                                        | Hub Interface Performance Monitor Compare Register (HL_PMCMP[1:0])           | 3-19 |  |  |  |  |  |

|   | 3.25                                                        | SIOH Control Registers (IOCTL)                                               |      |  |  |  |  |  |

|   | 3.26                                                        | System Reset Register (SYRE)                                                 |      |  |  |  |  |  |

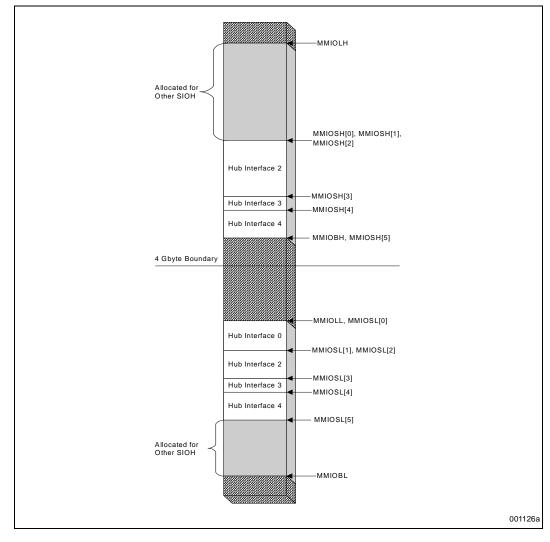

|   | 3.27                                                        | Memory-Mapped I/O Base Low Address Register (MMIOBL)                         |      |  |  |  |  |  |

|   | 3.28                                                        | Memory-Mapped I/O Limit Low Address Register (MMIOLL)                        |      |  |  |  |  |  |

|   | 3.29                                                        | Memory-Mapped I/O Segment Low Register (MMIOSL[5:0])                         |      |  |  |  |  |  |

|   | 3.30                                                        | Memory-Mapped I/O Base High Address Register (MMIOBH)                        |      |  |  |  |  |  |

|   | 3.31 Memory-Mapped I/O Limit High Address Register (MMIOLH) |                                                                              |      |  |  |  |  |  |

|   | 3.32                                                        | Memory-Mapped I/O Segment High Address Register (MMIOSH[5:0])                |      |  |  |  |  |  |

|   | 3.33                                                        | PCI Configuration Bus Base Register (BUSNO[5:0])                             |      |  |  |  |  |  |

|   | 3.34                                                        | SAPIC Segment Registers (SSEG[5:0])                                          |      |  |  |  |  |  |

|   | 3.35                                                        | I/O Link Registers (IOL[5:0])                                                |      |  |  |  |  |  |

|   | 3.36                                                        | Chip Boot Configuration Registers (CBC)                                      |      |  |  |  |  |  |

|   | 3.37                                                        | Boot Flag Registers (BOFL)                                                   |      |  |  |  |  |  |

|   | 3.38                                                        | Scratch Pad Register (SPAD)                                                  |      |  |  |  |  |  |

|   | 3.39                                                        | Scratch Pad Register Sticky (SPADS)                                          |      |  |  |  |  |  |

|   | 3.40                                                        | Performance Monitor Control Registers (PERFCON)                              |      |  |  |  |  |  |

|   | 3.41                                                        | SP Performance Monitor Response and Control Registers (SP_PMR[1:0])          |      |  |  |  |  |  |

|   | 3.42                                                        | SP Performance Monitor Event Registers (SP_PME[1:0])                         |      |  |  |  |  |  |

|   | 3.43                                                        | SP Performance Monitor Resource Event Registers (SP_PME_RSC[1:0])            |      |  |  |  |  |  |

|   | 3.44                                                        | SP Performance Monitor Data Registers (SP_PMD[1:0])                          |      |  |  |  |  |  |

|   | 3.45                                                        | SP Performance Monitor Compare Register (SP_PMCMP[1:0])                      |      |  |  |  |  |  |

|   | 3.46 Error Command Registers (ERRCOM)                       |                                                                              |      |  |  |  |  |  |

|   | 3.47                                                        | First Error Status Registers (FERRST)                                        |      |  |  |  |  |  |

|   | 3.48                                                        | Two or More Errors Status Register (SERRST)                                  |      |  |  |  |  |  |

|   | 3.49                                                        | Error Mask Registers (ERRMASK)                                               |      |  |  |  |  |  |

|   | 3.50                                                        | SPP Recoverable Error Control Register (RECSPP)                              |      |  |  |  |  |  |

|   | 3.51                                                        | SPP Non-Recoverable Error Control Register (NRECSPP)                         |      |  |  |  |  |  |

|   | 3.52                                                        | SP Interface Control Registers (SPINCO[1:0])                                 |      |  |  |  |  |  |

|   | 3.53                                                        | SPL Recoverable Error Control Register (RECSPL[1:0])                         |      |  |  |  |  |  |

|   | 3.54                                                        | SPL Recoverable Error Data Registers (REDSPL[1:0])                           |      |  |  |  |  |  |

| 4 | Addre                                                       | ss Map                                                                       |      |  |  |  |  |  |

|   | 4.1                                                         | Address Ranges                                                               |      |  |  |  |  |  |

|   |                                                             | 4.1.1 Memory-Mapped I/O                                                      |      |  |  |  |  |  |

|   |                                                             | 4.1.2 I/O Space                                                              |      |  |  |  |  |  |

|   |                                                             | 4.1.3 SAPIC/IOAPIC and PCI Hot-Plug Ranges                                   |      |  |  |  |  |  |

|   |                                                             | 4.1.4 Compatibility Bus                                                      |      |  |  |  |  |  |

|   |                                                             | 4.1.5 VGA Space                                                              |      |  |  |  |  |  |

|   | 4.2                                                         | Illegal Addresses                                                            |      |  |  |  |  |  |

| 5 |                                                             | ing                                                                          |      |  |  |  |  |  |

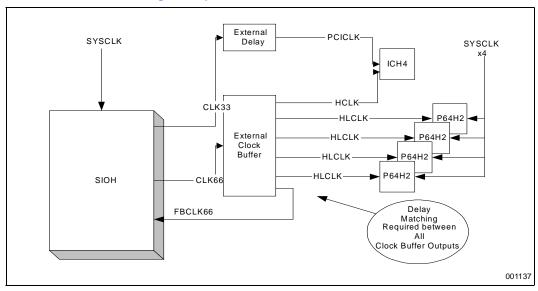

|   | 5.1                                                         | SIOH Clocking                                                                |      |  |  |  |  |  |

|   | 5.2                                                         | Reference Clock (SYSCLK)                                                     |      |  |  |  |  |  |

|   | 5.3                                                         | Clock Outputs                                                                |      |  |  |  |  |  |

|   | 5.4                                                         | Feedback and Matching                                                        | 5-2  |  |  |  |  |  |

# intط

|   | 5.5     | JTAG Test Access Port                               |      |

|---|---------|-----------------------------------------------------|------|

|   | 5.6     | SMBus Clocking                                      |      |

|   | 5.7     | Spread Spectrum Support                             |      |

|   | 5.8     | No Stop Clock or Thermal Shutdown                   |      |

|   | 5.9     | Deterministic Systems                               |      |

| 6 | Reset   |                                                     |      |

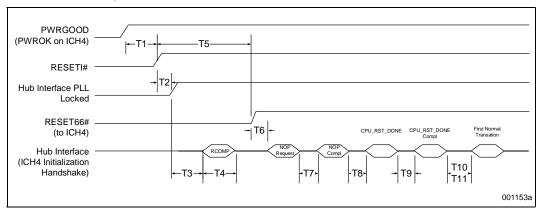

|   | 6.1     | Reset Sequence Overview                             |      |

|   | 6.2     | Power-Up Sequence                                   |      |

|   |         | 6.2.1 PWRGOOD Deasserted                            |      |

|   |         | 6.2.2 PWRGOOD Assertion                             |      |

|   | 0.0     | 6.2.3 First RESETI# Deassertion                     |      |

|   | 6.3     | Hard Reset                                          |      |

|   |         | 6.3.1 Hard Reset Assertion                          |      |

|   |         | 6.3.2 Hard Reset Deassertion                        |      |

|   | C 4     | 6.3.3 Non-Existent Hub Interface Devices            |      |

|   | 6.4     | Reset Signals                                       |      |

|   |         | 6.4.1 PWRGOOD<br>6.4.2 RESETI#                      |      |

|   |         | 6.4.2 RESETI#<br>6.4.3 RESET66#                     |      |

|   |         | 6.4.4 DET                                           |      |

|   |         |                                                     |      |

| 7 |         | oility, Availability and Serviceability (RAS)       |      |

|   | 7.1     | Data Integrity                                      |      |

|   |         | 7.1.1 End-to-End Error Correction                   |      |

|   |         | 7.1.2 Error Reporting                               |      |

|   |         | 7.1.3 Interface Details                             |      |

|   |         | 7.1.4 Time-Out                                      |      |

| 8 | Electri | ical Specifications                                 | 8-1  |

|   | 8.1     | Non-Operational Maximum Rating                      | 8-1  |

|   | 8.2     | Operational Power Delivery Specification            | 8-1  |

|   | 8.3     | Scalability Port (SP) Signal Group                  |      |

|   | 8.4     | Hub Interface 2.0 (HI 2.0) Signal Group             |      |

|   |         | 8.4.1 Hub Interface 2.0 DC Specifications           |      |

|   | 8.5     | Hub Interface 1.5 (HI 1.5) Signal Group             | 8-4  |

|   |         | 8.5.1 HI 1.5 Signal Groups                          |      |

|   |         | 8.5.2 Hub Interface 1.5 DC Specifications           |      |

|   | 8.6     | Analog Inputs                                       |      |

|   |         | 8.6.1 Hub Interface Impedance Compenstation (RCOMP) |      |

|   |         | 8.6.2 Hub Interface Vref/Vswing Decoupling          |      |

|   | 8.7     | SMBus and TAP Signal Group                          |      |

|   |         | 8.7.1 SMBus and TAP DC Specifications               |      |

|   |         | 8.7.2 SMBus and TAP AC Specifications               |      |

|   |         | 8.7.3 SMBus and TAP AC Timing Waveforms             |      |

|   | 8.8     | Miscellaneous Signal Group                          |      |

|   |         | 8.8.1 Miscellaneous Signal DC Specifications        |      |

|   |         | 8.8.2 Miscellaneous Signal AC Specifications        |      |

|   | 8.9     | Clock Signal Groups                                 |      |

|   |         | 8.9.1 AC Specification                              | 8-13 |

| 9              | Packa      | age and Ballout                                                                        | 9-1 |

|----------------|------------|----------------------------------------------------------------------------------------|-----|

|                | 9.1        | 1012-Ball OLGA2b Package Information                                                   | 9-1 |

|                | 9.2        | Ballout – Signal List                                                                  |     |

|                | 9.3        | Signal – Ball Number List                                                              |     |

| <b>Figures</b> |            |                                                                                        |     |

|                | 1-1        | Typical Intel <sup>®</sup> E8870 Chipset-Based Eight-Way Itanium <sup>®</sup> 2 Server |     |

|                |            | System Configuration                                                                   |     |

|                | 1-2        | SIOH Interfaces                                                                        |     |

|                | 1-3        | SIOH Functional Blocks                                                                 |     |

|                | 4-1        | SIOH Memory-Mapped I/O Space Example                                                   |     |

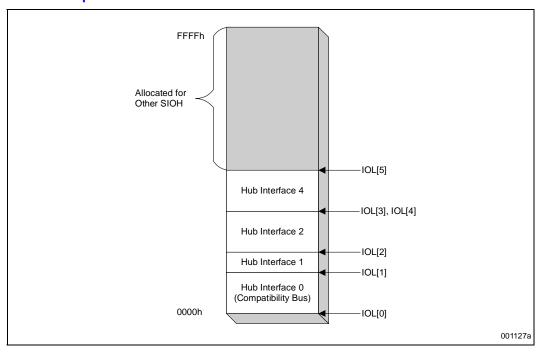

|                | 4-2        | SIOH I/O Space                                                                         |     |

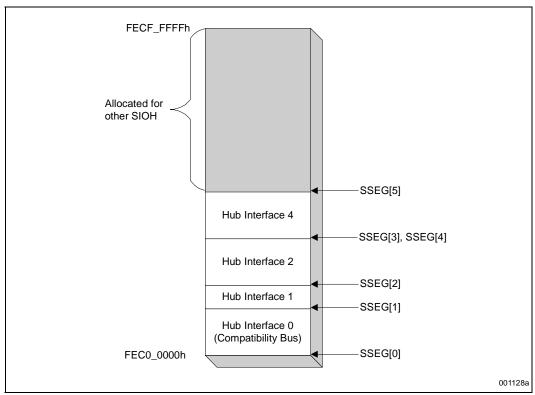

|                | 4-3        | SIOH SAPIC Space                                                                       |     |

|                | 5-1        | SIOH Platform Clocking Example                                                         |     |

|                | 6-1        | SIOH Reset Sequence                                                                    |     |

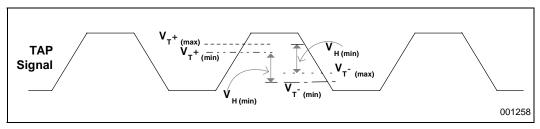

|                | 8-1        | TAP DC Thresholds                                                                      |     |

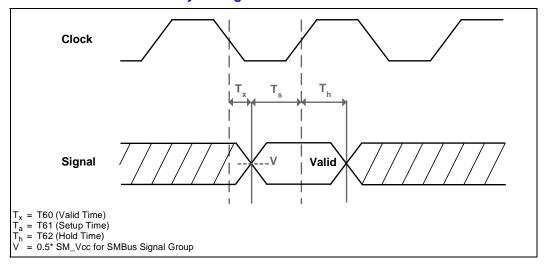

|                | 8-2        | TAP and SMBus Valid Delay Timing Waveform                                              |     |

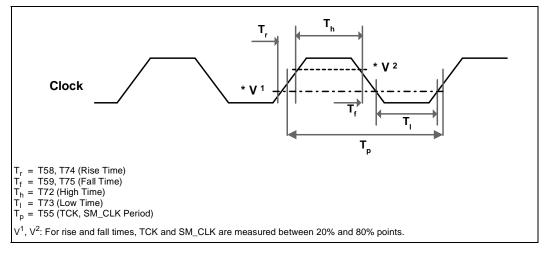

|                | 8-3        | TCK and SM_CLK Clock Waveform                                                          |     |

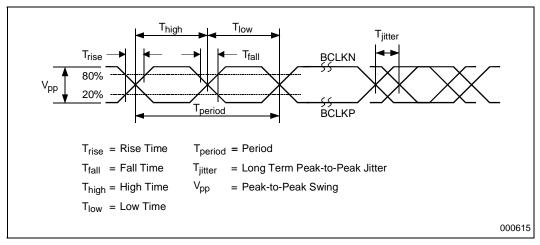

|                | 8-4        | Generic Differential Clock Waveform                                                    |     |

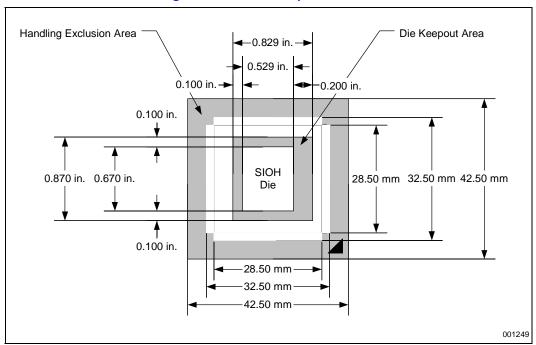

|                | 9-1        | 1012-Ball OLGA2b Package Dimensions – Top View                                         |     |

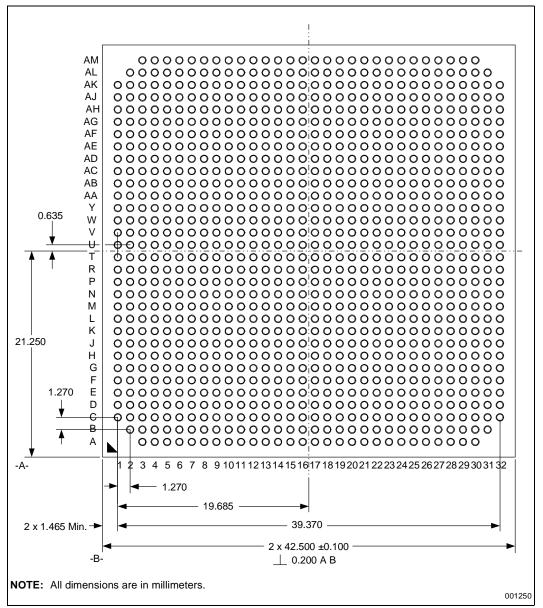

|                | 9-2        | 1012-Ball OLGA2b Package Dimensions – Bottom View                                      |     |

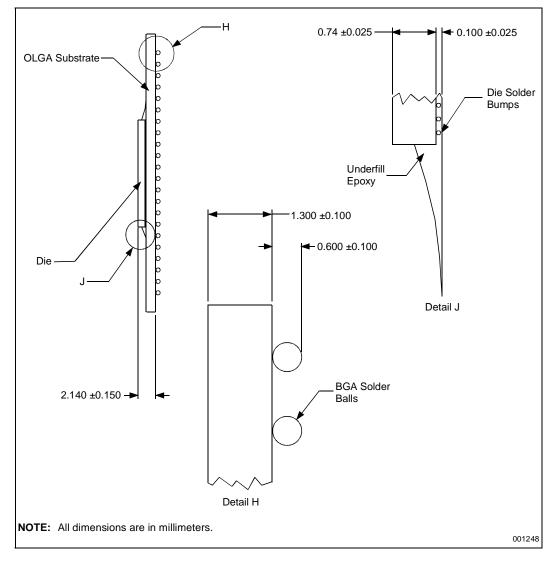

|                | 9-3        | 1012-Ball OLGA2b Solder Ball Detail                                                    | 9-3 |

| <b>Tables</b>  |            |                                                                                        |     |

| Tubico         | 1-1        | Chinaat Component Markings                                                             | 1 1 |

|                | 2-1        | Chipset Component MarkingsScalability Port (SP) Signals                                |     |

|                | 2-1        | Hub Interface 2.0 Signals                                                              |     |

|                | 2-3        | Hub Interface 1.5 Signals                                                              |     |

|                | 2-3<br>2-4 | Reset and Miscellaneous Signals                                                        |     |

|                | 2-5        | Input and Output Clock Signals                                                         |     |

|                | 2-6        | JTAG and SMBus Signals                                                                 |     |

|                | 3-1        | JTAG Read to Configuration Space                                                       |     |

|                | 3-2        | JTAG Write to Configuration Space                                                      |     |

|                | 3-3        | Outbound Configuration Cycle Routing                                                   |     |

|                | 3-4        | SIOH Function Mapping                                                                  |     |

|                | 3-5        | Register Attributes Definitions                                                        |     |

|                | 3-6        | Error Log Register Grouping                                                            |     |

|                | 4-1        | Memory-Mapped I/O Cycle Routing                                                        | 4-2 |

|                | 4-2        | I/O Cycle Routing                                                                      |     |

|                | 4-3        | I/O Space Programming Example                                                          |     |

|                | 4-4        | SAPIC/IOAPIC and PCI Hot-Plug Cycle Routing                                            |     |

|                | 6-1        | Power-Up and Hard Reset Timings                                                        |     |

|                | 8-1        | Absolute Maximum Non-Operational DC Ratings at the Package Pin                         |     |

|                | 8-2        | Voltage and Current Specifications                                                     |     |

|                | 8-3        | Scalability Port Interface Signal Group                                                |     |

|                | 8-4        | Hub Interface 2.0 Signal Groups                                                        |     |

|                | 8-5        | Hub Interface 2.0 DC Parameters                                                        |     |

|                | 8-6        | Hub Interface 2.0 Reference Voltages                                                   |     |

|                | 8-7        | Hub Interface 1.5 Signal Group                                                         |     |

|                | 8-8        | Hub Interface 1.5 DC Signaling Specifications                                          |     |

|                | 8-9        | SIOH Hub Interface 1.5 Reference Voltages                                              |     |

|                |            |                                                                                        |     |

# intel

| 8-10 | Table of Values for the RCOMP Resistor     | 8-5  |

|------|--------------------------------------------|------|

| 8-11 | SMBus and TAP Interface Signal Group       | 8-6  |

| 8-12 | TAP Signal Terminations                    | 8-6  |

| 8-13 | TAP DC Parameters                          |      |

| 8-14 | SMBus DC Parameters                        | 8-7  |

| 8-15 | SMBus Signal Group AC Specifications       | 8-8  |

| 8-16 | TAP Signal Group AC Specifications         | 8-8  |

| 8-17 | Miscellaneous Signal Group                 |      |

| 8-18 | VREFFBCLK66 Reference Voltage              |      |

| 8-19 | CMOS 1.3V DC Parameters                    | 8-10 |

| 8-20 | CMOS 1.5V Open Drain DC Parameters         | 8-10 |

| 8-21 | CMOS 1.5V DC Parameters                    |      |

| 8-22 | CMOS 1.3V Open Drain AC Parameters         | 8-11 |

| 8-23 | CMOS 1.5V Open Drain AC Parameters         | 8-11 |

| 8-24 | CMOS 1.5V Input AC Parameters              | 8-12 |

| 8-25 | CMOS 1.5 I/O Open Drain AC Parameters      | 8-12 |

| 8-26 | Clock Signal Groups                        | 8-12 |

| 8-27 | LVHSTL Clock DC Parameters                 |      |

| 8-28 | LVHSTL Differential Clock AC Specification | 8-13 |

| 9-1  | SIOH Ball List                             |      |

| 9-2  | SIOH Signal – Ball Number                  | 9-17 |

# intel

intel®

Introduction

#### **Overview** 1.1

The Intel<sup>®</sup> E8870 chipset delivers new levels of availability, features, and performance for servers. It provides flexible common modular architecture support for the Intel<sup>®</sup> Itanium<sup>®</sup> 2 processor family. The E8870 chipset up to four processors in a single node configuration, and up to eight processors in a multi-node configuration using the Scalability Port Switch (SPS) component, delivering stability to platforms through reuse and common architecture support.

The component names used throughout this document refer to the component markings listed in Table 1-1.

**Table 1-1. Chipset Component Markings**

| Component Name | Product Marking |

|----------------|-----------------|

| SNC            | E8870           |

| SIOH           | E8870IO         |

| SPS            | E8870SP         |

| DMH            | E8870DH         |

| P64H2          | 82870P2         |

| ICH4           | 82801DB         |

| FWH            | 82802AC         |

#### Server I/O Hub Architectural Overview 1.2

The Intel® E8870IO Server I/O Hub (SIOH) component provides connectivity between the I/O bridge components and the other components in the E8870 chipset. The SIOH is capable of interfacing to a total of five I/O bridges via Hub Interface ports. The E8870 chipset may include up to two SIOH components, depending on the configuration.

The example in Figure 1-1 illustrates a typical eight-way configuration. A four-way single node configuration would consist of one SIOH and one SNC component. The SIOH is capable of interfacing up to four P64H2 I/O bridge devices via the 16-bit Hub Interface 2.0 compliant ports. The 8-bit Hub Interface 1.5 compliant port is used to connect an ICH4 bridge device, providing legacy I/O functionality.

**Note:** One ICH4 is used in both single and multi-node configurations.

Processor Flash Flash (Scalable Node (Scalable Node Memory BIOS BIOS Controller) Controller) (Scalability Port) (Scalability Port) Switch Switch HI 1.5 SIOH SIOH Port Flash ICH4 (Serv er Input/Output (Serv er Input/Output I/O Bridge Hub) Hub) ∏ 32-bit, 33MHz PCI Super I/O 4x HI 2.0 4x HI 2.0 Ports USB 2.0 IDE CD-ROM P64H2 P64H2 PCI/PCI-X PCI/PCI-X BMIDE HDDs Bridge Bridge 64-bit, 33/66/ 64-bit, 33/66/ 100/133 MHz 100/133 MHz 001247

Figure 1-1. Typical Intel<sup>®</sup> E8870 Chipset-Based Eight-Way Itanium<sup>®</sup> 2 Server System Configuration

# 1.3 Interfaces

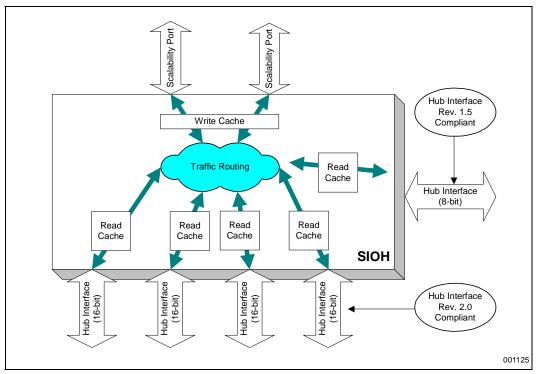

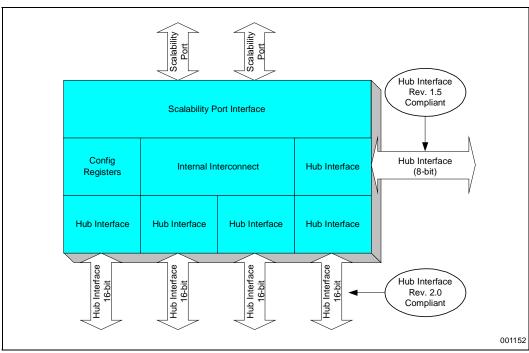

The SIOH component functions as a hub between multiple I/O ports (Hub Interfaces) and the other host bridge components. The SIOH connects the multiple I/O ports to the memory subsystem, the host processors, and other SIOH components. This section provides an overview of the SIOH functionality as three high-level functional blocks:

- Hub Interface

- Internal Interconnect

- Scalability Port Interface

Refer to Figure 1-2 and Figure 1-3.

Figure 1-2. SIOH Interfaces

The SIOH is responsible for routing traffic between the different Hub Interfaces and Scalability Ports.

Figure 1-3. SIOH Functional Blocks

# 1.4 Scalability Port Interface

The Scalability Port (SP) interface is responsible for accepting and sending packets between the SIOH and either the SPS or SNC components. The SIOH SP interface consists of two SP ports. The SP is a cache-coherent interface optimized for scalable multi-node systems that maintain coherency between all processors and their caches.

The SP uses a point-to-point bus topology using source-synchronous data transfer. In order to reduce pin counts, the SP uses Simultaneous Bi-directional (SBD) signalling technology. SBD technology eliminates any arbitration delays since data can be transmitted in both directions simultaneously. The SP interface includes a 40-bit data interface (32-bits of data and 8-bits of ECC) operating at 800MHz, resulting in 3.2 GB/s in each direction per SP.

## 1.5 Hub Interface

The Hub Interface is responsible for accepting and sending Hub Interface packets between the SIOH and an I/O bridge. The I/O bridges supported are P64H2 (Hub Interface-to-PCI bridge), ICH4 (Hub Interface-to-Compatibility bridge).

For the SIOH, there are four Hub Interface 2.0 ports and one 8-bit Hub Interface 1.5 port.

All Hub Interface ports support parallel termination. Parallel termination is required for the routing distances required for E8870 chipset-based platforms.

Hub Interface uses a point-to-point bus topology using source-synchronous data transfer. Hub Interface uses impedance matching techniques (RCOMP) for optimal signal integrity. It dynamically adjusts the driver impedance to match the impedance of the traces on the board throughout thermal variations. Impedance adjustment is accomplished using a dedicated pin (HLxRCOMP) connected to an external resistor that equals the impedance of the Hub Interface traces.

For optimal scalability, the Hub Interface cluster is replicated for each Hub Interface port.

# 1.6 SMBus Interface

The SIOH supports a SMBus 2.0 compatible slave interface to provide register visibility for a server management subsystem. This low cost port is a two-pin (SDA, SCL) serial interface useful for communicating with a baseboard management controller. The interface supports 100 kHz.

The interface allows for a multi-master subsystem, which means more than one device can initiate data transfers at the same time. To support this feature, the SMBus bus arbitration relies on the wired-AND connection of all SMBus interfaces. Two masters can drive the bus simultaneously provided they are driving identical data. The first master drives SDA high, while another master drives SDA low loses the arbitration. The SCL signal consists of a synchronized combination of clocks generated by the masters using the wired-AND connection to the SCL signal.

The SMBus serial operation uses an open-drain wired-AND bus structure that allows multiple devices to drive the bus lines and to communicate status about events such as arbitration, wait states, error conditions and so on. For example, when the slave is unable to accept or drive data at the rate that the master is requesting, the slave can hold the clock line low between the high states to insert a wait interval. The master's clock can only be altered by a slower slave peripheral keeping the clock line low or by another master during arbitration.

# 1.7 JTAG Tap Port

The SIOH supports the IEEE 1149.1 (JTAG) Test Access Port (TAP) for test and debug. The TAP interface is a serial interface comprised of five signals: TDI, TDO, TMS, TCK, and TRST#. The JTAG interface will operate from 4 to 25 MHz.

# 1.8 Terminology

Differential Input buffer logic that requires a voltage reference or the signal

complement.

Direct Connect/Single Node Up to 4-way Itanium® 2 processor/E8870 chipset platform

configuration that consists of one SIOH and SNC that are

directly connected by Scalability Ports.

Dirty Node The SNC or SIOH that owns a modified cache line.

FWH Firmware Hub. This is the chipset Flash Memory component that

typically provides the BIOS firmware code.

Hinted Peer-to-Peer A transaction initiated by one of the P64H2 PCI/PCI-X buses

destined for a target on the other PCI/PCI-X bus on the same

P64H2.

Home Node The SNC that controls the memory on which a particular cache

line resides.

HVCMOS 3.3V CMOS I/O buffer logic.

Inbound Transactions Transactions initiated on Hub Interface destined for the

Scalability Port interface.

iGTL Inverted GTL buffer logic.

IOxAPIC I/O Advanced Programmable Interrupt Controller. Intel authored

an interrupt specification that covers various methods for interrupting a host processor. Each I/O bridge contains an IOxAPIC controller for issuing these interrupts on behalf of their

child devices.

Local Peer-to-Peer A transaction initiated by one of the P64H2 PCI buses destined

for a target on another Hub Interface port on the same SIOH.

LVHSTL Low Voltage High Speed Tranceiver Logic

LVPECL Low Voltage Positive Emitter Coupled Logic

Outbound Transactions Transactions initiated on a Scalability Port destined for Hub

Interface.

Phit Physical unit of data transfer consisting of 40 bits of protocol

level information.

PHP PCI Hot-Plug.

Remote Peer-to-Peer A transaction initiated by one of the P64H2 PCI buses destined

for a target on another Hub Interface port on a different SIOH.

**SAPIC**

Streamlined Advanced Programmable Interrupt Controller. Implemented in Itanium $^{\circledR}$  2 processor-based platforms, this

interrupt mechanism uses inbound writes to specific addresses to

interrupt the host processor.

SAR I/O APIC Controller and Hot Plug Controller Range.

**SBD** Simultaneous Bi-Directional.

Server I/O Hub. This component is used for server platform SIOH

configurations requiring high bandwidth and high connectivity

I/O bus connectivity.

Scalable Node Controller. Includes the processor, memory, and **SNC**

Scalability Port interfaces.

SP Scalability Port.

**SPCMOS** Low speed SP I/O buffer logic.

SPS Scalability Port Switch. The crossbar/central snoop filter that

connects the SNCs and SIOHs.

#### 1.9 **Reference Documents**

• Intel® E8870 Scalable Node Controller (SNC) Datasheet

• Intel® E8870DH DDR Memory Hub (DMH) Datasheet

• Intel<sup>®</sup> E8870SP Scalability Port Switch (SPS) Datasheet

• Intel<sup>®</sup> 82870P2 64-bit Hub 2 (P64H2) Datasheet

• Intel® 82801DB I/O Controller Hub4 (ICH4) Datasheet

• SMBus Specification, Revision 2.0

• PCI Local Bus Specification, Revision 2.2

• PCI-X Local Bus Specification, Revision 1.0

#### 1.10 **Revision History**

| Revision<br>Number | Description                      | Date        |

|--------------------|----------------------------------|-------------|

| -001               | Initial release of the document. | August 2002 |

# intel® Signal Description

#### 2.1 **Conventions**

The terms assertion and deassertion are used extensively when describing signals, to avoid confusion when working with a mix of active-high and active-low signals. The term assert, or assertion, indicates that the signal is active, independent of whether the active level is represented by a high or low voltage. The term *deassert*, or *deassertion*, indicates that the signal is inactive.

Signal names may or may not have a "#" appended to them. The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name the signal is asserted when at the high voltage level.

The exception to the "#" symbol convention lies in the Hub Interface 1.5 signal description. Active is not applicable to HI 1.5. The reader is cautioned against attaching any meaning to the "#" symbol in HI 1.5 mode.

When discussing data values used inside the component, the logical value is used; i.e. a data value described as "1101b" would appear as "1101b" on an active-high bus and as "0010b" on an activelow bus. When discussing the assertion of a value on the actual pin, the physical value is used; i.e. asserting an active-low signal produces a "0" value on the pin.

The following notations are used to describe the signal types:

• I: Input pin

• O: Output pin

• I/O: Bi-directional (input/output) pin

• ASYNC: Asynchronous pin

#### 2.2 Scalability Port (SP) Interface

The SP is the interface between the SIOH to the SPS and SNC components of the E8870 chipset (refer to Table 2-1).

Table 2-1. Scalability Port (SP) Signals

| Signal Name      | Type           | Clock<br>Domain | Description                                                                                                                                                                                                                                                                           |

|------------------|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP{0/1}ZUPD[1:0] | I<br>Analog    | N/A             | <b>Impedance Update:</b> Used to adjust the impedance of I/O drivers.                                                                                                                                                                                                                 |

| SP{0/1}SYNC      | I/O<br>CMOS1.5 | ASYNC           | Reset Synchronization: Provides synchronization between ports for impedance control and reference voltage adjustment. This signal is also used by the SP reset logic to determine when SP comes out of reset.  SP{0/1}SYNC is released when ports at both ends of the link are ready. |

| SP{0/1}PRES      | I<br>CMOS1.5   | N/A             | SP Present: Signals the SP of an impending hot-plug event.                                                                                                                                                                                                                            |

Table 2-1. Scalability Port (SP) Signals (Continued)

| Signal Name        | Туре                  | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|-----------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP{0/1}AVREFH[3:0] | l<br>Analog           | N/A             | Strand A Voltage Reference High: 3/4 VCC reference.                                                                                                                                                                                                                                                                                                                                                |

| SP{0/1}AVREFL[3:0] | I<br>Analog           | N/A             | Strand A Voltage Reference Low: 1/4 VCC reference.                                                                                                                                                                                                                                                                                                                                                 |

| SP{0/1}ASTBP[1:0]  | I/O<br>SBD            | 400 MHz         | Strand A P Strobes: Positive phase data strobes for Strand A to transfer data at the 2x rate (800 MHz).                                                                                                                                                                                                                                                                                            |

| SP{0/1}ASTBN[1:0]  | I/O<br>SBD            | 400 MHz         | Strand A N Strobes: Negative phase data strobes for Strand A to transfer data at the 2x rate (800 MHz).                                                                                                                                                                                                                                                                                            |

| SP{0/1}AD[15:0]    | I/O<br>SBD            | 800 MHz         | Strand A Data Bus: 16-bits of the data portion of a PHIT on Strand A. These bits are SSO encoded. SP{0/1}ASSO determines if these are out of an inverter or not.                                                                                                                                                                                                                                   |

| SP{0/1}AEP[2:0]    | I/O<br>SBD            | 800 MHz         | Strand A Parity/ECC: Two of these signals carry the ECC information for the data flits (AEP[1:0]). There are four bits of ECC for each data PHIT. The header flits are not ECC protected. The third signal is for parity (AEP[2]). Each PHIT is always protected by two bits of parity.                                                                                                            |

| SP{0/1}ALLC        | I/O<br>SBD            | 800 MHz         | Strand A Link Layer Control: For each PHIT these signals carry two of the four bits of link layer control information.                                                                                                                                                                                                                                                                             |

| SP{0/1}ASSO        | I/O<br>SBD            | 800 MHz         | <b>Strand A SSO Encode:</b> This signal is asserted to indicate that the data bits over Strand A are inverted.                                                                                                                                                                                                                                                                                     |

| SP{0/1}BVREFH[3:0] | I<br>SBD              | N/A             | Strand B Voltage Reference High: 3/4 VCC reference.                                                                                                                                                                                                                                                                                                                                                |

| SP{0/1}BVREFL[3:0] | I<br>SBD              | N/A             | Strand B Voltage Reference Low: 1/4 VCC reference.                                                                                                                                                                                                                                                                                                                                                 |

| SP{0/1}BSTBP[1:0]  | I/O<br>SBD            | 400 MHz         | Strand B P Strobes: Positive phase data strobes for Strand B to transfer data at the 2x rate (800 MHz).                                                                                                                                                                                                                                                                                            |

| SP{0/1}BSTBN[1:0]  | I/O<br>SBD            | 400 MHz         | Strand B N Strobes: Negative phase data strobes for Strand B to transfer data at the 2x rate (800 MHz).                                                                                                                                                                                                                                                                                            |

| SP{0/1}BD[15:0]    | I/O<br>SBD            | 800 MHz         | Strand B Data Bus: 16-bits of the data portion of a PHIT on Strand B. These bits are SSO encoded. SP{0/1}BSSO determines if these are out of an inverter or not.                                                                                                                                                                                                                                   |

| SP{0/1}BEP[2:0]    | I/O<br>SBD            | 800 MHz         | Strand B Parity/ECC: Two of these signals carry the ECC information for the data flits (BEP[1:0]). There are 4-bits of ECC for each data PHIT. The header flits are not ECC protected. The third signal is for parity (BEP[2]). Each PHIT is always protected by two bits of parity.                                                                                                               |

| SP{0/1}BLLC        | I/O<br>SBD            | 800 MHz         | Strand B Link Layer Control: For each PHIT these signals carry two of the four bits of link layer control information.                                                                                                                                                                                                                                                                             |

| SP{0/1}BSSO        | I/O<br>SBD            | 800 MHz         | <b>Strand B SSO Encode:</b> This signal is asserted to indicate that the data bits over Strand B are inverted.                                                                                                                                                                                                                                                                                     |

| SP{0/1}GPIO[1:0]   | I/O<br>CMOS 1.5<br>OD | ASYNC           | General Purpose I/O Signals: These pins are asynchronous open drain I/O signals. To filter glitches on the inputs, the value of the input only changes when the same value has been sampled over four consecutive 200 MHz clock cycles. Similarly, to ensure accurate sampling of these signals by other devices, the output value will be asserted for a minimum of 6 consecutive 200 MHz cycles. |

| Vccsp              | Analog                | N/A             | VCC for the SP.                                                                                                                                                                                                                                                                                                                                                                                    |

The Hub Interface 2.0 connects the SIOH to a maximum of four P64H2 PCI/PCI-X bridge components (refer to Table 2-2).

Table 2-2. Hub Interface 2.0 Signals

| Signal Name                             | Type          | Clock<br>Domain | Description                                                                                                                                                  |

|-----------------------------------------|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HL{4/3/2/1}PD[17:0]                     | I/O<br>iGTL   | 533 MHz         | Packet data signals: PD[16] is connected to PD[20] on P64H2, and PD[17] is connected to PD[21] on P64H2.                                                     |

| HL{4/3/2/1}PSTRBF<br>HL{4/3/2/1}PUSTRBF | I/O<br>iGTL   | 533 MHz         | Hub Interface Strobe First: HL{n}PSTRBF strobes are used for HL{n}PD[7:0] & HL{n}PD[16].  HL{n}PUSTRBF strobes are used for HL{n}PD[15:8] & HL{n}PD[17].     |

| HL{4/3/2/1}PSTRBS<br>HL{4/3/2/1}PUSTRBS | I/O<br>iGTL   | 533 MHz         | Hub Interface Strobe Second: HL{n}PSTRBS strobes are used for HL{n}PD[7:0] & HL{n}PD[16]. HL{n}PUSTRBS are the strobes used for HL{n}PD[15:8] & HL{n}PD[17]. |

| HL{4/3/2/1}RQOUT                        | O<br>iGTL     | 66 MHz          | Hub Interface Request Out: This must be connected to HI[16] of the P64H2.                                                                                    |

| HL{4/3/2/1}RQIN                         | l<br>iGTL     | 66 MHz          | <b>Hub Interface Request In:</b> This must be connected to HI[17] of the P64H2.                                                                              |

| HL{4/3/2/1}STOP                         | I/O<br>iGTL   | 66 MHz          | <b>Hub Interface Stop:</b> This must be connected to HI[18] of the P64H2.                                                                                    |

| HL{4/3/2/1}VSWING                       | I/O<br>Analog | N/A             | Hub Interface voltage swing.                                                                                                                                 |

| HL{4/3/2/1}RCOMP                        | I/O<br>iGTL   | N/A             | Hub Interface Compensation: Connects to the external RCOMP resistor and used for impedance matching.                                                         |

| HL{4/3/2/1}VREF                         | I<br>Analog   | N/A             | Hub Interface voltage reference.                                                                                                                             |

# 2.3 Hub Interface 1.5

The Hub Interface 1.5 connects the SIOH to the legacy I/O ICH4 component (refer to Table 2-3).

Table 2-3. Hub Interface 1.5 Signals

| Signal Name | Type        | Clock<br>Domain | Description                                                            |

|-------------|-------------|-----------------|------------------------------------------------------------------------|

| HL0PD[7:0]# | I/O<br>iGTL | 266 MHz         | Packet data pins.                                                      |

| HL0PSTRBS   | I/O<br>iGTL | 266 MHz         | Second PD Interface Strobe.                                            |

| HL0PSTRBF   | I/O<br>iGTL | 266 MHz         | First PD Interface Strobe.                                             |

| HL0RQOUT#   | O<br>iGTL   | 66 MHz          | Hub Interface Request Out: This must be connected to HI[8] on ICH4.    |

| HL0RQIN#    | l<br>iGTL   | 66 MHz          | Hub Interface Request In: This must be connected to HI[9] on ICH4.     |

| HL0STOP#    | I/O<br>iGTL | 66 MHz          | Hub Interface Stop Signal: This must be connected to HI[10] on ICH4.   |

| HL0PAR#     | I/O<br>iGTL | 66 MHz          | Hub Interface Parity Signal: This must be connected to HI[11] on ICH4. |

Table 2-3. Hub Interface 1.5 Signals (Continued)

| Signal Name  | Туре          | Clock<br>Domain | Description                                                                                          |

|--------------|---------------|-----------------|------------------------------------------------------------------------------------------------------|

| HL0VREF[1:0] | I<br>Analog   | N/A             | Hub Interface Voltage Reference.                                                                     |

| HLORCOMP     | I/O<br>iGTL   | N/A             | Hub Interface Compensation: Connects to the external RCOMP resistor and used for impedance matching. |

| HL0VSWING    | I/O<br>Analog | N/A             | Hub Interface Voltage Swing.                                                                         |

# 2.4 Reset and Miscellaneous Signals

**Table 2-4. Reset and Miscellaneous Signals**

| Signal Name | Type                 | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                              |

|-------------|----------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETI#     | I<br>CMOS1.5         | 200 MHz         | Reset Input: Reset input driven by the system.                                                                                                                                                                                                                                                                           |

| RESET66#    | O<br>CMOS1.5         | 200 MHz         | Reset 66: Reset signal output for the downstream I/O components. Synchronized to the SIOH reset input (RESETI#) signal.                                                                                                                                                                                                  |

| PWRGOOD     | I<br>CMOS1.5         | ASYNC           | <b>Power Good:</b> Clears the SIOH. This signal is held low until all power supplies are within specification. This signal is followed by RESETI# Deassertion.                                                                                                                                                           |

| INT_OUT#    | O<br>CMOS 1.5        | ASYNC           | Interrupt Output: SIOH interrupt output pin for SP Hot-<br>Plug and performance.                                                                                                                                                                                                                                         |

|             | OD                   |                 | This pin is asynchronous and is driven for a minimum of six consecutive SYSCLKs before transitioning.                                                                                                                                                                                                                    |

| EV[3:0]#    | I/O<br>CMOS1.5<br>OD | ASYNC           | Event In/Out: Open-drain event pins connected to the performance monitors. As inputs they are used in signal conditioning the PerfMon's trigger selection. As an output they indicate that the target condition has been met for a particular monitor.                                                                   |

|             |                      |                 | To filter glitches on the inputs, the value of the input only changes when the same value has been sampled over four consecutive 200 MHz clock cycles. Similarly, to ensure accurate sampling of these signals by other devices, these output value will be asserted for a minimum of twelve consecutive 200 MHz cycles. |

| ERR[2:0]#   | I/O<br>CMOS1.5<br>OD | ASYNC           | <b>Error Out:</b> Open-drain error indicator pins to indicate the severity level of an error that has occurred internally or observed by this chip.                                                                                                                                                                      |

| BUSID[2:0]  | I<br>CMOS1.5         | N/A             | Bus Number Identification: Static inputs to set the PCI equivalent of bus ID.                                                                                                                                                                                                                                            |

| NODEID[4:0] | I<br>CMOS1.5         | N/A             | <b>Device Node Identification:</b> Static inputs to set the PCI equivalent of device ID. NODEID[3:0] specifies the SMBus slave address for the component.                                                                                                                                                                |

# 2.5 Clock Signals

The SIOH requires a 200 MHz LVHSTL clock source. The SIOH also generates 66 MHz and 33 MHz output clocks that can be used as source clocks by the downstream I/O components (refer to Table 2-5).

**Table 2-5. Input and Output Clock Signals**

| Signal Name    | Type              | Clock<br>Domain | Description                                                                                                                                                              |

|----------------|-------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSCLK/SYSCLK# | l<br>Differential | 200 MHz         | System Clock: Input clock source (and complement) to the SIOH.                                                                                                           |

| DET            | I<br>CMOS1.5      | N/A             | PLL Determinism Pin: DET pin is strapped high to enable determinism in the E8870 chipset. If high, CLK33 and CLK66 references are reset on First Hard Reset Deassertion. |

| FBCLK66        | I<br>CMOS 3.3     | 66 MHz          | <b>66 MHz Feedback Clock:</b> External 66 MHz PLL feedback input.                                                                                                        |

| VREFFBCLK66    | l<br>Analog       | 66 MHz          | <b>Voltage Reference for FBCLK66:</b> Reference voltage for the 66 MHz PLL feedback.                                                                                     |

| CLK66          | O<br>CMOS 3.3     | 66 MHz          | Clock 66: 66 MHz clock for all I/O subsystem common clock signals.                                                                                                       |

| CLK33          | O<br>CMOS 3.3     | 33 MHz          | Clock 33: Can be used as 33 MHz clock for ICH4 PCI bus.                                                                                                                  |

| LVHSTLODTEN    | I<br>CMOS1.5      | 200 MHz         | LVHSTL On Die Termination Enable: Enables the on die termination resistors for the LVHSTL input buffers used on clock inputs.                                            |

| VccaCore       | Analog            | N/A             | VCC for Core clock.                                                                                                                                                      |

| VssaCore       | Analog            | N/A             | VSS for Core clock.                                                                                                                                                      |

| VCCASP         | Analog            | N/A             | VCC for SP clock.                                                                                                                                                        |

| VSSASP         | Analog            | N/A             | VSS for SP clock.                                                                                                                                                        |

| VCCAHL         | Analog            | N/A             | VCC for HI clock.                                                                                                                                                        |

| VSSAHL         | Analog            | N/A             | VSS for HI clock.                                                                                                                                                        |

| VCCACom        | Analog            | N/A             | VCC for Common clock.                                                                                                                                                    |

| VSSACom        | Analog            | N/A             | VSS for Common clock.                                                                                                                                                    |

| Vcc33          | Analog            | N/A             | 3.3 VCC for all HVCMOS drivers.                                                                                                                                          |

# 2.6 JTAG and SMBus Signals

**Table 2-6. JTAG and SMBus Signals**

| Signal Name | Туре            | Clock<br>Domain | Description                                                                                                    |

|-------------|-----------------|-----------------|----------------------------------------------------------------------------------------------------------------|

| TCK         | I<br>JTAG       | TCK             | JTAG Test Clock: Clock input used to drive Test Access Port (TAP) state machine during test. TCK = 20 MHz max. |

| TDI         | I<br>JTAG       | TCK             | JTAG Test Data In: Data input for test mode, used to serially shift data and instructions into the TAP.        |

| TDO         | O<br>JTAG       | TCK             | JTAG Test Data Out: Data output for test mode, used to serially shift data out of the TAP.                     |

| TMS         | I<br>JTAG       | TCK             | JTAG Test Mode Select: This signal is used to control the state of the TAP controller.                         |

| TRST#       | I<br>JTAG       | ASYNC           | JTAG Test Reset: This signal resets the TAP controller logic.                                                  |

| SCL         | I/O<br>SMBus OD | SCL             | SMBus Clock: Provides synchronous operation of the SMBus.                                                      |

| SDA         | I/O<br>SMBus OD | SCL             | SMBus Addr/Data: Used for data transfer and arbitration on the SMBus.                                          |

# intel® Configuration Registers

The SIOH is viewed by the system as a single PCI device with seven different functions. While the standard PCI header is defined in the PCI Local Bus Specification, Revision 2.2, the remaining configuration registers typically reside above 40h.

#### **Register Access Mechanisms** 3.1

The SIOH configuration registers can be accessed from the following sources:

- Configuration Read/Write from Scalability Port (SP)

- System Management Bus (SMBus)

- JTAG

#### 3.1.1 **Scalability Port Initiated Register Access**

SIOH will accept only one configuration access from the SPs at a time. Subsequent accesses experience back pressure until the previous configuration access is finished.

#### 3.1.2 **JTAG Initiated Register Access**

The SIOH provides a JTAG configuration access mechanism that allows a user to access any register in the chipset. This is accomplished by using a mechanism similar to the PCI CF8/CFC data structure. The flow to read and write configuration space via JTAG is shown in Table 3-1 and Table 3-2.

Table 3-1. JTAG Read to Configuration Space

| Field of Serial Chain | Bit#  | Phase 1                                                         | Phase 2             | Phase 3 <sup>1</sup>         |

|-----------------------|-------|-----------------------------------------------------------------|---------------------|------------------------------|

| Data [31:0]           | 63:32 |                                                                 |                     | Read the data.               |

| Register Number       | 31:24 |                                                                 |                     |                              |

| Device                | 23:19 | Write with address to                                           |                     |                              |

| Function              | 18:16 | read.                                                           |                     |                              |

| Bus Number            | 15:8  |                                                                 |                     |                              |

| Error                 | 7     |                                                                 |                     | Read for proper termination. |

| Reserved              | 6:5   |                                                                 |                     |                              |

| Busy                  | 4     | Set to 1                                                        | Poll until cleared. |                              |

| Enable Access         | 3     | Set to 1                                                        |                     |                              |

| Byte Enable Command   | 2:0   | Set command:  • 100 - read dword Address must be dword aligned. |                     |                              |

<sup>1.</sup> Software could choose to merge Phase 2 and Phase 3 into one operation.

**Table 3-2. JTAG Write to Configuration Space**

| Field of Serial Chain | Bit#  | Phase 1                                                                                                                           | Phase 2             | Phase 3 <sup>1</sup>         |

|-----------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------|

| Data [31:0]           | 63:32 |                                                                                                                                   |                     |                              |

| Register Number       | 31:24 | ]                                                                                                                                 |                     |                              |

| Device                | 23:19 | Write with data and address to write.                                                                                             |                     |                              |

| Function              | 18:16 |                                                                                                                                   |                     |                              |

| Bus Number            | 15:8  | ]                                                                                                                                 |                     |                              |

| Error                 | 7     |                                                                                                                                   |                     | Read for proper termination. |

| Reserved              | 6:5   |                                                                                                                                   |                     |                              |

| Busy                  | 4     | Set to 1                                                                                                                          | Poll until cleared. |                              |

| Enable Access         | 3     | Set to 1                                                                                                                          |                     |                              |

| Byte Enable Command   | 2:0   | Set command:  001 - write byte.  010 - write word Address must be word aligned.  011 - write dword Address must be dword aligned. |                     |                              |

<sup>1.</sup> Software could choose to merge Phase 2 and Phase 3 into one operation.

The bus, function, device, and register numbers are similar to the CF8 structure. This mechanism may be used in run-time and in the middle of any other traffic.

*Note:* The JTAG port on the SIOH can only be used to access its own configuration registers.

# 3.1.3 SMBus Operation

The SIOH allows a server management subsystem to read and write its configuration registers. This is accomplished through an "out-of-band", slave-only SMBus 2.0 port.

The SIOH claims address 11X0\_XXX where XXXX specifies NODEID[3:0] pin strappings (sampled upon the deassertion of RESETI#).

**Note:** It is possible for software to change the default Node ID by programming the CBC register. This reprogramming will *not* affect the SMBus address assignment.

# 3.2 Device Mapping

The device number for each device connected to an SP is captured from pins upon the rising edge of hard reset. In the CBC register, Bus[2:0] is captured from the BUSID[2:0] pins. Bus[7:3] are assigned by software. Bus[7:0] are intended for truly large systems where the total # of devices on the cross-bar network may exceed the 32 device limit on a given PCI bus. Software must set Bus[7:0] to FF for the SIOH when using an SP switch.

*Note:* The compatibility bus must be programmed to Bus 0. Therefore, the SIOH Bus ID should never get assigned to 0 by software.

In the CBC register, Node ID[4:0] are also captured from external pins on the Node ID[4:0] pins. Those bits are compared with the device number field in the PCI configuration access. The device number can be any value between 0 and 31. Software must set Node ID[4:3] to 11 in the E8870 chipset.

The SIOH has a PCI bus range per Hub Interface. Each Hub Interface is assigned a bus number (BUSNO[x]) and is accessed with Type 0 configuration cycles. Bus range BUSNO[x] +1 to BUSNO[x+1] of SIOH encompasses all PCI buses behind Hub Interface[x] and is accessed with Type 1 configuration cycles.

Table 3-3 describes how configuration cycles are routed by the SIOH.

**Table 3-3. Outbound Configuration Cycle Routing**

| Configuration Cycle                                              | Route                                                                                            |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Bus[7:0] == Bus[7:0] (in CBC) AND<br>Device[4:0] == Node ID[4:0] | Configuration cycle targets this SIOH so service it locally and return the completion to source. |

| Bus[7:0] == BUSNO[x] <sup>1</sup>                                | Forward Type 0 configuration cycle to Hub Interface x.                                           |

| BUSNO[x] < Bus[7:0] < BUSNO[x+1] <sup>1</sup>                    | Forward Type 1 configuration cycle to Hub Interface x.                                           |

| None of the above.                                               | Master Abort.                                                                                    |

<sup>1.</sup> This test is performed only if the first row tests false.

Even if a Hub Interface is unpopulated, it must be assigned to a bus number. Any configuration cycles to this bus number will Master Abort.

Table 3-4 maps the function assignments for the SIOH.

**Table 3-4. SIOH Function Mapping**

| Function Number | SIOH Description                                           |

|-----------------|------------------------------------------------------------|