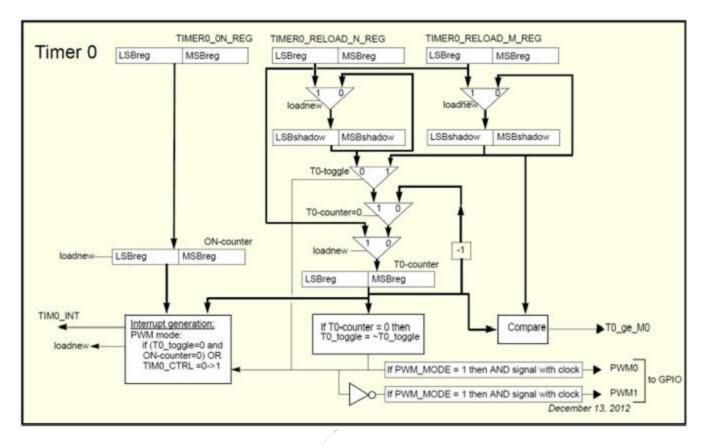

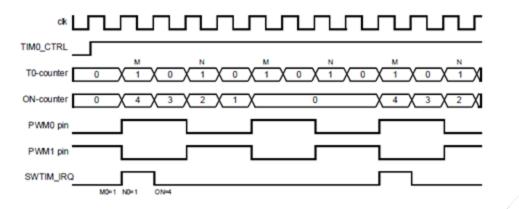

# Inventek Systems

Embedding Connectivity Everywhere

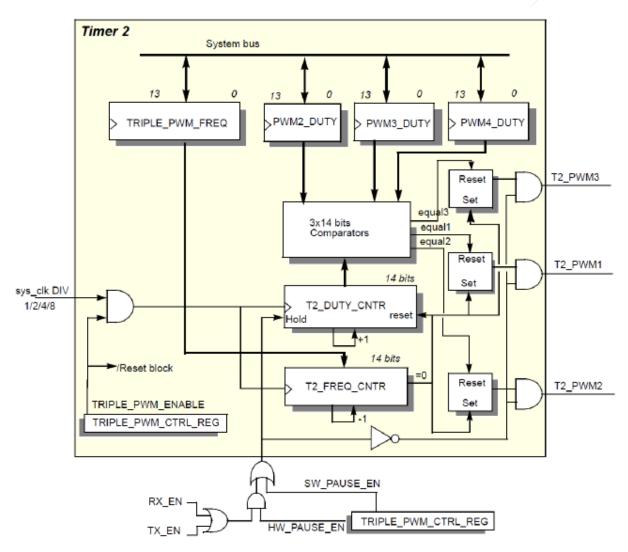

# **ISM14585-L35-P8** BLE 5.0 SiP

# Preliminary Data Sheet

5.0 BLE + Cortex M0 + PMU + PA + 8Mb Flash

#### **Table of Contents**

| 1  | PART NUMBER DETAIL DESCRIPTION                                                                | 5  |

|----|-----------------------------------------------------------------------------------------------|----|

|    | 1.1 Ordering Information                                                                      | 5  |

|    | 1.2 Ordering Information Configuration                                                        | 6  |

| 2  | OVERVIEW                                                                                      | 7  |

| 3  | FEATURES                                                                                      | 8  |

|    | 3.1 Feature Highlights:                                                                       | 9  |

|    | 3.2 Application Examples                                                                      | 10 |

|    | 3.3 Key Benefits                                                                              | 11 |

|    | 3.4 Limitations                                                                               |    |

|    | 3.5 Regulatory Compliance                                                                     |    |

| 4  | COMPLEMENTARY DOCUMENTATION                                                                   |    |

|    | 4.1 EVB                                                                                       |    |

| 5  | ISM14585-L35 SoC & Module BLOCK DIAGRAMS                                                      |    |

|    | 5.1 ISM14585-L35 SoC Block Diagram:                                                           |    |

|    | 5.2 ISM14585-L35 Module Block Diagram Configuration Options:                                  |    |

| 6  | Electrical Specification                                                                      | 17 |

|    | 6.1 Absolute Maximum Rating                                                                   | 17 |

|    | <ul><li>6.2 Recommendable Operation Condition.</li><li>6.2.1 Temperature, Humidity.</li></ul> | 17 |

|    | 6.2.1 Temperature, Humidity                                                                   | 17 |

|    | 6.2.2 Voltage                                                                                 | 17 |

|    | 6.3 Current Consumption                                                                       |    |

|    | 6.3.1 BLUETOOTH LOW ENERGY                                                                    |    |

| 7  |                                                                                               |    |

|    | 7.1 RF Transmitter Specification                                                              |    |

|    | 7.1.1 BLE RF SPECIFICATION                                                                    |    |

| 8  | Pin Definition                                                                                |    |

|    | 8.1 Module Pin Out Schematic (Internal Antenna configuration)                                 |    |

|    | 8.2 Detail Pin definition information                                                         |    |

| 9  |                                                                                               |    |

|    | 9.1 Microcontroller Unit                                                                      |    |

|    | 9.2 Buck Power Configuration                                                                  |    |

|    | 9.3 ANTENNA CONFIGURATION OPTIONS                                                             |    |

|    | 9.3.1 Integrated Antenna                                                                      |    |

|    | 9.3.2 External w.fl Antenna                                                                   |    |

|    | 9.4 External Reset                                                                            |    |

|    | 9.4.1 POR, HW AND SW RESET                                                                    |    |

|    | 9.4.2 POWER-ON RESET FUNCTIONALITY                                                            |    |

|    | 9.5 DMA Controller                                                                            |    |

| Fi | gure 7 DMA Controller Block Diagram                                                           |    |

| _  | 9.5.1 DMA PERIPHERALS                                                                         |    |

| T  | he list of peripherals that can request for a DMA service is presented in below table         |    |

|    | 9.5.2 INPUT/OUTPUT MULTIPLEXER                                                                | 30 |

| 9.5.3    | DMA CHANNEL OPERATION                           | 30 |

|----------|-------------------------------------------------|----|

|          | DMA ARBITRATION                                 |    |

| 9.5.5    | FREEZING DMA CHANNELS                           | 32 |

|          | C Interface                                     |    |

| 9.7 I2C  | C BUS TERMS                                     | 34 |

|          | I2C BEHAVIOR                                    |    |

|          | I2C PROTOCOLS                                   |    |

|          | MULTIPLE MASTER ARBITRATION                     |    |

|          | CLOCK SYNCHRONIZATION                           |    |

|          | OPERATION MODES                                 |    |

|          | DISABLING THE I2C CONTROLLER                    |    |

|          | ART                                             |    |

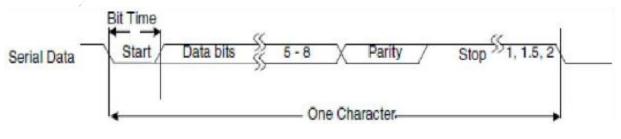

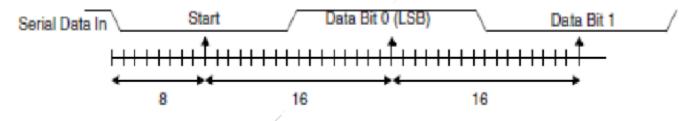

|          | UART (RS232) SERIAL PROTOCOL                    |    |

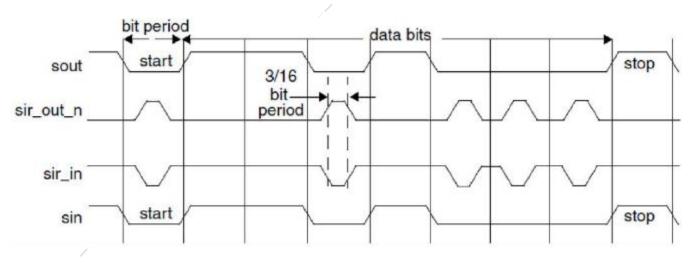

| 9.8.2    | IRDA 1.0 SIR PROTOCOL                           | 54 |

|          | CLOCK SUPPORT                                   |    |

|          | CLOCK SUPPORT                                   |    |

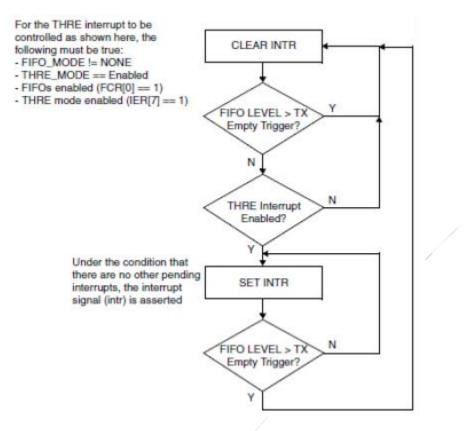

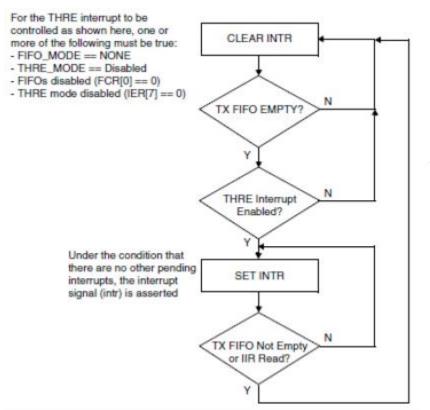

|          | PROGRAMMABLE THRE INTERRUPT                     |    |

| 9.8.6    | SHADOW REGISTERS                                | 59 |

|          | DIRECT TEST MODE                                |    |

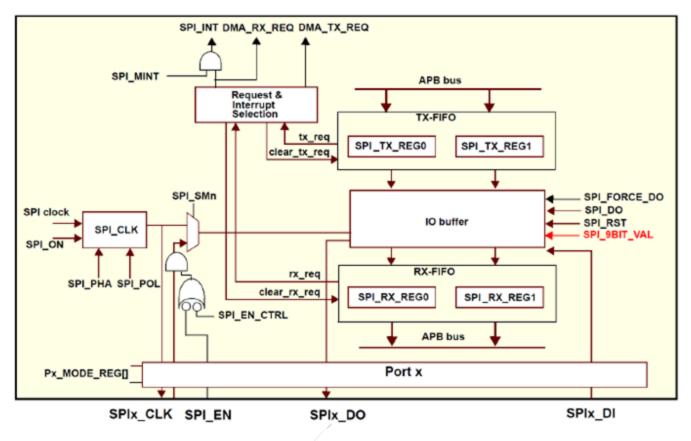

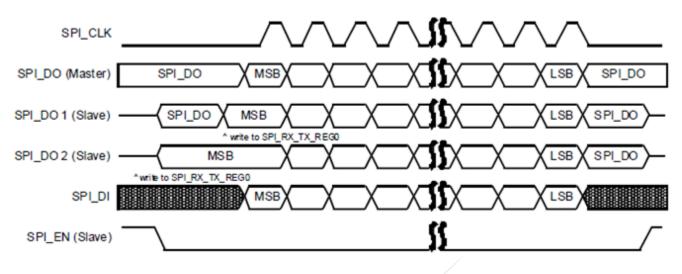

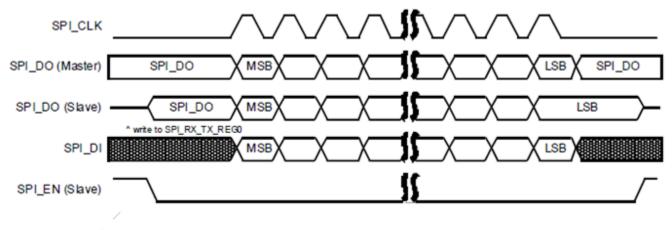

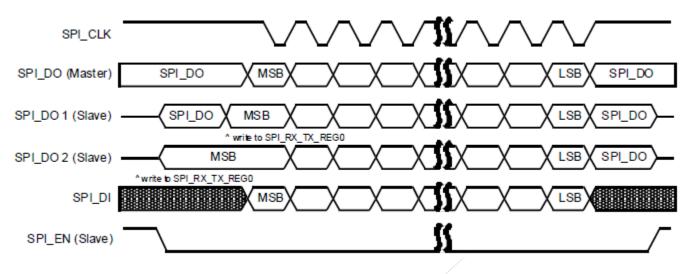

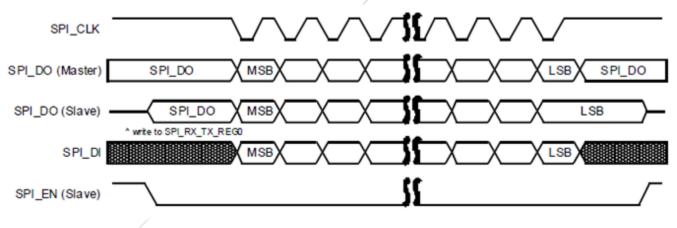

| 9.9 SP   | I+ Interface                                    | 60 |

| 9.9.1    | OPERATION WITHOUT FIFOSake-Up Timer             | 61 |

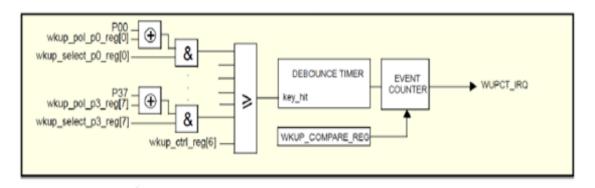

| 9.10 Wa  | ake-Up Timer                                    | 66 |

| 9.11 Ge  | neral Purpose Timers                            |    |

| 9.11.1   |                                                 |    |

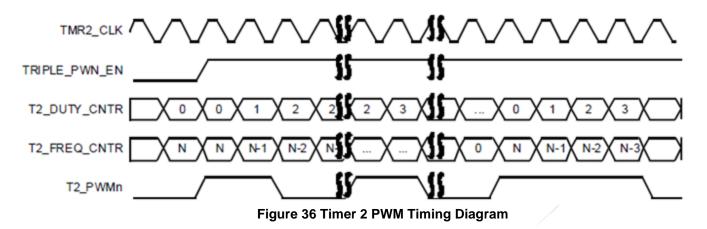

| 9.11.2   | TIMER 2                                         | 71 |

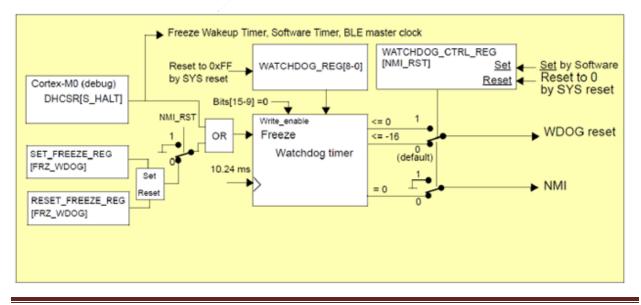

| 9.12 Wa  | atchdog Timer                                   | 74 |

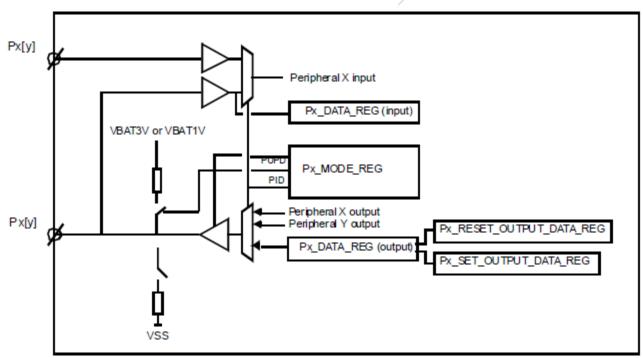

| 9.13 Inp | put/Output Ports                                |    |

| 9.13.1   | PROGRAMMABLE PIN ASSIGNMENT                     |    |

| 9.13.2   | GENERAL PURPOSE PORT REGISTERS                  |    |

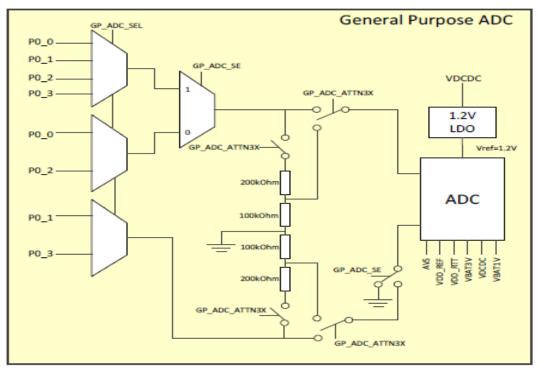

|          | neral Purpose ADC                               |    |

| 9.14.1   |                                                 |    |

| 9.14.2   | STARTING THE ADC AND SAMPLING RATE              |    |

| 9.14.3   | NON-IDEAL EFFECTS                               | 81 |

| 9.14.4   | CHOPPING                                        |    |

| 9.14.5   | OFFSET CALIBRATION                              |    |

| 9.14.6   | ZERO-SCALE ADJUSTMENT                           | 83 |

| 9.14.7   | COMMON MODE ADJUSTMENT                          |    |

| 9.14.8   | INPUT IMPEDANCE, INDUCTANCE, AND INPUT SETTLING | 83 |

| 9.14.9   | COMMON MODE ADJUSTMENT                          |    |

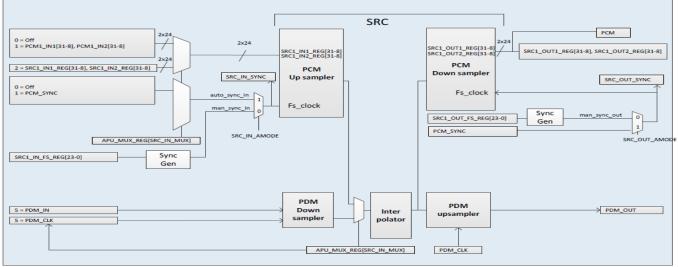

| 9.14.10  | Sample Rate Converter (SRC)                     | 85 |

| 9.14.11  | SRC ARCHITECTURE                                | 86 |

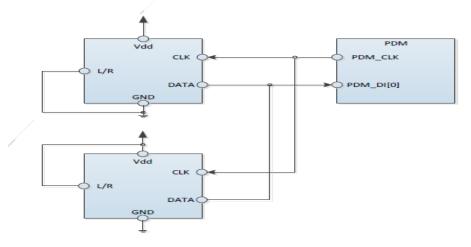

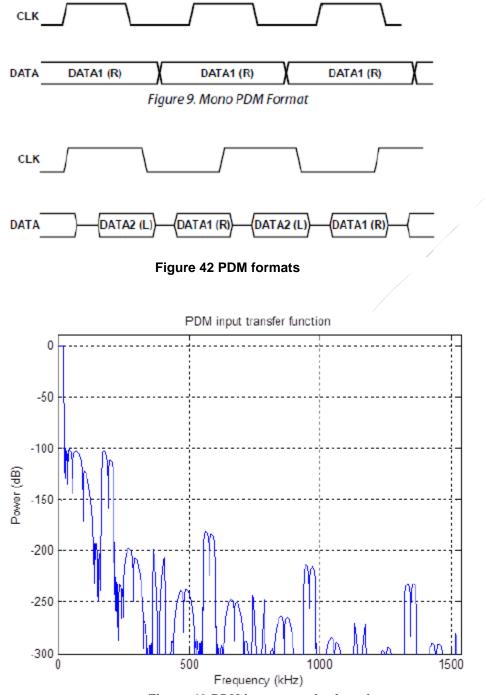

| 9.15 PD  | M Interface                                     | 88 |

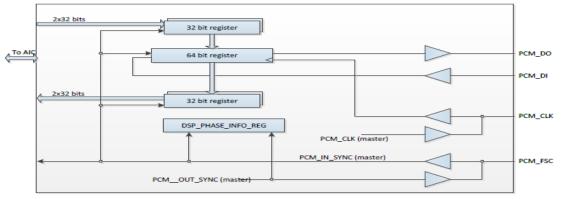

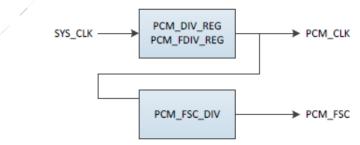

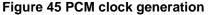

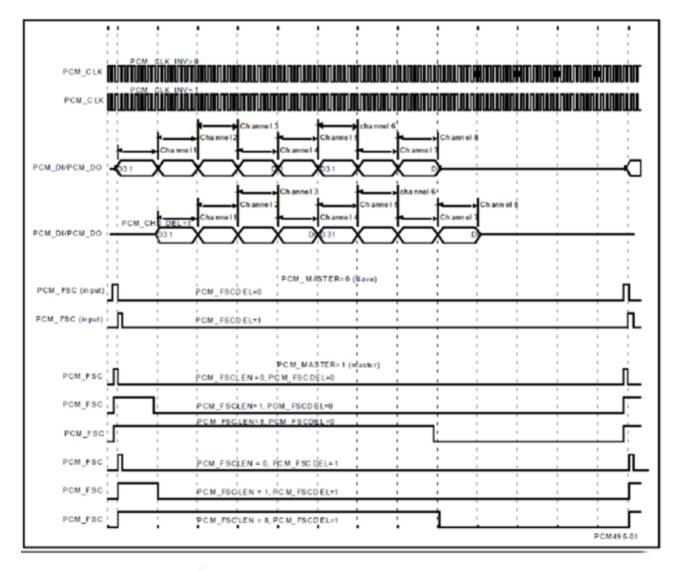

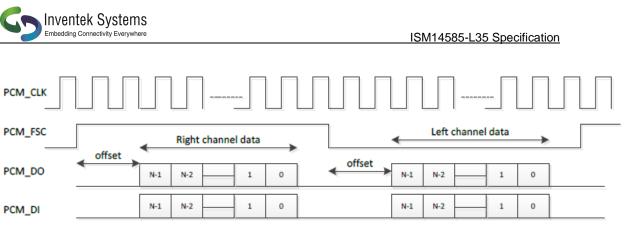

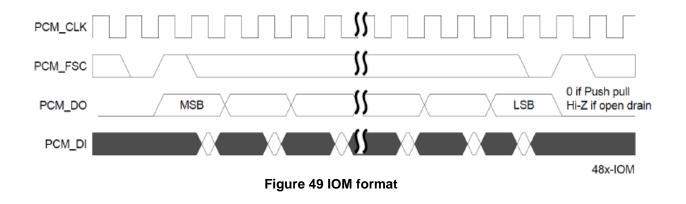

| 9.16 PC  | M Controller                                    | 90 |

| 9.16.1   | PCM ARCHITECTURE                                | 91 |

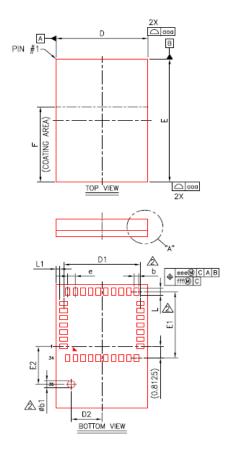

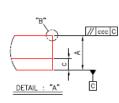

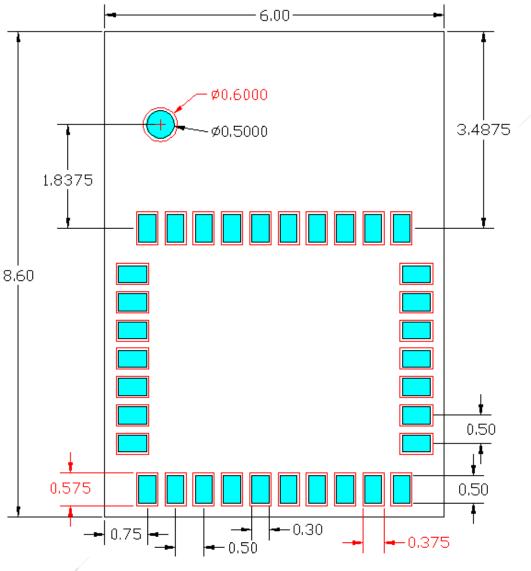

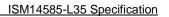

| 10 MECHANICAL SPECIFICATION               |     |  |  |

|-------------------------------------------|-----|--|--|

| 10.1 Size of the Module                   |     |  |  |

| 10.2 Mechanical Dimension                 |     |  |  |

| 11 Recommend Footprint (Board Design)     |     |  |  |

| 11.1 Module Dimension Measurement         |     |  |  |

| 11.2 The X-Y Central Location Coordinates | 100 |  |  |

| 12 Recommend Stencil                      | 102 |  |  |

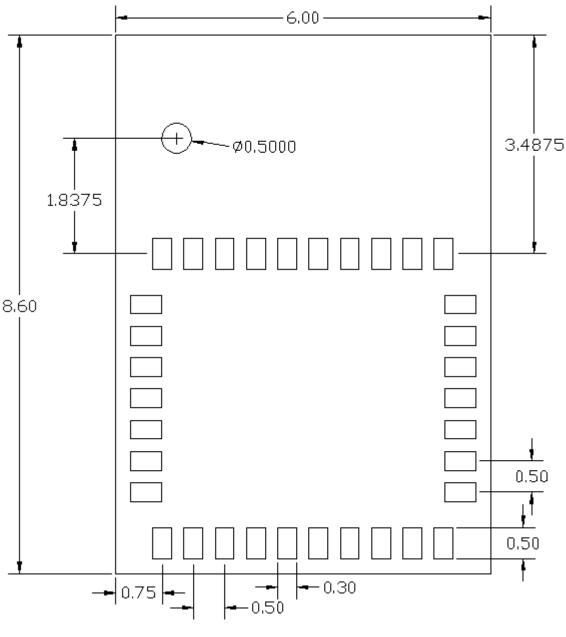

| 3 Recommended Reflow Profile              |     |  |  |

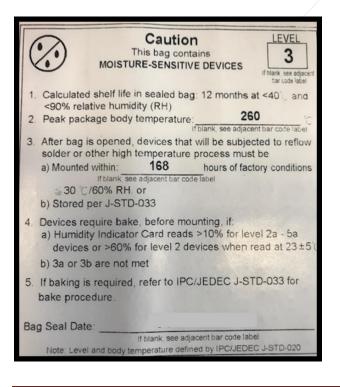

| 14 Storage Requirements                   | 103 |  |  |

| 14.1 MSD Specification                    |     |  |  |

| 15 REVISION CONTROL                       |     |  |  |

| 16 CONTACT INFORMATION                    |     |  |  |

# **1 PART NUMBER DETAIL DESCRIPTION**

# 1.1 Ordering Information

| Device                   | Description               | Standard Ordering Number |

|--------------------------|---------------------------|--------------------------|

| ISM14585 Module          | Certified BLE 5.0 +       | ISM14585-L35-P8          |

| Supports both Internal   | Cortex M0 Module with     |                          |

| Antenna or w.fl External | integrated PMU, PA,       |                          |

|                          | 8Mb of Flash and          |                          |

| Antenna options.         |                           |                          |

|                          | supports both a certified |                          |

|                          | internal antenna or       | /                        |

|                          | certified w.fl external   |                          |

|                          | antenna                   |                          |

| ISM14585-EVB             | BLE 5.0 + Cortex M0       |                          |

| Internal Antenna         | Module with integrated    | ISM14585-L35-P8-EVB      |

| Evaluation Board         | PMU, PA, 8Mb of Flash     |                          |

|                          | and internal antenna      |                          |

|                          | EVB (Evaluation Board)    |                          |

| ISM14585-EVB-W           | BLE 5.0 + Cortex M0       |                          |

| w.fl External Antenna    | Module with integrated    | ISM14585-L35-P8-EVB-W    |

| Evaluation Board         | PMU, PA, 8Mb of Flash     |                          |

|                          | and w.fl external antenna |                          |

|                          | EVB (Evaluation Board)    |                          |

| B24P-W w.fl Certified    | Certified w.fl External   |                          |

| External Antenna         | Antenna to accompany the  |                          |

|                          | /ISM14585-L35-P8-EVB-W    | B24P-W                   |

|                          | External Antenna EVB      |                          |

|                          | <u>option</u>             |                          |

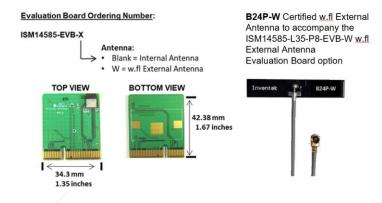

# **1.2 Ordering Information Configuration**

Module Standard Ordering Number: Evaluation Board Standard Ordering Numbers:

#### ISM14585-L35-P8

LGA 35, 6.0mm x 8.6mm x 1.2mm

ISM14585-L35-P8-EVB: Internal Antenna EVB Option

ISM14585-L35-P8-EVB-W: External w.fl Antenna EVB Option

ISM14585-L35-P8-EVB-W requires the Inventek B24P-W Certified <u>w.fl</u> External Antenna

- Please refer to the ISM14585-L35-P8-EVB User's Manual for additional information on the ISM14585 Evaluation Board configuration options.

- For additional module configuration options please contact Inventek Systems

- Audio Unit configuration

- 4Mb or 16Mb integrated Flash

- o Other

# 2 OVERVIEW

The Inventek Systems **ISM14585-L35** SiP (System in Package), is one of the smallest, lowest power and most integrated Bluetooth® 5.0 solutions available. The **ISM14585-L35** platform is the first BLE module from Inventek's *FLEXiBLE* product family. The **ISM14585-L35** SiP is an embedded wireless Bluetooth Low Energy (BLE) IoT radio, based on the Dialog Semiconductor DA14585 radio SoC (System on Chip). The **ISM14585-L35** offers designers all the benefits of the industry-leading DA14580 technology but with even greater flexibility to create more advanced applications from the smallest footprints and power budgets.

The **ISM14585-L35** is ideal for applications such as remote controls, beacons, connected sensors and innovative medical devices. Among the new features, the **ISM14585-L35** supports Data Packet Length Extension, Link Layer Privacy v1.2, Secure Connections, Bluetooth low energy and Efficient connectable Advertising.

The **ISM14585-L35** integrated Audio Unit (AU) is equipped with a Pulse-Density Modulation (PDM) interface that can be connected to up to 2 input devices (e.g. MEMS microphones) or output devices, a PulseCode modulation (PCM) controller which provides an up to 192 kHz synchronous interface to external audio devices, ISDN circuits and serial data interfaces (I2S) and a 24-bit Sample Rate Converting unit (SRC) used to convert the sampling rate of audio samples between the various interfaces. PDM and PCM functionality can be mapped to any GPIO through the user programmable pin logic. An integrated DMA controller handles all data transfers between the AU and the RAM providing the CPU with the freedom to cope with other tasks. Please Note that the AU feature requires a version of the ISM14585 module without the integrated 8Mb of Flash. The Microphone feature requires I2S or PDM via the SPI interface.

The **ISM14585-L35** SiP provide smarter, more flexible, and even lower power BLE connectivity with an integrated 32bit CortexTM-M0 (16MHz), processor, an <u>integrated PMU (Power Management Unit)</u>, an integrated PA (Power Amplifier), an integrated 128kB of ROM, 64KB OTP, 1MB SPI Flash as well as a foot print compatible options for an additional integrated 4Mb, 8Mb, or 16Mb of Flash.

The **ISM14585-L35** SiP provides a number of features and standard peripheral interfaces (see "Features" below), enabling a seamless connection to an embedded design. The **ISM14585-L35** is a very versatile SoC and is ideal for adding Bluetooth low energy to products like remote controls, proximity tags, beacons, connected medical devices and smart home nodes. The **ISM14585-L35** supports all Bluetooth developments up to and including Bluetooth 5.0.

The **ISM14585-L35** also includes 96KB of RAM, the **ISM14585-L35** has double the memory for User applications of its predecessor to take full advantage of the standard's features. The **ISM14585-L35** also includes an integrated microphone interface for voice

<u>support at no additional cost</u>. The wide supply voltage range (0.9–3.6 V) covering a larger choice of energy sources also enables full design flexibility.

The **ISM14585-L35** is easy to design-in and supports standalone as well as hosted applications. The **ISM14585-L35** is supported by a complete development environment with Dialog's SmartSnippets<sup>™</sup> software that helps customers optimize software for power consumption.

The **ISM14585-L35** supports several fully qualified profiles embedded in ROM (see "Typical Applications" below), and the option of loading additional profiles into RAM. The low cost, small footprint (6.0mm x 8.6mm x 1.2mm), LGA 35 pin package and ease of design-in make the **ISM14585-L35** ideal for a wide range of embedded applications.

The **ISM14585-L35** enables wireless connectivity to the simplest existing sensor products with minimal engineering effort. **ISM14585-L35** reduces development time, lowers manufacturing costs, saves board space, simplifies certification compliance, and minimizes customer RF expertise required during development of target applications.

The **ISM14585-L35** provides the highest level of integration for a wireless system, with market leading and integrated BLE 5.0 technology based on Dialog's DA14585 SoC. The **ISM14585-L35** is also fully supported by Dialog's Smartbond product family Development Kit-Pro evaluation board and Dialog SmartSnippets Studio SDK.

# **3 FEATURES**

The **ISM14585-L35** provides a reduced boot time and supports up to 8 connections. It has a fully integrated radio transceiver and baseband processor for Bluetooth® Low Energy. It can be used as a standalone application processor or as a data pump in hosted systems.

The **ISM14585-L35** is optimized for remote control units (RCU) requiring support for voice commands and motion/gesture recognition. Its integrated Audio Unit (AU) offers easy interface for MEMS microphones over PDM, external codecs over PCM/I2S and a Sample Rate Converter unit.

The **ISM14585-L35** Bluetooth Low Energy firmware includes the L2CAP service layer protocols, Security Manager (SM), Attribute Protocol (ATT), the Generic Attribute Profile (GATT) and the Generic Access Profile (GAP). All profiles published by the Bluetooth SIG as well as custom profiles are supported.

The transceiver interfaces directly to the antenna and is fully compliant with the Bluetooth 5.0 standard. The **ISM14585-L35** has dedicated hardware for the Link Layer

implementation of Bluetooth Low Energy and interface controllers for enhanced connectivity capabilities.

# 3.1 Feature Highlights:

- Frequency Band: 2.4GHz

- Complies to the Bluetooth 5 core specification

- Supports up to 8 Bluetooth LE connections

- Network Standard: Bluetooth Low Energy

- Longest battery life

- Operating voltage 3.3V

- Operating Temperature: -40°C to 85°C

- MSL level 3

- Low system Bill of Materials

- FCC, CE, IE and Japan certification in-process

- Certifications will comply with Bluetooth V5.0, ETSI EN 300, 328 and EN 300 440 Class 2 (Europe), FCC CFR47 Part 15 (US) and ARIB STD-T66 (Japan)

- Processing power

- 16 MHz 32 bit ARM Cortex-M0 with SWD

- o interface

- o Dedicated Link Layer Processor

- AES-128 bit encryption Processor

- Memory Resources

- Large memory to build complex applications

- Integrated One-Time-Programmable memory 64 kB (OTP)

- 96 kB Data/Retention SRAM

- o 128 kB ROM

- 8Mb integrated Flash

- Power Management

- Integrated Buck DCDC converter

- P0, P1 and P2 ports with 3.3 V tolerance

- o / Internal decoupling of the supply pins

- Supports Coin (typ. 3.3 V)

- 10-bit ADC for battery voltage measurement

- o Integrated Power Amplifier for maximum radio performance

- Digital controlled oscillators

- 16 MHz crystal (±20 ppm max) and RC oscillator

- 32 kHz crystal (±50 ppm, ±500 ppm max) and RCX oscillator

- Flexible Reset Circuitry

- System & Power-On Reset in a single pin

- Fast cold boot in less than 50ms

- General-purpose, Capture and Sleep timers

- Digital interfaces

- o Gen. Purpose I/Os: 14

- o 2 x UARTs with hardware flow control up to 1 MBd

- SPI+™ interface

- I2C bus at 100 kHz, 400 kHz

- o 3-axes capable Quadrature Decoder

- Analog interfaces

- o 4-channel 10-bit ADC

- Radio transceiver

- Fully integrated 2.4 GHz CMOS transceiver

- Single wire antenna: no RF matching, or RX/TX switching required

- Supply current at VBAT3V:

- TX: 3.4 mA

- RX: 3.7 mA (with ideal DCDC)

- Integrated 10dBm PA

- o -20 dBm output power in "Near Field Mode"

- -93 dBm receiver sensitivity

- Package:

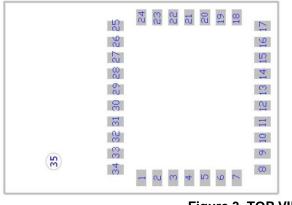

- o LGA 35, 6.0mm x 8.6mm x 1.2mm

# 3.2 Application Examples

- Voice-controlled remote controls

- Beacons

- (Multi-sensor) Wearable devices

- Fitness trackers

- Consumer health

- Smartwatches

- Human interface devices

- o Keyboard

- o Mouse

- Toys

- Consumer appliances

# 3.3 Key Benefits

- Lowest power consumption

- Smallest system size

- Lowest system cost

#### 3.4 Limitations

Inventek Systems products are not authorized for use in safety-critical applications (such as life support) where a failure of the Inventek Systems product would reasonably be expected to cause severe personal injury or death.

# 3.5 Regulatory Compliance

| Regulator | Status         |

|-----------|----------------|

| FCC       | O7P-14585      |

| IC        | / 10147A-14585 |

| RoHS      | Compliant      |

Inventek Systems FCC, IC, and CE module transmitter certifications for the **ISM14585-L35-P8** module can be used to the advantage of any manufacturer developing a product using these devices. In order to take full advantage of the certifications and remain in compliance, Developers may not interfere, modify, replace and/or enhance the SiP antenna design, layout and power settings. For FCC compliance, End Customer finished products will still need to meet the Declaration of Conformity (SDoC) requirements according to 47 CFR Chapter 1, part 15, subpart B.

The testing required for the Declaration of Conformity (SDoC) requirements is specified in sections 15.107 and 15.109. The official documents can be obtained from the U.S Government Printing Office online. U.S. Government Printing Office CFR 47.

Any changes to the Inventek certified antenna options such as a different antenna or adding an antenna diversity switch will require filing for a Class 2 permissive change. Any Class 2 permissive changes must be performed under Inventek's grant, and therefore must be done in cooperation with Inventek. In addition to this document, Inventek recommends verifying the schematic board design with Inventek Engineering once the schematic is complete for further review and validation.

If it is desired to add a connector or U.FL connector in the RF path or change the antenna to one of the same type (chip) with equal or less gain, customers can do so without refiling.

Other changes such as a different antenna or adding an antenna diversity switch will require filing for a Class 2 permissive change. Any Class 2 permissive changes must be performed under Inventek's grant, and therefore must be done in cooperation with Inventek. In addition to this document, Inventek recommends verifying the schematic board design with Inventek Engineering once the schematic is complete for further review and validation.

Inventek also provides customers additional certifications for specific countries upon request and an agreed upon service fee.

#### **3.5.1 FCC and IC Regulatory Information**

- Model: ISM14585-L35-P8

- FCC ID: 07P-14585

- IC: 10147A-14585

This module is limited to OEM installation only.

OEM integrators must ensure that the end-user has no manual instructions to remove or

install the module. OEM's must comply with FCC marking regulation part 15 declaration of conformity (Section 2.925(e)).

This module is to be installed only in mobile or fixed applications (Please refer to FCC CFR

47 Part 2.1091(b) for a definition of mobile and fixed devices).

Separate approval is required for all other operating configurations, including portable configurations with respect to FCC CFR 47 Part 2.1093, and different antenna configurations.

The antennas used with this module must be installed to provide a separation distance of at

least 20cm from all persons, and must not be co-located or transmit simultaneously with any

other antenna or transmitter, except in accordance with FCC multi transmitter product procedures. The ISM14585-L35-P8 Module has been designed to operate with the following antennas and gains. Use with other antenna types or with these antenna types at higher gains is strictly prohibited.

| Manufacturer | Type of Antenna | Model  | Gain dBi | Type of Connector |

|--------------|-----------------|--------|----------|-------------------|

| Inventek     | Integrated      | N/A    | -1       | embedded          |

| Inventek     | Trace           | B24P-W | 3.2      | w.fl              |

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference

- (2) This device must accept any interference received, including interference that may cause undesired operation.

Warning: Changes or modifications not expressly approved by the party responsible is prohibited.

NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications.

However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/ TV technician for help.

This equipment complies with FCC RF Exposure requirements and should be installed and operated with a minimum distance of 20cm between the radiator and any part of the human body.

A clearly visible label is required on the outside of the user's (OEM) enclosure with the following text:

- Contains FCC ID: 07P-14585

- Contains IC: 10147A-14585

This transmitter module is certified for FCC Part 15 operation; when installed in a host device, the host manufacturer is responsible for making sure that the host device with the transmitter installed continues to be compliant with Part 15B unintentional radiator requirements.

#### RSS-210/RSS-Gen Notices:

Operation is subject to the following two conditions:

(1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of this device.

L'opè ration est soumise aux deux conditions suivantes: (1) cet appareil ne peut pas provoquer d'interfè rences et (2) cet apparial doit accepter toute interfè rence, y compris les interfè rences qui peuvent causer un mauvis fonctionment de l'appareil.

Under Industry Canada regulations, this radio transmitter may only operate using an antenna of a type and maximum (or lesser) gain approved for the transmitter by Industry Canada. To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that necessary for successful communication.

Sous la rè glementation d'Industrie Canada, ce transmetteur radio ne peut fonctionner en utilisant une antenne d'un type et un maximum (ou moins) gain approuvè es pour l'è metteur

ISM14585-L35 Specification par Industrie Canada. Pour rè duire le risqué d'interference aux autres utilisateures, le type d'antenne et son gain doivent être choisis de maniè re que la puissance isotrpe rayonnè e è quivalente (PIRE) ne dè passe pas ce qui est nè cessaire pour une communication rè ussie.

The radio transmitter has been approved by Industry Canada to operate with the antenna types listed above with the maximum permissible gain and required antenna impedance for each antenna type indicated. Antenna types not included in this list having a gain greater than the maximum gain indicated for that type, are strictly prohibited for use with this device.

Cet è metteur de radio a è tè approuvè par Industrie Canada pour fonctionner avec les types d'antennes è numè rè es ci-dessus avec le gain maximal admissible et impè dance d'antenna requise pour chaque type d'antenne indiquè . Types d'antennes ne figurant pas dans cette liste, ayant un gain supè rieur au gain maximum indiquè pour ce type, sontstrictement interdites pour l'utilisation avec cet appareil.

# 4 COMPLEMENTARY DOCUMENTATION

# 4.1 EVB

- > The Inventek ISM14585-L35 Evaluation Board is the **ISM14585-L35-EVB**

- > Please reference the **ISM14585-L35-EVB User's Manual**

- Evaluation Board Specification

- EVB User's Guide

- o Design Guidelines

# 5 ISM14585-L35 SoC & Module BLOCK DIAGRAMS

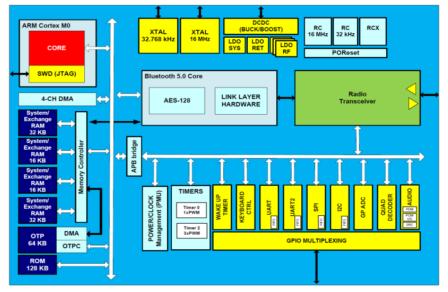

# 5.1 ISM14585-L35 SoC Block Diagram:

DIALOG DA14585 Radio w/Audio I/F SoC:

Figure 1 Dialog DA14585 SoC Block Diagram

Please Note: The Audio Unit feature requires a version of the ISM14585 module without the integrated 8Mb of Flash. The Microphone feature requires I2S or PDM via the SPI interface.

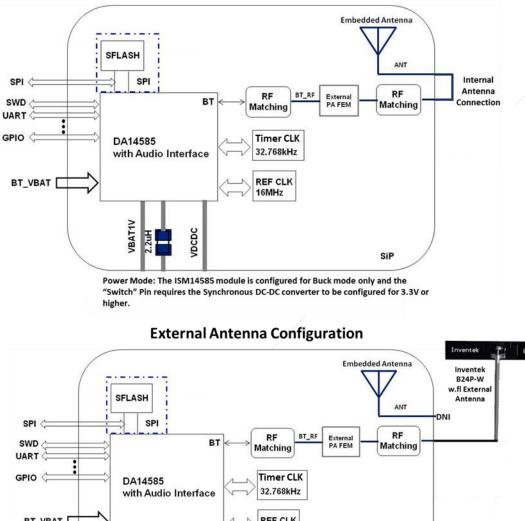

# 5.2 ISM14585-L35 Module Block Diagram Configuration Options:

**Internal Antenna Configuration**

B24P-W REF CLK BT\_VBAT 16MHz VBAT1V VDCDC SiP Power Mode: The ISM14585 module is configured for Buck mode only and the "Switch" Pin requires the Synchronous DC-DC converter to be configured for 3.3V or higher.

UART: Universal synchronous/asynchronous receiver transmitters

SPI: Serial Peripheral Interface

DOC-DS-14585-20 GBIC: General-purpose input/output SWD: Serial Wire Debug

# 6 Electrical Specification

# 6.1 Absolute Maximum Rating

| Supply Power                      | Max +4 Volt                    |                                     |          |

|-----------------------------------|--------------------------------|-------------------------------------|----------|

| Storage Temperature               | perature - 40° to 125° Celsius |                                     |          |

| Voltage ripple                    | +/- 2%                         | Max. Values not exceeding C voltage |          |

|                                   | Power                          | min                                 | Max      |

|                                   | BT_VBAT                        | -                                   | 3.6      |

| Power Supply Absolute             | VDD_PA                         | -                                   | 3.6      |

|                                   | VDD_FLASH                      | -                                   | 3.6      |

| Voltage on input or<br>output pin |                                | VSS-0.3                             | VBAT+0.3 |

# 6.2 Recommendable Operation Condition

# 6.2.1 Temperature, Humidity

The **ISM14585-L35** will withstand the operational requirements listed in the table below.

| Operating Temperature | -30° to 85° Celsius |                                   |

|-----------------------|---------------------|-----------------------------------|

| Humidity range        | Max 95%             | Non condensing, relative humidity |

# 6.2.2 Voltage

The Power supply for the **ISM14585-L35** will be provided by the host via the power pins

| Symbol    | Parameter | Min | Тур | Max | Unit |

|-----------|-----------|-----|-----|-----|------|

| BT_VBAT   |           | 3   | 3.3 | 3.6 | V    |

| VDD_PA    |           | 3   | 3.3 | 3.6 | V    |

| VDD_Flash |           | 3   | 3.3 | 3.6 | V    |

# 6.3 Current Consumption

# 6.3.1 BLUETOOTH LOW ENERGY

Condition: Condition: 25deg.C

| Item    | Condition                                         | Min | Nom | Max | Unit |

|---------|---------------------------------------------------|-----|-----|-----|------|

| Tx Mode | Transmitter and baseband are both operating, 100% |     | TBD |     | mA   |

|         | Receiver and baseband are both operating, 100%    |     | TBD |     | mA   |

# 7 **RF Specification**

#### 7.1 RF Transmitter Specification

# 7.1.1 BLE RF SPECIFICATION

| Parameter                           | Mode and Condition           | Min. | Тур. | Max. | Unit |

|-------------------------------------|------------------------------|------|------|------|------|

| Frequency Range                     |                              | 2402 |      | 2480 | MHz  |

| RX sense <sup>a</sup>               | LE GFSK, 0.1% BER,<br>1 Mbps |      | TBD  | -80  | dBm  |

| TX Power                            | N/A                          |      | TBD  | TBD  | dBm  |

| Mod char: delta f1 average          |                              | 225  | 225  | 275  | kHz  |

| Mod char: delta f2 max <sup>c</sup> |                              | 99.9 |      |      | %    |

| Mod char: ratio                     |                              | 0.8  | 0.95 |      | %    |

- Dirty TX is Off.

- Up to 1dB of variation may potentially be seen from typical sensitivity specs due to the chip, board, and associated variations.

- At least 99.9% of all delta F2 max frequency values recorded over 10 packets must be greater than 185 kHz.

- Additional specifications to reference is SIG

# 8 Pin Definition

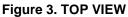

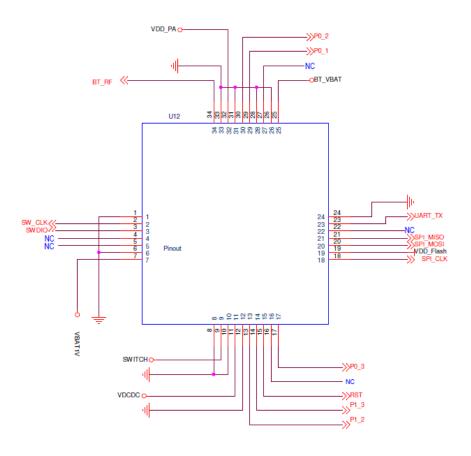

# 8.1 Module Pin Out Schematic (Internal Antenna configuration)

DOC-DS-14585-201911-3.8

Inventek Systems

#### 8.2 Detail Pin definition information

Please reference the Dialog **DA14585** Bluetooth 5.0 SoC Data Sheet for any additional information.

| Pin Name           | Pin<br>Number                   | I/О Туре | Description                                                                             |  |  |  |  |

|--------------------|---------------------------------|----------|-----------------------------------------------------------------------------------------|--|--|--|--|

| Radio              |                                 |          |                                                                                         |  |  |  |  |

| BT_RF              | 34                              | I/O      | RF I/O antenna port                                                                     |  |  |  |  |

| Antenna            |                                 |          | /                                                                                       |  |  |  |  |

| ANT                | 35                              | I/O      | Embedded Antenna Port.<br>Enable: tie to BT_RF pin<br>Disable: tie to GND when not use. |  |  |  |  |

| Voltage Regulators |                                 |          |                                                                                         |  |  |  |  |

| BT_VBAT            | 25                              | AI       | VBAT input Pin, Bypass with a 1uF                                                       |  |  |  |  |

| VDD_PA             | 32                              | AI       | PA VDD Input Pin, Bypass with a 1uF                                                     |  |  |  |  |

| VDD_FLASH          | 19                              | AI       | Flash VDD input pin                                                                     |  |  |  |  |

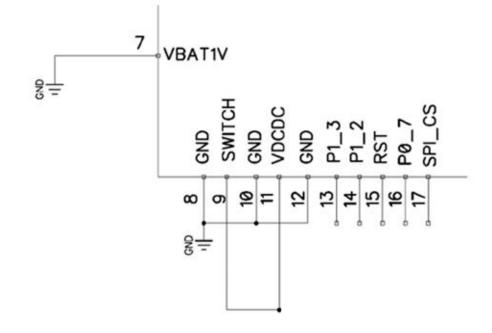

| VDCDC              | 11                              | AO       | Bypass with 2.2uF and 100nF. Reference Section 9.2                                      |  |  |  |  |

| SWITCH             | 9                               | AIO      | Reference Section 9.2                                                                   |  |  |  |  |

| VBAT1V             | 7                               | AI       | RESERVED, connect to Ground                                                             |  |  |  |  |

| Straps             |                                 |          |                                                                                         |  |  |  |  |

| RST                | 15                              | DI       | INPUT. Reset signal (active high). Must be connected to GND if not used.                |  |  |  |  |

| Grounds            |                                 | /        |                                                                                         |  |  |  |  |

| GND                | 1,6,8,10,12,24,<br>26, 28,31,33 | GND      | Module Grounds                                                                          |  |  |  |  |

| Pin Name          | Pin<br>Number | I/O Type                       | Description                                                                                                                                                                                                                                                                                                                                                                   |  |

|-------------------|---------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Digital I/O       |               |                                |                                                                                                                                                                                                                                                                                                                                                                               |  |

| P0_0 (Note2)      | 18            | DIO / ADC 0 /<br>SPI CLK       | INPUT/OUTPUT with selectable pull up/down resistor. Pulldown enabled during and after reset. General purpose I/O port bit or alternate function nodes. Contains state retention mechanism                                                                                                                                                                                     |  |

| P0_1 (Note2)      | 29            | DIO / ADC 1                    | during power down.<br>Drive current is 3.5mA                                                                                                                                                                                                                                                                                                                                  |  |

| P0_2 (Note2)      | 30            | DIO / ADC 2 /<br>I2C SCL       | Note 1: An increased Packet Error rate might occur if GPIO P1-2<br>and P1-3 is toggling. The root cause of this problem is the<br>close location of a few GPIO pins to the on-chip 16 MHz<br>XTAL oscillator circuitry. Toggling of these GPIOs might<br>corrupt the clock, which will be visible in the Packet Error<br>Rate. Please reference the Dialog DA14585 Errata for |  |

| P0_3 (Note2)      | 17            | DIO / ADC 3 /<br>I2C SDA       |                                                                                                                                                                                                                                                                                                                                                                               |  |

| P0_4 (Note2)      | 23            | DIO / UART<br>TX               |                                                                                                                                                                                                                                                                                                                                                                               |  |

| P0_5 (Note2 & 3)  | 21            | DIO / UART<br>RX / SPI<br>MISO | more details.<br>Note 2: All Port Pins can be PWM                                                                                                                                                                                                                                                                                                                             |  |

| P0_6 (Note2)      | 20            | DIO / SPI<br>MOSI              |                                                                                                                                                                                                                                                                                                                                                                               |  |

| P1_2 (Note 1 & 2) | 13            | DIO                            | Note 3: There is no execute in place from the SPI Flash, therefore<br>UART is available after Boot or the UART can be                                                                                                                                                                                                                                                         |  |

| P1_3 (Note 1 & 2) | 14            | DIO                            | interleaved with SPI. If configured, the SPI Flash can be used to load FW.                                                                                                                                                                                                                                                                                                    |  |

| Debug Interface   |               | /                              |                                                                                                                                                                                                                                                                                                                                                                               |  |

| SWCLK             | 2             | DIO                            | This signal is the JTAG clock by default                                                                                                                                                                                                                                                                                                                                      |  |

| SWDIO             | 3             | DIO                            | This signal is the JTAG data I/O by default                                                                                                                                                                                                                                                                                                                                   |  |

| No Connects       |               |                                | ·                                                                                                                                                                                                                                                                                                                                                                             |  |

| NC                | 4,5,16, 22,27 | NA                             | RESERVED                                                                                                                                                                                                                                                                                                                                                                      |  |

| Internal Flash    |               |                                |                                                                                                                                                                                                                                                                                                                                                                               |  |

| P0_0              | 18            | SPI CLK                        | Shared SPI clock, internally connected to SPI Flash                                                                                                                                                                                                                                                                                                                           |  |

| P0_5              | 21            | UART RX /<br>SPI MISO          | Shared SPI MISO internally connected to SPI Flash. See (Note 3)                                                                                                                                                                                                                                                                                                               |  |

| P0_6              | 20            | SPI MOSI                       | Shared SPI MOSI internally connected to SPI Flash                                                                                                                                                                                                                                                                                                                             |  |

| P0_7              | N/A           | SPI CS                         | Internally connected to the CS of the SPI Flash (Note: In Dialog SmartSnippet Studio, set Flash Enable to this Pin                                                                                                                                                                                                                                                            |  |

# 9 Addition Information

# 9.1 Microcontroller Unit

The **ISM14585-L35** includes a Cortex-M0 32-bit Reduced Instruction Set Computing (RISC) processor with a von Neumann architecture (single bus interface). It uses an instruction set called Thumb, which was first supported in the ARM7TDMI processor.

However, several newer instructions from the ARMv6 architecture and a few instructions from the Thumb-2 technology are also included. Thumb-2 technology extends the previous Thumb instruction set to allow all operations to be carried out in one CPU state. The instruction set in Thumb-2 includes both 16-bit and 32-bit instructions. Most instructions generated by the C compiler use the 16-bit instructions, and the 32-bit instructions are used when the 16-bit version cannot carry out the required operations. This results in high code density and avoids the overhead of switching between two instruction sets.

In total, the Cortex-M0 processor supports 56 base instructions, although some instructions can have more than one form. Although the instruction set is small, the Cortex-M0 processor is highly capable because the Thumb instruction set is highly optimized.

Academically, the Cortex-M0 processor is classified as load-store architecture, as it has separate instructions for reading and writing to memory, and instructions for arithmetic or logical operations that use registers.

# 9.2 Buck Power Configuration

The **ISM14585** module is configured for Buck mode only and the "Switch" Pin requires the Synchronous DC-DC converter to be configured for 3.3V or higher.

The ISM14585 module is configured for Buck mode only and the "Switch" Pin requires the Synchronous DC-DC converter to be configured for 3.3V or higher.

# 9.3 ANTENNA CONFIGURATION OPTIONS

#### 9.3.1 Integrated Antenna

- Pin 34 is connected to Pin 35.

- Please reference the ISM14585-L35-P8-EVB Evaluation Board User's Manual for Layout specification.

#### 9.3.2 External w.fl Antenna

- Pin 34 is connected to a w.fl external antenna connector.

- Please reference the ISM14585-L35-P8-EVB Evaluation Board User's Manual for Layout specification.

#### 9.4 External Reset

The **ISM14585-L35** comprises an RST pad which is active high. It contains an RC filter for spikes suppression with 400k $\Omega$  and 2.8pF for the resistor and the capacitor respectively. It also contains a 25k $\Omega$  pull-down resistor. This pad should be connected to ground if not needed by the application.

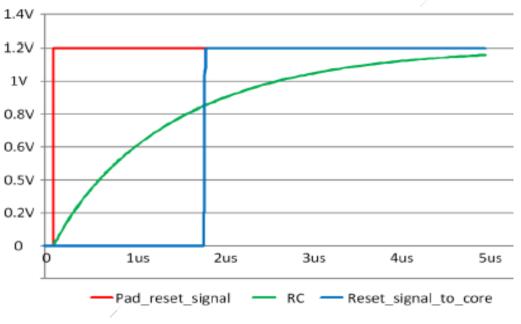

The response is illustrated in the **Figure 4** which displays the voltage (V) on the vertical axis and the time ( $\mu$ s) on the horizontal axis:

Figure 4. RST Pad Latency

The typical latency of the RST pad is in the range of 2us.

# 9.4.1 POR, HW AND SW RESET

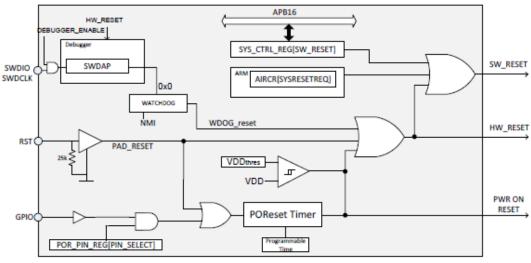

The Power-On Reset (POR) signal is generated:

• Internally and will release the system's flip flops as soon as the VDD voltage crosses the minimum threshold value.

• Externally by a Power-On Reset source (RST pad or GPIO).

There are three main reset signals in the **ISM14585-L35**:

- 1. The PWR-On reset which is triggered by a GPIO set as POR source with selectable polarity and/or the RST pad after a programmable time delay.

- 2. The HW reset which is basically triggered by the RST pad when it becomes active for a short period of time (less than the programmable delay for POR).

- 3. The SW reset which is triggered by writing the SYS\_CTRL\_REG[SW\_RESET] bit.

- The HW reset can also be automatically activated upon waking up of the system from the Extended or Deep Sleep mode by programming bit PMU\_CTRL\_REG [RESET\_ON\_WAKEUP].

- The PWR-On reset as well as the HW reset will basically run the cold start-up sequence and the BootROM code will be executed.

The SW reset is the logical OR of a signal from the ARM CPU (triggered by writing SCB->AIRCR = 0x05FA0004) and the SYS\_CTRL\_REG[SW\_RESET] bit.

This is mainly used to reboot the system after the base address has been remapped. The block diagram of the reset block is depicted in **Figure 5**.

Figure 5. Reset Block Diagram

DOC-DS-14585-201911-3.8

Certain registers are reset by POR only or by POR and the HW reset signal, but not by the SW reset. These registers are listed in the table below.

| Reset by POR Only           | Reset by POR or HW Reset     | Reset by POR, HW or SW<br>Reset |

|-----------------------------|------------------------------|---------------------------------|

| BANDGAP_REG                 | OTPC_NWORDS_REG              | The rest of the Register File   |

| POR_PIN_REG                 | CLK_FREQ_TRIM_REG            |                                 |

| POR_TIMER_REG               | CLK_RADIO_REG                |                                 |

| RF registers containing the | All RF calibration registers | /                               |

| trimming values for the     | BLE_CNTL2_REG                |                                 |

| VCO, the LNA and the I/O    | CLK_CTRL_REG                 |                                 |

| capacitance                 | PMU_CTRL_REG                 |                                 |

|                             | SYS_CTRL_REG                 |                                 |

|                             | CLK_32K_REG_I                |                                 |

|                             | CLK_16M_REG_I                |                                 |

|                             | CLK_RCX32K_REG               |                                 |

|                             | TRIM_CTRL_REG                |                                 |

|                             | DEBUG_REG[DEBUGS_FREEZE_EN]  |                                 |

|                             | GP_CONTROL_REG[EM_MAP]       |                                 |

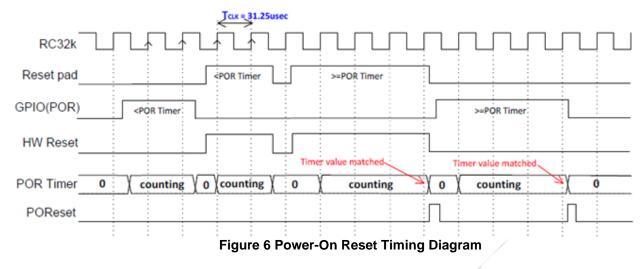

# 9.4.2 POWER-ON RESET FUNCTIONALITY

Power-On Reset functionality is available by two sources:

- Reset Pad: Reset pad is always capable of producing a Power-On Reset.

- GPIO Pin: A GPIO can be selected by the user application to act as POR source.

The time needed for the POReset pin to be active is stored in the POR\_TIMER\_REG. The register field POR\_TIME is a 7-bits field which holds time factor that the total time for POR is calculated. The maximum value of the field is 0x7F. The total time for POR is calculated by the following formula:

Total time = POR\_TIME x 4096 x RC32k clock period

where RC32k clock period = 31.25µs at 25oC.

The maximum time that a POR can be performed is ~16.2 seconds at 25oC.

The RC32k clock is temperature dependent so based on the temperature span of -10oC to 50oC, clock frequency range is calculated to be 25kHz to 39kHz. Then,

TPORcold = 13s

TPORhot = 20.8s

# 9.4.2.1 POR TIMER CLOCK

The Power-On Reset timer is clocked by the RC32k clock. If the application disables the RC32k, then the hardware takes care of enabling the RC32k clock when the POR source (Reset pad or GPIO) is asserted. It should be noted that if POR is generated from the Reset pad the RC32 will operate with the reset trimming value. If a GPIO is used as POR source, the RC32 clock will be trimmed. The deviation between both cases in terms of timing is expected to be minor.

# 9.4.2.2 RESET PAD

The Reset pad will produce a HW Reset if the pin active time is less than the programmed value in the POR\_TIMER\_REG register and a Power-On Reset if it is greater or equal the value. Reset pad is always Active High.

# 9.4.2.3 POR FROM GPIO

When a GPIO is used as a Power-on Reset source, the selected pin retains its capability to act as GPIO. The POR\_PIN\_REG[PIN\_SELECT] field holds the required GPIO pin number. If the value of the PIN\_SELECT field equals to 0 the POR over GPIO functionality is disabled. The polarity of the pin can be configured by the POR\_PIN\_REG [POR\_POLARITY] bit where 0 means Active Low and 1 Active High.

# 9.4.2.4 POWER-ON RESET TIMING DIAGRAM

The operation of the Power-On Reset for both Reset pad and GPIO is depicted in Figure 6.

# 9.4.2.5 POWER-ON RESET CONSIDERATIONS

If any of the POR sources is asserted then the POR timer starts to count. When a POR source is released before the timer has expired, POR timer will reset to 0. If a second source is asserted while the first is already asserted and the first is released after that point, POR will occur; assuming that the total time of both sources kept asserted is larger or equal than the POR\_TIME.

The POR\_PIN\_REG[PIN\_SELECT] field cannot survive any Reset (POR, HW, SW) and as such the user must take special care on setting up the GPIO POR source right after a reset. This also applies for the POR\_TIMER\_REG[POR\_TIME] field after a Power-On Reset.

The user must also take into account that if a GPIO is used as POR source, the dynamic current of the system increases due to the dynamic current consumed by the RC32k oscillator. This increase is calculated to be 100nA to 120nA and it is also present during sleep time period. POR from Reset pin does not add this dynamic current consumption.

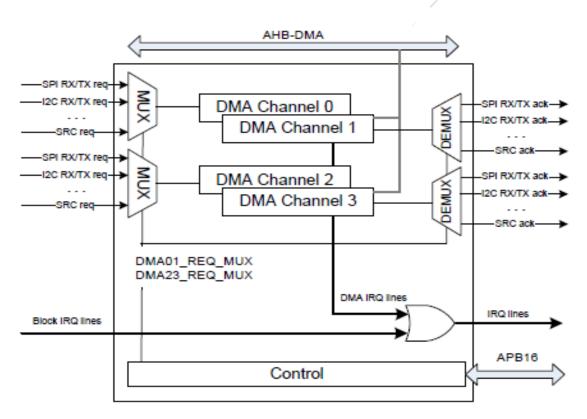

# 9.5 DMA Controller

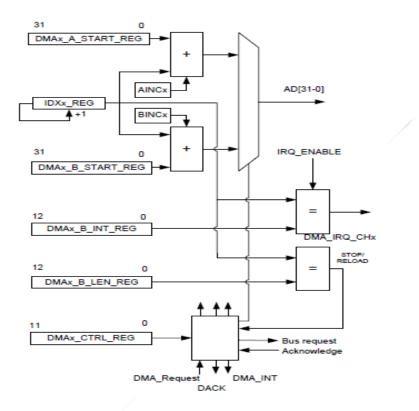

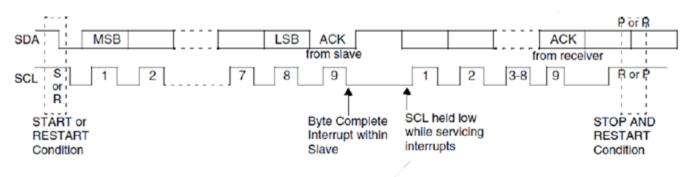

The DMA controller has 4 Direct Memory Access (DMA) channels for fast data transfers from/to SPI, UART, I2C, PDM and PCM to/from any on-chip RAM. The DMA controller off-loads the ARM interrupt rate if an interrupts is given after a number of transfers. More peripherals DMA requests are multiplexed on the 4 available channels, to increase utilization of the DMA. The block diagram of the DMA controller is depicted in Figure 7.

DOC-DS-14585-201911-3.8

Inventek Systems

Features:

- 4 channels with optional peripheral trigger

- Full 32 bit source and destination pointers.

- Flexible interrupt generation.

- Programmable length.

- Flexible peripheral request per channel.

- Option to initialize memory.

- Programmable Edge-Sensitive request support(suggested for UART and I2C service)

# 9.5.1 DMA PERIPHERALS

The list of peripherals that can request for a DMA service is presented in below table

| Name  | Direction |

|-------|-----------|

| SPI   | RX        |

| SPI   | TX        |

| UART  | RX        |

| UART  | TX        |

| UART2 | RX        |

| UART2 | TX        |

| I2C   | RX        |

| I2C   | TX        |

| PCM   | RX        |

| PCM   | TX        |

| SRC   | RX        |

| SRC   | TX        |

# 9.5.2 INPUT/OUTPUT MULTIPLEXER

The multiplexing of peripheral requests is controlled by DMA\_REQ\_MUX\_REG. Thus, if DMA\_REQ\_MUX\_REG [DMAxy\_SEL] is set to a certain (non-reserved) value, the TX/RX request from the corresponding peripheral will be routed to DMA channels y (TX request) and x (RX request) respectively.

Similarly, an acknowledging de-multiplexing mechanism is applied.

However, when two or more bit-fields (peripheral selectors) of DMA\_REQ\_MUX\_REG have the same value, the lesser significant selector will be given priority (see also the register's description).

# 9.5.3 DMA CHANNEL OPERATION

A DMA channel is switched on with bit DMA\_ON. This bit is automatically reset if the dma transfer is finished. The DMA channels can either be triggered by software or by a peripheral DMA request. If DREQ\_MODE is 0, then a DMA channel is immediately triggered. If DREQ\_MODE is 1 the DMA channel can be triggered by a Hardware interrupt.

If DMA starts, data is transferred from address DMAx\_A\_START\_REG to address DMAx\_B\_START\_REG for a length of DMAx\_LEN\_REG, which can be 8, 16 or 32 bits

wide. The address increment is realized with an internal 13 bits counter DMAx\_IDX\_REG, which is set to 0 if the DMA transfer starts and is compared with the DMA\_LEN\_REG after each transfer. The register value is multiplied according to the AINC and BINC and BW values before it is added to

DMA\_B\_START\_REG and DMA\_B\_START\_REG. AINC or BINC must be 0 for register access.

Figure 8 DMA Channel Diagram

If at the end of a DMA cycle, the DMA start condition is still true, the DMA continues. The DMA stops if DREQ\_MODE is low or if DMAx\_LEN\_REG is equal to the internal index register. This condition also clears the DMA\_ON bit.

If bit CIRCULAR is set to 1, the DMA controller automatically resets the internal index registers and continues from its starting address without intervention of the ARM CortexTM M0. If the DMA controller is started with DREQ\_MODE =0, the DMA will always stop, regardless of the state of CIRCULAR.

Each DMA channel can generate an interrupt if DMAx\_INT\_REG if equal to DMAx\_IDX\_REG. After the transfer and before DMAx\_IDX\_REG is incremented, the interrupt is generated. Example: if DMA\_x\_INT\_REG=0 and DMA\_x\_LEN\_REG=0, there will be one transfer and an interrupt.

# 9.5.4 DMA ARBITRATION

The priority level of a DMA channel can be set with bits DMA\_PRIO[2-0]. These bits determine which DMA channel will be activated in case more than one DMA channel requests DMA. If two or more channels have the same priority, an inherent priority applies, (see register description).

With DREQ\_MODE = 0, a DMA can be interrupted by a channel with a higher priority if the DMA\_IDLE bit is set. When DMA\_INIT is set, however, the DMA channel currently performing the transfer locks the bus and cannot be interrupted by any other channel, until the transfer is completed, regardless if DMA\_IDLE is set. The purpose of DMA\_INIT is to initialize a specific memory block with a certain value, fetched also from memory, without any interruption from other active DMA channels that may request the bus at the same time. Consequently, it should be used only for memory initialization, while when the DMA transfers data to/ from peripherals, it should be set to '0'. Note that AINC must be set to '0' and BINC to '1', when DMA\_INIT is enabled.

It should be noted that memory initialization could also be performed without having the DMA\_INIT enabled and by simply setting AINC to '0' and BINC to '1', provided that the source address memory value will not change during the transfer. However, it is not guaranteed that the DMA transfer will not be interrupted by other channels of higher priority, when these request access to the bus at the same time.

# 9.5.5 FREEZING DMA CHANNELS

Each channel of the DMA controller can be temporarily disabled by writing a 1 to freeze all channels at SET\_FREEZE\_REG.

To enable the channels again, a 1 to bits at the RESET\_FREEZE\_REG must be written.

There is no hardware protection from erroneous programming of the DMA registers.

It is noted that the on-going Memory-to-Memory transfers (DREQ\_MODE='0') cannot be interrupted. Thus, in that case, the corresponding DMA channels will be frozen after any on-going Memory-to memory transfer is completed.

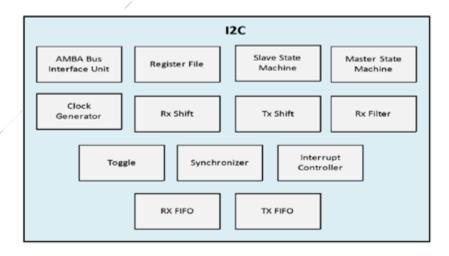

# 9.6 I2C Interface

The I2C Interface is a programmable control bus that provides support for the communications link between Integrated Circuits in a system. It is a simple two-wire bus with a software-defined protocol for system control, which is used in temperature sensors and voltage level translators to EEPROMs, general-purpose I/O, A/D and D/A converters.

Features

- Two-wire I2C serial interface consists of a serial data line (SDA) and a serial clock (SCL)

- Two speeds are supported:

- Standard mode (0 to 100kbit/s)

- Fast mode (<= 400kbit/s)</li>

- Clock synchronization

- 32B deep transmit/receive FIFOs

- Master transmit, Master receive operation

- 7-bit or 10-bit addressing

- 7-bit or 10-bit combined format transfers

- Bulk transmit mode

- Default slave address of 0x055

- Interrupt or polled-mode operation

- Handles Bit and Byte waiting at both bus speeds

- Programmable SDA hold time

- DMA support

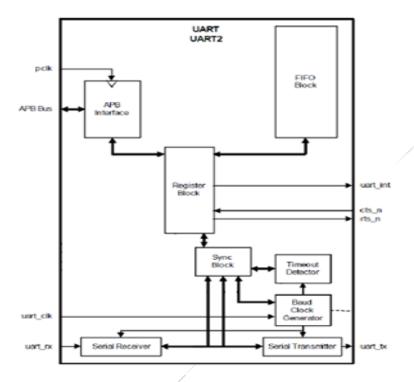

The I2C Controller block diagram shown in Figure 9 contains the following sub-blocks:

- AMBA Bus Interface Unit: Interfacing via the APB interface to access the register file.

- Register File: Contains configuration registers and is the interface with software.

- Master State Machine: Generates the I2C protocol for the master transfers.

- Clock Generator: Calculates the required timing to do the following:

- Generate the SCL clock when configured as a master

- Check for bus idle

- Generate a START and a STOP

- Setup the data and hold the data

- Rx Shift: Takes data into the design and extracts it in byte format.

- Tx Shift: Presents data supplied by CPU for transfer on the I2C bus.

- Rx Filter: Detects the events in the bus; for example, start, stop and arbitration lost.

- Toggle: Generates pulses on both sides and toggles to transfer signals across clock domains.

- Synchronizer: Transfers signals from one clock domain to another.

- Interrupt Controller: Generates the raw interrupt and interrupt flags, allowing them to be set and cleared.

- RX FIFO/TX: Holds the RX FIFO and TX FIFO register banks and controllers, along with their status levels.

# 9.7 I2C BUS TERMS

- The following terms relate to how the role of the I2C device and how it interacts with other I2C devices on the bus.

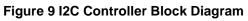

- Transmitter. The device that sends data to the bus. A transmitter can either be a device that initiates the data transmission to the bus (a master-transmitter) or responds to a request from the master to send data to the bus (a slave-transmitter).

- Receiver. The device that receives data from the bus. A receiver can either be a device that receives data on its own request (a master-receiver) or in response to a request from the master (a slave-receiver).

- Master. The component that initializes a transfer (START command), generates the clock (SCL) signal and terminates the transfer (STOP command). A master can be either a transmitter or a receiver.

- Slave. The device addressed by the master. A slave can be either receiver or transmitter. These concepts are illustrated in Figure 10.

Figure 10 Master/Slave and Transmitter/Receiver Relationships

- Multi-master. The ability for more than one master to co-exist on the bus at the same time without collision or data loss.

- Arbitration. The predefined procedure that authorizes only one master at a time to take control of the bus. For more information about this behavior, refer to Multiple Master Arbitration section.

- Synchronization. The predefined procedure that synchronizes the clock signals provided by two or more masters. For more information about this feature, refer to Clock Synchronization.

- SDA. Data signal line (Serial Data)

• SCL. Clock signal line (Serial Clock)

# 9.7.1.1BUS TRANSFER TERMS

The following terms are specific to data transfers that occur to/from the I2C bus:

- START (RESTART). Data transfer begins with a START or RESTART condition. The level of the SDA data line changes from high to low, while the SCL clock line remains high. When this occurs, the bus becomes busy.

- STOP. Data transfer is terminated by a STOP condition. This occurs when the level on the SDA data line passes from the low state to the high state, while the SCL clock line remains high. When the data transfer has been terminated, the bus is free or idle once again. The bus stays busy if a RESTART is generated instead of a STOP condition.

Note: START and RESTART conditions are functionally identical.

# 9.7.2 I2C BEHAVIOR

The I2C can be only be controlled via software to be an I2C master only, communicating with other I2C slaves;

The master is responsible for generating the clock and controlling the transfer of data. The slave is responsible for either transmitting or receiving data to/from the master. The acknowledgement of data is sent by the device that is receiving data, which can be either a master or a slave. As mentioned previously, the I2C protocol also allows multiple masters to reside on the I2C bus and uses an arbitration procedure to determine bus ownership.

Each slave has a unique address that is determined by the system designer. When a master wants to communicate with a slave, the master transmits a START/RESTART condition that is then followed by the slave's address and a control bit (R/W) to determine if the master wants to transmit data or receive data from the slave. The slave then sends an acknowledge pulse (ACK) after the address.

If the master (master-transmitter) is writing to the slave (slave-receiver), the receiver gets one byte of data. This transaction continues until the master terminates the

transmission with a STOP condition. If the master is reading from a slave (masterreceiver), the slave transmits (slave-transmitter) a byte of data to the master, and the

master then acknowledges the transaction with the ACK pulse. This transaction continues until the master terminates the transmission by not acknowledging (NACK) the transaction after the last byte is received, and then the master issues a STOP condition or addresses another slave after issuing a RESTART condition. This behavior is illustrated in Figure 11.

Figure 11 Data Transfer on the I2C Bus

The I2C is a synchronous serial interface. The SDA line is a bidirectional signal and changes only while the SCL line is low, except for STOP, START, and RESTART conditions. The output drivers are open-drain or open-collector to perform wire-AND functions on the bus. The maximum number of devices on the bus is limited by only the maximum capacitance specification of 400pF. Data is transmitted in byte packages.

# 9.7.2.1 START AND STOP GENERATION

When operating as an I2C master, putting data into the transmit FIFO causes the I2C Controller to generate a START condition on the I2C bus. Allowing the transmit FIFO to empty causes the I2C Controller to generate a STOP condition on the I2C bus.

When operating as a slave, the I2C Controller does not generate START and STOP conditions, as per the protocol. However, if a read request is made to the I2C Controller, it holds the SCL line low until read data has been supplied to it. This stalls the I2C bus until read data is provided to the slave I2C Controller, or the I2C Controller slave is disabled by writing a 0 to I2C\_ENABLE.

## 9.7.2.2 COMBINED FORMATS

The I2C Controller supports mixed read and write combined format transactions in both 7-bit and 10-bit addressing modes.

The I2C Controller does not support mixed address and mixed address format - that is, a 7-bit address transaction followed by a 10-bit address transaction or vice versa - combined format transactions.

To initiate combined format transfers, I2C\_CON.I2C\_RESTART\_EN should be set to 1. With this value set and operating as a master, when the I2C Controller completes an I2C transfer, it checks the transmit FIFO and executes the next transfer. If the direction of this transfer differs from the previous transfer, the combined format is used to issue the transfer. If the transmit FIFO is empty when the current I2C transfer completes, a STOP is issued, and the next transfer is issued following a START condition.

## 9.7.3 I2C PROTOCOLS

The I2C Controller has the following protocols:

- START and STOP Conditions

- Addressing Slave Protocol

- Transmitting and Receiving Protocol

- START BYTE Transfer Protocol

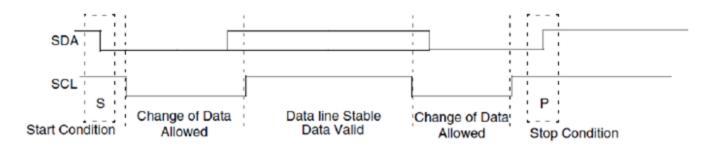

## 9.7.3.1 START AND STOP CONDITIONS

When the bus is idle, both the SCL and SDA signals are pulled high through external pull-up resistors on the bus. When the master wants to start a transmission on the bus, the master issues a START condition. This is defined to be a high-to-low transition of the SDA signal while SCL is 1. When the master wants to terminate the transmission, the master issues a STOP condition. This is defined to be a low-to-high transition of the SDA line while SCL is 1. Figure 12 shows the timing of the START and STOP conditions. When data is being transmitted on the bus, the SDA line must be stable when SCL is 1.

ISM14585-L35 Specification

Figure 12 START and STOP Conditions

Note: The signal transitions for the START/STOP conditions, as depicted in Figure 12, reflect those observed at the output signals of the Master driving the I2C bus. Care should be taken when observing the SDA/SCL signals at the input signals of the Slave(s), because unequal line delays may result in an incorrect SDA/SCL timing relationship.

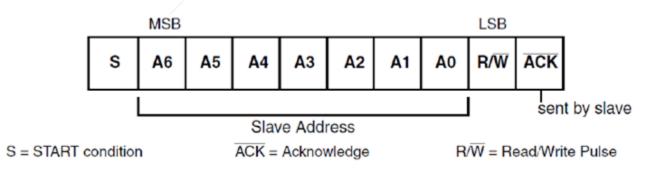

# 9.7.3.2 ADDRESSING SLAVE PROTOCOL

There are two address formats: 7-bit address format and 10-bit address format.

### 7-bit Address Format

During the 7-bit address format, the first seven bits (bits 7:1) of the first byte set the slave address and the LSB bit (bit 0) is the R/W bit as shown in Figure 13. When bit 0 (R/W) is set to 0, the master writes to the slave. When bit 0 (R/W) is set to 1, the master reads from the slave.

### 10-bit Address Format

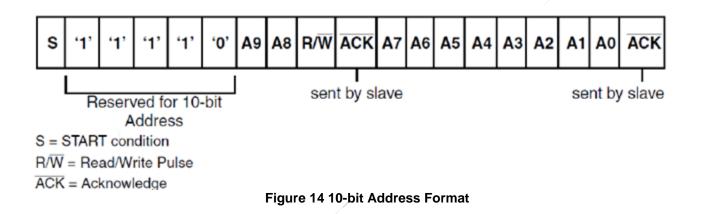

During 10-bit addressing, two bytes are transferred to set the 10-bit address. The transfer of the first byte contains the following bit definition. The first five bits (bits 7:3) notify the slaves that this is a 10-bit transfer followed by the next two bits (bits 2:1), which set the slaves address bits 9:8, and the LSB bit (bit 0) is the R/W bit. The second byte transferred sets bits 7:0 of the slave address. Figure 14 shows the 10-bit address format, and below table defines the special purpose and reserved first byte addresses.

| Slave Address | R/W Bits | Description                                                                                                       |  |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------|--|

| 0000 000      | 0        | General Call Address. I2C Controller places the data in the receive<br>buffer and issues a General Call interrupt |  |

| 0000 000      | 1        | START byte. For more details, refer to "START BYTE Transfer<br>Protocol" 0000                                     |  |

| 0000 001      | Х        | CBUS address. I2C Controller ignores these accesses                                                               |  |

| 0000 010      | Х        | Reserved                                                                                                          |  |

| 0000 011      | Х        | Reserved                                                                                                          |  |

| 0000 1XX      | Х        | High-speed master code (for more information, refer to "Multiple<br>Master Arbitration"                           |  |

| 1111 1XX      | Х        | Reserved                                                                                                          |  |

| 1111 0XX      | Х        | 10-bit slave addressing                                                                                           |  |

The I2C Controller does not restrict you from using these reserved addresses. However, if you use these reserved addresses, you may run into incompatibilities with other I2C components.

## 9.7.3.3TRANSMITTING AND RECEIVING PROTOCOLS

The master can initiate data transmission and reception to/from the bus, acting as either a master-transmitter or master-receiver. A slave responds to requests from the master to either transmit data or receive data to/from the bus, acting as either a slave-transmitter or slave-receiver, respectively.

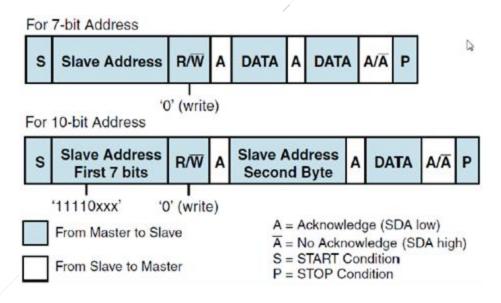

### Master-Transmitter and Slave-Receiver

All data is transmitted in byte format, with no limit on the number of bytes transferred per data transfer. After the master sends the address and R/W bit or the master transmits a byte of data to the slave, the slave-receiver must respond with the acknowledge signal (ACK). When a slave-receiver does not respond with an ACK pulse, the master aborts the transfer by issuing a STOP condition.

The slave must leave the SDA line high so that the master can abort the transfer. If the master-transmitter is transmitting data as shown in Figure 15, then the slave-receiver responds to the master-transmitter with an acknowledge pulse after every byte of data is received.

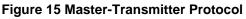

### Master-Receiver and Slave-Transmitter

If the master is receiving data as shown in Figure 16 then the master responds to the slave-transmitter with an acknowledge pulse after a byte of data has been received, except for the last byte. This is the way the master-receiver notifies the slave-transmitter that this is the last byte. The slave-transmitter relinquishes the SDA line after detecting the No Acknowledge (NACK) so that the master can issue a STOP condition.

When a master does not want to relinquish the bus with a STOP condition, the master can issue a RESTART condition. This is identical to a START condition except it occurs after the ACK pulse. The master can then communicate with the same slave or a different slave.

#### Figure 16 Master-Receiver Protocol

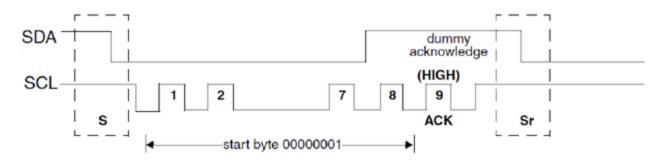

### START BYTE Transfer Protocol

The START BYTE transfer protocol is set up for systems that do not have an on-board dedicated I2C hardware module. When the I2C Controller is addressed as a slave, it always samples the I2C bus at the highest speed supported so that it never requires a START BYTE transfer. However, when I2C Controller is a master, it supports the generation of START BYTE transfers at the beginning of every transfer in case a slave device requires it. This protocol consists of seven zeros being transmitted followed by a 1, as illustrated in Figure 17. This allows the processor that is polling the bus to undersample the address phase until 0 is detected. Once the microcontroller detects a 0, it switches from the under sampling rate to the correct rate of the master.

The START BYTE procedure is as follows:

- 1. Master generates a START condition.

- 2. Master transmits the START byte (0000 0001).

- 3. Master transmits the ACK clock pulse. (Present only to conform with the byte handling format used on the bus)

- 4. No slave sets the ACK signal to 0.

- 5. Master generates a RESTART (R) condition.

A hardware receiver does not respond to the START BYTE because it is a reserved address and resets after the RESTART condition is generated.

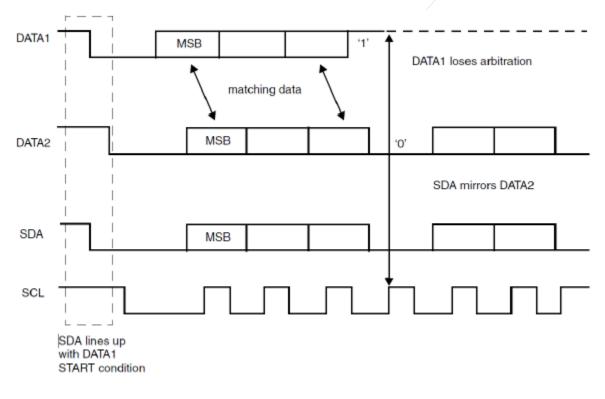

# 9.7.4 MULTIPLE MASTER ARBITRATION

The I2C Controller bus protocol allows multiple masters to reside on the same bus. If there are two masters on the same I2C-bus, there is an arbitration procedure if both try to take control of the bus at the same time by generating a START condition at the same time. Once a master (for example, a microcontroller) has control of the bus, no other master can take control until the first master sends a STOP condition and places the bus in an idle state.

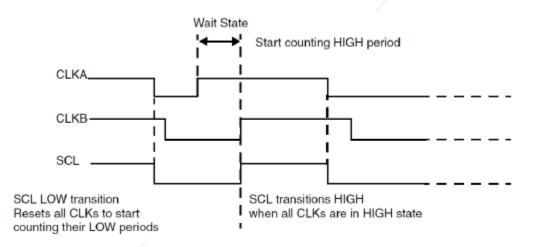

Arbitration takes place on the SDA line, while the SCL line is 1. The master, which transmits a 1 while the other master transmits 0, loses arbitration and turns off its data output stage. The master that lost arbitration can continue to generate clocks until the end of the byte transfer. If both masters are addressing the same slave device, the arbitration could go into the data phase. Figure 18 illustrates the timing of when two masters are arbitrating on the bus.

For high-speed mode, the arbitration cannot go into the data phase because each master is programmed with a unique high-speed master code. This 8-bit code is defined by the system designer and is set by writing to the High Speed Master Mode Code Address Register, I2C\_HS\_MADDR. Because the codes are unique, only one master can win arbitration, which occurs by the end of the transmission of the high-speed master code.