# 256K x 36 and 512K x 18 9Mb, PIPELINE 'NO WAIT' STATE BUS SRAM

**JUNE 2017**

#### **FEATURES**

- · 100 percent bus utilization

- · No wait cycles between Read and Write

- · Internal self-timed write cycle

- Individual Byte Write Control

- · Single R/W (Read/Write) control pin

- Clock controlled, registered address, data and control

- Interleaved or linear burst sequence control using MODE input

- Three chip enables for simple depth expansion and address pipelining

- · Power Down mode

- · Common data inputs and data outputs

- CKE pin to enable clock and suspend operation

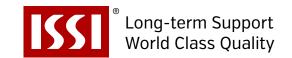

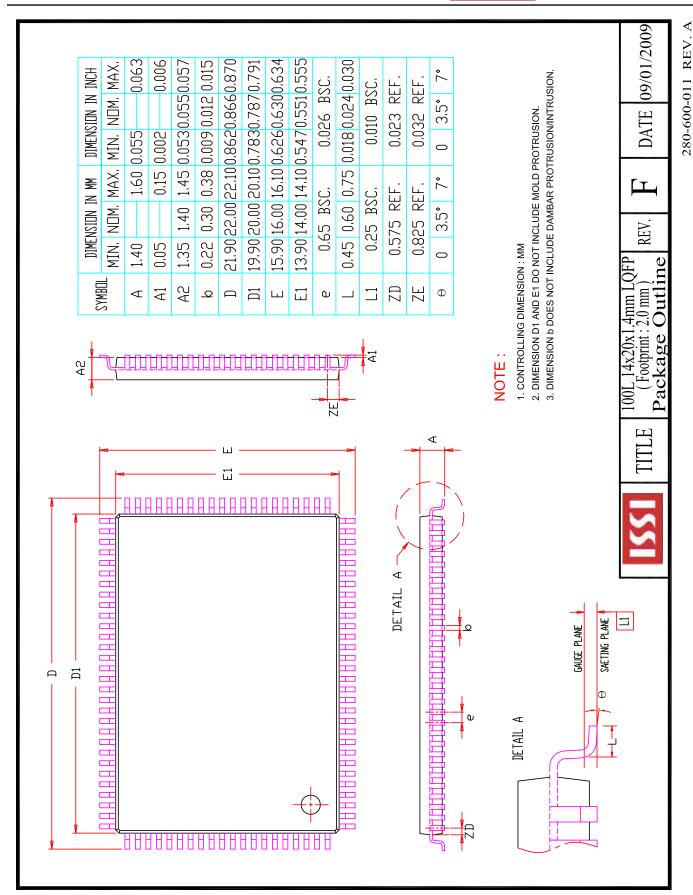

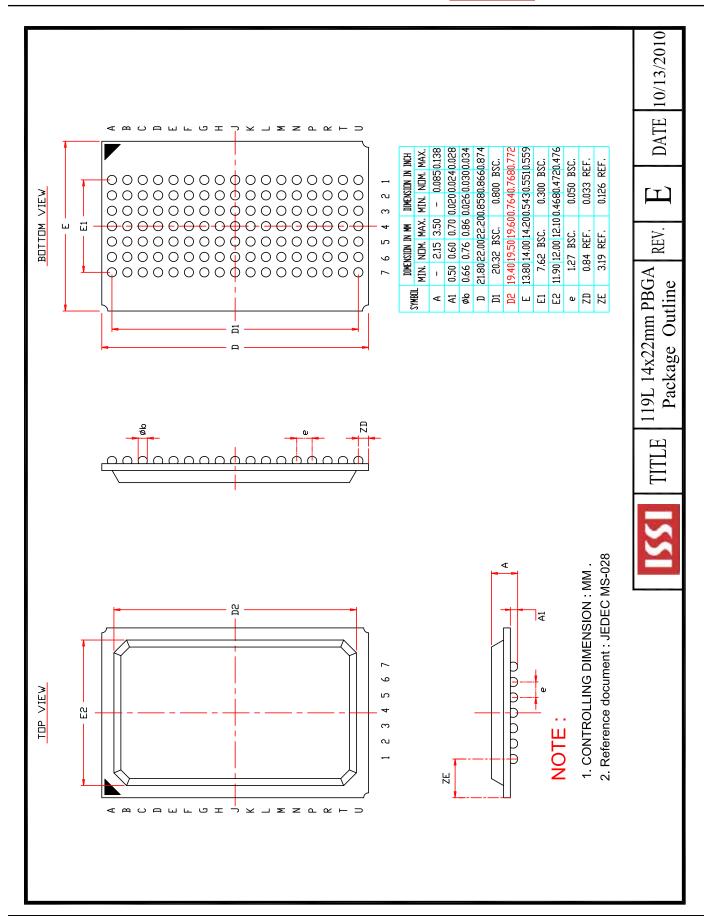

- JEDEC 100-pin QFP, 165-ball BGA and 119-ball BGA packages

- Power supply:

NLP: VDD 3.3V (± 5%), VDDQ 3.3V/2.5V (± 5%)

NVP: VDD 2.5V (± 5%), VDDQ 2.5V (± 5%)

NVVP: VDD 1.8V (± 5%), VDDQ 1.8V (± 5%)

- JTAG Boundary Scan for BGA packages

- Industrial temperature available

- Lead-free available

#### DESCRIPTION

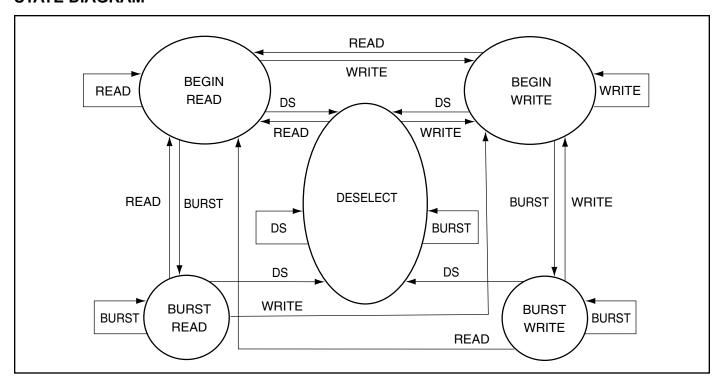

The 9 Meg product family features high-speed, low-power synchronous static RAMs designed to provide a burstable, high-performance, 'no wait' state, device for networking and communications applications. They are organized as 256K words by 36 bits and 512K words by 18 bits, fabricated with *ISSI*'s advanced CMOS technology.

Incorporating a 'no wait' state feature, wait cycles are eliminated when the bus switches from read to write, or write to read. This device integrates a 2-bit burst counter, high-speed SRAM core, and high-drive capability outputs into a single monolithic circuit.

All synchronous inputs pass through registers are controlled by a positive-edge-triggered single clock input. Operations may be suspended and all synchronous inputs ignored when Clock Enable,  $\overline{\text{CKE}}$  is HIGH. In this state the internal device will hold their previous values.

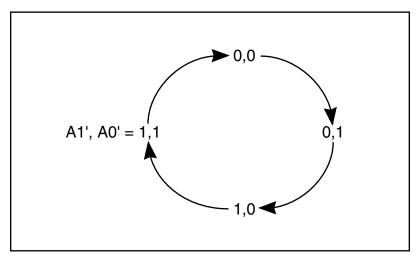

All Read, Write and Deselect cycles are initiated by the ADV input. When the ADV is HIGH the internal burst counter is incremented. New external addresses can be loaded when ADV is LOW.

Write cycles are internally self-timed and are initiated by the rising edge of the clock inputs and when  $\overline{\text{WE}}$  is LOW. Separate byte enables allow individual bytes to be written.

A burst mode pin (MODE) defines the order of the burst sequence. When tied HIGH, the interleaved burst sequence is selected. When tied LOW, the linear burst sequence is selected.

#### **FAST ACCESS TIME**

| Symbol      | Parameter         | -250 | -200 | -166 | Units |

|-------------|-------------------|------|------|------|-------|

| <b>t</b> KQ | Clock Access Time | 2.6  | 3.1  | 3.5  | ns    |

| <b>t</b> kc | Cycle Time        | 4    | 5    | 6    | ns    |

|             | Frequency         | 250  | 200  | 166  | MHz   |

Copyright © 2017 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

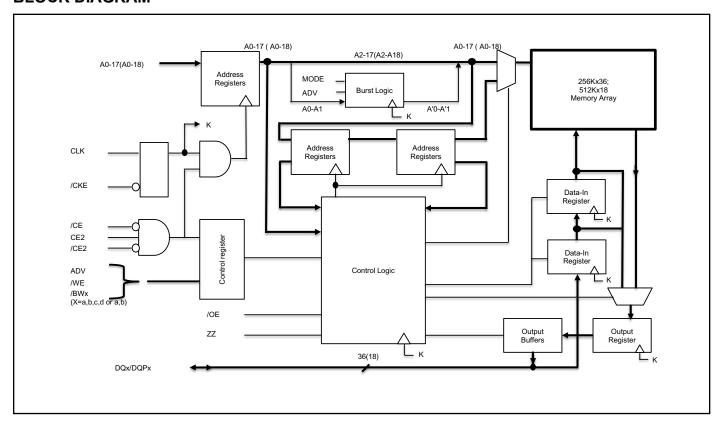

#### **BLOCK DIAGRAM**

|   |   |   |   |   |   |   |   | _ |

|---|---|---|---|---|---|---|---|---|

|   | _ | _ | _ | _ | 0 | _ | _ |   |

|   | _ | _ | _ | _ | 0 | _ | _ |   |

|   | _ | _ | _ | _ | 0 | _ | _ |   |

| ( | C | O | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | Ο | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

| ( | C | 0 | 0 | 0 | 0 | 0 | 0 |   |

|   |   |   |   |   |   |   |   |   |

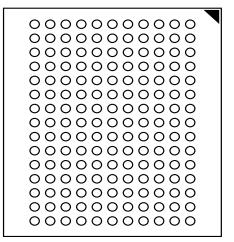

Bottom View 119-Ball, 14 mm x 22 mm BGA

Bottom View 165-Ball, 13 mm x 15mm BGA

# PIN CONFIGURATION — 256K x 36, 165-Ball BGA (TOP VIEW)

|   | 1    | 2   | 3    | 4               | 5   | 6   | 7   | 8               | 9    | 10  | 11   |

|---|------|-----|------|-----------------|-----|-----|-----|-----------------|------|-----|------|

| Α | NC   | Α   | CE   | B₩c             | ≅₩b | CE2 | CKE | ADV             | Α    | Α   | NC   |

| В | NC   | Α   | CE2  | ≅Wd             | BWa | CLK | WE  | ŌĒ              | NC   | Α   | NC   |

| С | DQPc | NC  | Vddq | Vss             | Vss | Vss | Vss | Vss             | VDDQ | NC  | DQPb |

| D | DQc  | DQc | VDDQ | VDD             | Vss | Vss | Vss | VDD             | VDDQ | DQb | DQb  |

| Е | DQc  | DQc | VDDQ | VDD             | Vss | Vss | Vss | VDD             | VDDQ | DQb | DQb  |

| F | DQc  | DQc | VDDQ | VDD             | Vss | Vss | Vss | V <sub>DD</sub> | Vddq | DQb | DQb  |

| G | DQc  | DQc | VDDQ | VDD             | Vss | Vss | Vss | VDD             | VDDQ | DQb | DQb  |

| Н | NC   | NC  | NC   | V <sub>DD</sub> | Vss | Vss | Vss | V <sub>DD</sub> | NC   | NC  | ZZ   |

| J | DQd  | DQd | VDDQ | VDD             | Vss | Vss | Vss | VDD             | VDDQ | DQa | DQa  |

| K | DQd  | DQd | VDDQ | V <sub>DD</sub> | Vss | Vss | Vss | V <sub>DD</sub> | VDDQ | DQa | DQa  |

| L | DQd  | DQd | VDDQ | VDD             | Vss | Vss | Vss | VDD             | VDDQ | DQa | DQa  |

| М | DQd  | DQd | VDDQ | VDD             | Vss | Vss | Vss | VDD             | VDDQ | DQa | DQa  |

| N | DQPd | NC  | VDDQ | Vss             | NC  | NC  | NC  | Vss             | VDDQ | NC  | DQPa |

| Р | NC   | NC  | А    | А               | TDI | A1* | TDO | Α               | А    | Α   | NC   |

| R | MODE | NC  | А    | Α               | TMS | A0* | TCK | Α               | Α    | Α   | Α    |

Note: A0 and A1 are the two least significant bits (LSB) of the address field and set the internal burst counter if burst is desired.

| Symbol       | Pin Name                                   |

|--------------|--------------------------------------------|

| Α            | Address Inputs                             |

| A0, A1       | Synchronous Burst Address Inputs           |

| ADV          | Synchronous Burst Address Advance/<br>Load |

| WE           | Synchronous Read/Write Control Input       |

| CLK          | Synchronous Clock                          |

| CKE          | Clock Enable                               |

| CE, CE2, CE2 | Synchronous Chip Enable                    |

| BWx (x=a-d)  | Synchronous Byte Write Inputs              |

| ŌĒ           | Output Enable                              |

| ZZ           | Power Sleep Mode                           |

| MODE Burst Sequence Selection |                     |  |  |  |  |

|-------------------------------|---------------------|--|--|--|--|

| TCK, TDIJTAG Pins<br>TDO, TMS |                     |  |  |  |  |

| VDD                           | Power Supply        |  |  |  |  |

| NC                            | No Connect          |  |  |  |  |

| DQx                           | Data Inputs/Outputs |  |  |  |  |

| DQPx                          | Parity Data I/O     |  |  |  |  |

| VDDQ                          | I/O Power Supply    |  |  |  |  |

| Vss                           | Ground              |  |  |  |  |

|                               |                     |  |  |  |  |

# 119-PIN BGA PACKAGE CONFIGURATION —256K x 36 (TOP VIEW)

|   | 1    | 2    | 3                | 4           | 5   | 6    | 7    |

|---|------|------|------------------|-------------|-----|------|------|

| Α | VDDQ | Α    | Α                | NC          | Α   | Α    | VDDQ |

| В | NC   | CE2  | Α                | ADV         | Α   | CE2  | NC   |

| С | NC   | Α    | Α                | Vdd         | Α   | Α    | NC   |

| D | DQc  | DQPc | Vss              | NC          | Vss | DQPb | DQb  |

| Ε | DQc  | DQc  | Vss              | CE          | Vss | DQb  | DQb  |

| F | VDDQ | DQc  | Vss              | ŌĒ          | Vss | DQb  | VDDQ |

| G | DQc  | DQc  | ≅Wc              | Α           | ≅₩b | DQb  | DQb  |

| Н | DQc  | DQc  | Vss              | WE          | Vss | DQb  | DQb  |

| J | VDDQ | VDD  | NC               | VDD         | NC  | VDD  | VDDQ |

| K | DQd  | DQd  | Vss              | CLK         | Vss | DQa  | DQa  |

| L | DQd  | DQd  | $\overline{BW}d$ | NC          | ≅Wa | DQa  | DQa  |

| М | VDDQ | DQd  | Vss              | CKE         | Vss | DQa  | VDDQ |

| N | DQd  | DQd  | Vss              | A1*         | Vss | DQa  | DQa  |

| Р | DQd  | DQPd | Vss              | <b>A</b> 0* | Vss | DQPa | DQa  |

| R | NC   | А    | MODE             | VDD         | NC  | Α    | NC   |

| Т | NC   | NC   | Α                | Α           | Α   | NC   | ZZ   |

| U | Vddq | TMS  | TDI              | TCK         | TDO | NC   | VDDQ |

Note: A0 and A1 are the two least significant bits(LSB) of the address field and set the internal burst counter if burst is desired.

| Pin Name                                   |

|--------------------------------------------|

| Address Inputs                             |

| Synchronous Burst Address Inputs           |

| Synchronous Burst Address Advance/<br>Load |

| Synchronous Read/Write Control Input       |

| Synchronous Clock                          |

| Clock Enable                               |

| Synchronous Chip Select                    |

| Synchronous Chip Select                    |

| Synchronous Chip Select                    |

| Synchronous Byte Write Inputs              |

|                                            |

| ŌĒ              | Output Enable            |

|-----------------|--------------------------|

| ZZ              | Power Sleep Mode         |

| MODE            | Burst Sequence Selection |

| TCK, TDO        | JTAG Pins                |

| TMS, TDI        |                          |

| V <sub>DD</sub> | Power Supply             |

| Vss             | Ground                   |

| NC              | No Connect               |

| DQa-DQd         | Data Inputs/Outputs      |

| DQPa-Pd         | Parity Data I/O          |

| VDDQ            | I/O Power Supply         |

|                 |                          |

# 165-PIN BGA PACKAGE CONFIGURATION —512K x 18 (TOP VIEW)

|   | 1    | 2   | 3    | 4                | 5   | 6   | 7   | 8   | 9    | 10  | 11   |

|---|------|-----|------|------------------|-----|-----|-----|-----|------|-----|------|

| Α | NC   | Α   | CE   | $\overline{BW}b$ | NC  | CE2 | CKE | ADV | Α    | Α   | Α    |

| В | NC   | Α   | CE2  | NC               | ≅Wa | CLK | WE  | ŌĒ  | NC   | Α   | NC   |

| С | NC   | NC  | Vddq | Vss              | Vss | Vss | Vss | Vss | Vddq | NC  | DQPa |

| D | NC   | DQb | VDDQ | Vdd              | Vss | Vss | Vss | VDD | VDDQ | NC  | DQa  |

| Ε | NC   | DQb | VDDQ | VDD              | Vss | Vss | Vss | VDD | VDDQ | NC  | DQa  |

| F | NC   | DQb | VDDQ | Vdd              | Vss | Vss | Vss | VDD | VDDQ | NC  | DQa  |

| G | NC   | DQb | VDDQ | Vdd              | Vss | Vss | Vss | VDD | VDDQ | NC  | DQa  |

| Н | NC   | NC  | NC   | Vdd              | Vss | Vss | Vss | VDD | NC   | NC  | ZZ   |

| J | DQb  | NC  | VDDQ | VDD              | Vss | Vss | Vss | Vdd | VDDQ | DQa | NC   |

| K | DQb  | NC  | VDDQ | VDD              | Vss | Vss | Vss | Vdd | VDDQ | DQa | NC   |

| L | DQb  | NC  | VDDQ | Vdd              | Vss | Vss | Vss | VDD | VDDQ | DQa | NC   |

| М | DQb  | NC  | VDDQ | Vdd              | Vss | Vss | Vss | Vdd | VDDQ | DQa | NC   |

| N | DQPb | NC  | VDDQ | Vss              | NC  | NC  | NC  | Vss | VDDQ | NC  | NC   |

| Р | NC   | NC  | Α    | А                | TDI | A1* | TDO | Α   | Α    | А   | NC   |

| R | MODE | NC  | Α    | Α                | TMS | A0* | TCK | Α   | А    | А   | Α    |

Note: A0 and A1 are the two least significant bits (LSB) of the address field and set the internal burst counter if burst is desired.

| Symbol                                                    | Pin Name                                   |

|-----------------------------------------------------------|--------------------------------------------|

| Α                                                         | Address Inputs                             |

| A0, A1                                                    | Synchronous Burst Address Inputs           |

| ADV                                                       | Synchronous Burst Address Advance/<br>Load |

| WE                                                        | Synchronous Read/Write Control Input       |

| CLK                                                       | Synchronous Clock                          |

| CKE                                                       | Clock Enable                               |

| $\overline{\text{CE}}, \overline{\text{CE2}}, \text{CE2}$ | Synchronous Chip Enable                    |

| BWx (x=a,b)                                               | Synchronous Byte Write Inputs              |

| ŌĒ                                                        | Output Enable                              |

| ZZ                                                        | Power Sleep Mode                           |

| MODE                 | Burst Sequence Selection |

|----------------------|--------------------------|

| TCK, TDI<br>TDO, TMS | JTAG Pins                |

| VDD                  | Power Supply             |

| NC                   | No Connect               |

| DQx                  | Data Inputs/Outputs      |

| DQPx                 | Parity Data I/O          |

| VDDQ                 | I/O Power Supply         |

| Vss                  | Ground                   |

# 119-PIN BGA PACKAGE CONFIGURATION —512K x 18 (TOP VIEW)

|   | 1    | 2    | 3                | 4           | 5   | 6    | 7    |

|---|------|------|------------------|-------------|-----|------|------|

| Α | VDDQ | Α    | Α                | NC          | Α   | Α    | VDDQ |

| В | NC   | CE2  | Α                | ADV         | Α   | CE2  | NC   |

| С | NC   | Α    | Α                | Vdd         | Α   | Α    | NC   |

| D | DQb  | NC   | Vss              | NC          | Vss | DQPa | NC   |

| Е | NC   | DQb  | Vss              | CE          | Vss | NC   | DQa  |

| F | VDDQ | NC   | Vss              | ŌE          | Vss | DQa  | VDDQ |

| G | NC   | DQb  | $\overline{BW}b$ | Α           | NC  | NC   | DQa  |

| Н | DQb  | NC   | Vss              | WE          | Vss | DQa  | NC   |

| J | VDDQ | Vdd  | NC               | VDD         | NC  | Vdd  | VDDQ |

| K | NC   | DQb  | Vss              | CLK         | Vss | NC   | DQa  |

| L | DQb  | NC   | NC               | NC          | B₩a | DQa  | NC   |

| М | VDDQ | DQb  | Vss              | CKE         | Vss | NC   | VDDQ |

| N | DQb  | NC   | Vss              | A1*         | Vss | DQa  | NC   |

| Р | NC   | DQPb | Vss              | <b>A</b> o* | Vss | NC   | DQa  |

| R | NC   | А    | MODE             | VDD         | NC  | Α    | NC   |

| Т | NC   | Α    | Α                | NC          | Α   | Α    | ZZ   |

| U | VDDQ | TMS  | TDI              | TCK         | TDO | NC   | VDDQ |

| U | Vddq |      | TDI              | TCK         | TDO | NC   | VDDC |

Note: A0 and A1 are the two least significant bits(LSB) of the address field and set the internal burst counter if burst is desired.

| Symbol      | Pin Name                                   |

|-------------|--------------------------------------------|

| Α           | Address Inputs                             |

| A0, A1      | Synchronous Burst Address Inputs           |

| ADV         | Synchronous Burst Address Advance/<br>Load |

| WE          | Synchronous Read/Write Control Input       |

| CLK         | Synchronous Clock                          |

| CKE         | Clock Enable                               |

| CE          | Synchronous Chip Select                    |

| CE2         | Synchronous Chip Select                    |

| CE2         | Synchronous Chip Select                    |

| BWx (x=a,b) | Synchronous Byte Write Inputs              |

| ŌĒ       | Output Enable            |

|----------|--------------------------|

| ZZ       | Power Sleep Mode         |

| MODE     | Burst Sequence Selection |

| TCK, TDO | JTAG Pins                |

| TMS, TDI |                          |

| VDD      | Power Supply             |

| Vss      | Ground                   |

| NC       | No Connect               |

| DQa-DQb  | Data Inputs/Outputs      |

| DQPa-Pb  | Parity Data I/O          |

| VDDQ     | I/O Power Supply         |

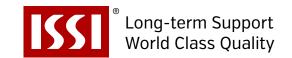

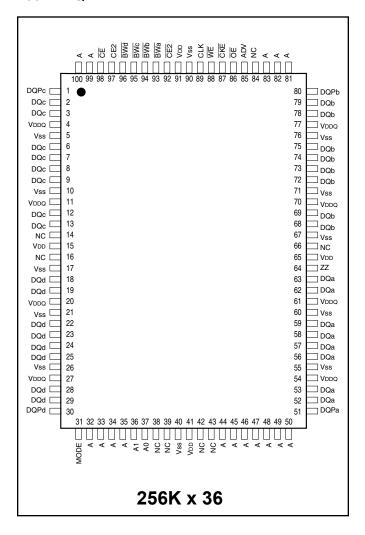

# PIN CONFIGURATION 100-Pin QFP

| PIN DESCRI | FIIONO                                                                               |

|------------|--------------------------------------------------------------------------------------|

| A0, A1     | Synchronous Address Inputs. These pins must tied to the two LSBs of the address bus. |

| Α          | Synchronous Address Inputs                                                           |

| CLK        | Synchronous Clock                                                                    |

| ADV        | Synchronous Burst Address Advance                                                    |

| BWa-BWd    | Synchronous Byte Write Enable                                                        |

| WE         | Write Enable                                                                         |

| CKE        | Clock Enable                                                                         |

| Vss        | Ground for Core                                                                      |

| NC         | Not Connected                                                                        |

| CE, CE2, CE2    | Synchronous Chip Enable       |

|-----------------|-------------------------------|

| ŌĒ              | Output Enable                 |

| DQa-DQd         | Synchronous Data Input/Output |

| DQPa-DQPd       | Parity Data I/O               |

| MODE            | Burst Sequence Selection      |

| V <sub>DD</sub> | Power Supply                  |

| Vss             | Ground for output Buffer      |

| VDDQ            | I/O Power Supply              |

| ZZ              | Snooze Enable                 |

#### STATE DIAGRAM

#### SYNCHRONOUS TRUTH TABLE(1)

| Operation             | Address<br>Used  | CE | CE2 | CE2 | ADV | WE | ≅₩x | ŌĒ | CKE | CLK        |

|-----------------------|------------------|----|-----|-----|-----|----|-----|----|-----|------------|

| Not Selected          | N/A              | Н  | Х   | Х   | L   | Χ  | Х   | Χ  | L   | <b>↑</b>   |

| Not Selected          | N/A              | Χ  | L   | Х   | L   | Χ  | Χ   | Χ  | L   | <b>↑</b>   |

| Not Selected          | N/A              | Χ  | X   | Н   | L   | Χ  | Χ   | Χ  | L   | <b>↑</b>   |

| Not Selected Continue | N/A              | Χ  | Х   | Χ   | Н   | Х  | Х   | Х  | L   | $\uparrow$ |

| Begin Burst Read      | External Address | L  | Н   | L   | L   | Н  | Х   | L  | L   | $\uparrow$ |

| Continue Burst Read   | Next Address     | Х  | Х   | Х   | Н   | Χ  | Х   | L  | L   | <b>↑</b>   |

| NOP/Dummy Read        | External Address | L  | Н   | L   | L   | Н  | Х   | Н  | L   | $\uparrow$ |

| Dummy Read            | Next Address     | Х  | Х   | Х   | Н   | Χ  | Х   | Н  | L   | <b>↑</b>   |

| Begin Burst Write     | External Address | L  | Н   | L   | L   | L  | L   | Χ  | L   | <b>↑</b>   |

| Continue Burst Write  | Next Address     | Χ  | Х   | Χ   | Н   | Χ  | L   | Χ  | L   | <b>↑</b>   |

| NOP/Write Abort       | N/A              | L  | Н   | L   | L   | L  | Н   | Х  | L   | <b>↑</b>   |

| Write Abort           | Next Address     | Х  | Х   | Х   | Н   | Х  | Н   | Х  | L   | <b>↑</b>   |

| Ignore Clock          | Current Address  | Χ  | Χ   | Χ   | Χ   | Χ  | Χ   | Χ  | Н   | <b>↑</b>   |

#### Notes:

- 1. "X" means don't care.

- 2. The rising edge of clock is symbolized by \( \backslash

- 3. A continue deselect cycle can only be entered if a deselect cycle is executed first.

- 4. WE = L means Write operation in Write Truth Table.

WE = H means Read operation in Write Truth Table.

- 5. Operation finally depends on status of asynchronous pins (ZZ and  $\overline{OE}$ ).

#### **ASYNCHRONOUS TRUTH TABLE(1)**

| Operation  | ZZ | ŌĒ | I/O STATUS  |  |

|------------|----|----|-------------|--|

| Sleep Mode | Н  | Х  | High-Z      |  |

| Read       | L  | L  | DQ          |  |

|            | L  | Н  | High-Z      |  |

| Write      | L  | Х  | Din, High-Z |  |

| Deselected | L  | Х  | High-Z      |  |

#### Notes:

- 1. X means "Don't Care".

- 2. For write cycles following read cycles, the output buffers must be disabled with  $\overline{\text{OE}}$ , otherwise data bus contention will occur.

- 3. Sleep Mode means power Sleep Mode where stand-by current does not depend on cycle time.

- 4. Deselected means power Sleep Mode where stand-by current depends on cycle time.

### **WRITE TRUTH TABLE** (x18)

| Operation       | WE | BWa | BW <b>b</b> |   |

|-----------------|----|-----|-------------|---|

| READ            | Н  | Х   | Х           |   |

| WRITE BYTE a    | L  | L   | Н           |   |

| WRITE BYTE b    | L  | Н   | L           |   |

| WRITE ALL BYTEs | L  | L   | L           | - |

| WRITE ABORT/NOP | L  | Н   | Н           |   |

#### Notes:

- 1. X means "Don't Care".

- 2. All inputs in this table must beet setup and hold time around the rising edge of CLK.

# **WRITE TRUTH TABLE** (x36)

| Operation       | WE | BWa | <u></u> B₩ <b>b</b> | BWc | ≅Wd |   |

|-----------------|----|-----|---------------------|-----|-----|---|

| READ            | Н  | Х   | Х                   | Х   | Х   |   |

| WRITE BYTE a    | L  | L   | Н                   | Н   | Н   |   |

| WRITE BYTE b    | L  | Н   | L                   | Н   | Н   |   |

| WRITE BYTE c    | L  | Н   | Н                   | L   | Н   |   |

| WRITE BYTE d    | L  | Н   | Н                   | Н   | L   |   |

| WRITE ALL BYTEs | L  | L   | L                   | Ĺ   | L   |   |

| WRITE ABORT/NOP | L  | Н   | Н                   | Н   | Н   | - |

#### Notes:

- 1. X means "Don't Care".

- 2. All inputs in this table must beet setup and hold time around the rising edge of CLK.

# INTERLEAVED BURST ADDRESS TABLE (MODE = VDD or NC)

| External Address<br>A1 A0 | 1st Burst Address<br>A1 A0 | 2nd Burst Address<br>A1 A0 | 3rd Burst Address<br>A1 A0 |

|---------------------------|----------------------------|----------------------------|----------------------------|

| 00                        | 01                         | 10                         | 11                         |

| 01                        | 00                         | 11                         | 10                         |

| 10                        | 11                         | 00                         | 01                         |

| 11                        | 10                         | 01                         | 00                         |

#### LINEAR BURST ADDRESS TABLE (MODE = Vss)

### **ABSOLUTE MAXIMUM RATINGS(1)**

| Symbol    | Parameter                                                  | NLP Value                      | NVP/NVVP Value     | Unit |

|-----------|------------------------------------------------------------|--------------------------------|--------------------|------|

| Тѕтс      | Storage Temperature                                        | -65 to +150                    | -65 to +150        | °C   |

| Po        | Power Dissipation                                          | 1.6                            | 1.6                | W    |

| Іоит      | Output Current (per I/O)                                   | 100                            | 100                | mA   |

| VIN, VOUT | Voltage Relative to Vss for I/O Pins                       | -0.5 to V <sub>DDQ</sub> + 0.3 | -0.5 to VDDQ + 0.3 | V    |

| VIN       | Voltage Relative to Vss for for Address and Control Inputs | -0.3 to V <sub>DD</sub> +0.5   | -0.3 to VDD+0.3    | V    |

#### Notes:

- Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

reliability.

- 2. This device contains circuity to protect the inputs against damage due to high static voltages or electric fields; however, precautions may be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

- 3. This device contains circuitry that will ensure the output devices are in High-Z at power up.

# **OPERATING RANGE (IS61NLPx)**

| Range      | Ambient Temperature | VDD       | <b>V</b> DDQ     |

|------------|---------------------|-----------|------------------|

| Commercial | 0°C to +70°C        | 3.3V ± 5% | 3.3V / 2.5V ± 5% |

| Industrial | -40°C to +85°C      | 3.3V ± 5% | 3.3V / 2.5V ± 5% |

#### **OPERATING RANGE (IS61NVPx)**

| Range      | <b>Ambient Temperature</b> | VDD       | <b>V</b> DDQ |  |

|------------|----------------------------|-----------|--------------|--|

| Commercial | 0°C to +70°C               | 2.5V ± 5% | 2.5V ± 5%    |  |

| Industrial | -40°C to +85°C             | 2.5V ± 5% | 2.5V ± 5%    |  |

#### OPERATING RANGE (IS61NVVPx)

| Range      | <b>Ambient Temperature</b> | <b>V</b> DD | <b>V</b> DDQ |  |

|------------|----------------------------|-------------|--------------|--|

| Commercial | 0°C to +70°C               | 1.8V ± 5%   | 1.8V ± 5%    |  |

| Industrial | -40°C to +85°C             | 1.8V ± 5%   | 1.8V ± 5%    |  |

## DC ELECTRICAL CHARACTERISTICS (Over Operating Range) 1, 2, 3

|             |                        |                                                              | 3    | 3.3V           | 2          | .5V            | 1.8                | V                     |      |

|-------------|------------------------|--------------------------------------------------------------|------|----------------|------------|----------------|--------------------|-----------------------|------|

| Symbol      | Parameter              | Test Conditions                                              | Min. | Max.           | Min.       | Max.           | Min.               | Max.                  | Unit |

| Vон         | Output HIGH Voltage    | loh = -4.0  mA  (3.3V)<br>loh = -1.0  mA  (2.5V, 1.8V)       | 2.4  | _              | 2.0        | _              | VDDQ - 0.4         | _                     | V    |

| Vol         | Output LOW Voltage     | IoL = 8.0 mA (3.3V)<br>IoL = 1.0 mA (2.5V, 1.8V)             | _    | 0.4            | _          | 0.4            | _                  | 0.4                   | V    |

| VIH         | Input HIGH Voltage     |                                                              | 2.0  | $V_{DD} + 0.3$ | 1.7        | $V_{DD} + 0.3$ | 0.6V <sub>DD</sub> | V <sub>DD</sub> + 0.3 | V    |

| VIL         | Input LOW Voltage      |                                                              | -0.3 | 8.0            | -0.3       | 0.7            | -0.3               | 0.3V <sub>DD</sub>    | ٧    |

| <b>I</b> LI | Input Leakage Current  | $V_{SS} \leq V_{IN} \leq V_{DD}{}^{(1)}$                     | -5   | 5              | -5         | 5              | <b>–</b> 5         | 5                     | μA   |

| ILO         | Output Leakage Current | $V_{SS} \leq V_{OUT} \leq V_{DDQ}, \ \overline{OE} = V_{IH}$ | -5   | 5              | <b>-</b> 5 | 5              | <b>–</b> 5         | 5                     | μΑ   |

#### Notes:

- 1. All voltages referenced to ground.

- 2. Overshoot:

- 3.3V and 2.5V: VIH (AC)  $\leq$  VDD + 1.5V (Pulse width less than tkc /2)

- 1.8V: ViH (AC)  $\leq$  VDD + 0.5V (Pulse width less than tkc /2)

- 3. Undershoot:

- 3.3V and 2.5V:  $V_{IL}$  (AC)  $\geq$  -1.5V (Pulse width less than tkc /2)

- 1.8V:  $V_{IL}$  (AC)  $\geq$  -0.5V (Pulse width less than tkc /2)

# POWER SUPPLY CHARACTERISTICS<sup>(1)</sup> (Over Operating Range)

|        |                                |                                                                                                                                                                               |              | _          | 50<br>AX   |            | 00<br>AX   | -          | 66<br>AX   | '    |

|--------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|------------|------------|------------|------------|------------|------|

| Symbol | Parameter                      | Test Conditions                                                                                                                                                               | Temp. range  | x18        | x36        | x18        | x36        | x18        | x36        | Unit |

| Icc    | AC Operating<br>Supply Current | Device Selected, $\overline{OE}$ = V <sub>IH</sub> ,<br>ZZ $\leq$ V <sub>IL</sub> , All Inputs $\leq$ 0.2V or<br>$\geq$ V <sub>DD</sub> - 0.2V, Cycle Time $\geq$<br>tkc min. | Com.<br>Ind. | 215<br>220 | 215<br>220 | 175<br>180 | 175<br>180 | 165<br>170 | 165<br>170 | mA   |

| Isb    | Standby Current<br>TTL Input   | Device Deselected, $V_{DD}$ = Max., All Inputs $\leq V_{IL}$ or $\geq V_{IH}$ , $ZZ \leq V_{IL}$ , $f$ = Max.                                                                 | Com.<br>Ind. | 65<br>70   | 65<br>70   | 65<br>70   | 65<br>70   | 65<br>70   | 65<br>70   | mA   |

| Isbi   | Standby Current<br>CMOS Input  | Device Deselected, $V_{DD}$ = Max., $V_{IN} \le V_{SS} + 0.2V$ or $\ge V_{DD} - 0.2V$ f = 0                                                                                   | Com.<br>Ind. | 50<br>55   | 50<br>55   | 50<br>55   | 50<br>55   | 50<br>55   | 50<br>55   | mA   |

#### Note:

<sup>1.</sup> MODE pin has an internal pullup and should be tied to V<sub>DD</sub> or V<sub>SS</sub>. It exhibits ±100μA maximum leakage current when tied to ≤ V<sub>SS</sub> + 0.2V or ≥ V<sub>DD</sub> − 0.2V.

# CAPACITANCE<sup>(1,2)</sup>

| Symbol | Parameter                | Conditions           | Max. | Unit |

|--------|--------------------------|----------------------|------|------|

| Cin    | Input Capacitance        | V <sub>IN</sub> = 0V | 6    | pF   |

| Соит   | Input/Output Capacitance | Vout = 0V            | 8    | pF   |

#### Notes:

- 1. Tested initially and after any design or process changes that may affect these parameters.

- 2. Test conditions:  $T_A = 25^{\circ}C$ , f = 1 MHz,  $V_{DD} = 3.3V$ .

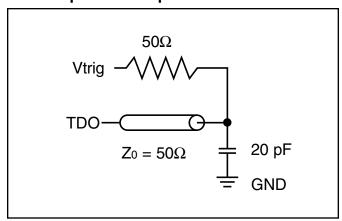

#### 3.3V I/O AC TEST CONDITIONS

| Parameter                                   | Unit                |

|---------------------------------------------|---------------------|

| Input Pulse Level                           | 0V to 3.0V          |

| Input Rise and Fall Times                   | 1.5 ns              |

| Input and Output Timing and Reference Level | 1.5V                |

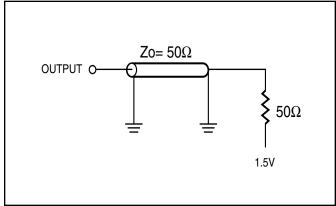

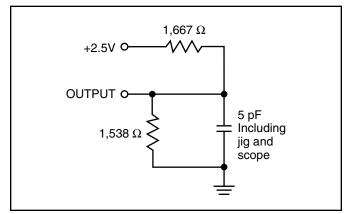

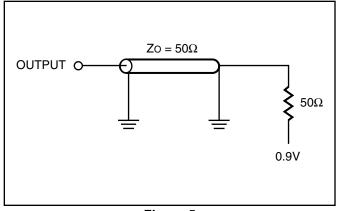

| Output Load                                 | See Figures 1 and 2 |

#### 3.3V I/O OUTPUT LOAD EQUIVALENT

Figure 1

Figure 2

### 2.5V I/O AC TEST CONDITIONS

| Parameter                                   | Unit                |

|---------------------------------------------|---------------------|

| Input Pulse Level                           | 0V to 2.5V          |

| Input Rise and Fall Times                   | 1.5 ns              |

| Input and Output Timing and Reference Level | 1.25V               |

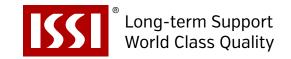

| Output Load                                 | See Figures 3 and 4 |

#### 2.5V I/O OUTPUT LOAD EQUIVALENT

Figure 3

Figure 4

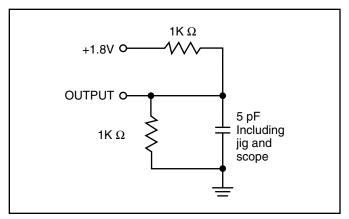

### 1.8V I/O AC TEST CONDITIONS

| Parameter                                   | Unit                |

|---------------------------------------------|---------------------|

| Input Pulse Level                           | 0V to 1.8V          |

| Input Rise and Fall Times                   | 1.5 ns              |

| Input and Output Timing and Reference Level | 0.9V                |

| Output Load                                 | See Figures 5 and 6 |

### 1.8V I/O OUTPUT LOAD EQUIVALENT

Figure 5

Figure 6

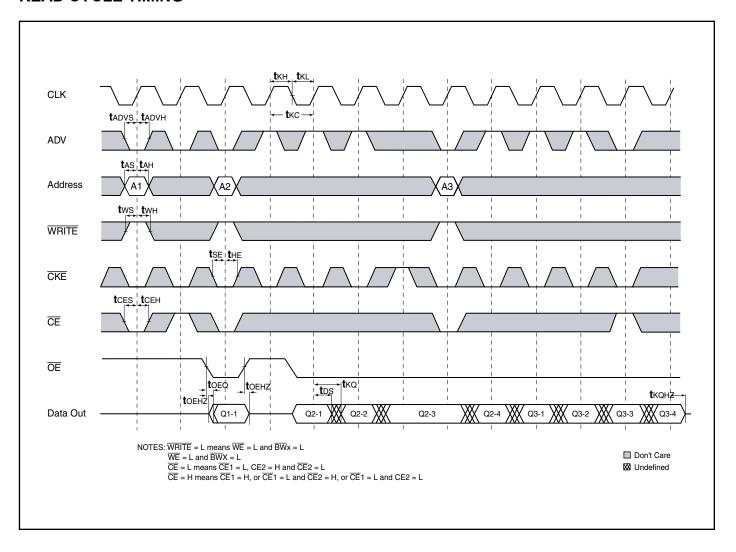

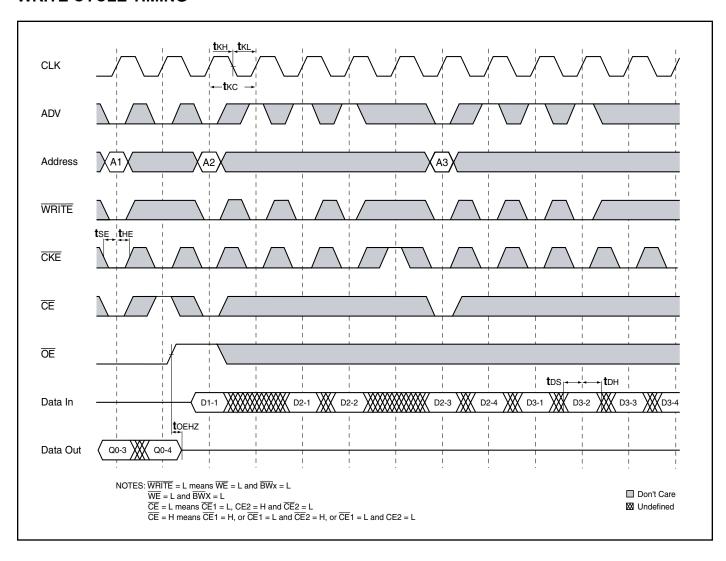

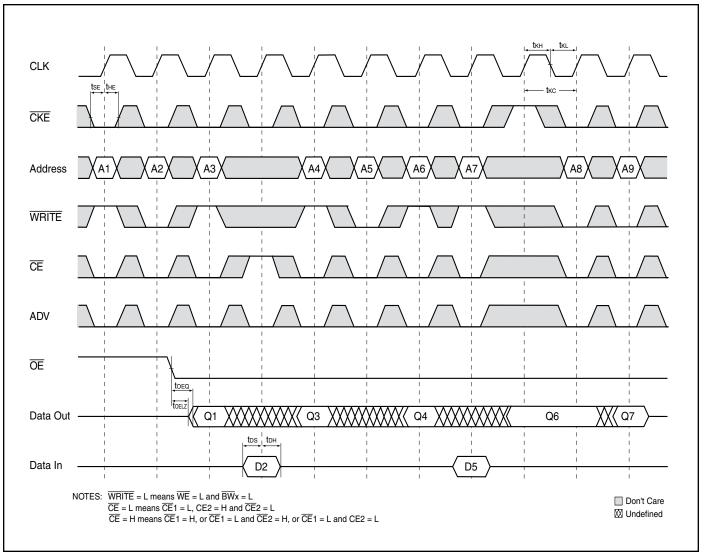

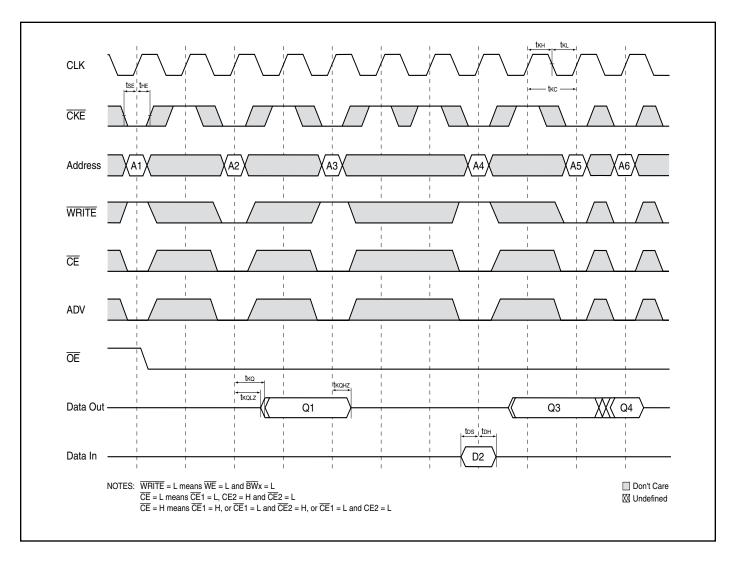

### READ/WRITE CYCLE SWITCHING CHARACTERISTICS(1) (Over Operating Range)

|                                |                                 | -25  | 50   | -200      | -166     |      |

|--------------------------------|---------------------------------|------|------|-----------|----------|------|

| Symbol                         | Parameter                       | Min. | Max. | Min. Max. | Min. Max | Unit |

| fmax                           | Clock Frequency                 | _    | 250  | — 200     | — 166    | MHz  |

| tкc                            | Cycle Time                      | 4.0  | _    | 5 —       | 6 —      | ns   |

| tкн                            | Clock High Time                 | 1.7  | _    | 2 —       | 2.4 —    | ns   |

| tĸL                            | Clock Low Time                  | 1.7  | _    | 2 —       | 2.4 —    | ns   |

| tkq                            | Clock Access Time               | _    | 2.6  | — 3.1     | — 3.5    | ns   |

| tkqx <sup>(2)</sup>            | Clock High to Output Invalid    | 0.8  | _    | 1.5 —     | 1.5 —    | ns   |

| tkQLZ <sup>(2,3)</sup>         | Clock High to Output Low-Z      | 0.8  | _    | 1 —       | 1.2 —    | ns   |

| <b>t</b> KQHZ <sup>(2,3)</sup> | Clock High to Output High-Z     | _    | 2.6  | — 3.1     | — 3.5    | ns   |

| toeq                           | Output Enable to Output Valid   | _    | 2.6  | — 3.1     | — 3.5    | ns   |

| toelz(2,3)                     | Output Enable to Output Low-Z   | 0    | _    | 0 —       | 0 —      | ns   |

| <b>t</b> OEHZ <sup>(2,3)</sup> | Output Disable to Output High-Z | _    | 2.6  | — 3.0     | — 3.5    | ns   |

| tas                            | Address Setup Time              | 1.2  | _    | 1.4 —     | 0 1.5    | ns   |

| tws                            | Read/Write Setup Time           | 1.2  | _    | 1.4 —     | 0 1.5    | ns   |

| tces                           | Chip Enable Setup Time          | 1.2  | _    | 1.4 —     | 0 1.5    | ns   |

| tse                            | Clock Enable Setup Time         | 1.2  | _    | 1.4 —     | 0 1.5    | ns   |

| tadvs                          | Address Advance Setup Time      | 1.2  | _    | 1.4 —     | 0 1.5    | ns   |

| tos                            | Data Setup Time                 | 1.2  | _    | 1.4 —     | 0 1.5    | ns   |

| <b>t</b> AH                    | Address Hold Time               | 0.3  | _    | 0.4 —     | 0.5 —    | ns   |

| the                            | Clock Enable Hold Time          | 0.3  | _    | 0.4 —     | 0.5 —    | ns   |

| twн                            | Write Hold Time                 | 0.3  | _    | 0.4 —     | 0.5 —    | ns   |

| <b>t</b> CEH                   | Chip Enable Hold Time           | 0.3  | _    | 0.4 —     | 0.5 —    | ns   |

| <b>t</b> advh                  | Address Advance Hold Time       | 0.3  | _    | 0.4 —     | 0.5 —    | ns   |

| <b>t</b> DH                    | Data Hold Time                  | 0.3  | _    | 0.4 —     | 0.5 —    | ns   |

| tpower <sup>(4)</sup>          | VDD (typical) to First Access   | 1    | _    | 1 —       | 1 —      | ms   |

#### Notes:

- 1. Configuration signal MODE is static and must not change during normal operation.

- 2. Guaranteed but not 100% tested. This parameter is periodically sampled.

- 3. Tested with load in Figure 2.

- 4. the time that the power needs to be supplied above VDD (min) initially before READ or WRITE operation can be initiated.

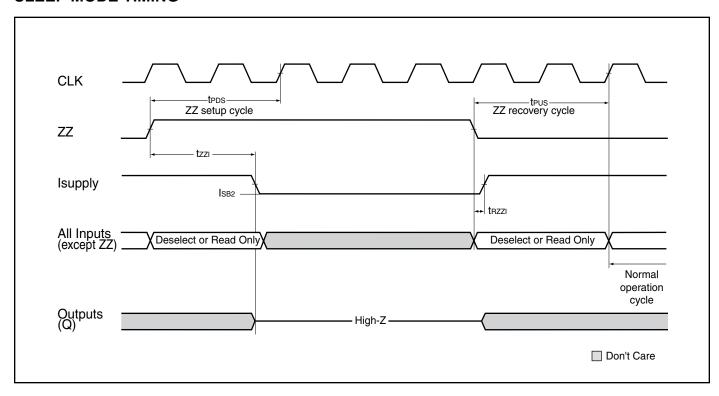

### **SNOOZE MODE ELECTRICAL CHARACTERISTICS**

| Symbol | Parameter                        | Conditions   | Temperature<br>Range | Min. | Max. | Unit  |

|--------|----------------------------------|--------------|----------------------|------|------|-------|

| ISB2   | Current during SNOOZE MODE       | $ZZ \ge Vih$ | Com.                 | _    | 20   | mA    |

|        |                                  |              | Ind.                 | _    | 25   |       |

| tpds   | ZZ active to input ignored       |              |                      | _    | 2    | cycle |

| tpus   | ZZ inactive to input sampled     |              |                      | 2    | _    | cycle |

| tzzı   | ZZ active to SNOOZE current      |              |                      | _    | 2    | cycle |

| trzzi  | ZZ inactive to exit SNOOZE curre | nt           |                      | 0    | _    | ns    |

#### **SLEEP MODE TIMING**

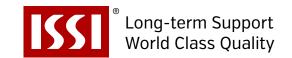

#### **READ CYCLE TIMING**

#### WRITE CYCLE TIMING

### SINGLE READ/WRITE CYCLE TIMING

### **CKE OPERATION TIMING**

# **CE OPERATION TIMING**

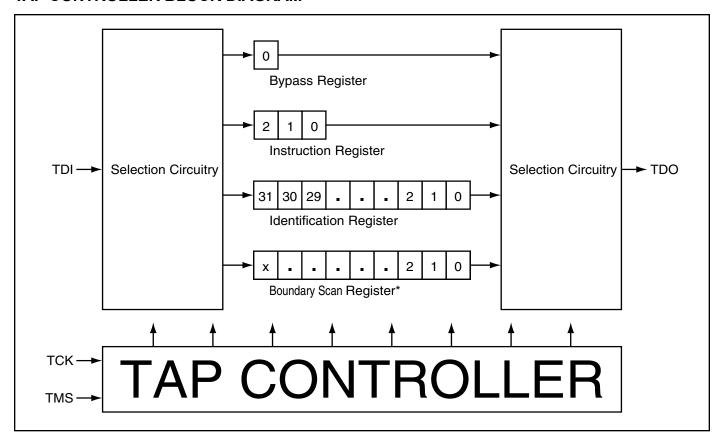

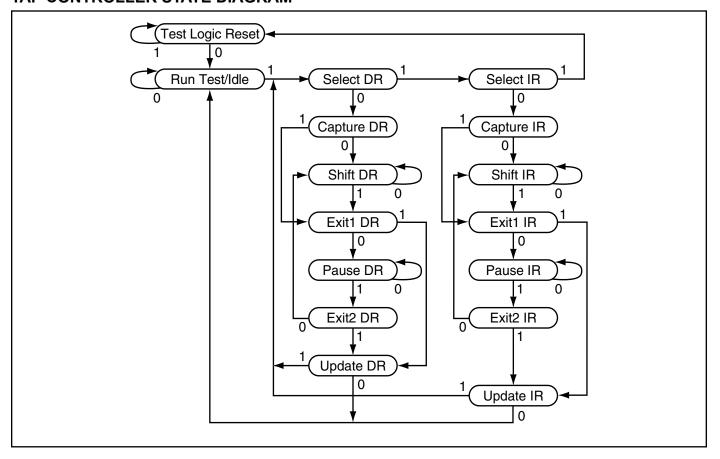

### **IEEE 1149.1 SERIAL BOUNDARY SCAN (JTAG)**

The serial boundary scan Test Access Port (TAP) is only available in the BGA package. (Not available in QFP package.) This port operates in accordance with IEEE Standard 1149.1-1900, but does not include all functions required for full 1149.1 compliance. These functions from the IEEE specification are excluded because they place added delay in the critical speed path of the SRAM. The TAP controller operates in a manner that does not conflict with the performance of other devices using 1149.1 fully compliant TAPs.

#### **DISABLING THE JTAG FEATURE**

The SRAM can operate without using the JTAG feature. To disable the TAP controller, TCK must be tied LOW (Vss) to prevent clocking of the device. TDI and TMS are internally pulled up and may be disconnected. They may alternately be connected to VDD through a pull-up resistor. TDO should be left disconnected. On power-up, the device will start in a reset state which will not interfere with the device operation.

#### **TEST ACCESS PORT (TAP) - TEST CLOCK**

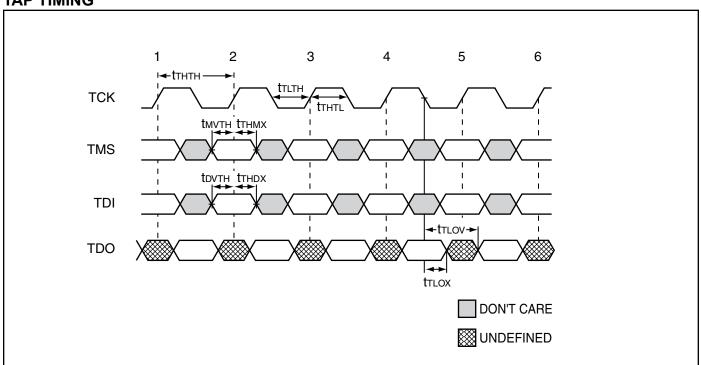

The test clock is only used with the TAP controller. All inputs are captured on the rising edge of TCK and outputs are driven from the falling edge of TCK.

### **TEST MODE SELECT (TMS)**

The TMS input is used to send commands to the TAP controller and is sampled on the rising edge of TCK. This pin may be left disconnected if the TAP is not used. The pin is internally pulled up, resulting in a logic HIGH level.

#### **TEST DATA-IN (TDI)**

The TDI pin is used to serially input information to the registers and can be connected to the input of any register. The register between TDI and TDO is chosen by the instruction loaded into the TAP instruction register. For information on instruction register loading, see the TAP Controller State Diagram. TDI is internally pulled up and can be disconnected if the TAP is unused in an application. TDI is connected to the Most Significant Bit (MSB) on any register.

#### TAP CONTROLLER BLOCK DIAGRAM

# **TEST DATA OUT (TDO)**

The TDO output pin is used to serially clock data-out from the registers. The output is active depending on the current state of the TAP state machine (see TAP Controller State Diagram). The output changes on the falling edge of TCK and TDO is connected to the Least Significant Bit (LSB) of any register.

#### **PERFORMING A TAP RESET**

A Reset is performed by forcing TMS HIGH (VDD) for five rising edges of TCK. RESET may be performed while the SRAM is operating and does not affect its operation. At power-up, the TAP is internally reset to ensure that TDO comes up in a high-Z state.

#### **TAP REGISTERS**

Registers are connected between the TDI and TDO pins and allow data to be scanned into and out of the SRAM test circuitry. Only one register can be selected at a time through the instruction registers. Data is serially loaded into the TDI pin on the rising edge of TCK and output on the TDO pin on the falling edge of TCK.

### Instruction Register

Three-bit instructions can be serially loaded into the instruction register. This register is loaded when it is placed between the TDI and TDO pins. (See TAP Controller Block Diagram) At power-up, the instruction register is loaded with the IDCODE instruction. It is also loaded with the IDCODE instruction if the controller is placed in a reset state as previously described.

When the TAP controller is in the CaptureIR state, the two least significant bits are loaded with a binary "01" pattern to allow for fault isolation of the board level serial test path.

# **Bypass Register**

To save time when serially shifting data through registers, it is sometimes advantageous to skip certain states. The bypass register is a single-bit register that can be placed between TDI and TDO pins. This allows data to be shifted through the SRAM with minimal delay. The bypass reg-

ister is set LOW (Vss) when the BYPASS instruction is executed.

# **Boundary Scan Register**

The boundary scan register is connected to all input and output pins on the SRAM. Several no connect (NC) pins are also included in the scan register to reserve pins for higher density devices. The x36 configuration has a 75-bit-long register and the x18 configuration also has a 75-bit-long register. The boundary scan register is loaded with the contents of the RAM Input and Output ring when the TAP controller is in the Capture-DR state and then placed between the TDI and TDO pins when the controller is moved to the Shift-DR state. The EXTEST, SAMPLE/PRELOAD and SAMPLE-Z instructions can be used to capture the contents of the Input and Output ring.

The Boundary Scan Order tables show the order in which the bits are connected. Each bit corresponds to one of the bumps on the SRAM package. The MSB of the register is connected to TDI, and the LSB is connected to TDO.

### Scan Register Sizes

| Register      | Bit Size | Bit Size |  |

|---------------|----------|----------|--|

| Name          | (x18)    | (x36)    |  |

| Instruction   | 3        | 3        |  |

| Bypass        | 1        | 1        |  |

| ID            | 32       | 32       |  |

| Boundary Scan | 90       | 90       |  |

#### Identification (ID) Register

The ID register is loaded with a vendor-specific, 32-bit code during the Capture-DR state when the IDCODE command is loaded to the instruction register. The IDCODE is hardwired into the SRAM and can be shifted out when the TAP controller is in the Shift-DR state. The ID register has vendor code and other information described in the Identification Register Definitions table.

#### **IDENTIFICATION REGISTER DEFINITIONS**

| Instruction Field        | Description                                  | 256K x 36   | 512K x 18   |

|--------------------------|----------------------------------------------|-------------|-------------|

| Revision Number (31:28)  | Reserved for version number.                 | XXXX        | xxxx        |

| Device Depth (27:23)     | Defines depth of SRAM. 256K or 512K          | 00111       | 01000       |

| Device Width (22:18)     | Defines width of the SRAM. x36 or x18        | 00100       | 00011       |

| ISSI Device ID (17:12)   | Reserved for future use.                     | XXXXX       | XXXXX       |

| ISSI JEDEC ID (11:1)     | Allows unique identification of SRAM vendor. | 00001010101 | 00001010101 |

| ID Register Presence (0) | Indicate the presence of an ID register.     | 1           | 1           |

#### TAP INSTRUCTION SET

Eight instructions are possible with the three-bit instruction register and all combinations are listed in the Instruction Code table. Three instructions are listed as RESERVED and should not be used and the other five instructions are described below. The TAP controller used in this SRAM is not fully compliant with the 1149.1 convention because some mandatory instructions are not fully implemented. The TAP controller cannot be used to load address, data or control signals and cannot preload the Input or Output buffers. The SRAM does not implement the 1149.1 commands EXTEST or INTEST or the PRELOAD portion of SAMPLE/ PRELOAD; instead it performs a capture of the Inputs and Output ring when these instructions are executed. Instructions are loaded into the TAP controller during the Shift-IR state when the instruction register is placed between TDI and TDO. During this state, instructions are shifted from the instruction register through the TDI and TDO pins. To execute an instruction once it is shifted in, the TAP controller must be moved into the Update-IR state.

#### **EXTEST**

EXTEST is a mandatory 1149.1 instruction which is to be executed whenever the instruction register is loaded with all 0s. Because EXTEST is not implemented in the TAP controller, this device is not 1149.1 standard compliant. The TAP controller recognizes an all-0 instruction. When an EXTEST instruction is loaded into the instruction register, the SRAM responds as if a SAMPLE/PRELOAD instruction has been loaded. There is a difference between the instructions, unlike the SAMPLE/PRELOAD instruction, EXTEST places the SRAM outputs in a High-Z state.

#### **IDCODE**

The IDCODE instruction causes a vendor-specific, 32-bit code to be loaded into the instruction register. It also places the instruction register between the TDI and TDO pins and allows the IDCODE to be shifted out of the device when the TAP controller enters the Shift-DR state. The IDCODE instruction is loaded into the instruction register upon power-up or whenever the TAP controller is given a test logic reset state.

#### SAMPLE-Z

The SAMPLE-Z instruction causes the boundary scan register to be connected between the TDI and TDO pins when the TAP controller is in a Shift-DR state. It also places all SRAM outputs into a High-Z state.

#### SAMPLE/PRELOAD

SAMPLE/PRELOAD is a 1149.1 mandatory instruction. The PRELOAD portion of this instruction is not implemented, so the TAP controller is not fully 1149.1 compliant. When the SAMPLE/PRELOAD instruction is loaded to the instruction register and the TAP controller is in the Capture-DR state, a snapshot of data on the inputs and output pins is captured in the boundary scan register.

It is important to realize that the TAP controller clock operates at a frequency up to 10 MHz, while the SRAM clock runs more than an order of magnitude faster. Because of the clock frequency differences, it is possible that during the Capture-DR state, an input or output will under-go a transition. The TAP may attempt a signal capture while in transition (metastable state). The device will not be harmed, but there is no guarantee of the value that will be captured or repeatable results.

To guarantee that the boundary scan register will capture the correct signal value, the SRAM signal must be stabilized long enough to meet the TAP controller's capture set-up plus hold times (tcs and tch). To insure that the SRAM clock input is captured correctly, designs need a way to stop (or slow) the clock during a SAMPLE/PRELOAD instruction. If this is not an issue, it is possible to capture all other signals and simply ignore the value of the CLK captured in the boundary scan register.

Once the data is captured, it is possible to shift out the data by putting the TAP into the Shift-DR state. This places the boundary scan register between the TDI and TDO pins.

Note that since the PRELOAD part of the command is not implemented, putting the TAP into the Update to the Update-DR state while performing a SAMPLE/PRELOAD instruction will have the same effect as the Pause-DR command.

#### **BYPASS**

When the BYPASS instruction is loaded in the instruction register and the TAP is placed in a Shift-DR state, the bypass register is placed between the TDI and TDO pins. The advantage of the BYPASS instruction is that it shortens the boundary scan path when multiple devices are connected together on a board.

#### **RESERVED**

These instructions are not implemented but are reserved for future use. Do not use these instructions.

# **INSTRUCTION CODES**

| Code | Instruction    | Description                                                                                                                                                                                                                            |

|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000  | EXTEST         | Captures the Input/Output ring contents. Places the boundary scan register between the TDI and TDO. Forces all SRAM outputs to High-Z state. This instruction is not 1149.1 compliant.                                                 |

| 001  | IDCODE         | Loads the ID register with the vendor ID code and places the register between TDI and TDO. This operation does not affect SRAM operation.                                                                                              |

| 010  | SAMPLE-Z       | Captures the Input/Output contents. Places the boundary scan register between TDI and TDO. Forces all SRAM output drivers to a High-Z state.                                                                                           |

| 011  | RESERVED       | Do Not Use: This instruction is reserved for future use.                                                                                                                                                                               |

| 100  | SAMPLE/PRELOAD | Captures the Input/Output ring contents. Places the boundary scan register between TDI and TDO. Does not affect the SRAM operation. This instruction does not implement 1149.1 preload function and is therefore not 1149.1 compliant. |

| 101  | RESERVED       | Do Not Use: This instruction is reserved for future use.                                                                                                                                                                               |

| 110  | RESERVED       | Do Not Use: This instruction is reserved for future use.                                                                                                                                                                               |

| 111  | BYPASS         | Places the bypass register between TDI and TDO. This operation does not affect SRAM operation.                                                                                                                                         |

#### TAP CONTROLLER STATE DIAGRAM

**TAP Electrical Characteristics** (2.5V and 3.3V operating range)

| Symbol           | Parameter             | Test Conditions                | Min. | Max.                 | Units |

|------------------|-----------------------|--------------------------------|------|----------------------|-------|

| Voн1             | Output HIGH Voltage   | Iон = −2.0 mA                  | 1.7  | _                    | V     |

| V <sub>OH2</sub> | Output HIGH Voltage   | Іон = −100 µА                  | 2.1  | _                    | V     |

| V <sub>OL1</sub> | Output LOW Voltage    | IoL = 2.0 mA                   | _    | 0.7                  | V     |

| Vol2             | Output LOW Voltage    | IoL = 100 μA                   | _    | 0.2                  | V     |

| VIH              | Input HIGH Voltage    |                                | 1.7  | V <sub>DD</sub> +0.3 | V     |

| VIL              | Input LOW Voltage     |                                | -0.3 | 0.7                  | V     |

| lx               | Input Leakage Current | $Vss \leq V \; I \leq V_{DDQ}$ | -10  | 10                   | μA    |

**TAP Electrical Characteristics** (1.8V operating range)

| Symbol | Parameter             | Test Conditions                  | Min.                 | Max.                 | Units |

|--------|-----------------------|----------------------------------|----------------------|----------------------|-------|

| Voн1   | Output HIGH Voltage   | Iон <b>=</b> −2.0 mA             | V <sub>DD</sub> -0.4 | _                    | V     |

| Vol1   | Output LOW Voltage    | IoL = 2.0 mA                     | -0.3                 | 0.5                  | V     |

| VIH    | Input HIGH Voltage    |                                  | 1.3                  | V <sub>DD</sub> +0.3 | V     |

| VIL    | Input LOW Voltage     |                                  | -0.3                 | 0.7                  | V     |

| lx     | Input Leakage Current | $Vss \leq V \mid I \leq V_{DDQ}$ | -10                  | 10                   | μA    |

# TAP AC ELECTRICAL CHARACTERISTICS (OVER OPERATING RANGE)

| Parameter             | Symbol        | Min | Max | Units |

|-----------------------|---------------|-----|-----|-------|

| TCK cycle time        | <u>т</u> тнтн | 100 | _   | ns    |

| TCK high pulse width  | tтнть         | 40  | _   | ns    |

| TCK low pulse width   | tтштн         | 40  | _   | ns    |

| TMS Setup             | tмvтн         | 10  | _   | ns    |

| TMS Hold              | tтнмх         | 10  | _   | ns    |

| TDI Setup             | <b>t</b> DVTH | 10  | _   | ns    |

| TDI Hold              | tthdx         | 10  | _   | ns    |

| TCK Low to Valid Data | <b>t</b> TLOV | _   | 20  | ns    |

### **TAP TEST CONDITIONS**

| (1.8V/2.5V/3.3V) Input pulse levels  | 0 to 1.8V/0 to 2.5V/0 to 3.0V |

|--------------------------------------|-------------------------------|

| Input rise and fall times            | 1.5ns                         |

| Input timing reference levels        | 0.9V/1.25V/1.5V               |

| Output reference levels              | 0.9V/1.25V/1.5V               |

| Test load termination supply voltage | 0.9V/1.25V/1.5V               |

| Vtrig                                | 0.9V/1.25V/1.5V               |

# **TAP Output Load Equivalent**

### **TAP TIMING**

119 BGA BOUNDARY SCAN ORDER

# **TBD**

### **165 BGA BOUNDARY SCAN ORDER**

|       | 165 BGA |        |         |        |  |

|-------|---------|--------|---------|--------|--|

|       | X36     |        | X18     |        |  |

| Bit # | Bump ID | Signal | Bump ID | Signal |  |

| 1     | N6      | NC     | N6      | NC     |  |

| 2     | N7      | NC     | N7      | NC     |  |

| 3     | N10     | NC     | N10     | NC     |  |

| 4     | P11     | NC     | P11     | NC     |  |

| 5     | P8      | A17    | P8      | A17    |  |

| 6     | R8      | A16    | R8      | A16    |  |

| 7     | R9      | A15    | R9      | A15    |  |

| 8     | P9      | A14    | P9      | A14    |  |

| 9     | P10     | A13    | P10     | A13    |  |

| 10    | R10     | A12    | R10     | A12    |  |

| 11    | R11     | A11    | R11     | A11    |  |

| 12    | H11     | ZZ     | H11     | ZZ     |  |

| 13    | N11     | DQa0   | N11     | NC     |  |

| 14    | M11     | DQa1   | M11     | NC     |  |

| 15    | L11     | DQa2   | L11     | NC     |  |

| 16    | M10     | DQa3   | M10     | NC     |  |

| 17    | L10     | DQa4   | L10     | NC     |  |

| 18    | K11     | DQa5   | K11     | DQa8   |  |

| 19    | J11     | DQa6   | J11     | DQa7   |  |

| 20    | K10     | DQa7   | K10     | DQa6   |  |

| 21    | J10     | DQa8   | J10     | DQa5   |  |

| 22    | H9      | NC     | H9      | NC     |  |

| 23    | H10     | NC     | H10     | NC     |  |

| 24    | G11     | DQb8   | G11     | DQa4   |  |

| 25    | F11     | DQb7   | F11     | DQa3   |  |

| 26    | G10     | DQb6   | G10     | DQa2   |  |

| 27    | E11     | DQb5   | E11     | DQa1   |  |

| 28    | D11     | DQb4   | D11     | DQa0   |  |

| 29    | F10     | DQb3   | C11     | NC     |  |

| 30    | E10     | DQb2   | E10     | NC     |  |

| 31    | D10     | DQb1   | D10     | NC     |  |

| 32    | C11     | DQb0   | F10     | NC     |  |

| 33    | A11     | NC     | A11     | A18    |  |

| 34    | B11     | NC     | B11     | NC     |  |

| 35    | A10     | A10    | A10     | A10    |  |

| 36    | B10     | A9     | B10     | A9     |  |

| 37    | A9      | A8     | A9      | A8     |  |

| 38    | B9      | NC     | B9      | NC     |  |

| 39    | C10     | NC     | C10     | NC     |  |

| 40    | A8      | ADV    | A8      | ADV    |  |

|       | 165 BGA |        |         |        |  |

|-------|---------|--------|---------|--------|--|

|       | X36     |        | X18     |        |  |

| Bit # | Bump ID | Signal | Bump ID | Signal |  |

| 41    | B8      | /OE    | B8      | /OE    |  |

| 42    | A7      | /CKE   | A7      | /CKE   |  |

| 43    | B7      | /WE    | В7      | /WE    |  |

| 44    | B6      | CLK    | B6      | CLK    |  |

| 45    | A6      | /CE2   | A6      | /CE2   |  |

| 46    | B5      | /Bwa   | B5      | /Bwa   |  |

| 47    | A5      | /Bwb   | A5      | NC     |  |

| 48    | A4      | /Bwc   | A4      | /Bwb   |  |

| 49    | B4      | /Bwd   | B4      | NC     |  |

| 50    | В3      | CE2    | В3      | CE2    |  |

| 51    | А3      | /CE1   | А3      | /CE1   |  |

| 52    | A2      | A7     | A2      | A7     |  |

| 53    | B2      | A6     | B2      | A6     |  |

| 54    | C2      | NC     | C2      | NC     |  |

| 55    | B1      | NC     | B1      | NC     |  |

| 56    | A1      | NC     | A1      | NC     |  |

| 57    | C1      | DQc0   | C1      | NC     |  |

| 58    | D1      | DQc1   | D1      | NC     |  |

| 59    | E1      | DQc2   | E1      | NC     |  |

| 60    | D2      | DQc3   | D2      | NC     |  |

| 61    | E2      | DQc4   | E2      | NC     |  |

| 62    | F1      | DQc5   | F1      | DQb8   |  |

| 63    | G1      | DQc6   | G1      | DQb7   |  |

| 64    | F2      | DQc7   | F2      | DQb6   |  |

| 65    | G2      | DQc8   | G2      | DQb5   |  |

| 66    | H1      | NC     | H1      | NC     |  |

| 67    | H2      | NC     | H2      | NC     |  |

| 68    | НЗ      | NC     | НЗ      | NC     |  |

| 69    | J1      | DQd8   | J1      | DQb4   |  |

| 70    | K1      | DQd7   | K1      | DQb3   |  |

| 71    | J2      | DQd6   | J2      | DQb2   |  |

| 72    | L1      | DQd5   | L1      | DQb1   |  |

| 73    | M1      | DQd4   | M1      | DQb0   |  |

| 74    | K2      | DQd3   | M1      | NC     |  |

| 75    | L2      | DQd2   | L2      | NC     |  |

| 76    | M2      | DQd1   | M2      | NC     |  |

| 77    | N1      | DQd0   | K2      | NC     |  |

| 78    | N2      | NC     | N2      | NC     |  |

| 79    | P1      | NC     | P1      | NC     |  |

| 80    | R1      | MODE   | R1      | MODE   |  |

Continued on next page

| 165 BGA |         |        |         |        |

|---------|---------|--------|---------|--------|

|         | X3      | 86     | X18     |        |

| Bit #   | Bump ID | Signal | Bump ID | Signal |

| 81      | R2      | NC     | R2      | NC     |

| 82      | P3      | A5     | P3      | A5     |

| 83      | R3      | A4     | R3      | A4     |

| 84      | P2      | NC     | P2      | NC     |

| 85      | P4      | A2     | P4      | A2     |

| 86      | R4      | A3     | R4      | A3     |

| 87      | N5      | NC     | N5      | NC     |

| 88      | P6      | A1     | P6      | A1     |

| 89      | R6      | AD     | R6      | AD     |

| 90      | *       | Int    | *       | Int    |

# ORDERING INFORMATION (VDD = 3.3V/VDDQ = 2.5V/3.3V)

Commercial Range: 0°C to +70°C

| Access Time | Order Part Number                                                                          | Package                                                        |

|-------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|             | 256Kx36                                                                                    |                                                                |

| 250         | IS61NLP25636B-250TQL                                                                       | 100 QFP, Lead-free                                             |

|             | IS61NLP25636BHD-250TQL(1)                                                                  | 100 QFP, Lead-free                                             |

|             | IS61NLP25636B-250B3<br>IS61NLP25636B-250B2                                                 | 165 BGA<br>119 BGA                                             |

| 200         | IS61NLP25636B-200TQL                                                                       | 100 QFP, Lead-free                                             |

|             | IS61NLP25636B-200B3<br>IS61NLP25636B-200B3L<br>IS61NLP25636B-200B2<br>IS61NLP25636B-200B2L | 165 BGA<br>165 BGA, Lead-free<br>119 BGA<br>119 BGA, Lead-free |

|             | 512Kx18                                                                                    |                                                                |

| 250         | IS61NLP51218B-250TQL                                                                       | 100 QFP, Lead-free                                             |

|             | IS61NLP51218B-250B3<br>IS61NLP51218B-250B2                                                 | 165 BGA<br>119 BGA                                             |

| 200         | IS61NLP51218B-200TQL                                                                       | 100 QFP, Lead-free                                             |

|             | IS61NLP51218B-200B3<br>IS61NLP51218B-200B2                                                 | 165 BGA<br>119 BGA                                             |

Note:

<sup>1.</sup> High driver strength

# ORDERING INFORMATION (VDD = 3.3V/VDDQ = 2.5V/3.3V)

Industrial Range: -40°C to +85°C

| Access Time | Order Part Number                                                                              | Package                                                        |

|-------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|             | 256Kx36                                                                                        |                                                                |

| 250         | IS61NLP25636B-250TQLI                                                                          | 100 QFP, Lead-free                                             |

|             | IS61NLP25636B-250B3I<br>IS61NLP25636B-250B2I                                                   | 165 BGA<br>119 BGA                                             |

| 200         | IS61NLP25636B-200TQLI                                                                          | 100 QFP, Lead-free                                             |

|             | IS61NLP25636B-200B3I<br>IS61NLP25636B-200B3LI<br>IS61NLP25636B-200B2I<br>IS61NLP25636B-200B2LI | 165 BGA<br>165 BGA, Lead-free<br>119 BGA<br>119 BGA, Lead-free |

|             | 512Kx18                                                                                        |                                                                |

| 250         | IS61NLP51218B-250TQLI                                                                          | 100 QFP, Lead-free                                             |

|             | IS61NLP51218B-250B3I<br>IS61NLP51218B-250B2I                                                   | 165 BGA<br>119 BGA                                             |

| 200         | IS61NLP51218B-200TQLI                                                                          | 100 QFP, Lead-free                                             |

|             | IS61NLP51218B-200B3I<br>IS61NLP51218B-200B2I                                                   | 165 BGA<br>119 BGA                                             |

# ORDERING INFORMATION (VDD = 2.5V/VDDQ = 2.5V)

Industrial Range: -40°C to +85°C

| Access Time | Order Part Number     | Package            |  |  |  |  |

|-------------|-----------------------|--------------------|--|--|--|--|

|             | 256Kx36               |                    |  |  |  |  |

| 250         | IS61NVP25636B-250TQLI | 100 QFP, Lead-free |  |  |  |  |

|             | IS61NVP25636B-250B3I  | 165 BGA            |  |  |  |  |

|             | IS61NVP25636B-250B2I  | 119 BGA            |  |  |  |  |

| 200         | IS61NVP25636B-200TQLI | 100 QFP, Lead-free |  |  |  |  |

|             | IS61NVP25636B-200B3I  | 165 BGA            |  |  |  |  |

|             | IS61NVP25636B-200B2I  | 119 BGA            |  |  |  |  |

|             | 512Kx18               |                    |  |  |  |  |

| 250         | IS61NVP51218B-250TQLI | 100 QFP, Lead-free |  |  |  |  |

|             | IS61NVP51218B-250B3I  | 165 BGA            |  |  |  |  |

|             | IS61NVP51218B-250B2I  | 119 BGA            |  |  |  |  |

| 200         | IS61NVP51218B-200TQLI | 100 QFP, Lead-free |  |  |  |  |

|             | IS61NVP51218B-200B3I  | 165 BGA            |  |  |  |  |

|             | IS61NVP51218B-200B2I  | 119 BGA            |  |  |  |  |

# ORDERING INFORMATION (VDD = 1.8V/VDDQ = 1.8V)

Please contact SRAM Marketing at sram@issi.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for SRAM category:

Click to view products by ISSI manufacturer:

Other Similar products are found below:

5962-8855206XA CY6116A-35DMB CY7C128A-45DMB CY7C1461KV33-133AXI CY7C199-45LMB CYDM128B16-55BVXIT

GS8161Z36DD-200I GS88237CB-200I R1QDA7236ABB-20IB0 RMLV0408EGSB-4S2#AA0 IS64WV3216BLL-15CTLA3

IS66WVE4M16ECLL-70BLI PCF8570P K6T4008C1B-GB70 CY7C1353S-100AXC AS6C8016-55BIN 515712X IS62WV51216EBLL45BLI IS63WV1288DBLL-10HLI IS66WVE2M16ECLL-70BLI 47L16-E/SN IS66WVE4M16EALL-70BLI IS62WV6416DBLL-45BLI

IS61WV102416DBLL-10TLI CY7C1381KV33-100AXC CY7C1381KV33-100BZXI CY7C1373KV33-100AXC CY7C1381KVE33-133AXI

CY7C4042KV13-933FCXC 8602501XA 5962-3829425MUA 5962-8855206YA 5962-8866201XA 5962-8866201YA 5962-8866204TA

5962-8866206MA 5962-8866207NA 5962-8866208UA 5962-8872502XA 5962-8959836MZA 5962-8959841MZA 5962-9062007MXA

5962-9161705MXA N08L63W2AB7I 7130LA100PDG GS81284Z36B-250I M38510/28902BVA IS62WV12816ALL-70BLI 59628971203XA 5962-8971202ZA