# IS62C25616BL, IS65C25616BL

# 256K x 16 HIGH-SPEED CMOS STATIC RAM

#### **MARCH 2013**

#### **FEATURES**

· High-speed access time: 45 ns

• Low Active Power: 50 mW (typical)

Low Standby Power: 10 μW (typical)

CMOS standby

· TTL compatible interface levels

Single 5V ± 10% power supply

Fully static operation: no clock or refresh required

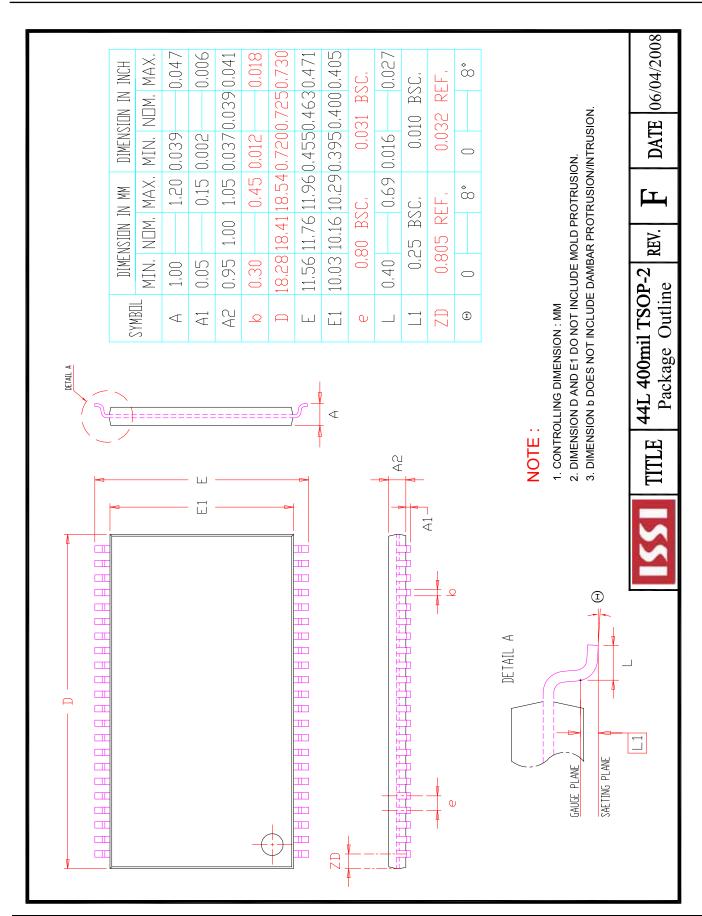

• Package: 44-pin TSOP (Type II)

Commercial, Industrial and Automotive temperature ranges available

Lead-free available

#### **DESCRIPTION**

The *ISSI* IS62C25616BL and IS65C25616BL are high-speed, 4,194,304-bit static RAMs organized as 262,144 words by 16 bits. They are fabricated using *ISSI*'s high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields access times as fast as 12 ns with low power consumption.

When  $\overline{\text{CE}}$  is HIGH (deselected), the device assumes a standby mode at which the power dissipation can be reduced down with CMOS input levels.

Easy memory expansion is provided by using Chip Enable and Output Enable inputs,  $\overline{CE}$  and  $\overline{OE}$ . The active LOW Write Enable ( $\overline{WE}$ ) controls both writing and reading of the memory. A data byte allows Upper Byte ( $\overline{UB}$ ) and Lower Byte ( $\overline{LB}$ ) access.

The IS62C25616BL and IS65C25616BL are packaged in the JEDEC standard 44-pin TSOP (Type II).

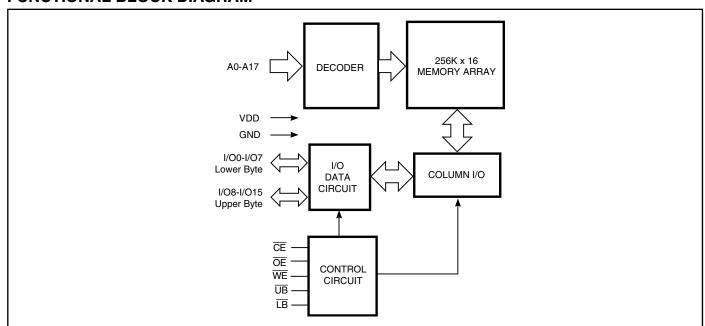

#### **FUNCTIONAL BLOCK DIAGRAM**

Copyright © 2013 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

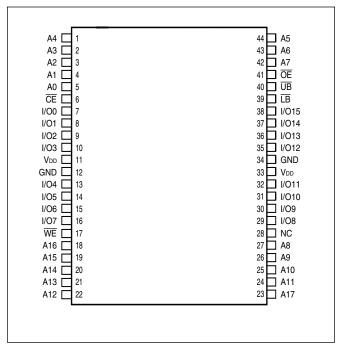

# PIN CONFIGURATIONS\* 44-Pin TSOP (Type II)

<sup>\*</sup>Please contact ISSI at SRAM@issi.com for availability of 48-pin BGA and 44-pin SOJ packages.

## **PIN DESCRIPTIONS**

| A0-A17     | Address Inputs      |

|------------|---------------------|

| I/O0-I/O15 | Data Inputs/Outputs |

| CE         | Chip Enable Input   |

| ŌĒ         | Output Enable Input |

| WE         | Write Enable Input  |

| ĪΒ  | Lower-byte Control (I/O0-I/O7)  |

|-----|---------------------------------|

| ŪB  | Upper-byte Control (I/O8-I/O15) |

| NC  | No Connection                   |

| VDD | Power                           |

| GND | Ground                          |

# IS62C25616BL, IS65C25616BL

## **TRUTH TABLE**

|                 |    |    |    |    | I/O PIN |              |              |             |  |

|-----------------|----|----|----|----|---------|--------------|--------------|-------------|--|

| Mode            | WE | CE | ŌĒ | ΙΒ | ŪB      | 1/00-1/07    | I/O8-I/O15   | VDD Current |  |

| Not Selected    | Х  | Н  | Х  | Х  | Х       | High-Z       | High-Z       | ISB1, ISB2  |  |

| Output Disabled | Н  | L  | Н  | Χ  | Χ       | High-Z       | High-Z       | Icc1, Icc2  |  |

|                 | Χ  | L  | Χ  | Н  | Н       | High-Z       | High-Z       |             |  |

| Read            | Н  | L  | L  | L  | Н       | <b>D</b> оит | High-Z       | Icc1, Icc2  |  |

|                 | Н  | L  | L  | Н  | L       | High-Z       | Dout         |             |  |

|                 | Н  | L  | L  | L  | L       | <b>D</b> оит | <b>D</b> out |             |  |

| Write           | L  | L  | Χ  | L  | Н       | Din          | High-Z       | Icc1, Icc2  |  |

|                 | L  | L  | Χ  | Н  | L       | High-Z       | DIN          |             |  |

|                 | L  | L  | Χ  | L  | L       | Din          | DIN          |             |  |

#### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Parameter                            | Value        | Unit |  |

|--------|--------------------------------------|--------------|------|--|

| VTERM  | Terminal Voltage with Respect to GND | -0.5 to +7.0 | V    |  |

| Тѕтс   | Storage Temperature                  | -65 to +150  | °C   |  |

| Рт     | Power Dissipation                    | 1.5          | W    |  |

| Іоит   | DC Output Current (LOW)              | 20           | mA   |  |

#### Notes:

## CAPACITANCE(1,2)

| Symbol | Parameter          | Conditions | Max. | Unit |

|--------|--------------------|------------|------|------|

| Cin    | Input Capacitance  | VIN = 0V   | 6    | pF   |

| Соит   | Output Capacitance | Vout = 0V  | 8    | pF   |

#### Notes:

1. Tested initially and after any design or process changes that may affect these parameters.

2. Test conditions:  $T_A = 25^{\circ}C$ , f = 1 MHz,  $V_{DD} = 5.0V$ .

## DC ELECTRICAL CHARACTERISTICS (Over Operating Range)

| Symbol | Parameter             | Test Conditions                           |       | Min.       | Max.      | Unit |

|--------|-----------------------|-------------------------------------------|-------|------------|-----------|------|

| Vон    | Output HIGH Voltage   | $V_{DD} = Min., I_{OH} = -1.0 \text{ mA}$ |       | 2.4        | _         | V    |

| Vol    | Output LOW Voltage    | VDD = Min., IOL = 2.1 mA                  |       |            | 0.4       | V    |

| VIH    | Input HIGH Voltage(1) |                                           |       | 2.2        | VDD + 0.5 | V    |

| VIL    | Input LOW Voltage(1)  |                                           |       | -0.3       | 0.8       | V    |

| ILI    | Input Leakage         | $GND \leq Vin \leq Vdd$                   | Com.  | -1         | 1         | μA   |

|        |                       |                                           | Ind.  | -2         | 2         |      |

|        |                       |                                           | Auto. | <b>–</b> 5 | 5         |      |

| ILO    | Output Leakage        | $GND \leq VOUT \leq VDD$                  | Com.  | -1         | 1         | μA   |

|        |                       | Outputs Disabled                          | Ind.  | -2         | 2         |      |

|        |                       | •                                         | Auto. | <b>–</b> 5 | 5         |      |

#### Note:

1. VILL (min) = -2.0V AC (pulse width <10 ns). Not 100% tested. VIHH (max) = VDD + 2.0V AC (pulse width <10 ns). Not 100% tested.

Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the

device. This is a stress rating only and functional operation of the device at these or any other conditions above

those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

## **OPERATING RANGE**

| Range      | Ambient Temperature | <b>V</b> DD | Speed (ns) |  |

|------------|---------------------|-------------|------------|--|

| Commercial | 0°C to +70°C        | 5V ± 10%    | 45         |  |

| Industrial | -40°C to +85°C      | 5V ± 10%    | 45         |  |

| Automotive | -40°C to +125°C     | 5V ± 10%    | 45         |  |

# POWER SUPPLY CHARACTERISTICS<sup>(1)</sup> (Over Operating Range)

| Symbo | l Parameter                             | Test Conditions                                                                                                                                                        |                                              | -45<br>Min. | ins<br>Max.         | Unit |  |

|-------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------|---------------------|------|--|

| Icc   | Average operating                       | CE = VIL,                                                                                                                                                              | Com.                                         | _           | 10                  | mA   |  |

|       | Current                                 | $V_{DD} = Max.,$ $I_{OUT} = 0 \text{ mA, } f = 0$                                                                                                                      | Ind.<br>Auto.                                | _           | 10<br>10            |      |  |

| lcc1  | VDD Dynamic Operating<br>Supply Current | VDD = Max., $\overline{CE}$ = VIL<br>IOUT = 0 mA, f = fmax<br>VIN = VIH or VIL                                                                                         | Com.<br>Ind.<br>Auto.                        | _           | 15<br>20<br>25      | mA   |  |

|       |                                         | VIN = VIH OI VIL                                                                                                                                                       | typ. <sup>(2)</sup>                          | 1           | -                   |      |  |

| ISB1  | TTL Standby Current (TTL Inputs)        | $\begin{aligned} V_{DD} &= Max., \\ V_{IN} &= V_{IH} \text{ or } V_{IL}, \ \overline{CE} \geq V_{IH}, \\ f &= 0 \end{aligned}$                                         | Com.<br>Ind.<br>Auto.                        |             | 1<br>1.5<br>2       | mA   |  |

| ISB2  | CMOS Standby<br>Current (CMOS Inputs)   | $\begin{split} & V_{DD} = Max., \\ & \overline{CE} \geq V_{DD} - 0.2V, \\ & V_{IN} \geq V_{DD} - 0.2V, \\ & \text{or } V_{IN} \leq V_{SS} + 0.2V, \ f = 0 \end{split}$ | Com.<br>Ind.<br>Auto.<br>typ. <sup>(2)</sup> | _<br>_<br>_ | 10<br>15<br>35<br>4 | μΑ   |  |

#### Note:

At f = fMAX, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.

Typical values are measured at VDD = 5V, TA = 25°C and not 100% tested.

# READ CYCLE SWITCHING CHARACTERISTICS<sup>(1)</sup> (Over Operating Range)

|                      |                         | -4   | 5    |      |  |

|----------------------|-------------------------|------|------|------|--|

| Symbol               | Parameter               | Min. | Max. | Unit |  |

| trc                  | Read Cycle Time         | 45   | _    | ns   |  |

| taa                  | Address Access Time     | _    | 45   | ns   |  |

| tона                 | Output Hold Time        | 3    | _    | ns   |  |

| tace                 | CE Access Time          | _    | 45   | ns   |  |

| tDOE                 | OE Access Time          | _    | 20   | ns   |  |

| thzoe(2)             | OE to High-Z Output     | 0    | 15   | ns   |  |

| tLZOE <sup>(2)</sup> | OE to Low-Z Output      | 5    | _    | ns   |  |

| thzce <sup>(2)</sup> | CE to High-Z Output     | 0    | 15   | ns   |  |

| tLZCE <sup>(2)</sup> | CE to Low-Z Output      | 5    | _    | ns   |  |

| <b>t</b> BA          | LB, UB Access Time      | _    | 45   | ns   |  |

| tнzв                 | LB, UB to High-Z Output | 0    | 15   | ns   |  |

| tlzв                 | LB, UB to Low-Z Output  | 0    | _    | ns   |  |

#### Notes:

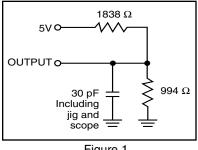

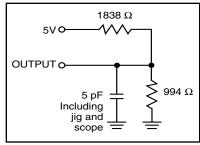

- 1. Test conditions assume signal transition times of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V and output loading specified in Figure 1.

- 2. Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.

- 3. Not 100% tested.

## **ACTEST CONDITIONS**

| 710 1 2 0 1 0 0 11 1 1 1 1 1 1 1 1 1 1 1    |                     |

|---------------------------------------------|---------------------|

| Parameter                                   | Unit                |

| Input Pulse Level                           | 0V to 3.0V          |

| Input Rise and Fall Times                   | 3 ns                |

| Input and Output Timing and Reference Level | 1.5V                |

| Output Load                                 | See Figures 1 and 2 |

## **ACTEST LOADS**

Figure 1

Figure 2

## **AC WAVEFORMS**

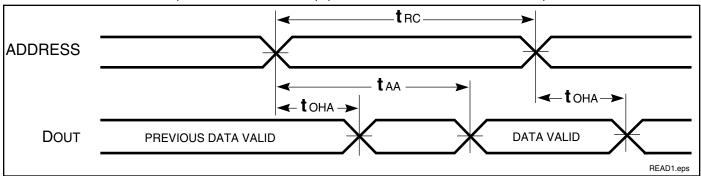

# **READ CYCLE NO.** $1^{(1,2)}$ (Address Controlled) ( $\overline{CE} = \overline{OE} = V_{IL}$ , $\overline{UB}$ or $\overline{LB} = V_{IL}$ )

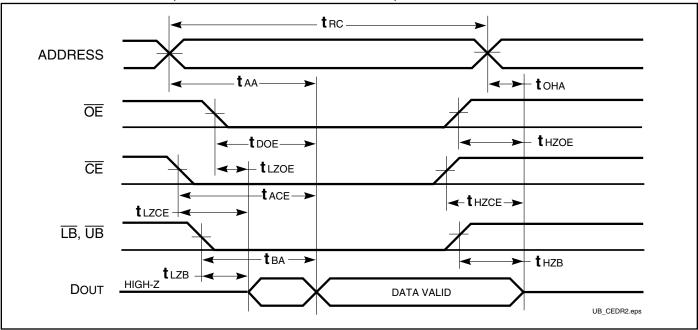

# READ CYCLE NO. 2<sup>(1,3)</sup> ( $\overline{CE}$ , $\overline{OE}$ and $\overline{UB}/\overline{LB}$ Controlled)

#### Notes:

- 1.  $\overline{\text{WE}}$  is HIGH for a Read Cycle.

- 2. The device is continuously selected.  $\overline{OE}$ ,  $\overline{CE}$ ,  $\overline{UB}$ , or  $\overline{LB} = V_{IL}$ .

- 3. Address is valid prior to or coincident with  $\overline{\text{CE}}$  LOW transition.

## WRITE CYCLE SWITCHING CHARACTERISTICS(1,3) (Over Operating Range)

|                      |                                 | -4   |      |      |  |

|----------------------|---------------------------------|------|------|------|--|

| Symbol               | Parameter                       | Min. | Max. | Unit |  |

| twc                  | Write Cycle Time                | 45   | _    | ns   |  |

| tsce                 | CE to Write End                 | 35   | _    | ns   |  |

| taw                  | Address Setup Time to Write End | 35   | _    | ns   |  |

| tha                  | Address Hold from Write End     | 0    | _    | ns   |  |

| <b>t</b> sa          | Address Setup Time              | 0    | _    | ns   |  |

| <b>t</b> PWB         | LB, UB Valid to End of Write    | 35   | _    | ns   |  |

| t <sub>PWE1</sub>    | WE Pulse Width (OE =High)       | 35   | _    | ns   |  |

| tPWE2                | WE Pulse Width (OE=Low)         | 35   | _    | ns   |  |

| tsp                  | Data Setup to Write End         | 25   | _    | ns   |  |

| thd                  | Data Hold from Write End        | 0    | _    | ns   |  |

| tHZWE <sup>(2)</sup> | WE LOW to High-Z Output         | _    | 20   | ns   |  |

| tLZWE <sup>(2)</sup> | WE HIGH to Low-Z Output         | 5    | _    | ns   |  |

#### Notes:

2. Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.

<sup>1.</sup> Test conditions assume signal transition times of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V and output loading specified in Figure 1.

<sup>3.</sup> The internal write time is defined by the overlap of  $\overline{\text{CE}}$  LOW and  $\overline{\text{UB}}$  or  $\overline{\text{LB}}$ , and  $\overline{\text{WE}}$  LOW. All signals must be in valid states to initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the write.

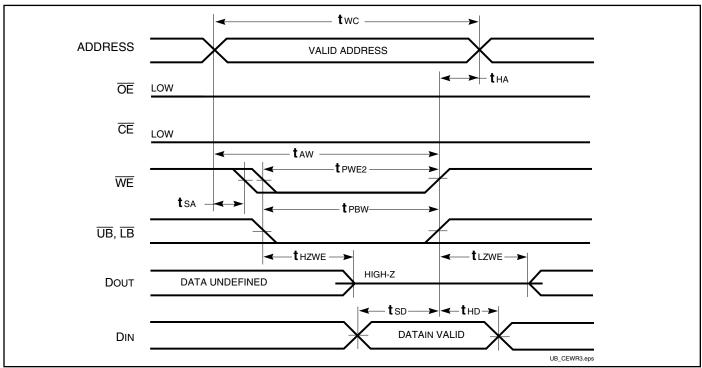

## **AC WAVEFORMS**

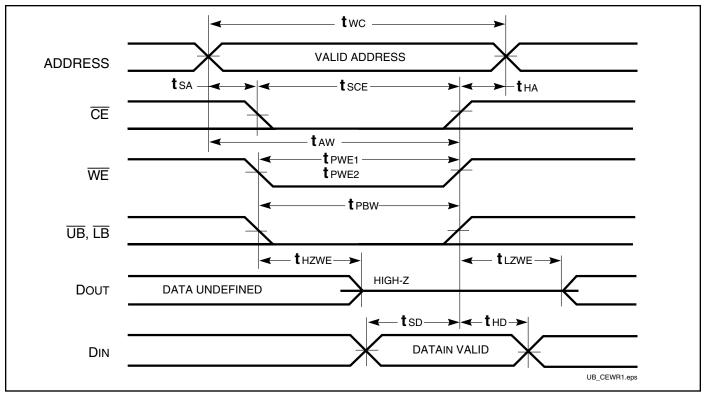

# WRITE CYCLE NO. 1 (WE Controlled)(1,2)

#### Notes:

- 1. WRITE is an internally generated signal asserted during an overlap of the LOW states on the  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  inputs and at least one of the LB and UB inputs being in the LOW state.

- 2. WRITE =  $(\overline{CE})$  [  $(\overline{LB})$  =  $(\overline{UB})$  ]  $(\overline{WE})$ .

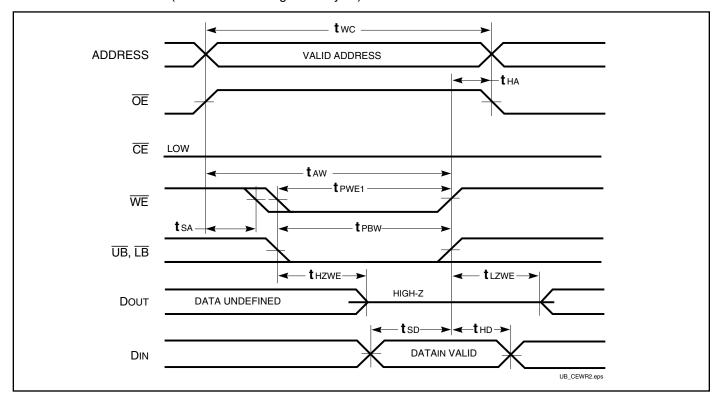

## WRITE CYCLE NO. 2 (OE is HIGH During Write Cycle) (1,2)

## WRITE CYCLE NO. 3 (OE is LOW During Write Cycle) (1)

#### Notes:

- 1. The internal write time is defined by the overlap of  $\overline{\text{CE}}$  LOW and  $\overline{\text{WE}}$  LOW. All signals must be in valid states to initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the Write.

- 2. I/O will assume the High-Z state if  $\overline{OE} \ge V_{IH}$ .

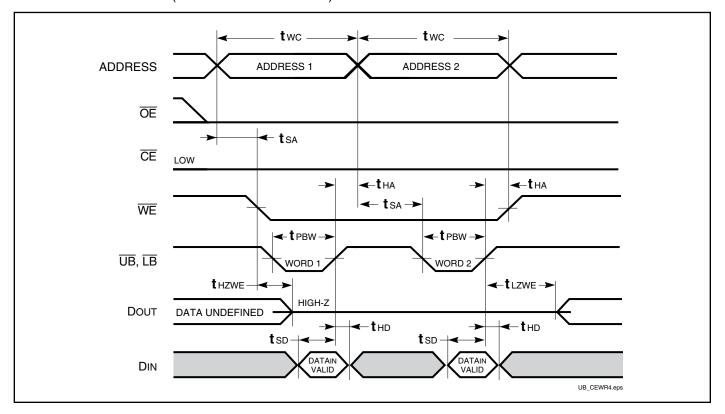

# WRITE CYCLE NO. 4 (UB/LB Back to Back Write)

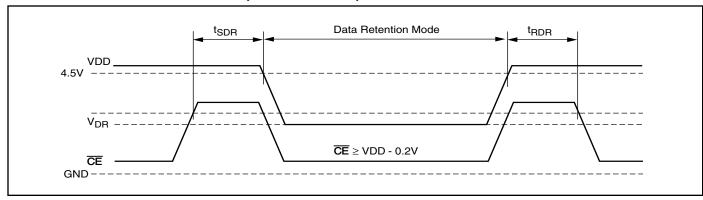

# **DATA RETENTION SWITCHING CHARACTERISTICS**

| Symbol          | Parameter                 | Test Condition                                                                                                       |                              | Min. | Max.     | Unit |

|-----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------|------|----------|------|

| V <sub>DR</sub> | VDD for Data Retention    | See Data Retention Waveform                                                                                          |                              | 2.0  | 5.5      | V    |

| IDR             | Data Retention Current    | $V_{DD} = 2.0V, \overline{CE} \ge V_{DD} - 0.2V$<br>$V_{IN} \ge V_{DD} - 0.2V, \text{ or } V_{IN} \le V_{SS} + 0.2V$ | Com.<br>Ind.                 |      | 10<br>15 | μΑ   |

|                 |                           |                                                                                                                      | Auto.<br>typ. <sup>(1)</sup> | _ 2  | 35       |      |

| tsdr            | Data Retention Setup Time | See Data Retention Waveform                                                                                          |                              | 0    | _        | ns   |

| trdr            | Recovery Time             | See Data Retention Waveform                                                                                          |                              | trc  | _        | ns   |

#### Note:

# **DATA RETENTION WAVEFORM (CE Controlled)**

<sup>1.</sup> Typical Values are measured at  $V_{DD} = 5V$ ,  $T_A = 25^{\circ}C$  and not 100% tested.

# IS62C25616BL, IS65C25616BL

**ORDERING INFORMATION: IS62C25616BL**

Industrial Range: -40°C to +85°C

| Speed (ns)                                   | Order Part No.    | Package        |

|----------------------------------------------|-------------------|----------------|

| 45                                           | IS62C25616BL-45TI | 44-pin TSOP-II |

| IS62C25616BL-45TLI 44-pin TSOP-II, Lead-free |                   |                |

Automotive Range: -40°C to +125°C

| Speed (ns) | Order Part No.       | Package                                     |

|------------|----------------------|---------------------------------------------|

| 45         | IS65C25616BL-45CTLA3 | 44-pin TSOP-II, Lead-free, Copper Leadframe |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for SRAM category:

Click to view products by ISSI manufacturer:

Other Similar products are found below:

CY6116A-35DMB CY7C1049GN-10VXI CY7C128A-45DMB GS8161Z36DD-200I GS88237CB-200I RMLV0408EGSB-4S2#AA0

IDT70V5388S166BG IS64WV3216BLL-15CTLA3 IS66WVE4M16ECLL-70BLI PCF8570P K6F2008V2E-LF70000 K6T4008C1B-GB70

CY7C1353S-100AXC AS6C8016-55BIN AS7C164A-15PCN 515712X IDT71V67603S133BG IS62WV51216EBLL-45BLI

IS63WV1288DBLL-10HLI IS66WVE2M16ECLL-70BLI IS66WVE4M16EALL-70BLI IS62WV6416DBLL-45BLI IS61WV102416DBLL

10TLI CY7C1381KV33-100AXC CY7C1381KVE33-133AXI 8602501XA 5962-3829425MUA 5962-3829430MUA 5962-8855206YA

5962-8866201YA 5962-8866204TA 5962-8866206MA 5962-8866208UA 5962-8872502XA 5962-9062007MXA 5962-9161705MXA

GS882Z18CD-150I M38510/28902BVA 8413202RA 5962-9161708MYA 5962-8971203XA 5962-8971202ZA 5962-8872501LA 5962-8866208YA 5962-8866205YA 5962-8866205YA 5962-8866205UA 5962-8866203YA 5962-8866205YA 5962-88667519XA