# 16M x 8 HyperRAM™

### NOVEMBER 2020

### Overview

The IS66/67WVH16M8DALL/BLL are integrated memory device containing 128Mbit Pseudo Static Random Access Memory using a self-refresh DRAM array organized as 16M words by 8 bits. The device supports a HyperBus interface, Very Low Signal Count (Address, Command and data through 8 DQ pins), Hidden Refresh Operation, and Automotive Temperature Operation, designed specially for Mobile and Automotive applications.

## **Distinctive Characteristics**

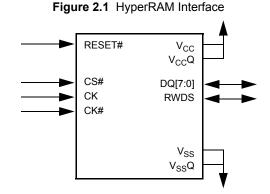

### HyperBus<sup>™</sup> Low Signal Count Interface

- 3.0V I/O, 11 bus signals

- Single ended clock (CK)

- 1.8V I/O, 12 bus signals

- Differential clock (CK, CK#)

- Chip Select (CS#)

- 8-bit data bus (DQ[7:0])

- Read-Write Data Strobe (RWDS)

- Bidirectional Data Strobe / Mask

- Output at the start of all transactions to indicate refresh latency

- Output during read transactions as Read Data Strobe

- Input during write transactions as Write Data Mask

- RWDS DCARS Timing

- During read transactions RWDS is offset by a second clock, phase shifted from CK

- The Phase Shifted Clock is used to move the RWDS transition edge within the read data eye

## **Performance Summary**

| Read Transaction Timings                                      |         |  |  |  |  |  |  |

|---------------------------------------------------------------|---------|--|--|--|--|--|--|

| Maximum Clock Rate at 1.8V V <sub>CC</sub> /V <sub>CC</sub> Q | 200 MHz |  |  |  |  |  |  |

| Maximum Clock Rate at 3.0V V <sub>CC</sub> /V <sub>CC</sub> Q | 166 MHz |  |  |  |  |  |  |

| Maximum Access Time, (t <sub>ACC</sub> at 200 MHz)            | 40 ns   |  |  |  |  |  |  |

### **High Performance**

- Up to 400MB/s

- Double-Data Rate (DDR) two data transfers per clock

- 200-MHz clock rate (400 MB/s) at 1.8V V<sub>CC</sub>, 105°C

- 166-MHz clock rate (332 MB/s) at 1.8V V<sub>CC</sub>, 125°C

- 166-MHz clock rate (332 MB/s) at 3.0V V<sub>CC</sub> ,105°C/125°C

- Sequential burst transactions

- Configurable Burst Characteristics

- Wrapped burst lengths:

- 16 bytes (8 clocks)

- 32 bytes (16 clocks)

- 64 bytes (32 clocks)

- 128 bytes (64 clocks)

- Linear burst

- Hybrid option one wrapped burst followed by linear burst

- Wrapped or linear burst type selected in each transaction

- Configurable output drive strength

- Temperature Grade

- Industrial: -40°C to +85°C

- Auto (A2) Grade: -40°C to +105°C

- Auto (A3) Grade: -40°C to +125°C

- Package

- 24-ball FBGA

| Maximum Current Consumption                         |         |  |  |  |  |  |  |

|-----------------------------------------------------|---------|--|--|--|--|--|--|

| Burst Read (linear burst at 200 MHz, 1.8V, 105 °C)  | 40 mA   |  |  |  |  |  |  |

| Burst Write (linear burst at 200 MHz, 1.8V, 105 °C) | 35 mA   |  |  |  |  |  |  |

| Standby (CS# = High, 3V, 105 °C)                    | 1200 µA |  |  |  |  |  |  |

| Deep Power Down (CS# = High, 3V, 105 °C)            | 50 µA   |  |  |  |  |  |  |

| Standby (CS# = High, 1.8V, 105 °C)                  | 1200 µA |  |  |  |  |  |  |

| Deep Power Down (CS# = High, 1.8V, 105 °C)          | 30 µA   |  |  |  |  |  |  |

Copyright © 2020 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

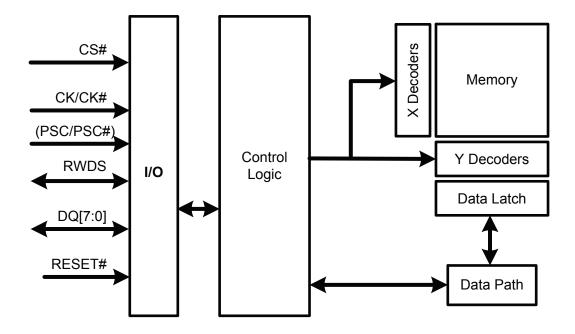

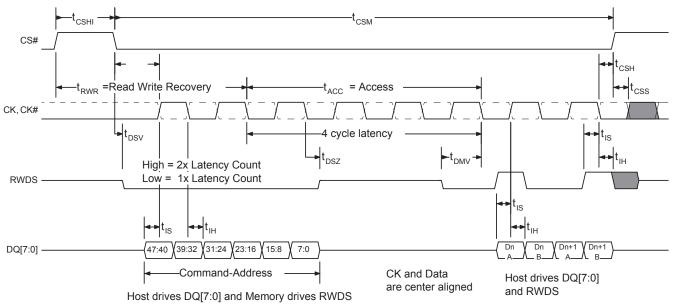

# Logic Block Diagram

# Contents

| 1.                                                                                                   | General Description                                                                     | . 4                              |

|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------|

| 2.                                                                                                   | HyperRAM Product Overview                                                               | . 7                              |

| <b>3.</b><br>3.1<br>3.2                                                                              | HyperRAM Signal Descriptions<br>Input/Output Summary<br>Command/Address Bit Assignments | . 8                              |

| 3.2<br>3.3<br>3.4                                                                                    | Read Transactions<br>Write Transactions with Initial Latency<br>(Memory Core Write)     | 13                               |

| 3.5                                                                                                  | Write Transactions without Initial Latency<br>(Register Write)                          | 16                               |

| 4.                                                                                                   | Memory Space                                                                            | 17                               |

| <b>5.</b><br>5.1<br>5.2                                                                              | Register Space<br>Device Identification Registers<br>Register Space Access              | 17<br>17<br>18                   |

| Нур                                                                                                  | erRAM Device Hardware Interface                                                         |                                  |

| <b>6.</b><br>6.1                                                                                     | Interface States<br>Power Conservation Modes                                            |                                  |

| <b>7.</b><br>7.1<br>7.2                                                                              | HyperRAM Connection Descriptions<br>Other Connectors Summary<br>HyperRAM Block Diagram  | 27                               |

|                                                                                                      | Hyperio an Dioek Diagram                                                                | 20                               |

| 8.                                                                                                   | Interface States                                                                        |                                  |

| <ol> <li>8.</li> <li>9.1</li> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>9.5</li> <li>9.6</li> </ol> |                                                                                         | 29<br>30<br>31<br>31<br>32<br>33 |

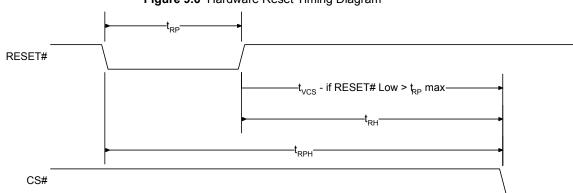

| 9.7                | Hardware Reset                                                                                  | 36       |

|--------------------|-------------------------------------------------------------------------------------------------|----------|

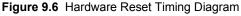

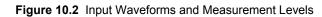

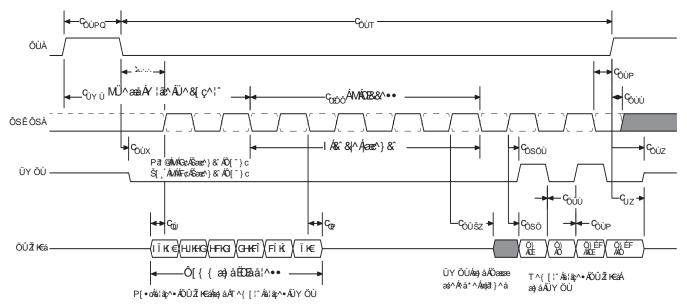

| 10.1<br>10.2       | Timing Specifications<br>Key to Switching Waveforms<br>AC Test Conditions<br>AC Characteristics | 37<br>37 |

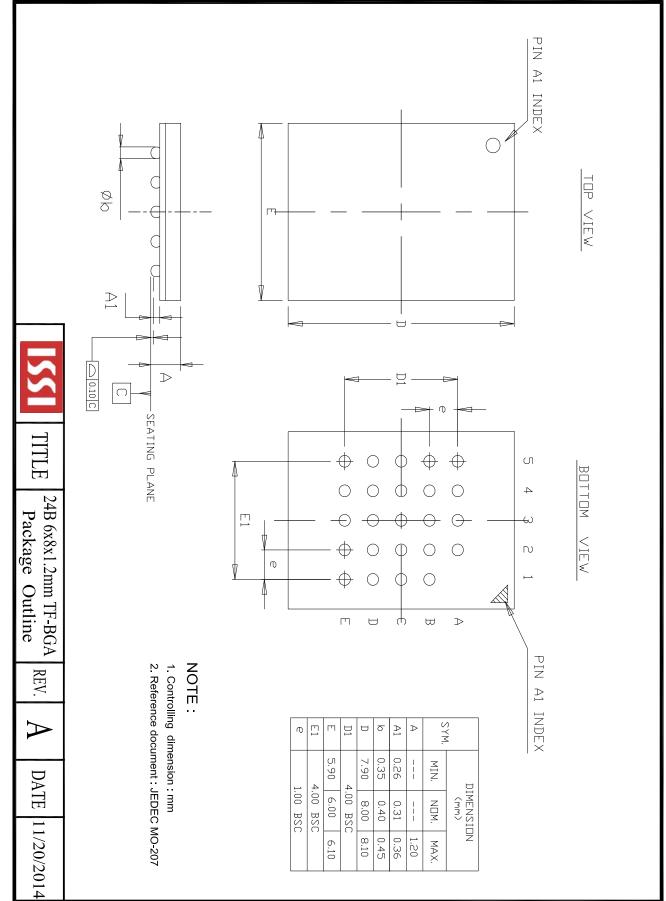

| 11.                | Physical Interface                                                                              | 41       |

| 11.1               | FBGA 24-Ball 5 x 5 Array Footprint                                                              | 41       |

|                    | DDR Center Aligned<br>Read Strobe Functionality                                                 | 42       |

|                    | HyperRAM Products with DCARS<br>Signal Descriptions                                             | 42       |

|                    | HyperRAM Products with DCARS<br>— FBGA 24-ball, 5x5 Array Footprint                             |          |

| 12.3               | HyperRAM Memory with DCARS Timing                                                               | 43       |

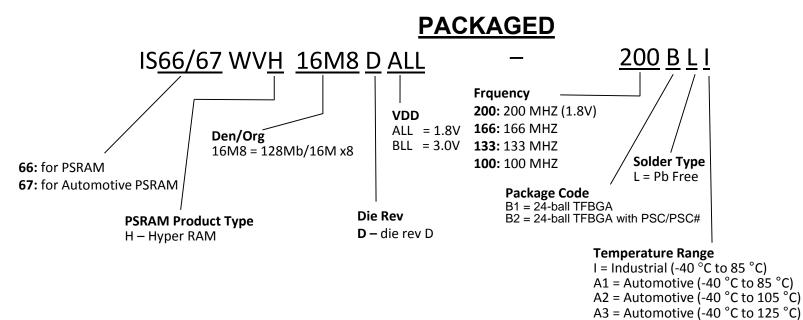

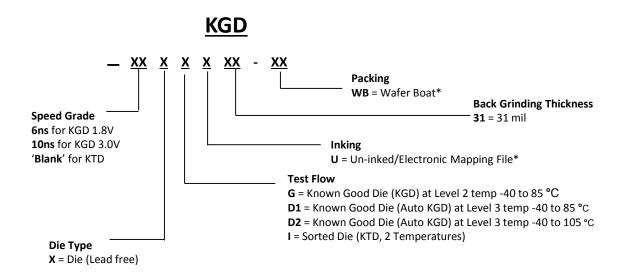

| <b>13.</b><br>13.1 | Ordering Rule Information                                                                       |          |

## 1. General Description

The ISSI 128-Mbit HyperRAM<sup>™</sup> device is a high-speed CMOS, self-refresh Dynamic RAM (DRAM), with a HyperBus interface.

The Random Access Memory (RAM) array uses dynamic cells that require periodic refresh. Refresh control logic within the device manages the refresh operations on the RAM array when the memory is not being actively read or written by the HyperBus interface master (host). Since the host is not required to manage any refresh operations, the DRAM array appears to the host as though the memory uses static cells that retain data without refresh. Hence, the memory can also be described as Pseudo Static RAM (PSRAM).

Because the DRAM cells cannot be refreshed during a read or write transaction, there is a requirement that the host not perform read or write burst transfers that are long enough to block the necessary internal logic refresh operations when they are needed. The host is required to limit the duration of transactions and allow additional initial access latency, at the beginning of a new transaction, if the memory indicates a refresh operation is needed.

HyperBus is a low signal count, Double Data Rate (DDR) interface, that achieves high speed read and write throughput. The DDR protocol transfers two data bytes per clock cycle on the DQ input/output signals. A read or write transaction on HyperBus consists of a series of 16-bit wide, one clock cycle data transfers at the internal HyperRAM core with two corresponding 8-bit wide, one-half-clock-cycle data transfers on the DQ signals. All inputs and outputs are LV-CMOS compatible. Ordering Part Number (OPN) device versions are available for core ( $V_{CC}$ ) and IO buffer ( $V_{CC}Q$ ) supplies of either 1.8V or 3.0V (nominal).

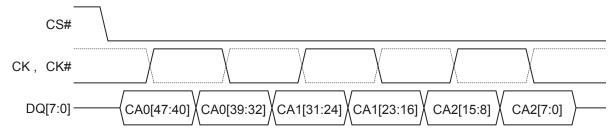

Command, address, and data information is transferred over the eight HyperBus DQ[7:0] signals. The clock is used for information capture by a HyperBus slave device when receiving command, address, or data on the DQ signals. Command or Address values are center aligned with clock transitions.

Every transaction begins with the assertion of CS# and Command-Address (CA) signals, followed by the start of clock transitions to transfer six CA bytes, followed by initial access latency and either read or write data transfers, until CS# is deasserted.

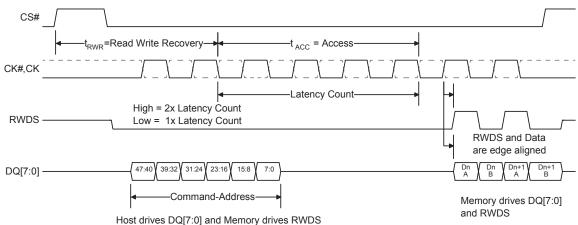

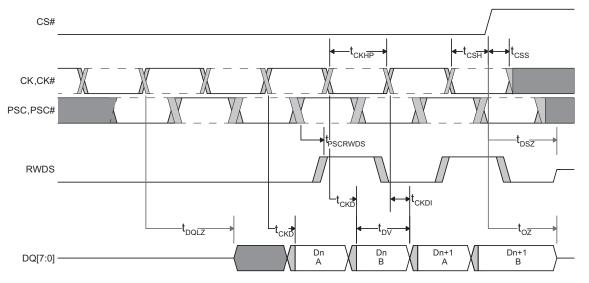

Figure 1.1 Read Transaction, Single Initial Latency Count

The Read/Write Data Strobe (RWDS) is a bidirectional signal that indicates:

- when data will start to transfer from a HyperRAM device to the master device in read transactions (initial read latency)

- when data is being transferred from a HyperRAM device to the master device during read transactions (as a source synchronous read data strobe)

- when data may start to transfer from the master device to a HyperRAM device in write transactions (initial write latency)

- data masking during write data transfers

During the CA transfer portion of a read or write transaction, RWDS acts as an output from a HyperRAM device to indicate whether additional initial access latency is needed in the transaction.

During read data transfers, RWDS is a read data strobe with data values edge aligned with the transitions of RWDS.

During write data transfers, RWDS indicates whether each data byte transfer is masked with RWDS High (invalid and prevented from changing the byte location in a memory) or not masked with RWDS Low (valid and written to a memory). Data masking may be used by the host to byte align write data within a memory or to enable merging of multiple non-word aligned writes in a single burst write. During write transactions, data is center aligned with clock transitions.

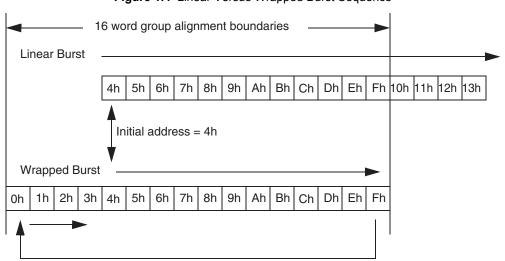

Read and write transactions are burst oriented, transferring the next sequential word during each clock cycle. Each individual read or write transaction can use either a wrapped or linear burst sequence.

#### Figure 1.4 Linear Versus Wrapped Burst Sequence

During wrapped transactions, accesses start at a selected location and continue to the end of a configured word group aligned boundary, then wrap to the beginning location in the group, then continue back to the starting location. Wrapped bursts are generally used for critical word first cache line fill read transactions. During linear transactions, accesses start at a selected location and continue in a sequential manner until the transaction is terminated when CS# returns High. Linear transactions are generally used for large contiguous data transfers such as graphic images. Since each transaction command selects the type of burst sequence for that transaction, wrapped and linear bursts transactions can be dynamically intermixed as needed.

## 2. HyperRAM Product Overview

The 128-Mbit HyperRAM device is a 1.8V or 3.0V core and I/O, synchronous self-refresh Dynamic RAM (DRAM). The HyperRAM device provides a HyperBus slave interface to the host system. HyperBus has an 8-bit (1 byte) wide DDR data bus and uses only word-wide (16-bit data) address boundaries. Read transactions provide 16 bits of data during each clock cycle (8 bits on both clock edges). Write transactions take 16 bits of data from each clock cycle (8 bits on each clock edge).

Read and write transactions require two clock cycles to define the target row address and burst type, then an initial access latency of  $t_{ACC}$ . During the Command-Address (CA) part of a transaction, the memory will indicate whether an additional latency for a required refresh time ( $t_{RFH}$ ) is added to the initial latency; by driving the RWDS signal to the High state. During the CA period the third clock cycle will specify the target word address within the target row. During a read (or write) transaction, after the initial data value has been output (or input), additional data can be read from (or written to) the row on subsequent clock cycles in either a wrapped or linear sequence. When configured in linear burst mode, the device will automatically fetch the next sequential row from the memory array to support a continuous linear burst. Simultaneously accessing the next row in the array while the read or write data transfer is in progress, allows for a linear sequential burst operation that can provide a sustained data rate of 400 MB/s (1 byte (8 bit data bus) \* 2 (*data clock edges*) \* 200 MHz = 400 MB/s).

# 3. HyperRAM Signal Descriptions

## 3.1 Input/Output Summary

HyperRAM signals are shown in Table 3.1. Active Low signal names have a hash symbol (#) suffix.

Table 3.1 I/O Summary

| Symbol            | Туре                                                                                                                                                                                                                                                                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#               | Master Output, Slave Input                                                                                                                                                                                                                                                                                                                            | <b>Chip Select.</b> Bus transactions are initiated with a High to Low transition. Bus transactions are terminated with a Low to High transition. The master device has a separate CS# for each slave.                                                                                                                                                                                               |

| СК, СК#           | <ul> <li>Differential Clock. Command, address, and data information is output with respect to the crossing of the CK and CK# signals. Differential clock is used on 1.8V I/O devices.</li> <li>Single Ended Clock. CK# is not used on 3.0V devices, only a single ended CK is used.</li> <li>The clock is not required to be free-running.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                     |

| DQ[7:0]           | Input/Output                                                                                                                                                                                                                                                                                                                                          | <b>Data Input/Output.</b> Command, Address, and Data information is transferred on these signals during Read and Write transactions.                                                                                                                                                                                                                                                                |

| RWDS              | Input/Output                                                                                                                                                                                                                                                                                                                                          | <b>Read Write Data Strobe.</b> During the Command/Address portion of all bus transactions RWDS is a slave output and indicates whether additional initial latency is required. Slave output during read data transfer, data is edge aligned with RWDS. Slave input during data transfer in write transactions to function as a data mask. (High = additional latency, Low = no additional latency). |

| RESET#            | Master Output, Slave Input,<br>Internal Pull-up                                                                                                                                                                                                                                                                                                       | <b>Hardware RESET</b> . When Low the slave device will self initialize and return to the Standby state. RWDS and DQ[7:0] are placed into the High-Z state when RESET# is Low. The slave RESET# input includes a weak pull-up, if RESET# is left unconnected it will be pulled up to the High state.                                                                                                 |

| V <sub>CC</sub>   | Power Supply                                                                                                                                                                                                                                                                                                                                          | Core Power.                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>CC</sub> Q | Power Supply                                                                                                                                                                                                                                                                                                                                          | Input/Output Power.                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>SS</sub>   | Power Supply                                                                                                                                                                                                                                                                                                                                          | Core Ground.                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>SS</sub> Q | Power Supply                                                                                                                                                                                                                                                                                                                                          | Input/Output Ground.                                                                                                                                                                                                                                                                                                                                                                                |

## 3.2 Command/Address Bit Assignments

All HyperRAM bus transactions can be classified as either read or write. A bus transaction is started with CS# going Low with clock in idle state (CK=Low and CK#=High). The first three clock cycles transfer three words of Command/Address (CA0, CA1, CA2) information to define the transaction characteristics. The Command/Address words are presented with DDR timing, using the first six clock edges. The following characteristics are defined by the Command/Address information:

- Read or Write transaction

- Address Space: memory array space or register space

- Register space is used to access Device Identification (ID) registers and Configuration Registers (CR) that identify the device characteristics and determine the slave specific behavior of read and write transfers on the HyperBus interface.

- Whether a transaction will use a linear or wrapped burst sequence.

- The target row (and half-page) address (upper order address)

- The target column (word within half-page) address (lower order address)

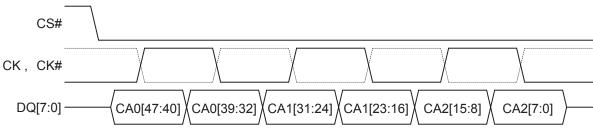

#### Figure 3.1 Command-Address Sequence

#### Notes:

1. Figure shows the initial three clock cycles of all transactions on the HyperBus.

2. CK# of differential clock is shown as dashed line waveform.

3. Command-Address information is "center aligned" with the clock during both Read and Write transactions.

| Signal | CA0[47:40] | CA0[39:32] | CA1[31:24] | CA1[23:16] | CA2[15:8] | CA2[7:0] |

|--------|------------|------------|------------|------------|-----------|----------|

| DQ[7]  | CA[47]     | CA[39]     | CA[31]     | CA[23]     | CA[15]    | CA[7]    |

| DQ[6]  | CA[46]     | CA[38]     | CA[30]     | CA[22]     | CA[14]    | CA[6]    |

| DQ[5]  | CA[45]     | CA[37]     | CA[29]     | CA[21]     | CA[13]    | CA[5]    |

| DQ[4]  | CA[44]     | CA[36]     | CA[28]     | CA[20]     | CA[12]    | CA[4]    |

| DQ[3]  | CA[43]     | CA[35]     | CA[27]     | CA[19]     | CA[11]    | CA[3]    |

| DQ[2]  | CA[42]     | CA[34]     | CA[26]     | CA[18]     | CA[10]    | CA[2]    |

| DQ[1]  | CA[41]     | CA[33]     | CA[25]     | CA[17]     | CA[9]     | CA[1]    |

| DQ[0]  | CA[40]     | CA[32]     | CA[24]     | CA[16]     | CA[8]     | CA[0]    |

| Table 3.2 | Command-Address | Bit Assignment to | DQ Signals |

|-----------|-----------------|-------------------|------------|

|-----------|-----------------|-------------------|------------|

#### Table 3.3 Command/Address Bit Assignments

| CA Bit# | Bit Name                      | Bit Function                                                                                                                                                                                                                                                                                                                                  |

|---------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47      | R/W#                          | Identifies the transaction as a read or write.<br>R/W#=1 indicates a Read transaction<br>R/W#=0 indicates a Write transaction                                                                                                                                                                                                                 |

| 46      | Address Space<br>(AS)         | Indicates whether the read or write transaction accesses the memory or register space.<br>AS=0 indicates memory space<br>AS=1 indicates the register space<br>The register space is used to access device ID and Configuration registers.                                                                                                     |

| 45      | Burst Type                    | Indicates whether the burst will be linear or wrapped.<br>Burst Type=0 indicates wrapped burst<br>Burst Type=1 indicates linear burst                                                                                                                                                                                                         |

| 44-16   | Row & Upper<br>Column Address | Row & Upper Column component of the target address: System word address bits A31-A3<br>Any upper Row address bits not used by a particular device density should be set to 0 by the<br>host controller master interface. The size of Rows and therefore the address bit boundary<br>between Row and Column address is slave device dependent. |

| 15-3    | Reserved                      | Reserved for future column address expansion.<br>Reserved bits are don't care in current HyperBus devices but should be set to 0 by the host<br>controller master interface for future compatibility.                                                                                                                                         |

| 2-0     | Lower Column<br>Address       | Lower Column component of the target address: System word address bits A2-0 selecting the starting word within a half-page.                                                                                                                                                                                                                   |

#### Notes:

- A Row is a group of words relevant to the internal memory array structure and additional latency may be inserted by RWDS when crossing Row boundaries this is device dependent behavior, refer to each HyperBus device data sheet for additional information. Also, the number of Rows may be used in the calculation of a distributed refresh interval for HyperRAM memory.

- 2. A Page is a 16-word (32-byte) length and aligned unit of device internal read or write access and additional latency may be inserted by RWDS when crossing Page boundaries this is device dependent behavior, refer to each HyperBus device data sheet for additional information.

- 3. The Column address selects the burst transaction starting word location within a Row. The Column address is split into an upper and lower portion. The upper portion selects an 8-word (16-byte) Half-page and the lower portion selects the word within a Half-page where a read or write transaction burst starts.

- 4. The initial read access time starts when the Row and Upper Column (Half-page) address bits are captured by a slave interface. Continuous linear read burst is enabled by memory devices internally interleaving access to 16 byte half-pages.

- 5. HyperBus protocol address space limit, assuming:

- 29 Row &Upper Column address bits

3 Lower Column address bits

Each address selects a word wide (16 bit = 2 byte) data value

29 + 3 = 32 address bits = 4G addresses supporting 8Gbyte (64Gbit) maximum address space

Future expansion of the column address can allow for 29 Row & Upper Column + 16 Lower Column address bits = 35 Tera-word = 70 Tera-byte address space.

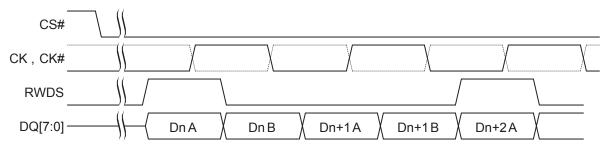

### Figure 3.2 Data Placement During a Read Transaction

#### Notes:

- 1. Figure shows a portion of a Read transaction on the HyperBus. CK# of differential clock is shown as dashed line waveform.

- 2. Data is "edge aligned" with the RWDS serving as a read data strobe during read transactions.

- 3. Data is always transferred in full word increments (word granularity transfers).

5. Data bits in each byte are always in high to low order with bit 7 on DQ7 and bit 0 on DQ0.

<sup>4.</sup> Word address increments in each clock cycle. Byte A is between RWDS rising and falling edges and is followed by byte B between RWDS falling and rising edges, of each word.

|           | <b>D</b> ( | D'' D'        | <b>-</b> · | <b>-</b> - |       |             |

|-----------|------------|---------------|------------|------------|-------|-------------|

| Table 3.4 | Data       | Bit Placement | During     | Read or    | write | Iransaction |

| Address<br>Space | Byte<br>Order | Byte<br>Position | Word<br>Data<br>Bit | DQ | Bit Order                                                                                                                                                                                                                                                      |

|------------------|---------------|------------------|---------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |               |                  | 15                  | 7  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 14                  | 6  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 13                  | 5  |                                                                                                                                                                                                                                                                |

|                  |               | А                | 12                  | 4  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 11                  | 3  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 10                  | 2  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 9                   | 1  |                                                                                                                                                                                                                                                                |

|                  | Big-          |                  | 8                   | 0  |                                                                                                                                                                                                                                                                |

|                  | endian        |                  | 7                   | 7  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 6                   | 6  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 5                   | 5  |                                                                                                                                                                                                                                                                |

|                  |               | В                | 4                   | 4  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 3                   | 3  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 2                   | 2  | When data is being accessed in memory space:                                                                                                                                                                                                                   |

|                  |               |                  | 1                   | 1  | The first byte of each word read or written is the "A" byte and the second is the "B" byte.                                                                                                                                                                    |

| Memory           |               |                  | 0<br>7              | 0  | The bits of the word within the A and B bytes depend on how the data was written. If the<br>lower address bits 7-0 are written in the A byte position and bits 15-8 are written into the<br>position, or vice versa, they will be read back in the same order. |

|                  |               |                  | 6                   | 6  | position, or vice versa, they will be read back in the same order.                                                                                                                                                                                             |

|                  |               | A                | 5                   | 5  | So, memory space can be stored and read in either little-endian or big-endian order.                                                                                                                                                                           |

|                  |               |                  | 4                   | 4  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 3                   | 3  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 2                   | 2  |                                                                                                                                                                                                                                                                |

|                  |               |                  | - 1                 | 1  |                                                                                                                                                                                                                                                                |

|                  | Little-       |                  | 0                   | 0  |                                                                                                                                                                                                                                                                |

|                  | endian        |                  | 15                  | 7  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 14                  | 6  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 13                  | 5  |                                                                                                                                                                                                                                                                |

|                  |               | _                | 12                  | 4  |                                                                                                                                                                                                                                                                |

|                  |               | В                | 11                  | 3  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 10                  | 2  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 9                   | 1  |                                                                                                                                                                                                                                                                |

|                  |               |                  | 8                   | 0  |                                                                                                                                                                                                                                                                |

| Address<br>Space | Byte<br>Order | Byte<br>Position | Word<br>Data<br>Bit | DQ  | Bit Order                                                                                                                                                                                |

|------------------|---------------|------------------|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |               |                  | 15                  | 7   |                                                                                                                                                                                          |

|                  |               |                  | 14                  | 6   |                                                                                                                                                                                          |

|                  |               |                  | 13                  | 5   |                                                                                                                                                                                          |

|                  |               | ۸                | 12                  | 4   |                                                                                                                                                                                          |

|                  | A             | A                | 11                  | 3   |                                                                                                                                                                                          |

|                  |               |                  | 10                  | 0 2 | When data is being accessed in register space:                                                                                                                                           |

|                  |               |                  | 9                   | 1   | During a Read transaction on the HyperBus two bytes are transferred on each clock cycle. The upper order byte A (Word[15:8]) is transferred between the rising and falling edges of RWDS |

| Pagistor         | Big-          |                  | 8                   | 0   | (edge aligned). The lower order byte B (Word[7:0]) is transferred between the falling and rising edges of RWDS.                                                                          |

| Register         | endian        |                  | 7                   | 7   | During a write the upper order byte A (Word[15:8]) is transferred on the CK rising edge and the                                                                                          |

|                  |               |                  | 6                   | 6   | During a write, the upper order byte A (Word[15:8]) is transferred on the CK rising edge and the lower order byte B (Word[7:0]) is transferred on the CK falling edge.                   |

|                  |               |                  | 5                   | 5   | So, register space is always read and written in Big-endian order because registers have device<br>dependent fixed bit location and meaning definitions.                                 |

|                  |               |                  | 4                   | 4   |                                                                                                                                                                                          |

|                  |               |                  | 3                   | 3   |                                                                                                                                                                                          |

|                  |               |                  | 2                   | 2   |                                                                                                                                                                                          |

|                  |               |                  | 1                   | 1   |                                                                                                                                                                                          |

|                  |               |                  | 0                   | 0   |                                                                                                                                                                                          |

#### Table 3.4 Data Bit Placement During Read or Write Transaction (Continued)

#### Figure 3.3 Data Placement During a Write Transaction

#### Notes:

- 1. Figure shows a portion of a Write transaction on the HyperBus.

- 2. Data is "center aligned" with the clock during a Write transaction.

- 3. RWDS functions as a data mask during write data transfers with initial latency. Masking of the first and last byte is shown to illustrate an unaligned 3 byte write of data.

- 4. RWDS is not driven by the master during write data transfers with zero initial latency. Full data words are always written in this case. RWDS may be driven low or left High-Z by the slave in this case.

## 3.3 Read Transactions

The HyperBus master begins a transaction by driving CS# Low while clock is idle. Then the clock begins toggling while Command-Address CA words are transfered.

In CA0, CA[47] = 1 indicates that a Read transaction is to be performed. CA[46] = 0 indicates the memory space is being read or CA[46] = 1 indicates the register space is being read. CA[45] indicates the burst type (wrapped or linear). Read transactions can begin the internal array access as soon as the row and upper column address has been presented in CA0 and CA1 (CA[47:16]). CA2 (CA(15:0]) identifies the target Word address within the chosen row. However, some HyperBus devices may require a minimum time between the end of a prior transaction and the start of a new access. This time is referred to as Read-Write-Recovery time (t<sub>RWR</sub>). The master interface must start driving CS# Low only at a time when the CA1 transfer will complete after t<sub>RWR</sub> is satisfied.

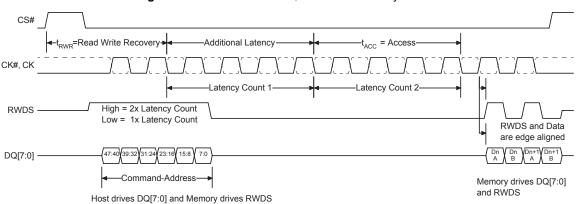

The HyperBus master then continues clocking for a number of cycles defined by the latency count setting in configuration register 0. The initial latency count required for a particular clock frequency is based on RWDS. If RWDS is Low during the CA cycles, one latency count is inserted. If RWDS is High during the CA cycles, an additional latency count is inserted. Once these latency clocks have been completed the memory starts to simultaneously transition the Read-Write Data Strobe (RWDS) and output the target data.

New data is output edge aligned with every transition of RWDS. Data will continue to be output as long as the host continues to transition the clock while CS# is Low. However, the HyperRAM device may stop RWDS transitions with RWDS Low, between the delivery of words, in order to insert latency between words when crossing memory array boundaries.

Wrapped bursts will continue to wrap within the burst length and linear burst will output data in a sequential manner across row boundaries. When a linear burst read reaches the last address in the array, continuing the burst beyond the last address will provide undefined data. Read transfers can be ended at any time by bringing CS# High when the clock is idle.

The clock is not required to be free-running. The clock may remain idle while CS# is high.

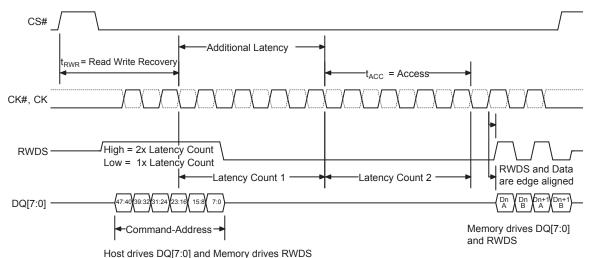

#### Figure 3.4 Read Transaction with Additional Initial Latency

#### Notes:

- 1. Transactions are initiated with CS# falling while CK=Low and CK#=High.

- 2. CS# must return High before a new transaction is initiated.

- 3. CK# is the complement of the CK signal. 3V devices use a single ended clock (CK only), CK# is used with CK on1.8V devices to provide a differential clock. CK# of a differential clock is shown as a dashed line waveform.

- 4. Read access array starts once CA[23:16] is captured.

- 5. The read latency is defined by the initial latency value in a configuration register.

- 6. In this read transaction example the initial latency count was set to four clocks.

- 7. In this read transaction a RWDS High indication during CA delays output of target data by an additional four clocks.

- 8. The memory device drives RWDS during read transactions.

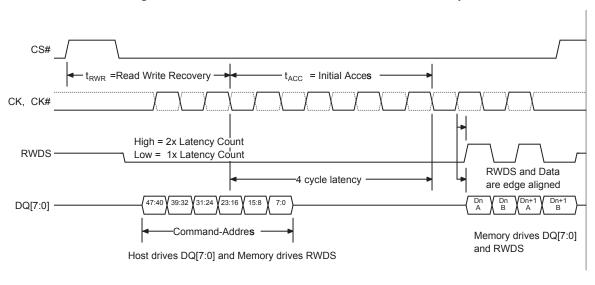

Figure 3.5 Read Transaction Without Additional Initial Latency

Notes:

1. RWDS is Low during the CA cycles. In this Read Transaction there is a single initial latency count for read data access because, this read transaction does not begin at a time when additional latency is required by the slave.

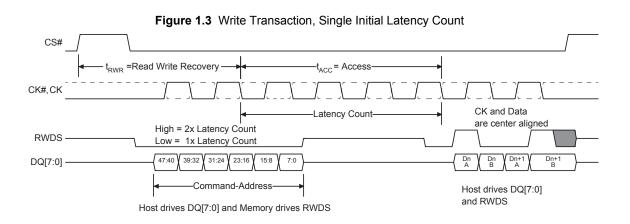

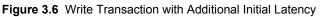

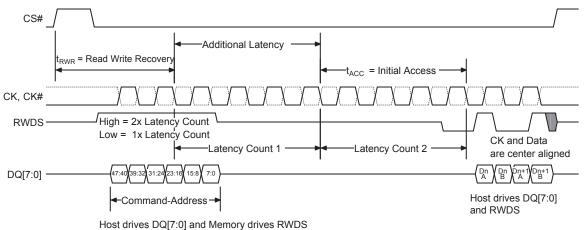

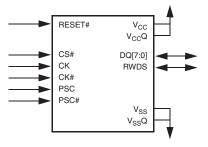

## 3.4 Write Transactions with Initial Latency (Memory Core Write)

The HyperBus master begins a transaction by driving CS# Low while clock is idle. Then the clock begins toggling while Command-Address CA words are transfered.

In CA0, CA[47] = 0 indicates that a Write transaction is to be performed. CA[46] = 0 indicates the memory space is being written. CA[45] indicates the burst type (wrapped or linear). Write transactions can begin the internal array access as soon as the row and upper column address has been presented in CA0 and CA1 (CA[47:16]). CA2 (CA(15:0]) identifies the target word address within the chosen row. However, some HyperBus devices may require a minimum time between the end of a prior transaction and the start of a new access. This time is referred to as Read-Write-Recovery time ( $t_{RWR}$ ). The master interface must start driving CS# Low only at a time when the CA1 transfer will complete after  $t_{RWR}$  is satisfied.

The HyperBus master then continues clocking for a number of cycles defined by the latency count setting in configuration register 0. The initial latency count required for a particular clock frequency is based on RWDS. If RWDS is Low during the CA cycles, one latency count is inserted. If RWDS is High during the CA cycles, an additional latency count is inserted.

Once these latency clocks have been completed the HyperBus master starts to output the target data. Write data is center aligned with the clock edges. The first byte of data in each word is captured by the memory on the rising edge of CK and the second byte is captured on the falling edge of CK.

During the CA clock cycles, RWDS is driven by the memory.

During the write data transfers, RWDS is driven by the host master interface as a data mask. When data is being written and RWDS is High the byte will be masked and the array will not be altered. When data is being written and RWDS is Low the data will be placed into the array. Because the master is driving RWDS during write data transfers, neither the master nor the HyperRAM device are able to indicate a need for latency within the data transfer portion of a write transaction. The acceptable write data burst length setting is also shown in configuration register 0.

Data will continue to be transferred as long as the HyperBus master continues to transition the clock while CS# is Low. Legacy format wrapped bursts will continue to wrap within the burst length. Hybrid wrap will wrap once then switch to linear burst starting at the next wrap boundary. Linear burst accepts data in a sequential manner across page boundaries. Write transfers can be ended at any time by bringing CS# High when the clock is idle.

When a linear burst write reaches the last address in the memory array space, continuing the burst will write to the beginning of the address range.

The clock is not required to be free-running. The clock may remain idle while CS# is high.

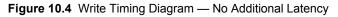

#### Notes:

- 1. Transactions must be initiated with CK=Low and CK#=High.

- 2. CS# must return High before a new transaction is initiated.

- 3. During Command-Address, RWDS is driven by the memory and indicates whether additional latency cycles are required.

- 4. In this example, RWDS indicates that additional initial latency cycles are required.

- 5. At the end of Command-Address cycles the memory stops driving RWDS to allow the host HyperBus master to begin driving RWDS. The master must drive RWDS to a valid Low before the end of the initial latency to provide a data mask preamble period to the slave.

- 6. During data transfer, RWDS is driven by the host to indicate which bytes of data should be either masked or loaded into the array.

- 7. The figure shows RWDS masking byte A0 and byte B1 to perform an unaligned word write to bytes B0 and A1.

#### Notes:

- 1. During Command-Address, RWDS is driven by the memory and indicates whether additional latency cycles are required.

- 2. In this example, RWDS indicates that there is no additional latency required.

- 3. At the end of Command-Address cycles the memory stops driving RWDS to allow the host HyperBus master to begin driving RWDS. The master must drive RWDS to a valid Low before the end of the initial latency to provide a data mask preamble period to the slave.

- 4. During data transfer, RWDS is driven by the host to indicate which bytes of data should be either masked or loaded into the array.

- 5. The figure shows RWDS masking byte A0 and byte B1 to perform an unaligned word write to bytes B0 and A1.

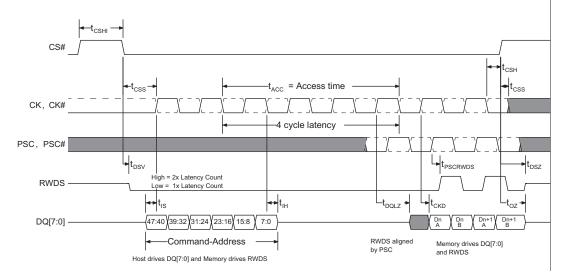

## 3.5 Write Transactions without Initial Latency (Register Write)

A Write transaction starts with the first three clock cycles providing the Command/Address information indicating the transaction characteristics. CA0 may indicate that a Write transaction is to be performed and also indicates the address space and burst type (wrapped or linear).

Writes without initial latency are used for register space writes. HyperRAM device write transactions with zero latency mean that the CA cycles are followed by write data transfers. Writes with zero initial latency, do not have a turn around period for RWDS. The HyperRAM device will always drive RWDS during the Command-Address period to indicate whether extended latency is required for a transaction that has initial latency. However, the RWDS is driven before the HyperRAM device has received the first byte of CA i.e. before the HyperRAM device knows whether the transaction is a read or write to register space. In the case of a write with zero latency, the RWDS state during the CA period does not affect the initial latency of zero. Since master write data immediately follows the Command-Address period in this case, the HyperRAM device may continue to drive RWDS Low or may take RWDS to High-Z during write data transfer. The master must not drive RWDS during Writes with zero latency. Writes with zero latency do not use RWDS as a data mask function. All bytes of write data are written (full word writes).

The first byte of data in each word is presented on the rising edge of CK and the second byte is presented on the falling edge of CK. Write data is center aligned with the clock inputs. Write transfers can be ended at any time by bringing CS# High when clock is idle. The clock is not required to be free-running.

#### Figure 3.8 Write Operation without Initial Latency

Host drives DQ[7:0] with Command-Address and Write Data

## 4. Memory Space

When CA[46] is 0 a read or write transaction accesses the DRAM memory array.

Table 4.1

Memory Space Address Map

| Unit Type                 | Count              | System Word Address<br>Bits | CA Bits | Notes                            |

|---------------------------|--------------------|-----------------------------|---------|----------------------------------|

| Rows within 128 Mb device | 16384 (Rows)       | A22- A9                     | 35 - 22 |                                  |

| Row                       | 1 (row)            | A8 - A3                     | 21 - 16 | 512 (word addresses)<br>1 kbytes |

| Half-Page                 | 8 (word addresses) | A2 - A0                     | 2 - 0   | 16 bytes                         |

## 5. Register Space

When CA[46] is 1 a read or write transaction accesses the Register Space.

Table 5.1 Register Space Address Map

| Register                               | System<br>Address | _          | _     | _      | 31-27 | 26-19 | 18-11 | 10-3  | —    | 2-0 |

|----------------------------------------|-------------------|------------|-------|--------|-------|-------|-------|-------|------|-----|

| <b>U</b>                               | CA Bits           | 47         | 46    | 45     | 44-40 | 39-32 | 31-24 | 23-16 | 15-8 | 7-0 |

| Identification Register<br>(read only) | 0                 |            | C0h c | or E0h |       | 00h   | 00h   | 00h   | 00h  | 00h |

| Identification Register<br>(read only) | 1                 | C0h or E0h |       | 00h    | 00h   | 00h   | 00h   | 01h   |      |     |

| Configuration Registe                  | r 0 Read          | C0h or E0h |       | 00h    | 01h   | 00h   | 00h   | 00h   |      |     |

| Configuration Registe                  | r 0 Write         | 60h        |       | 00h    | 01h   | 00h   | 00h   | 00h   |      |     |

| Configuration Registe                  | r 1 Read          | C0h or E0h |       | 00h    | 01h   | 00h   | 00h   | 01h   |      |     |

| Configuration Registe                  | r 1 Write         |            | 60h   |        |       | 00h   | 01h   | 00h   | 00h  | 01h |

#### Note:

1. CA45 may be either 0 or 1 for either wrapped or linear read. CA45 must be 1 as only linear single word register writes are supported.

## 5.1 Device Identification Registers

There are two read only, non-volatile, word registers, that provide information on the device selected when CS# is low. The device information fields identify:

- Manufacturer

- ∎ Туре

- Density

- Row address bit count

- Column address bit count

Table 5.2 ID Register 0 Bit Assignments

| Bits  | Function              | Settings (Binary)                 |

|-------|-----------------------|-----------------------------------|

| 15-14 | Reserved              | Reserved                          |

| 13    | Reserved              | 0 - default                       |

| 12-8  | Row Address Bit Count | 01101 - Fourteen Row address bits |

### Table 5.2 ID Register 0 Bit Assignments (Continued)

| Bits | Function                 | Settings (Binary)                                         |

|------|--------------------------|-----------------------------------------------------------|

| 7-4  | Column Address Bit Count | 1000 - Nine column address bits                           |

| 3-0  | Manufacturer             | 0000 - Reserved<br>0011 - ISSI<br>0010 to 1111 - Reserved |

Table 5.3 ID Register 1 Bit Assignments

| Bits | Function    | Settings (Binary)                          |

|------|-------------|--------------------------------------------|

| 15-4 | Reserved    | 0000_0000_0000b (default)                  |

| 3-0  | Device Type | 0000 - HyperRAM<br>0001 to 1111 - Reserved |

### 5.1.1 Density and Row Boundaries

The DRAM array size (density) of the device can be determined from the total number of system address bits used for the row and column addresses as indicated by the Row Address Bit Count and Column Address Bit Count fields in the ID0 register. For example: a 128-Mbit HyperRAM device has 9 column address bits and 14 row address bits for a total of 23 word address bits =  $2^{23} = 8$  Mwords = 16 Mbytes. The 9 column address bits indicate that each row holds  $2^9 = 512$  words = 1 kbytes. The row address bit count indicates there are 8196 x 2 rows to be refreshed within each array refresh interval. The row count within each array (8196) is used in calculating the refresh interval.

### 5.2 Register Space Access

Register default values are loaded upon power-up or hardware reset. The registers can be altered at any time while the device is in the standby state.

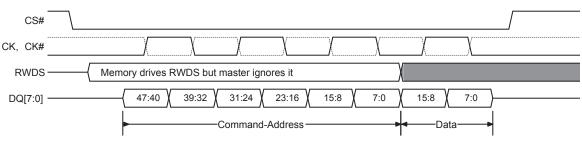

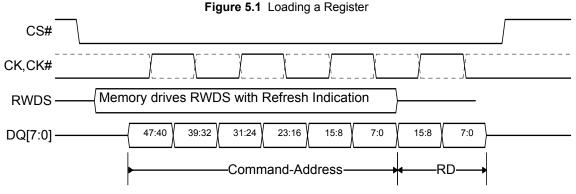

Loading a register is accomplished with a single 16-bit word write transaction as shown in Figure 5.1. CA[47] is zero to indicate a write transaction, CA[46] is a one to indicate a register space write, CA[45] is a one to indicate a linear write, lower order bits in the CA field indicate the register address.

Host drives DQ[7:0] with Command-Address and Register Data

#### Notes:

- 1. The host must not drive RWDS during a write to register space.

- 2. The RWDS signal is driven by the memory during the Command-Address period based on whether the memory array is being refreshed. This refresh indication does not affect the writing of register data. RWDS is driven immediately after CS# goes low, before CA[47:46] are received to indicate that the transaction is a write to register space, for which the RWDS refresh indication is not relevant.

- 3. The register value is always provided immediately after the CA value and is not delayed by a refresh latency.

- 4. The the RWDS signal returns to high impedance after the Command-Address period. Register data is never masked. Both data bytes of the register data are loaded into the selected register.

Each register is written with a separate single word write transaction. Register write transactions have zero latency, the single word of data immediately follows the Command-Address. RWDS is not driven by the host during the write because RWDS is always driven by the memory during the CA cycles to indicate whether a memory array refresh is in progress. Because a register space write goes directly to a register, rather than the memory array, there is no initial write latency, related to an array refresh that may be in progress. In a register write, RWDS is also not used as a data mask because both bytes of a register are always written and never masked.

Reserved register fields must be written with their default value. Writing reserved fields with other than default values may produce undefined results.

Reading of a register is accomplished with a single 16 bit read transaction with CA[46]=1 to select register space. If more than one word is read, the same register value is repeated in each word read. The CA[45] burst type is "don't care" because only a single register value is read. The contents of the register is returned in the same manner as reading array data, with one or two latency counts, based on the state of RWDS during the Command-Address period. The latency count is defined in the Configuration Register 0 Read Latency field (CR0[7:4]).

### 5.2.1 Configuration Register 0

Configuration Register 0 (CR0) is used to define the power mode and access protocol operating conditions for the HyperRAM device. Configurable characteristics include:

- Wrapped Burst Length (16, 32, 64, or 128-byte aligned and length data group)

- Wrapped Burst Type

- Legacy wrap (sequential access with wrap around within a selected length and aligned group)

- Hybrid wrap (Legacy wrap once then linear burst at start of the next sequential group)

- Initial Latency

- Variable Latency

- Whether an array read or write transaction will use fixed or variable latency. If fixed latency is selected the memory will always indicate a refresh latency and delay the read data transfer accordingly. If variable latency is selected, latency for a refresh is only added when a refresh is required at the same time a new transaction is starting.

- Output Drive Strength

- Deep Power Down Mode

Table 5.4 Configuration Register 0 Bit Assignments

| CR0 Bit | Function               | Settings (Binary)                                                                                                                               |

|---------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

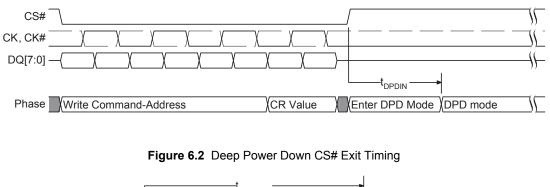

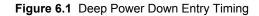

| 15      | Deep Power Down Enable | 1 - Normal operation (default)<br>0 - Writing 0 to CR[15] causes the device to enter Deep Power Down                                            |

| 14-12   | Drive Strength         | 000 - 34 ohms (default)<br>001 - 115 ohms<br>010 - 67 ohms<br>011 - 46 ohms<br>100 - 34 ohms<br>101 - 27 ohms<br>110 - 22 ohms<br>111 - 19 ohms |

| 11-8    | Reserved               | 1 - Reserved (default)<br>Reserved for Future Use. When writing this register, these bits should be set<br>to 1 for future compatibility.       |

|  | Table 5.4 | Configuration | Register 0 | Bit Assignments | (Continued) |

|--|-----------|---------------|------------|-----------------|-------------|

|--|-----------|---------------|------------|-----------------|-------------|

| CR0 Bit | Function             | Settings (Binary)                                                                                                                                                                              |

|---------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4     | Initial Latency      | 0000 - 5 Clock Latency<br>0001 - 6 Clock Latency (default)<br>0010 - Reserved<br>0011 - Reserved<br>0100 - Reserved<br><br>1101 - Reserved<br>1110 - 3 Clock Latency<br>1111 - 4 Clock Latency |

| 3       | Fixed Latency Enable | <ul> <li>0 - Variable Latency - 1 or 2 times Initial Latency depending on RWDS during CA cycles.</li> <li>1 - Fixed 2 times Initial Latency (default)</li> </ul>                               |

| 2       | Hybrid Burst Enable  | 0: Wrapped burst sequences to follow hybrid burst sequencing<br>1: Wrapped burst sequences in legacy wrapped burst manner (default)                                                            |

| 1-0     | Burst Length         | 00 - 128 bytes<br>01 - 64 bytes<br>10- 16 bytes<br>11 - 32 bytes (default)                                                                                                                     |

Note:

1. Initial latency of 6 clock Latency (default) is for 1.8V &\$\$MHz Uhi105°C (133MHz at 125°C)ZUbX'' '\$J'%\*A<n'Uhi%) š7 f%' A<n'at %) š7 Ł As for 1.8V # '\$J'%\*MHz at 125°C , bit[7:4] must be set to to 0011 (8 Clock Latency).

### 5.2.1.1 Wrapped Burst

A wrapped burst transaction accesses memory within a group of words aligned on a word boundary matching the length of the configured group. Wrapped access groups can be configured as 16, 32, 64, or 128 bytes alignment and length. During wrapped transactions, access starts at the Command-Address selected location within the group, continues to the end of the configured word group aligned boundary, then wraps around to the beginning location in the group, then continues back to the starting location. Wrapped bursts are generally used for critical word first instruction or data cache line fill read accesses.

### 5.2.1.2 Hybrid Burst

The beginning of a hybrid burst will wrap within the target address wrapped burst group length before continuing to the next halfpage of data beyond the end of the wrap group. Continued access is in linear burst order until the transfer is ended by returning CS# high. This hybrid of a wrapped burst followed by a linear burst starting at the beginning of the next burst group, allows multiple sequential address cache lines to be filled in a single access. The first cache line is filled starting at the critical word. Then the next sequential line in memory can be read in to the cache while the first line is being processed.

Table 5.5

CR0[2]

Control of Wrapped Burst Sequence

| Bit | Default Value | Name                                                                                                                                                           |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   |               | Hybrid Burst Enable<br>CR[2]= 0: Wrapped burst sequences to follow hybrid burst sequencing<br>CR[2]= 1: Wrapped burst sequences in legacy wrapped burst manner |

Table 5.6

Example Wrapped Burst Sequences

| Burst S | Selection | Burst         | Wrap                            | Start            | Address Sequence (Hex)                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|-----------|---------------|---------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CA[45]  | CR0[2:0]  | Туре          | Boundary<br>(bytes)             | Address<br>(Hex) | (Words)                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0       | 000       | Hybrid<br>128 | 128 Wrap<br>once then<br>Linear | XXXXXX03         | 03, 04, 05, 06, 07, 08, 09, 0A, 0B, 0C, 0D, 0E, 0F, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A, 1B, 1C, 1D, 1E, 1F, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 2A, 2B, 2C, 2D, 2E, 2F, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 3A, 3B, 3C, 3D, 3E, 3F, 00, 01, 02 (wrap complete, now linear beyond the end of the initial 128 byte wrap group) 40, 41, 42, 43, 44, 45, 46, 47, 48, 49, 4A, 4B, 4C, 4D, 4E, 4F, 50, 51, |

| 0       | 001       | Hybrid 64     | 64 Wrap<br>once then<br>Linear  | XXXXXX03         | 03, 04, 05, 06, 07, 08, 09, 0A, 0B, 0C, 0D, 0E, 0F, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A, 1B, 1C, 1D, 1E, 1F, 00, 01, 02, (wrap complete, now linear beyond the end of the initial 64 byte wrap group) 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 2A, 2B, 2C, 2D, 2E, 2F, 30, 31,                                                                                                                                 |

| 0       | 001       | Hybrid 64     | 64 Wrap<br>once then<br>Linear  | XXXXXX2E         | 2E, 2F, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 3A, 3B, 3C, 3D, 3E, 3F, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 2A, 2B, 2C, 2D, (wrap complete, now linear beyond the end of the initial 64 byte wrap group) 40, 41, 42, 43, 44, 45, 46, 47, 48, 49, 4A, 4B, 4C, 4D, 4E, 4F, 50, 51,                                                                                                                                 |

| 0       | 010       | Hybrid 16     | 16 Wrap<br>once then<br>Linear  | XXXXXX02         | 02, 03, 04, 05, 06, 07, 00, 01,<br>(wrap complete, now linear beyond the end of the initial 16 byte wrap<br>group)<br>08, 09, 0A, 0B, 0C, 0D, 0E, 0F, 10, 11, 12,                                                                                                                                                                                                                                                    |

| 0       | 010       | Hybrid 16     | 16 Wrap<br>once then<br>Linear  | XXXXXX0C         | 0C, 0D, 0E, 0F, 08, 09, 0A, 0B,<br>(wrap complete, now linear beyond the end of the initial 16 byte wrap<br>group)<br>10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A,                                                                                                                                                                                                                                                    |

| 0       | 011       | Hybrid 32     | 32 Wrap<br>once then<br>Linear  | XXXXXX0A         | 0A, 0B, 0C, 0D, 0E, 0F, 00, 01, 02, 03, 04, 05, 06, 07, 08, 09,                                                                                                                                                                                                                                                                                                                                                      |

| 0       | 011       | Hybrid 32     | 32 Wrap<br>once then<br>Linear  | XXXXXX1E         | 1E, 1F, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A, 1B, 1C, 1D,                                                                                                                                                                                                                                                                                                                                                      |

| 0       | 100       | Wrap 128      | 128                             | XXXXXX03         | 03, 04, 05, 06, 07, 08, 09, 0A, 0B, 0C, 0D, 0E, 0F, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A, 1B, 1C, 1D, 1E, 1F, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 2A, 2B, 2C, 2D, 2E, 2F, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 3A, 3B, 3C, 3D, 3E, 3F, 00, 01, 02,                                                                                                                                                      |

| 0       | 101       | Wrap 64       | 64                              | XXXXXX03         | 03, 04, 05, 06, 07, 08, 09, 0A, 0B, 0C, 0D, 0E, 0F, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A, 1B, 1C, 1D, 1E, 1F, 00, 01, 02,                                                                                                                                                                                                                                                                                      |

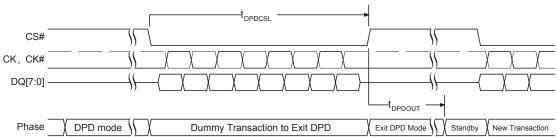

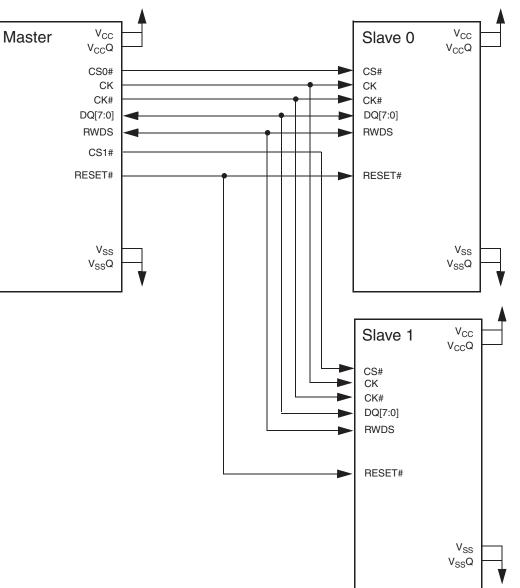

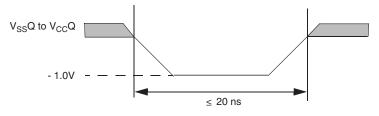

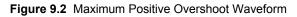

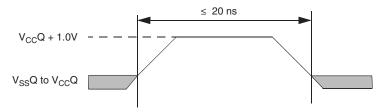

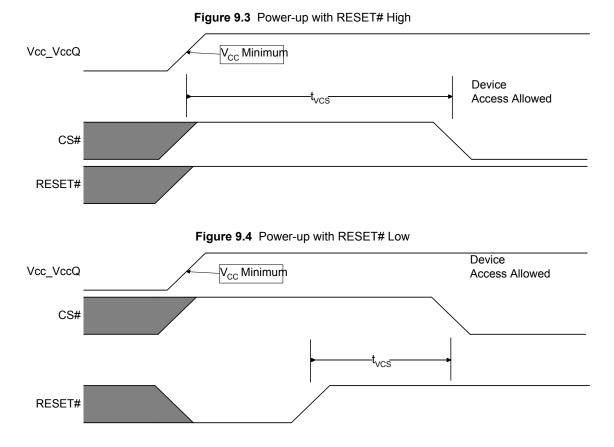

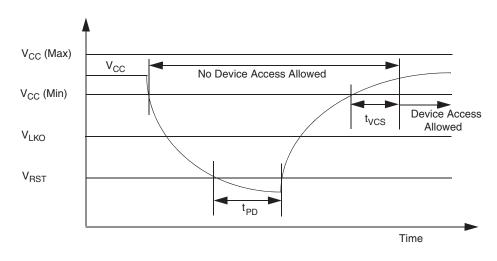

| 0       | 101       | Wrap 64       | 64                              | XXXXX2E          | 2E, 2F, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 3A, 3B, 3C, 3D, 3E, 3F, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 2A, 2B, 2C, 2D,                                                                                                                                                                                                                                                                                      |