# High Efficiency 4-CH LED Backlight Driver with Dual LCD Bias Power

# **Features**

## Backlight LED Driver

- Wide input range: 2.7V~5.5V

- High efficiency step-up LED driver with 4-Ch current sinks, up to 32V boost voltage.

- Up to 30mA/Ch in backlight mode

- ±0.7% current matching at 20mA

- ±2.2% current accuracy at 20mA

- I<sup>2</sup>C/PWM dual dimming control scheme

- High resolution I<sup>2</sup>C 11-bit linear or exponential dimming

- Wide range PWM dimming

- 100Hz to 100kHz frequency

- 0.2% to 100% duty cycle at 20kHz

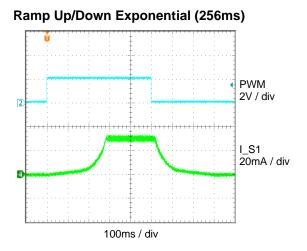

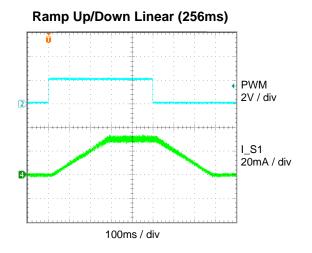

- Programmable current sink turn on/off ramp time/shape and transition ramp up/down time

- Selectable boost switching frequency 1.0MHz or 500kHz with Auto-Frequency Mode supported

- Programmable input PWM hysteresis to minimize jitter at low PWM duty cycle

- Programmable OVP and current limitation

- LED open/short protection

### > LCD Panel Bias

- Wide input range: 2.7V~5.5V

- Programmable dual output Bias regulator using a single inductor

- Programmable ramp time for OUTP and OUTN

- Charge pump PFM mode at light load

- LCD Bias efficiency: up to 85%

- Wide dual output voltage range ±4.0V to ±6.3V (50mV/step) and output current up to 120mA

- Active output discharge function

- Current limitation and short protection

#### > Others

- System level input UVLO

- Thermal shutdown protection

- Low shutdown current <1µA</li>

- Flexible I2C interface

- Pb-free Packages: WLCSP-24

- -40°C to +85°C Temperature Range

# **Applications**

• Smartphone/Tablet Backlight

# **Brief Description**

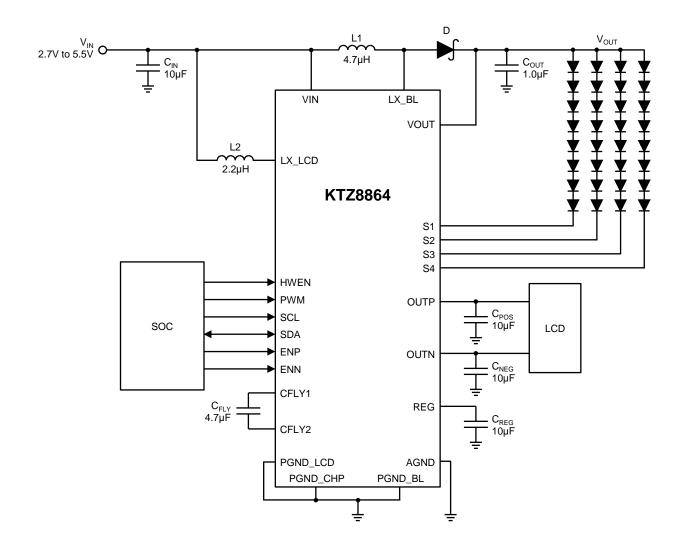

KTZ8864 is the ideal power solution for LED backlighting and LCD bias power of small and medium size panels. It integrates a step-up converter for LED backlighting, a step-up converter with LDO and inverting charge pump for LCD bias power, resulting in a simpler and smaller solution with fewer external components. High switching frequency allows the use of a smaller inductor and capacitor. Its input operating range is from 2.7V to 5.5V, accommodating 1-cell lithium ion batteries or 5V supply.

The LED driver's four regulated current sinks can regulate up to 30mA with its maximum boost output voltage up to 32V. 11-bit linear or exponential  $I_{LED}$  resolution can be obtained over  $I^2C$  or PWM dimming. For additional flexibility, PWM dimming offers wide range frequency and duty cycle to support Content Adaptive Brightness Control (CABC).

The LCD bias power section includes a step-up converter, LDO and an inverting charge pump to generate dual outputs, OUTP and OUTN, whose voltages can be programmed via an I<sup>2</sup>C interface. By integrating synchronous rectification MOSFETs for the step-up converter and charge pump, the KTZ8864 maximizes conversion efficiency up to 85%.

Various protection features are built into KTZ8864, including inductor current limit protection, output short circuit protection, output over-voltage protection, LED fault (open or short) protection and thermal shutdown protection.

KTZ8864 is equipped with I<sup>2</sup>C interface for various controls and status monitor.

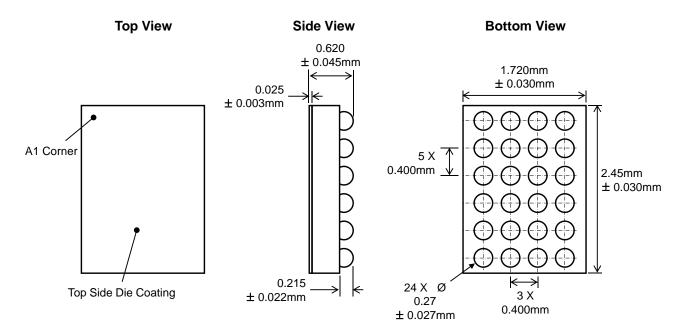

KTZ8864 is available in a RoHS compliant 24-ball 1.72mm x 2.45mm x 0.62mm WLCSP.

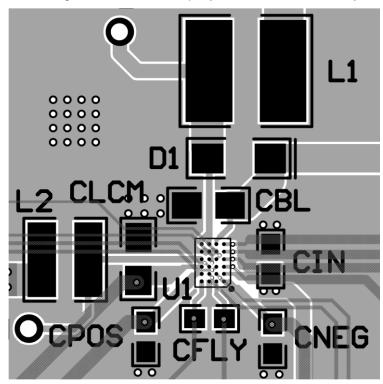

# **Typical Application**

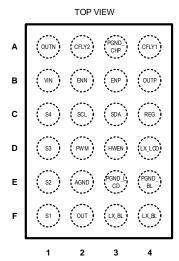

# **Pin Descriptions**

| Pin#   | Name     | Function                                                                                        |  |  |  |

|--------|----------|-------------------------------------------------------------------------------------------------|--|--|--|

| A1     | OUTN     | Charge pump output pin of the negative power. Bypass with a 10µF ceramic capacitor to PGND_CHP. |  |  |  |

| A2     | CFLY2    | Negative charge pump flying capacitor negative connection.                                      |  |  |  |

| А3     | PGND_CHP | Power ground for negative charge pump.                                                          |  |  |  |

| A4     | CFLY1    | Negative charge pump flying capacitor pin positive connection.                                  |  |  |  |

| B1     | VIN      | Input supply pin for the IC, bypass with a 10µF ceramic capacitor to GND.                       |  |  |  |

| B2     | ENN      | Enable pin for negative power (OUTN), 300KΩ pull down resistor to GND                           |  |  |  |

| B3     | ENP      | Enable pin for positive power (OUTP), 300KΩ pull down resistor to GND                           |  |  |  |

| B4     | OUTP     | LDO output pin of the positive power, bypass with a 10µF ceramic capacitor.                     |  |  |  |

| C1     | S4       | Regulated output current sink #4.                                                               |  |  |  |

| C2     | SCL      | Clock of the I <sup>2</sup> C interface.                                                        |  |  |  |

| C3     | SDA      | Bi-directional data pin of the I <sup>2</sup> C interface.                                      |  |  |  |

| C4     | REG      | LCD-Bias Boost converter output pin, bypass a 10µF ceramic capacitor to PGND_LCD                |  |  |  |

| D1     | S3       | Regulated output current sink #3.                                                               |  |  |  |

| D2     | PWM      | PWM dimming input pin, 300kΩ pull-down resistor at this pin to GND.                             |  |  |  |

| D3     | HWEN     | Active high hardware enable pin, 400kΩ pull-down resistor to GND.                               |  |  |  |

| D4     | LX_LCD   | Switching node of the LCD Bias boost converter.                                                 |  |  |  |

| E1     | S2       | Regulated output current sink #2.                                                               |  |  |  |

| E2     | AGND     | Analog ground pin.                                                                              |  |  |  |

| E3     | PGND_LCD | Power ground for LCD Bias power supply boost converter.                                         |  |  |  |

| E4     | PGND_BL  | Power Ground for LED boost converter.                                                           |  |  |  |

| F1     | S1       | Regulated output current sink #1.                                                               |  |  |  |

| F2     | VOUT     | Output voltage sense pin of the step-up converter.                                              |  |  |  |

| F3, F4 | LX_BL    | Switching pin of the LED step-up converter.                                                     |  |  |  |

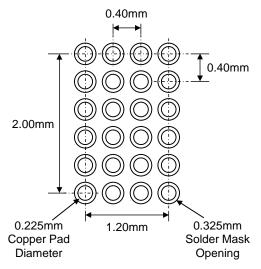

# **WLCSP46-24**

# 24-Bump 1.72mm x 2.45mm x 0.62mm WLCSP Package

Top Mark

WW = Device ID Code, XX = Date Code

YY = Assembly Code, ZZZZ = Serial Number

# Absolute Maximum Ratings<sup>1</sup>

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

| Symbol                                                    | Description                                               | Value           | Units |

|-----------------------------------------------------------|-----------------------------------------------------------|-----------------|-------|

| VIN                                                       | Input Voltage                                             | -0.3 to 6       | V     |

| LX_BL, VOUT                                               | LED Backlight driver switching node and output node       | -0.3 to 35      | V     |

| S1, S2, S3, S4                                            | LED Backlight driver current sink                         | -0.3 to 32      | V     |

| HWEN, SCL, SDA, PWM,<br>ENP, ENN                          | Control Pins                                              | -0.3 to VIN+0.3 | V     |

| LX_LCD, CFLY1, OUTP, REG                                  | , REG LCD Bias power positive voltage and switching node  |                 | V     |

| OUTN, CFLY2                                               | LCD Bias power negative output voltage and switching node | -7 to 0.3       | V     |

| TJ                                                        | Junction Operating Temperature Range                      | -40 to 150      | °C    |

| Ts                                                        | Storage Temperature Range                                 | -65 to 150      | °C    |

| T <sub>LEAD</sub> Maximum Soldering Temperature (at least |                                                           | 300             | °C    |

| ESD                                                       | HBM Electrical Static Discharge                           | 2.0             | kV    |

# **ESD Ratings**

| Symbol | Description                                                    | Value | Units |

|--------|----------------------------------------------------------------|-------|-------|

| VESD   | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001             | ±2000 | V     |

| VESD   | Charge device model (CDM), per JEDEC specification JESD22-C101 | ±500  | V     |

# Thermal Capabilities<sup>2</sup>

| Symbol                | Description                                        | Value  | Units |

|-----------------------|----------------------------------------------------|--------|-------|

| θЈА                   | Thermal Resistance – Junction to Ambient           | 70.3   | °C/W  |

| PD                    | Maximum Power Dissipation at T <sub>A</sub> ≤ 25°C | 1778   | mW    |

| $\Delta P_D/\Delta T$ | Derating Factor Above T <sub>A</sub> = 25°C        | -14.22 | mW/°C |

# **Ordering Information**

| Part Number    | Marking <sup>3</sup> | Operating<br>Temperature | Package  |  |

|----------------|----------------------|--------------------------|----------|--|

| KTZ8864EJAA-TR | NDXXYYZZZZ           | -40°C to +85°C           | WLCSP-24 |  |

December 2019 - Revision 04d Page 4 Company Confidential

Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>2.</sup> Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board.

<sup>3. &</sup>quot;WWXXYYZZZZ" is the device code, date code, assembly code and serial number.

# Electrical Characteristics<sup>4</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C, while *Typ* values are specified at room temperature (25°C).  $V_{IN} = 3.6$ V.

| Symbol               | Description                                                                                                  | Conditions                                                                           | Min  | Тур   | Max  | Units |

|----------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------|-------|------|-------|

| IC Supply            | •                                                                                                            |                                                                                      |      |       |      |       |

| V <sub>IN</sub>      | Input operating range                                                                                        |                                                                                      | 2.7  |       | 5.5  | V     |

| UVLO                 | Input under voltage lockout                                                                                  | Rising edge                                                                          |      | 2.45  | 2.65 | V     |

| UVLO <sub>HYST</sub> | UVLO hysteresis                                                                                              |                                                                                      |      | 0.05  |      | V     |

| ΙQ                   | IC standby current                                                                                           | HWEN = V <sub>IN</sub> , LCD Boost disabled,<br>LED Boost and Current Sink disabled. |      | 1     | 7    | μΑ    |

| I <sub>LCD_EN</sub>  | Bias power no load current                                                                                   | LED Boost and Current Sink disabled. OUTP, OUTN enabled with no load.                |      | 1.1   | 1.3  | mA    |

| I <sub>SHDN</sub>    | IC shutdown V <sub>IN</sub> current                                                                          | HWEN = 0, ENP = ENN = GND                                                            |      | 1     | 3    | μΑ    |

| <b>Boost Conv</b>    | erter for LED Backlight                                                                                      |                                                                                      |      |       |      |       |

| R <sub>DS(ON)</sub>  | NMOS on-resistance                                                                                           | Isw = 250mA                                                                          |      | 0.2   |      | Ω     |

| I <sub>LIM</sub>     | Peak NMOS current limit                                                                                      | Reg 0x11[1:0]=00, T <sub>A</sub> = 25°C                                              | 1.02 | 1.2   | 1.38 | Α     |

| E                    | Oscillator frequency                                                                                         | Reg 0x03[7]=0, T <sub>A</sub> = 25°C                                                 | 0.45 | 0.5   | 0.55 | MHz   |

| F <sub>SW</sub>      | Oscillator frequency                                                                                         | Reg 0x03[7]=1, default, T <sub>A</sub> = 25°C                                        | 0.9  | 1.0   | 1.1  | MHz   |

| EFFLEDBST            | Boost Efficiency  V <sub>IN</sub> = 3.6V, I <sub>LED</sub> = 5mA/ch, 4P6S LEDS, Typical application circuit. |                                                                                      |      | 87    |      | %     |

| $D_{MAX}$            | Maximum duty cycle FSW = 1MHz                                                                                |                                                                                      |      | 94    |      | %     |

|                      |                                                                                                              | Reg 0x02[7:5]=011, T <sub>A</sub> = 25°C                                             | 27.8 | 29    | 30.2 | V     |

|                      | OVP threshold                                                                                                | Reg 0x02[7:5]=010, T <sub>A</sub> = 25°C                                             | 23.9 | 25    | 26.1 | V     |

| $V_{OVP}$            |                                                                                                              | Reg 0x02[7:5]=001, default, T <sub>A</sub> = 25°C                                    | 20.1 | 21    | 21.9 | V     |

|                      |                                                                                                              | Reg 0x02[7:5]=000, T <sub>A</sub> = 25°C                                             | 16.2 | 17    | 17.8 | V     |

|                      | OVP hysteresis                                                                                               |                                                                                      |      | 2     |      | V     |

| <b>Current Sin</b>   | k for LED Backlight                                                                                          |                                                                                      |      |       |      |       |

|                      |                                                                                                              | Current setting = 30mA, T <sub>A</sub> = 25°C                                        | -2.0 |       | 2.0  | %     |

| Isink_acc            | Output current accuracy                                                                                      | Current setting = 20mA, T <sub>A</sub> = 25°C                                        | -2.2 |       | 2.2  | %     |

|                      |                                                                                                              | Current setting = 1mA, T <sub>A</sub> = 25°C                                         | -3.0 |       | 3.0  | %     |

|                      |                                                                                                              | Current setting = 30mA, T <sub>A</sub> = 25°C                                        | -0.7 |       | 0.7  | %     |

| ISINK_MATCH          | Output current matching <sup>5</sup>                                                                         | Current setting = 20mA, T <sub>A</sub> = 25°C                                        | -0.7 |       | 0.7  | %     |

|                      |                                                                                                              | Current setting = 1mA, T <sub>A</sub> = 25°C                                         | -1.5 |       | 1.5  | %     |

| $V_{HR}$             | Current sink head room voltage                                                                               |                                                                                      |      | 0.45  |      | V     |

| ILED_MIN             | Minimum LED current per string                                                                               | Linear or Exponential mapping                                                        |      | 60    |      | μA    |

|                      | LED stop size                                                                                                | Exponential Mode                                                                     |      | 0.3   |      | %     |

| I <sub>STEP</sub>    | LED step size                                                                                                | Linear Mode                                                                          |      | 14.63 |      | μΑ    |

| Vsov                 | Current sink over voltage threshold                                                                          |                                                                                      |      | 6     |      | V     |

| TFAULT               | Current sink fault delay                                                                                     |                                                                                      |      | 59    |      | ms    |

December 2019 - Revision 04d Page 5 Company Confidential

<sup>4.</sup> KTZ8864 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range by design, characterization and correlation with statistical process controls.

<sup>5.</sup> The current matching among channels is defined as  $|I_{SINK}-I_{AVG}|_{MAX}/I_{AVG}$ .

# Electrical Characteristics<sup>4</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C, while *Typ* values are specified at room temperature (25°C).  $V_{IN} = 3.6$ V.

| Symbol                                             | Description                          | Conditions                                                                         | Min  | Тур | Max  | Units |

|----------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------|------|-----|------|-------|

| Boost Conve                                        | erter for LCD Power Bias             |                                                                                    | •    | •   |      | •     |

| M                                                  | LCD boost output voltage range       |                                                                                    | 4    |     | 6.6  | V     |

| V <sub>REG</sub> LCD boost output voltage step siz |                                      |                                                                                    |      | 50  |      | mV    |

| I <sub>REG_LIM</sub>                               | Peak current limit                   |                                                                                    |      | 1.0 |      | Α     |

| Fsw                                                | Oscillator frequency                 | Continuous Mode                                                                    |      | 2.0 |      | MHz   |

| EFFLCDBST                                          | Efficiency                           | VIN = 3.6 V, VREG_OUT = 5.9 V,<br>6mA < lo < 160mA, Typical<br>application circuit |      | 85  |      | %     |

| R <sub>ON_HS</sub>                                 | High side FET on resistance          | VIN = 3.6V                                                                         |      | 340 |      | mΩ    |

| R <sub>ON_LS</sub>                                 | Low side FET on resistance           | VIN = 3.6V                                                                         |      | 200 |      | mΩ    |

| V <sub>REG_PP</sub>                                | LCD boost output ripple              | $Io = 5mA$ and $50mA$ , $Co = 10\mu F$                                             |      | 50  |      | mV    |

| $D_{MAX}$                                          | Maximum duty cycle                   |                                                                                    | 80   | 86  |      | %     |

| OUTP-Positiv                                       | ve Output                            |                                                                                    |      |     |      |       |

|                                                    | Positive output voltage range        |                                                                                    | 4.0  |     | 6.3  | V     |

| OUTP                                               | Output voltage step size             |                                                                                    |      | 50  |      | mV    |

|                                                    | Output voltage accuracy              | $V_{\text{OUTP}} = 5.5V$ , no load                                                 | -1.5 |     | +1.5 | %     |

| IOUTP_MAX                                          | Maximum output current limit         |                                                                                    | 120  |     |      | mA    |

| IOUTP_LIM                                          | Positive output current limit        |                                                                                    |      | 180 |      | mA    |

| VOUTP_LO<br>REG                                    | VOUTP LDO load regulation            | 0 ≤ lo ≤ IOUTP_MAX                                                                 |      | 50  |      | mV    |

| VOUTP_DO                                           | VOUTP LDO dropout voltage            |                                                                                    |      |     | 160  | mV    |

| TOUTP_SS                                           | Startup time                         | Co = 10µF, VOUTP = 5.75V,<br>VPOS_RAMP = 2b'01                                     |      | 456 |      | μs    |

| RPD_OUTP                                           | Output pulldown resistor in shutdown |                                                                                    | 40   | 70  | 100  | Ω     |

| OUTN-Negat                                         | ive Output                           |                                                                                    |      | •   |      |       |

|                                                    | Negative output voltage range        |                                                                                    | -6.3 |     | -4.0 | V     |

| OUTN                                               | Output voltage step size             |                                                                                    |      | 50  |      | mV    |

|                                                    | Output voltage accuracy              | Voutn = -5.4V, no load                                                             | -1.5 |     | +1.5 | %     |

| IOUTN_MAX                                          | Maximum output current limit         |                                                                                    | 120  |     |      | mA    |

| EFF <sub>CHP</sub>                                 | Inverting charge pump efficiency     | $V_{REG} = 5.7 \text{ V}, V_{OUTN} = -5.4 \text{V},$ $I_{OUTN} > -5 \text{mA}$     |      | 85  |      | %     |

| Voutn_pp                                           | Inverting charge pump output ripple  | Io = 0mA, Co = 10μF                                                                |      | 60  |      | mV    |

| T <sub>OUTN_</sub> ss                              | Startup time                         | Co = 10μF, V <sub>OUTN</sub> = -5.75V,<br>VNEG_RAMP = 4b'0001                      |      | 912 |      | μs    |

| R <sub>PD_OUTN</sub>                               | Output pulldown resistor in shutdown |                                                                                    |      | 22  | 35   | Ω     |

# Electrical Characteristics<sup>4</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C, while *Typ* values are specified at room temperature (25°C).  $V_{IN} = 3.6$ V.

| Symbol                    | Description                               | Conditions                       | Min | Тур | Max | Units |

|---------------------------|-------------------------------------------|----------------------------------|-----|-----|-----|-------|

| PWM INPUT                 |                                           |                                  | •   | •   |     |       |

| f <sub>PWM_INPUT</sub>    | PWM input frequency                       |                                  | 0.1 |     | 100 | kHz   |

| t <sub>MIN_ON</sub>       | Minimum pulse ON time                     |                                  |     | 150 |     | ns    |

| t <sub>MIN_OFF</sub>      | Minimum pulse OFF time                    |                                  |     | 150 |     | ns    |

| PWMRES                    | PWM input resolution                      | 100Hz < f <sub>PWM</sub> < 10KHz |     | 11  |     | bit   |

| I <sup>2</sup> C-Compatik | ole Voltage Specifications (SCL, SDA, ENI | P, ENN, PWM, HWEN)               | •   | •   |     |       |

| VIL                       | Input Logic Low Threshold                 |                                  |     |     | 0.4 | V     |

| V <sub>IH</sub>           | Input Logic High Threshold                |                                  | 1.2 |     |     | V     |

| V <sub>OL</sub>           | SDA Output Logic Low                      | I <sub>SDA</sub> = 3mA           |     |     | 0.4 | V     |

| RPD <sub>HWEN</sub>       | Pulldown resistance on HWEN pin           |                                  |     | 300 |     | ΚΩ    |

| RPD <sub>PWM</sub>        | Pulldown resistance on PWM pin            |                                  |     | 300 |     | ΚΩ    |

| RPDENP                    | Pulldown resistance on ENP pin            |                                  |     | 300 |     | ΚΩ    |

| $RPD_{ENN}$               | Pulldown resistance on ENN pin            |                                  |     | 300 |     | ΚΩ    |

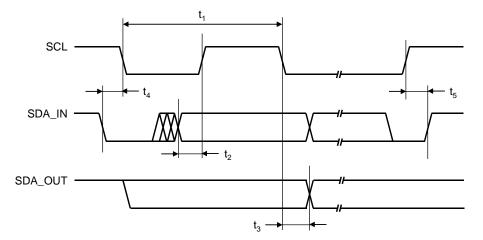

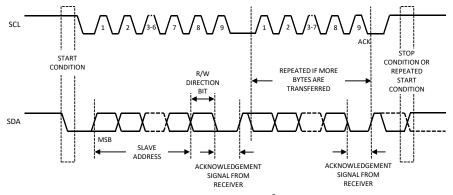

| I <sup>2</sup> C-Compatik | ole Timing Specifications (SCL, SDA), see | Figure 1                         |     |     |     |       |

| t <sub>1</sub>            | SCL clock period                          |                                  | 2.5 |     |     | μs    |

| t <sub>2</sub>            | Data in setup time to SCL high            |                                  | 100 |     |     | ns    |

| t <sub>3</sub>            | Data out stable after SCL low             |                                  | 0   |     |     | ns    |

| t <sub>4</sub>            | SDA low setup time to SCL low (Start)     |                                  | 100 |     |     | ns    |

| <b>t</b> 5                | SDA high hold time after SCL high (Stop)  |                                  | 100 |     |     | ns    |

| Thermal Shu               | tdown                                     |                                  |     |     |     |       |

| $T_{J-TH}$                | IC thermal shutdown threshold             |                                  |     | 150 |     | °C    |

| I J-I H                   | IC thermal shutdown hysteresis            |                                  |     | 15  |     | °C    |

Figure 1. I<sup>2</sup>C Compatible Interface Timing

## **LED Backlight**

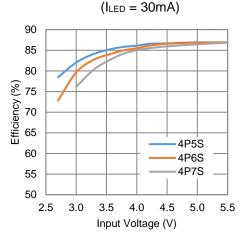

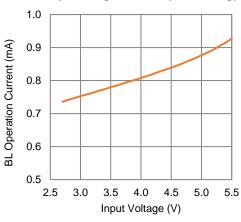

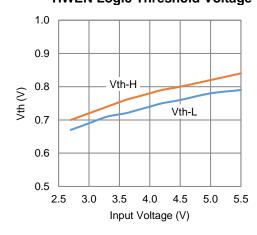

$V_{IN} = 3.6V$ , 4P7S LEDs,  $I_{LED} = 30$ mA,  $L = 4.7\mu$ H (TDK VLF504012MT-4R7M-CA),  $C_{IN} = 10\mu$ F,  $C_{OUT} = 1\mu$ F,  $I^2$ C register default settings, Temp = 25°C unless otherwise specified.

# LED Driver Efficiency vs. VIN

# **Operating Current (Switching)**

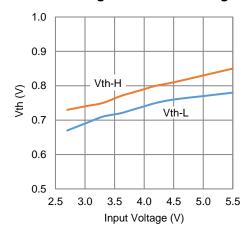

# **HWEN Logic Threshold Voltage**

## LED Driver Efficiency vs. IOUT

# Switching Frequency vs. VIN

# **PWM Logic Threshold Voltage**

$V_{IN} = 3.6V$ , 4P7S LEDs,  $I_{LED} = 30$ mA,  $L = 4.7\mu$ H (TDK VLF504012MT-4R7M-CA),  $C_{IN} = 10\mu$ F,  $C_{OUT} = 1\mu$ F,  $I^2$ C register default settings, Temp = 25°C unless otherwise specified.

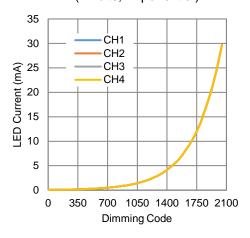

# LED Current vs. Current Ratio Code (11 bits, Exponential)

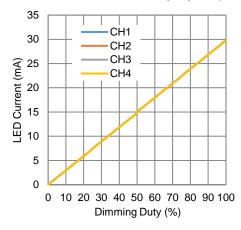

### LED Current vs. PWM Duty Cycle (20kHz)

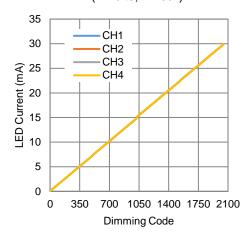

# LED Current vs. Current Ratio Code (11 bits, Linear)

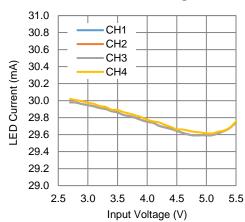

### **LED Current Line Regulation**

$V_{IN}=3.6V$ , 4P7S LEDs,  $I_{LED}=30mA$ ,  $L=4.7\mu H$  (TDK VLF504012MT-4R7M-CA),  $C_{IN}=10\mu F$ ,  $C_{OUT}=1\mu F$ ,  $I^2C$  register default settings, Temp = 25°C unless otherwise specified.

$V_{IN} = 3.6V$ , 4P7S LEDs,  $I_{LED} = 30$ mA,  $L = 4.7\mu$ H (TDK VLF504012MT-4R7M-CA),  $C_{IN} = 10\mu$ F,  $C_{OUT} = 1\mu$ F,  $I^2$ C register default settings, Temp = 25°C unless otherwise specified.

Inductor

Current 500mA / div

# **Steady State Switching** LX\_BL 20V / div VOUT (AC) 500mV / div

1µs / div

**PWM Dimming (20kHz)**

40µs / div

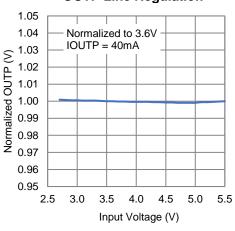

# Turn On with LED Open (OVP = 32V)

Turn On with LED Open (OVP = 21V)

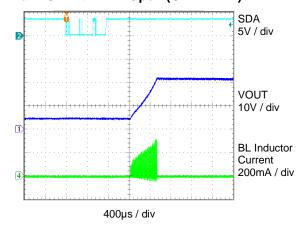

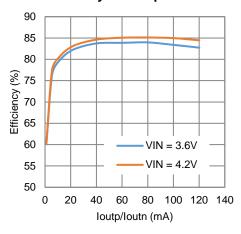

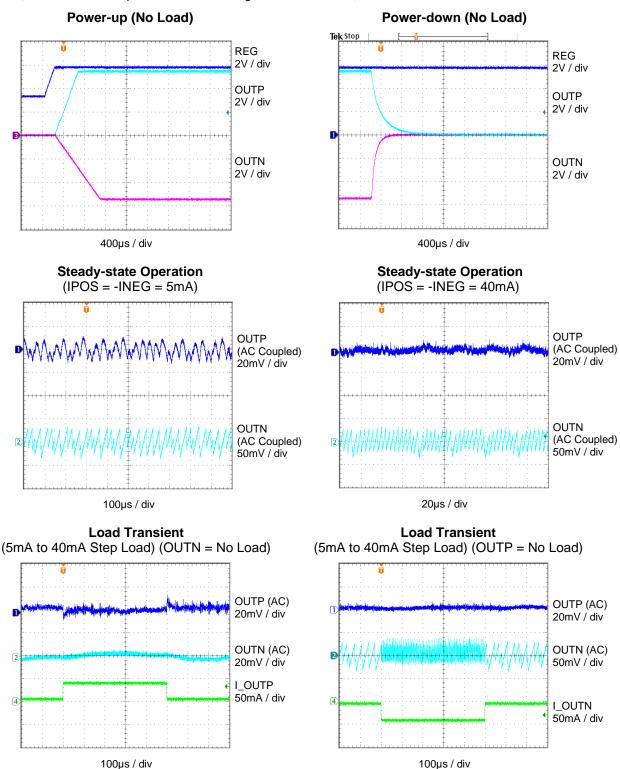

#### **LCD Bias**

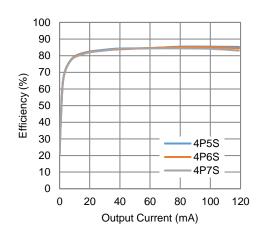

$V_{IN}=3.6V$ , L = 2.2 $\mu$ H (TOKO DFE201612P-2R2M=P2),  $C_{IN}=C_{REG}=C_{POS}=C_{NEG}=C_{FLY}=10\mu F$ ,  $I_{POS}=-I_{NEG}=40mA$ ,  $I_{A}=25^{\circ}C$ , unless otherwise specified. Default setting  $I_{POS}/I_{NEG}=\pm5.5V$ ,  $I_{REG}=5.8V$ .

## **Efficiency vs. Output Current**

# **OUTP Line Regulation**

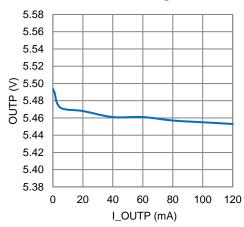

### **OUTP Load Regulation**

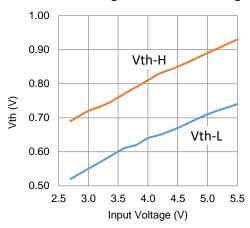

## **ENP/ENN Logic Threshold Voltage**

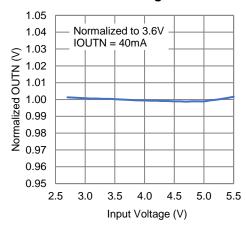

# **OUTN Line Regulation**

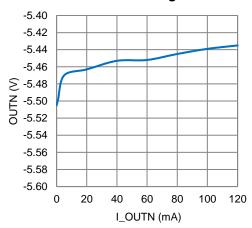

### **OUTN Load Regulation**

$V_{IN} = 3.6 \text{V}$ , L = 2.2 $\mu$ H (TOKO DFE201612P-2R2M=P2),  $C_{IN} = C_{REG} = C_{POS} = C_{NEG} = C_{FLY} = 10 \mu$ F,  $I_{POS} = -I_{NEG} = 40 \text{mA}$ ,  $I_{A} = 25 \text{°C}$ , unless otherwise specified. Default setting  $I_{POS}/I_{NEG} = \pm 5.5 \text{V}$ ,  $I_{REG} = 5.8 \text{V}$ .

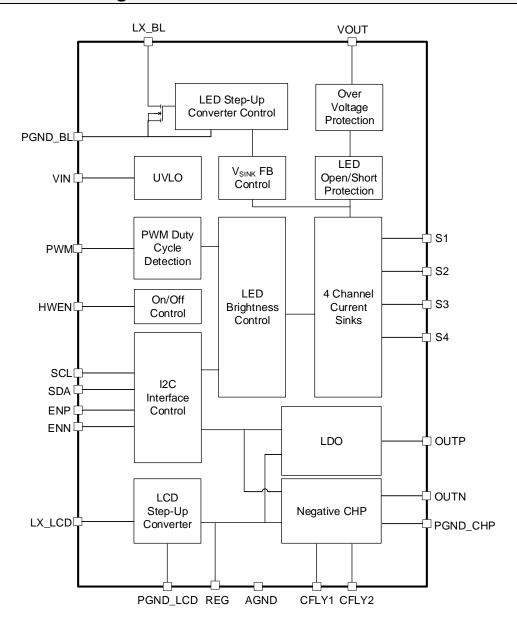

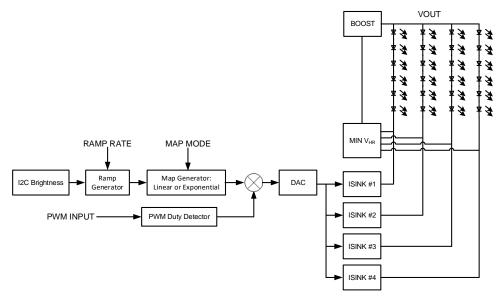

# **Functional Block Diagram**

# **Functional Description**

#### Overview

KTZ8864 is the ideal power solution for LED backlighting and LCD bias power of small and medium size panels. It integrates a step-up converter for LED backlighting, a step-up converter with LDO and inverting charge pump for LCD bias power, resulting in a simpler and smaller solution with fewer external components. High switching frequency allows the use of smaller inductors and capacitors. Its operating input ranges from 2.7V to 5.5V, accommodating 1-cell lithium ion batteries or 5V supply.

The LED driver's four regulated current sinks can regulate up to 30mA in backlight mode with its maximum boost output voltage up to 32V. 11bit linear or exponential I<sub>LED</sub> resolution can be obtained over I<sup>2</sup>C or PWM diming. For additional flexibility, PWM dimming offers wide range frequency and duty cycle to support Content Adaptive Brightness Control (CABC).

The LCD bias power includes a step-up converter, LDO and an inverting charge pump to generate dual outputs, OUTP and OUTN, whose voltages can be programmed via an I<sup>2</sup>C interface. By integrating synchronous rectification MOSFETs for the step-up converter and charge pump, the KTZ8864 maximizes conversion efficiency up to 85%.

Various protection features are built into KTZ8864, including inductor current limit protection, output short circuit protection, output over-voltage protection, LED fault (open or short) protection and thermal shutdown protection. KTZ8864 is equipped with I<sup>2</sup>C interface for various controls and status monitor.

#### **Hardware Enable & Standby Mode**

KTZ8864 has a logic input HWEN pin to enable/disable the device. When HWEN is set low, the device goes into shutdown mode, all I<sup>2</sup>C registers are reset to default, and the I<sup>2</sup>C interface is disabled. Under this condition, the device does not respond to any I<sup>2</sup>C command. Even when SCL/SDA's pull up voltage is much less than VIN voltage, it will not cause any extra leakage current.

When HWEN is set high, the device goes into standby mode, the I<sup>2</sup>C interface is enabled, and the device can respond to I<sup>2</sup>C command. Under this condition, if SCL/SDA's pull up voltage is much less than VIN voltage, it can cause a small leakage current from VIN. For example, if VIN = 4.2V and SCL/SDA's pull up voltage is 1.8V, there will be around 6.8µA additional leakage current from VIN in this standby mode.

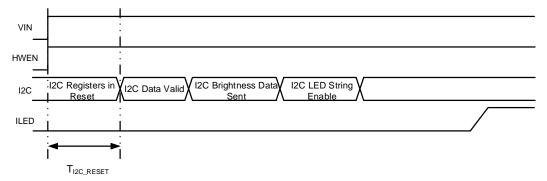

Based on HWEN's connection, there are two kinds of power-up sequences as below

- If HWEN is tied to VIN, once VIN goes above around 2.0V, HWEN should stay high for at least T<sub>I2C RESET</sub> = 150μs time before any I<sup>2</sup>C command can be accepted.

- If HWEN is driven by a GPIO, once HWEN goes from low to high, HWEN should stay high for at least T<sub>I2C\_RESET</sub> = 150μs time before receiving any I<sup>2</sup>C command.

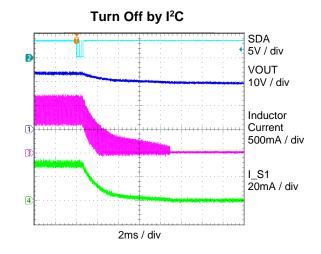

Either HWEN input or I<sup>2</sup>C command can be used to turn off the part, but there are some differences.

- If setting HWEN input low to turn off the part, the I<sub>LED</sub> will be turned off immediately without any ramp down control. After that, the I<sup>2</sup>C interface is disabled.

- If using an I<sup>2</sup>C command to turn off backlight while keeping HWEN high, the I<sub>LED</sub> will have ramp down control. After the LED current ramp down is finished, the I<sup>2</sup>C interface is still alive waiting for new command.

#### **Backlight Boost**

A step-up converter is used to generate high voltage for driving LED strings. An adaptive control method automatically adjusts output voltage by monitoring the headroom voltage of current sinks. In this way, KTZ8864 can offer much better efficiency. KTZ8864 Backlight Boost has three switching frequencies, 1.0MHz, 500kHz, and 250kHz, selected by setting register 0x03 bit [7] in combination with auto-frequency registers 0x06 and 0x07.

### **Backlight Current Sink Setting**

Each current sink can be enabled or disabled by register 0x08 bits [3:0]. They can be enabled by writing the backlight enable bit to HIGH in register 0x08 bit [4] after correctly setting of LED configuration and brightness. If a current sink is not used, connect its output to GND. During the startup, KTZ8864 will automatically detect and disable the corresponding channel.

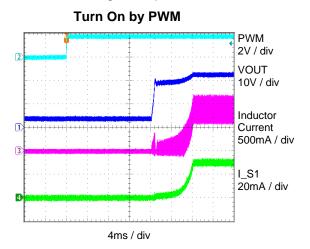

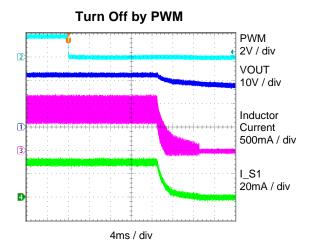

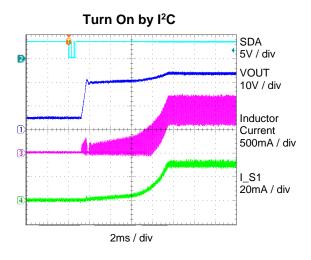

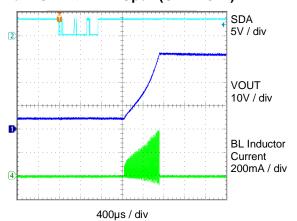

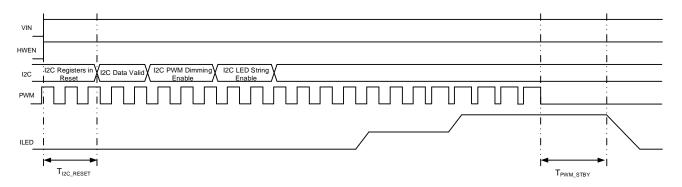

When PWM dimming is enabled and a non-zero PWM duty cycle is detected, the KTZ8864 multiplies the duty cycle with I<sup>2</sup>C brightness settings. Figure 2 and Figure 3 describe the start-up timing for operation with I<sup>2</sup>C controlled current and with PWM controlled current.

Figure 2. Enable of KTZ8864 via I<sup>2</sup>C

Figure 3. Enable of KTZ8864 via PWM

# **Operating Mode Description**

The KTZ8864 backlight can operate in different modes, see Table 1 below

**Table 1. Backlight Operating Modes**

| HWEN | BL_EN<br>0x08[4] | PWM<br>INPUT | I2C<br>BRIGHTNESS<br>0X05[7:0]<br>0X04[2:0] | CURRENT<br>SINKs<br>ENABLEs<br>0x08[3:0] | PWM_EN<br>0x02[0] | FEEDBACK<br>DISABLEs<br>0x10[6:3] | MAPPING MODE<br>0x02[3]                                                                        | ACTION                                                                                            |

|------|------------------|--------------|---------------------------------------------|------------------------------------------|-------------------|-----------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 0    | Х                | Х            | X                                           | Х                                        | Х                 | Χ                                 | Х                                                                                              | Shutdown                                                                                          |

| 1    | 0                | Х            | Х                                           | Х                                        | Х                 | Х                                 | Х                                                                                              | Standby <sup>6</sup>                                                                              |

| 1    | 1                | Х            | 0x000                                       | 0000                                     | Х                 | Х                                 | Х                                                                                              | Standby <sup>6</sup>                                                                              |

| 1    | 1                | х            | ≥0x001                                      | ≥0001                                    | 0                 | <1111                             | 0 = Exp. Mode<br>1 = Lin. Mode                                                                 | -Backlight boost enabled<br>-Selected current sink(s) enabled<br>-l <sup>2</sup> C control only   |

| 1    | 1                | Duty = 0     | X                                           | ≥0001                                    | 1                 | <1111                             | Х                                                                                              | Standby <sup>6</sup>                                                                              |

| 1    | 1                | Duty > 0     | ≥0x001                                      | ≥0001                                    | 1                 | <1111                             | 0 = Exp. Mode<br>1 = Lin. Mode<br>-Selected current sink(s)<br>-I <sup>2</sup> C × PWM control |                                                                                                   |

| 1    | 1                | Duty > 0     | ≥0x001                                      | ≥0001                                    | 1                 | 1111                              | 0 = Exp. Mode<br>1 = Lin. Mode                                                                 | -Backlight boost disabled<br>-Selected current sink(s) enabled<br>-I <sup>2</sup> C × PWM control |

December 2019 - Revision 04d Page 16 Company Confidential

Standby signifies that the backlight boost and current sinks are shut down. Register writes are still possible. Shutdown signifies that that

the device was reset and no I<sup>2</sup>C communication is accepted.

## **Backlight LED Current**

The LED current is always a DC current (not PWM). It can be programmed for either exponential mapping mode or linear mapping mode by Register 0x02 bit [3]. These two modes determine the transfer characteristic of dimming code to LED current. It also has 11-bit control, including the 8-bit MSBs from register 0x05 bits [7:0] and the 3-bit LSBs from register 0x04 bits [2:0]. If only 8-bit dimming is needed, the 3-bit LSBs should be kept as '111' while the 8-bit MSBs are programmed. If 11-bit dimming ratio is needed, the 3-bit LSBs should be programmed first, then the 8-bit MSBs are programmed. Only programming the 3-bit LSBs doesn't change the current ratio until the 8-bit MSBs are programmed.

In linear mapping 8-bit dimming mode, the LED current per channel can be calculated as:

$$I_{LED\_BL} = I_{LED\_FS} * D_{PWM} * \left(\frac{3}{2050} + \frac{Code * 8 + 7}{2050}\right), \quad (Code = 0 \sim 255)$$

where I<sub>LED\_FS</sub> is the backlight full-scale LED current which is programmed by 0x15 bits [7:3], ranges from 5.2mA to 30mA with 0.8mA step, D<sub>PWM</sub> is the input PWM duty cycle if PWM dimming is enabled, otherwise D<sub>PWM</sub> = 1.

In linear mapping 11-bit dimming mode, the LED current per channel can be calculated as:

$$I_{LED\_BL} = I_{LED\_FS} * D_{PWM} * \left(\frac{3}{2050} + \frac{Code}{2050}\right),$$

(Code = 1~2047)

For linear mapping 11-bit dimming's Code 0, current sink and boost converter will be disabled, LED will be turned off

In exponential mapping 8-bit dimming mode, the LED current per channel can be calculated as:

$$I_{LED\_BL} = I_{LED\_FS} * D_{PWM} * \frac{1.003040572^{(Code*8+7)}}{500} \quad (Code = 0 \sim 255)$$

In exponential mapping 11-bit dimming mode, the LED current per channel can be calculated as:

$$I_{LED\_BL} = I_{LED\_FS} * D_{PWM} * \frac{1.003040572^{Code}}{500} \quad (Code = 1 \sim 2047)$$

For exponential mapping 11-bit dimming's Code 0, current sink and boost converter will be disabled, LED will be turned off.

#### **Backlight Brightness Control Mode**

KTZ8864 has two brightness control mode, I<sup>2</sup>C Only Mode and I<sup>2</sup>C x PWM Mode, see Figure 4. In I<sup>2</sup>C Only Mode, register 0x02's bit [0] PWM\_ENABLE should be set to "0", the LED brightness is controlled by registers 0x04 and 0x05. In I<sup>2</sup>C x PWM Mode, register 0x02's bit [0] PWM\_ENABLE should be set to "1", the LED brightness will be controlled by I<sup>2</sup>C code and PWM duty together.

If the LED current is changed from one value to the other by I<sup>2</sup>C dimming Register 0x04 and Register 0x05, the ramp time can help LED current transit smoothly from one brightness level to next one. Ramp time can be adjusted from 1µs to 640ms via 0x03's bits [6:3]. Ramp time applies both to ramp up and ramp down, it remains same regardless the amount of change in brightness.

Figure 4. I<sup>2</sup>C and PWM Dimming Scheme

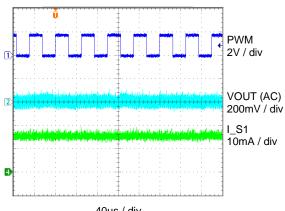

## **Backlight PWM Dimming**

In backlight I<sup>2</sup>C x PWM Mode, the input PWM duty cycle is converted internally to produce a DC output sink current (not pulsing). When PWM is enabled, it can be programmed as either active high or active low by register 0x02's bit [2], with active high as default. When PWM dimming is enabled, KTZ8864 uses internal 20MHz sampling clock to detect the PWM duty cycle. It is recommended to have the minimum PWM on time as  $0.1\mu s$ . For the example of 20kHz dimming frequency, the PWM duty cycle range can be  $0.2\% \sim 100\%$ . The PWM dimming frequency range can be as wide as 100Hz to 100kHz.

#### **PWM Dimming Step Response and Timeout**

If the LED current is changed from one value to the other by PWM dimming duty cycle, the transition ramp up/down time can be programmed by Register 0x15 bits [2:0]. For this transition ramp, its slope is fixed, so the final transition ramp time is dependent on the change amount of the PWM duty cycle.

The KTZ8864 PWM timeout feature turns off the boost output when the PWM is enabled and there is no PWM pulse detected.

#### **PWM to Digital Code Readback**

In I<sup>2</sup>C x PWM control mode, registers 0x12 and 0x13 contain the PWM duty cycle to the 11-bit code conversion information. Register 0x12 contains the 8 LSBs of the brightness code and register 0x13 the 3 MSBs. They are suggested to be read out in successive way to make sure the PWM duty result is correct. Too long delay between reading them may cause incorrect returned result, since input PWM duty may change during the delay time. To translate this reading to the actual LED current setting of the KTZ8864, convert it to the corresponding duty cycle and multiply it by the brightness level setting in the brightness registers (0x04 and 0x05).

## **Backlight PWM Hysteresis**

In backlight mode, if PWM dimming frequency is high and PWM dimming duty cycle is low, even the internal fast 20MHz sampling clock's sampling error can be sufficient to cause the output LED current jitter. KTZ8864 implements PWM hysteresis control to minimize the jitter. It can be programmed by register 0x03 bits [2:0]. The input PWM duty cycle is converted to an internal 11-bit digital value, this PWM hysteresis decides how many LSBs of this 11-bit digital value is changed before the output LED current can follow the change. When PWM duty cycle changes in the same direction, no hysteresis exists. Only when the PWM duty cycle's change starts to go in different direction, does the hysteresis starts to take effect, and only when the change is larger or equal to the number of LSBs programmed, the output LED current starts to follow the change. Table 2 shows the relationship between the minimum LSB(s) and the PWM duty cycle hysteresis. Table 3 summarizes register 0x03 bits [2:0]'s minimum setting to prevent jitter under different input PWM frequency conditions. The drawback of setting PWM hysteresis too high is that the output current becomes less accurate due to the hysteresis.

**Table 2. PWM Hysteresis**

| PWM Register<br>0x03 Bits [2:0] | Minimum<br>LSB(s) | PWM Duty<br>Cycle<br>Hysteresis |

|---------------------------------|-------------------|---------------------------------|

| 000                             | 0                 | 0/2047 = 0%                     |

| 001                             | 2                 | 2/2047 = 0.10%                  |

| 010                             | 4                 | 4/2047 = 0.20%                  |

| 011                             | 6                 | 6/2047 = 0.29%                  |

| 100                             | 8                 | 8/2047 = 0.39%                  |

| 101                             | 10                | 10/2047 = 0.48%                 |

| 110                             | 12                | 12/2047 = 0.59%                 |

| 111                             | 14                | 14/2047 = 0.68%                 |

Table 3. Register 0x03 Bits [2:0]'s Minimum Setting

| PWM Dimming<br>Frequency (kHz) | Sampling Error | Register 0x03 Bits [1:0]'s<br>Minimum Setting to Prevent Jitter |  |

|--------------------------------|----------------|-----------------------------------------------------------------|--|

| 0.1                            | 0.0005%        | 001                                                             |  |

| 1                              | 0.005%         | 001                                                             |  |

| 5                              | 0.025%         | 001                                                             |  |

| 10                             | 0.05%          | 001                                                             |  |

| 20                             | 0.1%           | 010                                                             |  |

| 40 0.2%                        |                | 011                                                             |  |

| 100                            | 0.5%           | 110                                                             |  |

## **Turn On/Off Ramp**

When backlight mode is enabled from standby mode or disabled to standby mode, the LED current waveform's turn on/off time is controlled by Turn On/Off Ramp Register 0x14 bits [7:4] and bits [3:0] respectively. The 16 options range from 512µs to 16384ms, with 8ms as default. The shape of the turn on/off ramp in backlight mode can also be programmed as exponential or linear through the Register 0x8 bit [5], with exponential as default.

### **Auto Frequency Mode**

KTZ8864 can automatically adjust the backlight boost switching frequency based on the programmed LED current for optimizing the conversion efficiency. Auto-Frequency Mode is configured by AUTOF\_LOW 0x06 and AUTOF\_HIGH 0x07. 0x06 sets the low threshold between 250KHz and 500KHz, while 0x07 sets the high threshold between 500KHz and 1MHz. Both 0x06 and 0x07 take an 8-bit code which is compared against the 8 MSB of the brightness register 0x05. For 250kHz, it can only access by auto frequency mode and max duty ratio is 50%. Table 4 details the boundaries for this mode.

**Table 4. Auto Switching Frequency Operation**

| Brightness Code MSBs (Register 0x05[7:0])        | Boost Switching Frequency |

|--------------------------------------------------|---------------------------|

| ≤ Auto Frequency Low Threshold (register 0x06)   | 250KHz                    |

| > Auto Frequency Low Threshold (register 0x06) & | 500KHz                    |

| ≤ Auto Frequency High Threshold (register 0x07)  | DUINH2                    |

| > Auto Frequency High Threshold (register 0x07)  | 1MHz                      |

By writing any non-zero code into 0x06 or 0x07 will enable Auto-Frequency Mode. Writing "0" into both 0x06 and 0x07 will disable Auto-Frequency Mode, the switching frequency will follow register 0x03 bit [7]) across the entire LED current range. Table 5 provides a guideline for selecting the auto frequency high/low threshold at Vin = 3.7V. The actual setting must be verified in the application and optimized for the desired input voltage.

**Table 5. Auto Frequency Threshold Setting Example**

| Condition<br>(Vf = 3.3V@I <sub>LED</sub> = 30mA) | Inductor<br>(µH) | Recommend Auto Frequency<br>High Threshold | Recommend Auto Frequency<br>Low Threshold |

|--------------------------------------------------|------------------|--------------------------------------------|-------------------------------------------|

| 2 × 4 LEDs                                       | 10               | 0x65 (12mA)                                | 0x43 (8mA)                                |

| 2 × 5 LEDs                                       | 10               | 0x5C (11mA)                                | 0x42 (7.9mA)                              |

| 2 × 6 LEDs                                       | 10               | 0x54 (10mA)                                | 0x3F (7.5mA)                              |

| 2 × 7 LEDs                                       | 10               | 0x4F (9.4mA)                               | 0x36 (6.5mA)                              |

| 2 × 8 LEDs                                       | 10               | 0x65 (12mA)                                | 0x3F (7.5mA)                              |

| 3 × 4 LEDs                                       | 10               | 0x4C (9mA)                                 | 0x2A (5.1mA)                              |

| 3 × 5 LEDs                                       | 10               | 0x43 (8mA)                                 | 0x28 (4.8mA)                              |

| 3 × 6 LEDs                                       | 10               | 0x3B (7mA)                                 | 0x27 (4.7mA)                              |

| 3 × 7 LEDs                                       | 10               | 0x35 (6.4mA)                               | 0x26 (4.6mA)                              |

| 3 × 8 LEDs                                       | 10               | 0x43 (8mA)                                 | 0x25 (4.5mA)                              |

| 4 × 4 LEDs                                       | 10               | 0x5C (11mA)                                | 0x2B (5.2mA)                              |

| 4 × 5 LEDs                                       | 10               | 0x50 (9.5mA)                               | 0x28 (4.8mA)                              |

| 4 × 6 LEDs                                       | 10               | 0x50 (9.5mA)                               | 0x28 (4.8mA)                              |

#### **LED Fault Protection**

Each current sink is protected against LED short or open conditions. The outcome of LED short event depends on the setting of LED\_SHORT\_MODE bit in register 0x10. If it is '1' and LED short circuit condition arises, the current sink continues to regulate until  $V_{SINK} > V_{SOV}$ . When any sink node voltage goes above  $V_{SOV}$  (6V) for more than 59ms (typ.), LED\_SHORT flag will be set in 0x0F and that channel's current sink will be turned off, and the other channel(s) will continue to work if they don't trigger this fault condition. If it is '0', the LED\_SHORT flag will be set in 0x0F when  $V_{SINK} > V_{SOV}$  more than 59ms(typ.) is detected, but KTZ8864 will keep working as usual without turning off the shorted channel's current sink until it reaches thermal shutdown.

In case of an LED failing open, the current sink voltage of the failed string will go close to ground and dominate the boost converter control loop. As a result, the output voltage will increase until it reaches the over-voltage threshold set by register 0x02. Once an OVP event has been detected, the boost will stop switching and the BL\_OVP flag will be set in register 0x0F. The outcome of OVP event depends on the setting of OVP\_MODE bit in register 0x02. If OVP\_MODE is set to 0, the LED open channel will not be disabled, as soon as VBL\_OUT falls below the backlight OVP threshold, the KTZ8864 begins switching again, so that VBL\_OUT will be kept close to OVP threshold. Once the opened channel resumes to connected later, its LED current will resume and VBL\_OUT will go back to normal level. If OVP\_MODE is set to 1, once the over-voltage incident is triggered, the BL\_OVP flag is set in register 0x0F. Any of the enabled current sink headroom voltage drops below 150mV will be disabled. Then the output voltage of the boost converter will go back to normal level. During the entire process, the rest of the LED string (healthy LED string) would continue in normal operation. Even if the open channel is reconnected later, its LED current will not resume until toggling HWEN or sending software reset command or resetting backlight mode.

In case where all LED channels are open, once the output voltage of the boost converter reaches the over-voltage threshold, all the current sinks will be disabled internally and the boost converter will stop switching. User needs to restart the IC by toggling HWEN or sending software reset command or resetting backlight mode.

## **Backlight Over Current Protection**

The KTZ8864 has 4 different OCP thresholds (1200mA, 1500mA, 1800mA, and 2100mA) chosen by register 0x11 bits [1:0]. It is a cycle-by-cycle current limit by detecting low side power FET current. Once the threshold is trigged, the low side power FET will be turned off immediately for the rest of the switching cycle time. If enough overcurrent threshold events occur, the BL\_OCP Flag (register 0x0F, bit [0]) will be set.

# **LCD Bias Boost Converter**

REG pin is the output of a high efficiency boost which is used to generate OUTP and OUTN power rails. REG boost ranges from 4V to 6.6V with 50mV step size. OUTP is generated by an LDO whose input is REG pin. OUTP ranges from 4V to 6.3V with 50mV step size and supports up to 120mA output current. OUTN is generated

by an inverting charge pump whose input is REG pin. OUTN ranges from -6.3V to -4V with 50mV step size and supports up to 120mA output current. Refer to 0x0C, 0x0D, 0x0E for the settings of REG, OUTP and OUTN.

For proper operation, REG voltage is suggested to be  $REG = MAX(OUTP, |OUTN|) + V_{HR}$ , where  $V_{HR} \ge 200mV$  for lower currents and  $V_{HR} \ge 300mV$  for higher currents.

OUTP and OUTN voltage settings can be changed while they are enabled, but user must re-write 0x09 to get new settings taking effect. The REG voltage changes immediately upon a register write. The LCD Bias outputs can be turned on/off either by ENP and ENN pins or by 0x09 register bits [2:1]. EXT\_EN bit in 0x09 is used to select on/off is controlled by external pins or internal register bits. Refer to Table 6 for detailed information.

**Table 6. LCD Bias Power Operating Mode**

| HWEN | ENN | ENP | LCD_EN_MODE<br>0x09[7] | OUTP_EN<br>0x09[2] | OUTN_EN<br>0x09[1] | EXT_EN<br>0x09[0] | ACTION                                     |

|------|-----|-----|------------------------|--------------------|--------------------|-------------------|--------------------------------------------|

| 0    | Χ   | Χ   | X                      | X                  | X                  | X                 | Device shutdown                            |

| 1    | 0   | 0   | 0                      | X                  | X                  | 1                 | Standby <sup>7</sup>                       |

| 1    | Χ   | Χ   | 1                      | 0                  | 0                  | 0                 | Standby <sup>7</sup>                       |

| 1    | 0   | 1   | 1                      | Х                  | X                  | 1                 | VPOS enabled via external input            |

| 1    | 1   | 0   | 1                      | Х                  | X                  | 1                 | VNEG enabled via external input            |

| 1    | 1   | 1   | 1                      | Х                  | Х                  | 1                 | VPOS and VNEG enabled via external Input   |

| 1    | Χ   | Χ   | 1                      | 1                  | 0                  | 0                 | VPOS enabled via I <sup>2</sup> C          |

| 1    | Χ   | Χ   | 1                      | 0                  | 1                  | 0                 | VNEG enabled via I <sup>2</sup> C          |

| 1    | Χ   | Х   | 1                      | 1                  | 1                  | 0                 | VPOS and VNEG enabled via I <sup>2</sup> C |

## **Fast Discharge**

KTZ8864 has internal switch resistance for discharging OUTP and OUTN when device is shutdown. The OUTP discharge function is enabled with register 0x09 bit [4] and the OUTN discharge is enabled with register 0x09 bit [3].

#### **OUTP Short Circuit Protection**

If output current of OUTP is greater than 180mA (typical), the OUTP\_SHORT flag will be set in register 0x0F. A  $I^2C$  readback is required to clear the flag. The outcome of an OUTP\_SHORT detection depends on the setting of register 0x0A bits [7:6], including report-only flag, shutdown OUTP/OUTN, and shutdown OUTP/OUTN and backlight. KTZ8864 provides four level short circuit detection filter:  $100\mu s$ ,  $500\mu s$ , 1ms, and 2ms by register 0x0B bits [3:2] to avoid false trigger problems.

#### **OUTN Short Circuit Protection**

OUTN\_SHORT flag will be set in register 0x0F if OUTN is found shorted to ground. An I²C readback of register 0x0F is required to clear the flag. The outcome of an OUTN\_SHORT detection depends on the setting of register 0x0A bits [7:6], including report-only flag, shutdown OUTP/OUTN, and shutdown OUTP/OUTN and backlight. KTZ8864 provides four level short circuit detection filter options: 100µs, 500µs, 1ms, and 2ms by register 0x0B bits [1:0] to avoid false trigger problems.

#### Soft Reset

All the I<sup>2</sup>C registers can be reset to their default settings by writing '1' to the SOFTWARE\_RESET bit in Register 0x08, this bit will be reset to '0' automatically after the software reset.

#### UVLO

Under voltage lock-out (UVLO) featured is included to monitor the input voltage VIN. Once VIN drops below UVLO falling threshold, the current sinks are disabled and the boost converters stop switching. After VIN increases above UVLO rising threshold, the boost converters and the current sinks will resume to their previous setting.

<sup>7.</sup> Standby signifies that OUTP and OUTN are either high impedance or being internally pulled low via the active pulldown, and that the LCD boost is off. Shutdown signifies that that the device was reset and no I<sup>2</sup>C communication is accepted.

#### Thermal Shutdown

The KTZ8864 has Thermal Shutdown Protection which will turn off the backlight boost, all current sinks, LCD bias boost, inverting charge pump, and the LDO when the die temperature reaches or exceeds 150°C (typ). The I²C access is still available during Thermal Shutdown event, but TSD flag will be set in register 0x0F, this bit is real time reflection of TSD. When TSD is gone, the bit will be reset back to 0 automatically.

#### **Device Functional Modes**

Shutdown: The KTZ8864 is in shutdown when the HWEN pin is low. I2C writes are not recognized in shutdown.

**Standby:** After the HWEN pin is set high the KTZ8864 goes into standby mode. In standby mode, I<sup>2</sup>C writes are allowed but references, bias currents, the oscillator, LCD Bias, and backlight are all disabled to keep the quiescent supply current low.

**Normal mode:** Each of the main blocks of the KTZ8864 are independently controlled. For details on how to control each mode, see Tables 1 and 6.

# **Application Information**

#### I<sup>2</sup>C Serial Data Bus

KTZ8864 supports the I<sup>2</sup>C bus protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the bus is called a master, whereas the devices controlled by the master are known as slaves. A master device must generate the serial clock (SCL), control bus access and generate START and STOP conditions to control the bus. KTZ8864 operates as a slave on the I<sup>2</sup>C bus. Within the bus specifications a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum clock rate) are defined. KTZ8864 works in both modes. Connections to the bus are made through the open-drain I/O lines SDA and SCL.

The following bus protocol has been defined in Figure 5:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is high are interpreted as control signals.

Accordingly, the following bus conditions have been defined:

#### **Bus Not Busy**

Both data and clock lines remain HIGH.

### Start Data Transfer

A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

#### Stop Data Transfer

A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

#### Data Valid

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions are not limited and are determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

#### Acknowledge

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse. Setup and hold times must also be taken into account.

Figure 5. Data Transfer on I<sup>2</sup>C Serial Bus

KTZ8864 7-bit slave device address is 0010001 binary (0x11h).

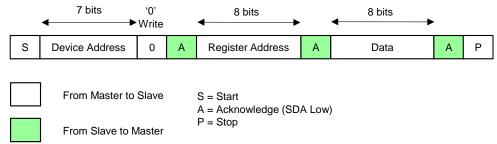

There are two kinds of I<sup>2</sup>C data transfer cycles: write cycle and read cycle.

## I<sup>2</sup>C Write Cycle

For I<sup>2</sup>C write cycle, data is transferred from a master to a slave. The first byte transmitted is the 7-bit slave address plus one bit of '0' for write. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first. Figure 6 shows the sequence of the I<sup>2</sup>C write cycle.

Figure 6. I<sup>2</sup>C Write Cycle

#### I<sup>2</sup>C Write Cycle Steps:

- · Master generates start condition.

- Master sends 7-bit slave address (0010001 for KTZ8864) and 1-bit data direction '0' for write.

- Slave sends acknowledge if the slave address is matched.

- · Master sends 8-bit register address.

- · Slave sends acknowledge.

- Master sends 8-bit data for that addressed register.

- · Slave sends acknowledge.

- If master sends more data bytes, the register address will be incremented by one after each acknowledge.

- Master generate stop condition to finish the write cycle.

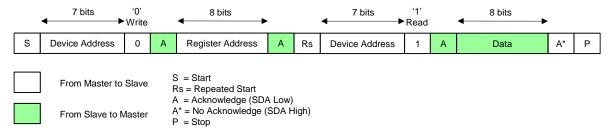

#### I<sup>2</sup>C Read Cycle

For I<sup>2</sup>C read cycle, data is transferred from a slave to a master. But to start the read cycle, master needs to write the register address first to define which register data to read. Figure 7 shows the steps of the I<sup>2</sup>C read cycle.

Figure 7. I<sup>2</sup>C Read Cycle

#### I<sup>2</sup>C Read Cycle Steps:

- Master generates start condition.

- Master sends 7-bit slave address (0010001 for KTZ8864) and 1-bit data direction '0' for write.

- Slave sends acknowledge if the slave address is matched.

- Master sends 8-bit register address.

- Slave sends acknowledge.

- Master generates repeated start condition.

- Master sends 7-bit slave address (0010001 for KTZ8864) and 1-bit data direction '1' for read.

- Slave sends acknowledge if the slave address is matched.

- Slave sends the data byte of that addressed register.

- If master sends acknowledge, the register address will be incremented by one after each acknowledge and the slave will continue to send the data for the updated addressed register.

- If master sends no acknowledge, the slave will stop sending the data.

- Master generate stop condition to finish the read cycle.

# I<sup>2</sup>C Register Map

Table 7 summarizes KTZ8864's 21 I<sup>2</sup>C registers, their read/write settings and default values. They can be reset to default values by VIN power on reset, toggling HWEN or I<sup>2</sup>C software reset.

Table 7. I<sup>2</sup>C Register Map

| Register Name            | Address (Hex) | R/W | Default Value |

|--------------------------|---------------|-----|---------------|

| REV                      | 0x01          | R   | xxxxxx10      |

| BL_CFG1                  | 0x02          | R/W | 0x28          |

| BL_CFG2                  | 0x03          | R/W | 0x8D          |

| BL_BRT_LSB               | 0x04          | R/W | 0x07          |

| BL_BRT_MSB               | 0x05          | R/W | 0xFF          |

| BL_AUTOF_LOW             | 0x06          | R/W | 0x00          |

| BL_AUTOF_HIGH            | 0x07          | R/W | 0x00          |

| BL_EN                    | 0x08          | R/W | 0x00          |

| LCD_BIAS_CFG1            | 0x09          | R/W | 0x18          |

| LCD_BIAS_CFG2            | 0x0A          | R   | 0x11          |

| LCD_BIAS_CFG3            | 0x0B          | R/W | 0x00          |

| LCD_BOOST_CFG            | 0x0C          | R/W | 0x28          |

| OUTP_CFG                 | 0x0D          | R/W | 0x1E          |

| OUTN_CFG                 | 0x0E          | R/W | 0x1C          |

| FLAG                     | 0x0F          | R   | 0x00          |

| BL_OPTION1               | 0x10          | R/W | 0x06          |

| BL_OPTION2               | 0x11          | R/W | 0x35          |

| PWM2DIG_LSBs             | 0x12          | R   | 0x00          |

| PWM2DIG_MSBs             | 0x13          | R   | 0x00          |

| TURN_ON/OFF_RAMP         | 0x14          | R/W | 0x44          |

| PWM_UP/DOWN_RAMP and IFS | 0x15          | R/W | 0XF8          |

# Table 8. REV Register

| ADDRESS | MODE         |        | RESET VALUE: 0x0A           |

|---------|--------------|--------|-----------------------------|

| 0x01    | R            |        | RESET VALUE: UXUA           |

| BIT     | NAME         | POR    | DESCRIPTION                 |

| 7:2     | DEV Revision | xxxxxx | Die Revision Identification |

| 1:0     | VENDOR       | 10     |                             |

Table 9. BL\_CFG1 Register

| ADDRESS | MODE<br>R/W |     | RESET VALUE: 0x28                                                                  |

|---------|-------------|-----|------------------------------------------------------------------------------------|

| 0x02    |             |     | RESET VALUE: 0X26                                                                  |

| BIT     | NAME        | POR | DESCRIPTION                                                                        |

| 7:5     | BL_OVP      | 001 | Backlight OVP 000: 17V 001: 21V 010: 25V 011: 29V 100: 19V 101: 23V 111: 23V       |

| 4       | OVP_MODE    | 0   | O: OVP is report only     OVP will turn off the fault string that cause OVP event. |

| 3       | BLED_MAP    | 1   | 0: Exponential 1: Linear                                                           |

| 2       | PWM_CONFIG  | 0   | 0: Active high 1: Active low                                                       |

| 1       | RSVD        | 0   |                                                                                    |

| 0       | PWM_ENABLE  | 0   | 0: PWM disabled<br>1: PWM enabled                                                  |

Note: When Backlight Current Mapping setting is changed, the LED current change will not take effect until Register 0x05 is programmed.

Table 10. BL\_CFG2 Register

| ADDRESS | MODE                |      | RESET VALUE: 0x8B                                                                                                                                                                                                                                                                                                                                                           |  |

|---------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x03    | R/W                 | 1    | RESET VALUE. UXOB                                                                                                                                                                                                                                                                                                                                                           |  |

| BIT     | NAME                | POR  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |  |

| 7       | BL_FREQ_FREQ        | 1    | Sets the backlight boost switch frequency 0: 500kHz 1: 1.0MHz (Default)                                                                                                                                                                                                                                                                                                     |  |

| 6:3     | LED CURRENT<br>RAMP | 0001 | Controls backlight LED ramping time. The transient time is a constant time that the backlight takes to transition from an existing programmed code to a new programmed code.  0000: 1µs 0001: 2ms(Default) 0010: 4ms 0011: 8ms 0100: 16ms 0101: 32ms 0110: 64ms 0111: 128ms 1000: 192ms 1001: 256ms 1010: 320ms 1011: 384ms 1100: 448ms 1101: 512ms 1110: 576ms 1111: 640ms |  |

| 2:0     | PWM_HYST            | 101  | Sets the minimum change in PWM input duty cycle that results in a change of backlight LED brightness level 000 : 0 LSB 001: 2 LSBs 010: 4 LSBs 011: 6 LSBs 100: 8 LSBs 101: 10 LSBs(Default) 110: 12 LSBs 111: 14 LSBs                                                                                                                                                      |  |

<sup>1.</sup> For LED CURRENT RAMP Time in the table, all the ramp times are fixed when current ramps from one level to the other except "0000" setting. For "0000" setting, the ramp slope is 1µs/step, the final ramp time is proportional to the 11-bit current steps.

# Table 11. BL\_BRT\_LSB Register

| ADDRESS | MODE     |       | RESET VALUE: 0x07          |

|---------|----------|-------|----------------------------|

| 0x04    | R/W      |       | RESET VALUE: UXU7          |

| BIT     | NAME     | POR   | DESCRIPTION                |

| 7:3     | RSVD     | 00000 |                            |

| 2:0     | BRT[2:0] | 111   | 3-bit brightness code LSBs |

# Table 12. BL\_BRT\_MSB Register

| ADDRESS | MODE     |          | RESET VALUE: 0xFF           |

|---------|----------|----------|-----------------------------|

| 0x05    | R/W      |          | RESET VALUE. 0XFF           |

| BIT     | NAME     | POR      | DESCRIPTION                 |

| 7:0     | BRT[7:0] | 11111111 | 11-bit brightness code MSBs |

#### Note:

- If only using 8-bit current ratio, keep the 3-bit LSBs as '111' and only program the 8-bit MSBs.

If using 11-bit current ratio, the 3-bit LSBs should be programmed first, then the 8-bit MSBs can be programmed to take effect. Even if only the 3-bit LSBs need to be changed, the 8-bit MSB should always be programmed to make the 3-bit LSBs change taking effect.

For 11-bit program code 11'b00000000000, both boost converter and current sinks are turned off.

### Table 13. BL\_AUTOF\_LOW Register

| ADDRESS | MODE |          | RESET VALUE: 0x00                                           |

|---------|------|----------|-------------------------------------------------------------|

| 0x06    | R/W  |          | RESET VALUE: 0X00                                           |

| BIT     | NAME | POR      | DESCRIPTION                                                 |

| 7:0     | AFLT | 00000000 | Compared against 8 MSB's of Brightness Code (register 0x05) |

### Table 14. BL\_AUTOF\_HIGH Register

| ADDRESS | MODE |          | RESET VALUE: 0x00                                           |

|---------|------|----------|-------------------------------------------------------------|

| 0x07    | R/W  |          | RESET VALUE: 0X00                                           |

| BIT     | NAME | POR      | DESCRIPTION                                                 |

| 7:0     | AFHT | 00000000 | Compared against 8 MSB's of Brightness Code (register 0x05) |

# Table 15. BL\_EN Register

| ADDRESS | MODE           |     | RESET VALUE: 0x00                                                         |

|---------|----------------|-----|---------------------------------------------------------------------------|

| 0x08    | R/W            |     | RESET VALUE: 0X00                                                         |

| BIT     | NAME           | POR | DESCRIPTION                                                               |

| 7       | SOFTWARE_RESET | 0   | 0 = No reset<br>1 = Device reset (automatically returns to 0 after reset) |

| 6       | RSVD           | 0   |                                                                           |

| 5       | RAMP_SHAPE     | 0   | 0: Exponential<br>1: Linear                                               |

| 4       | BL_EN          | 0   | 0 = BL disabled<br>1 = BL enabled                                         |