# Lattice **CORE**

Color Space Converter IP Core User Guide

# **Table of Contents**

| Chapter 1. Introduction                                          | . 4 |

|------------------------------------------------------------------|-----|

| Quick Facts                                                      | . 4 |

| Features                                                         | . 6 |

| Chapter 2. Functional Description                                | .7  |

| Color Spaces                                                     |     |

| Block Diagram                                                    |     |

| Color Space Conversion                                           |     |

| CSC Implementation                                               |     |

| Standard and Custom Core Types                                   |     |

| Full Precision Outputs                                           |     |

| Limited Precision Outputs                                        | 10  |

| Signal Descriptions                                              | 11  |

| Timing Diagrams                                                  |     |

| Parallel Architecture Timing                                     | 11  |

| Sequential Architecture Timing                                   |     |

| Chapter 3. Parameter Settings                                    |     |

| Input/Coefficient Tab                                            |     |

| Core Type                                                        |     |

| Architecture                                                     |     |

| Input Data Type                                                  |     |

| Input Data Width                                                 |     |

| Coefficient Width                                                |     |

| Use DSP Block                                                    |     |

| Registered Input                                                 |     |

| Keep Data at Blank Time                                          |     |

| Connect Reset Port to GSR                                        |     |

| ce                                                               |     |

| sr                                                               | 15  |

| inpvalid/outvalid                                                | 15  |

| Output Tab                                                       |     |

| Output Latency                                                   | 15  |

| Output Data Type                                                 | 15  |

| Output Data Width                                                | 15  |

| Overflow                                                         | 15  |

| Rounding                                                         | 15  |

| Chapter 4. IP Core Generation                                    | 16  |

| Licensing the IP Core                                            | 16  |

| Getting Started                                                  | 16  |

| IPexpress-Created Files and Top-Level Directory Structure        | 18  |

| Instantiating the Core                                           | 19  |

| Running Functional Simulation                                    | 19  |

| Synthesizing and Implementing the Core in a Top-Level Design     | 20  |

| Hardware Evaluation                                              |     |

| Enabling Hardware Evaluation in Diamond                          | 20  |

| Updating/Regenerating the IP Core                                | 20  |

| Regenerating an IP Core in Diamond                               | 20  |

| IP Core Generation in Clarity Designer                           | 22  |

| Getting Started                                                  |     |

| Clarity Designer Created Files and Top Level Directory Structure | 26  |

© 2015 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Simulation Evaluation            |  |

|----------------------------------|--|

| IP Core Implementation           |  |

| Chapter 5. Support Resources     |  |

| Lattice Technical Support        |  |

| E-mail Support                   |  |

| Local Support                    |  |

| Internet                         |  |

| References                       |  |

| LatticeECP3                      |  |

| MachXO2                          |  |

| ECP5                             |  |

| Revision History                 |  |

| Appendix A. Resource Utilization |  |

| LatticeECP3 Devices              |  |

| Ordering Part Number             |  |

| MachXO2 Devices                  |  |

| Ordering Part Number             |  |

| ECP5 LFE5UM Devices              |  |

| Ordering Part Number             |  |

| -                                |  |

Chapter 1: Introduction

Color Space Converters (CSC) are used in video and image display systems including televisions, computer monitors, color printers, video telephony and surveillance systems. CSCs are also used in many video/image compression and processing applications, and in the implementation of NTSC/PAL/SECAM television standards, JPEG and MPEG systems.

A CSC converts signals from one color space to another color space. Color space conversion is often required to ensure compatibility with display devices or to make the image data amenable for compression or transmission.

The Lattice CSC IP core is widely parameterizable and can support any custom color space conversion requirement. Furthermore, several commonly used color space conversion methods are provided as ready-to-use configurations.

## **Quick Facts**

Table 1-1 through Table 1-3 give quick facts about the CSC IP core for LatticeECP3<sup>™</sup>, MachXO2<sup>™</sup> and ECP5 devices. The configurations indicated in Table 1-1 through Table 1-3 correspond to the parameter selections given in Table A-1.

|                      |                         |                                              | CSC Con         | figuration            |          |

|----------------------|-------------------------|----------------------------------------------|-----------------|-----------------------|----------|

|                      |                         | Config1                                      | Config2         | Config3               | Config4  |

| Cara Paguiramanta    | FPGA Families Supported |                                              | Lattice         | ECP3                  | •        |

| Core Requirements    | Minimum Device Needed   |                                              | LFE3-17EA-      | 6FN484CES             |          |

|                      | Targeted Device         |                                              | LFE3-150EA      | A-6FN1156C            |          |

|                      | Data Path Width         | 8                                            | 8               | 16                    | 8        |

|                      | LUT4s                   | 259                                          | 98              | 835                   | 493      |

| Resource Utilization | sysMEM™ EBRs            | 0                                            | 0               | 0                     | 0        |

|                      | Registers               | 336                                          | 185             | 487                   | 300      |

|                      | MULT18x18C              | 9                                            | 3               | 5                     | 9        |

|                      | MULT9x9C                | 0                                            | 0               | 0                     | 0        |

|                      | Lattice Implementation  |                                              | Lattice Dia     | mond <sup>®</sup> 3.4 | •        |

| Design Tool Support  | Synthesis               | Synopsys Synplify Pro for Lattice J-2014.09L |                 |                       | 014.09L  |

| Design Tool Support  | Simulation              | Aldeo                                        | c Active-HDL 9. | 3 SPI Lattice I       | Edition  |

|                      | Simulation              | Mento                                        | r Graphics Mod  | lelSim SE6.6e         | or later |

#### Table 1-1. CSC IP Core for LatticeECP3 Devices – Quick Facts

#### Table 1-2. CSC IP Core for MachXO2 Devices – Quick Facts

|                      | CSC Configuration       |                                              |                |                 |          |

|----------------------|-------------------------|----------------------------------------------|----------------|-----------------|----------|

|                      |                         | Config1                                      | Config2        | Config3         | Config4  |

| Coro Roquiromonto    | FPGA Families Supported |                                              | Mach           | NXO2            | •        |

| Core Requirements    | Minimum Device Needed   |                                              | LCMXO2-1200    | 0HC-4TG100C     | ;        |

|                      | Targeted Device         |                                              | LCMXO2-4000    | DHE-5FG484C     | ;        |

|                      | Data Path Width         | 8                                            | 8              | 16              | 8        |

|                      | LUT4s                   | 1633                                         | 643            | 2645            | 1663     |

| Resource Utilization | sysMEM EBRs             | 0                                            | 0              | 0               | 0        |

|                      | Registers               | 798                                          | 368            | 835             | 625      |

|                      | MULT18x18               | 0                                            | 0              | 0               | 0        |

|                      | MULT9x9                 | 0                                            | 0              | 0               | 0        |

|                      | Lattice Implementation  |                                              | Lattice Dia    | amond 3.4       |          |

| Design Tool Support  | Synthesis               | Synopsys Synplify Pro for Lattice J-2014.09L |                |                 | 014.09L  |

| Design Tool Support  | Simulation              | Aldeo                                        | Active-HDL 9.  | 3 SPI Lattice E | Edition  |

|                      | Simulation              | Mento                                        | r Graphics Mod | lelSim SE6.6e   | or later |

### Table 1-3. CSC IP Core for ECP5UM Devices – Quick Facts

|                      |                         |                                              | CSC Con        | figuration      |          |

|----------------------|-------------------------|----------------------------------------------|----------------|-----------------|----------|

|                      |                         | Config1                                      | Config2        | Config3         | Config4  |

| Core Requirements    | FPGA Families Supported |                                              | ECP5           | U/UM            |          |

|                      | Minimum Device Needed   |                                              | LFE5UM-25      | F-6MG285C       |          |

|                      | Targeted Device         |                                              | LFE5UM-85      | F-7BG756C       |          |

|                      | Data Path Width         | 8                                            | 8              | 16              | 8        |

|                      | LUT4s                   | 259                                          | 251            | 835             | 493      |

| Resource Utilization | sysMEM EBRs             | 0                                            | 0              | 0               | 0        |

|                      | Registers               | 336                                          | 185            | 487             | 300      |

|                      | MULT18x18               | 9                                            | 3              | 5               | 9        |

|                      | MULT9x9                 | 0                                            | 0              | 0               | 0        |

|                      | Lattice Implementation  |                                              | Lattice Dia    | amond 3.4       |          |

| Design Tool Support  | Synthesis               | Synopsys Synplify Pro for Lattice J-2014.09L |                |                 | 2014.09L |

| Design Tool Support  | Simulation              | Aldeo                                        | Active-HDL 9.  | 3 SPI Lattice I | Edition  |

|                      | Simulation              | Mento                                        | r Graphics Mod | elSim SE6.6e    | or later |

# Features

- Input data width of 8, 10, 12, and 16 bits

- Signed or unsigned input and output data

- Supports standard configurations as well as custom configurations

- Parameterized coefficients precision from 9 to18 bits

- Full precision as well as limited precision output

- Programmable precision and rounding options for the output

- Optional sequential or parallel architecture for area or throughput optimization

- Configurable DSP block based or look-up-table (LUT) based multiplier implementations

- Registered input option available for input set-up time improvement.

This chapter provides a functional description of the CSC IP core.

# **Color Spaces**

A color space is a three dimensional representation of the color and intensity of an image's pixel. An example of a color space is a RGB color space where each pixel's color is represented by the constituent red, green and blue components. This color space is a natural choice for computer displays where the CRT uses these colors to display a multi-colored pixel. However, a RGB color space may not be the ideal one for image processing or efficient image transmission or human interpretation of color information. A color space that represents a color pixel using the characteristics of hue, saturation and brightness is more akin to the way humans interpret color information. HIS and HSV are examples of such color spaces.

It is known that human vision is more sensitive to brightness than color. In an image, green color carries more of the brightness information than the red and blue components. Therefore some of the information from the red and blue color components can be reduced in order to compress the signal for more efficient processing. It is useful to deploy a color space representing brightness (luminance) and color components (chrominance) for processing applications. Common examples of such color spaces are YUV, YIQ and YCbCr, which are part of many video standards.

The following are some commonly used color spaces:

- RGB: Red, Green, Blue. This color space is used in computer displays.

- YIQ,YUV,YCbCr: Luminance, Chrominance. These color spaces are used in television systems. YIQ is used in NTSC systems, YUV is used in PAL systems and YCbCr is used in digital television systems.

- **CMY(K):** Cyan, Magenta, Yellow, (Black). This color space is used in printing applications. The fourth component, black, is used to improve both the density range and color range. This removes the need to generate a good black color from CMY components.

# **Block Diagram**

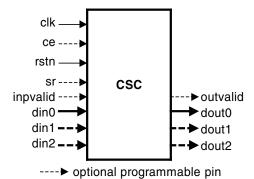

The top-level interface diagram for the CSC IP is given in Figure 2-1.

Figure 2-1. Top-level Interface Diagram for the CSC IP Core

# **Color Space Conversion**

Color space conversion is required when transferring data between devices that use different color space models. For example, RGB to YCbCr color space conversion is required when displaying a computer image on a television. Similarly, YCbCr to RGB color space conversion is required when displaying television movies on a computer monitor. As a color can be represented completely using three dimensions, a color space is a three dimensional space. Color space conversion is a one-to-one mapping from one color space to another color space.

R'G'B' to Y'CbCr color space conversion is given by the following equations. The prime notations are used to denote gamma-corrected values.

$\begin{array}{l} Y' = 0.257 * R' + 0.504 * G' + 0.098 * B' + 16 \\ Cb = -0.148 * R' - 0.291 * G' + 0.439 * B' + 128 \\ Cr = 0.439 * R' - 0.368 * G' - 0.071 * B' + 128 \end{array}$

Y'CbCr to computer R'G'B' conversion is given by the following equations.

R' = 1.164 \* Y' +0.0 \* Cb + 1.596 \* Cr -222.912 G' = 1.164 \* Y' -0.392 \* Cb -0.813 \* Cr + 135.616 B' = 1.164 \* Y' + 2.017 \* Cb + 0.0 \* Cr -276.8

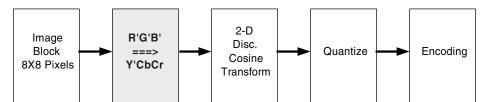

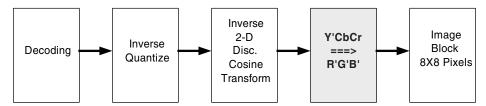

Example applications that use CSC for R'G'B' to Y'CbCr Conversion and Y'CbCr to R'G'B' conversion are shown in Figure 2-2 and Figure 2-3.

#### Figure 2-2. JPEG Encoding Application

Figure 2-3. JPEG Decoding Application

### **CSC** Implementation

The Color Space Converter is implemented using multipliers and adders operating on input pixel data and a set of coefficients defined for that conversion. The general color space conversion equations can be expressed by the following matrix multiplication.

| dout0 |   | сМН о | cMI cMJ | сМК |   | din0 |

|-------|---|-------|---------|-----|---|------|

| dout1 | = | cNH d | cNI cNJ | cNK | = | din1 |

| douti |   |       |         |     |   | din2 |

| dout2 |   | cPH o | cPI cPJ | cPK |   | GITZ |

|       |   |       |         |     |   | 1    |

The pixel values of the input color space, din0, din1 and din2 are read through the input ports. The constants denoted by cMH,cMI, ..., cPK, are the coefficients used for the color space conversion. These coefficients are either provided by the user or automatically determined by the IP GUI for standard conversions. The values of the pixel components in the converted color space are available through the output ports: dout0, dout1 and dout2.

The CSC IP offers the choice of two different architectures: parallel and sequential. In the parallel architecture, all three color plane data are applied at the same time. The output data for all the color planes are also available at the

same time after a latency of few clock cycles. In the sequential architecture, the input data for the three color planes is applied in sequence, one after the other, using the same input port din0. The output data for the color planes is given out sequentially using the same output port, dout0, after a latency of few clock cycles.

### **Standard and Custom Core Types**

Table 2-1 lists the standard configurations available in the CSC IP GUI and their coefficient values.

Table 2-1. Coefficients for Standard Configurations

| Core Type                      |       | *din0  | *din1  | *din2  | +        |

|--------------------------------|-------|--------|--------|--------|----------|

|                                | dout0 | 0.257  | 0.504  | 0.098  | 16.0     |

| Computer R_G_Bto Y_CbCr:SDTV   | dout1 | -0.148 | -0.291 | 0.439  | 128.0    |

|                                | dout2 | 0.439  | -0.368 | -0.071 | 128.0    |

|                                | dout0 | 0.183  | 0.614  | 0.062  | 16.0     |

| Computer R_G_Bto Y_CbCr:HDTV   | dout1 | -0.101 | -0.338 | 0.439  | 128.0    |

|                                | dout2 | 0.439  | -0.399 | -0.04  | 128.0    |

|                                | dout0 | 0.299  | 0.587  | 0.114  | 0.0      |

| Studio R_G_Bto Y_CbCr:SDTV     | dout1 | -0.172 | -0.339 | 0.511  | 128.0    |

|                                | dout2 | 0.511  | -0.428 | -0.083 | 128.0    |

|                                | dout0 | 0.213  | 0.715  | 0.072  | 0.0      |

| Studio R_G_Bto Y_CbCr:HDTV     | dout1 | -0.117 | -0.394 | 0.511  | 128.0    |

|                                | dout2 | 0.511  | -0.464 | -0.047 | 128.0    |

|                                | dout0 | 1.164  | 0.0    | 1.596  | -222.912 |

| Y_CbCr:SDTV to Computer R_G_B_ | dout1 | 1.164  | -0.391 | -0.813 | 135.488  |

|                                | dout2 | 1.164  | 2.018  | 0.0    | -276.928 |

|                                | dout0 | 1.164  | 0.0    | 1.793  | -248.128 |

| Y_CbCr:HDTV to Computer R_G_B_ | dout1 | 1.164  | -0.213 | -0.534 | 76.992   |

|                                | dout2 | 1.164  | 2.115  | 0.0    | -289.344 |

|                                | dout0 | 1.0    | 0.0    | 1.371  | -175.488 |

| Y_CbCr:SDTV to Studio R_G_B_   | dout1 | 1.0    | -0.336 | -0.698 | 132.352  |

|                                | dout2 | 1.0    | 1.732  | 0.0    | -221.696 |

|                                | dout0 | 1.0    | 0.0    | 1.54   | -197.12  |

| Y_CbCr:HDTV to Studio R_G_B_   | dout1 | 1.0    | -0.183 | -0.459 | 82.176   |

|                                | dout2 | 1.0    | 1.816  | 0.0    | -232.448 |

|                                | dout0 | 1.0    | 0.0    | 1.14   | 0.0      |

| Y_UV to Computer R_G_B_        | dout1 | 1.0    | -0.395 | -0.581 | 0.0      |

|                                | dout2 | 1.0    | -2.032 | 0.0    | 0.0      |

|                                | dout0 | 0.299  | 0.587  | 0.114  | 0.0      |

| Computer R_G_Bto Y_UV          | dout1 | -0.147 | -0.289 | 0.436  | 0.0      |

|                                | dout2 | 0.615  | -0.515 | -0.1   | 0.0      |

|                                | dout0 | 1.0    | 0.956  | 0.621  | 0.0      |

| Y_IQ to Computer R_G_B         | dout1 | 1.0    | -0.272 | -0.647 | 0.0      |

|                                | dout2 | 1.0    | -1.107 | 1.704  | 0.0      |

|                                | dout0 | 0.299  | 0.587  | 0.114  | 0.0      |

| Computer R_G_Bto Y_IQ          | dout1 | 0.596  | -0.275 | -0.321 | 0.0      |

|                                | dout2 | 0.212  | -0.523 | 0.311  | 0.0      |

#### Table 2-1. Coefficients for Standard Configurations (Continued)

| Соге Туре    |       | *din0 | *din1     | *din2    | +   |

|--------------|-------|-------|-----------|----------|-----|

|              | dout0 | 1.0   | 0.0       | 0.0      | 0.0 |

| Y_IQ to Y_UV | dout1 | 0.0   | -0.544639 | 0.838671 | 0.0 |

|              | dout2 | 0.0   | 0.838671  | 0.544639 | 0.0 |

Notes:

For RGB to YCbCr: din0/din1/din2/dout0/dout1/dout2 stands for R/G/B/Y/Cb/Cr accordingly. For YCbCr to RGB: din0/din1/din2/dout0/dout1/dout2 stands for Y/Cb/Cr/R/G/B accordingly. For YUV to RGB: din0/din1/din2/dout0/dout1/dout2 stands for Y/U/V/R/G/B accordingly. For RGB to YUV: din0/din1/din2/dout0/dout1/dout2 stands for R/G/B/Y/U/V accordingly. For YIQ to RGB: din0/din1/din2/dout0/dout1/dout2 stands for Y/I/Q/R/G/B accordingly. For RGB to YIQ: din0/din1/din2/dout0/dout1/dout2 stands for R/G/B/Y/I/Q accordingly. For RGB to YIQ: din0/din1/din2/dout0/dout1/dout2 stands for R/G/B/Y/I/Q accordingly. For YIQ to YUV: din0/din1/din2/dout0/dout1/dout2 stands for Y/I/Q/R/G/B accordingly.

When a Core type is selected as Custom, the user must manually enter the coefficient values in the GUI.

### **Full Precision Outputs**

The full precision output width is given by the following sum.

Fullwidth = Input Data Width + Coefficient Width + 2

When output data width Owidth is configured as Fullwidth, then the binary point position Bpoint in this case tells the scale factor for all the coefficients. Coefficients are multiplied by 2^Bpoint before quantization.

When output data width Owidth is less than (Fullwidth-Bpoint), the LSB of the output data is the (Bpoint-1)<sup>th</sup> bit of the full width output data, and the MSB of the output data is the (Owidth+Bpoint-1)<sup>th</sup> bit of the full width output data. In this case, binary point position is zero.

When output data width Owidth is larger than (Fullwidth-Bpoint), the LSB of the output data is the (Fullwidth-Owidth-1)<sup>th</sup> bit of the full width output data, and the MSB of the output data is the (Fullwidth-1)<sup>th</sup> bit of the full width output data. In this case, binary point position is (Bpoint+Owidth-Fullwidth).

# **Limited Precision Outputs**

The output setting can be used to configure the output data type and width. The output data type can be either configured as "Signed" or "Unsigned".

The following options are supported to deal with LSBs rounding:

- None Discards all bits to the right of the output least significant bit and leaves the output uncorrected.

- **Rounding up** Rounds up if the fractional part is exactly one-half (e.g. 2.5 will be rounded to 3, -2.5 will be rounded to -2).

- **Rounding away from zero** Rounds away from zero if the fractional part is exactly one-half (e.g. 2.5 will be rounded to 3, -2.5 will be rounded to -3).

- Rounding towards zero Rounds towards zero if the fractional part is exactly one-half (e.g. 2.5 will be rounded to 2, -2.5 will be rounded to -2).

- **Convergent rounding** Rounds to the nearest even value if the fractional part is exactly one-half (e.g. 2.5 will be rounded to 2, -2.5 will be rounded to -2, 3.5 will be rounded to 4, -3.5 will be rounded to -4).

The following options are supported to deal with MSBs overflow:

- Saturation The output is made equal to the maximum positive or negative value based on the sign bits.

- Wrap-around The MSBs are discarded without making any corrections.

# **Signal Descriptions**

The I/O port definitions are given in Table 2-2.

#### Table 2-2. Interface Signal Description

| Port          | Bits           | I/O         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|----------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All Configura | ations         |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| clk           | 1              | I           | Reference clock for input and output data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| rstn          | 1              | I           | System-wide asynchronous active-low reset signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| din0          | 8 - 16         | Ι           | Input data. When the sequential architecture is selected, this port is used to give input data for all the three input color planes in sequence. When the parallel architecture is selected, this port is used to give input data for the first input color plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| dout0         | 5 - 35         | 0           | Output data. When the sequential architecture is selected, this port is used to give output data for all the three output color planes in sequence. When the parallel architecture is selected, this port is used to give output data for the first output color plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| When Paralle  | el Architectur | e is Select | ed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| din1          | 8 - 16         | I           | Input data for second color plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| din2          | 8 - 16         | I           | Input data for third color plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| dout1         | 5 - 35         | 0           | Output data for second color plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| dout2         | 5 - 35         | 0           | Output data for third color plane. This port is always enabled when the parallel architecture is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Valid Signals | 5              |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| inpvalid      | 1              | I           | Input data valid. Indicates valid data is present on din0 (also on din1 and din2 when present). When the parallel architecture is selected, this port is optional. In this case this port is not used directly in the core but used to generate the outvalid signal after initial core latency. When the sequential architecture is selected, this port is always enabled. In this case, this port is used inside the core and also used to generate the outvalid signal after initial core latency. Also when the sequential architecture is selected, this signal should be asserted high for one clock cycle when valid data for the first input color plane is present on the din0 port. For the second and third input color planes data, this signal should be low. Input data for all the three input color planes should be applied at successive clock cycles without any gap. |

| outvalid      | 1              | 0           | Output data valid. Indicates valid data is present on dout0 (also on dout1 and dout2 when present). When the parallel architecture is selected, this port is optional. When the sequential architecture is selected, this port is always enabled and asserted high when the valid data is present for the first output color plane. During output data of second and third color planes outvalid is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Optional I/Os | S              | -           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| се            | 1              | 1           | Clock Enable. While this is de-asserted, the core will ignore all other synchronous inputs and maintain its current state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| sr            | 1              | 1           | Synchronous Reset. Asserted for at least one clock period duration to re-initialize the core. After synchronous reset, all internal registers are cleared and outvalid goes low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# **Timing Diagrams**

### Parallel Architecture Timing

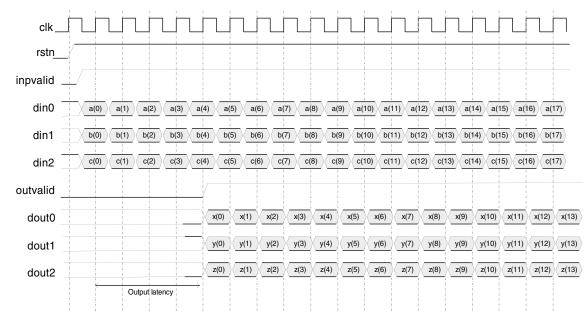

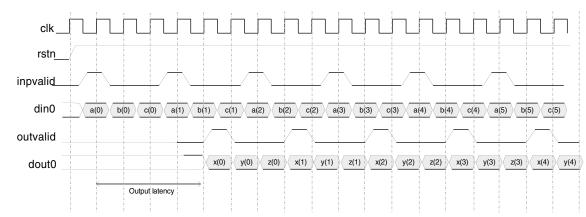

Figure 2-4 shows the input and output signal timing diagram for the parallel architecture. The input data for all the three color planes are applied simultaneously on the input ports din0, din1 and din2.

The signal inpvalid is asserted to indicate a valid input data present on the input ports. After a latency of a few cycles, the output data for all three color planes appears on the output ports dout0, dout1 and dout2. The signal outvalid is asserted to indicate valid output data present on the output ports.

#### Figure 2-4. Parallel Architecture

### **Sequential Architecture Timing**

Figure 2-5 shows the input and output signal timing for the sequential architecture. The input data for all three color planes are applied in sequence on the input port din0. The signal inpvalid is asserted to indicate the first color plane data on din0. In the following two cycles, the second and third color plane data are applied on din0. After a latency of a few cycles the output data for the first color plane appears on the output port dout0. The signal outvalid is asserted to indicate the first color plane data on dout0. In the following two cycles, the second and third color plane data are applied on din0. After a latency of a few cycles the output data for the first color plane appears on the output port dout0. The signal outvalid is asserted to indicate the first color plane data on dout0. In the following two cycles, the second and third color plane data appear on dout0.

#### Figure 2-5. Sequential Architecture

Chapter 3:

The IPexpress<sup>™</sup> or Diamond is used to create IP and architectural modules in the Diamond software. Refer to the IP Core Generation section for a description of how to generate the IP.

Table 3-1 provides the list of user-configurable parameters for the CSC IP core. The parameter settings are specified using the CSC IP core Configuration GUI in IPexpress.

| Parameters                         | Range/Options                                                                                                                                                                                                                                                                                                                                            | Default Value              |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Core Type                          |                                                                                                                                                                                                                                                                                                                                                          |                            |

| Core type                          | Custom<br>Computer RGB to YCbCr:SDTV<br>Computer RGB to YCbCr:HDTV<br>Studio RGB to YCbCr:SDTV<br>Studio RGB to YCbCr:HDTV<br>YCbCr:SDTV to Computer RGB<br>YCbCr:HDTV to Computer RGB<br>YCbCr:SDTV to Studio RGB<br>YCbCr:HDTV to Studio RGB<br>YUV to Computer RGB<br>Computer RGB to YUV<br>YIQ to Computer RGB<br>Computer RGB to YIQ<br>YIQ to YUV | Computer RGB to YCbCr:SDTV |

| Input Settings                     |                                                                                                                                                                                                                                                                                                                                                          |                            |

| Architecture                       | {Sequential, Parallel}                                                                                                                                                                                                                                                                                                                                   | Sequential                 |

| Input data type                    | {Signed, Unsigned}                                                                                                                                                                                                                                                                                                                                       | Unsigned                   |

| Input data width                   | {8, 10, 12, 16}                                                                                                                                                                                                                                                                                                                                          | 8                          |

| Coefficient precision width        | 9-18                                                                                                                                                                                                                                                                                                                                                     | 18                         |

| Implementation                     |                                                                                                                                                                                                                                                                                                                                                          |                            |

| Registered input                   | Yes or No                                                                                                                                                                                                                                                                                                                                                | Yes                        |

| <b>Optional Input/Output Ports</b> | 3                                                                                                                                                                                                                                                                                                                                                        |                            |

| се                                 | Yes or No                                                                                                                                                                                                                                                                                                                                                | No                         |

| sr                                 | Yes or No                                                                                                                                                                                                                                                                                                                                                | No                         |

| inpvalid/outvalid                  | Yes or No                                                                                                                                                                                                                                                                                                                                                | No                         |

| Output Settings                    | · · ·                                                                                                                                                                                                                                                                                                                                                    |                            |

| Output Data Type                   | Signed, Unsigned                                                                                                                                                                                                                                                                                                                                         | Unsigned                   |

| Output Data Width                  | 5-36                                                                                                                                                                                                                                                                                                                                                     | 8                          |

| Overflow                           | Saturation, Wrap-around                                                                                                                                                                                                                                                                                                                                  | Saturation                 |

| Rounding                           | None, Rounding up, Rounding away from zero, Rounding toward zero, convergent rounding                                                                                                                                                                                                                                                                    | None                       |

#### Table 3-1. Parameter Descriptions

# Input/Coefficient Tab

Figure 3-1 shows the content of the Input/Coefficient tab.

#### Figure 3-1. Input/Coefficient Tab

| Core type                     | Computer R'G'B' to ነ                          | /'CbCr:SDTV   |                  |

|-------------------------------|-----------------------------------------------|---------------|------------------|

| -Coefficient sett             | ng                                            | - 52          | 18 - X-          |

| dout0= 0.257                  | *din0+ 0.504                                  | *din1+0.098   | *din2+ 16.0      |

| lout1= -0.148                 | *din0+ -0.291                                 | *din1+ 0.439  | *din2+ 128.0     |

| dout2= 0.439                  | *din0+ -0.368                                 | *din1+ -0.071 | *din2+ 128.0     |

| Coeffi                        | data width 8<br>cient width 9<br>Tags width 1 |               |                  |

|                               |                                               |               |                  |

| Implementation                | 1. D                                          |               | put/output ports |

| Implementation<br>Use DSP Blo | ck                                            | Optional in   | put/output ports |

| Implementation                | ck                                            |               | put/output ports |

### Core Type

Selects between custom and pre-defined standard configurations.

### Architecture

Selects between parallel and sequential implementation architectures.

### Input Data Type

Signed or unsigned input data type

### Input Data Width

The bit width for the input color planes.

### **Coefficient Width**

The bit width for the input color planes.

### Use DSP Block

If this option is checked, the core will use the DSP Block for implementation (not applicable for LatticeSC/M).

### **Registered Input**

The inputs are registered, if this option is selected. The core inputs' set-up times will improve by registering the inputs. This option is useful when the input data is provided on the device pins.

### Keep Data at Blank Time

This option is to keep the auxiliary data of the Video stream unchanged during blank time.

### **Connect Reset Port to GSR**

If this option is checked, the GSR is instantiated and used to route the CSC's rstn input. Using GSR improves the utilization and performance of the CSC IP. However, if GSR is used an active input in rstn will reset most of the FPGA components as well. This option must be checked to enable the hardware evaluation capability for this IP.

#### се

Input port ce is added to the core when checked.

#### sr

Input port sr is added to the core when checked.

### inpvalid/outvalid

If Architecture is selected as Sequential, then this is always checked. If architecture is selected as Parallel, then this is optional. If checked, this option will add inpvalid and outvalid ports to the core.

# **Output Tab**

Figure 3-2 shows the content of the Output/Coefficient tab.

#### Figure 3-2. Output/Coefficient Tab

| Ouput latency       |                      |

|---------------------|----------------------|

| Latency             | 9                    |

| Output setting      |                      |

| Output data type    | Unsigned 💌           |

| Output data width   | 8                    |

| Precision control   | 20-10 AF             |

| Overflow Saturation | Rounding Rounding up |

### **Output Latency**

This provides the output latency for the selected core configuration.

### **Output Data Type**

Signed or unsigned output data type

### **Output Data Width**

The bit width for the output color planes

### Overflow

This option allows the user to specify what kind of overflow control is to be used. This parameter is available whenever there is a need to drop some of the MSBs from the true output. If the selection is Saturation, the output value is clipped to the maximum, if positive or minimum, if negative, while discarding the MSBs. If the selection is Wraparound, the MSBs are simply discarded without making any correction.

### Rounding

This option allows the user to specify the rounding method when there is a need to drop one or more LSBs from the true output.

# **IP Core Generation**

This chapter provides information on how to generate the Lattice CSC IP core using the Diamond software IPexpress tool, and how to include the core in a top-level design.

# Licensing the IP Core

An IP core- and device-specific license is required to enable full, unrestricted use of the CSC IP core in a complete, top-level design. Instructions on how to obtain licenses for Lattice IP cores are given at:

http://www.latticesemi.com/products/intellectualproperty/aboutip/isplevercoreonlinepurchas.cfm

Users may download and generate the CSC IP core and fully evaluate the core through functional simulation and implementation (synthesis, map, place and route) without an IP license. The CSC IP core also supports Lattice's IP hardware evaluation capability, which makes it possible to create versions of the IP core that operate in hardware for a limited time (several hours) without requiring an IP license. See the Hardware Evaluation section for further details. However, a license is required to enable timing simulation, to open the design in the Diamond EPIC tool, and to generate bitstreams that do not include the hardware evaluation timeout limitation.

# **Getting Started**

The CSC IP core is available for download from the Lattice IP server using the IPexpress tool. The IP files are automatically installed using InstallShield technology in any user-specified directory. After the IP core has been installed, the IP core will be available in the IPexpress GUI dialog box shown in Figure 4-1.

The Diamond IPexpress tool GUI dialog box for the CSC IP core is shown in Figure 4-1. To generate a specific IP core configuration, the user specifies:

- Project Path Path to the directory where the generated IP files will be loaded.

- File Name "username" designation given to the generated IP core and corresponding folders and files.

- (Diamond) Module Output Verilog or VHDL.

- Device Family Device family to which IP is to be targeted (e.g. MachXO2, ECP5, LatticeECP3, etc.). Only families that support the particular IP core are listed.

- Part Name Specific targeted part within the selected device family.

Figure 4-1. IPexpress Dialog Box (Diamond Version)

| 👫 IPexpress                                                                                                                                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Eile Help                                                                                                                                    |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| ] ] 🖳 🥔 😂 🏷 😫 🛍                                                                                                                              |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| Neme<br>→ Module<br>→ Architecture_Modules<br>→ Architecture_Modules<br>→ DSP_Modules<br>→ Memory_Modules<br>→ SP<br>→ Color Space Converter | Version<br>3.0 | Color Space Converter 3.0         Macro Type:       User Configurable IP       Version:       3.0         IP Name:       Color Space Converter         Project Path:       #13.4_x64/examples/CSC_test       Browse         File Name:       CSC_Core0       Module Output:       Version:         Module Output:       Version       ▼         Device Family:       LatticeECP3       Part Name:       LFE3-150EA-6FN1156C         Synthesis:       SynplifyPro |   |

| <b>•</b>                                                                                                                                     |                | Configuration About                                                                                                                                                                                                                                                                                                                                                                                                                                              | / |

Note that if the IPexpress tool is called from within an existing project, Project Path, Module Output, Device Family and Part Name default to the specified project parameters. Refer to the IPexpress tool online help for further information.

To create a custom configuration, the user clicks the **Customize** button in the IPexpress tool dialog box to display the CSC IP core Configuration GUI, as shown in Figure 4-2. From this dialog box, the user can select the IP parameter options specific to their application. Refer to the Parameter Settings section for more information on the CSC IP core parameter settings.

Figure 4-2. Configuration GUI (Diamond Version)

E

| Color Space Converter              | Input/coefficient   | output \            |               |                  |

|------------------------------------|---------------------|---------------------|---------------|------------------|

|                                    | Core type           | omputer R'G'B' to Y | CbCr:SDTV     | -                |

| 17                                 | Coefficient setting | 1                   |               |                  |

| ► clk                              | dout0= 0.257        | *din0+ 0.504        | *din1+ 0.098  | *din2+ 16.0      |

|                                    | dout1= -0.148       | *din0+ -0.291       | *din1+ 0.439  | *din2+ 128.0     |

| ► ce                               | dout2= 0.439        | *din0+ -0.368       | *din1+ 0.071  | *din2+ 128.0     |

| ► rstn                             | Input setting       |                     |               |                  |

| S 0803                             |                     | hitecture 🔿 Sequ    | ential 📀      | Parallel         |

|                                    | Support VSS         | IP Suite 💽 Yes      | С             | No               |

|                                    |                     | lata type Unsigned  |               |                  |

|                                    |                     | ata width 8         | <u> </u>      |                  |

|                                    |                     |                     |               |                  |

| ► B[7:0] Y[7:0]                    |                     | ent width 9         | <b>_</b>      |                  |

|                                    | Ta                  | gs width 1          |               |                  |

| ► G[7:0] Cb[7:0]                   | Implementation      |                     | - Optional in | put/output ports |

| ► B[7:0] Cr(7:0]                   | Use DSP Block       |                     | I ⊂ ce        | pus carpar porto |

|                                    | Registered inpu     |                     | □ sr          |                  |

| tags_in[0:0] tags_out[0:0]         | Keep data at bl     |                     |               | loutualid.       |

| entrage_interel stage_entral state |                     |                     |               | Outvaliu         |

| inpvalid outvalid                  |                     |                     |               |                  |

|                                    |                     |                     |               |                  |

|                                    |                     |                     |               |                  |

|                                    |                     |                     |               |                  |

|                                    |                     |                     |               |                  |

| mport IPX to Diamond project       | Generate            |                     | Close         | Help             |

# **IPexpress-Created Files and Top-Level Directory Structure**

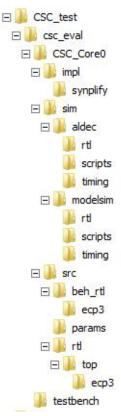

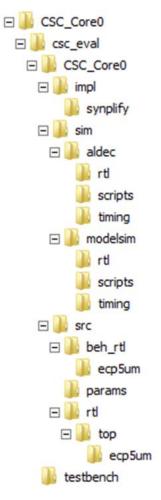

When the user clicks the **Generate** button in the IP Configuration dialog box, the IP core and supporting files are generated in the specified "Project Path" directory. The directory structure of the generated files is shown in Figure 4-3.

#### Figure 4-3. LatticeECP3 CSC IP Core Directory Structure

The design flow for IP created with the IPexpress tool uses a post-synthesized module (NGO) for synthesis and a protected model for simulation. The post-synthesized module is customized and created during the IPexpress tool generation. The protected simulation model is not customized during the IPexpress tool process, and relies on parameters provided to customize behavior during simulation. Table 4-1 provides a list of key files and directories created by the IPexpress tool and how they are used. The IPexpress tool creates several files that are used throughout the design cycle. The names of most of the created files are customized to the user's module name specified in the IPexpress tool.

| Table | 4-1. | File | List |

|-------|------|------|------|

|-------|------|------|------|

| File                            | Sim | Synthesis<br>Diamond | Description                                                                                                                                          |

|---------------------------------|-----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| <username>_inst.v</username>    |     |                      | This file provides an instance template for the IP.                                                                                                  |

| <username>.v</username>         | Yes |                      | This file provides the CSC core for simulation.                                                                                                      |

| <username>_beh.v</username>     | Yes |                      | This file provides a behavioral simulation model for the CSC IP core.                                                                                |

| <username>_bb.v</username>      |     | Yes                  | This file provides the synthesis black box for the user's synthesis.                                                                                 |

| <username>.ngo *.ngo</username> |     | Yes                  | The ngo files provide the synthesized IP core used by Diamond. This file needs to be pointed to by the Build step by using the search path property. |

#### Table 4-1. File List

| File                              | Sim      | Synthesis<br>Diamond | Description                                                                                                                                                                                                                |

|-----------------------------------|----------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u<i>username&gt;.lpc</u<i>       |          |                      | This file contains the IPexpress tool options used to recreate or modify the core in the IPexpress tool.                                                                                                                   |

| <username>_top.[v,vhd]</username> | Optional | Optional             | This file provides a module which instantiates the CSC core. This file can be easily modified for the user's instance of the CSC core. This file is located in the csc_eval/ <username>/src/rtl/top/ directory.</username> |

Table 4-2 provides a list of key additional files providing IP core generation status information and command line generation capability are generated in the user's project directory.

#### Table 4-2. Additional Files

| File                               | Description                                  |  |

|------------------------------------|----------------------------------------------|--|

| <username>_generate.log</username> | This is the synthesis and map log file.      |  |

| <username>_gen.log</username>      | This is the IPexpress IP generation log file |  |

## Instantiating the Core

The generated CSC IP core package includes black-box (*<username>\_bb.v*) and instance (*<user-name>\_inst.v*) templates that can be used to instantiate the core in a top-level design. An example RTL top-level reference source file that can be used as an instantiation template for the IP core is provided in

\<project\_dir>\csc\_eval\<username>\src\rtl\top. Users may also use this top-level reference as the starting template for the top-level for their complete design.

# **Running Functional Simulation**

Simulation support for the CSC IP core is provided for Aldec Active-HDL (Verilog and VHDL) simulator, Mentor Graphics ModelSim simulator. The functional simulation includes a configuration-specific behavioral model of the CSC IP core. The test bench sources stimulus to the core, and monitors output from the core. The generated IP core package includes the configuration-specific behavior model (*<username>\_beh.v*) for functional simulation in the "Project Path" root directory. The simulation scripts supporting ModelSim evaluation simulation is provided in

\<project\_dir>\csc\_eval\<username>\sim\modelsim\scripts. The simulation script supporting Aldec evaluation simulation is provided in

\<project\_dir>\csc\_eval\<username>\sim\aldec\scripts. Both ModelSim and Aldec simulation is supported via test bench files provided in

\<project\_dir>\csc\_eval\testbench. Models required for simulation are provided in the corresponding \models folder. Users may run the Aldec evaluation simulation by doing the following:

- 1. Open Active-HDL.

- 2. Under the Tools tab, select Execute Macro.

- 3. Browse to folder \<project\_dir>\csc\_eval\<username>\sim\aldec\scripts and execute one of the "do" scripts shown.

Users may run the ModelSim evaluation simulation by doing the following:

- 1. Open ModelSim.

- 2. Under the File tab, select **Change Directory** and choose the folder <project\_dir>\csc\_eval\<username>\sim\modelsim\scripts.

- 3. Under the Tools tab, select **Execute Macro** and execute the ModelSim "do" script shown.

**Note**: When the simulation completes, a pop-up window will appear asking "Are you sure you want to finish?" Answer **No** to analyze the results. Answering **Yes** closes ModelSim.

# Synthesizing and Implementing the Core in a Top-Level Design

The CSC IP core itself is synthesized and provided in NGO format when the core is generated through IPexpress. You may combine the core in your own top-level design by instantiating the core in your top-level file as described in the Instantiating the Core section and then synthesizing the entire design with either Synplify or Precision RTL Synthesis.

The following text describes the evaluation implementation flow for Windows platforms. The flow for Linux and UNIX platforms is described in the Readme file included with the IP core.

The top-level file <userame>\_top.v is provided in

<project\_dir>\csc\_eval<<username>\src\rtl\top. Push-button implementation of the reference design is supported via the project file <username>.ldf located in \<project\_dir>\csc\_eval<<username>\impl\(synplify or precision).

To use this project file in Diamond:

- 1. Choose File > Open > Project.

- 2. Browse to

$\csc_eval<username>\impl\symplify (or precision) in the Open Project dialog box.$

- 3. Select and open <username>\_.ldf. At this point, all of the files needed to support top-level synthesis and implementation will be imported to the project.

- 4. Select the Process tab in the left-hand GUI window.

- 5. Implement the complete design via the standard Diamond GUI flow.

### **Hardware Evaluation**

The CSC IP core supports Lattice's IP hardware evaluation capability, which makes it possible to create versions of the IP core that operate in hardware for a limited period of time (several hours) without requiring the purchase of an IP license. It may also be used to evaluate the core in hardware in user-defined designs.

### **Enabling Hardware Evaluation in Diamond**

Choose **Project > Active Strategy > Translate Design Settings**. The hardware evaluation capability may be enabled/disabled in the Strategy dialog box. It is enabled by default.

# **Updating/Regenerating the IP Core**

By regenerating an IP core with the IPexpress tool, you can modify any of its settings including device type, design entry method, and any of the options specific to the IP core. Regenerating can be done to modify an existing IP core or to create a new but similar one.

### **Regenerating an IP Core in Diamond**

To regenerate an IP core in Diamond:

- 1. In IPexpress, click the **Regenerate** button.

- 2. In the Regenerate view of IPexpress, choose the IPX source file of the module or IP you wish to regenerate.

- 3. IPexpress shows the current settings for the module or IP in the Source box. Make your new settings in the Target box.

- 4. If you want to generate a new set of files in a new location, set the new location in the **IPX Target File** box. The base of the file name will be the base of all the new file names. The IPX Target File must end with an .ipx extension.

- 5. Click **Regenerate.** The module's dialog box opens showing the current option settings.

- 6. In the dialog box, choose the desired options. To get information about the options, click Help. Also, check the About tab in IPexpress for links to technical notes and user guides. IP may come with additional information. As the options change, the schematic diagram of the module changes to show the I/O and the device resources the module will need.

- 7. To import the module into your project, if it's not already there, select **Import IPX to Diamond Project** (not available in stand-alone mode).

- 8. Click Generate.

- 9. Check the Generate Log tab to check for warnings and error messages.

#### 10.Click Close.

The IPexpress package file (.ipx) supported by Diamond holds references to all of the elements of the generated IP core required to support simulation, synthesis and implementation. The IP core may be included in a user's design by importing the .ipx file to the associated Diamond project. To change the option settings of a module or IP that is already in a design project, double-click the module's .ipx file in the File List view. This opens IPexpress and the module's dialog box showing the current option settings. Then go to step 6 above.

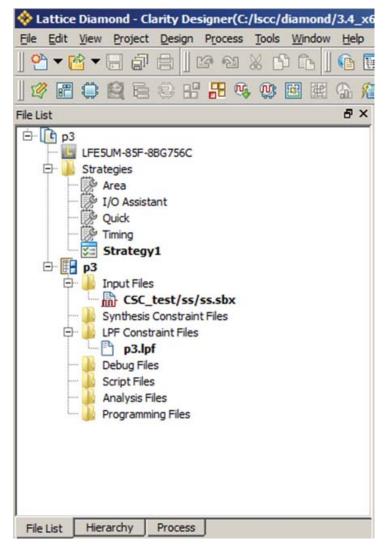

# **IP Core Generation in Clarity Designer**

### **Getting Started**