04/23/2019

# Multi-Mode PWM Controller of Flyback with Integrated BNI/BNO and Bulk cap. OVP

**REV: 01**

### **General Description**

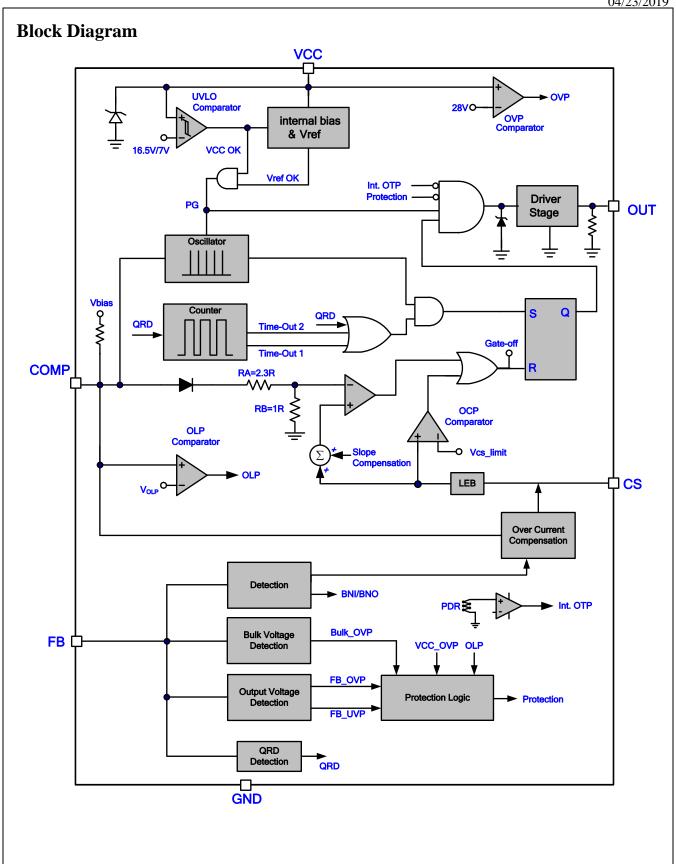

In order to enhance the efficiency performance, the LD5523NGL-M integrates the multi-mode PWM controller, which consists of Quasi-Resonant (QR) PWM control for light load condition and Continue Conduction Mode (CCM) for heavy load condition. Moreover, the QR controller not only gains the system performance, but also brings the worse EMI capability, while the frequency swapping function of LD5523NGL-M can reduce the EMI emission of SMPS and helps the power circuit designers to simply deal with EMI filter and saves several component and developing time.

The LD5523NGL-M is implemented in SOT-26 package, and includes the comprehensive protection function, such as Over Load Protection (OLP), Over Voltage Protection (OVP), Output Short Circuit Protection (OSCP) and internal Over Temperature Protection (OTP). Furthermore, the programmable brown-in/out and bulk cap. OVP protection is built-in.

### **Features**

- Secondary-side feedback control with quasi-resonant + CCM operation

- Low Startup Current (<1μA)</li>

- 0.285mA Ultra-low operating current at light load

- Current Mode Control with Cycle-by-Cycle Current

Limit

- Green Mode Control

- UVLO (Under Voltage Lockout)

- LEB (Leading-Edge Blanking) on CS Pin

- VCC OVP (Over Voltage Protection)

- Adj. OVP / UVP on FB pin

- Adj. BNI/BNO, Bulk cap. OVP on FB pin

- OLP (Over Load Protection)

- External OTP (Over Temperature Protection) on CS Pin

- Internal OTP (Over Temperature Protection)

- SDSP (Secondary Diode Short Protection)

- Gate Source/Sink Capability: 210mA/-350mA @ output pin with 33nF capacitor.

### **Applications**

Switching AC/DC Adaptor

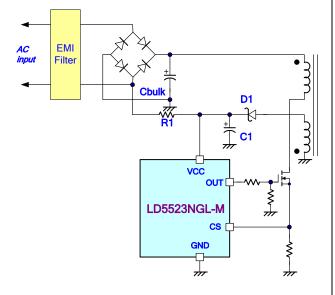

# Typical Application AC EMI Input Filter OUT OUT OUT Photocoupler Photocoupler

04/23/2019

### **Pin Configuration**

Y : Year code (D: 2004, E: 2005.....)

W : Week code PP : Production code 123N : LD5523NGL-M

### **Ordering Information**

| Part number | Package |                 | TOP MARK   | Shipping          |  |

|-------------|---------|-----------------|------------|-------------------|--|

| LD5523NGL-M | SOT-26  | (Green Package) | YW1/23N/PP | 3000 /tape & reel |  |

The LD5523NGL-M is RoHs compliant/ green packaged.

### **Protection Mode**

| Product<br>Name | Switching<br>Freq. | VCC_OVP  | FB_OVP   | OSCP     | OLP      | BNI/BNO  | Bulk cap<br>OVP | CS_OTP   | SDSP     |

|-----------------|--------------------|----------|----------|----------|----------|----------|-----------------|----------|----------|

| LD5523NGL-M     | 65kHz              | Auto     | Auto     | Auto     | Auto     | Auto     | Auto            | Auto     | Auto     |

| LD3323NOL-W     | OOKI IZ            | recovery | recovery | recovery | recovery | recovery | recovery        | recovery | recovery |

### **Pin Descriptions**

| NAME | PIN | FUNCTION                                                           |

|------|-----|--------------------------------------------------------------------|

| GND  | 1   | Ground                                                             |

| COMP | 2   | Output of the error amplifier for voltage compensation             |

| FB   | 3   | Auxiliary voltage sense, brown in/out and Quasi Resonant detection |

| CS   | 4   | Current sense pin, connect to sense the MOSFET current             |

| VCC  | 5   | Supply voltage pin                                                 |

| OUT  | 6   | Gate drive output to drive the external MOSFET                     |

04/23/2010

04/23/2019

### **Absolute Maximum Ratings**

| Supply Voltage VCC,                                       | -0.3V ~ 30V      |

|-----------------------------------------------------------|------------------|

| COMP                                                      | -0.3V ~ 12V      |

| FB, CS                                                    | -0.3V ~ 7V       |

| OUT                                                       | -0.3V ~ VCC+0.3V |

| Maximum Junction Temperature_                             | 150°C            |

| Storage Temperature Range                                 | -65°C ~ 150°C    |

| Package Thermal Resistance (SOT-26, $\theta$ JA)          | 200°C/W          |

| Power Dissipation (SOT-26, at Ambient Temperature = 85°C) | 200mW            |

| Lead temperature (Soldering, 10sec)                       | 260°C            |

| ESD Voltage Protection, Human Body Model                  | 2.5 KV           |

| ESD Voltage Protection, Machine Model                     | 250 V            |

|                                                           |                  |

### Caution:

Stress exceeding maximum ratings may damage the device. Maximum ratings are stress ratings only. Functional operation above the recommended operating conditions is not implied. Extended exposure to stress above recommended operating conditions may affect device reliability.

### **Recommended Operating Conditions**

| Item                                         | Min. | Max. | Unit |

|----------------------------------------------|------|------|------|

| Operating Junction Temperature               | -40  | 125  | °C   |

| Supply VCC Voltage                           | 8.0  | 26.5 | V    |

| VCC Capacitor                                | 3.3  | 10   | μF   |

| Start-up resistor Value (AC Side, Half Wave) | 400K | 2M   | Ω    |

| Comp Pin Capacitor (X7R type)                | 330  | 4700 | pF   |

| CS Pin Capacitor Value                       | 47   | 470  | pF   |

### Note:

- 1. It's essential to connect VCC pin with a SMD ceramic capacitor ( $0.1\mu F \sim 0.47\mu F$ ) to filter out the undesired switching noise for stable operation. This capacitor should be placed close to IC pin as possible.

- 2. It's also essential to connect a capacitor to COMP to filter out the undesired switching noise for stable operation.

- 3. The small signal components should be placed close to IC pin as possible.

04/23/2019

### **Electrical Characteristics**

(T<sub>A</sub> = +25°C unless otherwise stated, VCC=15.0V)

| PARAMETER                     | CONDITIONS                                                 | SYMBOL                 | MIN  | TYP   | MAX  | UNITS |

|-------------------------------|------------------------------------------------------------|------------------------|------|-------|------|-------|

| Supply Voltage (VCC Pin)      |                                                            |                        |      |       |      |       |

| Startup Current               |                                                            | Icc_st                 |      |       | 1    | μА    |

|                               | V <sub>COMP</sub> =0V, OUT=1nF                             | ICC_OP1                |      | 0.285 |      | mA    |

| Operating Current             | V <sub>COMP</sub> =1.7V, OUT=1nF<br>I <sub>FB</sub> =200μA | I <sub>CC_OP2</sub>    |      | 2.4   |      | mA    |

| (with 1nF load on OUT pin)    | Auto current protection                                    | ICC_OPA1               |      | 0.6   |      | mA    |

|                               | Brown in (Before the first pulse)/ Brown out               | ICC_OPA3               | 0.7  | 1.1   | 1.5  | mA    |

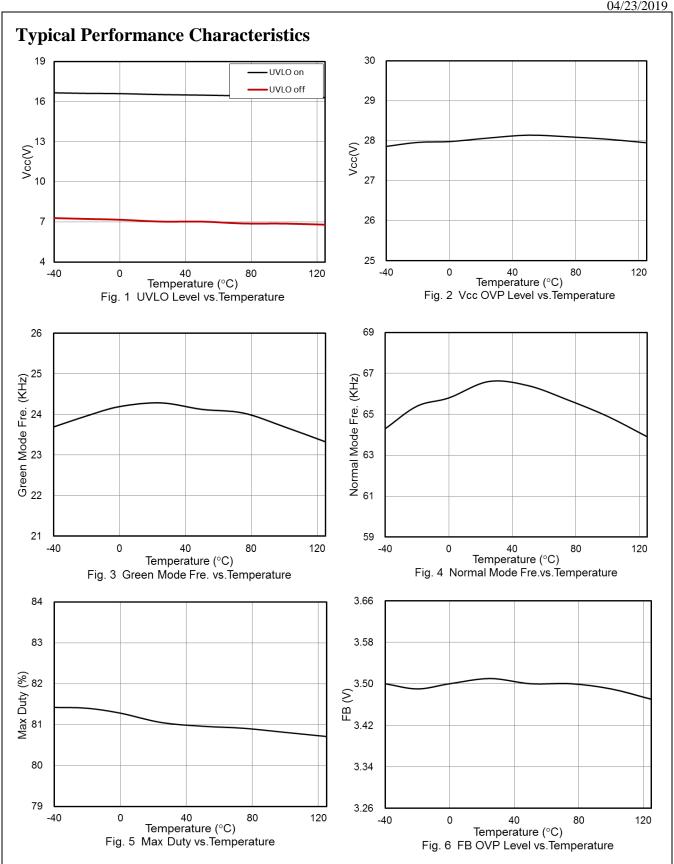

| UVLO(OFF)                     |                                                            | Vcc_off                | 6    | 7     | 8    | V     |

| UVLO(ON)                      |                                                            | Vcc_on                 | 15.5 | 16.5  | 17.5 | V     |

| VCC OVP Level                 |                                                            | Vcc_ovp                | 27   | 28    | 29   | V     |

| VCC OVP de-bounce time        |                                                            | T <sub>VCC_OVP</sub>   |      | 8     |      | Cycle |

| Voltage Feedback (COMP Pin)   |                                                            |                        |      |       |      |       |

| Short Circuit Current         | V <sub>COMP</sub> =0V                                      | Ісомр                  |      | 0.116 |      | mA    |

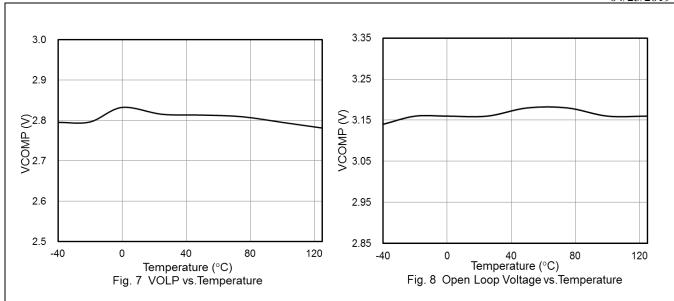

| Open Loop Voltage             | (1)                                                        | V <sub>COMP_OPEN</sub> |      | 3.15  |      | V     |

| Min. OCP Compensation Current | I <sub>FB</sub> =100μA <sup>(1)</sup>                      | IOCP_MIN               |      | 71    |      | μА    |

| Max. OCP Compensation Current | I <sub>FB</sub> =300μA                                     | IOCP_MAX               | 200  | 225   | 250  | μА    |

| Current Sensing (CS Pin)      |                                                            |                        |      |       |      |       |

| Maximum Input Voltage         |                                                            | Vcs_limit              | 0.48 | 0.5   | 0.52 | V     |

| Leading Edge Blanking Time    |                                                            | T <sub>LEB</sub>       |      | 275   |      | ns    |

| Internal Slope Compensation   | *ton>3µs to D <sub>MAX</sub> . (Linearly increase), (1)    | V <sub>SLP_L</sub>     |      | 165   |      | mV    |

| Delay to Output               | (1)                                                        | $T_{PD}$               |      | 80    |      | ns    |

| BNO Protection (FB Pin)       |                                                            |                        |      |       |      |       |

| Brown In Trip Level           |                                                            | I <sub>BNI</sub>       | 90   | 95    | 100  | μА    |

| BNO Hysteresis                |                                                            | I <sub>BNO_HYS</sub>   |      | 10    |      | μА    |

| Brown Out De-bounce Time      | V <sub>COMP</sub> =1.7V                                    | T <sub>DB_BNO</sub>    |      | 75    |      | ms    |

| Bulk Cap OVP                  |                                                            | I <sub>BULK_OVP</sub>  |      | 418   |      | μА    |

| Bulk Cap OVP delay            |                                                            | T <sub>FB_BOVP</sub>   |      | 500   |      | ms    |

04/23/2019

| PARAMETER                     | CONDITIONS                                            | SYMBOL                | MIN  | TYP  | MAX  | UNITS |

|-------------------------------|-------------------------------------------------------|-----------------------|------|------|------|-------|

| QRD (Quasi Resonant Detect    | ion, FB Pin)                                          |                       |      |      |      |       |

| FB OVP Trip voltage Level     |                                                       | V <sub>FB_OVP</sub>   | 3.3  | 3.5  | 3.7  | V     |

| FB OVP De-bounce Time         |                                                       | T <sub>FB_OVP</sub>   |      | 8    |      | Cycle |

| FB UVP Trip voltage Level     | (1)                                                   | $V_{FB\_UVP}$         |      | 0.8  |      | V     |

| QRD Trip Level                | (1)                                                   | IQRD                  |      | 20   |      | μА    |

| OTP (Over Temperature, CS I   | Pin)                                                  | "                     |      |      | •    |       |

| CS OTP Level                  | Vcs_limit                                             | V <sub>CS_OTP</sub>   | 0.48 | 0.5  | 0.52 | V     |

| CS OTP de-bounce time         | (1)                                                   | T <sub>CS_OTP</sub>   |      | 5.4  |      | ms    |

| Oscillator for Switching Freq | uency                                                 |                       |      | 1    | · I  | I     |

| CCM Frequency                 |                                                       | F <sub>CCM</sub>      | 60   | 65   | 70   | kHz   |

| Frequency Swapping            | (1)                                                   | F <sub>SW_MOD</sub>   |      | ±8   |      | %     |

| Green Mode Frequency          |                                                       | F <sub>SW_GREEN</sub> | 21   | 24   | 27   | kHz   |

| Temp. Stability               | (1)                                                   | F <sub>SW_TS</sub>    |      | 3    | 5    | %     |

| Voltage Stability             | VCC =9V~24V <sup>(1)</sup>                            | F <sub>SW_VS</sub>    |      |      | 1    | %     |

| Maximum Duty                  | (1)                                                   | D <sub>MAX</sub>      |      | 81   |      | %     |

| Gate Drive Output (OUT Pin)   |                                                       |                       |      |      |      |       |

| Output Low Level              | VCC =15V, Io=20mA <sup>(1)</sup>                      | VoL                   |      |      | 1    | V     |

| Output High Level             | VCC =15V, Io=20mA                                     | Vон                   | 9    |      | 14   | V     |

| Rising Time                   | VCC =15V C <sub>L</sub> =1000pF                       | Tr                    |      | 280  |      | ns    |

| Falling Time                  | VCC =15V C <sub>L</sub> =1000pF                       | Tf                    |      | 30   |      | ns    |

| Output High Clamp Level       | VCC =18V                                              | V <sub>O_CLAMP</sub>  |      | 11.5 |      | V     |

| Soft Start                    |                                                       |                       |      |      |      | 1     |

| Soft Start Time               | $V_{\text{CS\_OFF}}$ from 0.2V to 0.5V <sup>(1)</sup> | Tss                   |      | 7    |      | ms    |

| SDSP (Secondary Diode Sho     | rt Protection)                                        |                       |      |      |      |       |

| SDSP CS Pin Level             | Secondary diode short                                 | Vcs_sdsp              |      | 1.3  |      | V     |

| De-bounce Cycle               | (1)                                                   | $T_{D\_SDSP}$         |      | 4    |      | Cycle |

| Open Loop Protection          |                                                       |                       |      |      |      |       |

| OLP Trip Level                |                                                       | VOLP                  |      | 2.8  |      | V     |

| OLP delay time                | After soft-start                                      | T <sub>D_OLP</sub>    |      | 210  |      | ms    |

| On Chip OTP (Over Temperate   | ture Protection)                                      |                       |      |      |      |       |

| OTP Level                     | (1,2)                                                 | TINOTP                |      | 140  |      | °C    |

|                               |                                                       |                       |      |      |      |       |

### Notes:

- 1. Guaranteed by design.

- 2. The threshold temperature for enabling the output again and resetting the latch after OTP has been activated.

04/23/2019

04/23/2019

# Application Information Operation Overview

The LD5523NGL-M is built in the multi-mode PWM controller, in which operates a constant frequency to achieve the CCM as heavy load. For demanding higher power efficiency and power-saving in light load condition, the LD5523NGL-M implements QR function to allow the valley switching and accomplish zero voltage switching (ZVS). Under different load conditions, LD5523NGL-M provides the different solutions for achieving higher efficiency and performance.

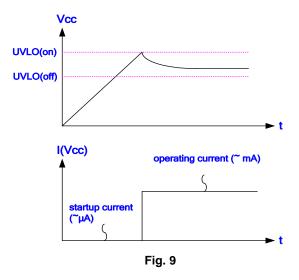

### **Under Voltage Lockout (UVLO)**

An UVLO comparator is implemented in it to detect the voltage on the VCC pin. It would assure the supply voltage enough to turn on the LD5523NGL-M PWM controllers and further to drive the power MOSFET. As shown in Fig. 9, a hysteresis is built in to prevent the shutdown from the voltage dip during startup. The turn-on and turn-off threshold level are set at 16.5V and 7V, respectively.

### **Startup Current and Startup Circuit**

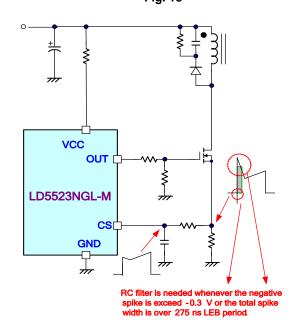

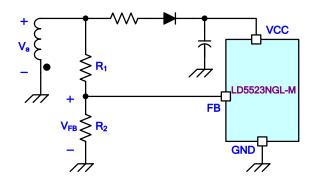

The typical startup circuit to generate the LD5523NGL-M VCC is shown in Fig. 10. During the startup transient, the VCC is lower than the UVLO threshold thus there is no

gate pulse produced from LD5523NGL-M to drive power MOSFET. Therefore, the current through R1 will provide the startup current and to charge the capacitor C1. Whenever the VCC voltage is high enough to turn on the LD5523NGL-M and further to deliver the gate drive signal, the supply current is provided from the auxiliary winding of the transformer.

Lower startup current requirement on the PWM controller will help to increase the value of R1 and then reduce the power consumption on R1. By using CMOS process and the special circuit design, the maximum startup current of LD5523NGL-M is only  $1\mu A.$  If a higher resistance value of R1 is chosen, it usually takes more time to start up. To select the value of R1 and C1 carefully will optimize the power consumption and startup time.

Fig. 10

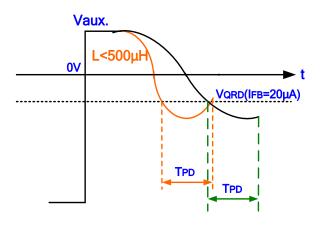

### **QR Mode Detection**

The transformer will be demagnetized after the main power MOSFET turns off. A quasi resonant signal will be detected from auxiliary winding by FB pin through the external resister.

As soon as the current of the secondary side diode is down to zero during MOSFET-off period, the transformer's core is demagnetized completely. V<sub>DS</sub> of MOSFET will

04/23/2019

resonate in discontinuous current mode. The resonance frequency (FQR) will be obtained as below.

$$F_{QR} = \frac{1}{2\pi\sqrt{L_m * C_R}} (Hz)$$

L<sub>M</sub> = Inductance of primary winding

C<sub>R</sub> = Resonance equivalent parasitic capacitance

If  $V_{DS}$  voltage falls to resonant valley level from max plateau value, the QRD comparator will be tripped while FB pin current is close to  $20\mu A$ .

However, the QR detection will be influenced by propagation delay. If inductance of primary winding is less than  $500\mu H$ , there is no valley detection in Vds (as shown in Fig. 11).

Fig. 11

### Voltage Feedback Loop

The voltage feedback signal is provided from the TL431 at the secondary side through the photo-coupler to the COMP pin of the LD5523NGL-M. Similar to UC3842, the LD5523NGL-M would without voltage offset to feed the voltage divider at the ratio of RA and RB, that is,

$$V_{-}(PWM_{COMPARATOR}) = \frac{RB}{RA + RB} \times V_{COMP}$$

A pull-high resistor is embedded internally and therefore no external one is required.

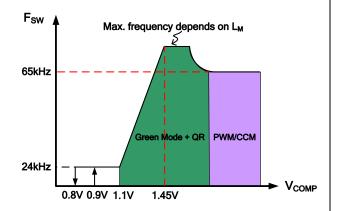

The LD5523NGL-M integrates the multi-mode PWM controller, and for enhance the light load efficiency, the

comp pin value corresponding to the frequency is as shown in Fig. 12 ( $I_{FB}$ <215uA).

Fig. 12

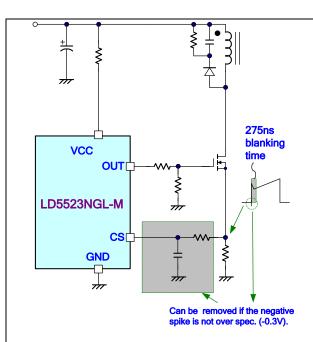

### **Current Sensing, Leading Edge Blanking**

The typical current mode of PWM controller feedbacks both current signal and voltage signal to close the control loop and achieve regulation. The LD5523NGL-M detect the primary MOSFET current from the CS pin, which is not only for the peak current mode control but also for the pulse-by-pulse current limit. The maximum voltage threshold of the current sensing pin sets at 0.5V. From above, the MOSFET peak current can be obtained from below.

$$I_{PEAK(MAX)} = \frac{0.5V}{R_{CS}}$$

A 275ns leading-edge blanking (LEB) time is included in the input of CS pin to prevent the false-trigger from the current spike. In the low power application, if the total pulse width of the turn-on spike is less than 275ns and the negative spike on the CS pin doesn't exceed -0.3V, it could remote the R-C filter (as shown in the Fig. 13).

However, the total pulse width of the turn-on spike is decided by the output power, circuit design and PCB layout. It is strongly recommended to adopt a smaller R-C filter (as shown in Fig. 14) for higher power application to avoid the CS pin being damaged by the negative turn-on spike.

04/23/2019

Fig. 13

Fig. 14

### **Output Stage and Maximum Duty**

An output stage of a CMOS buffer, with typical 350mA driving capability, is incorporated to drive a power MOSFET directly. The maximum duty of LD5523NGL-M is limited to 81% avoid detecting QR fail.

### **CCM Switching Frequency Clamp**

According to the QR operation principle, the switching frequency is inversely proportional to the output power. Therefore, as the output power increases, the switching frequency can become rather low without limiting. The CCM switching frequency of LD5523NGL-M is clamped at 65 kHz internally to provide the optimized operations by considering the EMI performance, thermal treatment, component sizes and transformer design.

# Over Voltage Protection on VCC Pin (VCC OVP) - Auto Recovery

The  $V_{GS}$  ratings of the nowadays power MOSFETs are often limited up to max. 28V. To prevent the  $V_{GS}$  from the fault condition, LD5523NGL-M is implemented with an OVP function on VCC. Whenever the VCC voltage is higher than the OVP threshold voltage, the output gate drive circuit will be shutdown simultaneously thus to stop the switching of the power MOSFET until the next UVLO(ON).

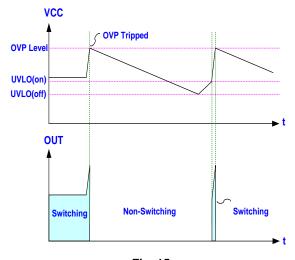

The VCC OVP function in LD5523NGL-M is an auto-recovery type protection. The Fig. 15 shows its operation.

On the other hand, if the OVP condition is removed, the VCC level will get back to normal level and the output will automatically return to the normal operation.

Fig. 15

04/23/2019

# Over Load Protection (OLP) - Auto Recovery

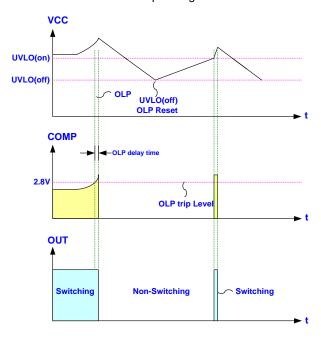

To protect the circuit from damage due to over-load condition and short or open-loop condition, the LD5523NGL-M is implemented with smart OLP function. It also features auto-recovery function; see Fig. 16 for the waveform. In case of fault condition, the feedback system will force the voltage loop toward the saturation and then pull the voltage high on COMP pin (Vcomp). When the Vcomp ramps up to the OLP threshold of 2.8V and continues over OLP delay time, the protection will be activated and then turn off the gate output to stop the switching of power circuit.

With the protection mechanism, the average input power will be minimized to remain the component temperature and stress within the safe operating area.

Fig. 16

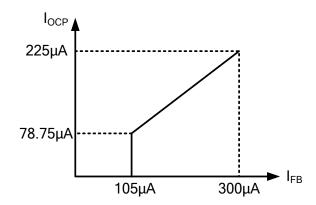

# Adjustable Over Current Compensation on FB Pin

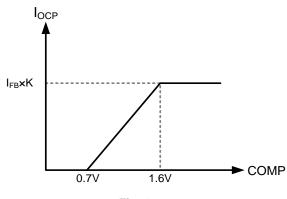

For compensating the differential input current from high/low line conditions on current sensing resistor, LD5523NGL-M mirrors compensation current  $I_{\text{OCP}}$  from  $I_{\text{FB}}$

to CS pin. The relationship of compensation current  $I_{\text{OCP}}$  and  $I_{\text{FB}}$  is expressed by following equation and shown in Fig. 17.

$$I_{OCP} = K \times I_{FB}$$

, where K = 0.75

K is the mirror current ratio of FB pin, and the  $I_{OCP}$  follows the input voltage. When the  $V_{COMP}$  ramps up to the  $I_{OCP}$  threshold 0.7V, the compensation current is added gradually. The maximum value of  $I_{OCP}$  is generated as  $V_{COMP}$  is higher than 1.6V. The corresponding  $V_{COMP}$  and  $I_{OCP}$  are shown in Fig. 18.

The compensation current  $I_{OCP}$  supplies an offset voltage by external resistor  $R_{OCP}$ , which is series between the current sensing resistor  $R_S$  and CS pin. By selecting a proper value of the resistor  $R_{OCP}$  in series with the CS pin, the amount of compensation can be adjusted.

Fig. 17

Fig. 18

04/23/2019

# Output Short Circuit Protection (OSCP) - Auto Recovery

The OSCP function can prevent the damage from output short circuit. Once the output is shorted, Vo and Vcc drop immediately, which always reflects the auxiliary winding during the gate off region. Therefore, as  $V_{FB}$  is lower than 0.8V during gate off region, then the FB\_UVP is triggered, and skips one cycle. According to the close loop control, COMP voltage will pull high in the meanwhile. If the VCOMP pulls higher than 2.8V over 13 ms and Vcc drops below 9.6V. At this time, the OSCP protection will be triggered and turn off the gate driving.

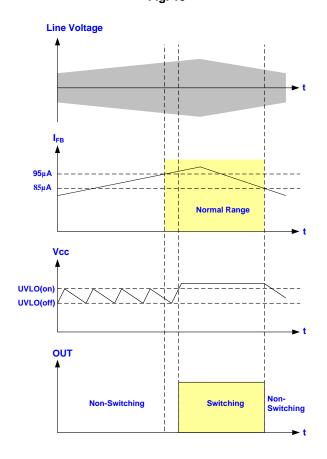

# Brown-In / Brown-Out Protection (BNI/BNO) and Bulk Cap OVP - Auto Recovery

The LD5523NGL-M integrates the brown in/out and bulk cap protections and valley detection into FB pin. The auxiliary voltage reflects a proportional bulk voltage during the on time. Fix the internal current at the BNI and BNO, the BNI level could be set by modulating the FB divided resistors and auxiliary voltage, as shown in Fig. 19. For preventing the abnormal condition of line voltage to causing damage, BNO function is implemented, while turns off the gate signal after de-bounce time 75ms as BNO occurring, as shown in Fig. 20. The relationship of input voltage and BNI/BNO is expressed in following equation.

$$\begin{split} V_{DC\_BNI} &= \frac{N_P}{N_a} \cdot I_{BNI} \cdot R_1 \\ V_{DC\_BNO} &= \frac{N_P}{N_a} \cdot I_{BNO} \cdot R_1 \\ V_{DC\_BULK\_OVP} &= \frac{N_P}{N_a} \cdot I_{BULK\_OVP} \cdot R_1 \end{split}$$

. where

V<sub>DC\_BNI</sub> is predicted BNI DC value of input voltage.

V<sub>DC\_BNO</sub> is predicted BNO DC value of input voltage.

$V_{DC\_BNULK\_OVP}$  is predicted BULK OVP DC value of input voltage.

$I_{\text{BNI}}$  is BNI trip current.

IBNO is BNO trip current.

IBULK\_OVP is BULK OVP trip current.

N<sub>p</sub> is turns ration of primary-side winding.

Na is turns ration of auxiliary winding.

Fig. 19

Fig. 20

04/23/2019

# Over Voltage Protection on FB Pin (FB OVP) - Auto Recovery

An output overvoltage protection is implemented in the LD5523NGL-M. The auxiliary winding voltage can be reflected from secondary winding, in which the FB pin voltage is proportional to output voltage during the gate off time. OVP is worked by sensing the auxiliary voltage via the divided resistors R2, referring to Fig. 19. The equation of FB OVP is shown as follows.

$$R_2 = \frac{R_1 \cdot V_{FB\_OVP}}{V_a - V_{FB\ OVP}}$$

$$V_a = \frac{N_a}{N_S} (V_0 + V_F)$$

$V_{FB\_OVP}$  is the FB pin OVP trip voltage level.  $V_a$  is the auxiliary winding voltage which reflects from the forward voltage  $V_F$  of Schottky diode and output voltage  $V_O$ .  $N_S$  is turns ration of secondary-side winding.

If  $V_{FB}$  is greater than the FB OVP trip level, the internal counter starts counting 8 cycles, and then LD5523NGL-M goes to auto-recovery protection mode till the FB OVP status is defused

# Over Temperature Protection on CS Pin (CS OTP) - Auto Recovery

LD5523NGL-M is implemented over temperature protection on CS pin which senses voltage to determine NTC status during gate off region. As  $V_{CS}$  is greater than 0.5V and continues for 5.4ms, CS\_OTP is triggered, than LD5523NGL-M is in auto recovery mode till the temperature drops to setting work condition.

### Oscillator and Switching Frequency

The LD5523NGL-M is implemented with frequency swapping function which helps the power supply designers to both optimize EMI performance and lower system cost.

# Secondary Diode Short Protection (SDSP) - Auto Recovery

The method that the LD5523NGL-M judges the logic of SDSP is described briefly as follows. When VCS is higher than 1.3V, it will reduce the frequency first, even the Ton < LEB+T<sub>PD</sub>. When the count is up to 4 times, its gate will be turned-off, shown as Fig. 21.

Fig. 21

### **Green Mode Operation**

By using the green-mode control, the switching frequency can be reduced under the light load condition. This feature helps to improve the efficiency in light load conditions. The green-mode control is Leadtrend Technology's own property.

### **Fault Protection**

There are several critical protections integrated in the LD5523NGL-M to prevent from damage to the power supply. Those damages usually come from open or short conditions on the pins of LD5523NGL-M.

In case under such conditions listed below, the gate output will turn off immediately to protect the power circuit.

- 1. CS pin floating

- 2. COMP pin floating

04/23/2019

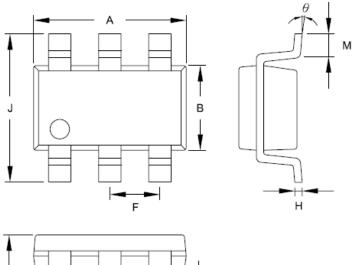

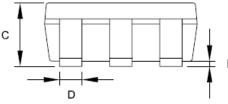

# **Package Information**

SOT-26

| Symbol | Dimension | in Millimeters | Dimensi   | ons in Inches |  |

|--------|-----------|----------------|-----------|---------------|--|

| Symbol | Min       | Max            | Min       | Max           |  |

| Α      | 2.692     | 3.099          | 0.106     | 0.122         |  |

| В      | 1.397     | 1.803          | 0.055     | 0.071         |  |

| С      |           | 1.450          |           | 0.057         |  |

| D      | 0.300     | 0.500          | 0.012     | 0.020         |  |

| F      | 0.95 TYP  |                | 0.037 TYP |               |  |

| Н      | 0.080     | 0.254          | 0.003     | 0.010         |  |

| I      | 0.050     | 0.150          | 0.002     | 0.006         |  |

| J      | 2.600     | 3.000          | 0.102     | 0.118         |  |

| М      | 0.300     | 0.600          | 0.012     | 0.024         |  |

| θ      | 0°        | 10°            | 0°        | 10°           |  |

04/23/2019

### **Revision History**

| REV. | Date       | Change Notice                     |

|------|------------|-----------------------------------|

| 00   | 01/07/2019 | Original Specification            |

| 01   | 04/23/2019 | Modify driving capability (33nF). |

### **Important Notice**

Leadtrend Technology Corp. reserves the right to make changes or corrections to its products at any time without notice. Customers should verify the datasheets are current and complete before placing order.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Leadtrend manufacturer:

Other Similar products are found below:

LV5065VB-TLM-H LV5066V-TLM-H LV5725JAZ-AH 633888R MP2908AGF AZ7500EP-E1 NCP1012AP133G NCP1217P133G

NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP1587GDR2G NCP6153MNTWG

NCP81005MNTWG NCP81101BMNTXG NCP81205MNTXG HV9123NG-G-M934 IR35207MTRPBF ISL6367HIRZ CAT874-80ULGT3

SJ6522AG SJE6600 TLE63893GV50XUMA1 IR35215MTRPBF SG3845DM NCP1216P133G NCP1236DD65R2G NCP1247BD100R2G

NCP1250BP65G NCP4202MNR2G NCP4204MNTXG NCP6132AMNR2G NCP81141MNTXG NCP81142MNTXG NCP81172MNTXG

NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UC3845ADM UBA2051C IR35201MTRPBF MAX8778ETJ+

MAX17500AAUB+T MAX17411GTM+T MAX16933ATIR/V+ NCP1010AP130G NCP1063AD100R2G NCP1216AP133G

NCP1217AP100G