11/18/2020

## High Performance Constant-Voltage Primary-Side-Regulation PWM Controller with Power Factor Correction

### **REV: P00**

The values contained in this preliminary datasheet are for reference only and not for approval. Users should verify for a current and complete document before placing orders

### **General Description**

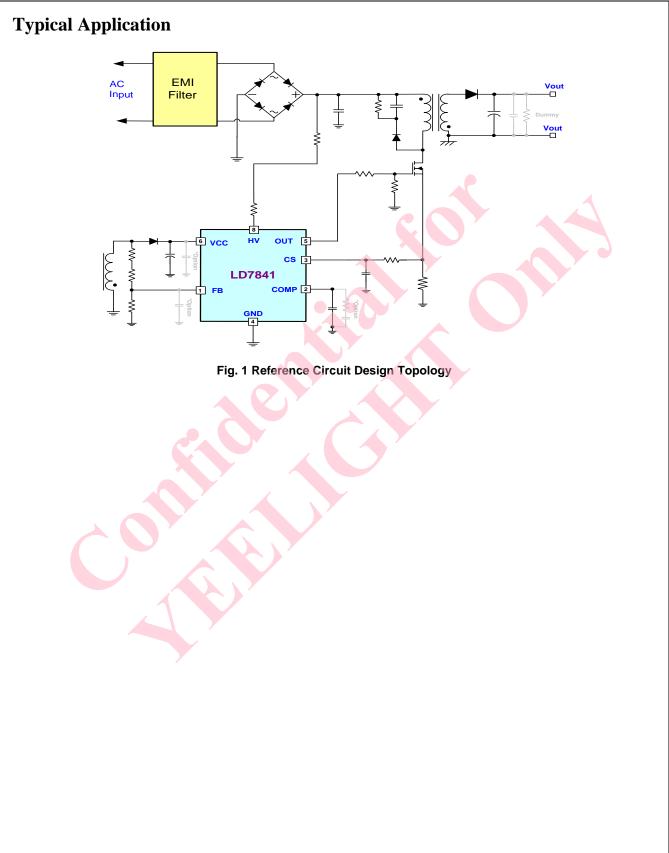

The LD7841 is a controller targeting for isolated and nonlsolated constant voltage LED drivers. Designed to support flyback, buck-boost topologies, its proprietary voltage mode control algorithm provides near-unity power factor and tightly regulates a constant output voltage from the primary side, thus eliminating the need for a secondary side feedback circuitry or an optocoupler.

The device is highly integrated with a minimum number of external components. A robust suite of safety protection is built in to simplify the design. This device is specifically intended for very compact space efficient designs and also provides a constant voltage regulation of the output if no load is connected to the LED driver.

### Feature

- Wide universal input range (85V<sub>AC</sub> ~ 305 V<sub>AC</sub>)

- High Voltage Startup: Start-up time : < 0.5 sec.

- Low standby power

- No load power saving : < 0.2W

- Standby power consumption: < 0.4W at 150mW output

- Precise CV regulation in the steady state : < ± 5 %</li>

- CV regulation in the load transient: < ± 15%

- Total Harmonic Current Optimization : THDi < 10%

- High Power Factor : PF > 0.92

- Robust Protection Features

- Brown-In/Out Detection on HV pin

- AC Over Voltage Protection on HV pin

- Programmable Output OVP on FB pin

- Cycle-by-cycle Peak Current Limit on CS pin

- Over Load Protection

- Secondary Diode short Protection

- Pin Short/Open Circuit Protection on CS and FB pin

- Winding Short Circuit Protection on FB pin

- Output Short Circuit Protection

- 250 mA / -700 mA Totem Pole Driving capability

### Applications

- LED Driver Power Supplies

- Off Line Appliances Requiring Power Factor Correction

11/18/2020

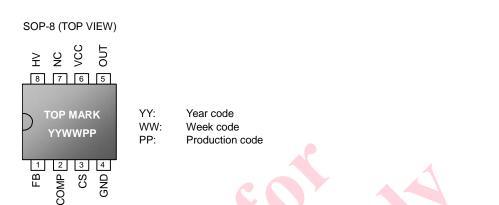

### **Pin Configuration**

### **Ordering Information**

| Part number | Package |               | Top Mark | Shipping          |

|-------------|---------|---------------|----------|-------------------|

| LD7841GS    | SOP-8   | Green package | LD7841GS | 2500 /tape & reel |

The LD7841 GS is ROHS compliant/ green packaged.

### **Protection Mode**

| ltem   | ACOVP         | BNO           | VCCOVP        | FBOVP         | SDSP           | CSSP           | CSOP          | FBUVP<br>(OSCP) | OLP            | Int. OTP      |

|--------|---------------|---------------|---------------|---------------|----------------|----------------|---------------|-----------------|----------------|---------------|

| 107044 | Auto          | Auto          | Auto          | Auto          | Auto           | Auto           | Auto          | Auto            | Auto           | Auto          |

| LD7841 | (VCC 1hiccup) | (VCC 1hiccup) | (VCC 1hiccup) | (VCC 1hiccup) | (VCC 8hiccups) | (VCC 8hiccups) | (VCC 1hiccup) | (VCC 4hiccups)  | (VCC 4hiccups) | (VCC 1hiccup) |

### **Pin Descriptions**

| Pin No | NAME | FUNCTION                                                                                                                          |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1      | FB   | This pin senses the auxiliary winding voltage for accurate output voltage control and detects the core reset event.               |

| 2      | COMP | This pin receives a compensation network to stabilize the CV loop.                                                                |

| 3      | CS   | This pin monitors the primary peak current. It is connected to sense resistor of MOSFET for cycle by cycle limitation.            |

| 4      | GND  | The controller ground.                                                                                                            |

| 5      | OUT  | Gate drive output to drive the external MOSFET.                                                                                   |

| 6      | VCC  | IC operating current and MOSFET driving current are supplied by this pin. This pin is connected to an external auxiliary voltage. |

| 7      | NC   | Not connection with chip.                                                                                                         |

| 8      | ΗV   | This pin connects to the bridge diode for providing the startup current and internal high voltage sensing function.               |

11/18/2020

### **Absolute Maximum Ratings**

| 6                                                        |                  |

|----------------------------------------------------------|------------------|

| High voltage pin, HV                                     | -0.3 ~ 700V      |

| Supply Voltage VCC                                       | -0.3 ~ 30V       |

| OUT                                                      | -0.3 ~ VCC+0.3V  |

| COMP, CS, FB                                             | -0.3 ~ 6V        |

| Source /Sink current on FB                               | 3mA / -1.5mA     |

| Storage Temperature Range                                | -65°C to 150°C   |

| Package Thermal Resistance (SOP-8, $\theta_{JA}$ )       | 160°C/W          |

| Power Dissipation (SOP-8 at Ambient Temperature = 85 °C) | 250mW            |

| Lead temperature (Soldering, 10sec)                      | 260°C            |

| ESD Voltage Protection, Human Body Model (HV pin)        | 1.5 KV           |

| ESD Voltage Protection, Human Body Model (except HV pin) | 2.5KV            |

| ESD Voltage Protection, Machine Model                    | 250 V            |

| Gate Output Current                                      | 250 mA / -700 mA |

| Caution:                                                 |                  |

Stresses beyond the ratings specified in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### **Recommended Operating Conditions**

| Item                                 | Min. | Max. | Unit |

|--------------------------------------|------|------|------|

| Operating Junction Temperature Note3 | -40  | 125  | °C   |

| Supply Voltage of VCC                | 10   | 24   | V    |

| HV Pin Resistance                    | 5    | 45   | kΩ   |

| HV Pin Bypass Capacitance            | -    | 220  | pF   |

| VCC pin Capacitance Note3            | 22   | 47   | μF   |

| COMP pin Capacitance                 | 47   | 2200 | nF   |

| CS pin Filter Capacitance            | -    | 220  | pF   |

| CS pin Filter Resistance             | 0.1  | 1    | kΩ   |

| FB pin Source Current                | -    | 2    | mA   |

| FB pin Sink Current                  | -    | 0.5  | mA   |

Note :

1) Exceeding these ratings may damage the device.

2) This product guarantees robust performance from -20°C to 105°C ambit temperature. The junction temperature range specification is assured by design, characterization and correlation with statistical process controls.

3) When operation at harsh environment condition, as temperature and humidity or climate change ...etc . Please pay attention to impedance variation between pin to pin or ground to avoid ripple remover closing loop and being failure.

### **Electrical Characteristics**

V<sub>CC</sub>=15V,  $T_A = 25^{\circ}C$  unless otherwise specified.)

| PARAMETER                                                         | CONDITIONS                                                                                                                    | SYMBOL               | MIN | TYP  | MAX | UNITS           |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|------|-----|-----------------|

| High voltage Supply (HV Pir                                       | n)                                                                                                                            |                      |     |      |     |                 |

|                                                                   | $V_{\text{HV}} = 100 V_{\text{DC},} V_{\text{VCC}} \leqq V_{\text{PDR}}$                                                      | I <sub>HV1</sub>     |     | 1.5  |     | mA              |

| High voltage current source                                       | $V_{HV}$ = 100 $V_{DC}$ , $V_{PDR}$ < $V_{VCC} \leq V_{UV_{ON}}$ -0.5 $V$                                                     | IHV2                 |     | 5    |     | mA              |

| Off state leakage current                                         | *; $V_{VCC}$ > $V_{UV_ON}$ , $V_{HV}$ =500 $V_{DC}$                                                                           | IHV_OFF              |     |      | 30  | μA              |

| Brown-in threshold voltage                                        | $V_{VCC} > V_{UV_ON}, V_{FB} = 0V$                                                                                            | V <sub>HVBI</sub>    |     | 100  |     | V <sub>DC</sub> |

| Brown-in de-bounce time                                           |                                                                                                                               | TBNI                 |     | 15   |     | ms              |

| Hysteresis of brown-in/out                                        | V <sub>HVBI</sub> - V <sub>HVBO</sub>                                                                                         | $\Delta  V_{HV}$     |     | 15   |     | VDC             |

| Brown-out de-bounce time                                          |                                                                                                                               | Твио                 |     | 15   |     | ms              |

| High line threshold voltage                                       | V <sub>HV_PEAK</sub> is rising.                                                                                               | VHLINE               | 215 | 230  | 245 | VDC             |

| Low line threshold voltage                                        | V <sub>HV_PEAK</sub> is falling                                                                                               | VLLINE               | 190 | 205  | 220 | VDC             |

| The de-bounce Time of change V <sub>OCP</sub> by low to high line | *; $V_{OCP_L}$ change to $V_{OCP_H}$                                                                                          | TDEB_HVLH            |     | 15   |     | ms              |

| The de-bounce Time of change V <sub>OCP</sub> by high to low line | *; $V_{\text{OCP}_{-H}}$ change to $V_{\text{OCP}_{-L}}$                                                                      | TDEB_HVHL            |     | 15   |     | ms              |

| ACOVP threshold voltage                                           |                                                                                                                               | VACOVP               |     | 485  |     | V <sub>DC</sub> |

| Hysteresis of ACOVP                                               | *                                                                                                                             | V <sub>ACOVP_H</sub> | -   | 20   | -   | V <sub>DC</sub> |

| The de-bounce time of ACOVP detect function                       |                                                                                                                               | Td_acovp             |     | 150  |     | μs              |

| Supply Voltage (VCC Pin)                                          |                                                                                                                               | 1                    |     |      |     |                 |

| Startup Current                                                   | V <sub>VCC</sub> < V <sub>UV_ON</sub>                                                                                         | Ist                  |     | 75   | 100 | μA              |

| Operating Current                                                 | $\begin{array}{l} 3.45V  \leq  V_{FB}  \leq  3.6V  @  F_{MIN}  , \\ \\ C_{OUT}  \leq  1nF,  C_{COMP} {=} 1 \mu F \end{array}$ | IOP_L                |     | 2.0  |     | mA              |

|                                                                   | VCCOVP, OLP, CSSP, SDSP,<br>CSOTP etc.                                                                                        | I <sub>OP_PRO</sub>  |     | 0.35 |     | mA              |

| UVLO (OFF)                                                        |                                                                                                                               | Vuv_off              |     | 8.5  |     | V               |

| UVLO (ON)                                                         |                                                                                                                               | V <sub>UV_ON</sub>   |     | 17.5 |     | V               |

| VCCOVP threshold voltage                                          |                                                                                                                               | Vcc_ovp              |     | 28   |     | V               |

| VCCOVP de-bounce Time                                             | *                                                                                                                             | T <sub>DEB_OVP</sub> |     | 150  |     | μS              |

11/18/2020

| PARAMETER                                         | CONDITIONS                                                                                                                        | SYMBOL                                            | MIN | ТҮР         | MAX  | UNITS |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|-------------|------|-------|

| Voltage Feedback (COMP P                          | in)                                                                                                                               |                                                   |     | l.          | •    |       |

| Short circuit current                             | *; V <sub>COMP</sub> =0V.                                                                                                         | ICOMP                                             |     | 1           |      | mA    |

| Open loop voltage                                 |                                                                                                                                   | V <sub>CMP_OPEN</sub>                             |     | 4.7         |      | V     |

| Over load protection threshold voltage            |                                                                                                                                   | Volp                                              | Vo  | CMP_OPEN -( | ).2  | v     |

| Over load protection<br>de-bounce Time            | *; $V_{COMP} \ge V_{LOP}$ .                                                                                                       | T <sub>DEB_OLP</sub>                              | -   | 210         | -    | ms    |

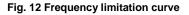

| Frequency limit reducing start threshold voltage  | Fs=Fs_max                                                                                                                         | Vcmp_flh                                          |     | 3.0         |      | v     |

| Frequency limit reducing<br>end threshold voltage | *; Fs=Fs_min                                                                                                                      | Vcmp_fll                                          |     | 0.3         |      | V     |

| Minimum on time threshold voltage                 | T <sub>ON</sub> =T <sub>ON_MIN</sub>                                                                                              | V <sub>CMP_TON_MIN</sub>                          |     | 1.0         |      | V     |

| COMP clamping low threshold voltage               | *                                                                                                                                 | Vcmp_low                                          |     | 0.35        |      | V     |

|                                                   | $22k\Omega  \geqq  R_{FB} \geqq  18k\Omega,  V_{HV} \text{=} 100 V_{DC}$                                                          | T <sub>MAX_1</sub>                                |     | 27          |      | μS    |

| MAX. turn on time setting                         | $12.5k\Omega \ge R_{FB} \ge 7.5k\Omega, V_{HV}=100V_{DC}$                                                                         | TMAX_2                                            | r   | 17          |      | μS    |

| MIN. turn on time                                 | V <sub>HV</sub> =100V <sub>DC</sub> , V <sub>COMP</sub> =V <sub>CMP_TON_MIN</sub> ,<br>Maximum on time setting=T <sub>MAX_1</sub> | TMIN_L                                            |     | 2.1         |      | μs    |

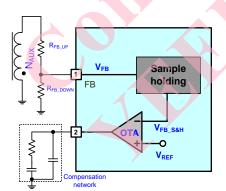

| Minimum frequency                                 | $V_{COMP} \leq V_{CMP_FLL}$                                                                                                       | F <sub>MIN</sub>                                  |     | 500         |      | Hz    |

| Green frequency                                   | *; V <sub>COMP</sub> = 1.3V                                                                                                       | FGREEN                                            |     | 14          |      | kHz   |

| Maximum frequency                                 | V <sub>COMP</sub> ≧V <sub>CMP_FLH</sub>                                                                                           | F <sub>MAX</sub>                                  |     | 90          |      | kHz   |

| Zero Current Detector and F                       | Feedback (FB Pin)                                                                                                                 |                                                   |     |             |      |       |

| Upper clamp voltage                               | $I_{FB} = 0.2 \text{mA}$                                                                                                          | $V_{ZH}$                                          | 4.6 | 4.8         | 5.0  | V     |

| Lower clamp voltage                               | I <sub>FB</sub> = -2mA                                                                                                            | Vzl                                               | 0   |             | -0.6 | V     |

| Blanking time of FB pin                           |                                                                                                                                   | T <sub>BLA</sub>                                  |     | 850         |      | ns    |

| Input voltage rising threshold voltage            |                                                                                                                                   | Vfbr                                              |     | 0.5         |      | V     |

| QRD threshold voltage                             |                                                                                                                                   | Vqrd                                              |     | 0.3         |      | V     |

| FBOVP threshold voltage for SET0                  | $R_{CS} \leq 500 \Omega$                                                                                                          | $V_{FB\_OVP\_0}$                                  |     | 4.0         |      | V     |

| FBOVP threshold voltage for SET1                  | $R_{CS} \ge 800 \Omega$                                                                                                           | Vfb_ovp_1                                         |     | 4.2         |      | V     |

| Hysteresis of FBOVP                               | *                                                                                                                                 | ${\scriptstyle \Delta}V_{\text{FB}_{\text{OVP}}}$ |     | -0.1        |      | V     |

| FBOVP De-bounce                                   | *                                                                                                                                 | T <sub>DEB_FBOV</sub>                             | -   | 4           | -    | Cycle |

11/18/2020

| PARAMETER                                            | CONDITIONS                                                                                   | SYMBOL               | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------|-------|-------|-------|-------|

| Zero Current Detector and F                          | eedback (FB Pin)                                                                             |                      |       |       |       |       |

| FBUVP Threshold                                      |                                                                                              | Vfb_uvp              | 0.7   | 0.8   | 0.9   | V     |

| Output Short Protection<br>De-bounce time            | *; Not including T <sub>SS1.</sub>                                                           | TDEB_OSCP            |       | 56    |       | ms    |

| Reference voltage during start up time               | *                                                                                            | Vref_ss              |       | 3.2   |       | V     |

| Soft start of Reference voltage                      | *                                                                                            | T <sub>VREF_SS</sub> |       | 300   |       | ms    |

|                                                      | Steady state ; Tj=25 °C                                                                      |                      | 3.465 | 3.500 | 3.535 | V     |

| Internal reference voltage                           | Steady state ; Tj=40~125 °C                                                                  | Vref                 |       | +/-2  |       | %     |

| Current Sensing (CS Pin)                             |                                                                                              |                      |       |       |       |       |

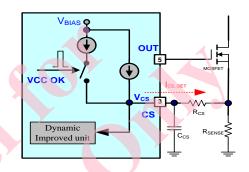

| V <sub>CS</sub> Soft Start Time                      | *; After T <sub>CCMP</sub> end                                                               | T <sub>SS1</sub>     |       | 39    |       | ms    |

| V <sub>CS</sub> soft start 1                         | *; After $T_{CCMP}$ end. During $T_{SS11}$<br>Fsw=22kHz and $V_{CS}$ limit = 0.2V            | Tss11                |       | 5     |       | ms    |

| V <sub>CS</sub> soft start 2                         | *; After T <sub>SS11</sub> end, V <sub>CS</sub> limit rising from 0.2 to 0.7V and 100mV/step | Tss12                |       | 34    |       | ms    |

| Leading edge blanking time                           | *; When 90KHz,max                                                                            | TLEB_CS              |       | 300   |       | ns    |

| Programming delay to OUT<br>pin                      |                                                                                              | Трр                  |       | 100   |       | nS    |

| Over Current Limit                                   | When $V_{HV} \ge V_{HLINE} \& T_{DEB} HVLH$                                                  | Vocp_h               |       | 0.80  |       | V     |

|                                                      | When $V_{HV} \leq V_{LLINE} \& T_{DEB}_{HVHL}$                                               | Vocp_l               |       | 1.00  |       | V     |

| Current Limit-2 for secondary diode short protection |                                                                                              | V <sub>OCP2</sub>    |       | 0.7   |       | V     |

| Counter times of Diode Short<br>Protection           | *; SDSP is triggered and continuously.                                                       | T <sub>DEB_DSP</sub> |       | 7     |       | cycle |

| CSSP Threshold Voltage                               |                                                                                              | VCSSP                |       | 100   |       | mV    |

| CSSP de-bounce time                                  | *; And $V_{COMP} \ge 2V$ continuous                                                          | TCSSP                |       | 56    |       | ms    |

| Gate Drive Output (OUT Pin)                          |                                                                                              |                      |       |       |       |       |

| Output Low Level                                     |                                                                                              | $V_{G_{LO}}$         |       |       | 0.5   | V     |

| Output High Level                                    |                                                                                              | Vg_hi                |       | 13    |       | V     |

| Rising Time                                          | *; C <sub>L</sub> =1000pF                                                                    | $T_{G_{RISE}}$       |       | 250   |       | ns    |

| Falling Time                                         | *; C∟=1000pF                                                                                 | $T_{G_{FALL}}$       |       | 35    |       | ns    |

| Internal OTP (Over Temp. Pr                          | otection)                                                                                    |                      |       |       |       |       |

| OTP Trip level                                       | *; No switching                                                                              | OTP                  |       | 140   |       | °C    |

| OTP Hysteresis                                       | *                                                                                            | ΔΟΤΡ                 |       | 20    |       | °C    |

\*: Guaranteed by design.

### Application Information Operation Overview

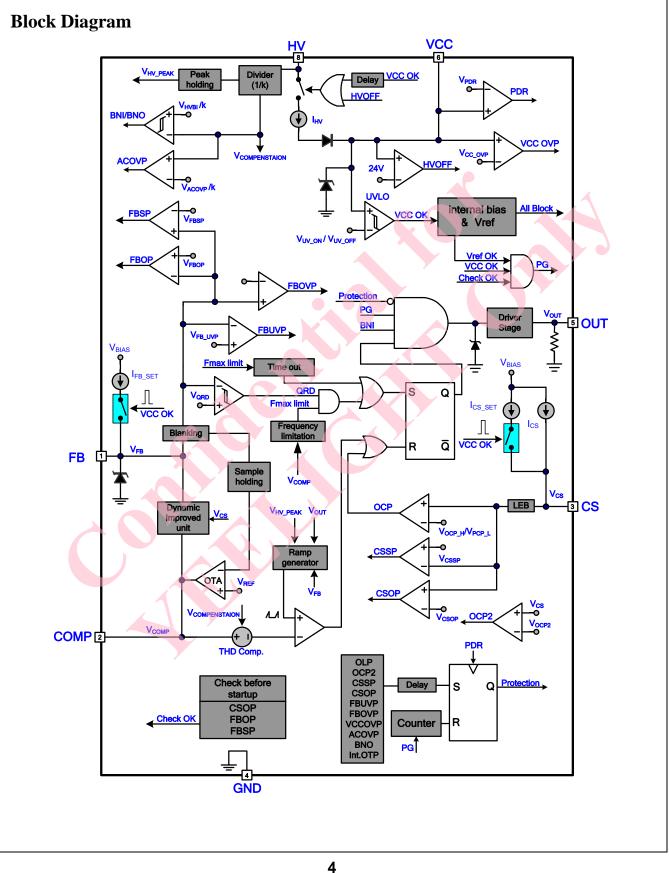

LD7841 is an excellent single-stage flyback PFC controller with constant voltage output and primary side regulation (PSR) control algorithm for LED lighting applications. It drives converter operating in quasiresonant or DCM mode to achieve high efficiency and low THD performance. By PSR, LD7841 is feedback accurately with primary side auxiliary winding without the shunt regulator and optocoupler at secondary side. By voltage-mode control, the turn-on time of the switch is fixed while the turn-off time is varied in steady state. Therefore, the switching frequency varies in accordance with the input voltage or output loading variation. The maximum switching frequency is limited about 90kHz and minimum switching frequency is limited about 500Hz. LD7841 provides robust protections as over load protection, over voltage protection, over current protection, under voltage lockout and LEB of the current sensing. Its major features are described as below.

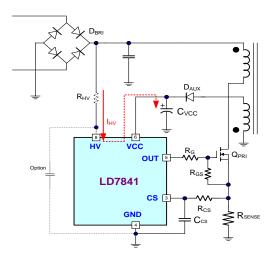

### Internal High-Voltage Startup Circuit and Under Voltage Lockout (UVLO)

The traditional circuit provides the startup current through a startup resistor to power up the PWM controller. However, it consumes significant power to meet the power saving requirement. In most cases, startup resistors carry large resistance. It will take longer time to start up.

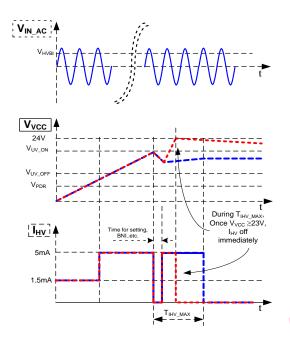

To achieve optimized topology, as shown in Fig. 2, LD7841 is implemented with a high-voltage startup circuit to enhance it. During startup, a high-voltage current source sinks current ( $I_{HV}$ ) from the full-bridge rectifier to provide the startup current and charge Vcc capacitor ( $C_{VCC}$ ) at the same time. If the voltage of VCC pin ( $V_{VCC}$ ) is lower than  $V_{PDR}$  ( $V_{UV_OFF}$ -1.5V, typ.),  $I_{HV}$  is limited about 1.5mA (typ.). Once  $V_{VCC}$  is higher than  $V_{PDR}$ ,  $I_{HV}$  increases to 5mA (typ.) around to speed up

startup sequence. Meanwhile, the VCC supply current (I<sub>ST</sub>) consumes only 75 $\mu$ A (typ.), that most of the I<sub>HV</sub> is reserved to charge C<sub>VCC</sub>. In using such configuration, the turn on delay time will be almost no difference either in low line or high line conditions.

Once the V<sub>VCC</sub> is higher than V<sub>UV\_ON</sub> (17.5V, typ.) and all of condition are checked (BNI, setting and CSSP...etc.), LD7841 powers on and further to deliver the gate drive signal, I<sub>HV</sub> will not disabled right away and keeping provide current about 65ms (= $T_{IHV_MAX}$ ) around for smaller C<sub>VCC</sub> application. During T<sub>IHV\_MAX</sub> period, if V<sub>VCC</sub> is higher than 23V (typ.), I<sub>HV</sub> is disabled immediately.

The supply current is provided from the auxiliary winding of the transformer. Therefore, it would eliminate the power loss on the startup circuit and perform highly power saving.

An UVLO comparator is embedded to detect V<sub>cc</sub> to ensure the supply voltage enough to power on and in addition to drive the power MOSFET. As shown in Fig. 3, a hysteresis is provided to prevent the shutdown from the voltage dip during startup.

Fig. 2 Startup circuit

Fig. 3 I<sub>HV</sub> Typically waveform

#### **Brown-In/Out**

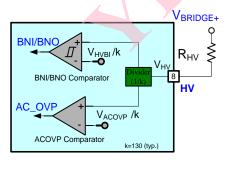

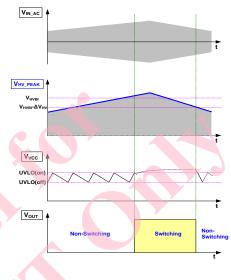

LD7841 provides brown-in/out function on HV pin. Fig. 4 and Fig. 5 show the operation. When V<sub>HV</sub> is always lower than V<sub>HVBI</sub> (100V, typ.) during each period of T<sub>BNI</sub> (15ms, typ.), the gate output will remain off even when the V<sub>VCC</sub> already reaches V<sub>UV\_ON</sub>. It therefore forces the V<sub>VCC</sub> hiccup between V<sub>UV\_ON</sub> and V<sub>UV\_OFF</sub> until V<sub>HV</sub> is higher than V<sub>HVBI</sub>. A hysteresis ( $\triangle$  V<sub>HV</sub>, 15V, typ.) is implemented to prevent the false-triggering during turn-on and turn off.

Fig. 4 BNI/BNO and AC\_OVP block

11/18/2020

After brown in condition is triggered, once  $V_{HV}$  is always lower than  $V_{HVBI}$ - $\triangle V_{HV}$  and longer than de-bounce time (T<sub>BNO</sub>, 15ms, typ.), LD7841 will shut off to prevent from any damage.

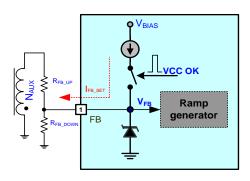

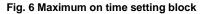

#### Maximum On-Time Setting

LD7841 provides the maximum on time ( $T_{ON\_MAX}$ ) programmable function on FB pin.  $T_{ON\_MAX}$  should be set according to the condition of the transformer, lowest AC line voltage, and maximum output power. A choice of optimum  $T_{ON\_MAX}$  would result in best performance. As Fig.6, after V<sub>VCC</sub> is higher than V<sub>UV\_ON</sub>, and BNI is triggered, the internal current source provides a constant current (I<sub>FB\_SET</sub>, 90  $\mu$  A, typ.) about 450  $\mu$  s (typ.) passed thought R<sub>FB\_T</sub> to check this voltage then set T<sub>MAX\_N</sub>.

Where:

$R_{FB_T} = \frac{(R_{FB_{UP}} \times R_{FB_{DOWN}})}{(R_{FB_{UP}} + R_{FB_{DOWN}})} \quad (eq.1)$

The following table is the resistance suggestion for maximum on-time setting.

| Тилу               | T <sub>MAX_N</sub> Condition |                                            | Max. on Time        | $R_{FB_T}$   |

|--------------------|------------------------------|--------------------------------------------|---------------------|--------------|

| I MAX_P            |                              |                                            | $@V_{HV}=100V_{DC}$ | suggestion   |

| T <sub>MAX_1</sub> | I                            | $25k\Omega \ge R_{FB_T} \ge 18k\Omega$     | 27µs                | <b>22k</b> Ω |

| T <sub>MAX_2</sub> | 2                            | 12.5k $\Omega \ge R_{FB_T} \ge 7.5k\Omega$ | 17µs                | 10k $\Omega$ |

#### Table. 1 Maximum on Time Setting

LD7841 implements the compensation of on time by monitor HV pin, as shown in below,

$T_{ON\_MAX} = T_{MAX\_N} \times K_{TON} \quad (eq.2)$

$$K_{TON} = \frac{100V}{V_{HV\_PEAK}} \quad (eq.3)$$

Where:  $V_{HV\_PEAK}$  is from 100V<sub>DC</sub> to 420V<sub>DC</sub>. For abnormal condition, if FB pin is shorted to GND or floating (badly soldered), LD7841 will interrupt startup sequence and operate into hiccup mode until the fault condition is removed.

### FB Short / Open Circuit Protection Before Startup

For abnormal condition, if the FB pin is floating (Open condition),  $I_{FB\_SET}$  will pull high the  $V_{FB}$ , once  $V_{FB}$  is higher than 2.7V (typ.). LD7841 will interrupt startup sequence and operate into hiccup mode until the fault condition is removed.

If the FB pin is shorted to GND,  $V_{FB}$  will be pull low, once  $V_{FB}$  is lower than 0.35V (typ.). LD7841 will interrupt startup sequence and operate into hiccup mode until the fault condition is removed.

#### 11/18/2020

#### **Dynamic Improved Threshold Level Setting**

LD7841 provides the dynamic improved threshold level programmable function. As Fig.7, after V<sub>CC</sub> is higher than V<sub>UV\_ON</sub>, and BNI is triggered, the internal current source provides a constant current (I<sub>CS\_SET</sub>, 270  $\mu$  A, typ.) about 600  $\mu$  s (typ.) passed thought R<sub>CS</sub> to set threshold level.

Table.2 is the resistance suggestion for dynamic improved threshold level setting.

| ITEM | R <sub>cs</sub> (Ω) | USD                    | OSD1  | OSD2  | OSD3  | VFB_OVP |

|------|---------------------|------------------------|-------|-------|-------|---------|

|      | $RCS(\Omega)$       | Percentage to VREF (%) |       |       |       | (V)     |

| SET0 | ≦500                | -4.3                   | +4.3  | +7.85 | +12.5 | 4.0V    |

| SET1 | ≧800                | -7.85                  | +7.85 | +12.5 | +17.5 | 4.2V    |

#### Table. 2 Dynamic and Over Voltage Setting

For abnormal condition, if the CS pin is floating,  $I_{CS\_SET}$  will pull high the V<sub>CS</sub>, once V<sub>CS</sub> is higher than 2V (min.) LD7841 will interrupt startup sequence and operate into hiccup mode until the fault condition is removed.

Current Sense Short Circuit Protection before Startup

After settings are done, LD7841 delivers one pulse gate drive signal to turn on the MOSFET and check the condition of CS pin. This pulse width is given by the following equation.

$T_{ON\_CSSP} \approx 0.3 \times (K_{TON}) \times T_{MAX\_N}$  (eq.4)

If Vcs is higher than VcssP (100mV, typ.) during ToN\_cssP, it means the function of current sense is normal, LD7841 will operate into soft start after  $T_{CCMP}$  (3ms, typ.). If Vcs is higher than 200mV, gate off immediately to avoid the saturation of transformer. Once Vcs is lower than VcssP, the protection of current sense short circuit before startup triggered, LD7841 will interrupt startup sequence and operate into hiccup mode until the fault condition is removed.

#### Soft Start

LD7841 provides soft start function by steps current sense limitation and steps reference voltage (V<sub>REF</sub>) of feedback loop. At startup, the output voltage is very low, system operates into CCM and causes higher stress. So, V<sub>cs</sub> is limited at 0.2V and the switching frequency (F<sub>SW</sub>) is fixed at 22kHz (typ.) in first 3ms during soft start (T<sub>SS1</sub>). After T<sub>SS1</sub>, V<sub>cs</sub> is rising from 0.2V to 0.7V step by step about 34ms (T<sub>SS2</sub>, typ.) and F<sub>SW</sub> is controlled by the voltage of COMP pin (V<sub>COMP</sub>). Fig. 8 is shown typical waveforms.

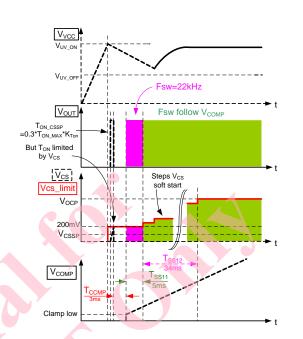

Besides the current sense limitation for soft start, LD7841 also provide the reference voltage steps to avoid the overshoot during startup. As shown in Fig.9, the  $V_{REF}$  is set as  $V_{REF\_SS}$  (3.2V, typ.) initial until feedback regulation. Once  $V_{COMP}$  is pulled low to appropriate level during soft start, the  $V_{REF}$  is rising from 3.2V to 3.5V step by step about 300ms ( $T_{VREF\_SS}$ , typ.).

Fig. 8 current sense limitation steps function

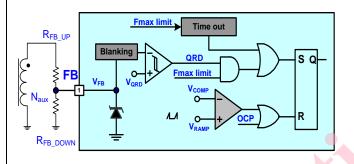

#### **Primary Side Regulation**

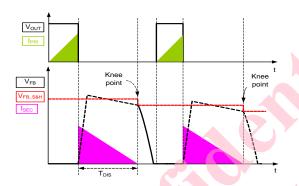

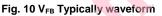

LD7841 detects the auxiliary winding to achieve constant voltage regulation. The typically waveform is shown in Fig.10. When the current of secondary side discharging to zero, the primary side V<sub>FB</sub> is at knee point, then LD7841 samples the voltage at knee point and holds it until next switching cycle. This signal ( $V_{FB_S&H}$ ) is compared to  $V_{REF}$  by the internal error amplifier. As shown in Fig.11. In order to keep the system is stable, place the compensation network at COMP pin to GND as closed as possible.

Fig. 11 Feedback function block

### Principle of Constant Voltage Operation

The output voltage is given by the following equation.

$$V_{OUT} = (V_{REF \times} \frac{N_{SEC}}{N_{AUX}} \times \frac{R_{FB\_UP} + R_{FB\_DOWN}}{R_{FB\_DOWN}}) - V_F \quad (eq.5)$$

Where:

N<sub>SEC</sub> is the turns of secondary main output winding.

$N_{AUX}$  is the turns of auxiliary winding voltage to supply for VCC.

$V_{REF}$  is the reference voltage of constant voltage feedback.

V<sub>F</sub> is forward voltage of secondary rectifier diode.

### **Frequency Limitation**

LD7841 implements the frequency limitation function to improve efficiency at light load. As shown in Fig.12, the maximum switching frequency is controlled by  $V_{COMP}$ .

# Ramp Generator Block and Zero Current Detection (ZCD)

Fig. 13 shows typical function block. V<sub>COMP</sub> and the output of the ramp generator block are compared to determine the MOSFET on-time.

A greater  $V_{COMP}$  produces more on-time. Using an external resistor connected to FB pin to set the desired slope of the internal ramp, the user may program the  $T_{ON\_MAX}$ . Alternatively, the on-time will also achieve its maximum when  $V_{COMP}$  trip to  $V_{CMP\_OPEN}$  (4.7V, typ.).

As shown in Fig.14, The block of zero current detection will detect auxiliary winding signal to drive MOSFET. If  $V_{FB}$  rises over  $V_{FBR}$  (0.5V, typ.) after  $T_{BLA}$ +400ns then drops under  $V_{QRD}$  (0.3V, typ.), the QRD signal is triggered and turn on MOSFET. As  $V_{FB}$  first drops to  $V_{QRD}$ , the current through the transformer is below zero. This feature enables transition-mode operation.

Fig. 13 QRD function block

Fig. 14 QRD detection on FB pin

#### 11/18/2020

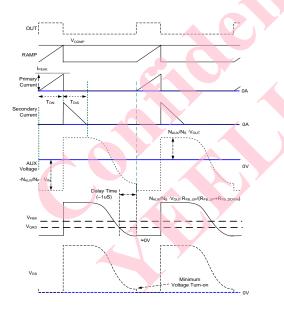

#### **Quasi-Resonant / DCM Operation**

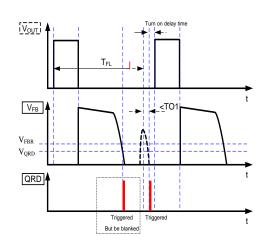

According to the difference of V<sub>FB</sub>, LD7841 could operate at quasi-resonant mode or DCM mode. As shown in Fig. 15. If QRD signal is triggered after the end of TO1 but before TO2, LD7841 operates at quasi-resonant mode.

As shown in Fig. 16. If QRD signal is triggered before the end of T<sub>FL</sub>, the QRD signal is triggered but blanked to turn on MOSFET. After T<sub>FL</sub>, QRD signal is triggered again and turn on the MOSFET during TO1 (~5  $\mu$  s.), LD7841 operates at DCM mode with valley switching. Where:

$$\Gamma_{\rm FL} = \frac{1}{\Gamma_{\rm SW \ LIMIT}}$$

(eq.6)

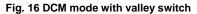

Same as previous condition but If QRD signal is not triggered again, the MOSFET will be turn on at the end of TO1 directly. LD7841 operates at DCM mode. As shown in Fig. 17.

### Output Drive Stage

With typical 250mA/-700mA peak driving capability, an output stage of a CMOS buffer is incorporated to drive a power MOSFET directly. The output voltage is clamped at 13V to protect the MOSFET gate even when the Vcc voltage is higher than 13V.

# Leading-Edge Blanking and Cycle by Cycle limitation

A 300ns (typ.) leading-edge blanking time ( $T_{LEB}$ ) is included in the input of CS pin to prevent the false-trigger from the current spike. In the different rated power application, if the total pulse width of the turn-on spikes is lower than and the negative spike on the CS pin doesn't exceed -0.3V, it could eliminated the R-C filter.

However, the total pulse width of the turn-on spike is determined by the output power, circuit design and PCB layout. It is strongly recommended to adopt a smaller R-C filter for higher power application to avoid the CS pin being damaged by the negative turn-on spike. 11/18/2020

LD7841 detects the primary side peak current from the CS pin, which is used for cycle by cycle peak current limit. The maximum voltage threshold of the CS pin set as  $V_{OCP\_L}$  (1.0V, typ.) or  $V_{OCP\_H}$  (0.8V, typ.) which are controlled by  $V_{HV}$ , once  $V_{CS}$  is higher than  $V_{OCP\_X}$ , gate off immediately.

#### **Protection Function**

#### VCC Over Voltage Protection - 1 Hiccup

The maximum rating of the VCC pin is limited below 30V. To prevent VCC from the fault condition, LD7841 is implemented with OVP function on VCC pin. When Vvcc higher than  $V_{CC\_CLAMP}$  (25V, typ.), LD7841 will sink a current about 2mA (typ.) first from VCC pin. But if supplier voltage keeps rising and higher than  $V_{CC\_OVP}$  (28V, typ.) and de-bounce about 250µs, LD7841 will enforce the gate off until the 1<sup>st</sup> cycle of VCC hiccup is tripped and the fault condition is removed.

#### FB Over Voltage Protection - 1 Hiccup

If  $R_{FB_UP}$  is shorted or  $R_{FB_DOWN}$  is opened during operating, the feedback signal is incorrect. LD7841 is implemented with OVP function on FB pin. Once V<sub>FB</sub> is higher than V<sub>FB\_OVP\_0</sub> (4.0V, typ.) or V<sub>FB\_OVP\_1</sub> (4.2V, typ.) and de-bounce about 4 switching cycles continuously, LD7841 will enforce the gate off until the 1<sup>st</sup> cycle of VCC hiccup is tripped and the fault condition is removed.

### FB Under Voltage Protection (OSCP) - 4 Hiccups

When the output short circuit occurs, the reflected output voltage of auxiliary winding will cause  $V_{FB}$  down. If  $V_{FB}$  is lower than  $V_{FB_UVP}$  (0.8V, typ.) and de-bounce about 56ms, LD7841 will enforce the gate off until the 4<sup>th</sup> cycle of VCC hiccup is tripped and the fault condition is removed. For abnormal condition, if  $R_{FB_UVP}$  is opened or  $R_{FB_DOWN}$  is shorted, FB under voltage protection is triggered too.

#### **CS Short Circuit Protection - 8 Hiccups**

To avoid the damaged which is caused by CS pin short circuit during operating, LD7841 implemented a smart and robust CS short circuit protection function. If such fault condition occurs and V<sub>CS</sub> is lower than V<sub>CSS</sub> (100mV, typ.) then V<sub>COMP</sub> is higher than 2V (typ.), after de-bounce about 56ms (T<sub>CSSP</sub>), LD7841 will enforce the gate off until the 8<sup>th</sup> cycle of VCC hiccup is tripped and the fault condition is removed. As shown in Fig. 18.

Fig. 18 Current Sense Short Circuit Protection

#### **CS** Open protection - 1 Hiccup

If R<sub>cs</sub> is opened during operating, The internal current source (I<sub>cs</sub>, 10  $\mu$  A, typ.) from CS pin to output, once V<sub>cs</sub> is higher than V<sub>ocP\_x</sub>, LD7841 will enforce the gate off until the 1<sup>ST</sup> cycle of VCC hiccup is tripped and the fault condition is removed.

#### AC Over Voltage protection - 1 Hiccup

To avoid the input voltage is too high to cause circuit damaged, LD7841 implemented the AC over voltage protection function on HV pin to monitor it. If such fault condition occurs and  $V_{HV}$  is higher than  $V_{ACOVP}$  (485V,

typ.), after de-bounce about  $150 \,\mu \,s$  (T<sub>D\_ACOVP</sub>), LD7841 will enforce the gate off until the 1<sup>st</sup> cycle of VCC hiccup is tripped and the fault condition is removed.

#### **Over Loading protection - 4 Hiccups**

LD7841 implemented the over loading protection, once  $V_{COMP}$  is higher than  $V_{OLP}$  ( $V_{CMP_OPEN}$ -0.2V, typ.) and after de-bounce about 210ms ( $T_{DEB_OLP}$ , typ.), LD7841 will enforce the gate off until the 4<sup>th</sup> cycle of VCC hiccup is tripped and the fault condition is removed.

### Secondary Diode Short Protection – 8 Hiccups

The circuit detects output diode short condition if 7 consecutive switching cycles occur within which the CS pin voltage exceeds  $V_{OCP2}$  (0.7V ,typ) during leading-edge blanking time (T<sub>LEB</sub>), LD7841 will enforce the gate off until the 8<sup>th</sup> cycle of VCC hiccup is tripped and the fault condition is removed.

### Internal Over Temperature Protection - 1 Hiccup

When the junction temperature reaches 140°C approximately, the thermal sensor signals would stop IC's switching. If the IC's junction temperature cools by 20°C or VCC restart again.

11/18/2020

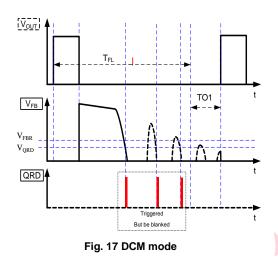

Package Information SOP-8

|        | <b>Dimensions</b> i | n Millimeters | Dimensio | ns in Inch |

|--------|---------------------|---------------|----------|------------|

| Symbol | MIN                 | МАХ           | MIN      | МАХ        |

| A      | 4.801               | 5.004         | 0.189    | 0.197      |

| В      | 3.810               | 3.988         | 0.150    | 0.157      |

| c      | 1.346               | 1.753         | 0.053    | 0.069      |

| D      | 0.330               | 0.508         | 0.013    | 0.020      |

| F      | 1.194               | 1.346         | 0.047    | 0.053      |

| н      | 0.178               | 0.254         | 0.007    | 0.010      |

| I      | 0.102               | 0.254         | 0.004    | 0.010      |

| J      | 5.791               | 6.198         | 0.228    | 0.244      |

| М      | 0.406               | 1.270         | 0.016    | 0.050      |

| θ      | 0°                  | 8°            | 0°       | 8°         |

### **Revision History**

| REV. | Date       | Change Notice           |

|------|------------|-------------------------|

| P00  | 11/18/2020 | Original Specification. |

#### **Important Notice**

Leadtrend Technology Corp. reserves the right to make changes or corrections to its products at any time without notice. Customers should verify the datasheets are current and complete before placing order.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Voltage Regulators category:

Click to view products by Leadtrend manufacturer:

Other Similar products are found below :

FAN53610AUC33XFAN53611AUC123XEN6310QA160215R3KE177614MPQ4423GQ-AEC1-ZFAN53611AUC12XMAX809TTRNCV891234MW50R2GAST1S31PURNCP81103MNTXGNCP81203PMNTXGNCP81208MNTXGPCA9412AUKZNCP81109GMNTXGNCP81109JMNTXGMP2161AGJ-ZNCP81241MNTXGMPQ4481GU-AEC1-PMP8756GD-PMPQ2171GJ-PMPQ2171GJ-AEC1-PMP2171GJ-PNCV1077CSTBT3GMP28160GC-ZMPM3509GQVE-AEC1-PXDPE132G5CG000XUMA1MP5461GC-PIR3888AMTRPBFAUMA1MPQ4409GQBE-AEC1-PS-19903DA-A8T1U7S-19903CA-A6T8U7S-19903CA-S8T1U7S-19902BA-A6T8U7S-19902CA-A6T8U7AP7361EA-SPR-13AP7361EA-33DR-13S-19902AA-A6T8U7S-19903AA-A6T8U7S-19902AA-S8T1U7S-19902BA-A8T1U7AU8310LMR36503R5RPERLMR36503RFRPERXC9110C301MR-GXC9141A50CMR-GXCL206F083CR-GXCL210A111GR-GLTM4663EV#PBF