#### **FEATURES**

- Wide Operating Input Voltage Range: 4.5V to 38V

- 10A DC Typical, 12A Peak Output Current

- **Output Range: 0.6V to 6V**

- ±1.5% Maximum Total Output DC Voltage Error

- Differential Remote Sense Amplifier for POL Regulation

- Internal Temperature, Analog Indicator Output

- **Overcurrent Foldback and Overtemperature** Protection

- Current Mode Control/Fast Transient Response

- Parallelable for Higher Output Current [2]

- Selectable Pulse-Skipping Operation

- Soft-Start/Voltage Tracking/Pre-Bias Start-Up

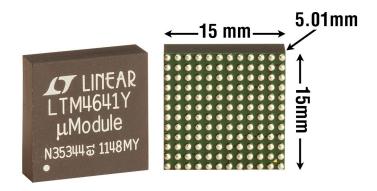

- 15mm  $\times$  15mm  $\times$  5.01mm BGA Package

- SnPb or RoHS Compliant Finish

#### Input Protection 💿

- UVLO, Overvoltage Shutdown and Latchoff Thresholds

- N-Channel Overvoltage Power-Interrupt MOSFET Driver

- Surge Stopper Capable with Few External Components

#### Load Protection D

- Robust, Resettable Latchoff Overvoltage Protection

- N-Channel Overvoltage Crowbar Power MOSFET Driver

#### **APPLICATIONS**

- Ruggedized Electronics

- Avionics and Industrial Equipment

## 38V, 10A DC/DC µModule Regulator with Advanced Input and Load Protection

#### DESCRIPTION

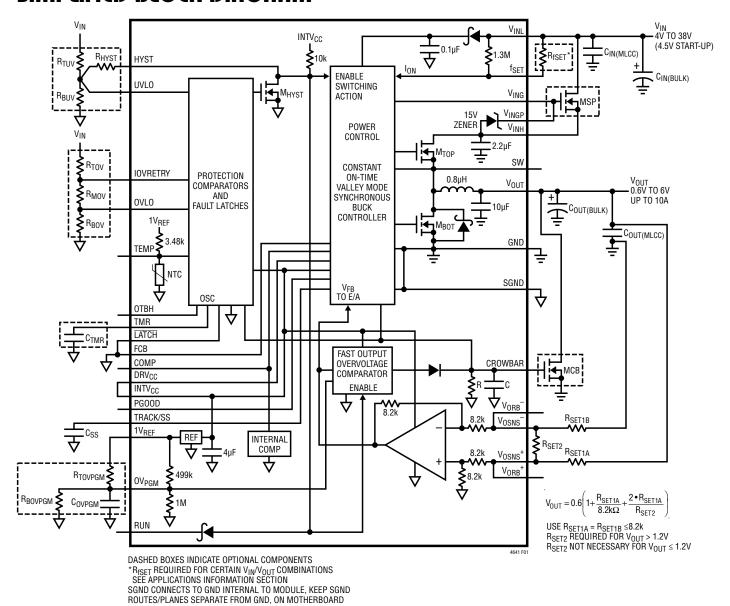

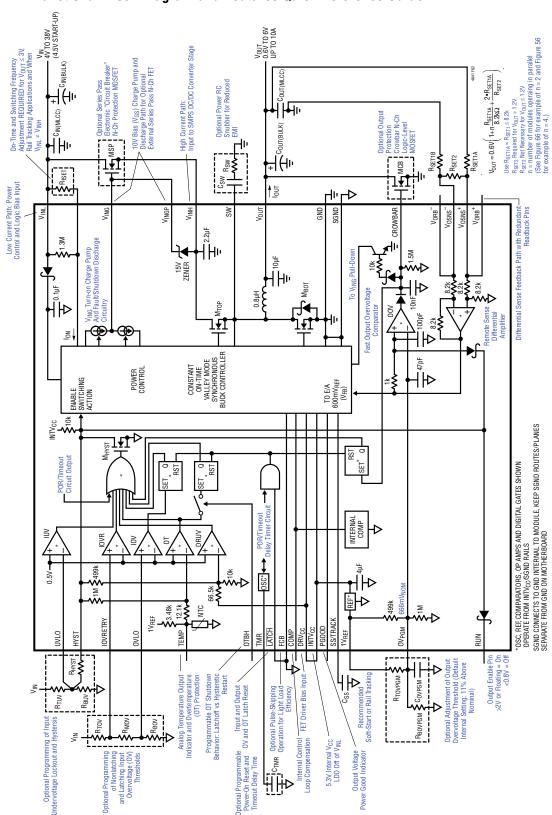

The LTM®4641 is a switch mode step-down DC/DC uModule® (micromodule) regulator with advanced input and load protection features. Trip detection thresholds for the following faults are customizable: input undervoltage, overtemperature, input overvoltage and output overvoltage. Select fault conditions can be set for latchoff or hysteretic restart response—or disabled. Included in the package are the switching controller and housekeeping ICs, power MOSFETs, inductor, overvoltage drivers, biasing circuitry and supporting components. Operating from input voltages of 4V to 38V (4.5V start-up), the device supports output voltages from 0.6V to 6V, set by an external resistor network remote sensing the point-of-load's voltage.

The LTM4641's high efficiency design can deliver up to 10A continuous current with a few input and output capacitors. The regulator's constant on-time current mode control architecture enables high step-down ratios and fast response to transient line and load changes. The LTM4641 is offered in a 15mm  $\times$  15mm  $\times$  5.01mm with SnPb or RoHS compliant terminal finish.

LT, LTC, LTM, µModule, Burst Mode, Linear Technology and the Linear logo are registered trademarks and LTpowerCAD is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5481178, 5847554, 6100678, 6304066, 6580258, 6677210, 8163643.

Click to view associated TechClip Videos.

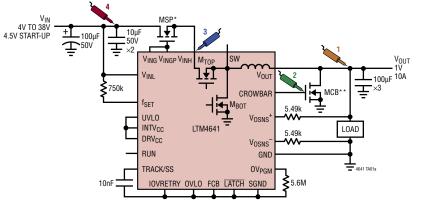

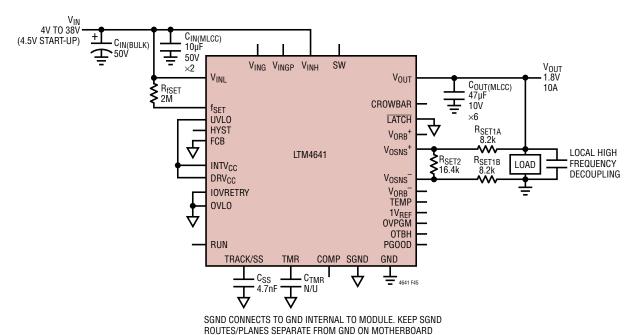

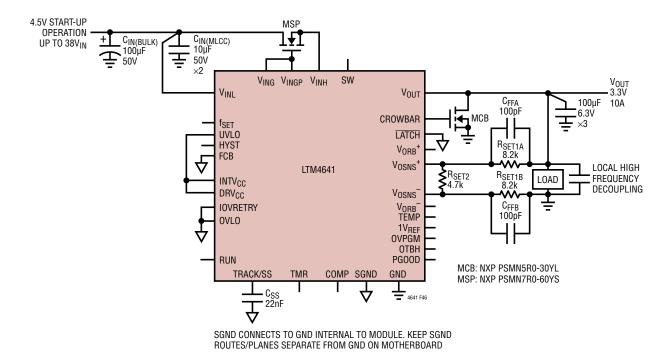

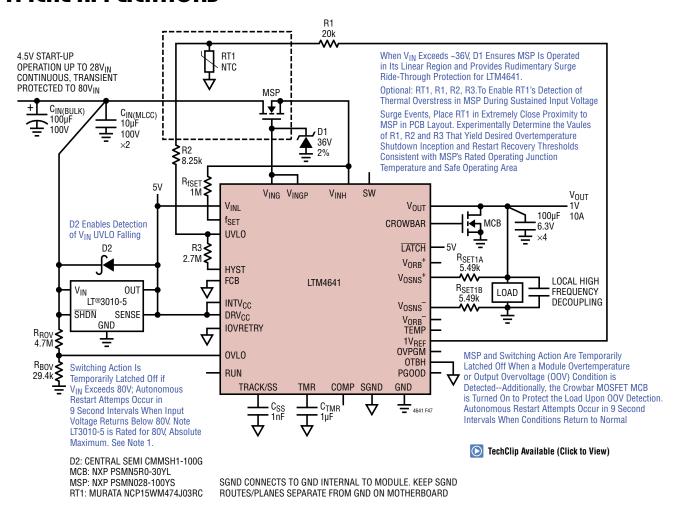

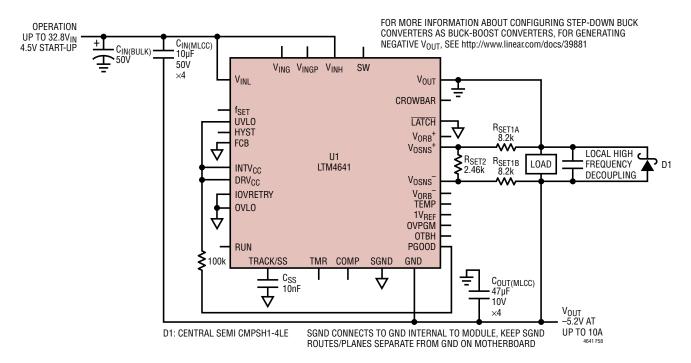

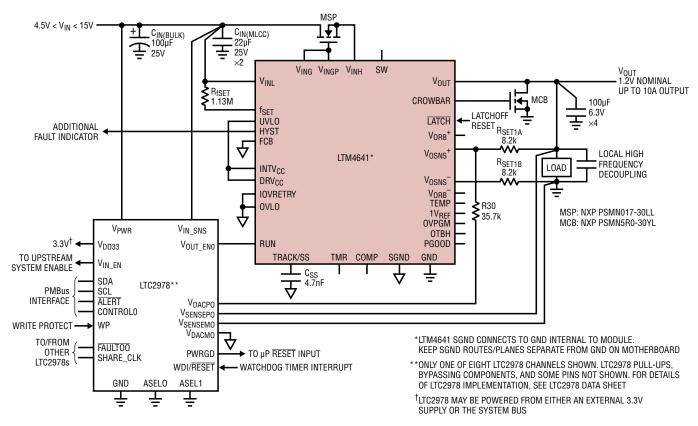

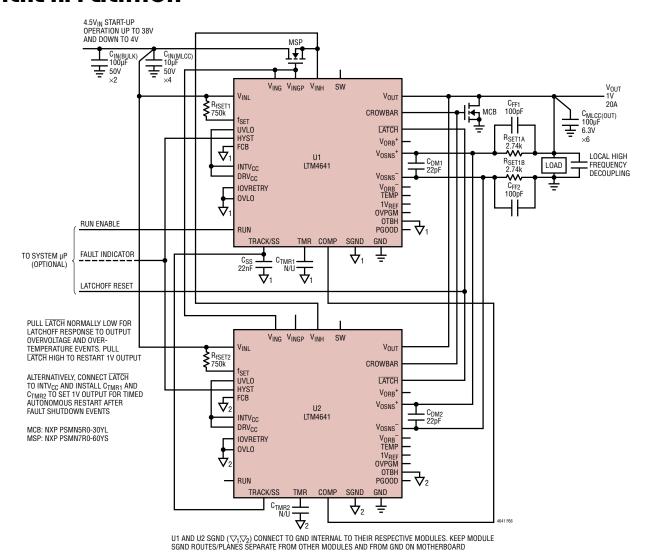

#### TYPICAL APPLICATION

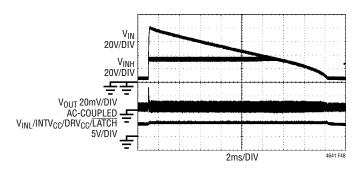

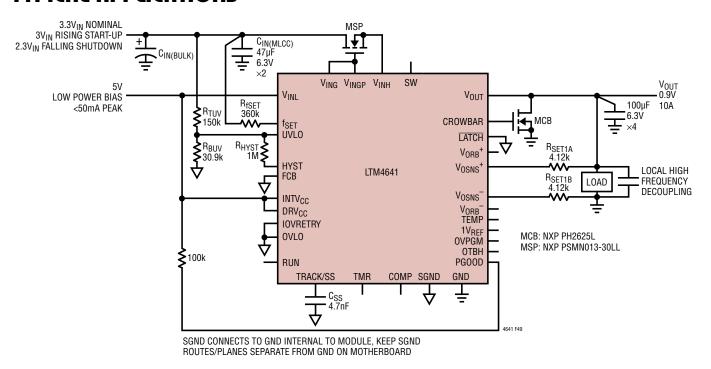

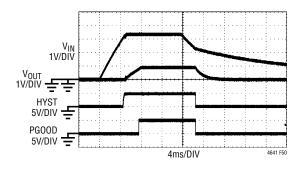

µModule Regulator with Input Disconnect and Fast Crowbar Output Overvoltage Protection

SGND CONNECTS TO GND INTERNAL TO µMODULE REGULATOR

MSP: (OPTIONAL) SERIES-PASS OVERVOLTAGE POWER INTERRUPT MOSFET, NXP PSMN014-60LS

(OPTIONAL) OUTPUT OVERVOLTAGE CROWBAR MOSFET, NXP PH2625

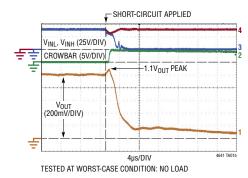

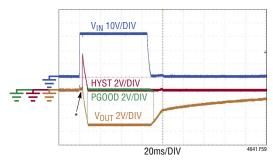

#### 1V Load Protected from M<sub>TOP</sub> Short-Circuit at 38V<sub>IN</sub>

## LTM4641

### TABLE OF CONTENTS

| Features                                                                  |       |

|---------------------------------------------------------------------------|-------|

| Applications                                                              | 1     |

| Typical Application                                                       | 1     |

| Description                                                               | 1     |

| Absolute Maximum Ratings                                                  | 3     |

| Order Information                                                         | 3     |

| Pin Configuration                                                         | 3     |

| Electrical Characteristics                                                | 4     |

| Typical Performance Characteristics                                       |       |

| Pin Functions                                                             |       |

| Simplified Block Diagram                                                  | . 15  |

| Decoupling Requirements                                                   |       |

| Operation                                                                 |       |

| Introduction                                                              |       |

| Motivation                                                                | . 16  |

| Power µModule Regulator Reliability                                       | . 16  |

| Overview                                                                  | . 16  |

| Applications Information—Power Supply Features .                          | . 17  |

| Power (V <sub>INH</sub> ) and Bias (V <sub>INL</sub> ) Input Pins         | . 17  |

| Switching Frequency (On Time) Selection and                               |       |

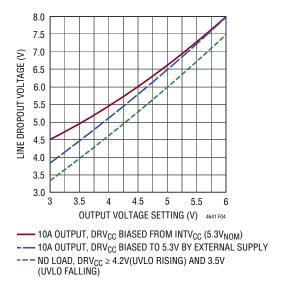

| Voltage Dropout Criteria (Achievable V <sub>IN</sub> -to-V <sub>OUT</sub> |       |

| Step-Down Ratios)                                                         | . 18  |

| Setting the Output Voltage; the Differential                              |       |

| Remote Sense Amplifier                                                    |       |

| Input Capacitors                                                          | . 23  |

| Output Capacitors and                                                     |       |

| Loop Stability/Loop Compensation                                          | . 23  |

| Pulse-Skipping Mode vs                                                    |       |

| Forced Continuous Mode                                                    | . 24  |

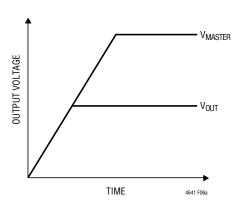

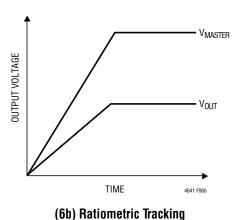

| Soft-Start, Rail-Tracking and Start-Up Into                               |       |

| Pre-Bias                                                                  |       |

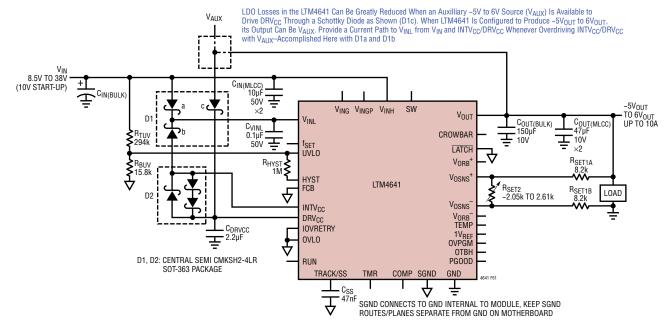

| INTV <sub>CC</sub> and DRV <sub>CC</sub>                                  | 27    |

| 1V <sub>REF</sub>                                                         | 28    |

| TEMP, OTBH and Overtemperature Protection                                 |       |

| Input Monitoring Pins: UVLO, IOVRETRY, OVLO                               | . 29  |

| Applications Information—Input Protection                                 | 20    |

| Features                                                                  | . 29  |

| Power-On Reset and Timeout Delay Time                                     | 21    |

| I OWEITOH NESEL AND THIREOUL DEIAY THIRE                                  | . J I |

| Applications Information—Load Protection          |    |

|---------------------------------------------------|----|

| Features                                          |    |

| Overcurrent Foldback Protection                   | 32 |

| Power Good Indicator and Latching Output          |    |

| Overvoltage Protection                            | 32 |

| Power-Interrupt MOSFET (MSP), CROWBAR Pin         |    |

| and Output CROWBAR MOSFET (MCB)                   |    |

| Fast Output Overvoltage Comparator Threshold      |    |

| The Switching Node: SW Pin                        | 35 |

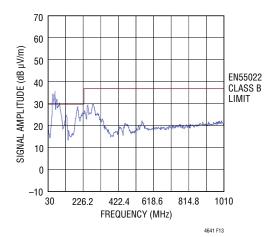

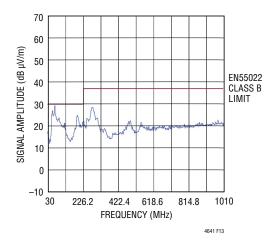

| Applications Information—EMI Performance          | 35 |

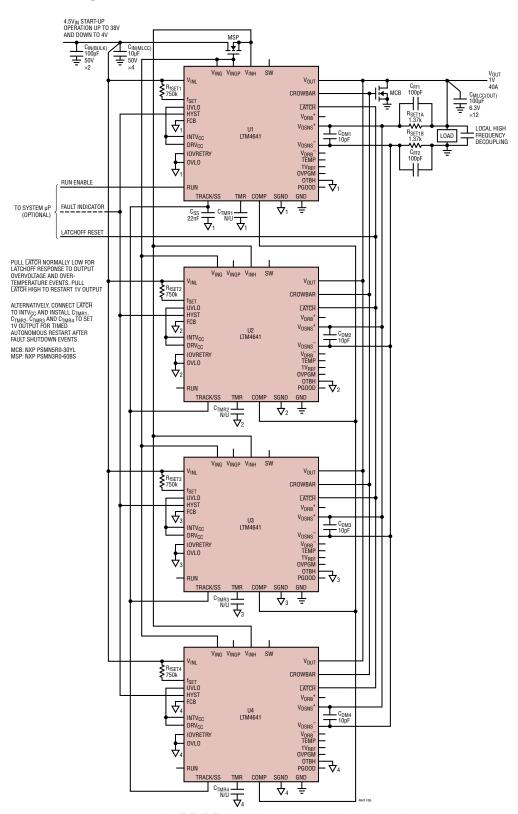

| Applications Information—Multimodule              |    |

| Parallel Operation                                | 36 |

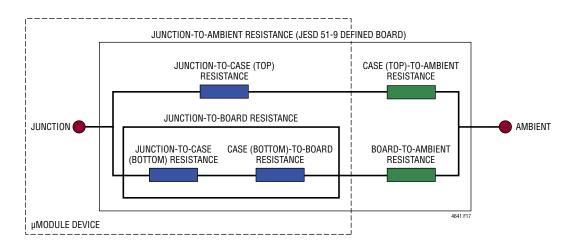

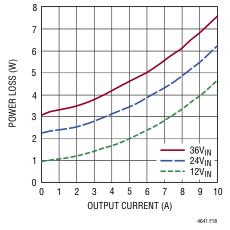

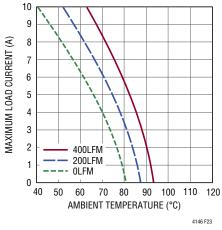

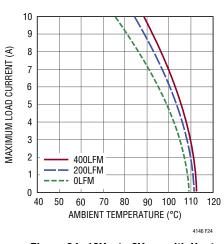

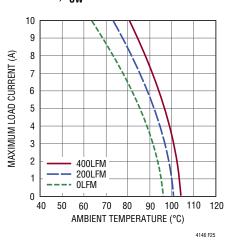

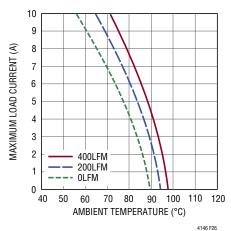

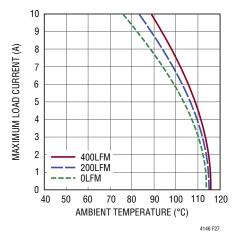

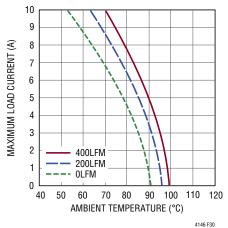

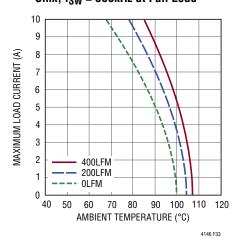

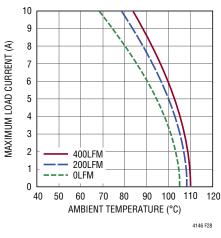

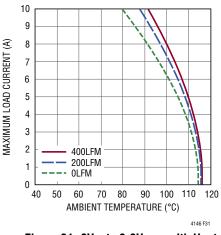

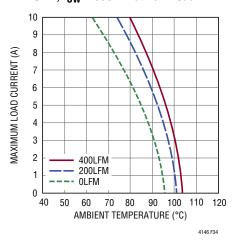

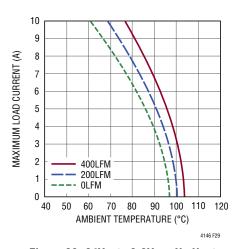

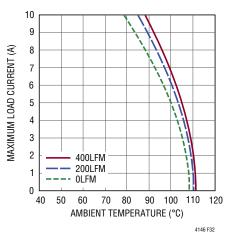

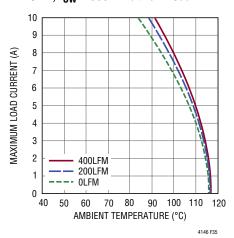

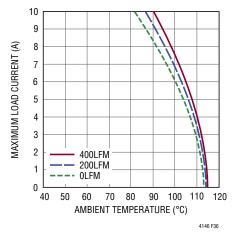

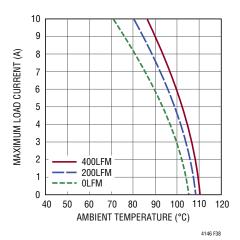

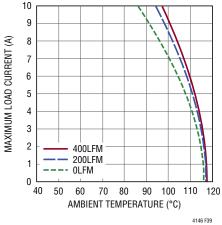

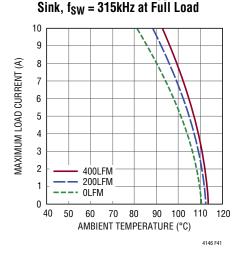

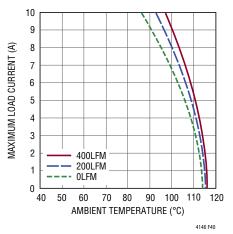

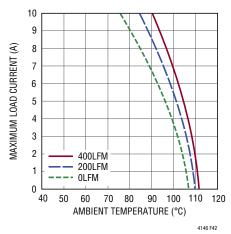

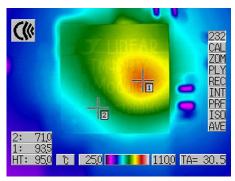

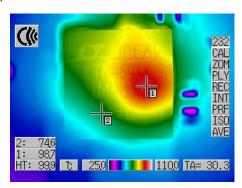

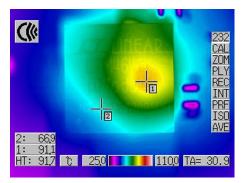

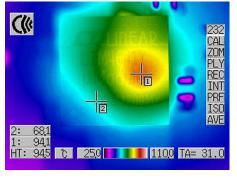

| Applications Information—Thermal Considerations   | ~~ |

| and Output Current Derating                       | 38 |

| Thermal Considerations and                        | 00 |

| Output Current Derating                           | 38 |

| Applications Information—Output Capacitance       | 45 |

| Table                                             | 45 |

| Applications Information—Safety and Layout        | 46 |

| Guidance                                          |    |

| Safety Considerations                             |    |

| Layout Checklist/Example                          |    |

| Typical Applications                              |    |

| Appendix A. Functional Block Diagram and          | JU |

| Features Quick Reference Guide                    | 56 |

| Appendix B. Start-Up/Shutdown State Diagram       |    |

| Appendix C. Switching Frequency Considerations    | Ji |

| and Usage of R <sub>fSFT</sub>                    | 58 |

| Appendix D. Remote Sensing in                     | 50 |

| Harsh Environments                                | 59 |

| Appendix E. Inspiration For Pulse-Skipping        | 00 |

| Mode Operation                                    | 60 |

| Appendix F. Adjusting the Fast Output Overvoltage | 00 |

| Comparator Threshold                              | 60 |

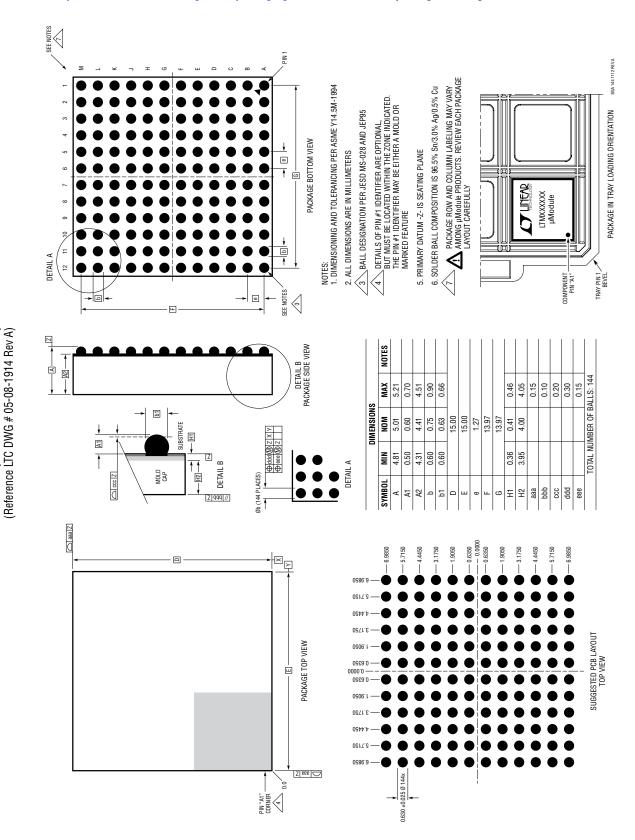

| Package Description                               |    |

| Package Photo                                     |    |

| Package Description                               |    |

| Revision History                                  |    |

| Typical Application                               |    |

| Related Parts                                     | 66 |

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Terminal Voltages                                                             |

|-------------------------------------------------------------------------------|

| V <sub>INL</sub> , V <sub>INH</sub> , SW, f <sub>SET</sub> 0.3V to 40V        |

| V <sub>OUT</sub> 0.3V to 9.2V                                                 |

| V <sub>ING</sub> –0.3V to V <sub>INH</sub> + 20V                              |

| INTV <sub>CC</sub> , DRV <sub>CC</sub> , RUN, TRACK/SS, PGOOD,                |

| CROWBAR, HYST0.3V to 6V                                                       |

| FCB, TMR0.3V to INTV <sub>CC</sub> + 0.3V                                     |

| COMP0.3V to 2.7V                                                              |

| V <sub>OSNS</sub> <sup>+</sup> , V <sub>ORB</sub> <sup>+</sup> –0.6V to 9.7V  |

| $V_{OSNS}^{-}$ , $V_{ORB}^{-}$ $V_{OSNS}^{+}$ – 2.7V to $V_{OSNS}^{+}$ + 0.3V |

| OTBH, UVLO, IOVRETRY, OVLO,                                                   |

| LATCH–0.3V to 7.5V                                                            |

| TEMP, OV <sub>PGM</sub> –0.3V to 1.5V                                         |

| Terminal Currents                                                             |

| INTV <sub>CC</sub> (Continuous)–30mA                                          |

| INTV <sub>CC</sub> (Continuous; CROWBAR                                       |

| Sourcing 15mA)15mA                                                            |

| CROWBAR (Continuous)15mA                                                      |

| V <sub>INGP</sub> (Continuous)–50mA to 15mA                                   |

| 1V <sub>REF</sub> (Continuous)–1mA to 1mA                                     |

| Internal Operating Temperature Range (Note 2)                                 |

| E- and I-Grades40°C to 125°C                                                  |

| MP-Grade –55°C to 125°C                                                       |

| Storage Temperature Range55°C to 125°C                                        |

| Peak Package Body Temperature (SMT Reflow) 245°C                              |

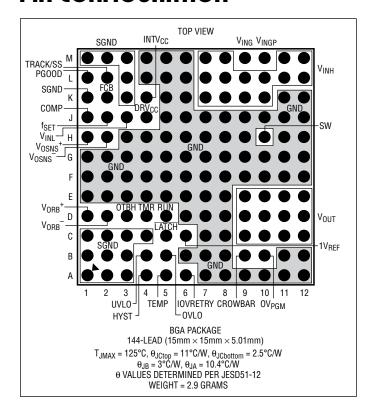

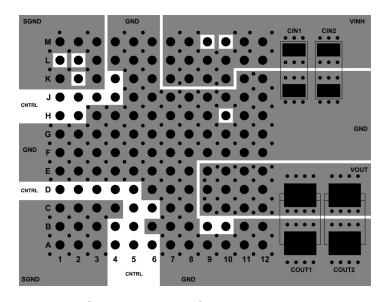

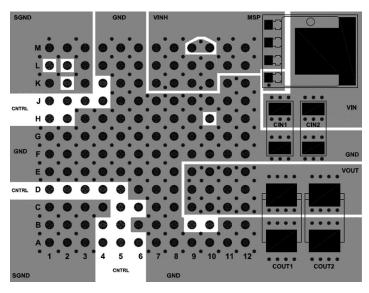

#### PIN CONFIGURATION

### ORDER INFORMATION

| PART NUMBER    | PAD OR BALL FINISH | PART MARKING* |             | PACKAGE | MSL    | TEMPERATURE RANGE |

|----------------|--------------------|---------------|-------------|---------|--------|-------------------|

|                |                    | DEVICE        | FINISH CODE | TYPE    | RATING | (Note 2)          |

| LTM4641EY#PBF  | SAC305 (RoHS)      | LTM4641Y      | e1          | BGA     | 4      | -40°C to 125°C    |

| LTM4641IY#PBF  | SAC305 (RoHS)      | LTM4641Y      | e1          | BGA     | 4      | -40°C to 125°C    |

| LTM4641IY      | SnPb (63/37)       | LTM4641Y      | e0          | BGA     | 4      | -40°C to 125°C    |

| LTM4641MPY#PBF | SAC305 (RoHS)      | LTM4641Y      | e1          | BGA     | 4      | –55°C to 125°C    |

| LTM4641MPY     | SnPb (63/37)       | LTM4641Y      | e0          | BGA     | 4      | −55°C to 125°C    |

Consult Marketing for parts specified with wider operating temperature ranges. \*Device temperature grade is indicated by a label on the shipping container. Pad or ball finish code is per IPC/JEDEC J-STD-609.

• Pb-free and Non-Pb-free Part Markings: www.linear.com/leadfree

- Recommended LGA and BGA PCB Assembly and Manufacturing Procedures: www.linear.com/umodule/pcbassembly

- LGA and BGA Package and Tray Drawings: www.linear.com/packaging

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full internal operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 2). $V_{IN} = V_{INH} = V_{INL} = 28V$ , per the typical application shown in Figure 45, unless otherwise noted.

| SYMBOL                         | PARAMETER                                                             | CONDITIONS                                                                                                                                                                       |   | MIN            | TYP                | MAX            | UNITS             |

|--------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|--------------------|----------------|-------------------|

| $V_{IN}$                       | Input DC Voltage                                                      |                                                                                                                                                                                  | • | 4.5            |                    | 38             | V                 |

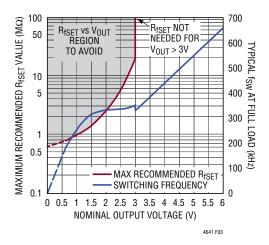

| V <sub>OUT</sub>               | Output Voltage Range                                                  | Use $R_{SET1A} = R_{SET1B} \le 8.2 k\Omega$ . $R_{fSET}$ Values Recommended in Table 1                                                                                           | • | 0.6            |                    | 6              | V                 |

| V <sub>OUT(DC)</sub>           | Output Voltage, Total Variation with Line and Load, and Prior to UVLO | $4.5V \le V_{IN} \le 38V$ , $0A \le I_{OUT} \le 10A$<br>$V_{IN} = 4V$ (Ramped Down from 4.5V), $I_{OUT} = 0A$                                                                    | • | 1.773<br>1.773 | 1.800<br>1.800     | 1.827<br>1.827 | V                 |

| Input Specifications           |                                                                       |                                                                                                                                                                                  |   |                |                    |                |                   |

| V <sub>RUN(ON,OFF)</sub>       | RUN On/Off Threshold                                                  | Run Rising, Turn On<br>Run Falling, Turn Off                                                                                                                                     | • | 0.8            | 1.25<br>1.15       | 2              | V                 |

| I <sub>RUN(ON)</sub>           | RUN Pull-Up Current                                                   | $V_{RUN} = 0V$<br>$V_{RUN} = 3.3V$                                                                                                                                               | • | -580<br>-220   | -520<br>-165       | -460<br>-110   | μA<br>μA          |

| I <sub>RUN(OFF)</sub>          | RUN Pull-Down Current, Switching Inhibited                            | V <sub>RUN</sub> = 3.3V, UVLO = 0V (M <sub>HYST</sub> On)                                                                                                                        |   |                | 1                  |                | nA                |

| V <sub>INL(UVLO)</sub>         | V <sub>INL</sub> Undervoltage Lockout                                 | V <sub>INL</sub> Rising<br>V <sub>INL</sub> Falling<br>Hysteresis                                                                                                                | • | 3.5<br>300     | 4.2<br>3.8<br>400  | 4.5<br>4       | V<br>V<br>mV      |

| INRUSH(VINH)                   | Input Inrush Current Through V <sub>INH</sub> , at Start-Up           | C <sub>SS</sub> = Open                                                                                                                                                           |   |                | 230                |                | mA                |

| I <sub>Q(VINH)</sub>           | Power Stage Bias Current (I <sub>VINH</sub> ) at<br>No Load           | I <sub>OUT</sub> = 0A and:<br>FCB ≥ 0.84V (Pulse-Skipping Mode)<br>FCB ≤ 0.76V (Forced Continuous Mode)<br>Shutdown, RUN = 0                                                     |   |                | 8<br>29<br>0.2     |                | mA<br>mA<br>mA    |

| I <sub>Q(VINL)</sub>           | Control Bias Current (I <sub>VINL</sub> )                             | INTV <sub>CC</sub> Connected to DRV <sub>CC</sub> and: $V_{IN} = 28V, \ I_{OUT} = 0A$ $V_{IN} = 28V, \ I_{OUT} = 10A$ $V_{IN} = 28V, \ Shutdown, \ RUN = 0$                      |   |                | 14.5<br>15.5<br>5  |                | mA<br>mA<br>mA    |

| I <sub>S(VINH)</sub>           | Power Stage Input Current (I <sub>VINH</sub> ) at Full Load           | $I_{OUT}$ = 10A and:<br>$V_{IN}$ = 4.5V<br>$V_{IN}$ = 28V<br>$V_{IN}$ = 38V                                                                                                      |   |                | 4.65<br>790<br>590 |                | A<br>mA<br>mA     |

| <b>Output Specification</b>    | ıs                                                                    |                                                                                                                                                                                  |   |                |                    |                |                   |

| I <sub>OUT(DC)</sub>           | Output Continuous Current Range                                       | (Note 3)                                                                                                                                                                         | • | 0              |                    | 10             | A                 |

| $\Delta V_{OUT(LINE)}/V_{OUT}$ | Line Regulation Accuracy                                              | V <sub>IN</sub> from 4.5V to 38V, I <sub>OUT</sub> = 0A                                                                                                                          | • |                | 0.02               | 0.15           | %                 |

| $\Delta V_{OUT(LOAD)}/V_{OUT}$ | Load Regulation Accuracy                                              | I <sub>OUT</sub> from 0A to 10A (Note 3)                                                                                                                                         | • |                | 0.04               | 0.15           | %                 |

| V <sub>OUT(AC)</sub>           | Output Voltage Ripple Amplitude                                       | I <sub>OUT</sub> = 0A                                                                                                                                                            |   |                | 16                 |                | mV <sub>P-P</sub> |

| fs                             | Output Voltage Ripple Frequency                                       | I <sub>OUT</sub> = 0A<br>I <sub>OUT</sub> = 10A                                                                                                                                  |   |                | 290<br>330         |                | kHz<br>kHz        |

| V <sub>OUT(START)</sub>        | Turn-On Overshoot                                                     | I <sub>OUT</sub> = 0A                                                                                                                                                            |   |                | 10                 |                | mV                |

| t <sub>START</sub>             | V <sub>IN</sub> -to-V <sub>OUT</sub> Start-Up Time                    | RUN Electrically Open Circuit, Time Between Application of $V_{IN}$ to $V_{OUT}$ Becoming Regulated, $OV_{PGM}=1.5V,C_{TMR}=C_{SS}=Open$                                         |   |                | 3                  |                | ms                |

| t <sub>run(on-delay)</sub>     | RUN-to-V <sub>OUT</sub> Turn-On Response<br>Time                      | V <sub>IN</sub> Established, (TMR-Set POR Time Expired)<br>Time Between RUN Releasing from GND to<br>PGOOD Going Logic High, C <sub>SS</sub> = Open,<br>OV <sub>PGM</sub> = 1.5V |   |                | 175                | 400            | μѕ                |

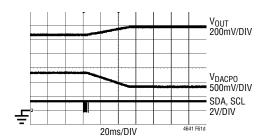

| $\Delta V_{OUT(LS)}$           | Peak Deviation for Dynamic Load<br>Step                               | I <sub>OUT</sub> from 0A to 5A at 5A/μs<br>I <sub>OUT</sub> from 5A to 0A at 5A/μs                                                                                               |   |                | 40<br>40           |                | mV<br>mV          |

| t <sub>SETTLE(LS)</sub>        | Settling Time for Dynamic Load Step                                   | $I_{OUT}$ from 0A to 5A at 5A/ $\mu$ s $I_{OUT}$ from 5A to 0A at 5A/ $\mu$ s                                                                                                    |   |                | 20<br>20           |                | μs<br>μs          |

T LINEAR

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full internal operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = V_{INH} = V_{INL} = 28V$ , per the typical application shown in Figure 45, unless otherwise noted.

| SYMBOL                                                     | PARAMETER                                                                                           | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                      |   | MIN                      | TYP                      | MAX                      | UNITS          |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------|--------------------------|--------------------------|----------------|

| I <sub>OUT(PK)</sub>                                       | Output Current Limit                                                                                | 5.1kΩ Pull-Up from PGOOD to 5V Source, I <sub>OUT</sub><br>Ramped Up Until V <sub>OUT</sub> Below PGOOD Lower<br>Threshold, PGOOD Pulls Logic Low                                                                                                                                                                                                                                               |   |                          | 24                       |                          | A              |

| I <sub>VINH(IOUT_SHORT)</sub>                              | Power Stage Input Current During<br>Output Short Circuit                                            | V <sub>OUT</sub> Electrically Shorted to GND                                                                                                                                                                                                                                                                                                                                                    |   |                          | 45                       |                          | mA             |

| Control Section                                            | -                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                 |   |                          |                          |                          |                |

| V <sub>FB</sub>                                            | Differential Feedback Voltage from V <sub>OSNS</sub> <sup>+</sup> to V <sub>OSNS</sub> <sup>-</sup> | I <sub>OUT</sub> = 0A                                                                                                                                                                                                                                                                                                                                                                           | • | 591                      | 600                      | 609                      | mV             |

| I <sub>TRACK/SS</sub>                                      | TRACK/SS Pull-Up Current                                                                            | V <sub>TRACK/SS</sub> = 0V                                                                                                                                                                                                                                                                                                                                                                      |   | -0.45                    | -1                       |                          | μΑ             |

| $\overline{V_{FCB}}$                                       | FCB Threshold                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                 |   | 0.76                     | 8.0                      | 0.84                     | V              |

| I <sub>FCB</sub>                                           | FCB Pin Current                                                                                     | $V_{FCB} = 0.8V$                                                                                                                                                                                                                                                                                                                                                                                |   |                          | 0                        | ±1                       | μA             |

| t <sub>ON(MIN)</sub>                                       | Minimum On-Time                                                                                     | (Note 4)                                                                                                                                                                                                                                                                                                                                                                                        |   |                          | 43                       | 75                       | ns             |

| t <sub>OFF(MIN)</sub>                                      | Minimum Off-Time                                                                                    | (Note 4)                                                                                                                                                                                                                                                                                                                                                                                        |   |                          | 220                      | 300                      | ns             |

| V <sub>OSNS(DM)</sub>                                      | Remote Sense Pin-Pair Differential<br>Mode Input Range                                              | Valid Differential V <sub>OSNS</sub> <sup>+</sup> -to- V <sub>OSNS</sub> <sup>-</sup> Range<br>(Use R <sub>SET1A</sub> = R <sub>SET1B</sub> ≤ 8.2k)                                                                                                                                                                                                                                             | • | 0                        |                          | 2.7                      | V              |

| V <sub>OSNS(CM)</sub>                                      | Remote Sense Pin-Pair Common<br>Mode Input Range                                                    | Valid V <sub>OSNS</sub> <sup>-</sup> Common Mode Range<br>Valid V <sub>OSNS</sub> <sup>+</sup> Common Mode Range<br>(Use R <sub>SET1A</sub> = R <sub>SET1B</sub> ≤ 8.2k)                                                                                                                                                                                                                        | • | -0.3                     |                          | 3                        | V<br>V         |

| R <sub>IN(VOSNS+)</sub>                                    | Input Resistance                                                                                    | V <sub>OSNS</sub> <sup>+</sup> to GND                                                                                                                                                                                                                                                                                                                                                           |   | 16318                    | 16400                    | 16482                    | Ω              |

| INTV <sub>CC</sub> , DRV <sub>CC</sub> , 1V <sub>F</sub>   | REF                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                 |   | '                        |                          |                          |                |

| V <sub>INTVCC</sub>                                        | Internal V <sub>CC</sub> Voltage                                                                    | $6V \leq V_{IN} \leq 38V, \mbox{ INTV}_{CC} \mbox{ Not Connected to DRV}_{CC}, \mbox{ DRV}_{CC} = 5.3V$                                                                                                                                                                                                                                                                                         | • | 5.1                      | 5.3                      | 5.4                      | V              |

| $\frac{\Delta V_{\text{INTVCC(LOAD)}}}{V_{\text{INTVCC}}}$ | INTV <sub>CC</sub> Load Regulation                                                                  | RUN = 0V, INTV <sub>CC</sub> Not Connected to DRV <sub>CC</sub> ,<br>DRV <sub>CC</sub> = 5.3V and:<br>I <sub>INTVCC</sub> Varied from 0mA to -20mA<br>I <sub>INTVCC</sub> Varied from 0mA to -30mA                                                                                                                                                                                              |   |                          | -0.7<br>-1               | ±2<br>±3                 | %<br>%         |

| V <sub>INTVCC(LOWLINE)</sub>                               | INTV <sub>CC</sub> Voltage at Low Line                                                              | $V_{IN}$ = 4.5V, $R_{SET1A}$ = $R_{SET1B}$ = $0\Omega$ (~0.6V <sub>OUT</sub> , $R_{fSET}$ Value Recommended in Table 1)                                                                                                                                                                                                                                                                         | • | 4.2                      | 4.3                      |                          | V              |

| DRV <sub>CC(UVLO)</sub>                                    | DRV <sub>CC</sub> Undervoltage Lockout                                                              | DRV <sub>CC</sub> Rising<br>DRV <sub>CC</sub> Falling                                                                                                                                                                                                                                                                                                                                           | • | 3.9<br>3.2               | 4.05<br>3.35             | 4.2<br>3.5               | V              |

| I <sub>DRVCC</sub>                                         | DRV <sub>CC</sub> Current                                                                           | INTV <sub>CC</sub> Not Connected to DRV <sub>CC</sub> , DRV <sub>CC</sub> = 5.3V, R <sub>SET1A</sub> , R <sub>SET1B</sub> and R <sub>SET2</sub> Setting V <sub>OUT</sub> to: 1.8V <sub>OUT</sub> , R <sub>ISET</sub> = $2M\Omega$ , $0A \le I_{OUT} \le 10A$ 6.0V <sub>OUT</sub> , R <sub>ISET</sub> = Open, $0A \le I_{OUT} \le 10A$ (Use R <sub>SET1A</sub> = R <sub>SET1B</sub> $\le 8.2k$ ) |   |                          | 11<br>20                 | 18<br>27                 | mA<br>mA       |

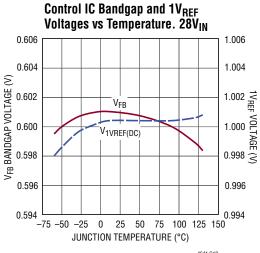

| V <sub>1VREF(DC)</sub>                                     | 1V <sub>REF</sub> DC Voltage Regulation                                                             | I <sub>1VREF</sub> = 0mA<br>I <sub>1VREF</sub> = ±1mA                                                                                                                                                                                                                                                                                                                                           | • | 0.985<br>0.980           | 1.000<br>1.000           | 1.015<br>1.020           | V              |

| PGOOD Output                                               |                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                 |   |                          |                          |                          |                |

| V <sub>PGOOD</sub> (TH)                                    | Power Good Window, Logic State<br>Transition Thresholds                                             | Ramping Differential $V_{OSNS}^+ - V_{OSNS}^-$ Voltage:<br>Up, PGOOD Goes Logic Low $\rightarrow$ High<br>Up, PGOOD Goes Logic High $\rightarrow$ Low<br>Down, PGOOD Goes Logic Low $\rightarrow$ High<br>Down, PGOOD Goes Logic High $\rightarrow$ Low                                                                                                                                         |   | 533<br>645<br>621<br>525 | 556<br>660<br>644<br>540 | 579<br>675<br>667<br>555 | mV<br>mV<br>mV |

| V <sub>PGOOD(HYST)</sub>                                   | Hysteresis                                                                                          | Differential V <sub>OSNS</sub> <sup>+</sup> – V <sub>OSNS</sub> <sup>-</sup> Voltage Returning                                                                                                                                                                                                                                                                                                  |   | 8                        | 16                       | 24                       | mV             |

| V <sub>PGOOD(VOL)</sub>                                    | Logic-Low Output Voltage                                                                            | I <sub>PGOOD</sub> = 5mA                                                                                                                                                                                                                                                                                                                                                                        | • |                          | 75                       | 400                      | mV             |

| t <sub>PGOOD</sub> (DELAY)                                 | PGOOD Logic-Low Blanking Time                                                                       | Delay Between Differential V <sub>OSNS</sub> <sup>+</sup> – V <sub>OSNS</sub> <sup>-</sup><br>Voltage Exiting PGOOD Valid Window to PGOOD<br>Going Logic Low (Note 4)                                                                                                                                                                                                                           |   |                          | 12                       |                          | μs             |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full internal operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = V_{INH} = V_{INL} = 28V$ , per the typical application shown in Figure 45, unless otherwise noted.

| SYMBOL                                            | PARAMETER                                                                | CONDITIONS                                                                                                                                                                                                                                                                                          |   | MIN                      | TYP                          | MAX                        | UNITS       |

|---------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------|------------------------------|----------------------------|-------------|

| Power-Interrupt MOSF                              | ET Drive                                                                 |                                                                                                                                                                                                                                                                                                     |   |                          |                              |                            |             |

| V <sub>VING</sub>                                 | Gate Drive Voltage for Power-<br>Interrupt MOSFET, MSP                   | $ \begin{array}{ c c c c c }\hline V_{IN}=4.5V,0A\leq I_{OUT}\leq 10A,V_{ING}Sourcing1\mu A\\ V_{IN}=28V,0A\leq I_{OUT}\leq 10A,V_{ING}Sourcing1\mu A\\ V_{IN}=38V,0A\leq I_{OUT}\leq 10A,V_{ING}Sourcing1\mu A\\ V_{IN}=4V(RampedDownfrom4.5V),I_{OUT}=0A,\\ V_{ING}Sourcing1\mu A\\ \end{array} $ | • | 11.5<br>35<br>45<br>10.5 | 13.3<br>38.4<br>48.4<br>11.5 | 15.5<br>41<br>51.5<br>14.2 | V<br>V<br>V |

| I <sub>VING(UP)</sub>                             | V <sub>ING</sub> Pull-Up Current                                         | V <sub>ING</sub> Tied to V <sub>INGP</sub> , and:<br>V <sub>IN</sub> = 4.5V, V <sub>ING</sub> Pulled to 6.5V<br>V <sub>IN</sub> = 28V, V <sub>ING</sub> Pulled to 30V                                                                                                                               | • | 350<br>425               | 475<br>550                   | 600<br>675                 | μΑ<br>μΑ    |

| IVING_DOWN(CROWBAR<br>ACTIVE,CROWBAR<br>INACTIVE) | V <sub>ING</sub> Pull-Down Current                                       | V <sub>ING</sub> Tied to V <sub>INGP</sub> , Pulled to 33V, and:<br>RUN Pulled to 0V (CROWBAR Inactive)<br>OV <sub>PGM</sub> Pulled to 0V (CROWBAR Active)                                                                                                                                          | • | 3<br>24                  | 20<br>27                     | 30<br>30                   | mA<br>mA    |

| t <sub>VING(OVP_DELAY)</sub>                      | V <sub>ING</sub> OVP Pull-Down Delay                                     | OV <sub>PGM</sub> Driven from 650mV to 550mV, V <sub>ING</sub><br>Discharge Response Time                                                                                                                                                                                                           | • |                          | 1.3                          | 2.6                        | μs          |

| I <sub>VINGP(LEAK)</sub>                          | Zener Diode Leakage Current                                              | V <sub>INGP</sub> Driven to (V <sub>INH</sub> + 10V)                                                                                                                                                                                                                                                |   |                          | 1                            |                            | nA          |

| V <sub>INGP(CLAMP)</sub>                          | Zener Diode Breakdown Voltage                                            | V <sub>INGP</sub> -to-V <sub>INH</sub> Differential Voltage; I <sub>VINGP</sub> = 5mA                                                                                                                                                                                                               |   |                          | 15                           |                            | V           |

| Fault Pins and Function                           | ins                                                                      |                                                                                                                                                                                                                                                                                                     |   | •                        |                              |                            |             |

| V <sub>OVPGM</sub>                                | Default Output Overvoltage Program<br>Setting                            | OV <sub>PGM</sub> Electrically Open Circuit                                                                                                                                                                                                                                                         | • | 650                      | 666                          | 680                        | mV          |

| I <sub>OVPGM(UP)</sub>                            | OV <sub>PGM</sub> Pull-Up Current                                        | OV <sub>PGM</sub> = 0V                                                                                                                                                                                                                                                                              | • | -2.07                    | -2                           | -1.91                      | μА          |

| I <sub>OVPGM(DOWN)</sub>                          | OV <sub>PGM</sub> Pull-Down Current                                      | OV <sub>PGM</sub> = 1V                                                                                                                                                                                                                                                                              | • | 0.945                    | 1                            | 1.06                       | μА          |

| OVP <sub>TH</sub>                                 | Output Overvoltage Protection Inception Threshold                        | Ramping Up Differential V <sub>OSNS</sub> <sup>+</sup> -to-V <sub>OSNS</sub> <sup>-</sup><br>Voltage Until CROWBAR Outputs Logic High                                                                                                                                                               | • | 647                      | 666                          | 683                        | mV          |

| OVP <sub>ERR</sub>                                | Output Overvoltage Protection Inception Error                            | Difference Between OVP <sub>TH</sub> and V <sub>OVPGM</sub> (OVP <sub>TH</sub> -V <sub>OVPGM</sub> )                                                                                                                                                                                                | • | -12                      | 0                            | 12                         | mV          |

| t <sub>CROWBAR(OVP_DELAY)</sub>                   | CROWBAR Response Time                                                    | OVP <sub>GM</sub> Driven from 650mV to 550mV                                                                                                                                                                                                                                                        | • |                          | 400                          | 500                        | ns          |

| V <sub>CROWBAR(OH)</sub>                          | CROWBAR Output, Active High<br>Voltage                                   | OVP <sub>GM</sub> Pulled to 0V and:<br>I <sub>CROWBAR</sub> = -100μA, I <sub>INTVCC</sub> = -20mA<br>I <sub>CROWBAR</sub> = -4mA, I <sub>INTVCC</sub> = -20mA                                                                                                                                       | • | 4.3<br>4.2               | 4.65<br>4.55                 | 5<br>4.9                   | V           |

| V <sub>CROWBAR(OL)</sub>                          | CROWBAR Output, Passive Low<br>Voltage                                   | I <sub>CROWBAR</sub> = 1μA                                                                                                                                                                                                                                                                          | • |                          | 260                          | 500                        | mV          |

| V <sub>CROWBAR(OVERSHOOT)</sub>                   | CROWBAR Peak Voltage Overshoot at V <sub>INL</sub> Start-Up and Shutdown | V <sub>INL</sub> Ramped Up from/Down to 0V                                                                                                                                                                                                                                                          | • |                          | 550                          | 900                        | mV          |

| V <sub>CROWBAR(TH)</sub>                          | CROWBAR Latchoff Threshold                                               | CROWBAR Ramped Up Until HYST Goes Logic<br>Low                                                                                                                                                                                                                                                      | • | 1.4                      | 1.5                          | 1.6                        | V           |

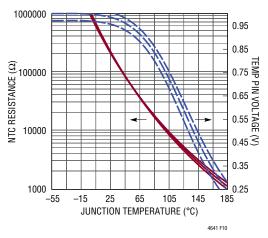

| $\overline{V_{TEMP}}$                             | TEMP Voltage                                                             | RUN = 0V, T <sub>A</sub> = 25°C<br>RUN = 0V, T <sub>A</sub> = 125°C<br>(See Figure 10 for Reference)                                                                                                                                                                                                |   | 950                      | 980<br>585                   | 1010                       | mV<br>mV    |

| OT <sub>TH(INCEPTION)</sub>                       | TEMP Overtemperature Inception<br>Threshold                              | Ramping TEMP Downward Until HYST Outputs Logic Low                                                                                                                                                                                                                                                  | • | 428                      | 438                          | 448                        | mV          |

| OT <sub>TH(RECOVER)</sub>                         | TEMP Overtemperature Recovery<br>Threshold                               | Ramping TEMP Upward Until HYST Outputs<br>Logic High                                                                                                                                                                                                                                                | • | 501                      | 514                          | 527                        | mV          |

| UVOV <sub>TH</sub>                                | UVLO/OVLO/IOVRETRY<br>Undervoltage/Overvoltage Inception<br>Thresholds   | Ramping UVLO, OVLO or IOVRETRY Positive Until HYST Toggles Its State                                                                                                                                                                                                                                | • | 488                      | 500                          | 512                        | mV          |

#### **ELECTRICAL CHARACTERISTICS**

shown in Figure 45, unless otherwise noted.

The • denotes the specifications which apply over the full internal operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C (Note 2).  $V_{IN} = V_{INH} = V_{INL} = 28V$ , per the typical application

| SYMBOL                                   | PARAMETER                                                          | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                      |   | MIN         | TYP        | MAX          | UNITS    |

|------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|------------|--------------|----------|

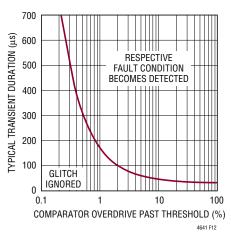

| t <sub>UVOVD</sub>                       | UVLO/OVLO/IOVRETRY/ TEMP<br>Response Time                          | ±50mV Overdrive (All Pins)<br>±5mV Overdrive, UVLO/OVLO/IOVRETRY Pins<br>Only (Note 4)                                                                                                                                                                                                                                                                                                                          | • | 50          | 25<br>125  | 100<br>500   | μs<br>μs |

| I <sub>UVOV</sub>                        | Input Current of UVLO, OVLO and IOVRETRY                           | UVLO = 0.55V or 0VLO = 0.45V or IOVRETRY = 0.45V                                                                                                                                                                                                                                                                                                                                                                | • |             |            | ±30          | nA       |

| V <sub>HOUSEKEEPING(UVLO)</sub>          | Housekeeping Circuitry UVLO                                        | Voltage on INTV <sub>CC</sub> , INTV <sub>CC</sub> Rising (Note 4)<br>Hysteresis, INTV <sub>CC</sub> Returning (Note 4)                                                                                                                                                                                                                                                                                         |   | 1.9<br>5    | 2<br>25    | 2.1<br>50    | V<br>mV  |

| V <sub>HYST(SWITCHING ON)</sub>          | HYST Voltage (M <sub>HYST</sub> Off, RUN<br>Logic High)            | RUN Electrically Open Circuit<br>RUN = 1.8V                                                                                                                                                                                                                                                                                                                                                                     | • | 4.9<br>1.85 | 5.1<br>2.1 | 5.25<br>2.35 | V        |

| VHYST(SWITCHING OFF, RUN)                | HYST Voltage (M <sub>HYST</sub> Off, RUN<br>Logic Low)             | RUN = 0V                                                                                                                                                                                                                                                                                                                                                                                                        | • | 170         | 350        | 480          | mV       |

| V <sub>HYST</sub> (SWITCHING OFF, FAULT) | HYST Voltage, Switching Action<br>Inhibited (M <sub>HYST</sub> On) | $ \begin{array}{l} \text{UVLO} < \text{UVOV}_{\text{TH}} \text{ or OVLO} > \text{UVOV}_{\text{TH}} \text{ or} \\ \text{IOVRETRY} > \text{UVOV}_{\text{TH}} \text{ or TEMP} < \text{OT}_{\text{TH}(\text{INCEPTION})} \\ \text{or CROWBAR} > \text{V}_{\text{CROWBAR}(\text{TH})} \text{ or} \\ \text{DRV}_{\text{CC}} < \text{DRVCC}_{\text{UVLO}(\text{FALLING})} \\ \text{(See Figures 62, 63)} \end{array} $ | • |             | 30         | 65           | mV       |

| TMR <sub>U0T0</sub>                      | Timeout and Power-On Reset Period                                  | C <sub>TMR</sub> = 1nF, Time from Fault Clearing to HYST<br>Being Released by Internal Circuitry                                                                                                                                                                                                                                                                                                                | • | 5           | 9          | 14           | ms       |

| V <sub>LATCH(IH)</sub>                   | LATCH Clear Threshold Input High                                   |                                                                                                                                                                                                                                                                                                                                                                                                                 | • | 1.2         |            |              | V        |

| V <sub>LATCH(IL)</sub>                   | LATCH Clear Threshold Input Low                                    |                                                                                                                                                                                                                                                                                                                                                                                                                 | • |             |            | 0.8          | V        |

| I <sub>LATCH</sub>                       | LATCH Input Current                                                | V <sub>LATCH</sub> = 7.5V                                                                                                                                                                                                                                                                                                                                                                                       | • |             |            | ±1           | μA       |

| I <sub>TMR(UP)</sub>                     | TMR Pull-Up Current                                                | V <sub>TMR</sub> = 0V                                                                                                                                                                                                                                                                                                                                                                                           | • | -1.2        | -2.1       | -2.8         | μA       |

| I <sub>TMR(DOWN)</sub>                   | TMR Pull-Down Current                                              | V <sub>TMR</sub> = 1.6V                                                                                                                                                                                                                                                                                                                                                                                         | • | 1.2         | 2.1        | 2.8          | μA       |

| V <sub>TMR(DIS)</sub>                    | Timer Disable Voltage                                              | Referenced to INTV <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                | • | -180        | -270       |              | mV       |

| OTBH <sub>VIL</sub>                      | OTBH Low Level Input Voltage                                       |                                                                                                                                                                                                                                                                                                                                                                                                                 | • |             |            | 0.4          | V        |

| OTBH <sub>VZ</sub>                       | OTBH Pin Voltage When Left<br>Electrically Open Circuit            | -10μA ≤ I <sub>OTBH</sub> ≤ 10μA                                                                                                                                                                                                                                                                                                                                                                                | • | 0.6         | 0.9        | 1.2          | V        |

| I <sub>OTBH(MAX)</sub>                   | Maximum OTBH Current                                               | OTBH Electrically Shorted to SGND                                                                                                                                                                                                                                                                                                                                                                               | • |             |            | 30           | μA       |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

The LTM4641 SW absolute maximum rating of 40V is verified in ATE by regulating VOLIT while at 40VIN, in a controlled manner guaranteed to not affect device reliability or lifetime. Static testing of SW leakage current at 40V<sub>IN</sub> is performed at control IC wafer level only.

Note 2: The LTM4641 is tested under pulsed load conditions such that  $T_{J} \approx T_{A}.$  The LTM4641E is guaranteed to meet performance specifications from 0°C to 125°C junction temperature. Specifications over the

-40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTM46411 is guaranteed over the -40°C to 125°C operating junction temperature range. The LTM4641MP is tested and guaranteed over the full -55°C to 125°C operating temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

Note 3: See output current derating curves for different V<sub>IN</sub>, V<sub>OUT</sub> and T<sub>A</sub>. Note 4: 100% tested at wafer level only.

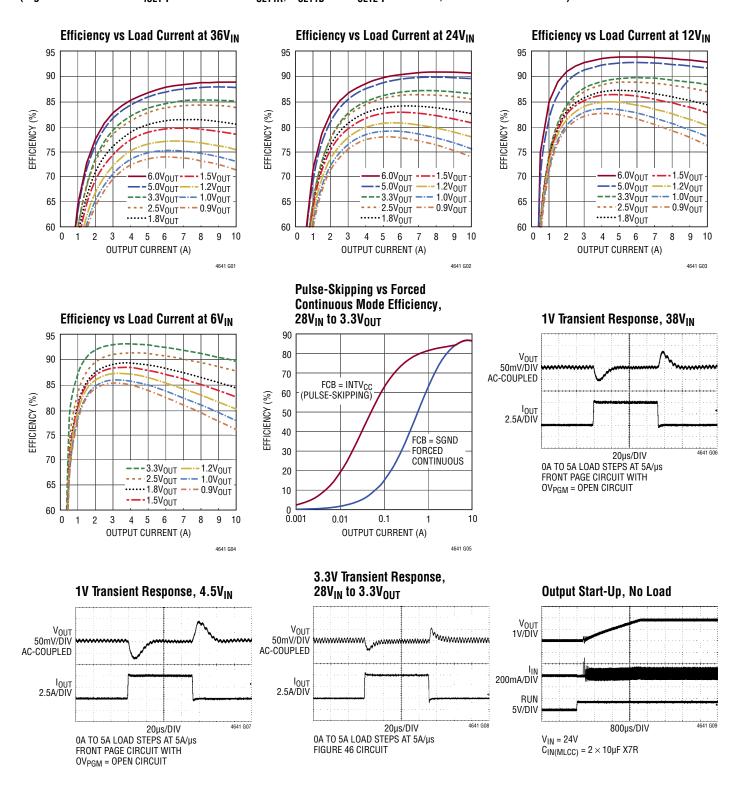

#### TYPICAL PERFORMANCE CHARACTERISTICS

(Figure 45 circuit with RfSET per Table 1 and RSET1A, RSET1B and RSET2 per Table 2, unless otherwise noted)

LINEAR

#### TYPICAL PERFORMANCE CHARACTERISTICS

(Figure 45 circuit with RfSET per Table 1 and RSET1A, RSET1B and RSET2 per Table 2, unless otherwise noted)

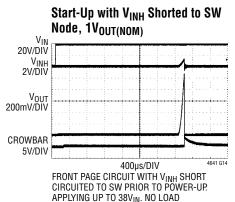

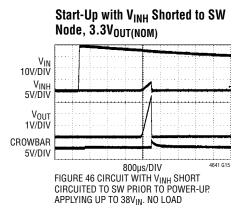

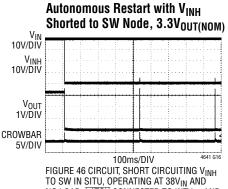

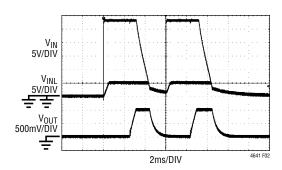

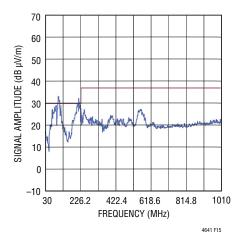

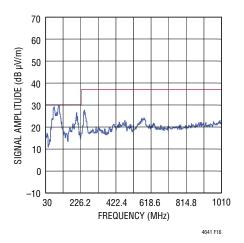

TO SW IN SITU, OPERATING AT 38V<sub>IN</sub> AND NO LOAD. LATCH CONNECTED TO INTV<sub>CC</sub> AND  $C_{TMR} = 47nF$

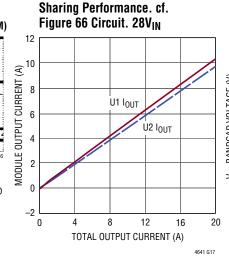

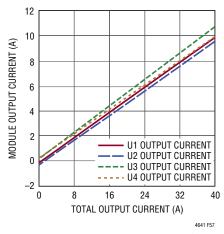

Paralleled Modules, Current-

**SGND** (A1-A3; B1-B3; C1-C4; K1, K3; L3; M1-M3): Signal Ground Pins. This is the return ground path for all analog control and low power circuitry. SGND is tied to GND internal to the μModule regulator in a manner that promotes the best internal signal integrity—therefore, SGND should not be connected to GND in the user's PCB layout. See the Layout Checklist/Example section of the Applications Information section for more information pertaining to SGND and layout. All SGND pins are electrically connected to each other, internally.

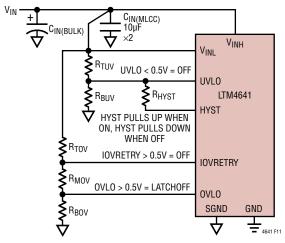

**HYST (A4):** Input Undervoltage Hysteresis Programming Pin. Normally used as an output, but can be used as an input. If the LTM4641's inherent, default undervoltage lockout (UVLO) settings are satisfactory, 4.5V<sub>IN(RISING, MAX)</sub> and 4V<sub>IN(FALLING, MAX)</sub>, HYST can be left electrically open circuit. See the Applications Information section to customize the LTM4641's UVLO thresholds.

HYST is a logic-high output with moderate pull-up strength that commands LTM4641's internal control IC to regulate the module's output voltage when conditions on the RUN, UVLO, OVLO, IOVRETRY, TEMP, CROWBAR, INTV $_{\rm CC}$  and DRV $_{\rm CC}$  pins permit it (any recent latchoff events notwithstanding, otherwise OTBH and LATCH can also play a role). When a fault condition is detected, internal circuitry (M $_{

m HYST}$ ; see Figure 1) drives HYST logic low and the LTM4641's output is turned off. HYST can be used as a fault-indicator. See the Applications Information section.

HYST is pulled low when the RUN pin is pulled low, via an internal Schottky diode. HYST can be driven low by external open-collector/open-drain circuitry directly—as an alternate to the RUN pin interface. However, external circuitry should never drive HYST high, since doing so (indiscriminately) could cause thermal overstress to MHYST, when MHYST is on.

**TEMP (A5):** Power Stage Temperature Indicator and Overtemperature Detection Pin. When left electrically open circuit, TEMP's voltage varies according to an internal NTC (negative temperature coefficient) thermistor, residing in close proximity to LTM4641's power stage. When TEMP falls below 438mV (corresponding to a thermistor and power stage temperature of ~145°C), the LTM4641 pulls HYST low to inhibit regulation of its output voltage. HYST

may be deasserted when TEMP subsequently exceeds 514mV (nominally corresponding to a cool-off hysteresis of ~10°C), depending on the OTBH setting. (See OTBH and the Applications Information section.)

To disable the  $\mu$ Module regulator's overtemperature shutdown feature, connect the TEMP and  $1V_{REF}$  pins. The thermal shutdown inception threshold can also be modified, see the Applications Information section.

**IOVRETRY (A6):** Nonlatching Input Overvoltage Threshold Programming Pin. The LTM4641 pulls HYST low to inhibit regulation of its output voltage when IOVRETRY exceeds 0.5V. The LTM4641 can resume switching action when IOVRETRY is below 0.5V. If no nonlatching input overvoltage shutdown behavior is desired, connect this pin to SGND. Do not leave this pin open circuit.

GND (A7-A12; B6-B8, B11-B12; C7-C8; D6-D8; E1-E8; F1-F12; G1-G12; H3-H9, H11-H12; J5-J12; K5-K6, K11-K12; L4-L6; M4-M6): Power ground pins for input and output returns. See the Layout Checklist/Example section of the Applications Information section. All GND pins are electrically connected to each other, internally.

**UVLO (B4):** Input Undervoltage Lockout Programming Pin. The LTM4641 pulls HYST low to inhibit regulation of its output voltage whenever UVLO is less than 0.5V. The LTM4641 can resume switching action when UVLO exceeds 0.5V. Do not leave this pin open circuit.

If the LTM4641's default UVLO settings are used,  $4.5V_{IN(RISING,\,MAX)}$  and  $4V_{IN(FALLING,\,MAX)}$ , then the UVLO pin should be electrically connected to  $1V_{REF}$  or  $INTV_{CC}$ . Otherwise, see HYST and the Applications Information section for using a resistor-divider network to implement personalized UVLO rising and UVLO falling settings.

**OVLO (B5):** Input Overvoltage Latchoff Programming Pin. LTM4641 pulls HYST low to inhibit regulation of its output voltage when OVLO exceeds 0.5V. If OVLO subsequently falls below 0.5V, the module's output remains latched off; the LTM4641 cannot resume regulation of the output voltage until either the  $\overline{LATCH}$  pin is toggled high or  $V_{INL}$  is power cycled. If input overvoltage latchoff behavior is not desired, electrically short this pin to SGND. Do not leave this pin open circuit.

LINEAR TECHNOLOGY

**CROWBAR (B9):** Crowbar Output Pin. Normally logic low, with moderate pull-down strength to SGND.

When an output overvoltage (OOV) condition is detected, the LTM4641's fast OOV comparator pulls CROWBAR logic high through a series-connected internal diode. If utilizing LTM4641's OOV feature, CROWBAR should connect to the gate of a logic-level N-channel MOSFET configured to crowbar the module's output voltage (MCB, in Figure 1).

Furthermore, the LTM4641 latches off its output when CROWBAR nominally exceeds 1.5V and latches HYST logic low (see HYST).

If not using the OOV protection features of the LTM4641, leave CROWBAR electrically open circuit.

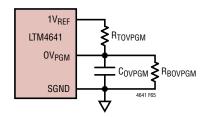

**OV**<sub>PGM</sub> (**B10**): Output Overvoltage Threshold Programming Pin. The voltage on this pin sets the trip threshold for the inverting input pin of LTM4641's fast OOV comparator. When left electrically open circuit, resistors internal to the LTM4641 nominally bias OV<sub>PGM</sub> to 666mV (OV<sub>PTH</sub>)—11% above the nominal V<sub>FB</sub> feedback voltage (600mV) that the control loop strives to present to the noninverting input pin of LTM4641's fast OOV comparator. The aforementioned voltages correspond proportionally to the module's OOV inception threshold and V<sub>OLIT</sub>'s nominal voltage of regulation, respectively. Altering the OV<sub>PGM</sub> voltage provides a means to adjust the OOV threshold; its DC-bias setpoint can be tightened with simple connections to external components (see the Applications Information section). Trace route lengths and widths to this sensitive analog node should be minimized. Minimize stray capacitance to this node unless altering the OOV threshold as described in the Applications Information section and Appendix F.

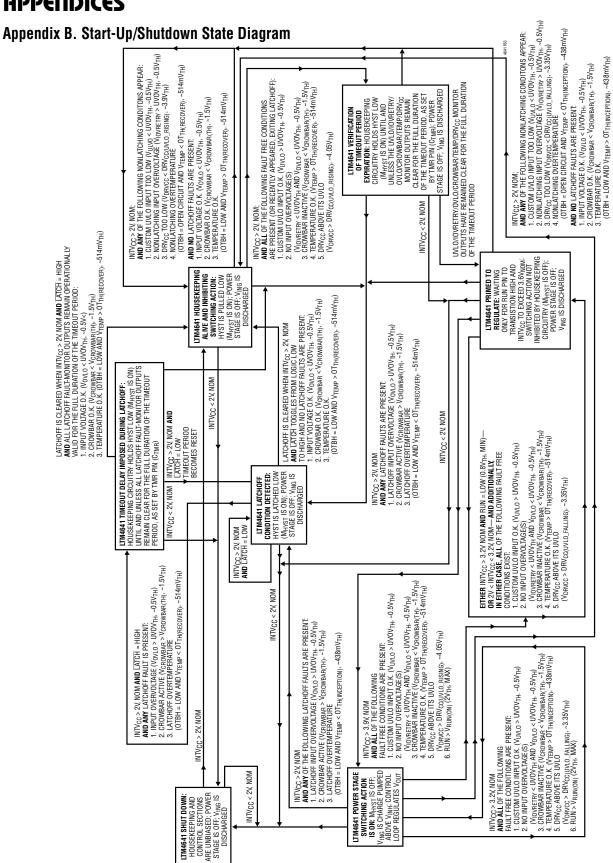

**LATCH** (C5): Latchoff Reset Pin. When a latchoff fault occurs, the LTM4641 turns off its output and latches  $M_{HYST}$  on to indicate a fault condition has occurred (see HYST). To configure the LTM4641 for latched off response to latchoff faults, connect LATCH to SGND. As long as LATCH is logic low, the LTM4641 will not unlatch. Regulation can be resumed by cycling  $V_{INL}$  or by toggling LATCH from logic low to high. It is also permissible to connect LATCH to INTV<sub>CC</sub>; this configures the LTM4641 for autonomous restart with a timeout delay (programmed by  $C_{TMR}$ —see TMR).

If no latchoff faults are present when  $\overline{LATCH}$  transitions from logic low to logic high, the LTM4641 immediately unlatches. If any latchoff fault is present when  $\overline{LATCH}$  is logic high, a timeout delay timing requirement is imposed: the LTM4641 will not unlatch until all latchoff fault-monitoring pins meet operationally valid states for the full duration of the timeout delay. If  $\overline{LATCH}$  becomes logic low before that timeout delay has expired, the LTM4641 remains latched off and the timeout delay is reset. Unlatching the LTM4641 can be reattempted by pulling  $\overline{LATCH}$  logic high at a later time.

The following are latchoff fault conditions:

- CROWBAR activates (see CROWBAR)

- Input latchoff overvoltage fault (see OVLO)

- Latchoff overtemperature fault (when OTBH is logic low; see TEMP and OTBH)

LATCH is a high impedance input and must not be left electrically open circuit. LATCH can be driven by a µController in intelligent systems: a reasonable implementation for unlatching the LTM4641 is to pull LATCH logic high for the maximum anticipated timeout delay time—after which, HYST can be observed to indicate whether the LTM4641 has become unlatched.

$1V_{REF}$  (C6): Buffered 1V Reference Output Pin. Minimize capacitance on this pin, to assure the  $0V_{PGM}$  and TEMP pins are operational in a timely manner at power-up.  $1V_{REF}$  should never be externally loaded except as explained in the Applications Information section.

$V_{OUT}$  (C9-C12; D9-D12; E9-E12): Power Output Pins of the LTM4641 DC/DC Converter Power Stage. All  $V_{OUT}$  pins are electrically connected to each other, internally. Apply output load between these pins and the GND pins. It is recommended to place output decoupling capacitance directly between these pins and the GND pins. Review Table 9. See the Layout Checklist/Example section of the Applications Information section.

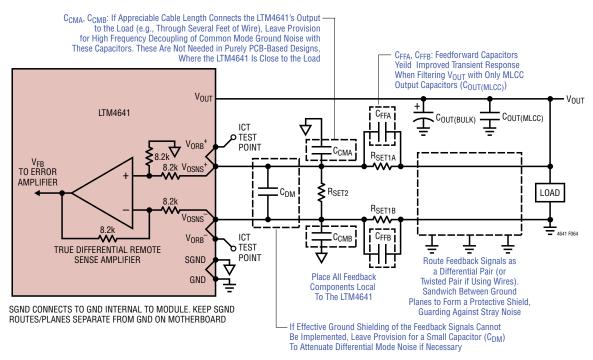

$V_{ORB}^+$  (D1):  $V_{OSNS}^+$  Readback Pin. This pin connects to  $V_{OSNS}^+$  internal to the  $\mu$ Module regulator. It is recommended to route this pin (differentially with  $V_{ORB}^-$ ) to a test point so as to allow the user a way to confirm the integrity

of the remote-sense connections prior to powering up the LTM4641.  $V_{ORB}^+$  can also be connected as a redundant feedback connection to  $V_{OSNS}^+$  on the user's motherboard.

$V_{ORB}^-$  (D2):  $V_{OSNS}^-$  Readback Pin. This pin connects to  $V_{OSNS}^-$  internal to the  $\mu$ Module regulator. It is recommended to route this pin (differentially with  $V_{ORB}^+$ ) to a test point so as to allow the user a way to confirm the integrity of the remote-sense connections prior to powering up the LTM4641.  $V_{ORB}^-$  can also be connected as a redundant feedback connection to  $V_{OSNS}^-$  on the user's motherboard.

**OTBH (D3):** Overtemperature Behavior Programming Pin. When an overtemperature condition is detected (see TEMP), HYST pulls logic low to inhibit switching. If OTBH is connected to SGND, the LTM4641 latches HYST low. If OTBH is left floating, output voltage regulation can resume when the overtemperature event clears.

**TMR (D4):** Timeout Delay Timer and Power-On Reset (POR) Programming Pin. Connect a capacitor ( $C_{TMR}$ ) from TMR to SGND to program the POR and timeout delay time of the LTM4641; 9ms delay time per nanofarad of capacitance. The minimum delay time is ~90µs, when TMR is left electrically open circuit. Even though they use the same capacitor, the power-on reset and timeout delay timers operate independently of each other. Any nonlatching fault or latching fault will reset the respective timer to the full delay time without impacting the other timer.

The timeout delay time programmed by a  $C_{TMR}$  capacitor can be negated by pulling TMR to  $INTV_{CC}$ .

**RUN (D5):** Run (On/Off) Control Pin. A RUN pin voltage below 0.8V will turn off the module. A voltage above 2V will command the module to turn on, if HYST is not asserted low by M<sub>HYST</sub>. The LTM4641 contains a moderate (10k) pull-up resistor from HYST to INTV<sub>CC</sub>, and a pull-up Schottky diode from RUN to HYST (see Figure 1). When RUN is pulled logic low, HYST is pulled logic low via the internal Schottky diode. RUN is compatible with direct-drive (totem-pole output drive) as well as open-collector/open-drain interfaces.

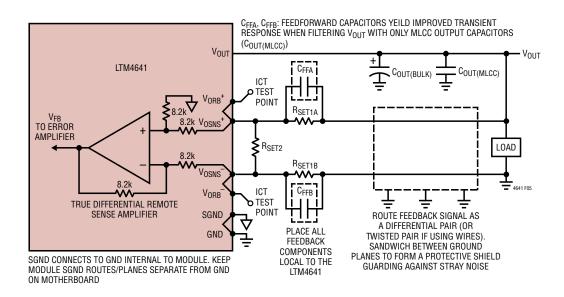

**V**<sub>OSNS</sub><sup>+</sup> (H1): Positive Input to the Remote Sense Differential Amplifier. This pin connects to the positive side of the output voltage remote sense point (V<sub>OUT</sub> potential) via a resistor (R<sub>SET1A</sub>). When regulating the output voltage,

the LTM4641 control loop drives the differential voltage between  $V_{OSNS}^+$  and  $V_{OSNS}^-$  to the lesser of TRACK/SS and 0.6V.  $V_{OSNS}^+$  is connected to  $V_{ORB}^+$  internal to the module (see  $V_{ORB}^+$ ). A resistor may be needed from  $V_{OSNS}^+$  to  $V_{OSNS}^-$  for some output voltage settings. (See the Applications Information section: Setting the Output Voltage.) Minimize stray capacitance to this pin to protect the integrity of the output voltage feedback signal.

$V_{OSNS}^-$  (H2): Negative Input to the Remote Sense Differential Amplifier. This pin connects to the negative side of the output voltage remote sense point (GND potential) via a resistor ( $R_{SET1B}$ ). When switching action is on, the LTM4641 control loop drives the differential voltage between  $V_{OSNS}^+$  and  $V_{OSNS}^-$  to the lesser of TRACK/SS and 0.6V.  $V_{OSNS}^-$  is connected to  $V_{ORB}^-$  internal to the module (see  $V_{ORB}^-$ ). A resistor may be needed from  $V_{OSNS}^+$  to  $V_{OSNS}^-$  for some output voltage settings. (See the Applications Information section.) Minimize stray capacitance to this pin to protect the integrity of the output voltage feedback signal.

**SW** (H10): Switching Node of the Power Stage. Mainly used for testing purposes, however, one may optionally connect a snubber (series-configured capacitor  $C_{SW}$  and resistor  $R_{SW}$ ) from SW to GND to reduce radiated EMI—in exchange for a minor compromise to power conversion efficiency. (See the Applications Information section.)

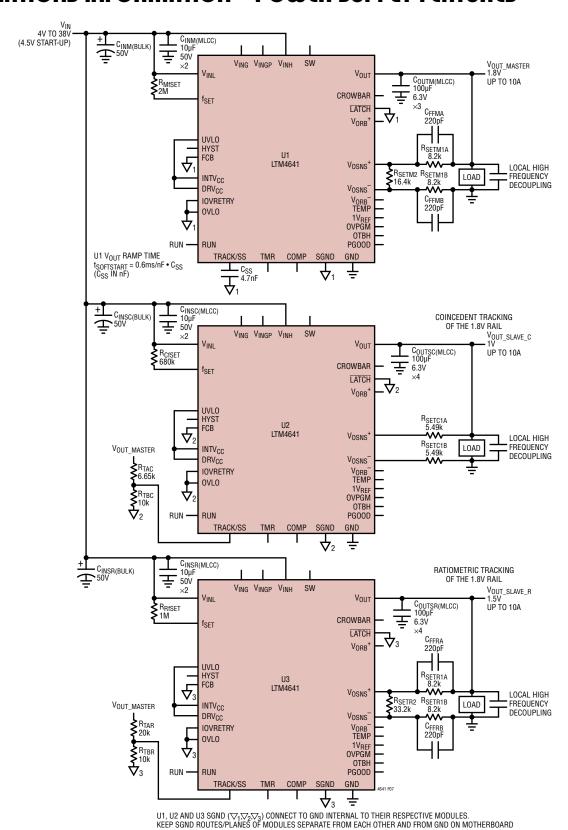

**COMP (J1):** Current Control Threshold and Error Amplifier Compensation Point. The current comparator threshold of LTM4641's valley current mode control loop—and correspondingly, the commanded trough of the power inductor current—increases as this control voltage increases. It can be useful to make COMP available for observation on a PCB via or test pad with an oscilloscope probe. However, stray capacitance and trace lengths to this sensitive analog node should be minimized.