64M Bits Serial Pseudo-SRAM with SPI and QPI

#### Rev. 0.7 Preliminary

#### **1 TABLE OF CONTENTS**

| 1 TABLE OF CONTENTS                                                                                                                          | 0                 |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 2 REVISION HISTORY                                                                                                                           | 1                 |

| 3 FEATURES                                                                                                                                   | 2                 |

| 4 SPECIFICATIONS                                                                                                                             | 2                 |

| 5 PIN CONFIGURATION                                                                                                                          | 2                 |

| 6 PACKAGE OUTLINE DIMENSION                                                                                                                  | 3/4               |

| 7 ORDERING INFORMATION                                                                                                                       | 5                 |

| 8 PIN DESCRIPTION                                                                                                                            | 5                 |

| 9 POWER-UP INITIALIZATION                                                                                                                    | 6                 |

| 10 INTERFACE DESCRIPTION                                                                                                                     | 7                 |

| 10.1 Address Space<br>10.2 Page Size<br>10.3 Drive Strength                                                                                  | 7                 |

| 10.3 Drive Strength                                                                                                                          |                   |

| 10.5 Truth Table                                                                                                                             |                   |

| 10.6    Command Termination      11    WRAP BOUNDARY TOGGLE OPERATION                                                                        |                   |

| 12 SPI MODE OPERATIONS                                                                                                                       |                   |

| 12.1    SPI Read Operations      12.2    SPI Write Operations      12.3    SPI Quad Mode Enable Operation      12.4    SPI Read ID Operation | 11/12<br>12<br>13 |

| 13 QPI MODE OPERATIONS                                                                                                                       |                   |

| 13.1 QPI Read Operations<br>13.2 QPI Write Operation(s)                                                                                      |                   |

| <ul><li>13.2 QPI Write Operation(s)</li><li>13.3 QPI Quad Mode Exit Operation</li></ul>                                                      | 4 5               |

|                                                                                                                                              | 15                |

| 13.3 QPI Quad Mode Exit Operation                                                                                                            | 15<br>16          |

| 13.3 QPI Quad Mode Exit Operation      14 RESET OPERATION                                                                                    | 15<br>16<br>17    |

*Lyontek Inc.* reserves the rights to change the specifications and products without notice. 2F, No. 17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan. TEL: 886-3-6668838 FAX: 886-3-6668836

64M Bits Serial Pseudo-SRAM with SPI and QPI

#### 2 REVISION HISTORY

| <u>Revision</u> | Description                                                                                                                                                                                                                                                                               | Issue Date  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Rev. 0.1        | Initial Issue                                                                                                                                                                                                                                                                             | May.06.2016 |

| Rev. 0.2        | Revised typos                                                                                                                                                                                                                                                                             | May.19.2016 |

| Rev. 0.3        | Revised the address bit length from 32 bits to 24 bits                                                                                                                                                                                                                                    | Oct.13.2016 |

| Rev. 0.4        | Added <b>Command Termination</b> in page 7                                                                                                                                                                                                                                                | May.03.2017 |

|                 | Revised <b>Truth Table</b> in page 7                                                                                                                                                                                                                                                      |             |

| Rev. 0.5        | Reworded linear burst, renamed page toggle CMDs.                                                                                                                                                                                                                                          | Jul.20.2017 |

|                 | Updated timing parameters for 144MHz.                                                                                                                                                                                                                                                     |             |

|                 | Removed QPI Read 'h0B support.                                                                                                                                                                                                                                                            |             |

|                 | Clarified termination section.                                                                                                                                                                                                                                                            |             |

|                 | Added <i>Pin Capacitance</i> tables.                                                                                                                                                                                                                                                      |             |

|                 | Extend to 20ns & to 50ns.                                                                                                                                                                                                                                                                 |             |

| Rev. 0.6        | Added <b>Truth Table</b> note: 2. Linear burst is prohibited.                                                                                                                                                                                                                             | Aug.04.2017 |

|                 | Added Table 3: Burst Type / Length in page 10                                                                                                                                                                                                                                             |             |

| Rev. 0.7        | Revised temperature range to -40 ~ 85°C                                                                                                                                                                                                                                                   | Nov.21.2017 |

|                 |                                                                                                                                                                                                                                                                                           |             |

|                 |                                                                                                                                                                                                                                                                                           |             |

|                 | Removed QPI Read 'h0B support.<br>Clarified termination section.<br>Added <i>Pin Capacitance</i> tables.<br>Extend t <sub>CHD</sub> to 20ns & t <sub>CPH</sub> to 50ns.<br>Added <i>Truth Table</i> note: 2. Linear burst is prohibited.<br>Added Table 3: Burst Type / Length in page 10 | C C         |

# **3 FEATURES**

- 50Ω Output Drive Strength LVCMOS.

- Linear Burst (continuous) or 32 byte wrapped burst via toggle command.

- Linear Burst is supported up to 84MHz and can cross page boundary as long as t<sub>CEM</sub> is met.

- Software reset.

- Green package available

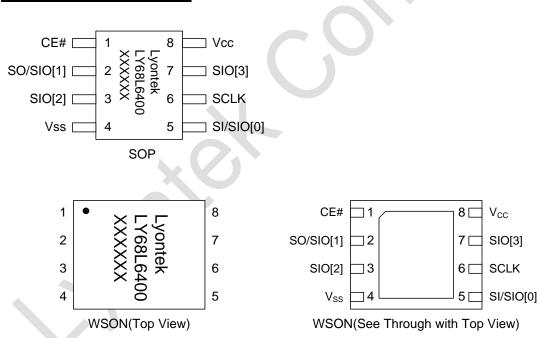

- Package : 8-pin 150mil SOP 8-pin 5mm x 6mm WSON

# **4** SPECIFICATIONS

- Single Supply Voltage:

- Vcc=2.7 to 3.6V

- Interface: SPI/QPI with SDR mode

- Performance: Clock rate up to 144MHz (non-page boundary crossing) 84MHz (page boundary crossing)

- Organization: 64Mb, 8M x 8bits

- Addressable bit range: A[22:0]

- Page size: 1024 bytes

- Refresh: Self-managed

- Operating temperature range

TC = -40°C to +85°C

- IC = -40 C to +85 C

Maximum Standby Current:

- 400µA @ 85°C

*Lyontek Inc.* reserves the rights to change the specifications and products without notice. 2F, No. 17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan. TEL: 886-3-6668838 FAX: 886-3-6668836

# **5 PIN CONFIGURATION**

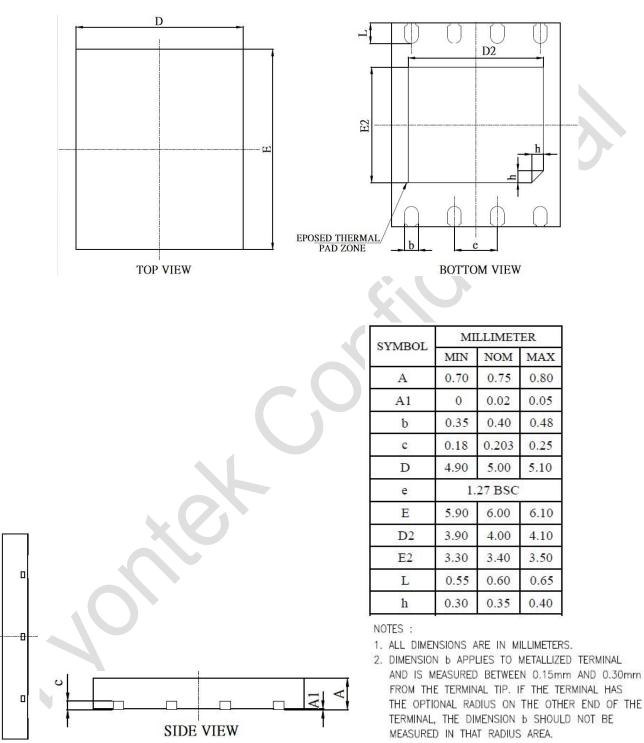

#### **6 PACKAGE OUTLINE DIMENSION**

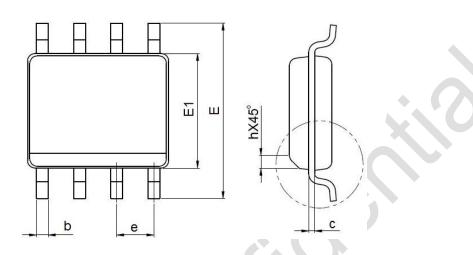

8-pin 150mil SOP Package Outline Dimension

VARIATIONS (ALL DIMENSIONS SHOWN IN MM)

| SYMBOLS- | STAN    | IDARD |

|----------|---------|-------|

| SIMBULS  | MIN.    | MAX.  |

| А        | <u></u> | 1.75  |

| A1       | 0.10    | 0.25  |

| A2       | 1.25    |       |

| Ь        | 0.31    | 0.51  |

| с        | 0.10    | 0.25  |

| D        | 4.90    | BSC   |

| E        | 6.00    | ) BSC |

| E1       | 3.90    | BSC   |

| е        | 1.27    | BSC   |

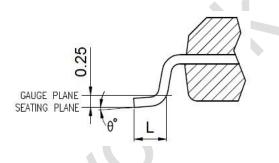

| L        | 0.40    | 1.27  |

| h        | 0.25    | 0.50  |

| θ°       | 0       | 8     |

NOTES:

- 1.JEDEC OUTLINE : MS-012 AA REV.F (STANDARD) MS-012 BA REV.F (THERMAL)

- 2.DIMENSIONS "D" DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH, PROTRUSIONS AND GATE BURRS SHALL NOT EXCEED 0.15mm. PER SIDE.

- 3.DIMENSIONS "E1" DOES NOT INCLUDE INTER-LEAD FLASH, OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25mm PER SIDE.

*Lyontek Inc.* reserves the rights to change the specifications and products without notice. 2F, No. 17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan. TEL: 886-3-6668838 FAX: 886-3-6668836

# 64M Bits Serial Pseudo-SRAM with SPI and QPI

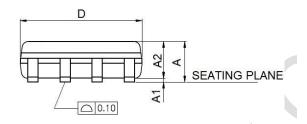

#### 8-pin 5mm x 6mm WSON Package Outline Dimension

64M Bits Serial Pseudo-SRAM with SPI and QPI

# 7 ORDERING INFORMATION

Table 1: Ordering Information

| Package Type      | Maximum<br>Clock Rate(MHz) | Temperature<br>Range(℃) | Packing<br>Type | Lyontek Item No. |

|-------------------|----------------------------|-------------------------|-----------------|------------------|

| 8-pin (150mil)    | 144                        | -40°C~85°C              | Tube            | LY68L6400SLI     |

| SOP               |                            |                         | Tape Reel       | LY68L6400SLIT    |

| 8-pin (5mm x 6mm) | 144                        |                         | Tray            | LY68L6400BLI     |

| WSON              | 144                        | <b>-40°C~85°</b> C      | Tape Reel       | LY68L6400BLIT    |

# 8 PIN DESCRIPTION

Table 2: Signals Table

| SYMBOL    | TYPE   | SPI Mode Function               | QPI Mode Function                                              | COMMENTS |  |  |  |

|-----------|--------|---------------------------------|----------------------------------------------------------------|----------|--|--|--|

| Vcc       | Power  | Core su                         | upply 3V                                                       |          |  |  |  |

| Vss       | Ground | Core supr                       | Core supply ground                                             |          |  |  |  |

| CE#       | Input  | Chip select, active low. When ( | Chip select, active low. When CE#=1, chip is in standby state. |          |  |  |  |

| CLK       | Input  | Clock                           | Clock Signal                                                   |          |  |  |  |

| SI/SIO[0] | I/O    | Serial Input                    | [/O[0]                                                         |          |  |  |  |

| SO/SIO[1] | I/O    | Serial Output                   | I/O[1]                                                         |          |  |  |  |

| SIO[2]    | I/O    | -                               | I/O[2]                                                         |          |  |  |  |

| SIO[3]    | I/O    | -                               | I/O[3]                                                         |          |  |  |  |

.

64M Bits Serial Pseudo-SRAM with SPI and QPI

Rev. 0.7 Preliminary

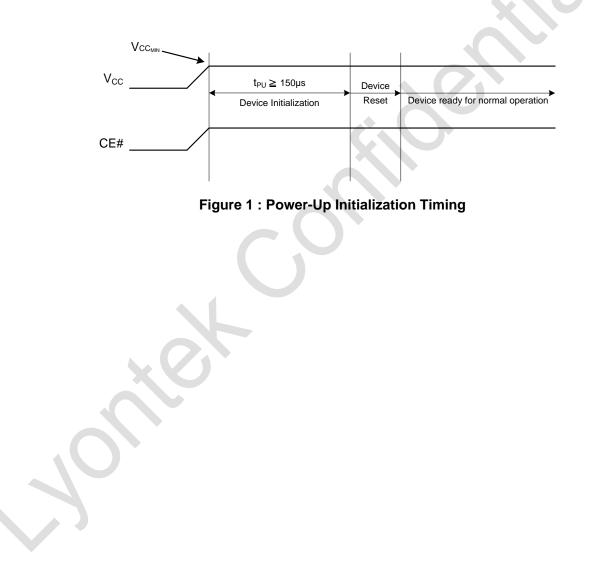

#### 9 POWER-UP INITIALIZATION

SPI/QPI products include an on-chip voltage sensor used to start the self-initialization process. When  $V_{CC}$  reaches a stable level at or above minimum  $V_{CC}$ , the device will require 150µs and user-issued RESET Operation (see section 14) to complete its self-initialization process. From the beginning of power ramp to the end of the 150µs period, CLK should remain LOW, CE# should remain HIGH (track  $V_{CC}$  within 200mV) and SI/SO/SIO[3:0] should remain LOW.

After the 150µs period the device is ready for normal operation.

64M Bits Serial Pseudo-SRAM with SPI and QPI

#### **10 INTERFACE DESCRIPTION**

#### 10.1 Address Space

SPI/QPI PSRAM device is byte-addressable. 64M device is addressed with A[22:0].

#### 10.2 Page Size

Page size is 1K (CA[9:0]). Default burst setting is Linear Bursting that crosses page boundary in a continuous manner. Note however that burst operations which cross page boundary have a lower max input clock frequency of 84MHz. Optionally the device can also be set to wrap 32 (CA[4:0]) via the Wrap Boundary Toggle command and is not allowed to cross page boundary in this configuration.

#### 10.3 Drive Strength

The device powers up in  $50\Omega$ .

#### 10.4 Power-on Status

The device powers up in SPI Mode. It is required to have CE# high before beginning any operations.

LY68L6400 64M Bits Serial Pseudo-SRAM with SPI and QPI

Rev. 0.7 Preliminary

## 10.5 Truth Table

The device recognizes the following commands specified by the various input methods.

|                  |      | SPI Mode (QE=0) |      |               |     |                   | QPI | Mode (       | QE=1)         |     |                   |

|------------------|------|-----------------|------|---------------|-----|-------------------|-----|--------------|---------------|-----|-------------------|

| COMMAND          | CODE | CMD             | Addr | Wait<br>Cycle | DIO | MAX.<br>Freq.     | CMD | Addr         | Wait<br>Cycle | DIO | MAX.<br>Freq.     |

| Read             | 'h03 | S               | S    | 0             | S   | 33                |     |              | N/A           |     |                   |

| Fast Read        | ʻh0B | S               | S    | 8             | S   | 144               |     |              | N/A           |     |                   |

| Fast Read Quad   | 'hEB | S               | Q    | 6             | Q   | 144               | Q   | Q            | 6             | Q   | 144* <sup>1</sup> |

| Write            | 'h02 | S               | S    | 0             | S   | 144* <sup>2</sup> | Q   | Q            | 0             | Q   | 144* <sup>1</sup> |

| Quad Write       | ʻh38 | S               | Q    | 0             | Q   | 144               |     | Same as 'h02 |               |     |                   |

| Enter Quad Mode  | ʻh35 | S               | -    | -             | -   | 144               |     |              | N/A           |     |                   |

| Exit Quad Mode   | ʻhF5 |                 |      | N/A           |     |                   | Q   | -            | -             | -   | 144               |

| Reset Enable     | 'h66 | S               | -    | -             | -   | 144               | Q   | -            | -             | -   | 144               |

| Reset            | 'h99 | S               | -    | -             | -   | 144               | Q   |              | -             | -   | 144               |

| Set Burst Length | ʻhC0 | S               | -    | -             | -   | 144               | Q   | Γ-           | -             | -   | 144               |

| Read ID          | ʻh9F | S               | S    | 0             | S   | 144               |     |              | N/A           |     |                   |

Remarks: S = Serial I/O, Q = Quad I/O

Note: 1. 144MHz max without crossing page boundary, and 84MHz max when burst commands cross page boundary. 2. Linear burst is prohibited.

64M Bits Serial Pseudo-SRAM with SPI and QPI

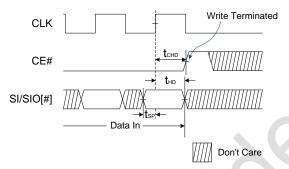

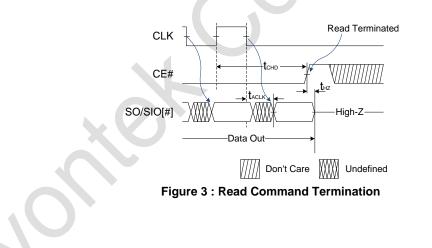

#### 10.6 Command Termination

All Reads & Writes must be completed by raising CE# high immediately afterwards in order to terminate the active command and set the device into standby. Not doing so will block internal refresh operations and cause memory failure.

For a memory controller to correctly latch the last piece of data prior to read termination, it is recommended to provide a longer CE# hold time ( $t_{CHD} > t_{ACLK} + t_{CLK}$ ) for a sufficient data window.

64M Bits Serial Pseudo-SRAM with SPI and QPI

Rev. 0.7 Preliminary

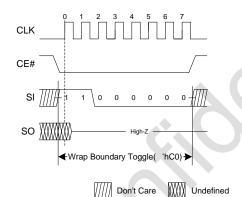

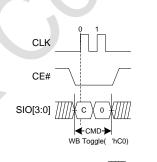

#### 11 WRAP BOUNDARY TOGGLE OPERATION

The Wrap Boundary Toggle Operation switches the device's wrapped boundary between Linear Burst which crosses the 1K page boundary (CA[9:0]) and wrap 32 (CA[4:0]) bytes. Default setting is Linear Burst.

Linear Burst allows the device to burst through page boundary. Page boundary crossing is invisible to the memory controller and limited to lower max CLK frequency of 84MHz. Table 3 shows an example of the sequence of bytes.

Figure 4 : SPI Wrap Boundary Toggle 'hC0

///// Don't Care

Figure 5 : QPI Wrap Boundary Toggle 'hC0

Table 3: Burst Type / Length

| Burst Type / Length | Starting Address | Byte Sequence                |

|---------------------|------------------|------------------------------|

| Linear Burst        | 4                | [4,5,6,1023,1024,1025,1026,] |

| Wrap 32             | 4                | [4,5,6,31,0,1,2,]            |

*Lyontek Inc.* reserves the rights to change the specifications and products without notice. 2F, No. 17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan. TEL: 886-3-6668838 FAX: 886-3-6668836

64M Bits Serial Pseudo-SRAM with SPI and QPI

#### **12 SPI MODE OPERATIONS**

The device powers up into SPI mode by default but can also be switched into QPI mode.

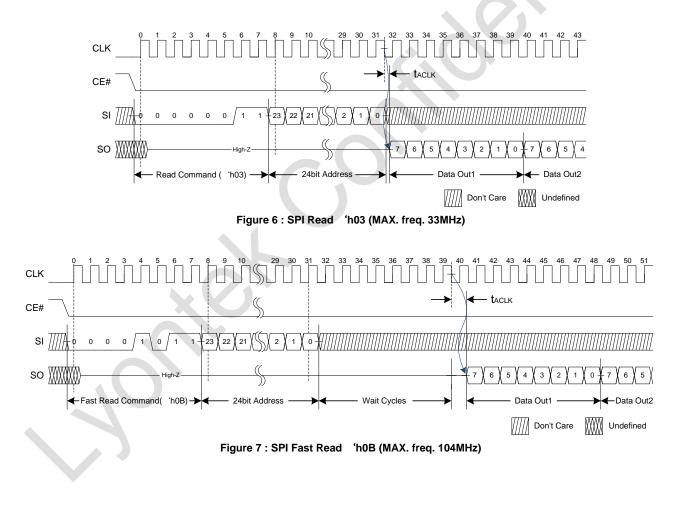

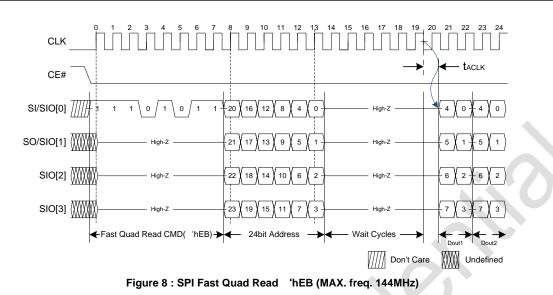

#### 12.1 SPI Read Operations

For all reads, data will be available tACLK after the falling edge of CLK.

SPI Reads can be done in three ways:

- 1. 'h03: Serial CMD, Serial I/O, slow frequency, with linear or burst wrap of 32 byte configurability.

- 2. 'h0B: Serial CMD, Serial I/O, fast frequency, with burst wrap of 32/1K byte configurability.

- 3. 'hEB: Serial CMD, Quad I/O, fast frequency, with burst wrap of 32/1K byte configurability.

LY68L6400 64M Bits Serial Pseudo-SRAM with SPI and QPI

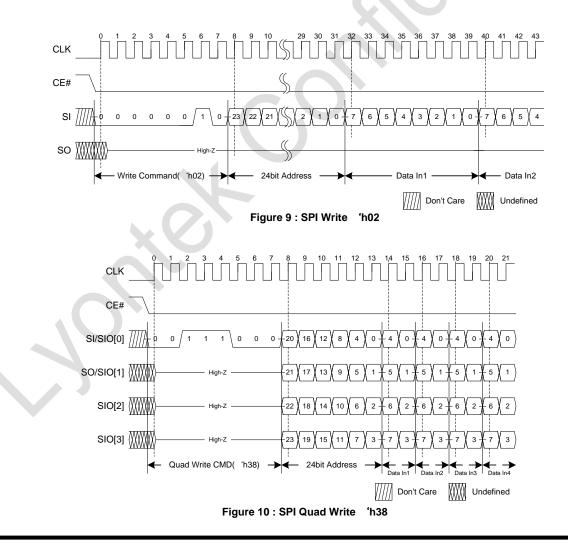

# 12.2 SPI Write Operations

**Lyontek Inc.** reserves the rights to change the specifications and products without notice. 2F, No. 17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan. TEL: 886-3-6668838 FAX: 886-3-6668836

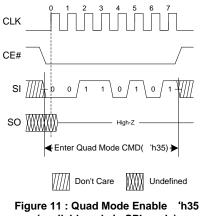

# 12.3 SPI Quad Mode Enable Operation

This command switches the device into quad I/O mode.

(available only in SPI mode)

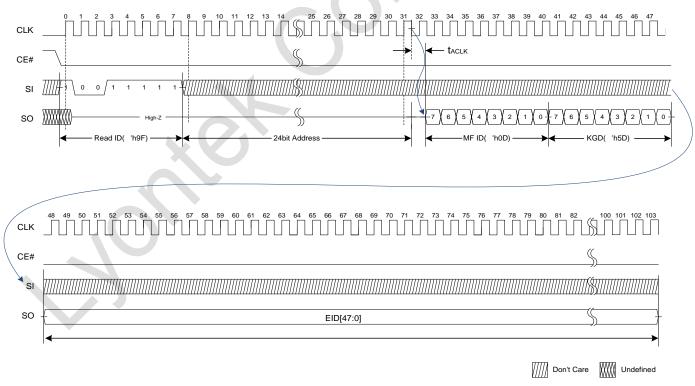

# 12.4 SPI Read ID Operation

This command is similar to Fast Read, but without the wait cycles and the device outputs EID value instead of data.

**Lyontek Inc.** reserves the rights to change the specifications and products without notice. 2F, No. 17, Industry E. Rd. II, Science-Based Industrial Park, Hsinchu 300, Taiwan. TEL: 886-3-6668838 FAX: 886-3-6668836

64M Bits Serial Pseudo-SRAM with SPI and QPI

Table 4: Known Good Die (KGD)

| KGD[7:0]    | Known Good Die |

|-------------|----------------|

| 'b0101_0101 | FAIL           |

| 'b0101_1101 | PASS           |

\*Note: Default is FAIL die, and only mark PASS after all tests passed.

# **13 QPI MODE OPERATIONS**

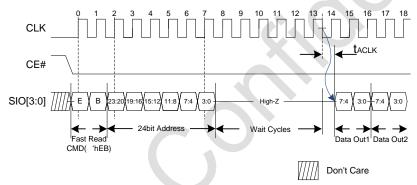

### 13.1 QPI Read Operations

For all reads, data will be available t<sub>ACLK</sub> after the falling edge of CLK.

Figure 13 : QPI Fast Read 'hEB (MAX. freq. 144MHz)

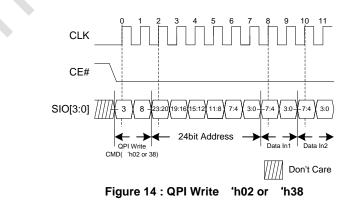

# 13.2 QPI Write Operation(s)

QPI write command can be input as 'h02 or 'h38.

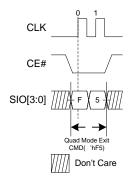

# 13.3 QPI Quad Mode Exit Operation

This command will switch the device back into serial I/O mode.

Figure 15 : Quad Mode Exit 'hF5 (only available in QPI mode)

64M Bits Serial Pseudo-SRAM with SPI and QPI

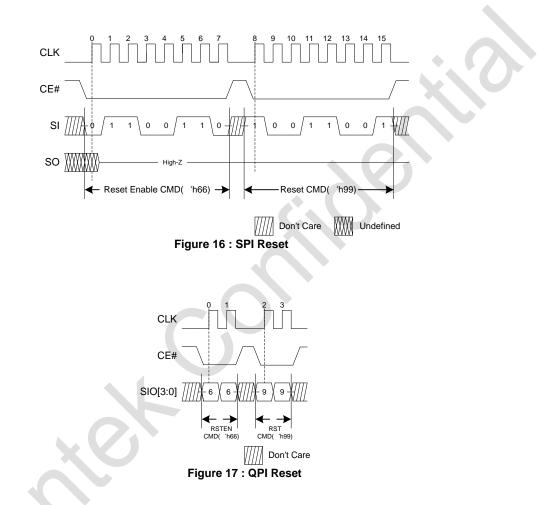

#### **14 RESET OPERATION**

The Reset operation is used as a system (software) reset that puts the device in SPI standby mode which is also the default mode after power-up. This operation consists of two commands: Reset-Enable (RSTEN) and Reset (RST).

Reset command has to immediately follow the Reset-Enable command in order for the reset operation to take effect. Any command other than the Reset command after the Reset-Enable command will cause the device to exit Reset-Enable state and abandon reset operation.

64M Bits Serial Pseudo-SRAM with SPI and QPI

#### Rev. 0.7 Preliminary

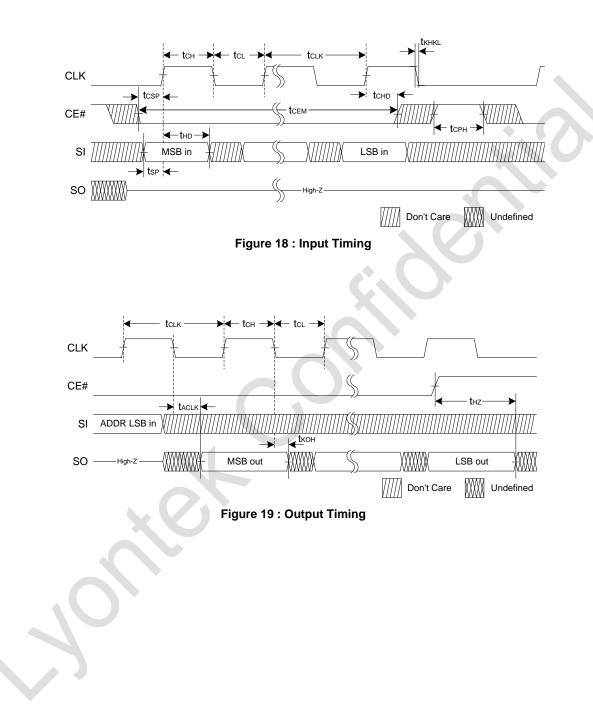

### 15 INPUT / OUTPUT TIMING

# 16 ELECTRICAL SPECIFICATIONS

# 16.1 Absolute Maximum Ratings\*

Table 5: Absolute Maximum Ratings\*

| PARAMETER                                                             | SYMBOL          | RATING                       | UNIT | NOTES |

|-----------------------------------------------------------------------|-----------------|------------------------------|------|-------|

| Voltage to any pad except $V_{\text{CC}}$ relative to $V_{\text{SS}}$ | VT              | -0.3 to V <sub>CC</sub> +0.3 | V    |       |

| Voltage on V <sub>CC</sub> supply relative to V <sub>SS</sub>         | V <sub>CC</sub> | -0.2 to +4.2                 | V    |       |

| Storage Temperature                                                   | Tstg            | -55 to +150                  | °C   | 1     |

Note: 1. Storage temperature refers to the case surface temperature on the center/top side of the PSRAM.

\* Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# 16.2 Pin Capacitance

Table 6: Package Pin Capacitance

| PARAMETER              | SYMBOL | MIN. | MAX. | UNIT | NOTES                |

|------------------------|--------|------|------|------|----------------------|

| Input Pin Capacitance  | CIN    | -    | 6    | pF   | V <sub>IN</sub> =0V  |

| Output Pin Capacitance | Cout   | -    | 8    | pF   | V <sub>OUT</sub> =0V |

Note: 1. Spec'd at 25°C.

# 16.3 Operating Conditions

**Table 7: Operating Characteristics**

| PARAMETER             | MIN. | MAX. | UNIT |

|-----------------------|------|------|------|

| Operating Temperature | -40  | 85   | °C   |

# 64M Bits Serial Pseudo-SRAM with SPI and QPI

## 16.4 DC Electrical Characteristics

**Table 8: DC Characteristics**

| SYMBOL          | PARAMETER                                     | MIN.                 | MAX.                 | UNIT | NOTES |

|-----------------|-----------------------------------------------|----------------------|----------------------|------|-------|

| Vcc             | Supply Voltage                                | 2.7                  | 3.6                  | V    |       |

| VIH             | Input high voltage                            | V <sub>CC</sub> -0.4 | V <sub>CC</sub> +0.2 | V    |       |

| VIL             | Input low voltage                             | -0.2                 | 0.4                  | V    |       |

| Vон             | Output high voltage (I <sub>OH</sub> =-0.2mA) | 0.8 Vcc              | -                    | V    |       |

| Vol             | Output low voltage (I <sub>OL</sub> =+0.2mA)  | -                    | 0.2 V <sub>CC</sub>  | V    |       |

| Iu              | Input leakage current                         | -                    | 1                    | μA   |       |

| ILO             | Output leakage current                        | -                    | 1                    | μA   |       |

| lcc             | Read/Write                                    | -                    | 40                   | mA   |       |

| I <sub>SB</sub> | Standby current                               | -                    | 400                  | μA   | 1     |

Note: 1. Standby current is measured when CLK is in DC low state.

### 16.5 AC Electrical Characteristics

#### Table 9: READ/WRITE Timing

| SYMBOL            | PARAMETER                                    | MIN. | MAX. | UNIT                   | NOTES      |

|-------------------|----------------------------------------------|------|------|------------------------|------------|

| t <sub>CLK</sub>  | CLK period - SPI Read('h03)                  | 30.3 | -    | ns                     | 33MHz      |

|                   | CLK period – all other operations            | 7    | -    |                        | 144MHz*1,2 |

| $t_{CH} / t_{CL}$ | Clock high/low width                         | 0.45 | 0.55 | t <sub>CLK</sub> (min) |            |

| t <sub>KHKL</sub> | CLK rise or fall time                        | -    | 1.5  | ns                     |            |

| tсрн              | CE# HIGH between subsequent burst operations | 50   | -    | ns                     |            |

| tсем              | CE# low pulse width                          | -    | 8    | μs                     |            |

| t <sub>CSP</sub>  | CE# setup time to CLK rising edge            | 2.5  | -    | ns                     |            |

| tснD              | CE# hold time from CLK rising edge           | 20   | -    | ns                     |            |

| tsp               | Setup time to active CLK edge                | 2    | -    | ns                     |            |

| t <sub>HD</sub>   | Hold time from active CLK edge               | 2    | -    | ns                     |            |

| t <sub>HZ</sub>   | Chip disable to DQ output high-Z             | -    | 6    | ns                     |            |

| <b>t</b> ACLK     | CLK to output delay                          | 2    | 6    | ns                     |            |

| tкон              | Data hold time from clock falling edge       | 1.5  | -    | ns                     |            |

Note: 1. Only Linear Burst allows page boundary crossing. Frequency limits are therefore 144MHz MAX. without crossing page boundary, and 84MHz MAX. when burst commands cross page boundary.

2. For operating frequencies > 84MHz, refer to JEDEC JESD84-B50 for data sampling training.

64M Bits Serial Pseudo-SRAM with SPI and QPI

THIS PAGE IS LEFT BLANK INTENTIONALLY.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for SRAM category:

Click to view products by Lyontek manufacturer:

Other Similar products are found below :

CY6116A-35DMB CY7C1049GN-10VXI CY7C1461KV33-133AXI GS8161Z36DD-200I GS88237CB-200I RMLV0408EGSB-4S2#AA0 IS64WV3216BLL-15CTLA3 IS66WVE4M16ECLL-70BLI PCF8570P K6F2008V2E-LF70000 K6T4008C1B-GB70 CY7C1353S-100AXC AS6C8016-55BIN AS7C164A-15PCN 515712X IS62WV51216EBLL-45BLI IS63WV1288DBLL-10HLI IS66WVE2M16ECLL-70BLI 70V639S10BCG IS66WVE4M16EALL-70BLI IS61WV102416DBLL-10TLI CY7C1381KV33-100AXC CY7C1460KV25-200BZI CY7C1373KV33-100AXC CY7C1381KVE33-133AXI CY7C4121KV13-600FCXC GS882Z18CD-150I IS61WV102416DBLL-10BLI IS66WVC2M16ECLL-7010BLI 7140LA35PDG CY7C1380KV33-250AXC AS6C8016-55BINTR CY7C1370KV33-250AXC CY7C1370KVE33-167AXI AS7C34096B-10TIN AS6C8016-55TIN IS62WV25616EALL-55TLI GS8128418B-167IV CY7C1460KV25-200BZXI CY7C1460KV25-167BZXI CY7C1315KV18-333BZXC CY7C1370KV25-200AXC 71421LA55JI8 CY62158G30-45ZSXI CY62157G30-45ZSXI RMLV3216AGSD-552#AA0 CY62187G30-55BAXI CY62157G30-45ZXI 71V016SA20YGI 71V124SA15YGI8