Octal 10/100/1000/2.5G/5GBASE-T Ethernet Transceiver

**Datasheet - Public**

For CUSTOMER Use Only

Doc. No. MV-S111723-U0 Rev. B

July 1, 2021

Document Classification: Public

THIS DOCUMENT AND THE INFORMATION FURNISHED IN THIS DOCUMENT ARE PROVIDED "AS IS" WITHOUT ANY WARRANTY. MARVELL AND ITS AFFILIATES EXPRESSLY DISCLAIM AND MAKE NO WARRANTIES OR GUARANTEES, WHETHER EXPRESS, ORAL, IMPLIED, STATUTORY, ARISING BY OPERATION OF LAW, OR AS A RESULT OF USAGE OF TRADE, COURSE OF DEALING, OR COURSE OF PERFORMANCE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NON-INFRINGEMENT.

This document, including any software or firmware referenced in this document, is owned by Marvell or Marvell's licensors, and is protected by intellectual property laws. No license, express or implied, to any Marvell intellectual property rights is granted by this document. The information furnished in this document is provided for reference purposes only for use with Marvell products. It is the user's own responsibility to design or build products with this information. Marvell products are not authorized for use as critical components in medical devices, military systems, life or critical support devices, or related systems. Marvell is not liable, in whole or in part, and the user will indemnify and hold Marvell harmless for any claim, damage, or other liability related to any such use of Marvell products.

Marvell assumes no responsibility for the consequences of use of such information or for any infringement of patents or other rights of third parties that may result from its use. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning the Marvell products disclosed herein. Marvell and the Marvell logo are registered trademarks of Marvell or its affiliates. Please visit www.marvell.com for a complete list of Marvell trademarks and guidelines for use of such trademarks. Other names and brands may be claimed as the property of others.

#### Copyright

Copyright © 2021. Marvell and/or its affiliates. All rights reserved.

### **Preface**

### **About this Document**

This document provides a feature list and overview, pin description, functional description, mechanical drawings, electrical specifications, and order information for the 88E2180 and 88E2110.

#### **Related Document**

88E2181/88E2180/88E2111/88E2110 Register Description

This document (MV-S111371-00) provides a description of the registers for the 88E2181, 88E2180, 88E2111, and 88E2110 devices.

# Alaska M 88E2180/88E2110 Octal/Single 10/100/1000/2.5GBASE-T Ethernet Transceiver

#### PRODUCT OVERVIEW

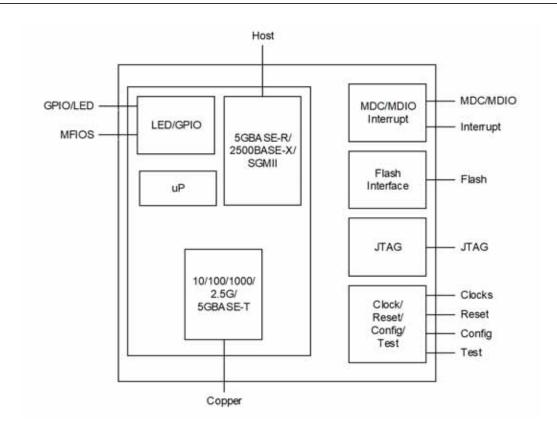

The Marvell® Alaska® M 88E2180 and 88E2110 are fully IEEE 802.3bz-compliant 1-port (88E2110) or 8-port (88E2180) physical layer (PHY) devices. The devices support a wide variety of host-side interfaces including 5GBASE-R, 2500BASE-X, and SGMII to support full backward compatibility with lower speed legacy Ethernet rates including 1 Gbps, 100 Mbps, and 10 Mbps.

The flexibility of the devices enable extremely low power across all structured wiring cable lengths, enabling dense 5 Gbps applications. The devices support Category 5e-, Category 6- (screened or unscreened), Category 6A- (Augmented), and Category 7-type cables for distances up to 100 meters.

#### **FEATURES**

- 1-port (88E2110 only), 5-speed PHY operating at 10M, 100M, 1G, 2.5G, or 5G data rates on UTP copper lines

- 8-port (88E2180 only), 5-speed PHY operating at 10M, 100M, 1G, 2.5G, or 5G data rates on UTP copper lines

- Compliant with both NBASE-T and IEEE 802.3bz specifications for 2.5G and 5G modes

- 5GBASE-R, 2500BASE-X (88E2180 and 88E2110 only), and SGMII system-side interfaces

- · EEE for all supported data rates

- Allows dense multi-port 2.5G/5G applications

- BER less than 1E-15 (88E2180), better than 1E-15 (88E2110)

- 100m reach on Category 5e for

- Clause 22 and 45 MDC/MDIO management interface

- TWSI support (88E2110 only)

- Serial LED (88E2180 only)

- 19 mm x 19 mm HFCBGA package (88E2180)

- Small 7 mm x 11 mm FC-TFBGA package (88E2110)

- Available in commercial and industrial grades

Clocks

Reset

Config

Test

Clock/

Reset/ Config/

Test

Host MDC/MDIO GPIO/LED MDC/MDIO LED/GPIO/ Interrupt Interrupt Serial LED MFIOS 5GBASE-R/ 2500BASE-X/ SGMII Flash Flash Interface uР JTAG **JTAG**

10/100/1000/ 2.5G/ 5GBASE-T

Copper

Page 5

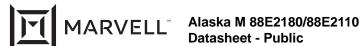

Figure 1: 88E2180 Top-level Block Diagram

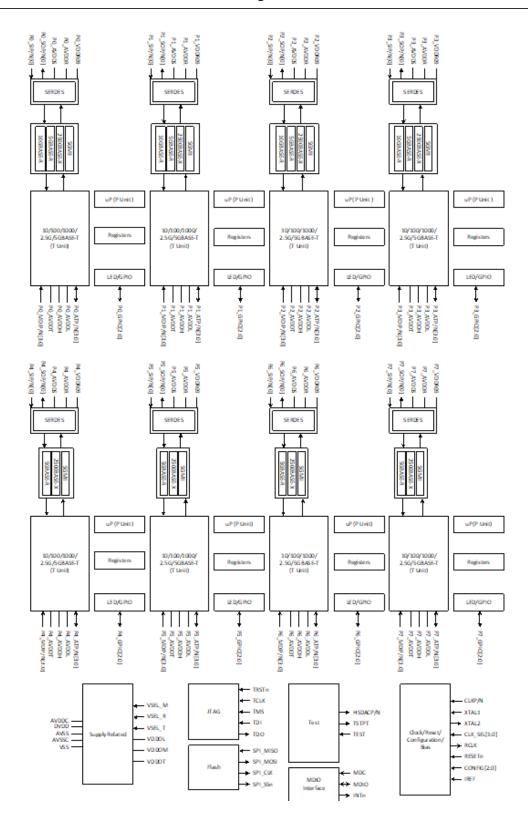

Figure 2: 88E2110 Top-level Block Diagram

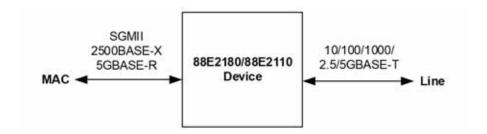

### **CONFIGURATION OPTIONS**

Figure 3: Device Application — Host Interface Speed Matched to Line Speed

### **Table of Contents**

| 1      | General Chip Description                                           | 17     |

|--------|--------------------------------------------------------------------|--------|

| 2      | Signal Description                                                 | 21     |

| 2.1    |                                                                    |        |

|        | 2.1.1 88E2110 Device Pin Map                                       |        |

| 0.0    | •                                                                  |        |

| 2.2    | •                                                                  |        |

| 2.3    | •                                                                  |        |

| 2.4    | Pin Assignment Lists                                               |        |

|        | 2.4.2 88E2180 Device Pin Assignment List                           |        |

| 3      | Functional Description                                             | 57     |

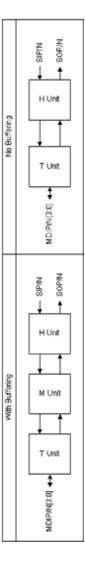

| 3.1    | Data Path                                                          | 57     |

| 3.2    | Auto-Speed Adjustment                                              | 58     |

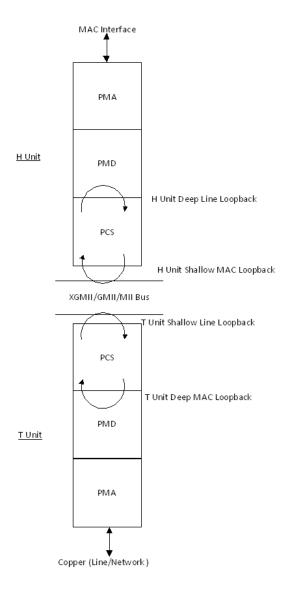

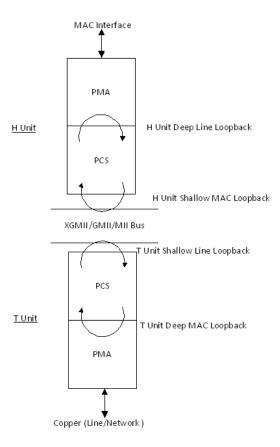

| 3.3    | Loopback                                                           | 59     |

|        | 3.3.1 MAC Loopback                                                 | 61     |

|        | 3.3.2 Line Loopback                                                |        |

| 3.4    | FIFO Overview                                                      |        |

| 3.5    |                                                                    |        |

|        | 3.5.1 Hardware and Software Resets                                 |        |

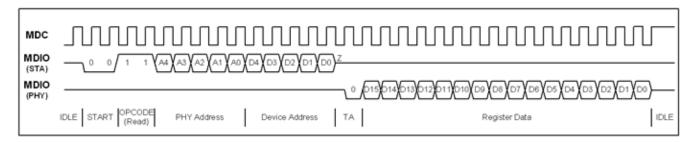

| 3.6    | MDC/MDIO Register Access                                           |        |

| 0.0    | 3.6.1 Clause 45 MDIO Framing                                       | 69     |

|        | 3.6.2 30 MHz High-Speed MDC/MDIO Management Interface Pro          |        |

|        | 3.6.3 XMDIO Register Access via Clause 22 MDIO Protocol            |        |

| 3.7    | Two-Wire Serial Interface (TWSI) Register Access for the 88E2110 D | Device |

|        | 3.7.1 Clause 45 Encapsulation                                      |        |

| 3.8    | Firmware Loading                                                   |        |

|        | 3.8.2 Firmware Download to RAM                                     |        |

| 3.9    | Power Management                                                   | 79     |

|        | 3.9.1 Manual Power Down                                            | 79     |

|        | 3.9.2 MAC Interface Power Down                                     |        |

| 3.10   | 0 GPIO                                                             |        |

|        | 3.10.1 Enabling the GPIO Function                                  |        |

|        | 3.10.2 Controlling and Sensing                                     |        |

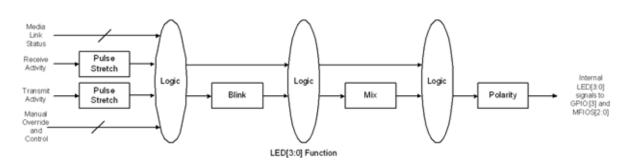

| 3 11   | 1 LED                                                              |        |

| J. 1 1 | 3 11 1 LED Polarity                                                |        |

|       | 3.11.2           | Pulse Stretching and Blinking                                        |     |

|-------|------------------|----------------------------------------------------------------------|-----|

|       | 3.11.3           | Bi-Color LED Mixing                                                  |     |

|       | 3.11.4           | Modes of Operation                                                   |     |

|       | 3.11.5<br>3.11.6 | Speed BlinkCombo LED Modes                                           |     |

|       | 3.11.0           | LED Output via MFIO Pins (88E2110), GPIO/LED or Serial LED (88E2180) |     |

|       | _                |                                                                      |     |

| 3.12  |                  | 80 Serial LED                                                        |     |

|       | 3.12.1<br>3.12.2 | 88E2180 Serial Display Order                                         |     |

|       | 3.12.2           | 88E2180 Serial Clock Speed Options                                   |     |

|       | 3.12.4           | 88E2180 Serial LED Feature Application Examples                      |     |

| 3 13  |                  | pt                                                                   |     |

|       |                  | 149.1 and 1149.6 Controller                                          |     |

| J. 14 | 3.14.1           | BYPASS Instruction                                                   |     |

|       | 3.14.2           | SAMPLE/PRELOAD Instruction                                           |     |

|       | 3.14.3           | EXTEST Instruction                                                   |     |

|       | 3.14.4           | CLAMP Instruction                                                    |     |

|       | 3.14.5           | HIGH-Z Instruction                                                   |     |

|       | 3.14.6           | ID CODE Instruction                                                  | 102 |

|       | 3.14.7           | EXTEST_PULSE Instruction                                             | 102 |

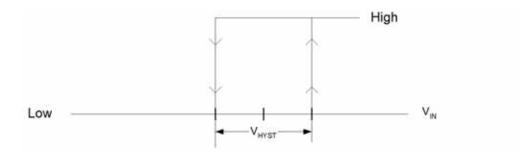

|       | 3.14.8           | PROG_HYST Instruction                                                | 103 |

|       | 3.14.9           | AC-JTAG Fault Detection                                              | 104 |

| 3.15  | Refere           | nce Clock                                                            | 107 |

| 3.16  | Tempe            | erature Sensor                                                       | 107 |

| 3.17  | Power            | Supplies                                                             | 107 |

|       | 3.17.1           |                                                                      |     |

|       | 3.17.2           | AVDDH                                                                |     |

|       | 3.17.3           | AVDDT                                                                |     |

|       | 3.17.4           | AVDDC                                                                |     |

|       | 3.17.5           | AVDDS                                                                |     |

|       | 3.17.6           | AVDDR                                                                |     |

|       | 3.17.7           | DVDD                                                                 |     |

|       | 3.17.8<br>3.17.9 | VDDOVDDR09                                                           |     |

|       | 3.17.9           | VDDR09                                                               | 109 |

| 4     | Coppe            | er Unit (T Unit)                                                     | 110 |

| 4.1   | Media            | Interface                                                            |     |

|       | 4.1.1            | 2.5GBASE-T and 5GBASE-T                                              | 110 |

|       | 4.1.2            | 1000BASE-T                                                           | 111 |

|       | 4.1.3            | 100BASE-TX                                                           | 111 |

|       | 4.1.4            | 10BASE-Te                                                            | 112 |

| 4.2   | Loopba           | ack                                                                  | 112 |

|       | 4.2.1            | Line Loopback                                                        | 112 |

| 4.3   | Synchr           | onization FIFO                                                       | 112 |

| 4.4   | Power            | Management                                                           | 113 |

|       | 4.4.1            | Manual Power Down                                                    |     |

|       | 4.4.2            | Energy Detect                                                        | 113 |

| 4.5  | Auto-Negotiation                                                              | 114 |

|------|-------------------------------------------------------------------------------|-----|

| 4.6  |                                                                               |     |

| 4.7  |                                                                               |     |

|      |                                                                               |     |

| 4.8  | •                                                                             |     |

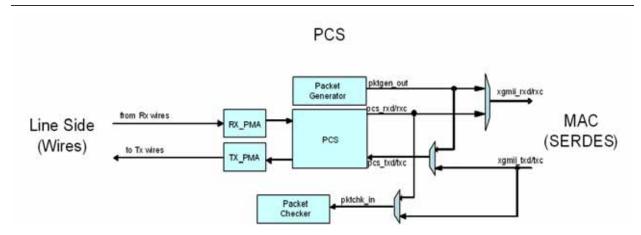

| 4.9  | Packet Generator and Checker                                                  |     |

|      | 4.9.2 10M/100M/1G Mode Packet Generator 4.9.2 10M/100M/1G Mode Packet Checker |     |

|      | 4.9.3 2.5G/5G Mode Packet Generator and Checker                               |     |

|      | 4.9.4 Link Drop Counter                                                       |     |

| 4.10 | 0 Interrupt                                                                   | 122 |

| 5    | Host Interface Unit (H Unit)                                                  | 123 |

| 5.1  | Host Electrical Interface                                                     | 123 |

| 5.2  | PCS                                                                           | 124 |

| 0.2  | 5.2.1 2500BASE-X                                                              |     |

|      | 5.2.2 SGMII                                                                   |     |

|      | 5.2.3 SXGMII                                                                  |     |

| 5.3  | · ·                                                                           |     |

|      | 5.3.1 MAC Loopback                                                            |     |

| 5.4  | Power Management                                                              | 127 |

| 5.5  | •                                                                             |     |

|      | 5.5.1 Packet Generator                                                        |     |

|      | 5.5.2 Checker                                                                 |     |

| 5.6  | ·                                                                             |     |

| 5.0  | 5.6.1 General PRBS Generators and Checkers                                    |     |

| 5.7  |                                                                               |     |

|      |                                                                               |     |

| 6    | Electrical Specifications                                                     |     |

| 6.1  | Absolute Maximum Ratings                                                      | 131 |

| 6.2  | Recommended Operating Conditions                                              | 132 |

| 6.3  |                                                                               |     |

|      | 6.3.1 Thermal Conditions for 104-pin, FC-TFBGA Package for the 88E2110 Device |     |

|      | 6.3.2 Thermal Conditions for 529-pin, HFCBGA Package for the 88E2180 Device   |     |

| 6.4  | · · · · · · · · · · · · · · · · · · ·                                         |     |

|      | 6.4.1 Current Consumption for C-Temp                                          |     |

| 0.5  | · · · · · · · · · · · · · · · · · · ·                                         |     |

| 6.5  | Digital I/O Electrical Specifications                                         |     |

|      | 6.5.2 Reset Timing                                                            |     |

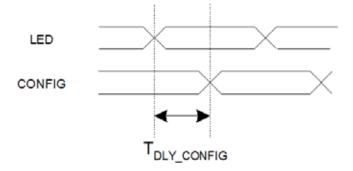

|      | 6.5.3 LED to CONFIG Timing                                                    | 140 |

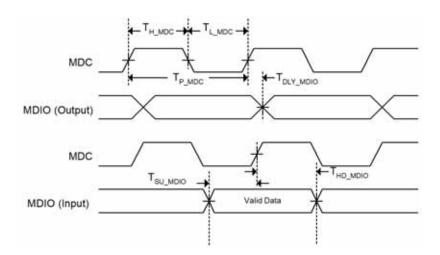

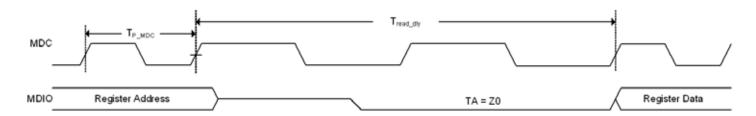

|      | 6.5.4 MDC/MDIO Management Interface Timing                                    |     |

|      | 6.5.5 JTAG Timing                                                             |     |

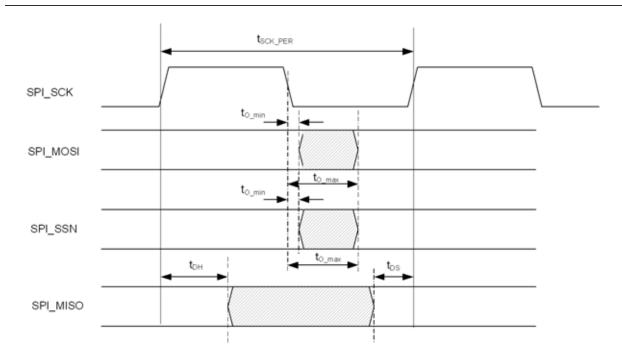

|      | 6.5.6 SPI Interface Timing                                                    |     |

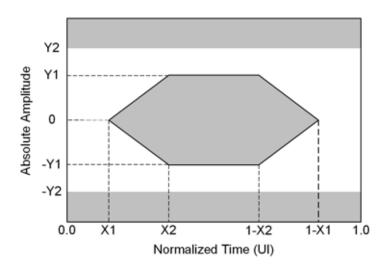

|      | 6.5.8 2500BASE-X Electrical Summary                                           |     |

|      | 6.5.9 5GBASE-R Electrical Summary                                             |     |

| Α   | Revisi           | on History                                                             | 159 |

|-----|------------------|------------------------------------------------------------------------|-----|

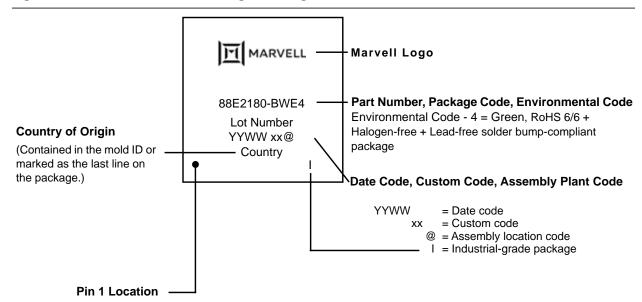

|     | 8.1.1            | Package Marking                                                        | 157 |

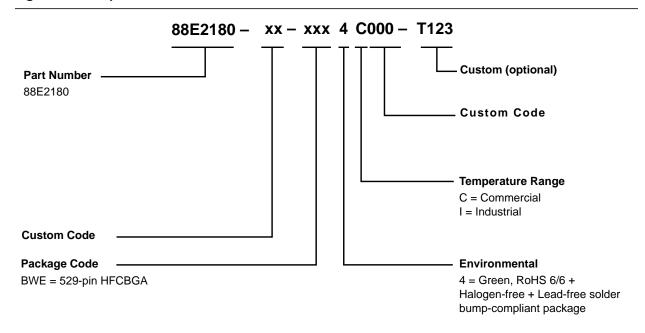

| 8.1 | Part Or          | der Numbering                                                          | 155 |

| 8   | Part O           | rder Numbering/Package Marking                                         | 155 |

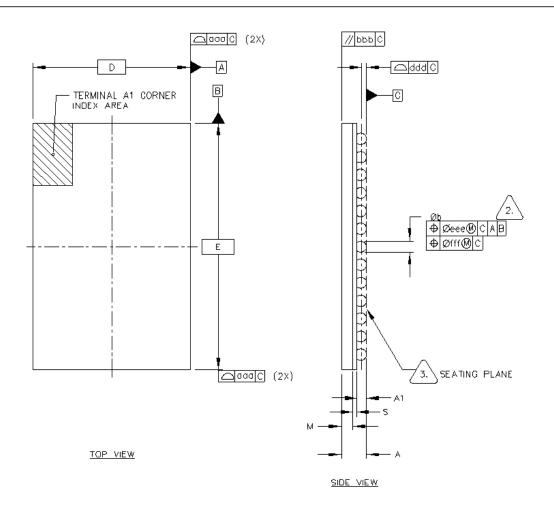

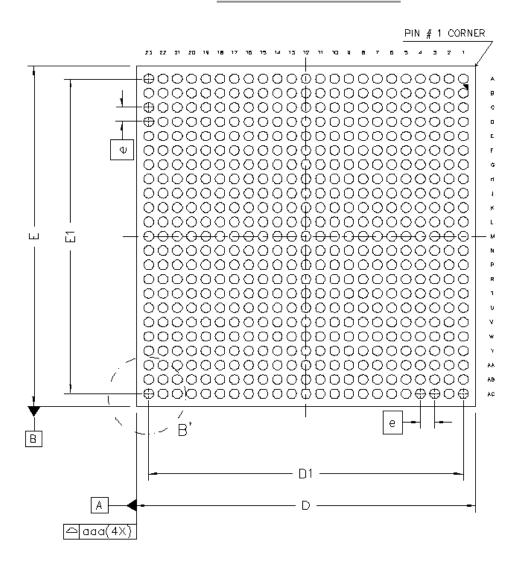

| 7.2 | 529-pin          | 19 mm x 19 mm HFCBGA Package Mechanical Drawings of the 88E2180 Device | 152 |

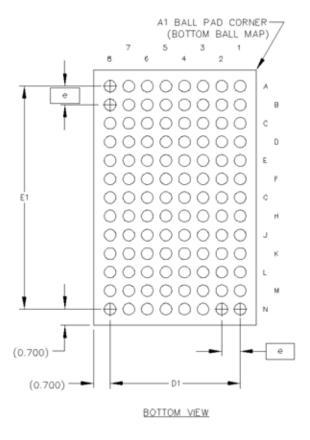

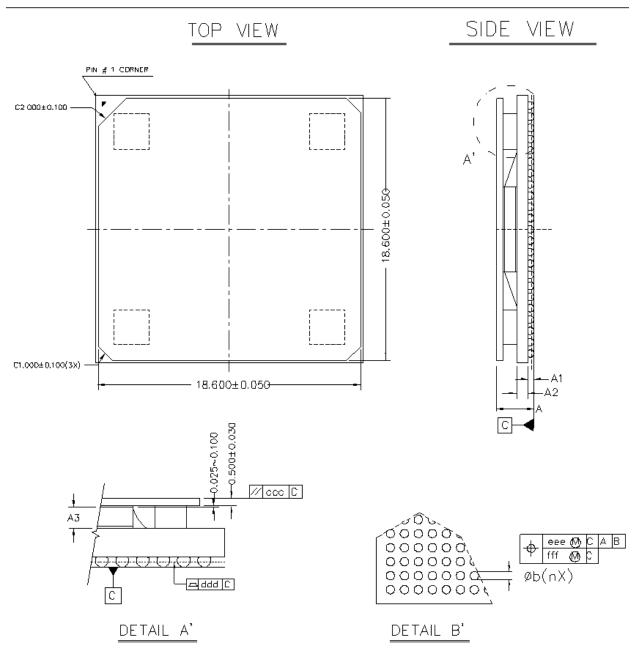

| 7.1 | 104-pin          | 7 mm x 11 mm FC-TBGA Package Mechanical Drawings of the 88E2110 Device | 149 |

| 7   | Mecha            | nical Drawings                                                         | 149 |

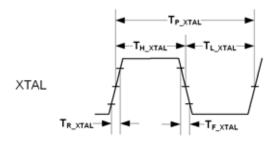

|     | 6.6.3            | CLKP/N Timing — 50 MHzXTAL Timing                                      | 148 |

|     |                  | CLKP/N Timing — 50.23 MHz                                              | 147 |

| 6.6 | Referer<br>6.6.1 | nce Clock                                                              | 147 |

|     | 6.5.10           | 10BASE-Te, 100BASE-TX, and 1000BASE-T Electrical Parameters            | 146 |

### **List of Tables**

| Pro | oduct Over | view                                           | 4  |

|-----|------------|------------------------------------------------|----|

| 1   | General (  | Chip Description                               | 17 |

| 2   | Signal De  | escription                                     | 21 |

|     | Table 1:   | Pin Type Definitions                           | 21 |

|     | Table 2:   | Media Dependent Interface                      | 25 |

|     | Table 3:   | SERDES Interface                               | 25 |

|     | Table 4:   | Clock/Reset/Reference                          | 26 |

|     | Table 5:   | Management Interface                           | 26 |

|     | Table 6:   | SPI Interface                                  | 26 |

|     | Table 7:   | GPIO                                           | 27 |

|     | Table 8:   | Multi-functional Input/Output                  | 27 |

|     | Table 9:   | Configuration                                  | 27 |

|     | Table 10:  | JTAG Interface                                 | 27 |

|     | Table 11:  | Test Pins                                      | 28 |

|     | Table 12:  | Power and Ground                               | 28 |

|     | Table 13:  | Do Not Connect                                 | 29 |

|     | Table 14:  | Media Dependent Interface                      | 30 |

|     | Table 15:  | SERDES Interface                               | 32 |

|     | Table 16:  | Clock/Reset/Reference                          | 33 |

|     | Table 17:  | Management Interface                           | 33 |

|     | Table 18:  | SPI Interface                                  | 33 |

|     | Table 19:  | GPIO                                           | 34 |

|     | Table 20:  | Multi-functional Input/Output                  | 34 |

|     | Table 21:  | Configuration                                  | 34 |

|     | Table 22:  | JTAG Interface                                 | 35 |

|     | Table 23:  | Test Pins                                      | 35 |

|     | Table 24:  | Power and Ground                               | 35 |

|     | Table 25:  | Do Not Connect                                 | 44 |

|     | Table 26:  | 88E2110 Pin List — Alphabetical by Signal Name | 45 |

|     | Table 27:  | 88E2180 Pin List — Alphabetical by Signal Name | 47 |

| 3   | Function   | al Description                                 | 57 |

|     | Table 28:  | Loopback Control                               | 59 |

|     | Table 29:  | 88E2110 Device Configuration Mapping           | 63 |

|     | Table 30:  | 88E2110 Device Three Bit Mapping               | 64 |

|     | Table 31:  | 88E2180 Device Configuration Mapping           | 64 |

|     | Table 32:  | 88E2180 Device Three Bit Mapping               | 64 |

|     | Table 33:  | 88E2180 Configuration Definition               | 65 |

|   | Table 34:  | 88E2110 Configuration Definition                                        | 66  |

|---|------------|-------------------------------------------------------------------------|-----|

|   | Table 35:  | Possible MACTYPE Change Combinations for the 88E2180 Device             | 67  |

|   | Table 36:  | Extensions for Management Frame Format for Indirect Access              | 69  |

|   | Table 37:  | Clause 22 Registers Not Defined in Clause 45                            | 69  |

|   | Table 38:  | MMD Access Control Register                                             | 70  |

|   | Table 39:  | MMD Access Address/Data Register                                        | 71  |

|   | Table 40:  | INS[2:0] Definition                                                     | 74  |

|   | Table 41:  | Dual LED Mode Behavior                                                  | 84  |

|   | Table 42:  | Basic LED Status                                                        | 85  |

|   | Table 43:  | Compound LED Status                                                     | 85  |

|   | Table 44:  | Speed Blinking Sequence                                                 | 86  |

|   | Table 45:  | Combo Mode Timer Control                                                | 87  |

|   | Table 46:  | Combo LED Flash Mode                                                    | 88  |

|   | Table 47:  | Example of GPIO Assignment for the 88E2180 Device                       | 89  |

|   | Table 48:  | Clock Speed Options                                                     | 91  |

|   | Table 49:  | 88E2180 Serial LED Control Register (Global Register)                   | 91  |

|   | Table 50:  | 88E2180 Global Interrupt Status (Port 0, 1, 6, and 7)                   | 92  |

|   | Table 51:  | 88E2180 Global Interrupt Status (Port 2, 3, 4, and 5)                   | 93  |

|   | Table 52:  | TAP Controller Opcodes                                                  | 93  |

|   | Table 53:  | Boundary Scan Chain for the 88E2180 Device                              | 94  |

|   | Table 54:  | Boundary Scan Chain for the 88E2110 Device                              | 100 |

|   | Table 55:  | ID CODE Instruction                                                     | 102 |

|   | Table 56:  | Test Receiver Hysteresis Setting                                        | 104 |

|   | Table 57:  | AC-Coupled Connection Fault Signature                                   | 105 |

|   | Table 58:  | DC-Coupled Connection Fault Signature                                   | 106 |

|   | Table 59:  | Reference Clock Options                                                 | 107 |

|   | Table 60:  | Signal Power Segment                                                    | 108 |

| 4 | Copper U   | Jnit (T Unit)                                                           | 110 |

|   | Table 61:  | Media Dependent Interface Pin Mapping                                   | 116 |

|   | Table 62:  | Generator/Checker Register Equivalence Between the 10M/100M/1G Mode     | 120 |

| 5 | Host Inte  | rface Unit (H Unit)                                                     | 123 |

|   | Table 63:  | 88E2110 Host Interface Configuration                                    | 124 |

|   | Table 64:  | 88E2180 Host Interface Configuration                                    | 124 |

|   | Table 65:  | SGMII Auto-Negotiation Modes                                            | 126 |

| 6 | Electrical | Specifications                                                          | 131 |

|   | Table 66:  | Absolute Maximum Ratings                                                | 131 |

|   | Table 67:  | Recommended Operating Conditions                                        | 132 |

|   | Table 68:  | Thermal Conditions for 104-pin, FC-TFBGA Package for the 88E2110 Device | 133 |

|   | Table 69:  | Thermal Conditions for 529-pin, HFCBGA Package for the 88E2180 Device   | 134 |

|   | Table 70:  | Base Current Consumption for C-Temp Devices                             | 135 |

|   | Table 71:  | Operational Current Consumption for per Port — Excludes Base Current    | 136 |

|   | Table 72   | CMS Enabled                                                             | 137 |

|   | Table 73: | DC Operating Conditions                                               | 138 |

|---|-----------|-----------------------------------------------------------------------|-----|

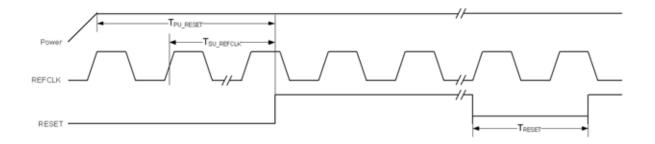

|   | Table 74: | Reset Timing                                                          | 139 |

|   | Table 75: | LED to CONFIG Timing                                                  | 140 |

|   | Table 76: | MDC/MDIO Management Interface Timing                                  | 141 |

|   | Table 77: | JTAG Timing                                                           | 142 |

|   | Table 78: | SPI Interface Timing                                                  | 143 |

|   | Table 79: | SGMII Electrical Summary                                              | 144 |

|   | Table 80: | 2500BASE-X Electrical Summary                                         | 145 |

|   | Table 81: | 5GBASE-R Electrical Summary                                           | 145 |

|   | Table 82: | IEEE DC Transceiver Parameters                                        | 146 |

|   | Table 83: | CLKP/N Timing — 156.25 MHz                                            | 147 |

|   | Table 84: | CLKP/N Timing — 50 MHz                                                | 147 |

|   | Table 85: | XTAL Timing                                                           | 148 |

| 7 | Mechanic  | cal Drawings                                                          | 149 |

|   | Table 86: | 104-pin 7 mm x 11 mm FC-TBGA Package Dimensions of the 88E2110 Device |     |

|   | Table 87: | 529-pin 19 mm x 19 mm HFCBGA Package Dimensions of the 88E2180 Device |     |

| 8 | Part Orde | er Numbering/Package Marking                                          | 155 |

|   | Table 88: | 88E2180 and 88E2110 Commercial Part Order Options                     | 156 |

|   | Table 89  | Document Change History                                               | 159 |

### **List of Figures**

| Pro | oduct Over | view                                                                           | 4   |

|-----|------------|--------------------------------------------------------------------------------|-----|

|     | Figure 1:  | 88E2180 Top-level Block Diagram                                                | 5   |

|     | Figure 2:  | 88E2110 Top-level Block Diagram                                                | 6   |

|     | Figure 3:  | Device Application — Host Interface Speed Matched to Line Speed                | 7   |

| 1   | General (  | Chip Description                                                               | 17  |

|     | Figure 4:  | 88E2180 Device Functional Block Diagram                                        | 18  |

|     | Figure 5:  | 88E2110 Device Functional Block Diagram                                        | 19  |

| 2   | Signal De  | escription                                                                     | 21  |

| 3   | Function   | al Description                                                                 | 57  |

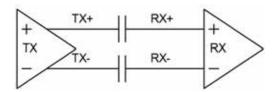

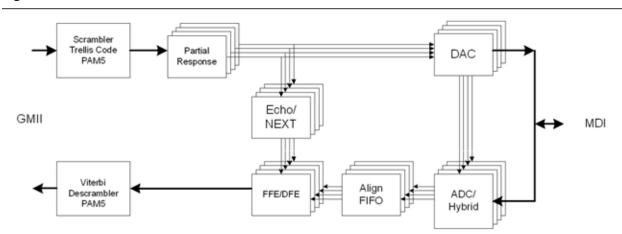

|     | Figure 6:  | Device Data Path                                                               | 57  |

|     | Figure 7:  | Loopback Paths for 88E2110 Devices                                             | 60  |

|     | Figure 8:  | Loopback Paths for 88E2180 Devices                                             | 61  |

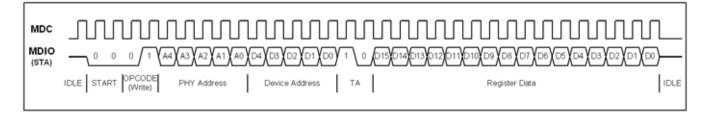

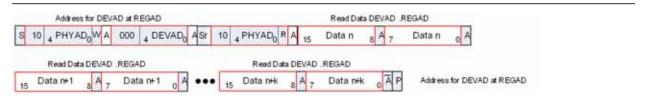

|     | Figure 9:  | Typical MDC/MDIO Read Operation                                                | 68  |

|     | Figure 10: | Typical MDC/MDIO Write Operation                                               | 68  |

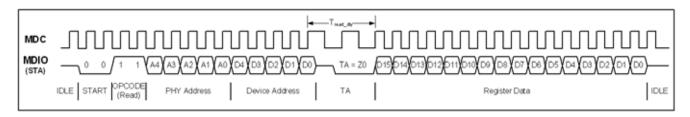

|     | Figure 11: | 30 MHz MDC/MDIO Read Operation                                                 | 72  |

|     | Figure 12: | First Two Bytes of All Transactions                                            | 74  |

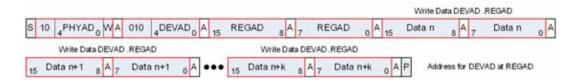

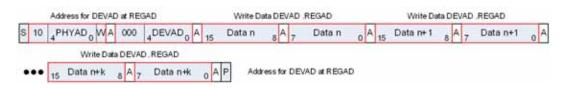

|     | Figure 13: | Write, Full Header, Retain REGAD                                               | 76  |

|     | Figure 14: | Write, Full Header, Post-Increment                                             | 76  |

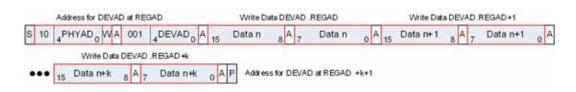

|     | Figure 15: | Write, Abbreviated Header, Retain REGAD                                        | 76  |

|     | Figure 16: | Write, Abbreviated Header, Post-Increment                                      | 76  |

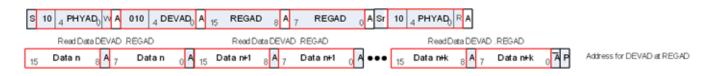

|     | Figure 17: | Read, Full Header, Retain REGAD                                                | 76  |

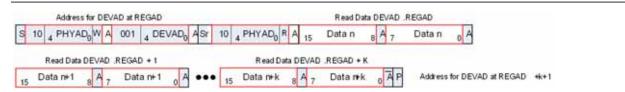

|     | Figure 18: | Read, Full Header, Post-Increment                                              | 77  |

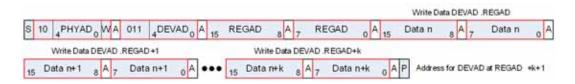

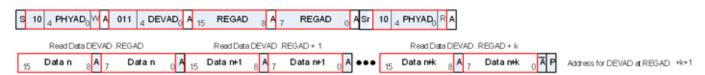

|     | Figure 19: | Read, Abbreviated Header, Retain REGAD                                         | 77  |

|     | Figure 20: | Read, Abbreviated Header, Post-Increment                                       | 77  |

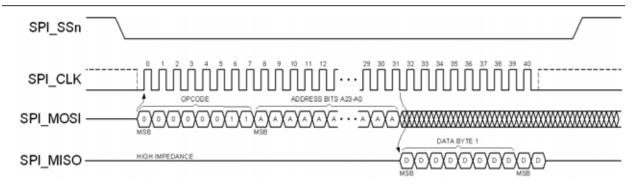

|     | Figure 21: | SPI Read Array                                                                 | 78  |

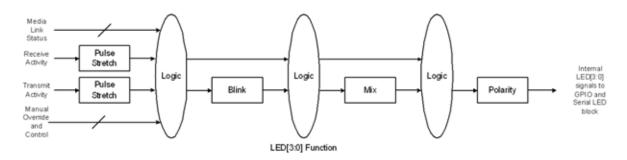

|     | Figure 22: | LED Chain for the 88E2110 Device                                               | 81  |

|     | Figure 23: | LED Chain for the 88E2180 Device                                               | 81  |

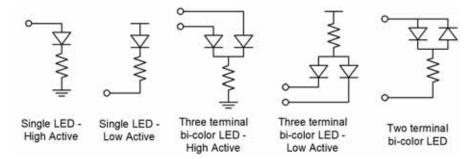

|     | Figure 24: | Various LED Hookup Configurations                                              | 82  |

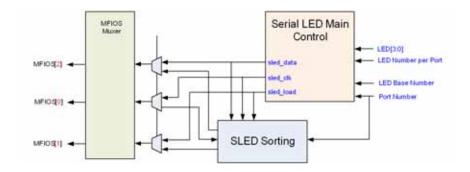

|     | Figure 25: | 88E2180 Serial LED Control Block Diagram                                       | 90  |

|     | Figure 26: | Interface Protocol Example in 88E2180 — One LED per Port                       | 90  |

|     | Figure 27: | Interface Protocol Example in 88E2180 — Two LEDs per Port                      | 90  |

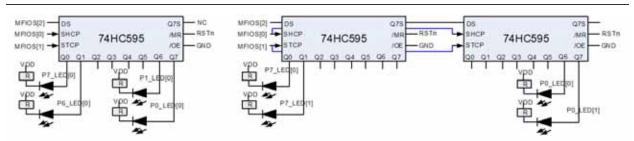

|     | Figure 28: | 88E2180 Serial LED Application Example: One LED per Port and Two LEDs per Port | 91  |

|     | Figure 29: | AC-Coupled Connection                                                          | 104 |

|     | Figure 30: | DC-Coupled Connection                                                          | 106 |

| 4   | Copper U   | Init (T Unit)                                                                  | 110 |

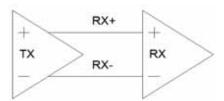

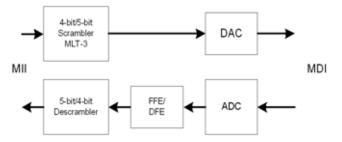

|     | Figure 31: | 2.5GBASE-T and 5GBASE-T Data Path                                              | 110 |

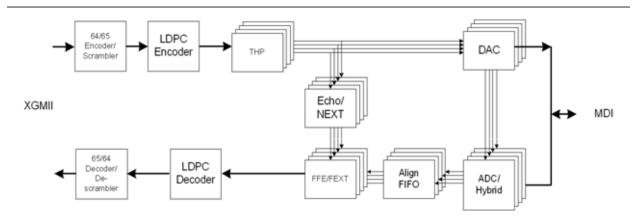

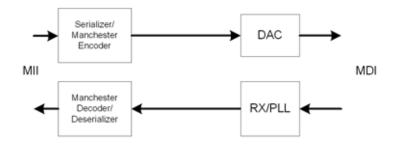

|   | Figure 32: | 1000BASE-T Data Path                                                  | 111 |

|---|------------|-----------------------------------------------------------------------|-----|

|   | Figure 33: | 100BASE-TX Data Path                                                  | 111 |

|   | Figure 34: | 10BASE-Te Data Path                                                   | 112 |

|   | Figure 35: | Packet Generator Data Paths                                           | 118 |

| 5 | Host Inte  | rface Unit (H Unit)                                                   | 123 |

| 6 | Electrical | Specifications                                                        | 131 |

|   | Figure 36: | Reset Timing                                                          | 139 |

|   | Figure 37: | LED to CONFIG Timing                                                  | 140 |

|   | Figure 38: | MDC/MDIO Management Interface Timing                                  | 141 |

|   | Figure 39: | MDC/MDIO Input Hysteresis                                             | 141 |

|   | Figure 40: | MDC Read Turnaround Delay                                             | 142 |

|   | Figure 41: | JTAG Timing                                                           | 142 |

|   | Figure 42: | SPI Interface Timing                                                  | 143 |

|   | Figure 43: | Transmitter Eye Mask                                                  | 144 |

|   | Figure 44: | XTAL Timing                                                           | 148 |

| 7 | Mechanic   | eal Drawings                                                          | 149 |

|   | Figure 45: | 104-pin 7 mm x 11 mm FC-TFBGA Top and Side View of the 88E2110 Device | 149 |

|   | Figure 46: | 104-pin 7 mm x 11 mm FC-TFBGA Bottom View of the 88E2110 Device       | 150 |

|   | Figure 47: | 529-pin 19 mm x 19 mm HFCBGA Top and Side View of the 88E2180 Device  | 152 |

|   | Figure 48: | 529-pin 19 mm x 19 mm HFCBGA Bottom View of the 88E2180 Device        | 153 |

| 8 | Part Orde  | er Numbering/Package Marking                                          | 155 |

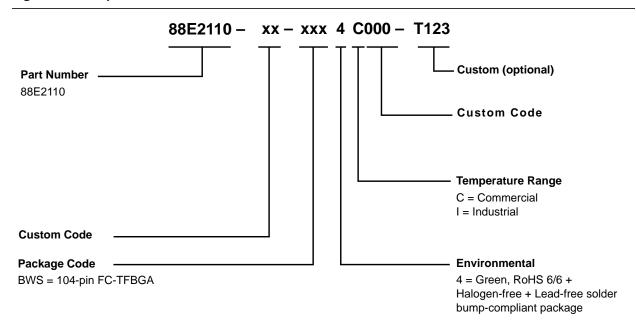

|   | Figure 49: | Sample Part Number for 88E2180                                        | 155 |

|   | Figure 50: | Sample Part Number for 88E2110                                        | 156 |

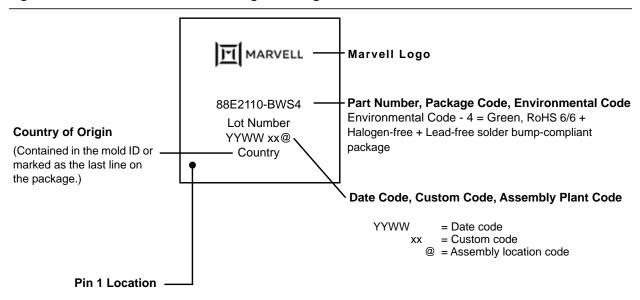

|   | Figure 51: | 88E2110 Commercial Package Marking and Pin 1 Location                 | 157 |

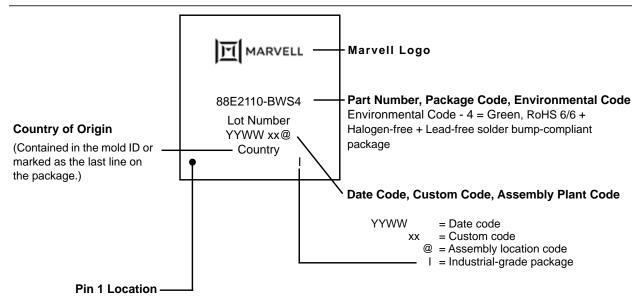

|   | Figure 52: | 88E2110 Industrial Package Marking and Pin 1 Location                 | 157 |

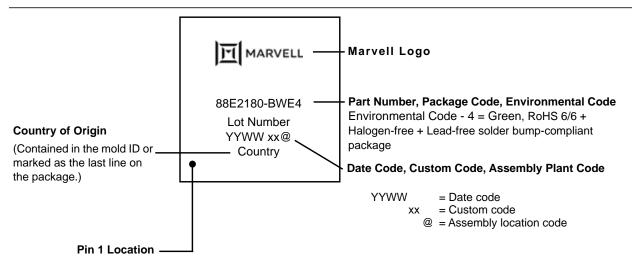

|   | Figure 53: | 88E2180 Commercial Package Marking and Pin 1 Location                 | 158 |

|   | Figure 54: | 88F2180 Industrial Package Marking and Pin 1 Location                 | 158 |

## 1

### **General Chip Description**

The device is an eight-port (88E2180) or single-port (88E2110) integrated multi-speed copper Ethernet transceiver.

For the 88E2180/88E2110 device, the host interface to the MAC is via 5GBASE-R, 2500BASE-X, or SGMII

Registers can be accessed through standard Clause 45 (or 22) MDC/MDIO or Two-wire Serial Interface (TWSI) for the 88E2110 device.

Figure 4: 88E2180 Device Functional Block Diagram

Figure 5: 88E2110 Device Functional Block Diagram

- VDDOM

- VDDOT

VSS VDDCTRL

MFIOS[2:0]

GPI0[5:0]

The datasheet comprises the following sections:

- Section 1 describes the general function of the device.

- Section 2 describes signal pinout and pin definitions of the device.

- Section 3 provides a functional description of the device.

- Section 4 describes the copper interface functions (T Unit).

- Section 5 describes the host interface functions (H Unit).

- Section 6 describes the electrical specification of the device.

- Section 7 describes the package mechanical dimensions.

- Section 8 provides the order information.

The conventions used in the datasheet are as follows.

All registers are specified per IEEE 802.3 section 45. The format is X.Y, X.Y.Z or X.Y.Z1:Z2, where X is the device address in decimal from 0 to 31, Y is the register address in hexadecimal from 0000 to FFFF, and Z is the bit in decimal from 0 to 15.

T Unit - 10/100/1000/2.5G/5GBASE-T interface.

H Unit - SGMII/2500BASE-X/5GBASE-R host interface.

# 2

### **Signal Description**

Table 1: Pin Type Definitions

| Pin Type | Definition            |

|----------|-----------------------|

| Н        | Input with hysteresis |

| I/O      | Input and output      |

| 1        | Input only            |

| 0        | Output only           |

| PU       | Internal pull-up      |

| PD       | Internal pull-down    |

| D        | Open drain output     |

| Z        | Tri-state output      |

| mA       | DC sink capability    |

### 2.1 Pin Maps

### 2.1.1 88E2110 Device Pin Map

|   | 1      | 2          | 3       | 4       | 5       | 6         | 7         | 8        |   |

|---|--------|------------|---------|---------|---------|-----------|-----------|----------|---|

| A | vss    | AVSS       | SIP     | AVSS    | SOP     | AVSS      | RESETn    | VSS      | A |

| В | TRSTn  | TEST       | SIN     | AVSS    | SON     | CONFIG[0] | SPI_SSn   | SPI_CLK  | В |

| С | TCK    | TMS        | VSEL_T  | DNC     | AVSS    | CONFIG[2] | SPI_MOSI  | SPI_MISO | С |

| D | TDI    | VDDCTRL    | VSS     | VSS     | VSS     | AVDDR     | CONFIG[1] | GPIO[0]  | D |

| E | TDO    | NTn        | DVDD    | VSS     | DVDD    | AVSS      | AVDDS     | GPIO[1]  | E |

| F | MDIO   | VDDOT      | DVDD    | VSS     | DVDD    | VDDR09    | GPIO[3]   | GPIO[2]  | F |

| G | MDC    | VDDOM      | DVDD    | DVDD    | DVDD    | VSS       | RCLK      | MFIOS[2] | G |

| н | VSEL_M | AVDDC      | vss     | vss     | vss     | vss       | VDDOL     | MFIOS[1] | н |

| J | CLKN   | CLK_SEL[0] | AVSS    | AVSS    | AVSS    | AVSS      | HSDA CN   | MFIOS[0] | J |

| к | CLKP   | CLK_SEL[1] | AVDDH   | AVDDL   | AVDDL   | AVDDT     | HSDACP    | GPIO[4]  | к |

| L | XTAL2  | AVSSC      | AVDDH   | AVSS    | AVSS    | AVDDT     | TSTPT     | GPIO[5]  | L |

| м | XTAL1  | AVSS       | AVSS    | MDIN[1] | MDN[2]  | AVSS      | AVSS      | IREF     | М |

| N | AVSS   | MDIP[0]    | MDIN[0] | MDIP[1] | MDIP[2] | MDIN[3]   | MDIP[3]   | AVSS     | N |

|   | 1      | 2          | 3       | 4       | 5       | 6         | 7         | 8        |   |

(Top View)

### 2.1.2 88E2180 Device Pin Map

Due to the large number of pins, the package is depicted graphically over two pages.

|    | 1       | 2          | 3           | 4           | 5           | 6          | 7        | 8           | 9           | 10          | 11         | 12   |    |

|----|---------|------------|-------------|-------------|-------------|------------|----------|-------------|-------------|-------------|------------|------|----|

| Α  | AVSS    | AVSS       | P7_MDIP[0]  | P7_MDIP[1]  | P7_M DIP[2] | P7_MDIP[3] | AVSS     | P6_M DIP[3] | P6_MDIP[2]  | P6_MDIP[1]  | P6_MDIP[0] | AVSS | Α  |

| В  | RESETn  | TRSTn      | P7_M DIN[0] | P7_M DIN[1] | P7_MDIN[2]  | P7_MDIN[3] | AVSS     | P6_M DIN[3] | P6_M DIN[2] | P6_M DIN[1] | P6_MDIN[0] | AVSS | В  |

| C  | SPLMOSI | TDI        | TEST        | AVSS        | AVSS        | AVSS       | AVSS     | AVSS        | AVSS        | AVSS        | AVSS       | AVSS | Ç  |

| D  | SPI_CLK | TCK.       | TMS         | P7_AVDDT    | P7_AVDDT    | P7_AVDDL   | P7_AVDDL | P6_AVDDL    | P6_AVDDL    | P6_AVDDT    | P6_AVDDT   | AVSS | D  |

| E  | SPLMIS0 | TDO        | RCLK        | V SEL_T     | AVSS        | AVSS       | AVSS     | AVSS        | AVSS        | AVSS        | AVSS       | AVSS | E  |

| F  | SPI_SSn | VSS        | VSS         | AVSS        | AVSS        | AVSS       | AVSS     | AVSS        | AVSS        | AVSS        | P6_SON     | AVSS | F  |

| G  | VDDOL   | VDDOT      | VSS         | AVSS        | P7_AVDDH    | P7_AVDDH   | P6_AVDDH | P6_AVDDH    | AVSS        | AVSS        | P6_SOP     | AVSS | G  |

| н  | AVSS    | AVSS       | P7_AVDDR    | AVSS        | VSS         | vss        | AVSS     | VSS         | AVSS        | P6_AVDDR    | AVSS       | AVSS | Н  |

| J  | P7_SIP  | P7_SIN     | P7_AVDDS    | VSS         | VSS         | VSS        | VSS      | VSS         | VSS         | P6_AVDDS    | P6_SIP     | AVSS | J  |

| K  | AVSS    | AVSS       | P7_VDDR09   | DVDD        | DVDD        | DVDD       | DVDD     | DVDD        | DVDD        | VSS         | P6_SIN     | AVSS | K  |

| L  | P7_SOP  | P7_SON     | AVSS        | DVDD        | VSS         | VSS        | VSS      | DVDD        | VSS         | P6_VDDR09   | AVSS       | AVSS | L  |

| М  | AVSS    | AVSS       | VSS         | DVDD        | DVDD        | DNC        | DVDD     | DVDD        | VSS         | AVSS        | AVSS       | AVSS | М  |

| N  | PO_SOP  | P0_SON     | AVSS        | DVDD        | VSS         | VSS        | VSS      | DVDD        | VSS         | P1_VDDR09   | AVSS       | AVSS | N  |

| Р  | AVSS    | AVSS       | PO_VDDR09   | DVDD        | DVDD        | DVDD       | DVDD     | DVDD        | DVDD        | vss         | P1_SIN     | AVSS | Р  |

| R  | P0_SIP  | P0_SIN     | P0_AVDDS    | VSS         | VSS         | VSS        | VSS      | VSS         | VSS         | PLAVDDS     | P1_SIP     | AVSS | R  |

| Т  | AVSS    | AVSS       | P0_AVDDR    | AVSS        | VSS         | vss        | AVSS     | VSS         | AVSS        | PLAVDDR     | AVSS       | AVSS | Т  |

| U  | MDC     | MDIO       | VSS         | AVDDC       | P0_AVDDH    | P0_AVDDH   | P1_AVDDH | P1_AVDDH    | AVDDC       | AVSS        | P1_S0P     | AVSS | U  |

| ٧  | VSS     | VDDOM      | VSS         | AVSS        | AVSS        | AVSS       | AVSS     | AVSS        | AVSS        | AVSS        | P1_SON     | AVSS | ٧  |

| w  | CLKN    | TSTCN      | V SEL_M     | AVSS        | AVSS        | AVSS       | AVSS     | AVSS        | AVSS        | AVSS        | AVSS       | AVSS | W  |

| Υ  | CLKP    | TSTCP      | INTn        | P0_AVDDT    | P0_AVDDT    | P0_AVDDL   | PO_AVDDL | P1_AVDDL    | P1_AVDDL    | P1_AVDDT    | P1_AVDDT   | ATN  | Υ  |

| AA | XTAL2   | AVSSC      | CLK_SEL[0]  | AVSS        | AVSS        | AVSS       | AVSS     | AVSS        | AVSS        | AVSS        | AVSS       | ATP  | AA |

| AB | XTAL1   | CLK_SEL[1] | P0_MDIN[0]  | P0_MDIN[1]  | P0_M DIN[2] | P0_MDIN[3] | AVSS     | PLMDIN[3]   | PLMDIN[2]   | PLMDIN[1]   | P1_MDIN[0] | AVSS | AB |

| AC | AVSS    | AVSS       | P0_MDIP[0]  | P0_MDIP[1]  | P0_MDIP[2]  | 60"WDI6[3] | AVSS     | P1_MDIP[3]  | P1_MDIP[2]  | P1_MDIP[1]  | P1_MDIP[0] | AVSS | AC |

|    | 1       | 2          | 3           | 4           | 5           | 6          | 7        | 8           | 9           | 10          | 11         | 12   |    |

(Top View)

|    | 13            | 14           | 15          | 16          | 17       | 18           | 19         | 20          | 21         | 22         | 23         |    |

|----|---------------|--------------|-------------|-------------|----------|--------------|------------|-------------|------------|------------|------------|----|

| Α  | P5_MDIP[0]    | P5_M DIP[1]  | P5_M DIP[2] | P5_M DIP[3] | AVSS     | P4_M D IP[3] | P4_MDIP[2] | P4_M DIP[1] | P4_MDIP[0] | AVSS       | AVSS       | Α  |

| В  | P5_M D IN [0] | P5_M D IN[1] | P5_MDIN[2]  | P5_M DIN[3] | AVSS     | P4_MDIN[3]   | P4_MDIN[2] | P4_M DIN[1] | P4_MDIN[0] | CONFIG[2]  | CONFIG[1]  | В  |

| С  | AVSS          | AVSS         | AVSS        | AVSS        | AVSS     | AVSS         | AVSS       | AVSS        | M FIOS[0]  | P7_GPIO[1] | P7_GPIO[0] | С  |

| D  | P5_AVDDT      | P5_AVDDT     | P5_AVDDL    | P5_AVDDL    | P4_AVDDL | P4_AVDDL     | P4_AVDDT   | P4_AVDDT    | MFIOS[1]   | P6_GPIO[0] | P6_GPIO[1] | D  |

| Е  | AVSS          | AVSS         | AVSS        | AVSS        | AVSS     | AVSS         | AVSS       | AVSS        | M FIOS[2]  | P5_GPIO[1] | P5_GPIO(0) | Е  |

| F  | P5_SON        | AVSS         | AVSS        | AVSS        | AVSS     | AVSS         | AVSS       | AVSS        | VSS        | VDDOL      | P4_GPIO[0] | F  |

| G  | P5_SOP        | AVSS         | AVSS        | P5_AVDDH    | P5_AVDDH | P4_AVDDH     | P4_AVDDH   | AVSS        | vss        | P4_GPIO[1] | CONFIG[0]  | G  |

| Н  | AVSS          | P5_AVDDR     | AVSS        | VSS         | AVSS     | VSS          | VSS        | AVSS        | P4_AVDDR   | AVSS       | AVSS       | Н  |

| J  | P5_SIP        | P5_AVDDS     | VSS         | VSS         | VSS      | VSS          | VSS        | VSS         | P4_AVDDS   | P4_SIN     | P4_SIP     | J  |

| K  | P5_SIN        | VSS          | DVDD        | DVDD        | DVDD     | DVDD         | DVDD       | DVDD        | P4_VDDR09  | AVSS       | AVSS       | K  |

| L  | AVSS          | P5_VDDR09    | VSS         | DVDD        | VSS      | VSS          | VSS        | DVDD        | AVSS       | P4_SON     | P4_SOP     | L  |

| M  | AVSS          | AVSS         | VSS         | DVDD        | DVDD     | DNC          | DVDD       | DVDD        | VSS        | AVSS       | AVSS       | M  |

| N  | AVSS          | P2_VDDR09    | VSS         | DVDD        | vss      | VSS          | VSS        | DVDD        | AVSS       | P3_SON     | P3_90P     | N  |

| P  | P2_SIN        | VSS          | DVDD        | DVDD        | DVDD     | DVDD         | DVDD       | DVDD        | P3_VDDR09  | AVSS       | AVSS       | P  |

| R  | P2_SIP        | P2_AVDDS     | VSS         | VSS         | VSS      | VSS          | VSS        | VSS         | P3_AVDDS   | P3_SIN     | P3_SIP     | R  |

| Т  | AVSS          | P2_AVDDR     | AVSS        | VSS         | AVSS     | VSS          | VSS        | AVSS        | P3_AVDDR   | AVSS       | AVSS       | Т  |

| U  | P2_SOP        | AVSS         | AVDDC       | P2_AVDDH    | P2_AVDDH | P3_AVDDH     | P3_AVDDH   | AVDDC       | vss        | P3_GPIO[1] | IREF       | U  |

| ٧  | P2_SON        | AVSS         | AVSS        | AVSS        | AVSS     | AVSS         | AVSS       | AVSS        | vss        | VDDOL      | P3_GPIO[0] | ٧  |

| W  | AVSS          | AVSS         | AVSS        | AVSS        | AVSS     | AVSS         | AVSS       | AVSS        | HSDACN     | TEST_CLKN  | P2_GPIO[1] | W  |

| Υ  | P2_AVDDT      | P2_AVDDT     | P2_AVDDL    | P2_AVDDL    | P3_AVDDL | P3_AVDDL     | P3_AVDDT   | P3_AVDDT    | HSDACP     | TEST_CLKP  | P2_GPIO[0] | Y  |

| AA | AVSS          | AVSS         | AVSS        | AVSS        | AVSS     | AVSS         | AVSS       | AVSS        | TSTPT      | P1_GPI0[1] | P1_GPIO[0] | AA |

| AB | P2_M DIN[0]   | P2_M DIN[1]  | P2_M DIN[2] | P2_M DIN[3] | AVSS     | P3_MDIN[3]   | P3_MDIN[2] | P3_M DIN[1] | P3_MDIN[0] | P0_GPIO[1] | P0_GPIO[0] | AB |

| AC | P2_M DIP[0]   | P2_M DIP[1]  | P2_MDIP[2]  | P2_M DIP[3] | AVSS     | P3_MDIP[3]   | P3_MDIP[2] | P3_M DIP[1] | P3_MDIP[0] | AVSS       | AVSS       | AC |

|    | 13            | 14           | 15          | 16          | 17       | 18           | 19         | 20          | 21         | 22         | 23         |    |

(Top View)

### 2.2 Pin Description for the 88E2110 Device

Table 2: Media Dependent Interface

| 88E2110<br>Pin # | Pin Name           | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N2<br>N3         | MDIP[0]<br>MDIN[0] | I/O         | Media Dependent Interface[0] In 2.5G/5GBASE-T and 1000BASE-T modes in MDI configuration, MDIP/N[0] correspond to BI_DA±. In MDIX configuration, MDIP/N[0] correspond to BI_DB±. In 100BASE-TX and 10BASE-Te modes in MDI configuration, MDIP/N[0] are used for the transmit pair. In MDIX configuration, MDIP/N[0] are used for the receive pair. MDIP/N[0] should be tied to ground if not used. The device contains an internal 100Ω resistor between the MDIP/N[0] pins.      |

| N4<br>M4         | MDIP[1]<br>MDIN[1] | I/O         | Media Dependent Interface[1] In 2.5G/5GGBASE-T and 1000BASE-T modes in the MDIX configuration, MDIP/N[1] correspond to BI_DA±. In MDI configuration, MDIP/N[1] correspond to BI_DB±. In 100BASE-TX and 10BASE-Te modes in MDIX configuration, MDIP/N[1] are used for the transmit pair. In MDI configuration, MDIP/N[1] are used for the receive pair. MDIP/N[1] should be tied to ground if not used. The device contains an internal 100Ω resistor between the MDIP/N[1] pins. |

| N5<br>M5         | MDIP[2]<br>MDIN[2] | I/O         | Media Dependent Interface[2] In 2.5G/5GGBASE-T and 1000BASE-T modes in the MDI configuration, MDIP/N[2] correspond to BI_DC±. In MDIX configuration, MDIP/N[2] correspond to BI_DD±. In 100BASE-TX and 10BASE-Te modes these pins are floating. MDIP/N[2] should be tied to ground if not used. The device contains an internal 100Ω resistor between the MDIP/N[2] pins.                                                                                                        |

| N7<br>N6         | MDIP[3]<br>MDIN[3] | I/O         | Media Dependent Interface[3] In 2.5G/5GBASE-T and 1000BASE-T modes in the MDIX configuration, MDIP/N[3] correspond to BI_DC±. In MDI configuration, MDIP/N[3] correspond to BI_DD±. In 100BASE-TX and 10BASE-Te modes these pins are floating. MDIP/N[3] should be tied to ground if not used. The device contains an internal 100Ω resistor between the MDIP/N[3] pins.                                                                                                         |

Table 3: SERDES Interface

| 88E2110<br>Pin # | Pin Name   | Pin<br>Type | Description                             |

|------------------|------------|-------------|-----------------------------------------|

| A3<br>B3         | SIP<br>SIN | I           | Host SERDES Receive, Positive/Negative  |

| A5<br>B5         | SOP<br>SON | 0           | Host SERDES Transmit, Positive/Negative |

#### Table 4: Clock/Reset/Reference

| 88E2110<br>Pin # | Pin Name     | Pin<br>Type | Description                                                                              |

|------------------|--------------|-------------|------------------------------------------------------------------------------------------|

| M8               | IREF         | I           | Analog Reference. This pin should be connected via a 4.99 k $\Omega$ 1% resistor to VSS. |

| K1<br>J1         | CLKP<br>CLKN | I           | 156.25 MHz or 50 MHz differential Reference Clock Input.<br>±50 ppm tolerance.           |

| M1               | XTAL1        | 1           | 50 MHz crystal input                                                                     |

| L1               | XTAL2        | 0           | 50 MHz crystal output                                                                    |

| G7               | RCLK         | 0           | Recovered clock output                                                                   |

| A7               | RESETn       | I           | Reset<br>0 = Reset<br>1 = Normal                                                         |

#### Table 5: Management Interface

| 88E2110<br>Pin # | Pin Name | Pin<br>Type | Description                                                                                                                                                                                                                                              |

|------------------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G1               | MDC      | I           | Management Clock pin. MDC is the management data clock reference for the serial management interface. A continuous clock stream is not expected. The maximum continuous frequency supported is 12.5 MHz. A 30 MHz non-continuous mode is also supported. |

| F1               | MDIO     | I/O         | Management Data pin. MDIO is the management data. MDIO transfers management data in and out of the device synchronously to MDC. This pin requires a pull-up resistor in a range from 1.5 k $\Omega$ to 10 k $\Omega$ .                                   |

| E2               | INTn     | OD          | Interrupt pin. (Polarity programmable)                                                                                                                                                                                                                   |

#### Table 6: SPI Interface

| 88E2110<br>Pin # | Pin Name | Pin<br>Type | Description       |

|------------------|----------|-------------|-------------------|

| B7               | SPI_SSn  | 0           | SPI device enable |

| B8               | SPI_CLK  | 0           | SPI clock         |

| C7               | SPI_MOSI | 0           | SPI serial out    |

| C8               | SPI_MISO | I           | SPI serial in     |

#### Table 7: GPIO

| 88E2110<br>Pin #     | Pin Name                                 | Pin<br>Type | Description          |

|----------------------|------------------------------------------|-------------|----------------------|

| D8<br>E8             | GPIO[0]<br>GPIO[1]                       | I/O         | General-Purpose I/Os |

| F8<br>F7<br>K8<br>L8 | GPIO[2]<br>GPIO[3]<br>GPIO[4]<br>GPIO[5] | I/O         | General-Purpose I/Os |

#### Table 8: Multi-functional Input/Output

| 88E2180<br>/88E211<br>0<br>Pin # |                                  | Pin<br>Type | Description                                                                      |

|----------------------------------|----------------------------------|-------------|----------------------------------------------------------------------------------|

| G8<br>H8<br>J8                   | MFIOS[2]<br>MFIOS[1]<br>MFIOS[0] | I/O         | MFIOS[2]: output of LED[2] MFIOS[1]: output of LED[1] MFIOS[0]: output of LED[0] |

#### Table 9: Configuration

| 88E2110<br>Pin # | Pin Name                            | Pin<br>Type | Description                                                                                                                                  |

|------------------|-------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| J2<br>K2         | CLK_SEL[0]<br>CLK_SEL[1]            | I, PD       | Reference clock selection $00 = 50 \text{ MHz XTAL1/2}$ $01 = 50 \text{ MHz CLKP/N}$ $10 = 156.25 \text{ MHz CLKP/N}$ $11 = \text{Reserved}$ |

| B6<br>D7<br>C6   | CONFIG[0]<br>CONFIG[1]<br>CONFIG[2] | I           | Hardware Configuration. Refer to Section 3.5.2 for details.                                                                                  |

| H1               | VSEL_M                              | I           | VDDOM Voltage Level Select<br>VSS = 2.5V/3.3V, VDDOM = 1.2V/1.5V/1.8V                                                                        |

| C3               | VSEL_T                              | I           | VDDOT Voltage Level Select<br>VSS = 2.5V/3.3V, VDDOT = 1.5V/1.8V                                                                             |

#### Table 10: JTAG Interface

| 88E2110<br>Pin # | Pin Name | Pin<br>Type | Description                                                                                |

|------------------|----------|-------------|--------------------------------------------------------------------------------------------|

| D1               | TDI      | I, PU       | JTAG Data Input                                                                            |

| E1               | TDO      | 0           | JTAG Data Output                                                                           |

| C2               | TMS      | I, PU       | JTAG Mode Select                                                                           |

| C1               | TCK      | I, PU       | JTAG Clock                                                                                 |

| B1               | TRSTn    | I, PU       | JTAG Reset. TRSTn pin requires a 4.7 k $\Omega$ pull-down externally for normal operation. |

#### Table 11: Test Pins

| 88E2110<br>Pin # | Pin Name         | Pin<br>Type | Description                                       |

|------------------|------------------|-------------|---------------------------------------------------|

| K7<br>J7         | HSDACP<br>HSDACN | 0           | AC Test NOTE: Test purposes only, do not connect. |

| L7               | TSTPT            | 0           | DC Test                                           |

| B2               | TEST             | I, PD       | Test Enable This pin should be left floating.     |

#### Table 12: Power and Ground

| 88E2110<br>Pin #                       | Pin Name | Pin<br>Type | Description                                                                                                       |

|----------------------------------------|----------|-------------|-------------------------------------------------------------------------------------------------------------------|

| E7                                     | AVDDS    | Power       | 1.5V or 1.8V analog power                                                                                         |

| D6                                     | AVDDR    | Power       | 1.5V or 1.8V analog power. Can tie to AVDDS.                                                                      |

| H2                                     | AVDDC    | Power       | 1.5V or 1.8V analog power                                                                                         |

| K4<br>K5                               | AVDDL    | Power       | 1.5V or 1.8V analog power                                                                                         |

| K3<br>L3                               | AVDDH    | Power       | 1.8V analog power                                                                                                 |

| K6<br>L6                               | AVDDT    | Power       | 3.3V analog                                                                                                       |

| F6                                     | VDDR09   | Power       | 0.9V internally regulated power. This pin must be tied to a capacitor. Do not connect this pin to external power. |

| E3<br>E5<br>F3<br>F5<br>G3<br>G4<br>G5 | DVDD     | Power       | Digital power 0.8V core digital power                                                                             |

| H7                                     | VDDOL    | Power       | I/O power - LED, CONFIG, CLK_SEL, TEST, GPIO, MFIOS, SPI, RCLK, RESET                                             |

| G2                                     | VDDOM    | Power       | I/O power - MDC, MDIO, INTn                                                                                       |

| F2                                     | VDDOT    | Power       | I/O power - JTAG                                                                                                  |

Table 12: Power and Ground (Continued)

| 88E2110<br>Pin #                                                                                         | Pin Name | Pin<br>Type | Description                                    |

|----------------------------------------------------------------------------------------------------------|----------|-------------|------------------------------------------------|

| A2<br>A4<br>A6<br>B4<br>C5<br>E6<br>J3<br>J4<br>J5<br>J6<br>L4<br>L5<br>M2<br>M3<br>M6<br>M7<br>N1<br>N8 | AVSS     | Power       | Analog Ground                                  |

| L2                                                                                                       | AVSSC    | Power       | Analog Ground This must be isolated from AVSS. |

| A1<br>A8<br>D3<br>D4<br>D5<br>E4<br>F4<br>G6<br>H3<br>H4<br>H5                                           | VSS      | Power       | Ground                                         |

#### Table 13: Do Not Connect

| 88E2110<br>Pin # | Pin Name | Pin<br>Type   | Description     |

|------------------|----------|---------------|-----------------|

| C4               | DNC      | No<br>Connect | Do not connect. |

### 2.3 Pin Description for the 88E2180 Device

Table 14: Media Dependent Interface

| 88E2180<br>Pin # | Pin Name                 | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC3<br>AB3       | P0_MDIP[0]<br>P0_MDIN[0] | I/O         | Media Dependent Interface[0], Port 0. In 2.5G/5GBASE-T and 1000BASE-T modes in MDI configuration, MDIP/N[0] correspond to BI_DA±. In MDIX configuration, MDIP/N[0] correspond to BI_DB±. In 100BASE-TX and 10BASE-Te modes in MDI configuration, MDIP/N[0] are used for the transmit pair. In MDIX configuration, MDIP/N[0] are used for the receive pair. MDIP/N[0] should be tied to ground if not used. The device contains an internal $100\Omega$ resistor between the MDIP/N[0] pins.      |

| AC4<br>AB4       | P0_MDIP[1]<br>P0_MDIN[1] | I/O         | Media Dependent Interface[1], Port 0. In 2.5G/5GGBASE-T and 1000BASE-T modes in the MDIX configuration, MDIP/N[1] correspond to BI_DA±. In MDI configuration, MDIP/N[1] correspond to BI_DB±. In 100BASE-TX and 10BASE-Te modes in MDIX configuration, MDIP/N[1] are used for the transmit pair. In MDI configuration, MDIP/N[1] are used for the receive pair. MDIP/N[1] should be tied to ground if not used. The device contains an internal $100\Omega$ resistor between the MDIP/N[1] pins. |

| AC5<br>AB5       | P0_MDIP[2]<br>P0_MDIN[2] | I/O         | Media Dependent Interface[2], Port 0. In 2.5G/5GGBASE-T and 1000BASE-T modes in the MDI configuration, MDIP/N[2] correspond to BI_DC±. In MDIX configuration, MDIP/N[2] correspond to BI_DD±. In 100BASE-TX and 10BASE-Te modes these pins are floating. MDIP/N[2] should be tied to ground if not used. The device contains an internal 100Ω resistor between the MDIP/N[2] pins.                                                                                                               |

| AC6<br>AB6       | P0_MDIP[3]<br>P0_MDIN[3] | I/O         | Media Dependent Interface[3], Port 0. In 2.5G/5GBASE-T and 1000BASE-T modes in the MDIX configuration, MDIP/N[3] correspond to BI_DC±. In MDI configuration, MDIP/N[3] correspond to BI_DD±. In 100BASE-TX and 10BASE-Te modes these pins are floating. MDIP/N[3] should be tied to ground if not used. The device contains an internal 100Ω resistor between the MDIP/N[3] pins.                                                                                                                |

| AC11<br>AB11     | P1_MDIP[0]<br>P1_MDIN[0] | I/O         | Media Dependent Interface [0], Port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AC10<br>AB10     | P1_MDIP[1]<br>P1_MDIN[1] | I/O         | Media Dependent Interface [1], Port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AC9<br>AB9       | P1_MDIP[2]<br>P1_MDIN[2] | I/O         | Media Dependent Interface [2], Port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AC8<br>AB8       | P1_MDIP[3]<br>P1_MDIN[3] | I/O         | Media Dependent Interface [3], Port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AC13<br>AB13     | P2_MDIP[0]<br>P2_MDIN[0] | I/O         | Media Dependent Interface [0], Port 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AC14<br>AB14     | P2_MDIP[1]<br>P2_MDIN[1] | I/O         | Media Dependent Interface [1], Port 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 14: Media Dependent Interface (Continued)

| 88E2180<br>Pin # | Pin Name                 | Pin<br>Type | Description                            |

|------------------|--------------------------|-------------|----------------------------------------|

| AC15<br>AB15     | P2_MDIP[2]<br>P2_MDIN[2] | I/O         | Media Dependent Interface [2], Port 2. |

| AC16<br>AB16     | P2_MDIP[3]<br>P2_MDIN[3] | I/O         | Media Dependent Interface [3], Port 2. |

| AC21<br>AB21     | P3_MDIP[0]<br>P3_MDIN[0] | I/O         | Media Dependent Interface [0], Port 3. |

| AC20<br>AB20     | P3_MDIP[1]<br>P3_MDIN[1] | I/O         | Media Dependent Interface [1], Port 3. |

| AC19<br>AB19     | P3_MDIP[2]<br>P3_MDIN[2] | I/O         | Media Dependent Interface [2], Port 3. |

| AC18<br>AB18     | P3_MDIP[3]<br>P3_MDIN[3] | I/O         | Media Dependent Interface [3], Port 3. |

| A21<br>B21       | P4_MDIP[0]<br>P4_MDIN[0] | I/O         | Media Dependent Interface [0], Port 4. |

| A20<br>B20       | P4_MDIP[1]<br>P4_MDIN[1] | I/O         | Media Dependent Interface [1], Port 4. |

| A19<br>B19       | P4_MDIP[2]<br>P4_MDIN[2] | I/O         | Media Dependent Interface [2], Port 4. |

| A18<br>B18       | P4_MDIP[3]<br>P4_MDIN[3] | I/O         | Media Dependent Interface [3], Port 4. |

| A13<br>B13       | P5_MDIP[0]<br>P5_MDIN[0] | I/O         | Media Dependent Interface [0], Port 5. |

| A14<br>B14       | P5_MDIP[1]<br>P5_MDIN[1] | I/O         | Media Dependent Interface [1], Port 5. |

| A15<br>B15       | P5_MDIP[2]<br>P5_MDIN[2] | I/O         | Media Dependent Interface [2], Port 5. |

| A16<br>B16       | P5_MDIP[3]<br>P5_MDIN[3] | I/O         | Media Dependent Interface [3], Port 5. |

| A11<br>B11       | P6_MDIP[0]<br>P6_MDIN[0] | I/O         | Media Dependent Interface [0], Port 6. |

| A10<br>B10       | P6_MDIP[1]<br>P6_MDIN[1] | I/O         | Media Dependent Interface [1], Port 6. |

| A9<br>B9         | P6_MDIP[2]<br>P6_MDIN[2] | I/O         | Media Dependent Interface [2], Port 6. |

| A8<br>B8         | P6_MDIP[3]<br>P6_MDIN[3] | I/O         | Media Dependent Interface [3], Port 6. |

| A3<br>B3         | P7_MDIP[0]<br>P7_MDIN[0] | I/O         | Media Dependent Interface [0], Port 7. |

| A4<br>B4         | P7_MDIP[1]<br>P7_MDIN[1] | I/O         | Media Dependent Interface [1], Port 7. |

| A5<br>B5         | P7_MDIP[2]<br>P7_MDIN[2] | I/O         | Media Dependent Interface [2], Port 7. |

#### Table 14: Media Dependent Interface (Continued)

| 88E2180<br>Pin # | Pin Name                 | Pin<br>Type | Description                            |

|------------------|--------------------------|-------------|----------------------------------------|

| A6<br>B6         | P7_MDIP[3]<br>P7_MDIN[3] | I/O         | Media Dependent Interface [3], Port 7. |

#### Table 15: SERDES Interface

| 88E2180<br>Pin # | Pin Name         | Pin<br>Type | Description                                     |

|------------------|------------------|-------------|-------------------------------------------------|

| R1<br>R2         | P0_SIP<br>P0_SIN | I           | Host SERDES Receive, Positive/Negative, Port 0  |

| R11<br>P11       | P1_SIP<br>P1_SIN | I           | Host SERDES Receive, Positive/Negative, Port 1  |

| R13<br>P13       | P2_SIP<br>P2_SIN | I           | Host SERDES Receive, Positive/Negative, Port 2  |

| R23<br>R22       | P3_SIP<br>P3_SIN | 1           | Host SERDES Receive, Positive/Negative, Port 3  |

| J23<br>J22       | P4_SIP<br>P4_SIN | 1           | Host SERDES Receive, Positive/Negative, Port 4  |

| J13<br>K13       | P5_SIP<br>P5_SIN | 1           | Host SERDES Receive, Positive/Negative, Port 5  |

| J11<br>K11       | P6_SIP<br>P6_SIN | 1           | Host SERDES Receive, Positive/Negative, Port 6  |

| J1<br>J2         | P7_SIP<br>P7_SIN | 1           | Host SERDES Receive, Positive/Negative, Port 7  |

| N1<br>N2         | P0_SOP<br>P0_SON | 0           | Host SERDES Transmit, Positive/Negative, Port 0 |

| U11<br>V11       | P1_SOP<br>P1_SON | 0           | Host SERDES Transmit, Positive/Negative, Port 1 |

| U13<br>V13       | P2_SOP<br>P2_SON | 0           | Host SERDES Transmit, Positive/Negative, Port 2 |

| N23<br>N22       | P3_SOP<br>P3_SON | 0           | Host SERDES Transmit, Positive/Negative, Port 3 |

| L23<br>L22       | P4_SOP<br>P4_SON | 0           | Host SERDES Transmit, Positive/Negative, Port 4 |

| G13<br>F13       | P5_SOP<br>P5_SON | 0           | Host SERDES Transmit, Positive/Negative, Port 5 |

| G11<br>F11       | P6_SOP<br>P6_SON | 0           | Host SERDES Transmit, Positive/Negative, Port 6 |

| L1<br>L2         | P7_SOP<br>P7_SON | 0           | Host SERDES Transmit, Positive/Negative, Port 7 |

Table 16: Clock/Reset/Reference

| 88E2180<br>Pin # | Pin Name     | Pin<br>Type | Description                                                                              |

|------------------|--------------|-------------|------------------------------------------------------------------------------------------|

| U23              | IREF         | I           | Analog Reference. This pin should be connected via a 4.99 k $\Omega$ 1% resistor to VSS. |

| Y1<br>W1         | CLKP<br>CLKN | I           | 156.25 MHz or 50 MHz differential Reference Clock Input.<br>±50 ppm tolerance.           |

| AB1              | XTAL1        | 1           | 50 MHz crystal input                                                                     |

| AA1              | XTAL2        | 0           | 50 MHz crystal output                                                                    |

| E3               | RCLK         | 0           | 25 MHz Recovered clock output                                                            |

| B1               | RESETn       | I           | Reset<br>0 = Reset<br>1 = Normal                                                         |

Table 17: Management Interface

| 88E2180<br>Pin # | Pin Name | Pin<br>Type | Description                                                                                                                                                                                                                                               |

|------------------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U1               | MDC      | I           | Management Clock pin.  MDC is the management data clock reference for the serial management interface. A continuous clock stream is not expected. The maximum continuous frequency supported is 12.5 MHz. A 30 MHz non-continuous mode is also supported. |

| U2               | MDIO     | I/O         | Management Data pin. MDIO is the management data. MDIO transfers management data in and out of the device synchronously to MDC. This pin requires a pull-up resistor in a range from 1.5 k $\Omega$ to 10 k $\Omega$ .                                    |

| Y3               | INTn     | OD          | Interrupt pin. (Polarity programmable)                                                                                                                                                                                                                    |

#### Table 18: SPI Interface

| 88E2180<br>Pin # | Pin Name | Pin<br>Type | Description       |

|------------------|----------|-------------|-------------------|

| F1               | SPI_SSn  | 0           | SPI device enable |

| D1               | SPI_CLK  | 0           | SPI clock         |

| C1               | SPI_MOSI | 0           | SPI serial out    |

| E1               | SPI_MISO | I           | SPI serial in     |

#### Table 19: GPIO

| 88E2180<br>Pin # | Pin Name                 | Pin<br>Type | Description                   |

|------------------|--------------------------|-------------|-------------------------------|

| AB23<br>AB22     | P0_GPIO[0]<br>P0_GPIO[1] | I/O         | General-Purpose I/Os, Port 0. |

| AA23<br>AA22     | P1_GPIO[0]<br>P1_GPIO[1] | I/O         | General-Purpose I/Os, Port 1. |

| Y23<br>W23       | P2_GPIO[0]<br>P2_GPIO[1] | I/O         | General-Purpose I/Os, Port 2. |

| V23<br>U22       | P3_GPIO[0]<br>P3_GPIO[1] | I/O         | General-Purpose I/Os, Port 3. |

| F23<br>G22       | P4_GPIO[0]<br>P4_GPIO[1] | I/O         | General-Purpose I/Os, Port 4. |

| E23<br>E22       | P5_GPIO[0]<br>P5_GPIO[1] | I/O         | General-Purpose I/Os, Port 5. |

| D22<br>D23       | P6_GPIO[0]<br>P6_GPIO[1] | I/O         | General-Purpose I/Os, Port 6. |

| C23<br>C22       | P7_GPIO[0]<br>P7_GPIO[1] | I/O         | General-Purpose I/Os, Port 7. |

#### Table 20: Multi-functional Input/Output

| 88E2180<br>/88E211<br>0<br>Pin # | Pin Name                         | Pin<br>Type | Description                                                                                                                                     |

|----------------------------------|----------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|