# 73S8010R Low Cost Smart Card Interface

Simplifying System Integration™

**DATA SHEET**

DS\_8010R\_022 August 2009

1SO/IEC 7816-3

#### **DESCRIPTION**

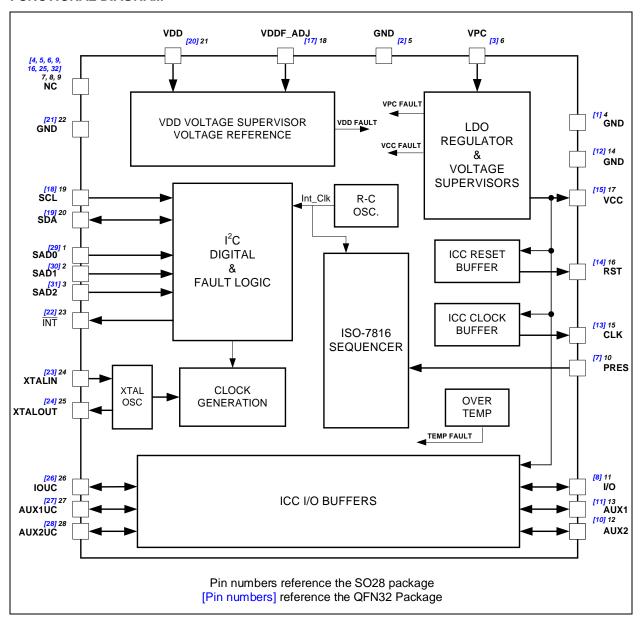

The Teridian 73S8010R is a single smart card interface IC that provides full electrical compliance with ISO-7816-3 and EMV 4.0 (EMV2000) specifications.

Interfacing with the host is done through the two-wire I<sup>2</sup>C bus and one interrupt output to inform the system controller of the card presence and faults. The card clock signal can be generated by an on-chip oscillator using an external crystal, or by connection to a clock signal.

The Teridian 73S8010R incorporates an ISO-7816-3 activation/deactivation sequencer that controls the card signals. Level-shifters drive the card signals with the selected card voltage (3 V or 5 V), coming from an internal Low Drop-Out (LDO) voltage regulator. This LDO regulator is powered by a dedicated power supply input,  $V_{PC}$ . Digital circuitry is separately powered by a digital power supply,  $V_{DD}$ .

With its embedded LDO regulator, the Teridian 73S8010R is a cost-effective solution for any application where a 5 V (typically -5% +10%) power supply is available. Hardware support for auxiliary I/O lines, C4 / C8 contacts is provided.

Emergency card deactivation is initiated upon card extraction or upon any fault generated by the protection circuitry. The fault can be a card over-current, a  $V_{DD}$  (digital power supply), a  $V_{PC}$  (regulator power supply), a  $V_{CC}$  (card power supply) or an over-heating fault.

The card over-current circuitry is a true current detect function, as opposed to  $V_{\rm CC}$  voltage drop detection, as usually implemented in ICC interface ICs.

The  $V_{DD}$  voltage fault has a threshold voltage that can be adjusted with an external resistor or resistor network. It allows automated card deactivation at a customized  $V_{DD}$  voltage threshold value. It can be used, for instance, to match the system controller operating voltage range.

#### **APPLICATIONS**

- Set-Top-Box Conditional Access and Pay-per-View

- Point of Sales & Transaction Terminals

- Control Access & Identification

- Multiple card and SAM reader configurations

#### **ADVANTAGES**

- Single smart card interface

- IC firmware compatible with TDA8020

- Traditional step-up converter is replaced by an LDO regulator

- → Greatly reduced power dissipation

- → Fewer external components are required

- → Better noise performance

- → High current capability (90 mA supplied to the card)

- Small format (5x5x0.8 mm) QFN32 package option

- True card over-current detection

#### **FEATURES**

- Card Interface

- Complies with ISO-7816-3 and EMV 4.0

- An LDO voltage regulator provides 3 V / 5 V to the card from an external power supply input

- ISO-7816-3 Activation / Deactivation sequencer with emergency automated deactivation on card removal or fault detected by the protection circuitry

- Protection includes 3 voltage supervisors that detect voltage drops on V<sub>CC</sub> card and on power supplies V<sub>DD</sub> and V<sub>PC</sub>

- Over-current detection 150 mA max

- 1 card detection input

- Auxiliary I/O lines, for C4 / C8 contact signals

- Host Interface

- Fast mode, 400 kbps I<sup>2</sup>C slave bus

- 8 possible devices in parallel

- One control register and one status register

- Interrupt output to the host for fault detection

- Crystal oscillator or host clock, up to 27 MHz

- 6 kV ESD protection on the card interface

- SO28 or QFN32 package

#### **FUNCTIONAL DIAGRAM**

Figure 1: 73S8010R Block Diagram

# **Table of Contents**

| 1   | Pinc           | out                                                | 5  |

|-----|----------------|----------------------------------------------------|----|

| 2   | Elec           | etrical Specifications                             | 8  |

|     | 2.1            | Absolute Maximum Ratings                           |    |

|     | 2.2            | Recommended Operating Conditions                   |    |

|     | 2.3            | Smart Card Interface Requirements                  |    |

|     | 2.4            | Digital Signals Characteristics                    |    |

|     | 2.5            | DC Characteristics                                 |    |

|     | 2.6            | I <sup>2</sup> C Interface Characteristics         | 12 |

|     | 2.7            | Voltage / Temperature Fault Detection Circuits     | 12 |

| 3   | App            | lications Information                              | 13 |

|     | 3.1            | Example 73S8010R Schematics                        |    |

|     | 3.2            | System Controller Interface (I <sup>2</sup> C Bus) |    |

|     | 3.3            | Power Supply and Voltage Supervision               |    |

|     | 3.4            | Card Power Supply                                  |    |

|     | 3.5            | Over-temperature Monitor                           | 18 |

|     | 3.6            | On-chip Oscillator and Card Clock                  | 18 |

|     | 3.7            | Activation Sequence                                | 19 |

|     | 3.8            | Deactivation Sequence                              | 19 |

|     | 3.9            | Interrupt                                          |    |

|     |                | Warm Reset                                         |    |

|     | 3.11           | I/O Circuitry and Timing                           | 21 |

| 4   | Mec            | hanical Drawings                                   | 22 |

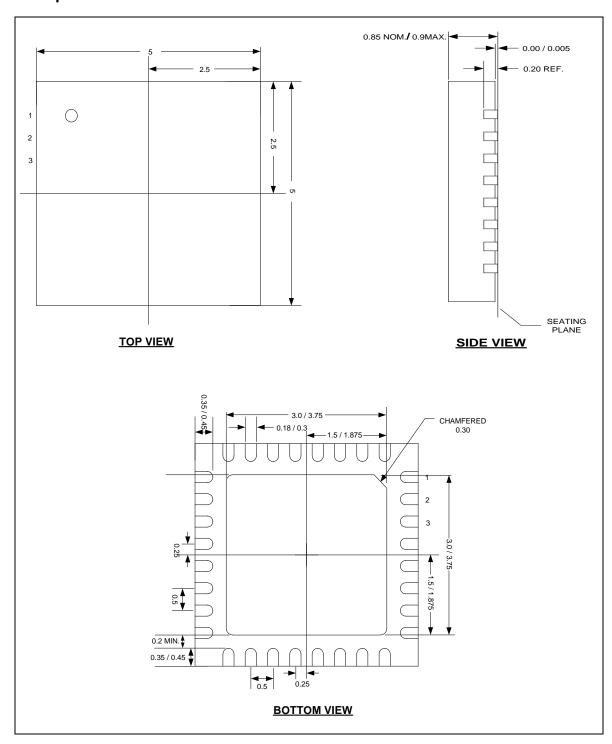

|     | 4.1            | 32-pin QFN                                         | 22 |

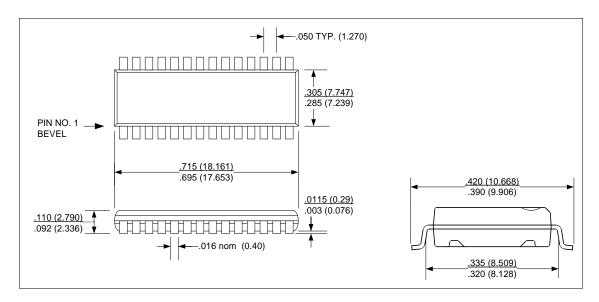

|     | 4.2            | ·                                                  |    |

| 5   | Orde           | ering Information                                  | 24 |

| 6   |                | ated Documentation                                 |    |

| 7   |                | tact Information                                   |    |

| •   |                | History                                            |    |

| VG. | <b>/101011</b> | ⊓וסוטו y                                           | ∠ວ |

# **Figures**

| Figure 1: 73S8010R Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Figure 2: 73S8010R 32-Pin QFN Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

| Figure 3: 73S8010R 28-Pin SO Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                  |

| Figure 4: Typical 73S8010R Application Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13                 |

| Figure 5: I <sup>2</sup> C Bus Write Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15                 |

| Figure 6: 1 <sup>2</sup> C Bus Read Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |

| Figure 7: I <sup>2</sup> C Bus Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                 |

| Figure 8: Activation Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |

| Figure 9: Deactivation Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |

| Figure 10: Interrupt operation due to Fault and Status Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |

| Figure 11: Warm Reset Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |

| Figure 12: I/O Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |

| Figure 13: 32-pin QFN Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |

| Figure 14: 28-Pin SO Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23                 |

| Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |

| Table 1: 73S8010R Pin Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8                  |

| Table 2: Absolute Maximum Device Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88                 |

| Table 2: Absolute Maximum Device Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88<br>8            |

| Table 2: Absolute Maximum Device Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8<br>8<br>9        |

| Table 2: Absolute Maximum Device Ratings Table 3: Recommended Operating Conditions Table 4: DC Smart Card Interface Requirements Table 5: Digital Signals Characteristics Table 6: DC Characteristics                                                                                                                                                                                                                                                                                                                                  | 8<br>9<br>11<br>11 |

| Table 2: Absolute Maximum Device Ratings Table 3: Recommended Operating Conditions Table 4: DC Smart Card Interface Requirements Table 5: Digital Signals Characteristics Table 6: DC Characteristics Table 7: I <sup>2</sup> C Characteristics                                                                                                                                                                                                                                                                                        | 8<br>11<br>11      |

| Table 2: Absolute Maximum Device Ratings Table 3: Recommended Operating Conditions Table 4: DC Smart Card Interface Requirements Table 5: Digital Signals Characteristics Table 6: DC Characteristics Table 7: I <sup>2</sup> C Characteristics Table 8: Voltage / Temperature Fault Detection Circuits                                                                                                                                                                                                                                | 81112              |

| Table 2: Absolute Maximum Device Ratings Table 3: Recommended Operating Conditions Table 4: DC Smart Card Interface Requirements Table 5: Digital Signals Characteristics Table 6: DC Characteristics Table 7: I <sup>2</sup> C Characteristics Table 8: Voltage / Temperature Fault Detection Circuits. Table 9: Device Address Selection                                                                                                                                                                                             | 8111212            |

| Table 2: Absolute Maximum Device Ratings Table 3: Recommended Operating Conditions Table 4: DC Smart Card Interface Requirements Table 5: Digital Signals Characteristics Table 6: DC Characteristics Table 7: I <sup>2</sup> C Characteristics Table 8: Voltage / Temperature Fault Detection Circuits Table 9: Device Address Selection Table 10: Control Register Description                                                                                                                                                       | 811121214          |

| Table 2: Absolute Maximum Device Ratings Table 3: Recommended Operating Conditions Table 4: DC Smart Card Interface Requirements Table 5: Digital Signals Characteristics Table 6: DC Characteristics Table 7: I <sup>2</sup> C Characteristics Table 8: Voltage / Temperature Fault Detection Circuits Table 9: Device Address Selection Table 10: Control Register Description Table 11: Card Clock Rate Selection                                                                                                                   | 811121214          |

| Table 2: Absolute Maximum Device Ratings Table 3: Recommended Operating Conditions Table 4: DC Smart Card Interface Requirements Table 5: Digital Signals Characteristics Table 6: DC Characteristics Table 7: I <sup>2</sup> C Characteristics Table 8: Voltage / Temperature Fault Detection Circuits Table 9: Device Address Selection Table 10: Control Register Description Table 11: Card Clock Rate Selection Table 12: Status Register Description                                                                             |                    |

| Table 2: Absolute Maximum Device Ratings Table 3: Recommended Operating Conditions Table 4: DC Smart Card Interface Requirements Table 5: Digital Signals Characteristics Table 6: DC Characteristics Table 7: I <sup>2</sup> C Characteristics Table 8: Voltage / Temperature Fault Detection Circuits. Table 9: Device Address Selection Table 10: Control Register Description Table 11: Card Clock Rate Selection Table 12: Status Register Description Table 13: I2C Bus Timing Parameters                                        |                    |

| Table 2: Absolute Maximum Device Ratings Table 3: Recommended Operating Conditions Table 4: DC Smart Card Interface Requirements Table 5: Digital Signals Characteristics Table 6: DC Characteristics Table 7: I <sup>2</sup> C Characteristics Table 8: Voltage / Temperature Fault Detection Circuits Table 9: Device Address Selection Table 10: Control Register Description Table 11: Card Clock Rate Selection Table 12: Status Register Description                                                                             |                    |

| Table 2: Absolute Maximum Device Ratings Table 3: Recommended Operating Conditions Table 4: DC Smart Card Interface Requirements Table 5: Digital Signals Characteristics Table 6: DC Characteristics Table 7: I <sup>2</sup> C Characteristics Table 8: Voltage / Temperature Fault Detection Circuits. Table 9: Device Address Selection Table 10: Control Register Description. Table 11: Card Clock Rate Selection Table 12: Status Register Description Table 13: I2C Bus Timing Parameters Table 14: Choice of VCC Pin Capacitor |                    |

DS\_8010R\_022 73S8010R Data Sheet

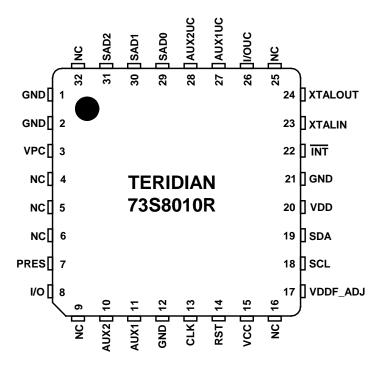

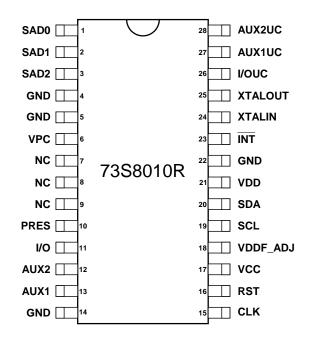

## 1 Pinout

The 73S8010R is supplied as a 32-pin QFN package and as a 28-pin SO package.

Figure 2: 73S8010R 32-Pin QFN Pinout

Figure 3: 73S8010R 28-Pin SO Pinout

Table 1 describes the pin functions for the device.

Table 1: 73S8010R Pin Definitions

| Pin<br>Name    | Pin<br>(SO28) | Pin<br>(QFN32)       | Туре | Description                                                                                                                                                              |

|----------------|---------------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Card Interface | e             |                      |      |                                                                                                                                                                          |

| I/O            | 11            | 8                    | Ю    | Card I/O: Data signal to/from card. Includes a pull-up resistor to $V_{\text{CC.}}$                                                                                      |

| AUX1           | 13            | 11                   | Ю    | AUX1: Auxiliary data signal to/from card. Includes a pull-up resistor to V <sub>CC</sub> .                                                                               |

| AUX2           | 12            | 10                   | Ю    | AUX2: Auxiliary data signal to/from card. Includes a pull-up resistor to V <sub>CC</sub> .                                                                               |

| RST            | 16            | 14                   | 0    | Card reset: provides reset (RST) signal to card.                                                                                                                         |

| CLK            | 15            | 13                   | 0    | Card clock: provides clock signal (CLK) to card. The crystal oscillator frequency and CLKSEL bits in the control register determine the rate of this clock.              |

| PRES           | 10            | 7                    | I    | Card Presence switch: active high indicates card is present. Includes a pull-down resistor.                                                                              |

| VCC            | 17            | 15                   | PSO  | Card power supply – logically controlled by the sequencer, output of LDO regulator. Requires an external filter capacitor to GND.                                        |

| GND            | 14            | 12                   | GND  | Card ground.                                                                                                                                                             |

| Miscellaneou   | s Inputs and  | Outputs              |      |                                                                                                                                                                          |

| XTALIN         | 24            | 23                   | I    | Crystal oscillator input: can be connected to crystal or driven as a source for the card clock.                                                                          |

| XTALOUT        | 25            | 24                   | 0    | Crystal oscillator output: connected to crystal. Left open if XTALIN is being used as an external clock input.                                                           |

| VDDF_ADJ       | 18            | 17                   | I    | V <sub>DD</sub> threshold adjustment input: this pin can be used to overwrite a higher VDDF value (that controls deactivation of the card). Must be left open if unused. |

| NC             | 7, 8, 9       | 4,5,6,9,<br>16,25,32 | -    | Non-connected pin.                                                                                                                                                       |

| Power Supply   | and Ground    |                      |      |                                                                                                                                                                          |

| VDD            | 21            | 20                   |      | System interface supply voltage and supply voltage for internal circuitry.                                                                                               |

| VPC            | 6             | 3                    |      | LDO regulator power supply source.                                                                                                                                       |

| GND            | 4             | 1                    | GND  | LDO regulator ground.                                                                                                                                                    |

| GND            | 14            | 12                   | GND  | Smart card I/O ground.                                                                                                                                                   |

| GND            | 5, 22         | 2,21                 | GND  | Digital ground.                                                                                                                                                          |

DS\_8010R\_022 73S8010R Data Sheet

| Pin<br>Name  | Pin<br>(SO28) | Pin<br>(QFN32) | Туре | Description                                                                                                       |            |            |                                     |       |  |  |

|--------------|---------------|----------------|------|-------------------------------------------------------------------------------------------------------------------|------------|------------|-------------------------------------|-------|--|--|

| Microcontrol | ler Interface | 1              |      |                                                                                                                   |            |            |                                     |       |  |  |

| ĪNT          | 23            | 22             | 0    | Interrupt output processor. A 2 internally.                                                                       |            |            |                                     | е     |  |  |

| SAD0         | 1             | 29             | 1    | Serial device a                                                                                                   |            |            |                                     |       |  |  |

| SAD1         | 2             | 30             | 1    | selection that a                                                                                                  |            |            |                                     |       |  |  |

| SAD2         | 3             | 31             | 1    | devices in para                                                                                                   | allel. Add | dress sele | ctions is as fol                    | lows: |  |  |

|              |               |                |      | SAD2                                                                                                              | SAD1       | SAD0       | (7 bit) I <sup>2</sup> C<br>Address |       |  |  |

|              |               |                |      | 0                                                                                                                 | 0          | 0          | 0x40                                |       |  |  |

|              |               |                |      | 0                                                                                                                 | 0          | 1          | 0x42                                |       |  |  |

|              |               |                |      | 0                                                                                                                 | 1          | 0          | 0x44                                |       |  |  |

|              |               |                |      | 0                                                                                                                 | 1          | 1          | 0x46                                |       |  |  |

|              |               |                |      | 1                                                                                                                 | 0          | 0          | 0x48                                |       |  |  |

|              |               |                |      | 1                                                                                                                 | 0          | 1          | 0x4A                                |       |  |  |

|              |               |                |      | 1                                                                                                                 | 1          | 0          | 0x4C                                |       |  |  |

|              |               |                |      | 1                                                                                                                 | 1          | 1          | 0x4E                                |       |  |  |

|              |               |                |      | Pins SAD0 and SAD2 is intern when unconne                                                                         | ally pulle | d up. The  |                                     |       |  |  |

| SCL          | 19            | 18             | I    | I <sup>2</sup> C clock signa                                                                                      | al input.  |            |                                     |       |  |  |

| SDA          | 20            | 19             | I/O  | I <sup>2</sup> C bi-direction                                                                                     | al serial  | data signa | al.                                 |       |  |  |

| I/OUC        | 26            | 26             | Ю    | System contro<br>an internal pul                                                                                  |            |            |                                     | ludes |  |  |

| AUX1UC       | 27            | 27             | Ю    | System controller auxiliary data I/O to/from the card. Includes an internal pull-up resistor to V <sub>DD</sub> . |            |            |                                     |       |  |  |

| AUX2UC       | 28            | 28             | Ю    | System control Includes an int                                                                                    |            |            |                                     | ard.  |  |  |

## 2 Electrical Specifications

This section provides the following:

- Absolute Maximum Ratings

- Recommended Operating Conditions

- Smart Card Interface Requirements

- Digital Signals Characteristics

- DC Characteristics

- I2C Interface Characteristics

- Voltage / Temperature Fault Detection Circuits

## 2.1 Absolute Maximum Ratings

Table 2 lists the maximum operating conditions for the 73S8010R. Permanent device damage may occur if absolute maximum ratings are exceeded. Exposure to the extremes of the absolute maximum rating for extended periods may affect device reliability.

**Parameter** Rating Supply voltage V<sub>DD</sub> -0.5 to 6.0 VDC Supply voltage V<sub>PC</sub> -0.5 to 6.0 VDC Input voltage for digital inputs -0.3 to (V<sub>DD</sub> +0.5) VDC -60 °C to +150 °C Storage temperature Pin voltage (except card interface) -0.3 to  $(V_{DD} + 0.5)$  VDC Pin voltage (card interface) -0.3 to (V<sub>CC</sub> + 0.5) VDC ESD tolerance - Card interface pins +/- 6 kV

+/- 2 kV

**Table 2: Absolute Maximum Device Ratings**

Note: ESD testing on smart card pins is HBM condition, 3 pulses, each polarity referenced to ground.

## 2.2 Recommended Operating Conditions

ESD tolerance - Other pins

Function operation should be restricted to the recommended operating conditions specified in Table 3.

**Table 3: Recommended Operating Conditions**

| Parameter                        | Rating                           |

|----------------------------------|----------------------------------|

| Supply voltage V <sub>DD</sub>   | 2.7 to 5.5 VDC                   |

| Supply voltage V <sub>PC</sub>   | 4.75 to 5.5 VDC                  |

| Ambient operating temperature    | -40 °C to +85 °C                 |

| Input voltage for digital inputs | 0 V to V <sub>DD</sub> to +0.3 V |

DS\_8010R\_022 73S8010R Data Sheet

## 2.3 Smart Card Interface Requirements

Table 4 lists the 73S8010R Smart Card interface requirements.

**Table 4: DC Smart Card Interface Requirements**

| Symbol             | Parameter                                                              | Condition                                                                                   | Min                    | Nom  | Max  | Unit     |

|--------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------|------|------|----------|

|                    | wer Supply (V <sub>cc</sub> ) Regulator<br>Conditions: -40 °C < T < 85 | 5 °C, 4.75 V < V <sub>PC</sub> < 5.5 V, 2.7 V                                               | < V <sub>DD</sub> < 5. | 5 V  |      | 1        |

|                    |                                                                        | Inactive mode                                                                               | -0.1                   | _    | 0.1  | V        |

|                    |                                                                        | Inactive mode I <sub>CC</sub> = 1 mA                                                        | -0.1                   | _    | 0.4  | V        |

|                    |                                                                        | Active mode; I <sub>CC</sub> < 65 mA; 5 V                                                   | 4.60                   | _    | 5.25 | V        |

|                    |                                                                        | Active mode; I <sub>CC</sub> < 90 mA; 5 V                                                   | 4.55                   | _    |      | V        |

|                    |                                                                        | Active mode; I <sub>CC</sub> < 90 mA; 3 V                                                   | 2.80                   | _    | 3.2  | V        |

| $V_{cc}$           | Card supply voltage including ripple and                               | Active mode; single pulse of 100 mA for 2 μs; 5 V, fixed load = 25 mA                       | 4.6                    | -    | 5.25 | V        |

| v cc               | noise                                                                  | Active mode; single pulse of 100 mA for 2 µs; 3 V, fixed load = 25 mA                       | 2.76                   | _    | 3.2  | ٧        |

|                    |                                                                        | Active mode; current pulses of 40 nAs with peak $ I_{CC} $ < 200 mA, t < 400 ns; 5 V        | 4.6                    | _    | 5.25 | <b>V</b> |

|                    |                                                                        | Active mode; current pulses of 40 nAs with peak  I <sub>CC</sub>   < 200 mA, t <400 ns; 3 V | 2.76                   | _    | 3.2  | V        |

| I <sub>CCmax</sub> | Maximum supply current to the card                                     | Static load current, V <sub>CC</sub> >4.6 or 2.7 volts as selected                          | 90                     | _    | _    | mA       |

| I <sub>CCF</sub>   | I <sub>CC</sub> fault current                                          |                                                                                             | 100                    | _    | 150  | mA       |

| $V_{SR}$           | Vcc slew rate, rise rate on activate                                   | $C_F = 3.3 \ \mu F$ on $V_{CC}$                                                             | 0.02                   | 0.05 | 0.08 | V/µs     |

| V <sub>SF</sub>    | Vcc slew rate, fall rate on de-activate                                | $C_F$ = 3.3 $\mu F$ on $V_{CC}$                                                             | 0.025                  | 0.06 | 0.08 | V/µs     |

| C <sub>F</sub>     | External filter capacitor (V <sub>CC</sub> to GND)                     |                                                                                             | 1                      | 3.3  | 5    | μF       |

| Symbol                            | Parameter                                                                                                     | Condition                                                                                                                       | Min                    | Nom | Max                   | Unit |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----------------------|------|

|                                   |                                                                                                               | nals: I/O, AUX1, AUX2, an<br>requirements do not per                                                                            |                        |     |                       |      |

| V <sub>OH</sub>                   | Output level, high (I/O,                                                                                      | I <sub>OH</sub> = 0 μA                                                                                                          | 0.9 * V <sub>CC</sub>  | _   | V <sub>CC</sub> +0.1  | V    |

|                                   | AUX1, AUX2)                                                                                                   | I <sub>OH</sub> = -40 μA                                                                                                        | 0.75 * V <sub>CC</sub> | ı   | V <sub>CC</sub> +0.1  | V    |

| V <sub>OH</sub>                   | Output level, high                                                                                            | I <sub>OH</sub> = 0 μA                                                                                                          | 0.9 * V <sub>CC</sub>  | ı   | V <sub>DD</sub> +0.1  | V    |

|                                   | (I/OUC, AUX1UC,<br>AUX2UC)                                                                                    | I <sub>OH</sub> = -40 μA                                                                                                        | 0.75 * V <sub>CC</sub> | -   | V <sub>DD</sub> +0.1  | V    |

| V <sub>OL</sub>                   | Output level, low                                                                                             | I <sub>OL</sub> = 1 mA                                                                                                          | _                      | ı   | 0.3                   | V    |

| V <sub>IH</sub>                   | Input level, high (I/O, AUX1, AUX2)                                                                           |                                                                                                                                 | 1.8                    | _   | V <sub>CC</sub> +0.30 | V    |

| V <sub>IH</sub>                   | Input level, high (I/OUC, AUX1UC, AUX2UC)                                                                     |                                                                                                                                 | 1.8                    | _   | V <sub>CC</sub> +0.30 | V    |

| V <sub>IL</sub>                   | Input level, low                                                                                              |                                                                                                                                 | -0.3                   | ı   | 0.8                   | V    |

| V <sub>INACT</sub>                | Output voltage when                                                                                           | I <sub>OL</sub> = 0                                                                                                             | _                      | -   | 0.1                   | V    |

|                                   | outside of session                                                                                            | I <sub>OL</sub> = 1 mA                                                                                                          | _                      | -   | 0.3                   | V    |

| I <sub>LEAK</sub>                 | Input leakage                                                                                                 | $V_{IH} = V_{CC}$                                                                                                               | _                      | _   | 10                    | μΑ   |

| I <sub>IL</sub>                   | Input current, low                                                                                            | V <sub>IL</sub> = 0                                                                                                             | _                      | 1   | 0.65                  | mA   |

| I <sub>SHORTL</sub>               | Short circuit output current                                                                                  | For output low, shorted to $V_{\text{CC}}$ through 33 $\Omega$                                                                  | _                      | _   | 15                    | mA   |

| I <sub>SHORTH</sub>               | Short circuit output current                                                                                  | For output high, shorted to ground through 33 $\Omega$                                                                          | _                      | -   | 15                    | mA   |

| t <sub>R</sub> , t <sub>F</sub>   | Output rise time, fall time                                                                                   | For I/O, AUX1, AUX2,<br>$C_L = 80 \text{ pF}, 10\% \text{ to } 90\%.$<br>For I/OUC, AUX1UC,<br>AUX2UC, CL=50 pF,<br>10% to 90%. | -                      | -   | 100                   | ns   |

| t <sub>IR</sub> , t <sub>IF</sub> | Input rise, fall times                                                                                        |                                                                                                                                 | _                      | ı   | 1                     | μS   |

| R <sub>PU</sub>                   | Internal pull-up resistor                                                                                     | Output stable for >200 ns                                                                                                       | 8                      | 11  | 14                    | kΩ   |

| $FD_MAX$                          | Maximum data rate                                                                                             |                                                                                                                                 | _                      | _   | 1                     | MHz  |

| T <sub>FDIO</sub>                 | Delay, I/O to I/OUC,<br>I/OUC to I/O, AUX1 to<br>AUX1UC, AUX1UC to<br>AUX1, AUX2 to AUX2UC,<br>AUX2UC to AUX2 | Falling edge from master<br>to slave measured at<br>50% point                                                                   | 60                     | 100 | 200                   | ns   |

| $T_{RDIO}$                        | Delay, I/O to I/OUC,<br>I/OUC to I/O, AUX1 to<br>AUX1UC, AUX1UC to<br>AUX1, AUX2 to AUX2UC,<br>AUX2UC to AUX2 | Rising edge from master<br>to slave measured at<br>50% point                                                                    | -                      | 25  | 90                    | ns   |

| C <sub>IN</sub>                   | Input capacitance                                                                                             |                                                                                                                                 | _                      | _   | 10                    | pF   |

DS\_8010R\_022 73S8010R Data Sheet

| Symbol                          | Parameter                                    | Condition                                         | Min                   | Nom | Max             | Unit |  |  |  |

|---------------------------------|----------------------------------------------|---------------------------------------------------|-----------------------|-----|-----------------|------|--|--|--|

| Reset a                         | Reset and Clock for card interface, RST, CLK |                                                   |                       |     |                 |      |  |  |  |

| V <sub>OH</sub>                 | Output level, high                           | I <sub>OH</sub> = -200 μA                         | 0.9 * V <sub>CC</sub> | _   | V <sub>CC</sub> | V    |  |  |  |

| V <sub>OL</sub>                 | Output level, low                            | I <sub>OL</sub> = 200 μA                          | 0                     | -   | 0.3             | V    |  |  |  |

| V <sub>INACT</sub>              | Output voltage when                          | I <sub>OL</sub> = 0                               | -                     | _   | 0.1             | V    |  |  |  |

|                                 | outside of session                           | $I_{OL} = 1 \text{ mA}$                           | _                     | _   | 0.3             | V    |  |  |  |

| I <sub>RST_LIM</sub>            | Output current limit, RST                    |                                                   | _                     | _   | 30              | mA   |  |  |  |

| I <sub>CLK_LIM</sub>            | Output current limit, CLK                    |                                                   | _                     | _   | 70              | mA   |  |  |  |

| t <sub>R</sub> , t <sub>F</sub> | Output rise time, fall time                  | $C_L = 35 \text{ pF for CLK},$ 10% to 90%         | _                     | _   | 8               | ns   |  |  |  |

|                                 |                                              | C <sub>L</sub> = 200 pF for RST,<br>10% to 90%    | _                     | _   | 100             | ns   |  |  |  |

| δ                               | Duty cycle for CLK                           | $C_L = 35 \text{ pF}, F_{CLK} \leq 20 \text{MHz}$ | 45                    | _   | 55              | %    |  |  |  |

## 2.4 Digital Signals Characteristics

Table 5 lists the 73S8010R digital signals characteristics.

**Table 5: Digital Signals Characteristics**

| Symbol              | Parameter                   | Condition               | Min                   | Nom | Max                  | Unit |

|---------------------|-----------------------------|-------------------------|-----------------------|-----|----------------------|------|

| Digital I/C         | Dexcept for OSC I/O         | 1                       |                       | 1.  |                      |      |

| V <sub>IL</sub>     | Input low voltage           |                         | -0.3                  | _   | 0.8                  | V    |

| V <sub>IH</sub>     | Input high voltage          |                         | 0.7 * V <sub>DD</sub> | _   | V <sub>DD</sub> +0.3 | V    |

| V <sub>OL</sub>     | Output low voltage          | I <sub>OL</sub> = 2 mA  |                       | _   | 0.45                 | V    |

| V <sub>OH</sub>     | Output high voltage         | I <sub>OH</sub> = -1 mA | V <sub>DD</sub> -0.45 | _   |                      | V    |

| R <sub>OUT</sub>    | Pull-up resistor; INT       |                         | _                     | 20  | _                    | kΩ   |

| $ I_{IL1} $         | Input leakage current       | $GND < V_{IN} < V_{DD}$ | -5                    | _   | 5                    | μA   |

| Oscillato           | r (XTALIN) I/O              |                         | 1                     |     |                      |      |

| $V_{ILXTAL}$        | Input low voltage - XTALIN  |                         | -0.3                  | -   | 0.5                  | V    |

| V <sub>IHXTAL</sub> | Input high voltage - XTALIN |                         | 0.7*V <sub>DD</sub>   | _   | V <sub>DD</sub> +0.3 | V    |

| I <sub>ILXTAL</sub> | Input current - XTALIN      | $GND < V_{IN} < V_{DD}$ | -30                   | _   | 30                   | μA   |

## 2.5 DC Characteristics

Table 6 lists the DC characteristics.

**Table 6: DC Characteristics**

| Symbol          | Parameter                         | Condition                                           | Min | Nom  | Max  | Unit |

|-----------------|-----------------------------------|-----------------------------------------------------|-----|------|------|------|

| $I_{DD}$        | Supply current on V <sub>DD</sub> |                                                     | _   | 1.5  | 3.0  | mA   |

| I <sub>PC</sub> | Supply current on V <sub>PC</sub> | $V_{CC}$ on, $I_{CC} = 0$<br>I/O, AUX1, AUX2 = high | _   | 0.45 | 0.65 | mA   |

# 2.6 I<sup>2</sup>C Interface Characteristics

Table 7 lists the I<sup>2</sup>C Interface characteristics.

**Table 7: I<sup>2</sup>C Characteristics**

| Symbol          | Parameter                                 | Condition                                           | Min                     | Nom | Max                   | Unit |

|-----------------|-------------------------------------------|-----------------------------------------------------|-------------------------|-----|-----------------------|------|

| V <sub>IL</sub> | Input low voltage                         |                                                     | -0.3                    | _   | 0.3 * V <sub>DD</sub> | V    |

| V <sub>IH</sub> | Input high voltage                        |                                                     | 0.7 * V <sub>DD</sub>   | 1   | V <sub>DD</sub> +0.3  | V    |

| V <sub>OL</sub> | Output low voltage                        | I <sub>OL</sub> = 3 mA                              | _                       | 1   | 0.40                  | V    |

| C <sub>IN</sub> | Pin capacitance                           |                                                     | _                       | -   | 10                    | pF   |

| I <sub>IN</sub> | Output high voltage                       | $I_{OH} = -1 \text{ mA}$                            | V <sub>DD</sub> - 0.45  | -   |                       | V    |

| T <sub>F</sub>  | Output fall time                          | C <sub>L</sub> = 0 to 400 pF                        | 20 + 0.1*C <sub>L</sub> | -   | 250                   | ns   |

| T <sub>SP</sub> | Pulse width of spikes that are suppressed | Transition from valid logic level to opposite level | -                       | _   | 50                    | ns   |

# 2.7 Voltage / Temperature Fault Detection Circuits

Table 8 lists the voltage / temperature fault detection circuits.

**Table 8: Voltage / Temperature Fault Detection Circuits**

| Symbol           | Parameter                                                               | Condition                                             | Min  | Nom                   | Max  | Unit     |

|------------------|-------------------------------------------------------------------------|-------------------------------------------------------|------|-----------------------|------|----------|

| $V_{DDF}$        | V <sub>P</sub> over-current fault                                       | No external resistor on VDDF_ADJ pin                  | 2.15 | -                     | 2.4  | <b>\</b> |

| V <sub>PCF</sub> | V <sub>PC</sub> fault (V <sub>PC</sub> Voltage<br>Supervisor threshold) | V <sub>PC</sub> < V <sub>CC</sub> , a transient event | _    | V <sub>CC</sub> - 0.2 | -    | V        |

| $V_{CCF}$        | V <sub>CC</sub> fault (V <sub>CC</sub> Voltage                          | $V_{CC} = 5 \text{ V}$                                | 4.20 | _                     | 4.55 | ٧        |

|                  | Supervisor threshold)                                                   | $V_{CC} = 3 V$                                        | 2.5  | -                     | 2.7  | ٧        |

| T <sub>F</sub>   | Die over temperature fault                                              |                                                       | 115  | _                     | 145  | °C       |

## 3 Applications Information

This section provides general usage information for the design and implementation of the 73S8010R.

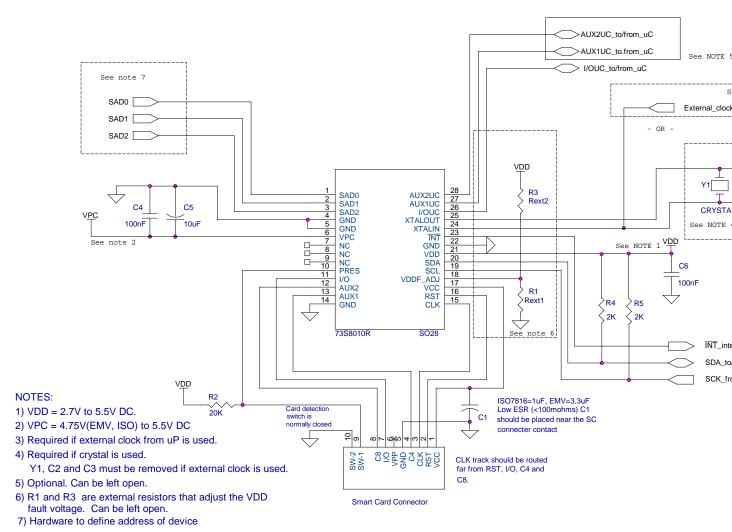

#### 3.1 Example 73\$8010R Schematics

Figure 4 shows a typical application schematic for the implementation of the 73S8010R. Note that minor changes may occurate and the reader is encouraged to contact Teridian for the latest information

Figure 4: Typical 73S8010R Application Schematic

# 3.2 System Controller Interface (I<sup>2</sup>C Bus)

A fast-mode 400 kHz I<sup>2</sup>C bus slave interface is used for controlling the 73S8010R device and reading the status of the device via the data pin SDA and clock pin SCL. The bus has 3 address select pins, SAD0, SAD1, and SAD2. This allows up to 8 devices to be connected in parallel. Table 9 lists the device address selections for the SAD2:0 settings.

**Table 9: Device Address Selection**

| SAD2 | SAD1 | SAD0 | (7 bit) I <sup>2</sup> C<br>Address |

|------|------|------|-------------------------------------|

| 0    | 0    | 0    | 0x40                                |

| 0    | 0    | 1    | 0x42                                |

| 0    | 1    | 0    | 0x44                                |

| 0    | 1    | 1    | 0x46                                |

| 1    | 0    | 0    | 0x48                                |

| 1    | 0    | 1    | 0x4A                                |

| 1    | 1    | 0    | 0x4C                                |

| 1    | 1    | 1    | 0x4E                                |

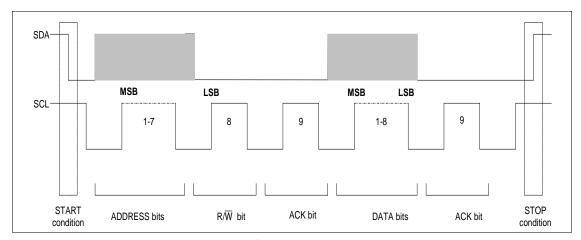

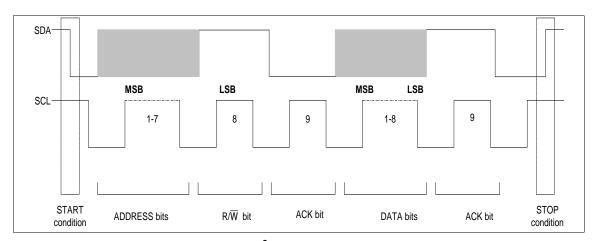

Bit 0 of the I<sup>2</sup>C address is the R/W bit. Refer to Figure 5 and Figure 6 for usage.

Table 10 describes the Control Register Bits.

Table 10: Control Register Description Power-on-reset value = 0x00

| Name             | Bit | Description                                                                                                                                                                    |  |

|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Start/Stop       | 0   | When set, initiates an activation and a cold reset procedure; when reset, initiates a deactivation sequence.                                                                   |  |

| Warm reset       | 1   | When set, initiates a warm reset procedure; automatically reset by hardware when the card starts answering or when the card is declared mute.                                  |  |

| 5 V and 3 V      | 2   | When set, $V_{CC} = 3$ V; when reset, $V_{CC} = 5$ V. When de-activating (setting bit $0 = 0$ ) and operating with 3 V (bit $2 = 1$ ), do not simultaneously set bit $2 = 0$ . |  |

| Clock Stop       | 3   | When set, the card clock is stopped. Bit 4 determines the card clock stop level.                                                                                               |  |

| Clock Stop Level | 4   | When set, card clock stops high; when reset card clock stops low.                                                                                                              |  |

| Clksel1          | 5   | Bits 5 and 6 determine the clock rate to the card. See Table 11 for more                                                                                                       |  |

| Clksel2          | 6   | details.                                                                                                                                                                       |  |

| I/O enable       | 7   | I/O enable bit. When set, I/O is transferred on I/OUC; when reset I/O to I/OUC is high impedance.                                                                              |  |

**Table 11: Card Clock Rate Selection**

| Bit Clksel2 | Bit Clksel1 | Card Clock     |

|-------------|-------------|----------------|

| 0           | 0           | Clkin/8        |

| 0           | 1           | Clkin/4        |

| 1           | 0           | Clkin/2        |

| 1           | 1           | Clkin (Xtalin) |

DS 8010R 022 73S8010R Data Sheet

#### I<sup>2</sup>C-bus Write to Control Register

The  $I^2$ C-bus Write command to the control register follows the format shown in Figure 5. After the START condition, the master sends a slave address. This address is seven bits long followed by an eighth bit which is an opcode bit (R/W) – a 'zero' indicates the master will write data to the control register. After the R/W bit, the 'zero' ACK bit is sent to the master by the device. The master now starts sending the 8 bits of data to the control register during the DATA bits. After the DATA bits, the 'zero' ACK bit is sent to the master by the device. The master should send the STOP condition after receiving this ACK bit.

Figure 5: I<sup>2</sup>C Bus Write Protocol

Table 12 describes the Status Register bits.

Table 12: Status Register Description Power On Reset = 0x04

| Name   | Bit | Description                                                                                                                                                 |

|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRES   | 0   | Set when the card is present (pin PRES is high); reset when the card is not present.                                                                        |

| PRESL  | 1   | Set when the PRES pin changes state (rising/falling edge); reset when the status register is read. Generates an interrupt when set.                         |

| I/O    | 2   | Set when I/O is high; reset when I/O is low.                                                                                                                |

| SUPL   | 3   | Set when a voltage fault is detected; reset when the status register is read. Generates an interrupt when set.                                              |

| PROT   | 4   | Set when an over-current or over-heating fault has occurred during a card session; reset when the status register is read. Generates an interrupt when set. |

| MUTE   | 5   | Set during ATR when the card has not answered during the ISO 7816-3 time window (40000 card clock cycles); reset when the next session begins.              |

| EARLY  | 6   | Set during ATR when the card has answered before 400 card clock cycles; reset when the next session begins.                                                 |

| ACTIVE | 7   | Set when the card is active (V <sub>CC</sub> is on); reset when the card is inactive.                                                                       |

## I<sup>2</sup>C-bus Read from Status Register

The I<sup>2</sup>C-bus Read Command from the Status Register follows the format shown in Figure 6. After the START condition, the master sends a slave address. This address is seven bits long followed by an eighth bit which is an opcode bit (R/W) – a 'one' indicates the master will read data from the status register. After the R/W bit, the 'zero' ACK bit is sent to the master by the device. The device now starts sending the 8-bit status register data to the control register during the DATA bits. After the DATA bits, the 'one' ACK bit is sent to the device by the master. The master should send the STOP condition after receiving the ACK bit.

Figure 6: I<sup>2</sup>C Bus Read Protocol

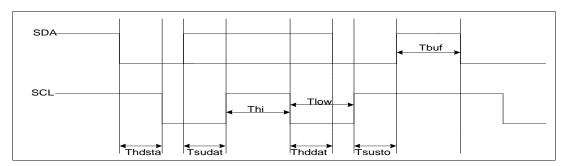

Figure 7: I<sup>2</sup>C Bus Timing Diagram

**Table 13: I2C Bus Timing Parameters**

| Symbol | Parameter                                        | Min. | Тур. | Max. | Unit |

|--------|--------------------------------------------------|------|------|------|------|

| Fsclk  | Clock frequency                                  | _    | _    | 400  | kHz  |

| Tlow   | Clock low                                        | 1.3  | _    | _    | μS   |

| Thi    | Clock high                                       | 0.6  | _    | _    | μS   |

| Thdsta | Hold time START condition                        | 0.6  | _    | _    | μS   |

| Tsudat | Data setup time                                  | 100  | -    | -    | ns   |

| Thddat | Data hold time                                   | 5    | _    | 900  | ns   |

| Tsusto | Set up time STOP condition                       | 0.6  | _    | _    | μS   |

| Tbuf   | Bus free time between a STOP and START condition | 1.3  | _    | _    | μS   |

DS 8010R 022 73S8010R Data Sheet

#### 3.3 Power Supply and Voltage Supervision

The Teridian 73S8010R smart card interface IC incorporates a LDO voltage regulator. The voltage output is controlled by the digital input  $5V/\overline{3V}$ . This regulator is able to provide either 3 V or 5 V card voltage from the power supply applied on the VPC pin.

Digital circuitry is powered by the power supply applied on the VDD pin. V<sub>DD</sub> also defines the voltage range to interface with the system controller.

Three voltage supervisors constantly check the presence of the voltages  $V_{DD}$ ,  $V_{PC}$  and  $V_{CC}$ . A card deactivation sequence is forced upon fault of any of these voltage supervisors. The two voltage supervisors for  $V_{PC}$  and  $V_{CC}$  are linked so that a fault is generated to activate a deactivation sequence when the voltage  $V_{PC}$  becomes lower than  $V_{CC}$ . This allows the 73S8010R to operate at lower  $V_{PC}$  voltage when using 3 V cards only.

The voltage regulator can provide a current of at least 90 mA on  $V_{CC}$  which easily complies with the EMV 4.0 specification. The  $V_{PC}$  voltage supervisor threshold values are defined from the EMV 4.0 standard. A third voltage supervisor monitors the  $V_{DD}$  voltage. It is used to initialize the ISO-7816-3 sequencer at power-on, and to deactivate the card at power-off or upon a fault. The voltage threshold of the  $V_{DD}$  voltage supervisor is internally set by default to 2.3 V nominal. However, it may be desirable in some applications to modify this threshold value. The pin VDDF\_ADJ (pin 18 in the SO package, pin 17 in the QFN package) is used to connect an external resistor  $R_{EXT}$  to ground to raise the  $V_{DD}$  fault voltage to another value  $V_{DDF}$ . The resistor value is defined as follows:

$$R_{EXT} = 56 k\Omega / (V_{DDF} - 2.33)$$

An alternative (more accurate) method of adjusting the  $V_{DD}$  fault voltage is to use a resistive network of R3 from the pin to supply and R1 from the pin to ground (see Figure 4). In order to set the new threshold voltage, the equivalent resistance must be determined. This resistance value will be designated Kx. Kx is defined as R1/(R1+R3). Kx is calculated as:

$Kx = (2.789 / V_{TH}) - 0.6125$  where  $V_{TH}$  is the desired new threshold voltage.

To determine the values of R1 and R3, use the following formulas.

```

R3 = 24000 / Kx R1 = R3*(Kx / (1 - Kx))

```

Taking the example above, where a  $V_{DD}$  fault threshold voltage of 2.7 V is desired, solving for Kx gives:  $\rightarrow$  Kx = (2.789 / 2.7) - 0.6125 = 0.42046.

Solving for R3 gives:  $\rightarrow$  R3 = 24000 / 0.42046 = 57080.

Solving for R1 gives:  $\rightarrow$  R1 = 57080 \*(0.42046 / (1 – 0.42046)) = 41412.

Using standard 1 % resistor values gives R3 = 57.6 K $\Omega$  and R1 = 42.4 K $\Omega$ .

These values give an equivalent resistance of Kx = 0.4228, a 0.6% error.

If the 2.3 V default threshold is used, this pin must be left unconnected.

#### 3.4 Card Power Supply

The card power supply is provided by the LDO regulator, and controlled by the digital ISO-7816-3 sequencer. Card voltage selection is carried out by bit 2 of the control register.

#### Choice of the V<sub>CC</sub> capacitor:

Depending on the application, the requirements in terms of both the  $V_{CC}$  minimum voltage and the transient currents that the interface must be able to provide to the card are different. An external capacitor must be connected between the VCC pin and the card ground in order to guarantee stability of the LDO regulator, and to handle the transient requirements. The type and value of this capacitor can be optimized to meet the desired specification. Table 14 shows the recommended capacitors for each  $V_{PC}$  power supply configuration and applicable specification.

| Specification Requirements |                                                                    |                                 | System Requirements                          |                    |                    |

|----------------------------|--------------------------------------------------------------------|---------------------------------|----------------------------------------------|--------------------|--------------------|

| Specification              | Min V <sub>cc</sub> Voltage<br>allowed during<br>transient current | Max Transient<br>Current Charge | Min V <sub>PC</sub> Power<br>Supply required | Capacitor<br>Type  | Capacitor<br>Value |

| EMV 4.0                    | 4.6 V                                                              | 30 nA⋅s                         | 4.75 V                                       | X5R/X7R            | 3.3 ΩF             |

| ISO-7816-3                 | 4.5 V                                                              | 20 nA·s                         | 4.75 V                                       | with<br>ESR<100 mΩ | 1 ΩF               |

**Table 14: Choice of VCC Pin Capacitor**

## 3.5 Over-temperature Monitor

A built-in detector monitors die temperature. When an over-temperature condition occurs (resulting from a heavily loaded card interface, including short circuits, for example), a card deactivation sequence is initiated, and a fault condition is reported to the system controller (bit 4 of the status register is set and an interrupt is generated).

#### 3.6 On-chip Oscillator and Card Clock

The Teridian 73S8010R device has an on-chip oscillator that can generate the smart card clock using an external crystal connected between the XTALIN and XTALOUT pins to set the oscillator frequency. When the card clock signal is available from another source, it can be connected to the pin XTALIN, and in this case, the XTALOUT pin should be left unconnected.

The card clock frequency may be chosen from 4 different division rates, defined by the Clksel2 and Clksel1 bits (bits 5 and 6) of the  $I^2C$  Control register, as listed in Table 15.

| Clksel2 | Clksel1 | Card Clock     |

|---------|---------|----------------|

| 0       | 0       | Clkin / 8      |

| 0       | 1       | Clkin / 4      |

| 1       | 0       | Clkin / 2      |

| 1       | 1       | Clkin (Xtalin) |

**Table 15: Card Clock Divisor Options**

DS 8010R 022 73S8010R Data Sheet

#### 3.7 Activation Sequence

After Power on Reset, the signal  $\overline{INT}$  is low until the  $V_{DD}$  is stable. When  $V_{DD}$  has been stable for approximately 10 ms and the signal  $\overline{INT}$  is high, the system controller may read the status register to see if the card is present. If all the status bits are satisfied, the system controller can initiate the activation sequence by writing a '1' to the Start/Stop bit (bit 0) of the control register.

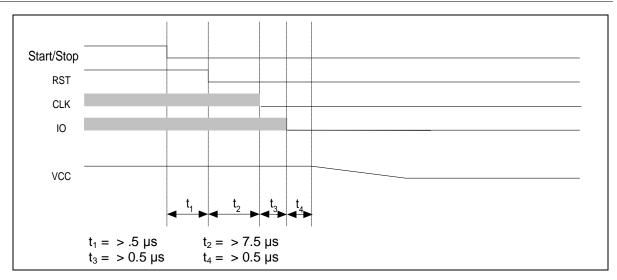

The following steps and Figure 8 show the activation sequence and the timing of the card control signals when the system controller initiates the Start/Stop bit (bit 0) of the control register:

- 1. Voltage  $V_{CC}$  to the card should be valid by the end of  $t_1$ . If  $V_{CC}$  is not valid for any reason, then the session is aborted.

- 2. Turn I/O to reception mode at the end of t<sub>1</sub>.

- 3. CLK is applied to the card at the end of t<sub>2</sub>.

- 4. RST (to the card) is set high at the end of t<sub>3</sub>.

Figure 8: Activation Sequence

#### 3.8 Deactivation Sequence

Deactivation is initiated either by the system controller by resetting the Start/Stop bit, or automatically in the event of hardware faults. Hardware faults are over-current, over-temperature,  $V_{DD}$  fault,  $V_{PC}$  fault,  $V_{CC}$  fault, and card extraction during the session.

The following steps and Figure 9 show the deactivation sequence and the timing of the card control signals when the system controller clears the start/stop bit:

- 1. RST goes low at the end of t<sub>1</sub>.

- 2. CLK goes low at the end of t<sub>2</sub>.

- 3. I/O goes low at the end of t<sub>3</sub>. Out of reception mode.

- 4. Shut down  $V_{\text{CC}}$  at the end of time  $t_4$ .

Figure 9: Deactivation Sequence

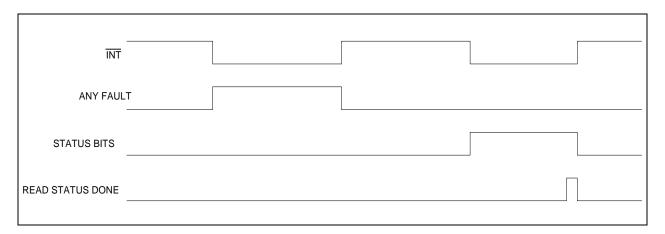

#### 3.9 Interrupt

The Interrupt is an active low interrupt. It is set low if any of the following internal faults are detected:

- V<sub>CC</sub> fault

- V<sub>DD</sub> fault

- V<sub>PC</sub> fault

The interrupt will also be set if one of the following status bit conditions is detected:

- Early ATR

- Mute ATR

- Card insert or card extract

- Protection status from Over-current or Over-heating

When the interrupt is set low by the detection of one of the status bits, it is set high when the status bits are read. (READ STATUS DONE) Figure 10 shows the interrupt operation resulting from the fault or status bit conditions.

Figure 10: Interrupt operation due to Fault and Status Conditions

A power-on-reset event will reset all of the control and status registers to their default states. A  $V_{DD}$  fault event does not reset these registers, but it will signal an interrupt condition and by the action of the timer that creates the interval " $t_1$ ," not clearing the interrupt until  $V_{DD}$  is valid for at least  $t_1$ . A  $V_{DD}$  fault can be considered valid for  $V_{DD}$  as low as 1.5 to 1.8 volts. At the lower range of  $V_{DD}$  fault, POR will be asserted.

DS 8010R 022 73S8010R Data Sheet

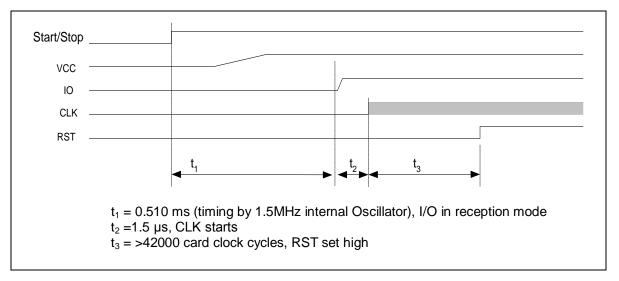

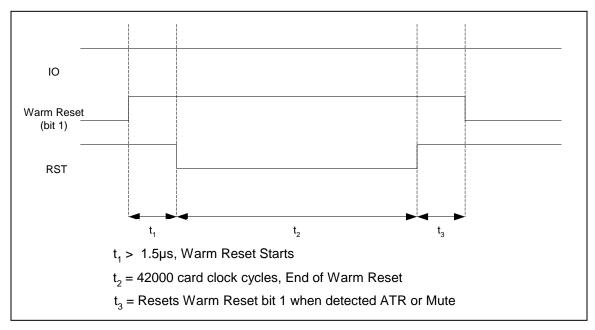

#### 3.10 Warm Reset

The 73S8010R automatically asserts a warm reset to the card when instructed through bit 1 of the I<sup>2</sup>C Control register (bit Warm Reset). The warm reset length is automatically defined as 42,000 card clock cycles. The Warm Reset bit is automatically reset when the card starts answering or when the card is declared mute.

Figure 11: Warm Reset Operation

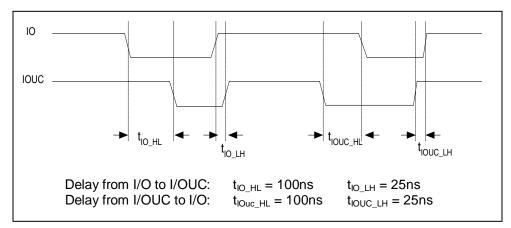

## 3.11 I/O Circuitry and Timing

The states of the I/O, AUX1, and AUX2 pins are low after power-on-reset and they are high when the activation sequencer enables the I/O reception state. See Section 3.7 Activation Sequence for more details on when the I/O reception is enabled. The states of the I/OUC, AUX1UC, and AUX2UC are high after power on reset.

When the control I/O enable bit (bit 7) of the control register is set, the first I/O line on which a falling edge is detected becomes the input I/O line and the other becomes the output I/O line. When the input I/O line rising edge is detected, then both I/O lines return to their neutral state. The delay between these signals is shown in Figure 12.

Figure 12: I/O Timing Diagram

# 4 Mechanical Drawings

# 4.1 32-pin QFN

Figure 13: 32-pin QFN Package Dimensions

DS\_8010R\_022 73S8010R Data Sheet

## 4.2 28-Pin SO

Figure 14: 28-Pin SO Package Dimensions

## 5 Ordering Information

Table 16 lists the order numbers and packaging marks used to identify 73S8010R products.

**Table 16: Order Numbers and Packaging Marks**

| Part Description                               | Order Number    | Packaging Mark |

|------------------------------------------------|-----------------|----------------|

| 73S8010R-SOL, 28-pin Lead-Free SO              | 73S8010R -IL/F  | 73S8010R -IL   |

| 73S8010R–SOL, 28-pin Lead-Free SO Tape / Reel  | 73S8010R -ILR/F | 73S8010R -IL   |

| 73S8010R–QFN, 32-pin Lead-Free QFN             | 73S8010R -IM/F  | 73S8010R       |

| 73S8010R–QFN, 32-pin Lead-Free QFN Tape / Reel | 73S8010R -IMR/F | 73S8010R       |

#### 6 Related Documentation

The following 73S8010R documents are available from Teridian Semiconductor Corporation:

73S8010R 28SO Demo Board User's Guide

#### 7 Contact Information

For more information about Teridian Semiconductor products or to check the availability of the 73S8010R, contact us at:

6440 Oak Canyon Road Suite 100 Irvine, CA 92618-5201

Telephone: (714) 508-8800 FAX: (714) 508-8878

Email: scr.support@teridian.com

For a complete list of worldwide sales offices, go to http://www.teridian.com.