# DS1232LP/LPS Low Power MicroMonitor Chip

#### www.dalsemi.com

### **FEATURES**

- Super-low power version of DS1232

- 50 µA quiescent current

- Halts and restarts an out-of-control microprocessor

- Automatically restarts microprocessor after power failure

- Monitors pushbutton for external override

- Accurate 5% or 10% microprocessor power supply monitoring

- 8-pin DIP, 8-pin SOIC or space saving μ-SOP package available

- Optional 16-pin SOIC package available

- Industrial temperature -40°C to +85°C available, designated N

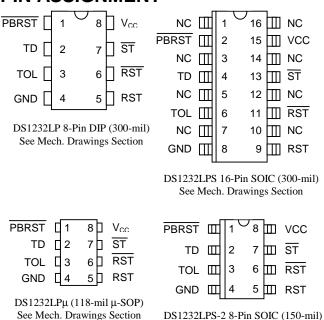

#### **PIN ASSIGNMENT**

See Mech. Drawings Section

#### PIN DESCRIPTION

| PBRST    | - Pushbutton Reset Input                   |

|----------|--------------------------------------------|

| TD       | - Time Delay Set                           |

| TOL      | - Selects 5% or 10% V <sub>CC</sub> Detect |

| GND      | - Ground                                   |

| RST      | - Reset Output (Active High)               |

| RST      | - Reset Output (Active Low, open drain)    |

| ST       | - Strobe Input                             |

| $V_{CC}$ | - +5 Volt Power                            |

#### DESCRIPTION

The DS1232LP/LPS Low Power MicroMonitor Chip monitors three vital conditions for a microprocessor: power supply, software execution, and external over-ride. First, a precision temperature-compensated reference and comparator circuit monitors the status of  $V_{\rm CC}$ . When an out-of-tolerance condition occurs, an internal power-fail signal is generated which forces reset to the active state. When  $V_{\rm CC}$  returns to an in-tolerance condition, the reset signals are kept in the active state for a minimum of 250 ms to allow the power supply and processor to stabilize.

1 of 7

The second function the DS1232LP/LPS performs is pushbutton reset control. The DS1232LP/LPS debounces the pushbutton input and guarantees an active reset pulse width of 250 ms minimum. The third function is a watchdog timer. The DS1232LP/LPS has an internal timer that forces the reset signals to the active state if the strobe input is not driven low prior to timeout. The watchdog timer function can be set to operate on timeout settings of approximately 150 ms, 600 ms, and 1.2 seconds.

#### **OPERATION - POWER MONITOR**

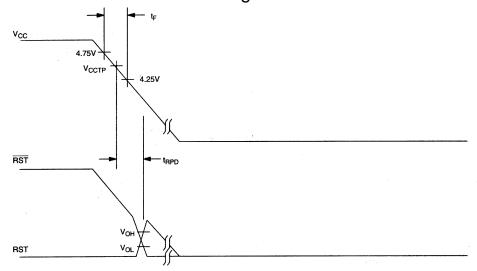

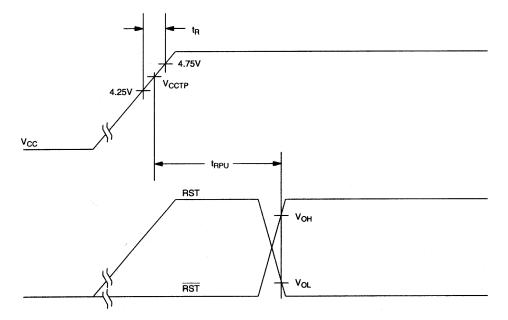

The DS1232LP/LPS detects out-of-tolerance power supply conditions and warns a processor-based system of impending power failure. When  $V_{CC}$  falls below a preset level as defined by TOL, the  $V_{CC}$  comparator outputs the signals RST and  $\overline{RST}$ . When TOL is connected to ground, the RST and  $\overline{RST}$  signals become active as  $V_{CC}$  falls below 4.75 volts. When TOL is connected to  $V_{CC}$ , the RST and  $\overline{RST}$  signals become active as  $V_{CC}$  falls below 4.5 volts. The RST and  $\overline{RST}$  are excellent control signals for a microprocessor, as processing is stopped at the last possible moments of valid  $V_{CC}$ . On power-up, RST and  $\overline{RST}$  are kept active for a minimum of 250 ms to allow the power supply and processor to stabilize.

#### **OPERATION - PUSHBUTTON RESET**

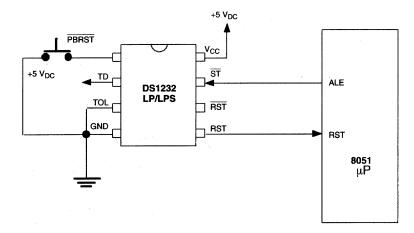

The DS1232LP/LPS provides an input pin for direct connection to a pushbutton (Figure 1). The pushbutton reset input requires an active low signal. Internally, this input is debounced and timed such that RST and RST signals of at least 250 ms minimum are generated. The 250 ms delay starts as the pushbutton reset input is released from low level.

### **OPERATION - WATCHDOG TIMER**

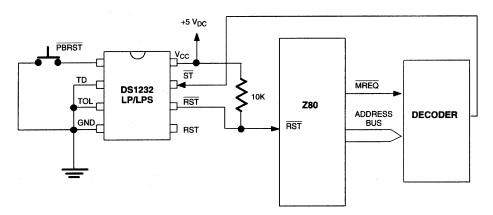

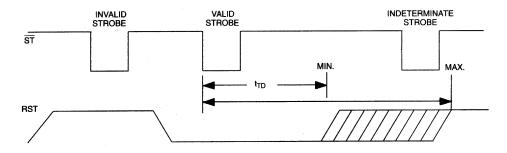

The watchdog timer function forces RST and RST signals to the active state when the ST input is not stimulated for a predetermined time period. The time period is set by the TD input to be typically 150 ms with TD connected to ground, 600 ms with TD left unconnected, and 1.2 seconds with  $\overline{\text{TD}}$  connected to  $V_{\text{CC}}$ . The watchdog timer starts timing out from the set time period as soon as RST and  $\overline{\text{RST}}$  are inactive. If a high-to-low transition occurs on the  $\overline{\text{ST}}$  input pin prior to timeout, the watchdog timer is reset and begins to timeout again. If the watchdog timer is allowed to timeout, then the RST and  $\overline{\text{RST}}$  signals are driven to the active state for 250 ms minimum. The  $\overline{\text{ST}}$  input can be derived from microprocessor address signals, data signals, and/or control signals. When the microprocessor is functioning normally, these signals would, as a matter of routine, cause the watchdog to be reset prior to timeout. To guarantee that the watchdog timer does not timeout, a high-to-low transition must occur at or less than the minimum shown in Table 1. A typical circuit example is shown in Figure 2.

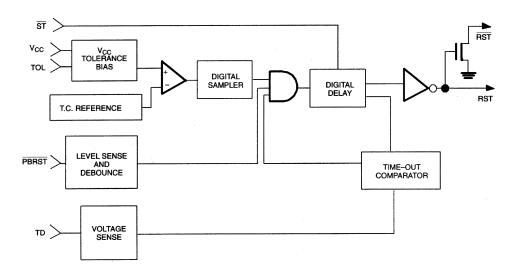

### **MICROMONITOR BLOCK DIAGRAM**

### **PUSHBUTTON RESET** Figure 1

### **WATCHDOG TIMER** Figure 2

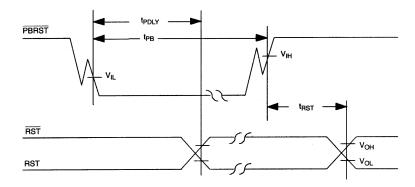

# TIMING DIAGRAM: PUSHBUTTON RESET Figure 3

### TIMING DIAGRAM: STROBE INPUT Figure 4

### **WATCHDOG TIME-OUTS** Table 1

|                 | TIME-OUT |         |         |  |  |

|-----------------|----------|---------|---------|--|--|

| TD              | MIN      | TYP     | MAX     |  |  |

| GND             | 62.5 ms  | 150 ms  | 250 ms  |  |  |

| Float           | 250 ms   | 600 ms  | 1000 ms |  |  |

| V <sub>CC</sub> | 500 ms   | 1200 ms | 2000 ms |  |  |

# TIMING DIAGRAM: POWER-DOWN Figure 5

## TIMING DIAGRAM: POWER-UP Figure 6

### **ABSOLUTE MAXIMUM RATINGS\***

$\begin{array}{lll} \mbox{Voltage on $V_{CC}$ Pin Relative to Ground} & -0.5 \mbox{V to } +7.0 \mbox{V} \\ \mbox{Voltage on I/O Relative to Ground} & -0.5 \mbox{V to $V_{CC}$} + 0.5 \mbox{V} \\ \mbox{Operating Temperature} & 0^{\circ}\mbox{C to } 70^{\circ}\mbox{C} \\ \mbox{Operating Temperature (Industrial Version)} & -40^{\circ}\mbox{C to } +85^{\circ}\mbox{C} \\ \mbox{Storage Temperature} & -55^{\circ}\mbox{C to } +125^{\circ}\mbox{C} \\ \mbox{Soldering Temperature} & 260^{\circ}\mbox{C for } 10 \mbox{ seconds} \\ \end{array}$

### RECOMMENDED DC OPERATING CONDITIONS

(0°C to 70°C)

| PARAMETER                     | SYMBOL            | MIN  | TYP | MAX                  | UNITS | NOTES |

|-------------------------------|-------------------|------|-----|----------------------|-------|-------|

| Supply Voltage                | $V_{CC}$          | 4.5  | 5.0 | 5.5                  | V     | 1     |

| ST and PBRST Input High Level | $V_{IH}$          | 2.0  |     | V <sub>CC</sub> +0.3 | V     | 1     |

| ST and PBRST Input Low Level  | $V_{\mathrm{IL}}$ | -0.3 |     | +0.8                 | V     | 1     |

### DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}\text{C to } 70^{\circ}\text{C}; V_{\text{CC}}=4.5 \text{ to } 5.5\text{V})$

|                                                   |                   | <b>\</b> | ,        | 00   | /     |       |

|---------------------------------------------------|-------------------|----------|----------|------|-------|-------|

| PARAMETER                                         | SYMBOL            | MIN      | TYP      | MAX  | UNITS | NOTES |

| Input Leakage                                     | $I_{ m IL}$       | -1.0     |          | +1.0 | μΑ    | 3     |

| Output Current @ 2.4V                             | $I_{OH}$          | -8       | -10      |      | mA    | 5     |

| Output Current @ 0.4V                             | $I_{OL}$          | 10       |          |      | mA    |       |

| Low Level @ RST                                   | $V_{OL}$          |          |          | 0.4  | V     | 1     |

| Output Voltage @ -500 uA                          | $V_{OH}$          | $V_{CC}$ | $V_{CC}$ |      | V     | 1, 7  |

|                                                   |                   | -0.5V    | -0.1V    |      |       |       |

| Output Current (CMOS)                             | $I_{CC1}$         |          |          | 50   | μΑ    | 2     |

| Operating Current (TTL)                           | I <sub>CC2</sub>  |          | 200      | 500  | μΑ    | 8     |

| V <sub>CC</sub> Trip Point (TOL=GND)              | V <sub>CCTP</sub> | 4.50     | 4.62     | 4.74 | V     | 1     |

| V <sub>CC</sub> Trip Point (TOL=V <sub>CC</sub> ) | V <sub>CCTP</sub> | 4.25     | 4.37     | 4.49 | V     | 1     |

#### **CAPACITANCE**

$(t_A=25^{\circ}C)$

| PARAMETER          | SYMBOL    | MIN | TYP | MAX | UNITS | NOTES |

|--------------------|-----------|-----|-----|-----|-------|-------|

| Input Capacitance  | $C_{IN}$  |     |     | 5   | pF    |       |

| Output Capacitance | $C_{OUT}$ |     |     | 7   | pF    |       |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

### **AC ELECTRICAL CHARACTERISTICS**

| $(0^{\circ}\text{C to } 70^{\circ}\text{C}; V_{\text{CC}}=5\text{V} \pm 10$ | 0% | 1 | $\pm$ | cc=5V | V | 70°C: | to | $0^{\circ}C$ | ( |

|-----------------------------------------------------------------------------|----|---|-------|-------|---|-------|----|--------------|---|

|-----------------------------------------------------------------------------|----|---|-------|-------|---|-------|----|--------------|---|

| PARAMETER                                      | SYMBOL              | MIN | TYP | MAX  | UNITS | NOTES |

|------------------------------------------------|---------------------|-----|-----|------|-------|-------|

| $\overline{PBRST} = V_{IL}$                    | $t_{PB}$            | 20  |     |      | ms    |       |

| RESET Active Time                              | t <sub>RST</sub>    | 250 | 610 | 1000 | ms    |       |

| ST Pulse Width                                 | $t_{ST}$            | 20  |     |      | ns    | 6, 9  |

| V <sub>CC</sub> Fail Detect to RST and RST     | $t_{ m RPD}$        |     | 50  | 175  | μs    |       |

| V <sub>CC</sub> Slew Rate 4.75V to 4.25V       | $t_{\mathrm{F}}$    | 300 |     |      | μs    |       |

| V <sub>CC</sub> Detect to RST and RST Inactive | $t_{ m RPU}$        | 250 | 610 | 1000 | ms    | 4     |

| V <sub>CC</sub> Slew Rate 4.25V to 4.75V       | $t_R$               | 0   |     |      | ns    |       |

| PBRST Stable Low to RST and RST                | $t_{\mathrm{PDLY}}$ |     |     | 20   | ms    |       |

### **NOTES:**

- 1. All voltages referenced to ground.

- 2. Measured with outputs open and  $\overline{ST}$  and  $\overline{PBRST}$  within 0.5V of supply rails.

- 3.  $\overline{PBRST}$  is internally pulled up to  $V_{CC}$  with an internal impedance of 40k typical.

- 4.  $t_R = 5 \mu s$ .

- 5. RST is an open-drain output.

- 6. Must not exceed  $t_{TD}$  minimum. See Table 1.

- 7. RST remains within 0.5V of  $V_{CC}$  on power-down until  $V_{CC}$  drops below 2.0V. RST remains within 0.5V of GND on power-down until  $V_{CC}$  drops below 2.0V.

- 8. Measured with outputs open and  $\overline{ST}$  and  $\overline{PBRST}$  at TTL levels.

- 9. Watchdog can not be disabled. It must be strobed to avoid resets.

### **MARKING INFORMATION:**

8-pin DIP - "DS1232L" 16-pin SOIC - "DS1232L" 8-pin SOIC - "DS1232L" 8-pin μ-SOP - "1232"

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Supervisory Circuits category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

CAT1161LI-25-G CAT853STBI-T3 CAT1026LI-30-G CAT1320LI-25-G TC54VN2402EMB713 MCP1316T-44NE/OT MCP1316MT-45GE/OT MCP1316MT-23LI/OT MAX8997EWW+ MAX6725AKASYD3-LF-T DS1232L NCV302HSN45T1G PT7M6130NLTA3EX PT7M7811STBEX-2017 S-1000N28-I4T1U CAT1161LI-28-G MCP1321T-29AE/OT MCP1319MT-47QE/OT S-1000N23-I4T1U S-1000N19-I4T1U CAT824UTDI-GT3 TC54VC2502ECB713 PT7M6133NLTA3EX PT7M6127NLTA3EX AP0809ES3-r HG811RM4/TR MD7030C MD7033C MD7019 MD7020 MD7021 MD7023 MD7024 MD7027 MD7030 MD7033 MD7035 MD7036 MD7039 MD7040 MD7044 MD7050 MD7015 MD7022 MD7028 MD7031 MD7042 MD7043 MD7047 MD7060