## **DS8024**

## **Smart Card Interface**

#### Features

**General Description**

The DS8024 smart card interface IC is a low-cost, analog front-end for a smart card reader, designed for all ISO 7816, EMV<sup>®</sup>, and GSM11-11 applications. The DS8024 is a pin-for-pin drop-in replacement for the NXP TDA8024 and is offered in 28-pin TSSOP and SO packages.

Applications requiring support for 1.8V smart cards or requiring low power should consider the DS8113, which achieves lower active- and stop-mode power with minimal changes to application hardware and software.

#### **Applications**

Set-Top Box Conditional Access Access Control Banking Applications POS Terminals Debit/Credit Payment Terminals PIN Pads Automated Teller Machines Telecommunications

Pay/Premium Television

## Ordering Information

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| DS8024-RJX+   | -40°C to +85°C | 28 TSSOP    |

| DS8024-RJX/V+ | -40°C to +85°C | 28 TSSOP    |

| DS8024-RRX+   | -40°C to +85°C | 28 SO       |

*Note:* Contact the factory for availability of other variants and package options.

+Denotes a lead(Pb)-free/RoHS-compliant package.

N denotes an automotive-qualified part.

#### Selector Guide appears at end of data sheet.

- Analog Interface and Level Shifting for IC Card Communication

- ♦ ±8kV (min) ESD (IEC) Protection on Card Interfaces

- Internal IC Card Supply-Voltage Generation: 5.0V ±5%, 80mA (max) 3.0V ±8%, 65mA (max)

- Automatic Card Activation and Deactivation Controlled by Dedicated Internal Sequencer

- I/O Lines from Host Directly Level Shifted for Smart Card Communication

- Flexible Card Clock Generation, Supporting External Crystal Frequency Divided by 1, 2, 4, or 8

- High-Current, Short-Circuit and High-Temperature Protection

EMV is a registered trademark of EMVCo LLC. EMV Level 1 library and hardware reference design available. Contact factory for details.

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: <u>www.maximintegrated.com/errata</u>.

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

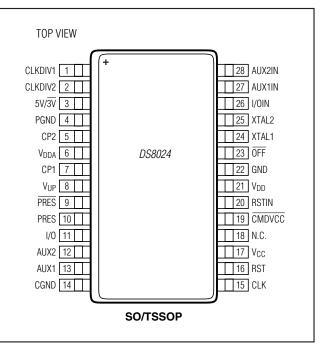

### **Pin Configuration**

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on VDD Relative to GND   | 0.5V to +6.5V                    |

|----------------------------------------|----------------------------------|

| Voltage Range on VDDA Relative to PGND | )0.5V to +6.5V                   |

| Voltage Range on CP1, CP2, and VUP     |                                  |

| Relative to PGND                       | 0.5V to +7.5V                    |

| Voltage Range on All Other Pins        |                                  |

| Relative to GND                        | 0.5V to (V <sub>DD</sub> + 0.5V) |

| Maximum Junction Temperature           | +125°C                           |

| Continuous Power Dissipation (multilayer board, $T_A = +70^{\circ}C$ ) |              |  |  |  |

|------------------------------------------------------------------------|--------------|--|--|--|

| TSSOP (derate 14mW/°C above +70°C)                                     | 1117.3mW     |  |  |  |

| SO (derate 16.7mW/°C above +70°C)                                      | 1355.9mW     |  |  |  |

| Storage Temperature Range55                                            | °C to +150°C |  |  |  |

| Lead Temperature (soldering, 10s)                                      | +300°C       |  |  |  |

| Soldering Temperature (reflow)                                         |              |  |  |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **RECOMMENDED DC OPERATING CONDITIONS**

(V\_DD = +3.3V, V\_DDA = +5.0V, T\_A = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                                     | SYMBOL                                     | CONDITIONS                                                                                        | MIN                      | ТҮР  | MAX                      | UNITS |  |

|-------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------|--|

| POWER SUPPLY                                                                  |                                            |                                                                                                   |                          |      |                          |       |  |

| Digital Supply Voltage                                                        | V <sub>DD</sub>                            |                                                                                                   | 2.7                      |      | 6.0                      | V     |  |

| Card Voltage-Generator Supply Voltage                                         |                                            | $V_{CC} = 5V$ , $ I_{CC}  < 80mA$                                                                 | 4.0                      |      | 6.0                      | v     |  |

| Card Voltage-Generator Suppry Voltage                                         | V <sub>DDA</sub>                           | $V_{CC} = 5V$ , $ I_{CC}  < 30mA$                                                                 | 3.0                      |      | 6.0                      | V     |  |

| Reset Voltage Thresholds                                                      | V <sub>TH2</sub>                           | Threshold voltage (falling)                                                                       | 2.30                     | 2.45 | 2.60                     | V     |  |

| heset voltage miesholds                                                       | V <sub>HYS2</sub>                          | Hysteresis                                                                                        | 50                       | 100  | 150                      | mV    |  |

| CURRENT CONSUMPTION                                                           |                                            |                                                                                                   |                          |      |                          |       |  |

| Active V <sub>DD</sub> Current 5V Cards<br>(Including 80mA Draw from 5V Card) | IDD_50V                                    | $I_{CC} = 80$ mA, f <sub>XTAL</sub> = 20MHz,<br>f <sub>CLK</sub> = 10MHz, V <sub>DDA</sub> = 5.0V |                          |      | 215                      | mA    |  |

| Active V <sub>DD</sub> Current 5V Cards<br>(Current Consumed by DS8024 Only)  | IDD_IC                                     | $I_{CC} = 80$ mA, $f_{XTAL} = 20$ MHz,<br>$f_{CLK} = 10$ MHz, $V_{DDA} = 5.0V$ (Note 2)           |                          |      | 135                      | mA    |  |

| Active V <sub>DD</sub> Current 3V Cards<br>(Including 65mA Draw from 3V Card) | IDD_30V                                    | $I_{CC} = 65$ mA, f <sub>XTAL</sub> = 20MHz,<br>f <sub>CLK</sub> = 10MHz, V <sub>DDA</sub> = 5.0V |                          |      | 100                      | mA    |  |

| Active V <sub>DD</sub> Current 3V Cards<br>(Current Consumed by DS8024 Only)  | IDD_IC                                     | $I_{CC} = 65$ mA, $f_{XTAL} = 20$ MHz,<br>$f_{CLK} = 10$ MHz, $V_{DDA} = 5.0V$ (Note 2)           |                          |      | 35                       | mA    |  |

| Inactive-Mode Current                                                         | IDD                                        | Card inactive                                                                                     |                          |      | 500                      | μA    |  |

| CLOCK SOURCE                                                                  |                                            |                                                                                                   |                          |      |                          |       |  |

| Crystal Frequency                                                             | fxtal                                      | External crystal                                                                                  | 0                        |      | 20                       | MHz   |  |

|                                                                               | fXTAL1                                     |                                                                                                   | 0                        |      | 20                       | MHz   |  |

| XTAL1 Operating Conditions                                                    | VIL_XTAL1                                  | Low-level input on XTAL1 (Note 3)                                                                 | -0.3                     |      | 0.3 x<br>V <sub>DD</sub> | v     |  |

|                                                                               | VIH_XTAL1                                  | High-level input on XTAL1 (Note 3)                                                                | 0.7 x<br>V <sub>DD</sub> |      | V <sub>DD</sub> + 0.3    |       |  |

| External Capacitance for Crystal                                              | C <sub>XTAL1</sub> ,<br>C <sub>XTAL2</sub> | (Note 3)                                                                                          |                          |      | 15                       | pF    |  |

| Internal Oscillator                                                           | fINT                                       |                                                                                                   |                          | 2.7  |                          | MHz   |  |

| SHUTDOWN TEMPERATURE                                                          |                                            |                                                                                                   |                          |      |                          |       |  |

| Shutdown Temperature                                                          | T <sub>SD</sub>                            | (Note 3)                                                                                          |                          | +150 |                          | °C    |  |

## **RECOMMENDED DC OPERATING CONDITIONS (continued)**

| PARAMETER           |                               | SYMBOL CONDITIONS    |                                                                                     | MIN                      | TYP  | MAX  | UNITS |

|---------------------|-------------------------------|----------------------|-------------------------------------------------------------------------------------|--------------------------|------|------|-------|

| RST PIN             |                               |                      |                                                                                     |                          |      |      | •     |

| Cord Incotive Mart- | Output Low Voltage            | VOL_RST1             | I <sub>OL_RST</sub> = 1mA                                                           | 0                        |      | 0.3  | V     |

| Card-Inactive Mode  | Output Current                | IOL_RST1             | V <sub>O_LRST</sub> = 0V                                                            | 0                        |      | -1   | mA    |

|                     | Output Low Voltage            | VOL_RST2             | I <sub>OL_RST</sub> = 200µA                                                         | 0                        |      | 0.3  | V     |

|                     | Output High<br>Voltage        | VOH_RST2             | IOH_RST = -200µA                                                                    | V <sub>CC</sub> -<br>0.5 |      | Vcc  | V     |

|                     | Rise Time                     | t <sub>R_RST</sub>   | C <sub>L</sub> = 30pF (Note 3)                                                      |                          |      | 0.1  | μs    |

| Card-Active Mode    | Fall Time                     | tF_RST               | C <sub>L</sub> = 30pF (Note 3)                                                      |                          |      | 0.1  | μs    |

|                     | Shutdown Current<br>Threshold | I <sub>RST(SD)</sub> |                                                                                     |                          | -20  |      | mA    |

|                     | Current Limitation            | IRST(LIMIT)          |                                                                                     | -20                      |      | +20  | mA    |

|                     | RSTIN to RST Delay            | tD(RSTIN-RST)        |                                                                                     |                          |      | 2    | μs    |

| CLK PIN             |                               |                      |                                                                                     |                          |      |      |       |

| Cord Inactive Made  | Output Low Voltage            | VOL_CLK1             | I <sub>OLCLK</sub> = 1mA                                                            | 0                        |      | 0.3  | V     |

| Card-Inactive Mode  | Output Current                | IOL_CLK1             | V <sub>OLCLK</sub> = 0V                                                             | 0                        |      | -1   | mA    |

| Card-Active Mode    | Output Low Voltage            | VOL_CLK2             | I <sub>OLCLK</sub> = 200μA                                                          | 0                        |      | 0.3  | V     |

|                     | Output High<br>Voltage        | VOH_CLK2             | I <sub>ОНСLК</sub> = -200µА                                                         | V <sub>CC</sub> -<br>0.5 |      | Vcc  | V     |

|                     | Rise Time                     | tr_CLK               | C <sub>L</sub> = 30pF (Note 3)                                                      |                          |      | 8    | ns    |

|                     | Fall Time                     | tF_CLK               | C <sub>L</sub> = 30pF (Note 3)                                                      |                          |      | 8    | ns    |

|                     | Current Limitation            | ICLK(LIMIT)          |                                                                                     | -70                      |      | +70  | mA    |

|                     | Clock Frequency               | fclk                 | Operational (Note 3)                                                                | 0                        |      | 10   | MHz   |

|                     | Duty Factor                   | δ                    | C <sub>L</sub> = 30pF (Note 3)                                                      | 45                       |      | 55   | %     |

|                     | Slew Rate                     | SR                   | C <sub>L</sub> = 30pF (Note 3)                                                      | 0.2                      |      |      | V/ns  |

| V <sub>CC</sub> PIN |                               |                      |                                                                                     |                          |      |      |       |

| Card-Inactive Mode  | Output Low Voltage            | VCC1                 | I <sub>CC</sub> = 1mA                                                               | 0                        |      | 0.3  | V     |

| Cal d-Inactive Mode | Output Current                | ICC1                 | $V_{CC} = 0V$                                                                       | 0                        |      | -1   | mA    |

|                     |                               |                      | I <sub>CC(5V)</sub> < 80mA                                                          | 4.75                     | 5.00 | 5.25 |       |

|                     |                               |                      | I <sub>CC(3V)</sub> < 65mA                                                          | 2.78                     | 3.00 | 3.22 |       |

| Card-Active Mode    | Output Low Voltage            | V <sub>CC2</sub>     | 5V card: current pulses of 40nC<br>with I < 200mA, t < 400ns,<br>f < 20MHz (Note 3) | 4.6                      |      | 5.4  | V     |

|                     |                               |                      | 3V card: current pulses of 24nC<br>with I < 200mA, t < 400ns,<br>f < 20MHz (Note 3) | 2.75                     |      | 3.25 |       |

|                     |                               | loca                 | $V_{CC(5V)} = 0$ to 5V                                                              |                          |      | -80  | mA    |

|                     | Output Current                | ICC2                 | $V_{CC(3V)} = 0$ to 3V                                                              |                          |      | -65  | mA    |

|                     | Shutdown Current<br>Threshold | ICC(SD)              |                                                                                     |                          | 120  |      | mA    |

|                     | Slew Rate                     | VCCSR                | Up/down, C < 300nF                                                                  | 0.05                     | 0.16 | 0.22 | V/µs  |

### **RECOMMENDED DC OPERATING CONDITIONS (continued)**

$(V_{DD} = +3.3V, V_{DDA} = +5.0V, T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                  |                               | SYMBOL              | CONDITIONS                                                                 | MIN                       | TYP | MAX                      | UNITS |

|----------------------------|-------------------------------|---------------------|----------------------------------------------------------------------------|---------------------------|-----|--------------------------|-------|

| DATA LINES (I/O AN         | ND I/OIN)                     |                     | •                                                                          | •                         |     |                          |       |

| I/O ⇔ I/OIN Falling E      | dge Delay                     | td(10-101N)         | (Note 3)                                                                   |                           |     | 200                      | ns    |

| Pullup Pulse Active T      | ïme                           | tPU                 | (Note 3)                                                                   |                           |     | 100                      | ns    |

| Maximum Frequency          | ,                             | fIOMAX              |                                                                            |                           |     | 1                        | MHz   |

| Input Capacitance          |                               | CI                  | (Note 3)                                                                   |                           |     | 10                       | pF    |

| I/O, AUX1, AUX2 PI         | NS                            |                     |                                                                            |                           |     |                          |       |

|                            | Output Low Voltage            | Vol_IO1             | $I_{OL_{IO}} = 1mA$                                                        | 0                         |     | 0.3                      | V     |

| Card-Inactive Mode         | Output Current                | I <sub>OL_IO1</sub> | $V_{OL_{IO}} = 0V$                                                         | 0                         |     | -1                       | mA    |

|                            | Internal Pullup<br>Resistor   | R <sub>PU_IO</sub>  | To V <sub>CC</sub>                                                         | 9                         | 11  | 19                       | kΩ    |

|                            | Output Low Voltage            | VOL_IO2             | $I_{OL_{IO}} = 1 \text{mA}$                                                | 0                         |     | 0.3                      | V     |

|                            | Output High<br>Voltage        | VOH_IO2             | I <sub>OH_IO</sub> = < -40µA (3V/5V)                                       | 0.75 x \                  | /cc | V <sub>CC</sub>          | V     |

|                            | Output Rise/Fall<br>Time      | tor                 | C <sub>L</sub> = 30pF (Note 3)                                             |                           |     | 0.1                      | μs    |

| Card-Active Mode           | Input Low Voltage             | VIL_IO              |                                                                            | -0.3                      |     | +0.8                     | - v   |

|                            | Input High Voltage            | VIH_IO              |                                                                            | 1.5                       |     | V <sub>CC</sub>          |       |

|                            | Input Low Current             | IIL_IO              | $V_{IL_{IO}} = 0V$                                                         |                           |     | 700                      | μA    |

|                            | Input High Current            | IIH_IO              | VIH_IO = VCC                                                               |                           |     | 20                       | μA    |

|                            | Input Rise/Fall Time          | tIT                 | (Note 3)                                                                   |                           |     | 1.2                      | μs    |

|                            | Current Limitation            | IIO(LIMIT)          | $C_L = 30 pF$                                                              | -15                       |     | +15                      | mA    |

|                            | Current When<br>Pullup Active | IPU                 | C <sub>L</sub> = 80pF, V <sub>OH</sub> = 0.9 x V <sub>DD</sub><br>(Note 3) | -1                        |     |                          | mA    |

| I/OIN, AUX1IN, AUX         | 2IN PINS                      |                     |                                                                            | •                         |     |                          | •     |

| Output Low Voltage         |                               | VOL                 | I <sub>OL</sub> = 1mA                                                      | 0                         |     | 0.3                      | V     |

| Output High Voltage        |                               | V <sub>OH</sub>     | I <sub>OH</sub> < -40µА                                                    | 0.75 x<br>V <sub>DD</sub> |     | V <sub>DD</sub> +<br>0.1 | V     |

| Output Rise/Fall Time      | 9                             | tor                 | C <sub>L</sub> = 30pF, 10% to 90% (Note 3)                                 |                           |     | 0.1                      | μs    |

| Input Low Voltage          |                               | VIL                 |                                                                            | -0.3                      |     | 0.3 x<br>V <sub>DD</sub> | V     |

| Input High Voltage         |                               | VIH                 |                                                                            | 0.7 x<br>V <sub>DD</sub>  |     | V <sub>DD</sub> + 0.3    | v     |

| Input Low Current          |                               | I <sub>IL_IO</sub>  | $V_{IL} = 0V$                                                              |                           |     | 600                      | μA    |

| Input High Current         |                               | IIH_IO              | $V_{IH} = V_{DD}$                                                          |                           |     | 10                       | μA    |

| Input Rise/Fall Time       |                               | t <sub>IT</sub>     | V <sub>IL</sub> to V <sub>IH</sub> (Note 3)                                |                           |     | 1.2                      | μs    |

| Integrated Pullup Resistor |                               | R <sub>PU</sub>     | Pullup to V <sub>DD</sub>                                                  | 9                         | 11  | 13                       | kΩ    |

| Current When Pullup        | Active                        | IPU                 | C <sub>L</sub> = 30pF, V <sub>OH</sub> = 0.9 x V <sub>DD</sub><br>(Note 3) | -1                        |     |                          | mA    |

### **RECOMMENDED DC OPERATING CONDITIONS (continued)**

(V<sub>DD</sub> = +3.3V, V<sub>DDA</sub> = +5.0V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                      |                    | SYMBOL             | CONDITIONS                                   | MIN                       | ТҮР | MAX                      |    |

|--------------------------------|--------------------|--------------------|----------------------------------------------|---------------------------|-----|--------------------------|----|

| CONTROL PINS (C                | LKDIV1, CLKDIV2, ( | CMDVCC, RSTIN      | , 5V/ <u>3V</u> )                            | ·                         |     |                          | •  |

| Input Low Voltage              |                    | VIL                |                                              | -0.3                      |     | 0.3 x<br>V <sub>DD</sub> | V  |

| Input High Voltage             |                    | VIH                |                                              | 0.7 x<br>V <sub>DD</sub>  |     | V <sub>DD</sub> +<br>0.3 | V  |

| Input Low Current              |                    | l <sub>IL_IO</sub> | $0 < V_{IL} < V_{DD}$                        |                           |     | 5                        | μA |

| Input High Current             |                    | IIH_IO             | $0 < V_{IH} < V_{DD}$                        |                           |     | 5                        | μA |

| Integrated Pullup Re           | esistor            | R <sub>PU</sub>    | Pullup to $V_{DD}$ , $5V/\overline{3V}$ only | 50                        | 85  | 120                      | kĀ |

| INTERRUPT OUTP                 | UT PIN (OFF)       |                    |                                              |                           |     |                          |    |

| Output Low Voltage             | )                  | Vol                | $I_{OL} = 2mA$                               | 0                         |     | 0.3                      | V  |

| Output High Voltage            |                    | V <sub>OH</sub>    | I <sub>OH</sub> = -15μA                      | 0.75 x<br>V <sub>DD</sub> |     |                          | V  |

| Integrated Pullup Re           | esistor            | R <sub>PU</sub>    | Pullup to V <sub>DD</sub>                    | 12                        | 20  | 28                       | kΩ |

| PRES, PRES PINS                |                    | ·                  | •                                            | •                         |     |                          | ·  |

| Input Low Voltage              |                    | VIL_PRES           |                                              |                           |     | 0.3 x<br>V <sub>DD</sub> | V  |

| Input High Voltage             |                    | VIH_PRES           |                                              | 0.7 x<br>V <sub>DD</sub>  |     |                          | V  |

| Input Low Current              |                    | IIL_PRES           | V <sub>IL_PRES</sub> = 0V                    |                           |     | 40                       | μA |

| Input High Current             |                    | IIH_PRES           | VIH_PRES = VDD                               |                           |     | 40                       | μA |

| TIMING                         |                    | · ·                |                                              |                           |     |                          |    |

| Activation Time                |                    | tact               |                                              |                           | 160 |                          | μs |

| Deactivation Time              |                    | <b>TDEACT</b>      |                                              |                           | 80  |                          | μs |

| CLK to Card Start Window Start |                    | t3                 |                                              |                           | 95  |                          |    |

| Time                           | Window End         | t5                 |                                              |                           | 160 |                          | μs |

| PRES/PRES Debour               | nce Time           | <b>T</b> DEBOUNCE  |                                              |                           | 8   |                          | ms |

**Note 1:** Operation guaranteed at  $T_A = -40^{\circ}C$  and  $T_A = +85^{\circ}C$ , but not tested.

Note 2: IDD\_IC measures the amount of current used by the DS8024 to provide the smart card current minus the load.

Note 3: Guaranteed by design, but not production tested.

## **Pin Description**

| PIN    | NAME                | FUNCTION                                                                                                                                                                                                                |

|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2   | CLKDIV1,<br>CLKDIV2 | Clock Divider. Determines the divided-down input clock frequency (presented at XTAL1 or from a crystal at XTAL1 and XTAL2) on the CLK output pin. Dividers of 1, 2, 4, and 8 are available.                             |

| 3      | 5V/ <del>3</del> V  | 5V/3V Selection Pin. Allows selection of 5V or 3V for communication with an IC card. Logic-high selects 5V operation; logic-low selects 3V operation. See Table 3 for a complete description of choosing card voltages. |

| 4      | PGND                | Analog Ground                                                                                                                                                                                                           |

| 5, 7   | CP2, CP1            | Step-Up Converter Contact. Charge-pump capacitor. Connect a 100nF capacitor (ESR < $100m\bar{A}$ ) between CP1 and CP2.                                                                                                 |

| 6      | VDDA                | Charge-Pump Supply. Must be equal to or higher than V <sub>DD</sub> . Connect a supply of at least 3.3V.                                                                                                                |

| 8      | V <sub>UP</sub>     | Charge-Pump Output. Connect a 100nF capacitor (ESR < $100m\bar{A}$ ) between V <sub>UP</sub> and GND.                                                                                                                   |

| 9      | PRES                | Card Presence Indicator. Active-low card presence inputs. When the presence indicator becomes active, a debounce timeout begins. After 8ms (typ) the OFF signal becomes active.                                         |

| 10     | PRES                | Card Presence Indicator. Active-high card presence inputs. When the presence indicator becomes active, a debounce timeout begins. After 8ms (typ) the OFF signal becomes active.                                        |

| 11     | I/O                 | Smart Card Data-Line Output. Card data communication line, contact C7.                                                                                                                                                  |

| 12, 13 | AUX2,<br>AUX1       | Smart Card Auxiliary Line (C4, C8) Output. Data line connected to card reader contacts C4 (AUX1) and C8 (AUX2).                                                                                                         |

| 14     | CGND                | Smart Card Ground                                                                                                                                                                                                       |

| 15     | CLK                 | Smart Card Clock. Card clock, contact C3.                                                                                                                                                                               |

| 16     | RST                 | Smart Card Reset. Card reset output from contact C2.                                                                                                                                                                    |

| 17     | V <sub>CC</sub>     | Smart Card Supply Voltage. Decouple to CGND (card ground) with 2 x 100nF or 100 + 220nF capacitors (ESR < 100m $\Omega$ ).                                                                                              |

| 18     | N.C.                | No Connection. Unused on the DS8024.                                                                                                                                                                                    |

| 19     | CMDVCC              | Activation Sequence Initiate. Active-low input from host.                                                                                                                                                               |

| 20     | RSTIN               | Card Reset Input. Reset input from the host.                                                                                                                                                                            |

| 21     | V <sub>DD</sub>     | Supply Voltage                                                                                                                                                                                                          |

| 22     | GND                 | Digital Ground                                                                                                                                                                                                          |

| 23     | OFF                 | Status Output. Active-low interrupt output to the host. Use a $20k\Omega$ integrated pullup resistor to V <sub>DD</sub> .                                                                                               |

| 24, 25 | XTAL1,<br>XTAL2     | Crystal/Clock Input. Connect an input from an external clock to XTAL1 or connect a crystal across XTAL1 and XTAL2. For the low idle-mode current variant, an external clock must be driven on XTAL1.                    |

| 26     | I/OIN               | I/O Input. Host-to-interface chip data I/O line.                                                                                                                                                                        |

| 27, 28 | AUX1IN,<br>AUX2IN   | C4/C8 Input. Host-to-interface I/O line for auxiliary connections to C4 and C8.                                                                                                                                         |

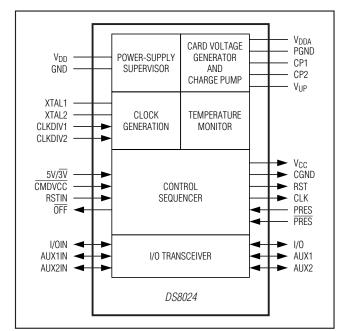

## **Detailed Description**

The DS8024 is an analog front-end for communicating with 3V and 5V smart cards. Using an integrated charge pump, the DS8024 can operate from a single input voltage. The device translates all communication lines to the correct voltage level and provides power for smart card operation. It can operate from a wide input voltage range (3.3V to 6.0V). The DS8024 is compatible with the NXP TDA8024 and is provided in the same packages. (Note that the PORADJ pin is not present in the DS8024. Most applications do not make use of this

Figure 1. Functional Diagram

input pin, instead using the DS8024's default reset threshold.)

#### **Power Supply**

The DS8024 can operate from a single supply or a dual supply. The supply pins for the device are V<sub>DD</sub>, GND, V<sub>DDA</sub>, and PGND. V<sub>DD</sub> should be in the range of 2.7V to 6.0V, and is the supply for signals that interface with the host controller. It should, therefore, be the same supply as used by the host controller. All smart card contacts remain inactive during power on or power off. The internal circuits are kept in the reset state until V<sub>DD</sub> reaches V<sub>TH2</sub> + V<sub>HYS2</sub> and for the duration of the internal power-on reset pulse, t<sub>W</sub>. A deactivation sequence is executed when V<sub>DD</sub> falls below V<sub>TH2</sub>.

An internal charge pump and regulator generate the 3V or 5V card supply voltage (V<sub>CC</sub>). The charge pump and regulator are supplied by V<sub>DDA</sub> and PGND. V<sub>DDA</sub> should be connected to a minimum 3.3V (maximum 6.0V) supply and should be at a potential that is equal to or higher than V<sub>DD</sub>.

The charge pump operates in a 1x (voltage follower) or 2x (voltage doubler) mode depending on the input V<sub>DDA</sub> and the selected card voltage (5V or 3V).

- For 5V cards, the DS8024 operates in a 1x mode for V<sub>DDA</sub> > 5.8V and in a 2x mode for V<sub>DDA</sub> < 5.8V.</li>

- For 3V cards, the DS8024 operates in a 1x mode for V<sub>DDA</sub> > 4.1V and in a 2x mode for V<sub>DDA</sub> < 4.0V.</li>

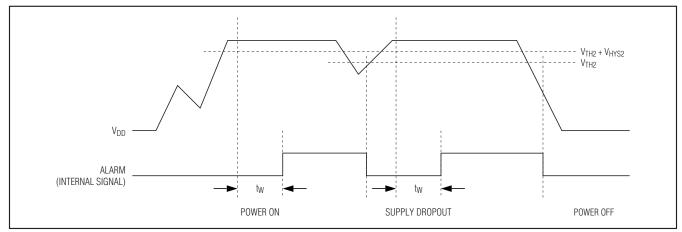

#### **Voltage Supervisor**

The voltage supervisor monitors the  $V_{DD}$  supply. A 220µs reset pulse (t<sub>W</sub>) is used internally to keep the device inactive during power on or power off of the  $V_{DD}$  supply. See Figure 2.

Figure 2. Voltage Supervisor Behavior

Maxim Integrated

The DS8024 card interface remains inactive no matter the levels on the command lines until duration tw after V<sub>DD</sub> has reached a level higher than V<sub>TH2</sub> + V<sub>HYS2</sub>. When V<sub>DD</sub> falls below V<sub>TH2</sub>, the DS8024 executes a card deactivation sequence if its card interface is active.

### **Clock Circuitry**

The clock signal from the DS8024 to the smart card (CLK) is generated from the clock input on XTAL1 or from a crystal operating at up to 20MHz connected between pins XTAL1 and XTAL2. The inputs CLKDIV1 and CLKDIV2 determine the frequency of the CLK signal, which can be  $f_{XTAL}$ ,  $f_{XTAL}/2$ ,  $f_{XTAL}/4$ , or  $f_{XTAL}/8$ . Table 1 shows the relationship between CLKDIV1 and CLKDIV2 and the frequency of CLK.

Do not change the state of pins CLKDIV1 and CLKDIV2 simultaneously; a delay of 10ns minimum between changes is required. The minimum duration of any state of CLK is 8 periods of XTAL1.

The hardware in the DS8024 guarantees that the frequency change is synchronous. During a transition of the clock divider, no pulse is shorter than 45% of the smallest period, and the clock pulses before and after the instant of change have the correct width.

To achieve a 45% to 55% duty factor on pin CLK when no crystal is present, the input signal on XTAL1 should have a 48% to 52% duty factor. Transition time on XTAL1 should be less than 5% of the period.

With a crystal, the duty factor on pin CLK may be 45% to 55% depending on the circuit layout and on the crystal characteristics and frequency.

The DS8024 crystal oscillator runs when the device is powered up. If the crystal oscillator is used or the clock pulse on pin XTAL1 is permanent, the clock pulse is applied to the card at time t4 (see Figures 7 and 8). If the signal applied to XTAL1 is controlled by the host microcontroller, the clock pulse is applied to the card when it is sent by the system microcontroller (after completion of the activation sequence).

#### **Table 1. Clock Frequency Selection**

| CLKDIV1 | CLKDIV2 | fclk                 |

|---------|---------|----------------------|

| 0       | 0       | f <sub>XTAL</sub> /8 |

| 0       | 1       | f <sub>XTAL</sub> /4 |

| 1       | 1       | f <sub>XTAL</sub> /2 |

| 1       | 0       | fxtal                |

### I/O Transceivers

The three data lines I/O, AUX1, and AUX2 are identical. This section describes the characteristics of I/O and I/OIN but also applies to AUX1, AUX1IN, AUX2, and AUX2IN.

I/O and I/OIN are pulled high with an  $11k\Omega$  resistor (I/O to V<sub>CC</sub> and I/OIN to V<sub>DD</sub>) in the inactive state. The first side of the transceiver to receive a falling edge becomes the master. When the master is decided, the opposite side switches to slave mode, ignoring subsequent edges until the master releases. After a time delay tD(EDGE), an n transistor on the slave side is turned on, thus transmitting the logic 0 present on the master side.

When the master side asserts a logic 1, a p transistor on the slave side is activated during the time delay tpU and then both sides return to their inactive (pulled up) states. This active pullup provides fast low-to-high transitions. After the duration of tpU, the output voltage depends only on the internal pullup resistor and the load current. Current to and from the card I/O lines is limited internally to 15mA. The maximum frequency on these lines is 1MHz.

#### **Inactive Mode**

The DS8024 powers up with the card interface in the inactive mode. Minimal circuitry is active while waiting for the host to initiate a smart card session.

- All card contacts are inactive (approximately 200  $\!\Omega$  to GND).

- Pins I/OIN, AUX1IN, and AUX2IN are in the highimpedance state (11kΩ pullup resistor to V<sub>DD</sub>).

- Voltage generators are stopped.

- XTAL oscillator is running (if included in the device).

- Voltage supervisor is active.

- The internal oscillator is running at its low frequency.

#### **Activation Sequence**

After power-on and the reset delay, the host microcontroller can monitor card presence with signals  $\overrightarrow{OFF}$  and  $\overrightarrow{CMDVCC}$ , as shown in Table 2.

#### **Table 2. Card Presence Indication**

| OFF  | CMDVCC | STATUS                   |

|------|--------|--------------------------|

| High | High   | Card present.            |

| Low  | High   | Card <b>not</b> present. |

**DS8024**

## **Smart Card Interface**

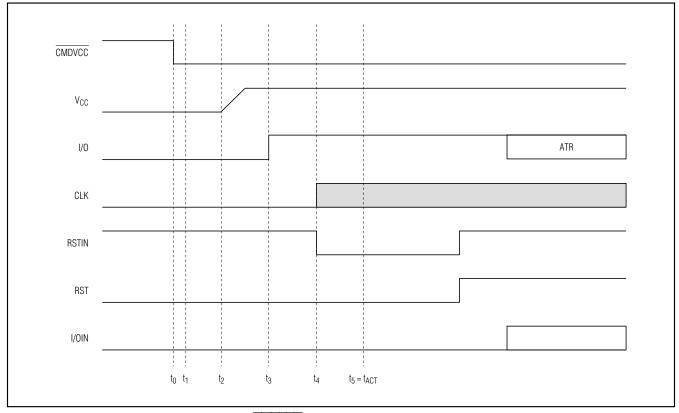

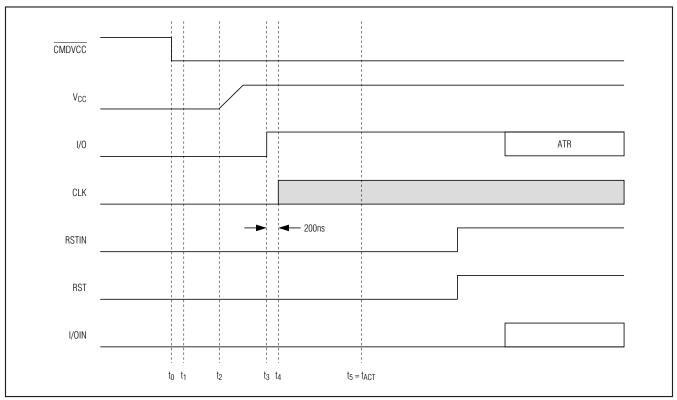

When a card is inserted into the reader (if PRES is active), the host microcontroller can begin an activation sequence (start a card session) by pulling CMDVCC low. The following events form an activation sequence (Figure 3):

- 1) Host: CMDVCC is pulled low.

- 2) DS8024: The internal oscillator changes to high frequency (t<sub>0</sub>).

- DS8024: The voltage generator is started simultaneously (t<sub>0</sub> = t<sub>1</sub>).

- 4) DS8024: V<sub>CC</sub> rises from 0 to 5V or 3V with a controlled slope ( $t_2 = t_1 + 1.5 \times T$ ). T is 64 times the internal oscillator period (approximately 25µs).

- 5) DS8024: I/O, AUX1, and AUX2 are enabled (t\_3 = t\_1 + 4T).

- 6) DS8024: The CLK signal is applied to the C3 contact (t<sub>4</sub>).

- 7) DS8024: RST is enabled simultaneously (t<sub>5</sub> = t<sub>4</sub> =  $t_1 + 7T$ ).

An alternate sequence allows the application to control when the clock is applied to the card.

- 1) Host: Set RSTIN high.

- 2) Host: Set CMDVCC low.

- 3) Host: Set RSTIN low between t<sub>3</sub> and t<sub>5</sub>; CLK will now start.

- 4) DS8024: RST stays low until t<sub>5</sub>, then RST becomes the copy of RSTIN.

- 5) DS8024: RSTIN has no further effect on CLK after t5.

If the applied clock is not needed, set CMDVCC low with RSTIN low. In this case, CLK starts at t<sub>3</sub> (minimum 200ns after the transition on I/O, see Figure 4); after t<sub>5</sub>, RSTIN can be set high to obtain an answer to request (ATR) from an inserted smart card. Do not perform activation with RSTIN held permanently high.

#### Active Mode

When the activation sequence is completed, the DS8024 card interface is in active mode. The host microcontroller and the smart card exchange data on the I/O lines.

Figure 3. Activation Sequence Using RSTIN and CMDVCC

Figure 4. Activation Sequence at t3

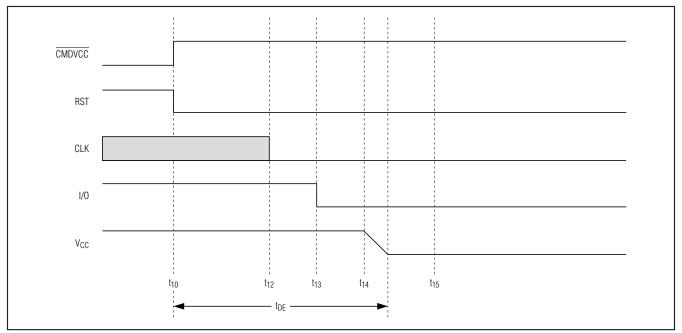

Figure 5. Deactivation Sequence

**DS8024**

## **Smart Card Interface**

### **Deactivation Sequence**

When the host microcontroller is done communicating with the smart card, it sets the CMDVCC line high to execute an automatic deactivation sequence and returns the card interface to the inactive mode.

The following sequence of events occurs during a deactivation sequence (Figure 5):

- 1) RST goes low (t<sub>10</sub>).

- 2) CLK is held low ( $t_{12} = t_{10} + 0.5 \times T$ ), where T is 64 times the period of the internal oscillator (approximately 25µs).

- 3) I/O, AUX1, and AUX2 are pulled low ( $t_{13} = t_{10} + T$ ).

- 4) V<sub>CC</sub> starts to fall ( $t_{14} = t_{10} + 3T$ ).

- 5) When V<sub>CC</sub> reaches its inactive state, the deactivation sequence is complete (at t<sub>DE</sub>).

- 6) All card contacts become low impedance to GND; I/OIN, AUX1IN, and AUX2IN remain at V<sub>DD</sub> (pulled up through an internal  $11k\Omega$  resistor).

- 7) The internal oscillator returns to its lower frequency.

#### Vcc Generator

The card voltage (V<sub>CC</sub>) generator can supply up to 80mA continuously at 5V or 65mA at 3V. An internal overload detector triggers at approximately 120mA. Current samples to the detector are filtered. This allows spurious current pulses (with a duration of a few  $\mu$ s) up to 200mA to be drawn without causing deactivation. The average current must stay below the specified maximum current value.

See the *Applications Information* section for recommendations to help maintain V<sub>CC</sub> voltage accuracy.

#### Fault Detection

The DS8024 integrates circuitry to monitor the following fault conditions:

- Short-circuit or high current on VCC

- Card removal while the interface is activated

- V<sub>DD</sub> dropping below threshold

- Card voltage generator operating out of the specified values (V<sub>DDA</sub> too low or current consumption too high)

- Overheating

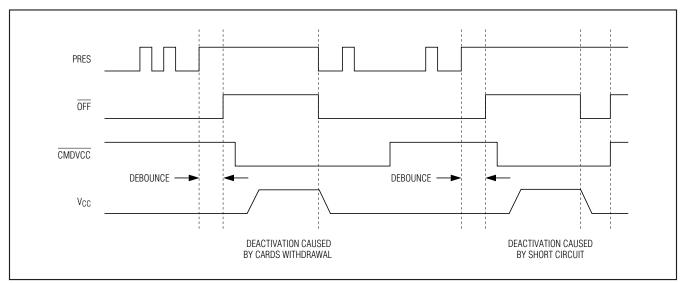

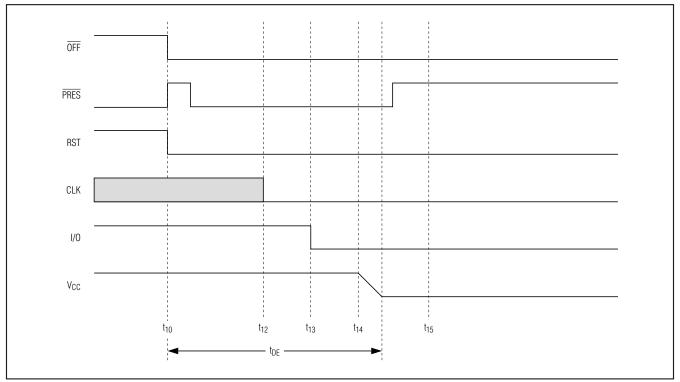

There are two different cases for how the DS8024 reacts to fault detection (Figure 6):

- Outside a Card Session (CMDVCC High). Output OFF is low if a card is not in the card reader and high if a card is in the reader. The V<sub>DD</sub> supply is monitored—a decrease in input voltage generates an internal power-on reset pulse but does not affect the OFF signal. Short-circuit and temperature detection are disabled because the card is not powered up.

- Within a Card Session (CMDVCC Low). Output OFF goes low when a fault condition is detected, and an emergency deactivation is performed automatically (Figure 7). When the system controller resets CMDVCC to high, it may sense the OFF level again after completing the deactivation sequence. This distinguishes between a card extraction and a hardware problem (OFF goes high again if a card is present). Depending on the connector's card-present switch (normally closed or normally open) and the mechanical characteristics of the switch, bouncing can occur on the PRES signals at card insertion or withdrawal.

The DS8024 has a debounce feature with an 8ms typical duration (Figure 6). When a card is inserted, output OFF goes high after the debounce time delay. When the card is extracted, an automatic deactivation sequence of the card is performed on the first true/false transition on PRES and output OFF goes low.

### Stop Mode (Low-Power Mode)

The DS8024 (like the TDA8024) does not support a lowpower stop mode. For applications requiring low-power support, refer to the DS8113.

### Smart Card Power Select

The DS8024 supports two smart card V<sub>CC</sub> voltages: <u>3V</u> and 5V. The power select is controlled by the 5V/<u>3V</u> signal as shown in Table 3. V<sub>CC</sub> is 5V if 5V/<u>3V</u> is asserted to a logic-high state, and V<sub>CC</sub> is 3V if 5V/<u>3V</u> is pulled to a logic-low state.

#### Table 3. VCC Select and Operation Mode

| 5V/3V | CMDVCC | V <sub>CC</sub><br>SELECT (V) | CARD INTERFACE<br>STATUS |

|-------|--------|-------------------------------|--------------------------|

| 0     | 0      | 3                             | Activated                |

| 0     | 1      | 3                             | Inactivated              |

| 1     | 0      | 5                             | Activated                |

| 1     | 1      | 5                             | Inactivated              |

Figure 6. Behavior of PRES, OFF, CMDVCC, and V<sub>CC</sub>

Figure 7. Emergency Deactivation Sequence (Card Extraction)

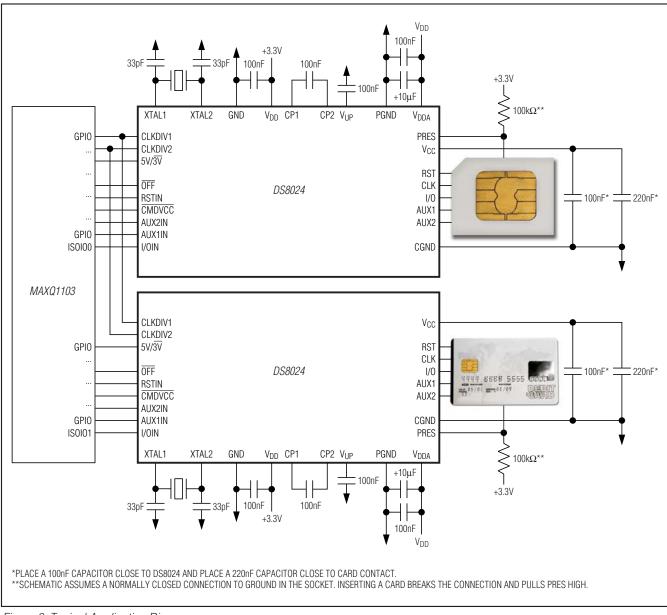

Figure 8. Typical Application Diagram

### **Applications Information**

Performance can be affected by the layout of the application. For example, an additional cross-capacitance of 1pF between card reader contacts C2 (RST) and C3 (CLK) or C2 (RST) and C7 (I/O) can cause contact C2 to be polluted with high-frequency noise from C3 (or C7). In this case, include a 100pF capacitor between contacts C2 and CGND.

Application recommendations include the following:

- Ensure there is ample ground area around the DS8024 and the connector; place the DS8024 very near to the connector; decouple the V<sub>DD</sub> and V<sub>DDA</sub> lines separately. These lines are best positioned under the connector.

- The DS8024 and the host microcontroller must use the same V<sub>DD</sub> supply. Pins CLKDIV1, CLKDIV2, RSTIN, PRES, AUX1IN, I/OIN, AUX2IN, 5V/3V, CMDVCC, and OFF are referenced to V<sub>DD</sub>; if pin XTAL1 is to be driven by an external clock, also reference this pin to V<sub>DD</sub>.

- Trace C3 (CLK) should be placed as far as possible from the other traces.

- The trace connecting CGND to C5 (GND) should be straight (the two capacitors on C1 (V<sub>CC</sub>) should be connected to this ground trace).

- Avoid ground loops among CGND, PGND, and GND.

- Decouple V<sub>DDA</sub> and V<sub>DD</sub> separately; if the two supplies are the same in the application, they should be connected in a star on the main trace.

- Connect a 100nF capacitor (ESR < 100mΩ) between V<sub>CC</sub> and CGND and place near the DS8024's V<sub>CC</sub> pin.

- Connect a 100nF or 220nF capacitor (220nF preferred, ESR < 100m $\Omega$ ) between V<sub>CC</sub> and CGND and place near the smart card socket's C1 contact.

With all these layout precautions, noise should be kept to an acceptable level and jitter on C3 (CLK) should be less than 100ps.

### Technical Support

For technical support, go to <u>https://support.maxim-integrated.com/micro</u>.

#### \_Selector Guide

| PART          | CURRENT<br>VOLTAGES<br>SUPPORTED (V) | SUPPORTS<br>STOP<br>MODE? | PIN-<br>PACKAGE |

|---------------|--------------------------------------|---------------------------|-----------------|

| DS8024-RJX+   | 3.0, 5.0                             | No                        | 28 TSSOP        |

| DS8024-RJX/V+ | 3.0, 5.0                             | No                        | 28 TSSOP        |

| DS8024-RRX+   | 3.0, 5.0                             | No                        | 28 SO           |

**Note:** Contact the factory for availability of other variants and package options.

+Denotes a lead(Pb)-free/RoHS-compliant package.

N denotes an automotive qualified part.

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE  | PACKAGE<br>CODE | OUTLINE NO.    | LAND<br>PATTERN NO. |

|------------------|-----------------|----------------|---------------------|

| 28 SO (300 mils) | W28+6           | <u>21-0042</u> | <u>90-0109</u>      |

| 28 TSSOP         | U28+1           | <u>21-0066</u> | <u>90-0171</u>      |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                             |          |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------|----------|

| 0                  | 6/08             | Initial release                                                                                                         | _        |

| 1                  | 8/08             | Clarified the V <sub>DDA</sub> specification in the <i>Recommended DC Operating Conditions</i> table                    | 2        |

| 2                  | 2/12             | Added the automotive TSSOP version to the Ordering Information and Selector Guide; updated the Absolute Maximum Ratings | 1, 2, 14 |

| 3                  | 7/12             | Added footnote to the resistor value on the PRES pin in Figure 8                                                        | 13       |

| 4                  | 4/13             | Clarified t <sub>1</sub> , t <sub>5</sub> , and t <sub>14</sub>                                                         | 9, 11    |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

#### Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000

© 2013 Maxim Integrated Products, Inc.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - Specialised category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

CY7C910-51LMB MEC1632-AUE RKSAS4 HMC677G32 LPC47N207-JV FTP-637DSL633R SM712GX04LF04-BA MCW1001A-I/SS HOA6241-001 SC74HC4066ADTR2G NCN5120MNTWG NCN5150DR2G NCN8025MTTBG C100N50Z4A DG407AK/883B SRT2-ATT01 TDA8035HN/C1/S1J LTC1694CS5#TRMPBF DS90UB947TRGCRQ1 SP510ECF-L NCS2300MUTAG ADG1404YCPZ-REEL HMC677LP5E HMC677LP5ETR LTC1756EGN#PBF LTC1955EUH#PBF LT3669EUFD-2#PBF LTC6820HMS#3ZZTRPBF MXL1543BCAI MAX3170CAI+ XL1192D CP82C59AZ KTU1109EFAA-TR CH368L CH7307C-DEF LTC1694-1IS5#TRMPBF LTC1694CS5#TRPBF LTC1694IS5#TRM 73S8024RN-20IMF 73S8024RN-IL/F DS2413P+ DS2413P+T&R DS28E17Q+ DS8113-RNG+ MAX13174ECAG+ MAX216CWN+ MAX3172CAI+ AS8222-HSSM MAX6618AUB+ MAX6817MUT+T