### **General Description**

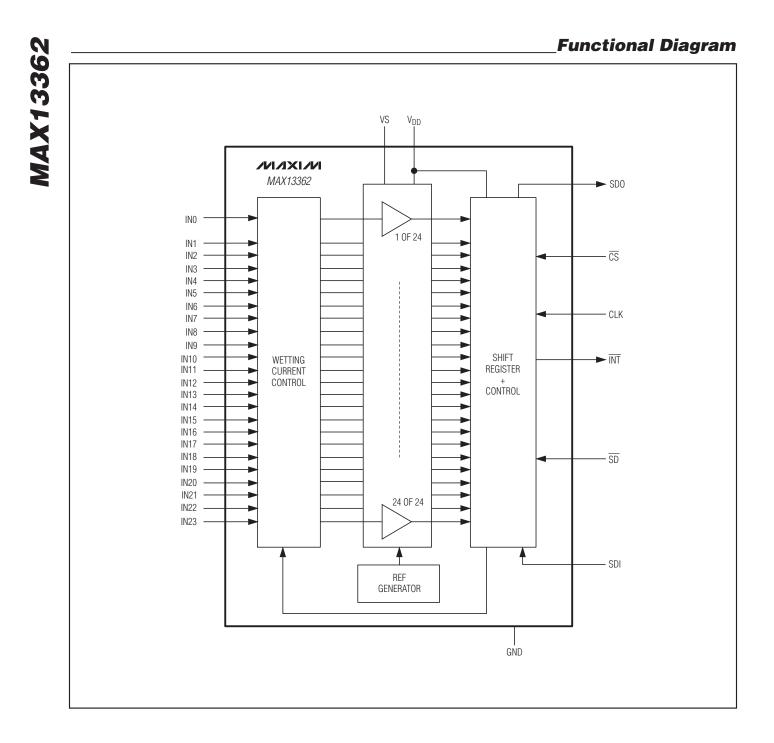

The MAX13362 is a 24-channel automotive contact monitor designed as an interface between mechanical switches and low-voltage processors or other logic circuits. The IC operates over a voltage range of 5.5V to 28V, and withstands voltages up to 40V. It protects lowvoltage circuitry from high voltages and reverse battery conditions. The MAX13362's low-current operation under all operating conditions makes it suitable for use in electronic control units (ECUs) that are connected directly to the automotive battery. It has an adjustable scan mode that significantly reduces the current drawn in key-off.

19-4464; Rev 0; 2/09

EVALUATION KIT AVAILABLE

The MAX13362 features an SPI™ interface to monitor the switch status and set the device configuration. Multiple MAX13362s can be cascaded to support any multiple of 24 switches.

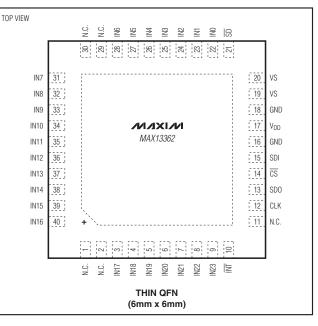

The MAX13362 is available in a 6mm x 6mm, 40-pin thin QFN package and operates over the -40°C to +125°C temperature range.

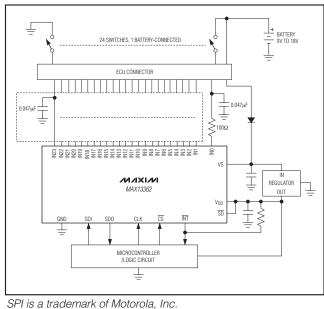

**Typical Application Circuit**

### **Applications**

Automotive Body Controllers Automotive Door Modules Automotive Smart Junction Boxes

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **Features**

9V to 18V Operating Voltage Range with Full Performance

- Fully Functional Range of 5.5V to 28V

- Switch Inputs Withstand 27V

- Switch Inputs Withstand Reverse Battery

- Ultra-Low Operating Current 100µA (typ) in Scan Mode

- Built-In Switching Hysteresis

- Built-In Switch Deglitching

- CMOS-Compatible Logic Outputs Down to 3.0V

- Interrupt Output to Processor

- Configurable Wetting Current (0mA, 5mA, 10mA, or 15mA) for Each Switch Input

- AEC-Q100 Qualified

# **Ordering Information**

| PART           | TEMP RANGE      | PIN-PACKAGE                    |

|----------------|-----------------|--------------------------------|

| MAX13362ATL/V+ | -40°C to +125°C | 40 Thin QFN-EP*<br>(6mm x 6mm) |

\*EP = Exposed pad.

+Denotes a lead(Pb)-free/RoHS-compliant package. N Denotes an automotive qualified part.

# **Pin Configuration**

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATING**

| V <sub>DD</sub> , CLK, SDI, CS to GND  | 0.3V to +6V                          |

|----------------------------------------|--------------------------------------|

| VS, SD, INT to GND                     | 0.3V to +40V                         |

| IN0–IN23 to GND                        | 15V to +27V                          |

| SDO to GND                             | 0.3V to $(V_{DD} + 0.3V)$            |

| ESD Protection, All Pins (HBM)         | ±2kV                                 |

| ESD Protection on Pins INO-IN23 to IEC |                                      |

| (with added 0.047µF capacitor, and,    | /or 100 $\Omega$ resistor) $\pm$ 8kV |

| Current Into Any Pin±20mA                             |

|-------------------------------------------------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| (derate 37mW/°C above +70°C)(multilayer board)2963mW  |

| Operating Temperature Range40°C to +125°C             |

| Junction Temperature40°C to +150°C                    |

| Storage Temperature Range65°C to +150°C               |

| Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

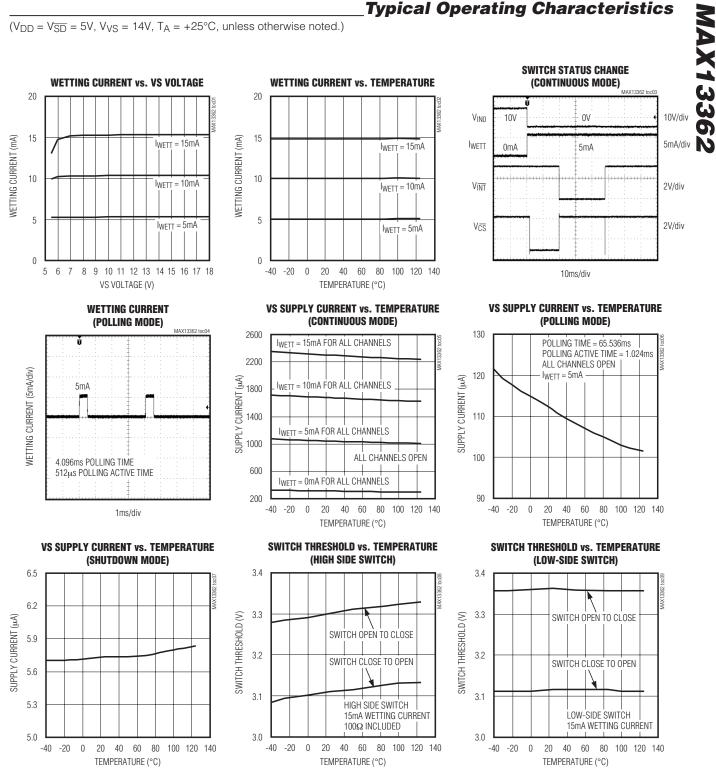

$(V_{DD} = 5V, V_{VS} = 14V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                                            | SYMBOL            | CONDITIONS                                                                                                                                                  | MIN  | ТҮР  | МАХ   | UNITS |

|------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|

| POWER SUPPLY                                         |                   | ·                                                                                                                                                           |      |      |       |       |

| V <sub>DD</sub> Operating Supply Range               | V <sub>DD</sub>   |                                                                                                                                                             | 3    |      | 5.5   | V     |

| V <sub>DD</sub> Supply Current                       | IDD               |                                                                                                                                                             |      | 0.1  | 10    | μΑ    |

| VS Supply Range                                      | Vvs               | (Note 1)                                                                                                                                                    | 5.5  |      | 28    | V     |

| VS Undervoltage Lockout                              | Vuvlo             |                                                                                                                                                             | 3    |      | 5.5   | V     |

|                                                      |                   | $t_{POLL} = 64ms$ , $t_{POLL\_ACT} = 1ms$ ; $\overline{LP}$ bit in<br>internal register = 0, 24 channels active, all<br>switches open, $T_A = +25^{\circ}C$ |      | 100  | 170   |       |

| Total Supply Current (Flowing into VS and $V_{DD}$ ) | ISUP              | $t_{POLL} = 64ms$ , $t_{POLL\_ACT} = 1ms$ ; $\overline{LP}$ bit in<br>internal register = 0, 24 channels active, all<br>switches open                       |      | 100  | 200   | μA    |

|                                                      |                   | Continuous polling mode, wetting current set to 5mA                                                                                                         |      | 1000 |       |       |

| VS Supply Current in Shutdown<br>Mode                | ISDVS             | $V_{\overline{SD}} = 0$ , $V_{VS} = 14V$ , all switches open, $T_A = +25^{\circ}C$                                                                          |      | 6    | 10    | μA    |

| V <sub>DD</sub> Supply Current in Shutdown<br>Mode   | ISDVDD            | $V_{\overline{SD}} = 0$ , $V_{VS} = 14V$ , $T_A = +25^{\circ}C$                                                                                             |      | 0.1  | 5     | μA    |

| SWITCH INPUTS                                        |                   | ·                                                                                                                                                           |      |      |       |       |

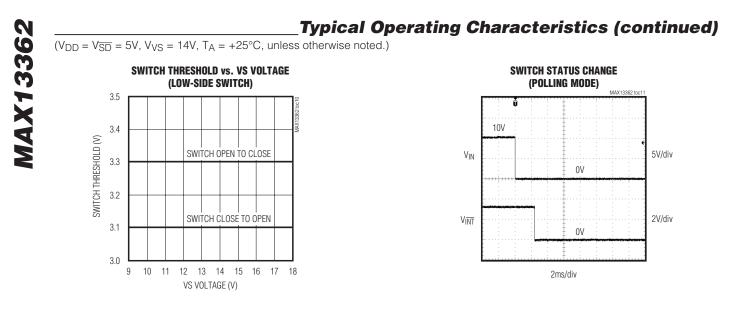

| Input Voltage Threshold                              | V <sub>TH</sub>   | $V_{VS}$ = 5.5V to 28V, measured with 100 $\Omega$ series resistor for high-side switches                                                                   | 2.5  |      | 3.7   | V     |

| Input Hysteresis                                     | V <sub>H</sub>    | $V_{VS}$ = 5.5V to 28V, measured with 100 $\Omega$ series resistor for high-side switches                                                                   |      | 0.2  |       | V     |

| Wetting Current Rise/Fall Time                       | tIWETT            |                                                                                                                                                             |      | 5    |       | μs    |

| Watting Ourset                                       | L                 | Wetting current set to 15mA,<br>$9V \le V_{VS} \le 18V$                                                                                                     | 12.7 | 15   | 17.25 | mA    |

| Wetting Current                                      | IWETT             | Wetting current set to 15mA,<br>(5.5V $\leq$ V <sub>VS</sub> < 9V) or (18V < V <sub>VS</sub> $\leq$ 28V)                                                    | 10.5 | 15   | 19.5  | mA    |

| IN0–IN23 Input Current                               |                   | $V_{IN_{}} = 0, T_{A} = +25^{\circ}C$                                                                                                                       |      |      | 2     |       |

|                                                      | I <sub>IN</sub> _ | V <sub>IN</sub> = 14V, T <sub>A</sub> = +25°C (Note 2)                                                                                                      |      | 16   | 30    | μA    |

| IN0–IN23 Input Leakage Current<br>in Shutdown        | ILEAKSD           | $V_{VS} = 0 \text{ or } 14V, V_{\overline{SD}} = 0, T_A = +25^{\circ}C$                                                                                     |      |      | ±2    | μA    |

| IN4–IN23 Dropout Voltage                             | VDO15             | IWETT = 15mA (Note 3)                                                                                                                                       |      | 2.8  | 4.0   | V     |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V, V_{VS} = 14V, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                             | SYMBOL              | CONDITIONS                                            | MIN                    | ТҮР  | MAX                    | UNITS |

|-----------------------------------------------------------------------|---------------------|-------------------------------------------------------|------------------------|------|------------------------|-------|

| LOGIC LEVELS                                                          | •                   | •                                                     | •                      |      |                        |       |

| INT Output-Voltage Low                                                | Volint              | Sinking 1mA                                           |                        |      | 0.4                    | V     |

| SDO Output-Voltage Low                                                | Volsdo              | Sinking 1mA                                           |                        |      | 0.2 x V <sub>DD</sub>  | V     |

| SDO Output-Voltage High                                               | Vohsdo              | Sourcing 1mA                                          | 0.8 x V <sub>DD</sub>  |      |                        | V     |

| SDO Leakage Current in High-<br>Impedance Mode                        | ILSDO               | $V_{\overline{CS}} = 5V$                              | -1                     |      | +1                     | μA    |

| SDI, CLK, CS Input-Voltage Low                                        | VIL                 |                                                       |                        | (    | ).33 x V <sub>DD</sub> | V     |

| SDI, CLK, CS Input-Voltage High                                       | VIH                 |                                                       | 0.66 x V <sub>DE</sub> | )    |                        | V     |

| SD Input Low Voltage                                                  | VILSD               |                                                       | 0.8                    |      |                        | V     |

| SD Input High Voltage                                                 | VIHSD               |                                                       |                        |      | 2.4                    | V     |

| SDI Internal Pulldown Resistor                                        | R <sub>PD</sub>     |                                                       | 30                     | 50   | 120                    | kΩ    |

| CLK Pin Leakage                                                       | ILEAKCLK            | $V_{CLK} = 5V, T_A = +25^{\circ}C$                    |                        |      | 1                      | μA    |

| CS Pin Leakage                                                        | ILEAKCS             | $V_{\overline{CS}} = 5V, T_A = +25^{\circ}C$          |                        |      | 1                      | μA    |

| SD Pin Leakage                                                        | ILEAKSD             | $V_{\overline{SD}} = 5V, T_A = +25^{\circ}C$          |                        |      | 1                      | μA    |

| INT Pin Leakage                                                       | ILEAKINT            | $V_{\overline{INT}}$ = high impedance, $T_A$ = +25°C  |                        |      | 1                      | μA    |

| THERMAL SHUTDOWN                                                      |                     |                                                       |                        |      |                        |       |

| Thermal Shutdown Threshold                                            | TSHDN               | Temperature rising (Note 4)                           | +150                   | +165 |                        | °C    |

| Thermal Shutdown Hysteresis                                           | THYST               |                                                       |                        | 15   |                        | °C    |

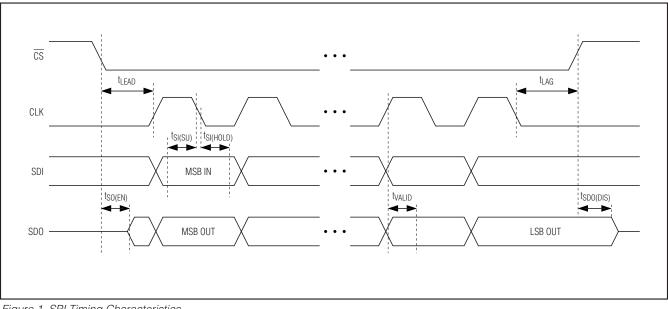

| TIMING                                                                |                     |                                                       |                        |      |                        |       |

| Switch Inputs Deglitching Time                                        | tgт                 |                                                       | 37                     | 50   | 63                     | μs    |

| CLK Frequency Range                                                   | fCLK                | (Note 4)                                              | 0.01                   |      | 4                      | MHz   |

| Falling Edge of CS to Rising<br>Edge of CLK Setup Time                | tlead               | Polling mode, input rise/fall time<br>< 10ns (Note 4) | 100                    |      |                        | ns    |

| Falling Edge of CLK to Rising<br>Edge of CS Setup Time                | tlag                | Input rise/fall time < 10ns<br>(Note 4)               | 100                    |      |                        | ns    |

| SDI-to-CLK Falling Edge Setup<br>Time                                 | tsi(su)             | (Note 4)                                              | 30                     |      |                        | ns    |

| SDI Hold Time After Falling Edge of CLK                               | tsi(HOLD)           | (Note 4)                                              | 20                     |      |                        | ns    |

| Time from Rising Edge of CLK to<br>SDO Data Valid                     | tvalid              | C <sub>SDO</sub> = 50pF (Note 3)                      |                        |      | 70                     | ns    |

| Time from Falling Edge of $\overline{\text{CS}}$ to SDO Low Impedance | t <sub>SO(EN)</sub> | (Note 4)                                              |                        |      | 55                     | ns    |

| Time from Rising Edge of CS to SDO High Impedance                     | tsdo(dis)           | (Note 4)                                              |                        |      | 55                     | ns    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V, V_{VS} = 14V, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                              | SYMBOL         | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|----------------------------------------|----------------|------------|-----|-----|-----|-------|

| Polling Active Time Accuracy           | tpoll_act      |            | -20 |     | +20 | %     |

| Polling Time Accuracy                  | <b>t</b> POLL  |            | -20 |     | +20 | %     |

| Time from Shutdown to Normal Operation | <b>t</b> START |            |     | 0.1 | 1   | ms    |

Note 1: When V<sub>VS</sub> is above 28V, the wetting current is disabled to limit power dissipation, and the switch inputs are not monitored. When V<sub>VS</sub> returns, there is a 1ms blanking time before the external switches are polled.

**Note 2:** This current only flows during the polling active time thus the average value is much lower. For example with a polling time of 64ms and a polling active time of 1ms the average current on an input when connected to 14V is typically  $16\mu A \times 1/64 = 0.25\mu A$ .

Note 3: Difference between VS and IN\_ voltage when wetting current has dropped to 90% of its nominal value.

Note 4: Guaranteed by design.

Figure 1. SPI Timing Characteristics

5

# **Pin Description**

| PIN                 | NAME            | FUNCTION                                                                                                                                                                                                                                                                                            |

|---------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 11,<br>29, 30 | N.C.            | No Connection. Not internally connected.                                                                                                                                                                                                                                                            |

| 3                   | IN17            | Switch Monitor Input Channel 17. Connect IN17 to a ground-connected switch.                                                                                                                                                                                                                         |

| 4                   | IN18            | Switch Monitor Input Channel 18. Connect IN18 to a ground-connected switch.                                                                                                                                                                                                                         |

| 5                   | IN19            | Switch Monitor Input Channel 19. Connect IN19 to a ground-connected switch.                                                                                                                                                                                                                         |

| 6                   | IN20            | Switch Monitor Input Channel 20. Connect IN20 to a ground-connected switch.                                                                                                                                                                                                                         |

| 7                   | IN21            | Switch Monitor Input Channel 21. Connect IN21 to a ground-connected switch.                                                                                                                                                                                                                         |

| 8                   | IN22            | Switch Monitor Input Channel 22. Connect IN22 to a ground-connected switch.                                                                                                                                                                                                                         |

| 9                   | IN23            | Switch Monitor Input Channel 23. Connect IN23 to a battery-connected or ground-connected switch. When used for a battery-connected switch, add a $100\Omega$ series protection resistor to the input.                                                                                               |

| 10                  | ĪNT             | Interrupt Output. INT is an open-drain output that asserts low when one or more of the inputs (IN0–IN23) change state and are enabled for interrupts, or when the overtemperature threshold is exceeded.                                                                                            |

| 12                  | CLK             | SPI Serial Clock Input                                                                                                                                                                                                                                                                              |

| 13                  | SDO             | SPI Serial Data Output. SPI data is output on SDO on the rising edges of CLK while $\overline{CS}$ is held low.<br>SDO is high impedance when $\overline{CS}$ is high. Connect SDO to a microcontroller data input or to a succeeding device in a daisy chain.                                      |

| 14                  | CS              | SPI Chip-Select Input. Drive $\overline{CS}$ low to enable clocking of data into and out of the IC. SPI data is latched into the device on the rising edge of $\overline{CS}$ .                                                                                                                     |

| 15                  | SDI             | SPI Serial Data Input. SPI data is latched into the internal shift register on the falling edges of CLK while $\overline{CS}$ is held low. SDI has an internal 50k $\Omega$ pulldown resistor. Connect SDI to the SDO of a preceding device in a daisy chain or to the microcontroller data output. |

| 16, 18              | GND             | Ground. Pins 16 and 18 must be connected to ground.                                                                                                                                                                                                                                                 |

| 17                  | V <sub>DD</sub> | Logic Supply Voltage. Connect $V_{DD}$ to a 3.3V or 5V logic supply. Bypass $V_{DD}$ to GND with at least a 0.1µF capacitor placed as close as possible to $V_{DD}$ .                                                                                                                               |

# \_\_\_\_\_Pin Description (continued)

| PIN    | NAME | FUNCTION                                                                                                                                                                                                                                      |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19, 20 | VS   | Supply Voltage Input. VS should be protected from reverse battery using a series diode. Bypass VS to GND with a $0.1\mu$ F ceramic capacitor placed as close as possible to VS. In addition, bypass VS with a $47\mu$ F or greater capacitor. |

| 21     | SD   | Shutdown Input. Drive $\overline{SD}$ low to place the IC into shutdown mode. Drive $\overline{SD}$ high for normal operation.<br>$\overline{SD}$ is battery-voltage compatible.                                                              |

| 22     | INO  | Switch Monitor Input Channel 0. Connect IN0 to a battery-connected or ground-connected switch. When used for a battery-connected switch, add a $100\Omega$ series protection resistor to the input.                                           |

| 23     | IN1  | Switch Monitor Input Channel 1. Connect IN1 to a battery-connected or ground-connected switch. When used for a battery-connected switch, add a $100\Omega$ series protection resistor to the input.                                           |

| 24     | IN2  | Switch Monitor Input Channel 2. Connect IN2 to a battery-connected or ground-connected switch. When used for a battery-connected switch, add a $100\Omega$ series protection resistor to the input.                                           |

| 25     | IN3  | Switch Monitor Input Channel 3. Connect IN3 to a battery-connected or ground-connected switch. When used for a battery-connected switch, add a $100\Omega$ series protection resistor to the input.                                           |

| 26     | IN4  | Switch Monitor Input Channel 4. Connect IN4 to a ground-connected switch.                                                                                                                                                                     |

| 27     | IN5  | Switch Monitor Input Channel 5. Connect IN5 to a ground-connected switch.                                                                                                                                                                     |

| 28     | IN6  | Switch Monitor Input Channel 6. Connect IN6 to a ground-connected switch.                                                                                                                                                                     |

| 31     | IN7  | Switch Monitor Input Channel 7. Connect IN7 to a ground-connected switch.                                                                                                                                                                     |

| 32     | IN8  | Switch Monitor Input Channel 8. Connect IN8 to a ground-connected switch.                                                                                                                                                                     |

| 33     | IN9  | Switch Monitor Input Channel 9. Connect IN9 to a ground-connected switch.                                                                                                                                                                     |

| 34     | IN10 | Switch Monitor Input Channel 10. Connect IN10 to a ground-connected switch.                                                                                                                                                                   |

| 35     | IN11 | Switch Monitor Input Channel 11. Connect IN11 to a ground-connected switch.                                                                                                                                                                   |

| 36     | IN12 | Switch Monitor Input Channel 12. Connect IN12 to a ground-connected switch.                                                                                                                                                                   |

| 37     | IN13 | Switch Monitor Input Channel 13. Connect IN13 to a ground-connected switch.                                                                                                                                                                   |

| 38     | IN14 | Switch Monitor Input Channel 14. Connect IN14 to a ground-connected switch.                                                                                                                                                                   |

| 39     | IN15 | Switch Monitor Input Channel 15. Connect IN15 to a ground-connected switch.                                                                                                                                                                   |

| 40     | IN16 | Switch Monitor Input Channel 16. Connect IN16 to a ground-connected switch.                                                                                                                                                                   |

| _      | EP   | Exposed Pad. Connect EP to GND for enhanced thermal performance.                                                                                                                                                                              |

### **Detailed Description**

The MAX13362 is a 24-channel automotive contact monitor designed as an interface between mechanical switches and low-voltage microcontrollers or other logic circuits. It features an SPI interface to monitor individual switch inputs and to configure interrupt capability, wetting current, switch configuration (battery-connected or ground-connected), polling time and polling active time. Any switch status change will cause an interrupt signal if the switch is interrupt enabled. The MAX13362 has three modes of operation: continuous mode, polling mode, and shutdown mode.

#### **V**<sub>DD</sub> and **V**S

$V_{DD}$  is the power-supply input for the logic input/ output circuitry. Connect  $V_{DD}$  to a 3V to 5.5V logic-level supply. Bypass  $V_{DD}$  to GND with at least a 0.1µF capacitor placed as close as possible to  $V_{DD}$ .

VS is the main power-supply input. Bypass VS to GND with a 0.1 $\mu$ F ceramic capacitor placed as close as possible to VS. In addition, bypass VS with a 47 $\mu$ F or greater capacitor.

### Mechanical Switch Inputs (IN0–IN23)

INO–IN23 are the inputs for remote mechanical switches. The switch status is indicated by the S0–S23 bits in the status register, and each switch input can be programmed to assert an interrupt (INT) by writing to the IEO–IE23 bits in the command register. All switch inputs are interrupt disabled upon power-up.

The IN4–IN22 inputs are intended for ground-connected switches. The IN0–IN3 and IN23 inputs can be programmed for either ground-connected switches or battery-connected switches by writing to the LH0–LH3 and LH23 bits (see Table 2). The default configuration of the IN0–IN3 and IN23 inputs after power-up is for ground-connected switches.

### Wetting Current

The MAX13362 applies a programmable wetting current to any closed switch to clean switch contacts that are exposed to adverse conditions. The wetting current for each switch can be set to 0mA, 5mA, 10mA, or 15mA by the W\_.0 and W\_.1 data bits in the command registers (see Table 5) by means of an SPI data transaction.

When using wetting current, special care must be taken to avoid exceeding the maximum power dissipation of the MAX13362 (see the *Applications Information* section). Disabling the wetting current or limiting the active-wetting current time reduces power consumption. The default state upon power-up is with wetting current disabled.

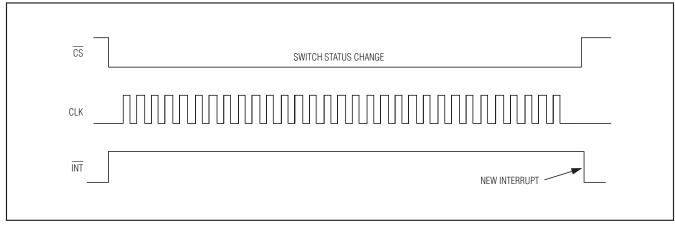

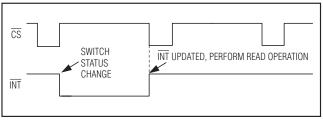

### Interrupt Output (INT)

INT is an active-low, open-drain output that asserts low when any of the switch inputs change state and is enabled for interrupts, or when the overtemperature threshold is exceeded. An external pullup resistor to  $V_{DD}$  is needed on INT. INT is cleared when  $\overline{CS}$  is driven low for a read/write operation. However, in polling mode, any switch state change or overtemperature change which occurs during an SPI transaction is stored and causes an additional interrupt after the SPI transaction is over and  $\overline{CS}$  goes high (shown in Figure 2).

If  $V_{DD}$  is absent, the  $\overline{INT}$  output is functional provided that it is pulled up to a different supply voltage.

Figure 2. Switch State Change During the SPI transaction

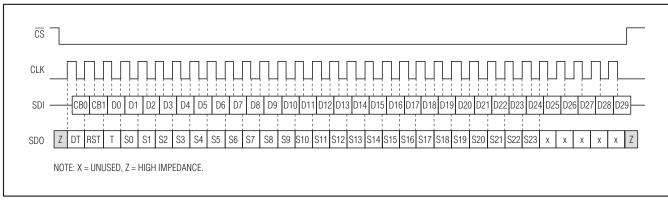

#### Serial Peripheral Interface (CS, SDO, SDI, CLK)

The MAX13362 operates as a serial peripheral interface (SPI) slave device. An SPI master accesses and programs the MAX13362 by reading/writing the control registers. The control registers are 32 bits wide, have 2 command bits (or register addresses) and 30 data bits (see Table 1). Figure 3 shows the read/write sequence through SPI. The SPI logic counts the number of bits clocked into the IC (using a modulo-32 counter so that daisy chaining is possible) and enables data latching only if exactly 32 bits (or an integer multiple thereof) have been clocked in.

#### Status Register

The status register contains the status of the switches connected to INO–IN23. The status register also contains an overtemperature warning bit, a power-on-reset bit and a device type bit (see Table 1). The status register is accessed by the SPI-compatible interface.

Figure 3. SPI Read/Write Sequence

### Table 1. Bit Description

| BIT NAME | BIT DESCRIPTION                                                                                                                                                                        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CB0, CB1 | Command bits. Select the internal register to which data bits D0–D29 are to be written.                                                                                                |

| D0-D29   | Data bits.                                                                                                                                                                             |

| S0-S23   | Switch state bit. 0 = switch open, 1 = switch closed.                                                                                                                                  |

| Т        | Overtemperature bit. When overtemperature occurs, this bit is set to 1. It is reset on the rising edge of $\overline{CS}$ .                                                            |

| RST      | Power-on-reset bit. It indicates whether the IC has had a power-on-reset since the last SPI read. $0 =$ device has been reset. RST is set to 1 on the rising edge of $\overline{CS}$ . |

| DT       | Device type. 0 = reserved for future use, 1 = MAX13362.                                                                                                                                |

MAX13362

ground connected.

### Command Register

Three 32-bit command registers are used to configure the MAX13362 for various modes of operation and are accessed by the SPI-compatible interface (see Table 2).

### Table 2. Command Register Map

|          |     |     |     |     |           |           |           | -         |           |           | -         |           |           |           |           |           |           |           |          |          |          |          |          |          |          |          |          |          |    |     |     |

|----------|-----|-----|-----|-----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----|-----|-----|

| D29      | D28 | D27 | D26 | D25 | D24       | D23       | D22       | D21       | D20       | D19       | D18       | D17       | D16       | D15       | D14       | D13       | D12       | D11       | D10      | D9       | D8       | D7       | D6       | D5       | D4       | D3       | D2       | D1       | D0 | CB1 | CB0 |

| х        | τ́р | PA2 | PA1 | PA0 | W23.<br>0 | W22.<br>0 | W21<br>.0 | W20<br>.0 | W19<br>.0 | W18<br>.0 | W17<br>.0 | W16.<br>0 | W15<br>.0 | W14<br>.0 | W13<br>.0 | W12<br>.0 | W11<br>.0 | W10<br>.0 | W9.<br>0 | W8.<br>0 | W7.<br>0 | W6.<br>0 | W5.<br>0 | W4.<br>0 | W3.<br>0 | W2.<br>0 | W1.<br>0 | W0.<br>0 | Х  | 0   | 0   |

| х        | P3  | P2  | P1  | P0  | W23.<br>1 | W22.<br>1 | W21<br>.1 | W20<br>.1 | W19<br>.1 | W18<br>.1 | W17<br>.1 | W16.<br>1 | W15<br>.1 | W14<br>.1 | W13<br>.1 | W12<br>.1 | W11<br>.1 | W10<br>.1 | W9.<br>1 | W8.<br>1 | W7.<br>1 | W6.<br>1 | W5.<br>1 | W4.<br>1 | W3.<br>1 | W2.<br>1 | W1.<br>1 | W0.<br>1 | Х  | 0   | 1   |

| LH2<br>3 | LH3 | LH2 | LH1 | LH0 | IE23      | IE22      | IE21      | IE20      | IE19      | IE18      | IE17      | IE16      | IE15      | IE14      | IE13      | IE12      | IE11      | IE10      | IE9      | IE8      | IE7      | IE6      | IE5      | IE4      | IE3      | IE2      | IE1      | IE0      | Х  | 1   | 0   |

|          |     |     |     |     |           |           |           |           |           |           | Ν         | NO OF     | ERAT      | ION (N    | IO DA     | TA WF     | RITTEN    | 1)        |          |          |          |          |          |          |          |          |          |          |    | 1   | 1   |

*LH\_: Switch Configuration for IN0–IN3 and IN23* The LH0–LH3 and LH23 bits set the switch configuration for IN0–IN3 and IN23, respectively. Set LH\_ to 0 to configure the input channel to ground connected. Set LH\_ to1 to configure the input channel to battery connected. P0–P3: Polling Time

P0–P3 are used to set the polling time as shown in Table 3.

The default configuration after power-on is  $LH_{-} = 0$ ,

#### PA0–PA2: Polling Active Time

PA0–PA2 are used to set the polling active time as shown in Table 4.

### Table 3. Polling Time Setting

|    | 1  |    | r  |                   |

|----|----|----|----|-------------------|

| P3 | P2 | P1 | P0 | POLLING TIME (ms) |

| 0  | 0  | 0  | 0  | Continuous*       |

| 0  | 0  | 0  | 1  | 4.096             |

| 0  | 0  | 1  | 0  | 4.096             |

| 0  | 0  | 1  | 1  | 4.096             |

| 0  | 1  | 0  | 0  | 4.096             |

| 0  | 1  | 0  | 1  | 4.096             |

| 0  | 1  | 1  | 0  | 8.192             |

| 0  | 1  | 1  | 1  | 16.384            |

| 1  | 0  | 0  | 0  | 32.768            |

| 1  | 0  | 0  | 1  | 65.536            |

| 1  | 0  | 1  | 0  | 131               |

| 1  | 0  | 1  | 1  | 262.1             |

| 1  | 1  | 0  | 0  | 524.3             |

| 1  | 1  | 0  | 1  | 1049              |

| 1  | 1  | 1  | 0  | 2097              |

| 1  | 1  | 1  | 1  | 4194              |

### Table 4. Polling-Active Time Setting

| <b>1 PA0</b><br>0 | POLLING ACTIVE TIME (μs)<br>64 |

|-------------------|--------------------------------|

| 0                 | 64                             |

|                   | 54                             |

| 1                 | 128                            |

| 0                 | 256                            |

| 1                 | 512*                           |

| 0                 | 1024                           |

| 1                 | 2048                           |

| 0                 | 4096                           |

| 1                 | 4096                           |

|                   | 1                              |

\*Default POR Value.

\*Default POR value.

### IE\_: Interrupt Enable

The IE\_ bit programs the switch input channel, IN\_, to be interrupt-enabled or interrupt-disabled (0 = interrupt disabled, 1 = interrupt enabled). The default value after power-on is 0.

W .0 and W .1: Wetting Current

W\_.0 and W\_.1 bits set the corresponding switch channel-wetting current as shown in Table 5.

### Table 5. Wetting Current Setting

| W1 | W0 | WETTING CURRENT (mA) |

|----|----|----------------------|

| 0  | 0  | 0*                   |

| 0  | 1  | 5                    |

| 1  | 0  | 10                   |

| 1  | 1  | 15                   |

\*Default POR value.

#### *LP: Low Quiescent Current Bit*

In polling mode, when  $\overline{LP}$  is set to 0, the IC is operating with the lowest quiescent current. The channels that are not enabled to interrupt have their wetting current disabled and are not monitored. The first pulse of wetting current after the switch is closed and sampled is 5mA unless the wetting current for that channel is set to 0mA. The default value of  $\overline{LP}$  after power-on is 0. When  $\overline{LP}$  is 1, all channels are monitored and the wetting current for each channel is set to the value determined by W\_.0 and W\_.1. If the MAX13362 is in continuous mode,  $\overline{LP}$  is ignored.

#### **Operating Modes**

The MAX13362 features three modes of operation: continuous mode, polling mode, and shutdown mode. In continuous mode, the wetting currents (if enabled) are continuously applied to the closed switches. In polling mode, the wetting currents are applied to the closed switches for a preset duration to reduce the power consumption. In shutdown mode, all switch inputs are high impedance and all circuitry is shutdown.

### Continuous Mode Operation (P0–P3 = 0)

In continuous mode, reading of the switch status is initiated by a falling edge on  $\overline{CS}$ . The microcontroller initiates a low pulse on  $\overline{CS}$  to update the MAX13362 switch status register. If  $\overline{INT}$  remains high, no action needs be taken by the microcontroller. If  $\overline{INT}$  goes low, the microcontroller may perform a read operation to read the updated switch status. On the rising edge of  $\overline{CS}$ ,  $\overline{INT}$  is updated. To get correct data, the microcontroller must wait 10µs before initiating a switch status read operation. (See Figure 4.)

Figure 4. Continuous Mode Operation

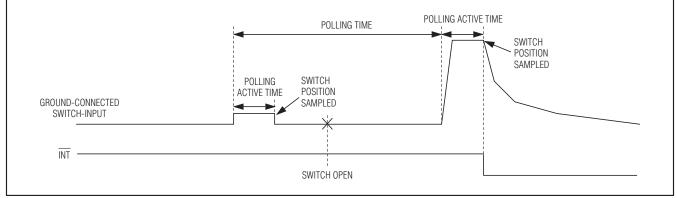

#### Polling-Mode Operation

In polling mode (see Figure 5), each switch input is sampled for a programmable polling active time set by the PAO–PA2 bits between 64µs and 4ms (see Table 4). Sampling is repeated at a period set by the PO–P3 bits (from 4ms to continuous, see Table 3). All switch inputs are sampled simultaneously at the end of the polling active time. Wetting currents (if enabled) are applied to closed switches during the polling active time. Therefore, the polling mode reduces the current consumption from the VS power supply to some value dependent on the polling time chosen.

Figure 5. Switch Sampling in Polling Mode

Any switch position change (if the switch is interruptenabled) is signaled through the active-low open-drain INT output. The INT output is cleared when CS goes low.

#### Shutdown Mode

In shutdown mode, all switch inputs are high impedance and the external switches are no longer monitored, reducing current consumption on VS to  $6\mu A$ (typ). The IC resets upon entering shutdown mode and the contents of the command registers are lost. Therefore, any setting other than power-on-reset defaults needs to be reprogrammed after exiting from the shutdown mode.

### Applications Information

#### **Overtemperature Protection**

If the IC junction temperature exceeds +165°C, an interrupt signal is generated and the wetting currents are disabled to reduce the on-chip power dissipation. During an overtemperature event, the last switch status is retained in internal memory and the switch status is not updated. The interrupt output is cleared when CS goes high, but the overtemperature bit T in the output word remains for as long as the overtemperature condition persists. When the junction temperature drops by 15°C, the wetting currents are re-enabled and there is a 1ms blanking time before the switches can be polled.

#### **Reverse-Battery Tolerance**

The INO–IN23 switch inputs withstand up to -15V DC voltage without damage. A reverse-battery diode is needed to protect VS as shown in the *Typical Application Circuit*. SD can be controlled from a bat-

tery-level source but should be protected against reverse battery in the application.

#### Wetting Current and Power Dissipation

The maximum power dissipation happens when all switch inputs configured with 15mA continuous wetting current are all closed. Assuming the battery voltage is 14V, the corresponding power dissipated by the IC is  $24 \times 14V \times 15mA = 5040$ mW. This exceeds the absolute maximum power dissipation of 2963mW. In polling mode, the wetting currents are pulsed at the programmed polling time to reduce the total power dissipated in the IC.

### **ISO 7637 Pulse Immunity**

VS,  $\overline{\text{SD}}$ , and INO–IN23 are potentially exposed to ISO 7637 pulses. Bypass VS with a 0.1µF and a 47µF capacitor. The VS and  $\overline{\text{SD}}$  voltage must be limited below 40V during load dump. Bypass INO–IN23 with at least 0.047µF capacitors at the ECU connector. When INO–IN3 or IN23 inputs are used with battery-connected switches, a 100 $\Omega$  series resistor is needed. These external components allow VS,  $\overline{\text{SD}}$ , and INO–IN23 to withstand ISO 7637 pulses in the application circuit.

#### **Mechanical Switch Characteristics**

The MAX13362 is designed to operate with switches that have the following characteristics:

- 1) Minimum resistance value with switch open (due to leakage):  $10k\Omega$ .

- 2) Maximum resistance value with switch closed: 100 $\Omega$ .

### Chip Information

PROCESS: BICMOS

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 40 TQFN-EP   | T4066+5      | <u>21-0141</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2009 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Supervisory Circuits category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

NCP304LSQ38T1G NCP304LSQ40T1G NCP304LSQ42T1G NCP304LSQ43T1G NCP304LSQ46T1G NCP305LSQ11T1G NCP305LSQ16T1G NCP305LSQ17T1G NCP305LSQ18T1G NCP305LSQ24T1G NCP305LSQ25T1G NCP305LSQ29T1G NCP305LSQ31T1G NCP305LSQ32T1G NCP308MT250TBG NCP308SN300T1G NCP391FCALT2G NCV303LSN42T1G CAT1161LI-25-G CAT853STBI-T3 MAX1232CPA MAX705CPA CAT1026LI-30-G CAT1320LI-25-G CAT872-30ULGT3 NCP304HSQ18T1G NCP304HSQ29T1G NCP304LSQ27T1G NCP304LSQ29T1G NCP304LSQ45T1G NCP305LSQ26T1G NCP305LSQ35T1G NCP305LSQ37T1G NCP308MT300TBG NCV300LSN36T1G NCV302LSN30T1G NCV303LSN16T1G NCV303LSN22T1G NCV303LSN27T1G NCV33161DMR2G TC54VN2402EMB713 MCP1316T-44NE/OT MCP1316MT-45GE/OT MCP1316MT-23LI/OT MCP1316T-26LE/OT MAX8997EWW+ MAX821RUS+T MAX6725AKASYD3-LF-T MAX809SEUR MAX708TEPA