### **General Description**

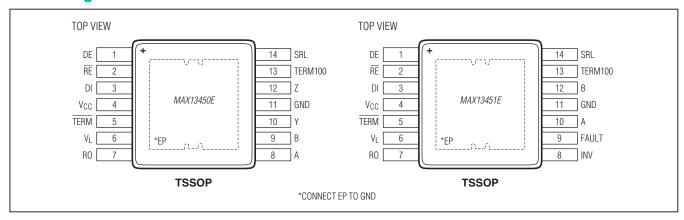

The MAX13450E/MAX13451E are half-duplex and full-duplex RS-485/RS-422 transceivers. These devices feature internal  $100\Omega$  and  $120\Omega$  termination resistors. The resistor values are pin selectable. A logic supply input allows interfacing to logic levels down to +1.8V.

The MAX13450E/MAX13451E feature strong drivers specified to drive low-impedance lines found when a fully loaded bus, based on today's  $100\Omega$  characteristic impedance cable, is doubly terminated. Both devices allow slew-rate limiting of the driver output to reduce EMI and reflections for data rates up to 500kbps.

The MAX13451E has a FAULT alarm indication output to signal to the system that an error condition exists in the driver. The MAX13451E also features a logic inversion function. The logic inversion allows phase reversal of the A-B signals in case these are inadvertently connected wrongly.

The MAX13450E/MAX13451E have 1/8-unit load receiver input impedance, allowing up to 256 transceivers on the bus. All driver outputs are protected to  $\pm 30$ kV ESD using the Human Body Model (HBM).

The MAX13450E/MAX13451E are available in a 14-pin TSSOP package and operate over the automotive -40°C to +125°C temperature range.

### **Applications**

- Industrial Control Systems

- Portable Industrial Equipment

- Motor Control

- Security Networks

- Medical Networks

## **Ordering Information/Selector Guide**

| PART          | HALF/FULL<br>DUPLEX | PIN-PACKAGE  |  |

|---------------|---------------------|--------------|--|

| MAX13450EAUD+ | Full                | 14 TSSOP-EP* |  |

| MAX13451EAUD+ | Half                | 14 TSSOP-EP* |  |

**Note:** All devices are specified over the -40 $^{\circ}$ C to +125 $^{\circ}$ C operating temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

# RS-485 Transceivers with Integrated $100\Omega/120\Omega$ Termination Resistors

#### **Benefits and Features**

- Easy Configuration of RS-422 and RS-485 Networks Up to 20Mbps (max) Data Rate

- Software/Pin-Selectable  $100\Omega/120\Omega$  Termination

- Integrated, Switchable Resistors Eliminate the Need for External Resistors or DIP Switches

- Driver Drives 100Ω Double Termination and Supports Cat-5/Cat-6 and 24-AWG Cables

- Pin-Selectable Slew-Rate Limiting Reduces EMI for Data Rates Up to 500kbps

- 1/8 Unit Load Allows Up to 256 Transceivers On the Bus

- Designed to Perform in Harsh Environments

- Extended ESD Protection

±30kV Human Body Model

±15kV Air Gap Discharge per IEC 61000-4-2

±7kV Contact Discharge per IEC 61000-4-2

- Inverting of A, B Line Polarity (MAX13451E) Allows Phase Reversal if Misconnected

- · Thermal and Overcurrent Protection

- Driver Fault Indication (MAX13451E)

- · Fail-Safe Receivers

- -40°C to +125°C Temperature Range

- +4.5V to +5.5V Supply Voltage Range

- Integrated Low-Voltage Logic Interface (Down to 1.8V)

Interfaces with Small-Geometry ASICs and FPGA

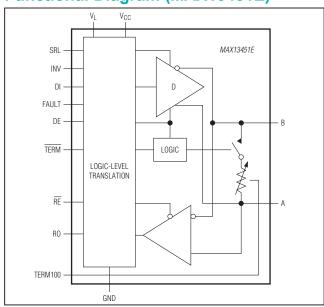

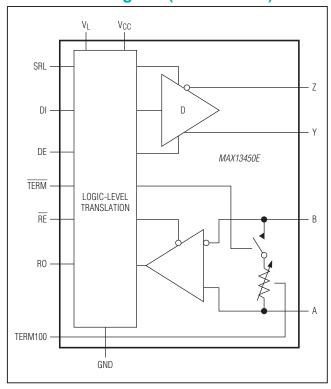

## **Functional Diagram (MAX13451E)**

# RS-485 Transceivers with Integrated $100\Omega/120\Omega$ Termination Resistors

### **Absolute Maximum Ratings**

| (All voltages referenced to GND.)        |                           |

|------------------------------------------|---------------------------|

| VCC, VL                                  | 0.3V to +6V               |

| DE, RE, DI, RO, TERM, TERM100, SRL       | $-0.3V$ to $(V_L + 0.3V)$ |

| INV, FAULT                               | $-0.3V$ to $(V_L + 0.3V)$ |

| A, B, Z, Y                               | 8V to +13V                |

| A to B (High-Z State)                    | +14V                      |

| B to A (High-Z State)                    | +14V                      |

| Short-Circuit Duration (RO, Y, Z) to GND |                           |

| Continuous Power Dissipation ( $I_A = +70^{\circ}C$ ) |                    |

|-------------------------------------------------------|--------------------|

| TSSOP (derate 25.6mW/°C above +70°C)                  | 2051mW             |

| Operating Temperature Range                           | -40°C to $+125$ °C |

| Storage Temperature Range                             | -65°C to $+150$ °C |

| Junction Temperature                                  | +150°C             |

| Lead Temperature (soldering, 10s)                     | +300°C             |

| Soldering Temperature (reflow)                        | +260°C             |

|                                                       |                    |

## **Package Thermal Characteristics (Note 1)**

**TSSOP**

Junction-to-Ambient Thermal Resistance (θJA) .......39°C/W Junction-to-Case Thermal Resistance (θJC) ......3°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{CC} = +4.5V \text{ to } +5.5V, V_L = +1.62V \text{ to } V_{CC}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V, V_L = +1.8V, \text{ and } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                          | SYMBOL                                        | CONDITIONS                                                                            | MIN  | TYP                | MAX  | UNITS |  |

|----------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------|------|--------------------|------|-------|--|

| Supply Voltage                                     | Vcc                                           |                                                                                       | 4.5  |                    | 5.5  | V     |  |

| Logic Supply Voltage                               | VL                                            |                                                                                       | 1.62 | 1.8                | Vcc  | V     |  |

| Supply Current                                     | loo                                           | $DE = \overline{RE} = high, \overline{TERM} = high, no load$                          |      |                    | 6    | mA    |  |

| Supply Current                                     | Icc                                           | $DE = \overline{RE} = low, \overline{TERM} = low, no load$                            |      |                    | 12   | IIIA  |  |

| Logic Supply Current                               | IL                                            | Current into $V_L$ , no load on RO, device not switching, $DE = \overline{RE} = high$ |      |                    | 2    | μА    |  |

| Chart down Course int                              | loupu                                         | Current into $V_{CC}$ , $DE = low$ , $\overline{RE} = \overline{TERM} = high$         |      |                    | 30   | μА    |  |

| Shutdown Current                                   | ISHDN                                         |                                                                                       |      |                    | 8    | mA    |  |

| DRIVER                                             |                                               |                                                                                       |      |                    |      |       |  |

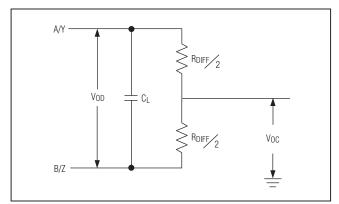

| Differential Driver Output                         | Vop                                           | RDIFF = $100\Omega$ , Figure 1 (Note 3)                                               | 2.0  |                    | Vcc  | V     |  |

| Differential Driver Output VoD                     |                                               | $R_{DIFF} = 46\Omega$ , Figure 1 (Note 3)                                             | 1.5  |                    | Vcc  | V     |  |

| Change in Magnitude of Differential Output Voltage | ΔV <sub>OD</sub>                              | R <sub>DIFF</sub> = 100 $\Omega$ or 46 $\Omega$ , Figure 1 (Note 3)                   |      |                    | 0.2  | V     |  |

| Driver Common-Mode Output<br>Voltage               | Voc                                           | R <sub>DIFF</sub> = 100 $\Omega$ or 46 $\Omega$ , Figure 1 (Note 3)                   |      | V <sub>CC</sub> /2 | 3    | V     |  |

| Change In Magnitude of Common-Mode Voltage         | ΔV <sub>OC</sub>                              | R <sub>DIFF</sub> = 100 $\Omega$ or 46 $\Omega$ , Figure 1 (Note 3)                   |      |                    | 0.2  | V     |  |

| Driver Short-Circuit Output                        | Circuit Output , OV ≤ V <sub>OUT</sub> ≤ +12V |                                                                                       |      |                    | +280 | m ^   |  |

| Current                                            | losp                                          | -7V ≤ VOUT ≤ 0V                                                                       | -250 |                    |      | mA    |  |

## **Electrical Characteristics (continued)**

(V<sub>CC</sub> = +4.5V to +5.5V, V<sub>L</sub> = +1.62V to V<sub>CC</sub>, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>CC</sub> = +5V, V<sub>L</sub> = +1.8V, and T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                  | SYMBOL           | CONDITIO                                                                                                  | NS                                      | MIN                  | TYP   | MAX      | UNITS |  |

|--------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|-------|----------|-------|--|

| Driver Short-Circuit Foldback              | loops            | $(V_{CC} - 1V) \le V_{OUT} \le +12V$                                                                      | /                                       | +15                  |       |          | m A   |  |

| Output Current                             | IOSDF            | -7V ≤ V <sub>OUT</sub> ≤ 0V                                                                               |                                         |                      |       | -15      | mA    |  |

| RECEIVER                                   |                  |                                                                                                           |                                         |                      |       |          |       |  |

|                                            |                  | $DE = \overline{RE} = GND;$                                                                               | $V_A$ or $V_B = +12V$                   |                      |       | 125      |       |  |

| Input Current (A and B)                    | IA, B            | TERM = VL; VCC = GND or 5.5V                                                                              | V <sub>A</sub> or V <sub>B</sub> = -7V  | -100                 |       |          | μΑ    |  |

| Receiver Differential Threshold<br>Voltage | VTH              | $-7V \le V_{CM} \le +12V$ ,<br>$DE = \overline{RE} = GND$ ;<br>$\overline{TERM} = V_{L}$ ; $V_{CC} = GND$ | V <sub>A</sub> or V <sub>B</sub> = +12V | -200                 |       | -50      | mV    |  |

| Receiver Input Hysteresis                  | ΔVτΗ             | $V_A + V_B = 0V$                                                                                          |                                         |                      | 15    |          | mV    |  |

| LOGIC INTERFACE                            |                  |                                                                                                           |                                         |                      |       |          |       |  |

| Input High Voltage                         | VIH              | DI, DE, RE, TERM, SRL, T                                                                                  | ERM100, INV                             | 2/3 x V <sub>L</sub> |       |          | V     |  |

| Input Low Voltage                          | VIL              | DI, DE, RE, TERM, SRL, T                                                                                  | ERM100, INV                             |                      |       | 1/3 x VL | V     |  |

| Input Current                              | IIN              | DI, DE, RE, TERM, TERM                                                                                    | 100, SRL, INV                           | -1                   |       | +1       | μΑ    |  |

| Receiver Output High Voltage               | VROH             | IOUT = -1mA                                                                                               | IOUT = -1mA                             |                      |       |          | V     |  |

| Receiver Output Low Voltage                | V <sub>ROL</sub> | $I_{OUT} = +1mA$                                                                                          | I <sub>OUT</sub> = +1mA                 |                      |       | 0.4      | V     |  |

| Three-State Output Current at Receiver     | lozr             | $0V \le V_{RO} \le V_{L}$                                                                                 |                                         | -1                   | +0.01 | +1       | μΑ    |  |

| Receiver Output Short-Circuit<br>Current   | Iosr             | $0V \le V_{RO} \le V_L$                                                                                   |                                         | ±1                   |       | ±80      | mA    |  |

| Fault Output High Voltage (MAX13451E)      | VFAULTH          | Fault condition, IOUT = -1                                                                                | mA                                      | V <sub>L</sub> - 0.6 |       |          | V     |  |

| Fault Output Low Voltage (MAX13451E)       | VFAULTL          | Nonfault condition; IOUT =                                                                                | = +1mA                                  |                      |       | 0.4      | V     |  |

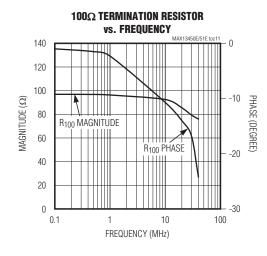

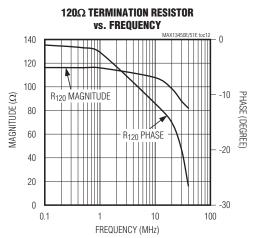

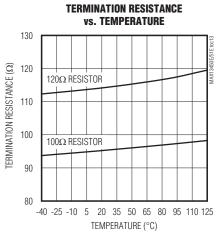

| TERMINATION RESISTOR                       |                  |                                                                                                           |                                         |                      |       |          |       |  |

| 100Ω Termination Resistor                  | R100             | TERM = low, TERM100 =                                                                                     | high                                    | 85                   | 100   | 115      | Ω     |  |

| 120 $\Omega$ Termination Resistor          | R <sub>120</sub> | TERM = low, TERM100 = low                                                                                 |                                         | 101                  | 120   | 139      | Ω     |  |

| Single-Ended Input Capacitance vs. GND     | CIN              | f = 1MHz (MAX13451E only)                                                                                 |                                         |                      | 40    |          | рF    |  |

| ESD PROTECTION                             |                  |                                                                                                           |                                         |                      |       |          |       |  |

|                                            |                  | Human Body Model                                                                                          |                                         |                      | ±30   |          |       |  |

| ESD Protection (A, B, Y, Z)                |                  | IEC 61000-4-2 Air Gap Di                                                                                  | scharge                                 |                      | ±15   |          | kV    |  |

|                                            |                  | IEC 61000-4-2 Contact Di                                                                                  | scharge                                 |                      | ±7    |          |       |  |

| ESD Protection (All Other Pins)            |                  | Human Body Model                                                                                          |                                         |                      | ±2    |          |       |  |

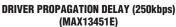

## **Switching Characteristics—SRL = HIGH**

$(V_{CC} = +4.5V \text{ to } +5.5V, V_L = +1.62V \text{ to } V_{CC}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V, V_L = +1.8V \text{ and } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                          | SYMBOL                 | CONDITIONS                                                                                                  | MIN | TYP | MAX        | UNITS |

|----------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|------------|-------|

| DRIVER                                             |                        |                                                                                                             |     |     |            |       |

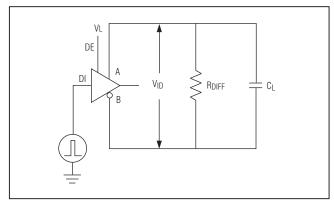

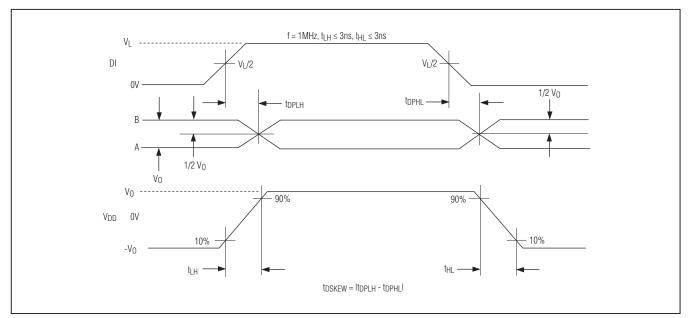

| Driver Propagation Delay                           | t <sub>DPLH</sub>      | RDIFF = 54Ω, CL = 50pF, Figures 2 and 3                                                                     |     |     | 800<br>800 | ns    |

| Differential Driver Output Skew<br>ltDPLH - tDPHLI | tDSKEW                 | RDIFF = $54\Omega$ , CL = $50$ pF, Figure 3                                                                 |     |     | 100        | ns    |

| Driver Differential Output Rise or Fall Time       | t <sub>HL</sub>        | RDIFF = $54\Omega$ , CL = $50$ pF, Figures 2 and 3                                                          | 100 |     | 600        | ns    |

| Maximum Data Rate                                  | DRMAX                  |                                                                                                             | 500 |     |            | kbps  |

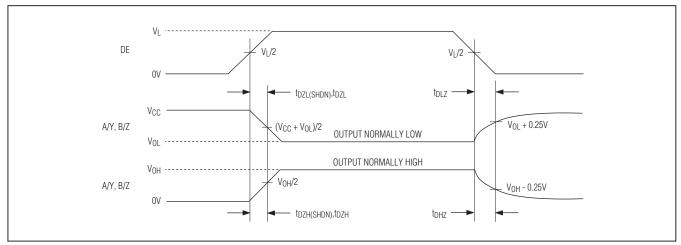

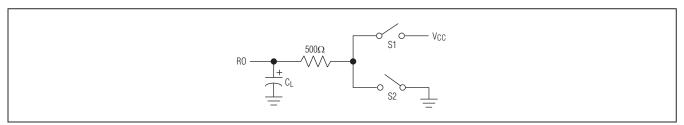

| Driver Enable from Shutdown to Output High         | tDZH(SHDN)             | S2 closed, $R_L = 500\Omega$ , $C_L = 100pF$ , Figures 4 and 5                                              |     |     | 4500       | ns    |

| Driver Enable from Shutdown to Output Low          | tDZL(SHDN)             | S1 closed, $R_L = 500\Omega$ , $C_L = 100pF$ , Figures 4 and 5                                              |     |     | 5200       | ns    |

| Driver Disable Delay                               | tDLZ, tDHZ             | Figures 4 and 5                                                                                             |     |     | 100        | ns    |

| Driver Enable Delay                                | tdzl, tdzh             | Figures 4 and 5                                                                                             |     |     | 2500       | ns    |

| RECEIVER                                           | _                      |                                                                                                             |     |     |            |       |

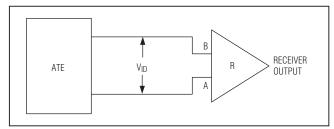

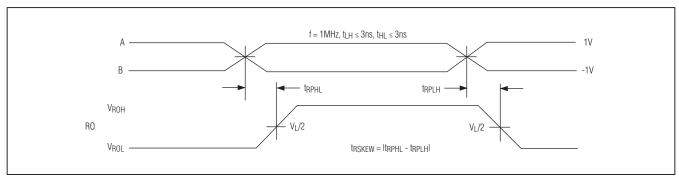

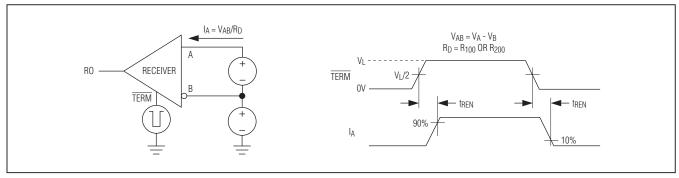

| Receiver Propagation Delay                         | trplh<br>trphl         | C <sub>L</sub> = 15pF, IV <sub>ID</sub> I ≥ 2.0V; t <sub>LH</sub> , t <sub>HL</sub> ≤ 15ns, Figures 6 and 7 |     |     | 200        | ns    |

| Receiver Output Skew                               | trskew                 | C <sub>L</sub> = 15pF, Figures 6 and 7                                                                      |     |     | 30         | ns    |

| Maximum Data Rate                                  | DRMAX                  |                                                                                                             | 500 |     |            | kbps  |

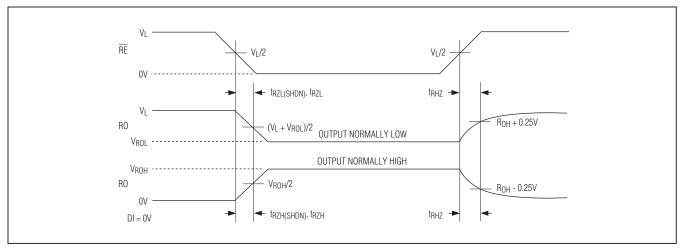

| Receiver Enable to Output High                     | <sup>‡</sup> RZH       | S2 closed, $C_L$ = 100pF, $R_L$ = 500 $\Omega$ , Figures 8 and 9                                            |     |     | 50         | ns    |

| Receiver Enable to Output Low                      | tRZL                   | S1 closed, $C_L = 100 pF$ , $R_L = 500 \Omega$ , Figures 8 and 9                                            |     |     | 50         | ns    |

| Receiver Disable from High                         | tRHZ                   | Figures 8 and 9                                                                                             |     |     | 50         | ns    |

| Receiver Disable from Low                          | t <sub>RLZ</sub>       | Figures 8 and 9                                                                                             |     |     | 50         | ns    |

| Receiver Enable from Shutdown to Output High       | trzh(shdn)             | Figures 8 and 9                                                                                             |     |     | 5000       | ns    |

| Receiver Enable from Shutdown to Output Low        | <sup>†</sup> RZL(SHDN) | Figures 8 and 9                                                                                             |     |     | 5000       | ns    |

| TERMINATION RESISTOR                               |                        |                                                                                                             |     | ,   |            |       |

| Turn-Off Time                                      | trtz                   | Figure 10                                                                                                   |     | 120 |            | μs    |

| Turn-On Time                                       | trten                  | Figure 10                                                                                                   |     | 1   |            | μs    |

|                                                    |                        |                                                                                                             |     |     |            |       |

## **Switching Characteristics—SRL = LOW**

$(V_{CC} = +4.5V \text{ to } +5.5V, V_L = +1.62V \text{ to } V_{CC}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V, V_L = +1.8V, \text{ and } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                       | SYMBOL           | CONDITIONS                                                       | MIN | TYP | MAX      | UNITS |

|-------------------------------------------------|------------------|------------------------------------------------------------------|-----|-----|----------|-------|

| DRIVER                                          |                  |                                                                  |     |     |          |       |

| Driver Propagation Delay                        | tdplh<br>tdphl   | $R_{DIFF} = 54\Omega$ , $C_L = 50pF$ , Figures 2 and 3           |     |     | 50<br>50 | ns    |

| Differential Driver Output Skew ItDPLH - tDPHLI | tDSKEW           | $R_{DIFF} = 54\Omega$ , $C_L = 50pF$ , Figure 3                  |     |     | 6        | ns    |

| Driver Differential Output Rise or Fall Time    | tHL, tLH         | $R_{DIFF} = 54\Omega$ , $C_L = 50pF$ , Figures 2 and 3           |     |     | 15       | ns    |

| Maximum Data Rate                               | DRMAX            |                                                                  | 20  |     |          | Mbps  |

| Driver Enable from Shutdown to<br>Output High   | tDZH(SHDN)       | S2 closed, $R_L = 500\Omega$ , $C_L = 100pF$ , Figures 4 and 5   |     |     | 2000     | ns    |

| Driver Enable from Shutdown to<br>Output Low    | tDZL(SHDN)       | S1 closed, $R_L = 500\Omega$ , $C_L = 100pF$ , Figures 4 and 5   |     |     | 2000     | ns    |

| Driver Disable Delay                            | tDLZ, tDHZ       | Figures 4 and 5                                                  |     |     | 100      | ns    |

| Driver Enable Delay                             | tdzl, tdzh       | Figures 4 and 5                                                  |     |     | 100      | ns    |

| RECEIVER                                        |                  |                                                                  |     |     |          | •     |

| Receiver Propagation Delay                      | trplh<br>trphl   | CL = 15pF, IVIDI ≥ 2.0V; tLH, tHL ≤ 15ns, Figures 6 and 7        |     |     | 50<br>50 | ns    |

| Receiver Output Skew                            | trskew           | C <sub>L</sub> = 15pF, Figures 6 and 7                           |     |     | 6        | ns    |

| Maximum Data Rate                               | DRMAX            |                                                                  | 20  |     |          | Mbps  |

| Receiver Enable to Output High                  | t <sub>RZH</sub> | S2 closed, $C_L$ = 100pF, $R_L$ = 500 $\Omega$ , Figures 8 and 9 |     |     | 50       | ns    |

| Receiver Enable to Output Low                   | t <sub>RZL</sub> | S1 closed, $C_L$ = 100pF, $R_L$ = 500 $\Omega$ , Figures 8 and 9 |     |     | 50       | ns    |

| Receiver Disable Time from High                 | tRHZ             | Figures 8 and 9                                                  |     |     | 50       | ns    |

| Receiver Disable Time from Low                  | tRLZ             | Figures 8 and 9                                                  |     |     | 50       | ns    |

| Receiver Enable from Shutdown to Output High    | trzh(shdn)       | Figures 8 and 9                                                  |     |     | 2000     | ns    |

| Receiver Enable from Shutdown to Output Low     | tRZL(SHDN)       | Figures 8 and 9                                                  |     |     | 2000     | ns    |

| TERMINATION RESISTOR                            | ,                |                                                                  |     |     |          |       |

| Turn-Off Time                                   | trtz             | Figure 10                                                        |     | 120 |          | μs    |

| Turn-On Time                                    | trten            | Figure 10                                                        |     | 1   |          | μs    |

Note 2: All devices are 100% production tested at  $T_A = +25$ °C. Limits over temperature are guaranteed by design.

**Note 3:** Termination resistance is disabled (TERM = high).

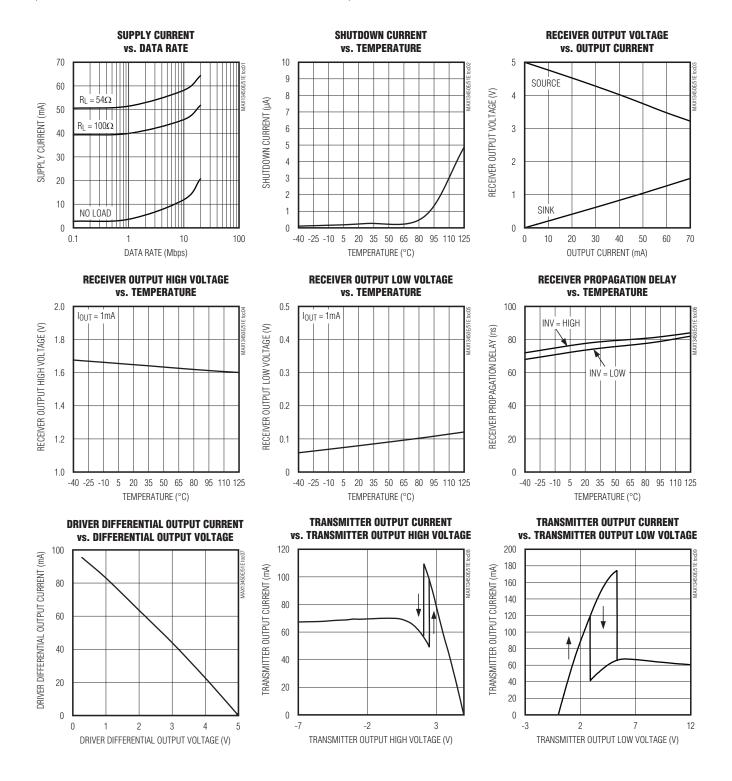

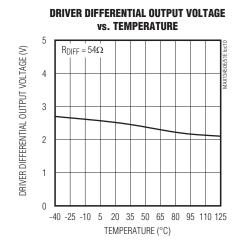

## **Typical Operating Characteristics**

$(VCC = +5V, VL = +1.8V, TA = +25^{\circ}C, unless otherwise noted.)$

## **Typical Operating Characteristics (continued)**

$(VCC = +5V, VL = +1.8V, TA = +25^{\circ}C, unless otherwise noted.)$

**DRIVER ENABLE TIME FROM SHUTDOWN**

### **Test Circuits and Waveforms**

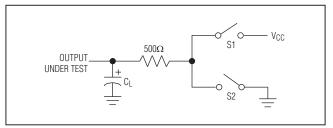

Figure 1. Driver DC Test Load

Figure 2. Driver Timing Test Circuit

Figure 3. Driver Propagation Delays

## **Test Circuits and Waveforms (continued)**

Figure 4. Driver Enable and Disable Times

Figure 5. Driver-Enable and Disable-Timing Test Load

Figure 6. Receiver Propagation Delay Test Circuit

Figure 7. Receiver Propagation Delays

## **Test Circuits and Waveforms (continued)**

Figure 8. Receiver Enable and Disable Times

Figure 9. Receiver Enable and Disable Times

Figure 10. Termination Resistor Turn-On/-Off Times

## **Pin Configurations**

## **Pin Description**

| PIN       |           | NAME | FUNCTION                                                                                                                                                                                                                                                                                  |

|-----------|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX13450E | MAX13451E | NAME | FUNCTION                                                                                                                                                                                                                                                                                  |

| 1         | 1         | DE   | Driver-Output Enable. Drive DE low to put the driver output in three-state. Drive DE high to enable the driver. DE is referenced to V <sub>L</sub> .                                                                                                                                      |

| 2         | 2         | RE   | Receiver-Output Enable. Drive $\overline{RE}$ low to enable the RO. Drive $\overline{RE}$ high to disable the RO output and put the RO output in a high-impedance state. $\overline{RE}$ is referenced to V <sub>L</sub> .                                                                |

| 3         | 3         | DI   | Driver Input. Drive DI low to force the noninverting output low and the inverting output high. Drive DI high to force the noninverting output high and inverting output low. DI is referenced to $V_L$ .                                                                                  |

| 4         | 4         | Vcc  | Power-Supply Voltage. Bypass VCC to GND with a 0.1µF ceramic capacitor placed as close as possible to the device.                                                                                                                                                                         |

| 5         | 5         | TERM | Active-Low Termination Resistor Enable. Drive $\overline{\text{TERM}}$ low to enable the internal termination resistor. $\overline{\text{TERM}}$ is referenced to $V_L$ .                                                                                                                 |

| 6         | 6         | VL   | Logic Supply Voltage. Bypass V <sub>L</sub> to GND with a 0.1µF ceramic capacitor placed as close as possible to the device.                                                                                                                                                              |

| 7         | _         | RO   | Receiver Output. When receiver is enabled and $V_A$ - $V_B \ge$ -50mV, RO is high. If $V_A$ - $V_B \le$ -200mV, RO is low. RO is referenced to $V_L$ .                                                                                                                                    |

| _         | 7         | RO   | Receiver Output. When INV is low, receiver is enabled and $V_A$ - $V_B \ge$ -50mV, RO is high. If $V_A$ - $V_B \le$ -200mV, RO is low. When INV is high, receiver is enabled and $V_A$ - $V_B \ge$ -50mV, RO is low. If $V_A$ - $V_B \le$ -200mV, RO is high. RO is referenced to $V_L$ . |

| 8         | _         | А    | Noninverting Receiver Input                                                                                                                                                                                                                                                               |

| _         | 10        | А    | If INV is low, A is a noninverting receiver input and a noninverting driver output. If INV is high, A is an inverting receiver input and an inverting driver output.                                                                                                                      |

| 9         | _         | В    | Inverting Receiver Input                                                                                                                                                                                                                                                                  |

| _         | 12        | В    | If INV is low, B is an inverting receiver input and an inverting driver output. If INV is high, B is a noninverting receiver input and a noninverting driver output.                                                                                                                      |

# **Pin Description (continued)**

| Р         | IN        |         |                                                                                                                                                                                                     |

|-----------|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX13450E | MAX13451E | NAME    | FUNCTION                                                                                                                                                                                            |

| 10        | _         | Υ       | Noninverting Driver Output                                                                                                                                                                          |

| 11        | 11        | GND     | Ground                                                                                                                                                                                              |

| 12        | _         | Z       | Inverting Driver Output                                                                                                                                                                             |

| 13        | 13        | TERM100 | Termination Resistor Value Selection Input. Drive TERM100 low to select a $120\Omega$ termination and high to select a $100\Omega$ termination. The TERM100 input is referenced to V <sub>L</sub> . |

| 14        | 14        | SRL     | Slew-Rate Limiting-Enable Input. Drive SRL high to enable slew-rate limiting and low to disable slew-rate limiting. The SRL input is referenced to VL.                                              |

| _         | 8         | INV     | Inversion Input. Drive INV high to internally swap RO logic level with respect to A and B signals.                                                                                                  |

| _         | 9         | FAULT   | Fault Flag Output. FAULT asserts high in overcurrent conditions or if A/B are forced below GND or above VCC when the driver is enabled. FAULT is referenced to VL.                                  |

|           | _         | EP      | Exposed Pad. Connect EP to GND. Do not use EP as the only GND connection.                                                                                                                           |

### **Function Tables**

# Table 1. Termination Resistor Control (MAX13450E/MAX13451E)

| TERM | DE | RE | TERMINATION RESISTOR |

|------|----|----|----------------------|

| Low  | X  | X  | Activated            |

| High | Х  | Χ  | Not activated        |

# Table 2. Shutdown Control (MAX13450E/MAX13451E)

| DE  | RE   | TERM | STATE    |

|-----|------|------|----------|

| Low | High | High | Shutdown |

# **Table 3. Function Table for Transmitter** (MAX13450E)

| INF  | TUT  | OUTPUT |        |  |  |

|------|------|--------|--------|--|--|

| DE   | DI   | Υ      | Z      |  |  |

| Low  | X    | High-Z | High-Z |  |  |

| High | Low  | Low    | High   |  |  |

| High | High | High   | Low    |  |  |

# Table 4. Function Table for Receiver (MAX13450E)

| INPUT  |                 | OUTPUT |

|--------|-----------------|--------|

| RE A-B |                 | RO     |

| High   | X               | High-Z |

| Low    | ≥ -50mV or Open | High   |

| Low    | ≤ -200mV        | Low    |

# **Table 5. INV Input Function Table for Transmitter (MAX13451E)**

| INPUT |      |      | OUTPUT |        |

|-------|------|------|--------|--------|

| DE    | INV  | DI   | Α      | В      |

| Low   | Х    | Х    | High-Z | High-Z |

|       | Low  | Low  | Low    | High   |

| High  |      | High | High   | Low    |

| High  | High | Low  | High   | Low    |

|       |      | High | Low    | High   |

### **Function Tables (continued)**

# Table 6. INV Input Function Table for Receiver (MAX13451E)

| INPUT |      |                             | OUTPUT |

|-------|------|-----------------------------|--------|

| RE    | INV  | A-B                         | RO     |

| High  | Х    | X                           | High-Z |

|       | Low  | ≥ -50mV or<br>Short or Open | High   |

| Low   |      | ≤ -200mV                    | Low    |

| LOW   | High | ≥ -50mV or<br>Open          | Low    |

|       |      | ≤ -200mV                    | High   |

### **Detailed Description**

The MAX13450E is a full-duplex, RS-485/RS-422-compatible transceiver and the MAX13451E is a half-duplex, RS-485/RS-422-compatible transceiver. Both devices have an internal  $100\Omega/120\Omega$  termination resistor. The MAX13450E/MAX13451E have a V $_{L}$  supply voltage input to support down to a +1.8V voltage logic interface.

The MAX13450E/MAX13451E feature a 1/8-unit load receiver input impedance, allowing up to 256 transceivers on the bus. All line interface pins are protected to ±30kV ESD based on the HBM. These devices also include fail-safe circuitry, guaranteeing a defined logic-level receiver output when the receiver inputs are open or shorted.

The MAX13450E/MAX13451E allow slew-rate-limited driver outputs for lower data rates below 500kbps. The SRL reduces the slew rate, which reduces EMI emissions and reflections caused by improperly terminated cables.

The MAX13451E has a FAULT output that indicates a fault condition on the driver. The MAX13451E also has an INV input that inverts the phase of A and B pins.

### **Termination Resistor**

The MAX13450E/MAX13451E feature a selectable internal termination resistor. Drive the  $\overline{\text{TERM}}$  input low to enable the internal termination resistor. Drive the  $\overline{\text{TERM}}$  input high to disable the internal termination resistor.

### **Functional Diagram (MAX13450E)**

Drive the TERM100 input high to select the 100 $\Omega$  termination resistor. Drive TERM100 input low to select the 120 $\Omega$  termination resistor.

### **INV Input (MAX13451E)**

The INV input of the MAX13451E reverses the polarity of the RO receiver output (see Table 5 and 6). If the INV input is high then the RO output is low under fail-safe receiver conditions. This is the opposite polarity of normal fail-safe operations.

#### Fault Condition (MAX13451E)

The MAX13451E also has a FAULT output to indicate a fault condition. The FAULT output is active high when there is a short circuit at the driver's output, an over/undervoltage at the driver's outputs, or the device's temperature is higher than +150°C.

# RS-485 Transceivers with Integrated $100\Omega/120\Omega$ Termination Resistors

#### Thermal Shutdown

When the devices' temperature goes over +150°C, the termination resistor turns off, and the transmitter shuts down while the receiver stays active.

#### Fail Safe

The MAX13450E guarantee a logic-high receiver output when the receiver inputs are shorted or open, or when they are connected to a terminated transmission line with all drivers disabled. This is done by setting the receiver input threshold between -50mV and -200mV. If the differential receiver input voltage (A - B) is greater than or equal to -50mV, RO is logic-high. If (A - B) is less than or equal to -200mV, RO is logic-low. In the case of a terminated bus with all transmitters disabled, the receiver's differential input voltage is pulled to 0V by the termination resistor. With the receiver thresholds of the MAX13450E, this results in RO being logic-high.

The MAX13451E has the same fail-safe receiver behavior as the MAX13450E when the INV input is low. When the INV input is high, RO is low under the fail-safe condition.

#### **ESD Protection**

As with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The driver outputs and receiver inputs of the MAX13450E/MAX13451E have extra protection against static electricity. The ESD structures withstand high ESD in all states: normal operation, shutdown, and powered down. After an ESD event, the MAX13450E/MAX13451E keep working without latchup or damage.

ESD protection can be tested in various ways. The transmitter outputs and receiver inputs of the MAX13450E/MAX13451E are characterized for protection to the following limits:

- ±30kV using the Human Body Model

- ±15kV using the Air Gap Discharge Method specified in IEC 61000-4-2

- ±7kV using the Contact Discharge Method specified in IEC 61000-4-2

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

#### **Human Body Model**

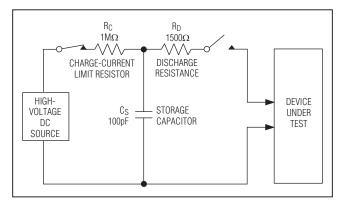

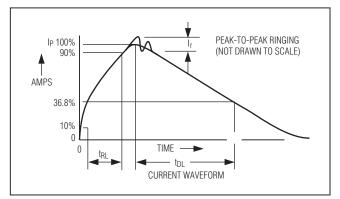

Figure 11a shows the Human Body Model, and Figure 11b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a  $1.5 \mathrm{k}\Omega$  resistor.

#### IEC 61000-4-2

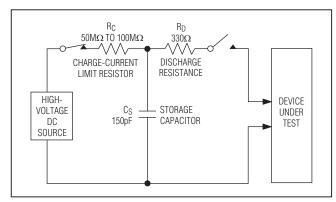

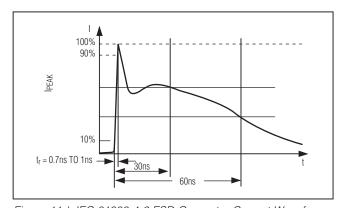

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. However, it does not specifically refer to integrated circuits. The MAX13450E/MAX13451E help equipment designs to meet IEC 61000-4-2, without the need for additional ESD-protection components. The major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2 because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD withstand voltage measured to IEC 61000-4-2 is generally lower than that measured using the Human Body Model. Figure 11c shows the IEC 61000-4-2 model, and Figure 11d shows the current waveform for the IEC 61000-4-2 ESD Contact Discharge test.

### **Applications Information**

#### **Typical Applications**

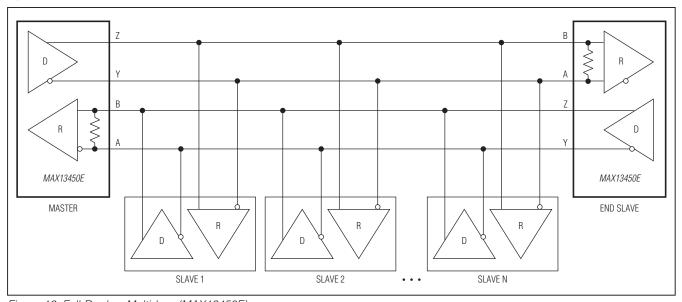

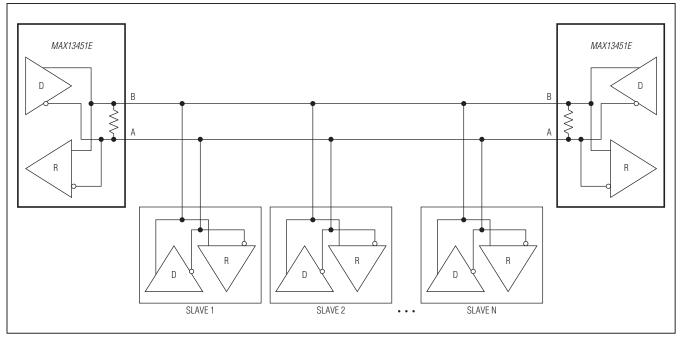

The MAX13450E transceiver is designed for full-duplex, bidirectional data communications on point-to-point or multipoint bus transmission lines (Figure 12). The MAX13451E transceiver is designed for half-duplex, bidirectional data communications on point-to-point or multipoint bus transmission lines (Figure 13).

#### 256 Transceivers on the Bus

The standard RS-485 receiver input impedance is oneunit load, and the standard driver can drive up to 32-unit loads. The MAX13450E/MAX13451E have a 1/8-unit load receiver input impedance, allowing up to 256 transceivers to be connected in parallel on one communication line. Any combination of these devices, as well as other RS-485 transceivers with a total of 32-unit loads or fewer, can be connected to the line.

#### **Reduced EMI and Reflections**

The MAX13450E/MAX13451E feature reduced slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated cables, allowing error-free data transmission up to 500kbps.

Figure 11a. Human Body ESD Test Model

Figure 11c. IEC 61000-4-2 ESD Test Model

Figure 11b. Human Body Current Waveform

Figure 11d. IEC 61000-4-2 ESD Generator Current Waveform

## **Typical Application Circuits**

Figure 12. Full-Duplex, Multidrop (MAX13450E)

## **Typical Application Circuits (continued)**

Figure 13. Half-Duplex, Multidrop, and Point-to-Point Systems (MAX13451E)

#### Low-Power Shutdown Mode

Drive  $\overline{\text{RE}}$  high, DE low, and  $\overline{\text{TERM}}$  high to enter low-power shutdown mode (see Table 2).

### **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns, go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN<br>NO. |

|-----------------|-----------------|----------------|------------------------|

| 14 TSSOP-EP     | U14E+3          | 21-0108        | 90-0119                |

## RS-485 Transceivers with Integrated $100\Omega/120\Omega$ Termination Resistors

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                   | PAGES<br>CHANGED |

|--------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 4/10          | Initial release                                                                                                               | _                |

| 1                  | 11/10         | Updated the V <sub>L</sub> specification in the <i>Electrical Characteristics</i> and <i>Switching Characteristics</i> tables | 2–5              |

| 2                  | 2/15          | Added the Benefits and Features section                                                                                       | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RS-485 Interface IC category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

LTC1483CN8 LTC1482CN8 SN75976A1MDGGREP SN65HVD24DR SN65HVD70DR SN65HVD1477DGKR SN65HVD1477DGK

LTC1685CS8#PBF LTC486CN#PBF LTC488CSW#PBF LTC2876HMS8E#PBF LTC485CS8#PBF THVD1550DR LTC1487CN8#PBF

LTC489CSW#PBF LTC1485CN8#PBF LTC2861IDE#PBF LTC1686IS8#PBF LTC488CN#PBF LTC1480IN8#PBF ADM3066EARMZ

ADM3095EBRZ LTC487IN#PBF LTC1482CMS8#PBF LTC488IN#PBF LTC486IN#PBF LTC1481IN8#PBF ADM3063EARZ

ADM3068EARZ ADM3064EARZ-R7 ADM3064EARZ ADM3065ETRMZ-EP ADM3066EBRMZ-R7 ADM3066ETRMZ-EP

ADM3095EARZ ADM3061EBRZ LTC1687IS#PBF MAX3443EASA+T LTC1483IS8#PBF LTC1686CS8#PBF LTC1481CS8#PBF

LTC1485IS8#TRPBF LTC1482CS8#TRPBF LTC2877HDD#PBF LTC485CN8#PBF SP488CS MAX3443ECPA+ LTC1484CN8#PBF

LTC1482CN8#PBF LTC1483IN8#PBF