# 16-Bit, Low-Power, 2-Channel, Sigma-Delta ADCs

### **General Description**

The MAX1415/MAX1416 low-power, 2-channel, serial-output analog-to-digital converters (ADCs) use a sigmadelta modulator with a digital filter to achieve 16-bit resolution with no missing codes. These ADCs are pincompatible upgrades to the MX7705/AD7705. The MAX1415/MAX1416 feature an internal oscillator (1MHz or 2.4576MHz), an on-chip input buffer, and a programmable gain amplifier (PGA). The devices offer an SPI<sup>TM</sup>-/QSPI<sup>TM</sup>-/MICROWIRE<sup>TM</sup>-compatible serial interface.

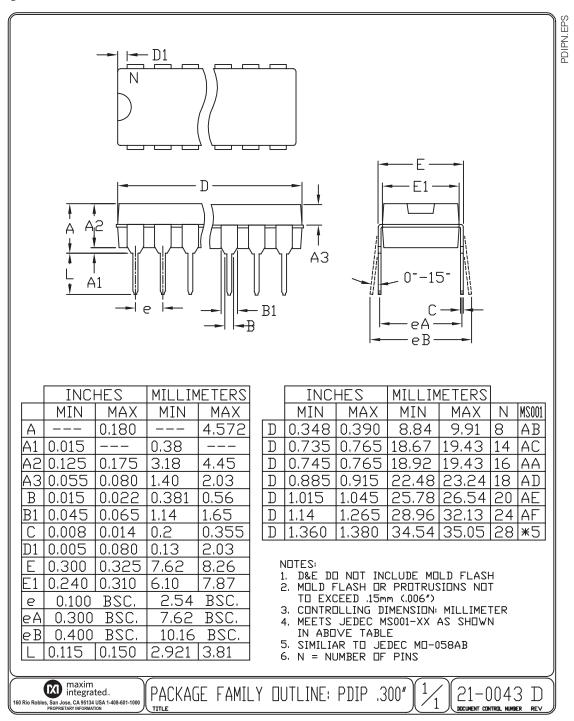

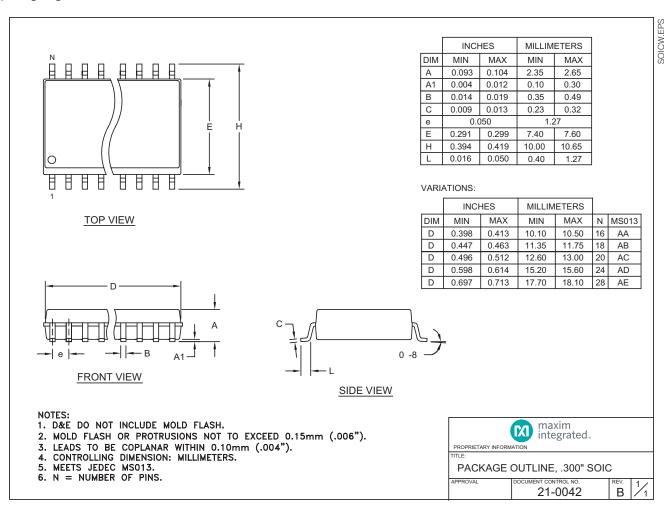

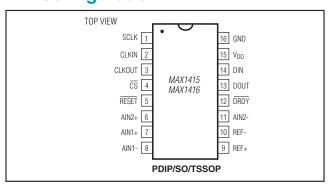

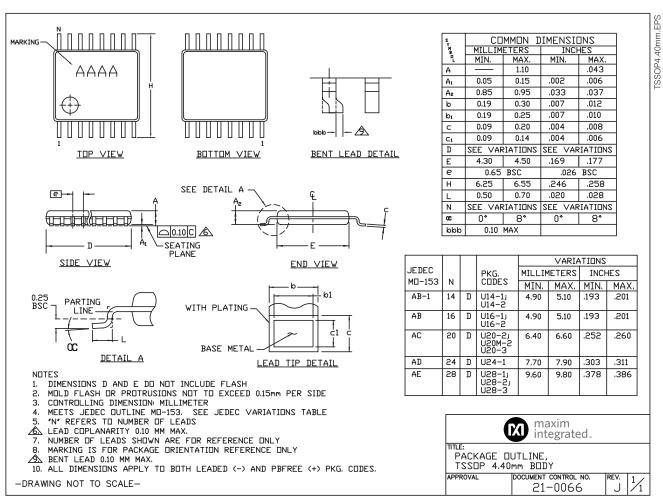

The MAX1415/MAX1416 are available in 16-pin PDIP, SO, and TSSOP packages.

### **Applications**

- Industrial Instruments

- Weigh Scales

- Strain-Gauge Measurements

- Loop-Powered Systems

- · Flow and Gas Meters

- Medical Instrumentation

- Pressure Transducers

- Thermocouple Measurements

- RTD Measurements

#### **Benefits and Features**

- Improve Measurement Quality with Excellent DC Accuracy

- 16-Bit Sigma-Delta ADC with Two Fully-Differential Input Channels

- · 0.0015% INL (max) with No Missing Codes

- Minimize Power Consumption with Low-Power Dissipation

- 1.2mW (max) 3V supply

- 2µA (typ) Power-Down Current

- Lower System Cost with Integrated Functionality

- PGA with 1 to 128 Programmable Gain

- · Optional Input Buffers

- > 98dB 50Hz/60Hz Rejection

- Increase System Accuracy with Built-in Self Calibration

- On-Demand Offset and Gain Self-Calibration and System Calibration

- · User-Programmable Offset and Gain Registers

- Flexible Single Supply Options

- 2.7V to 3.6V (MAX1415)

- 4.75V to 5.25V (MAX1416)

- Pin Compatible Upgrades for MX7705/AD7705

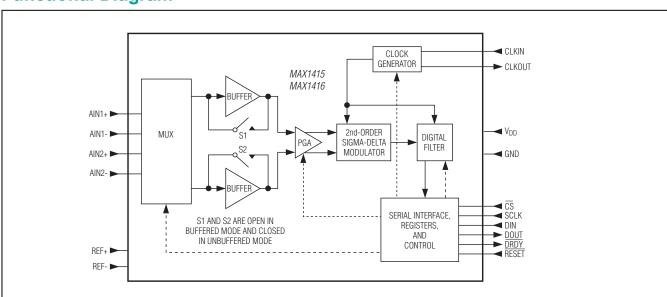

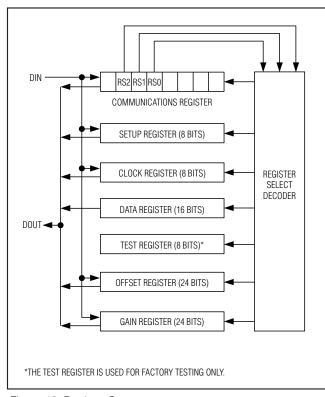

# **Functional Diagram**

SPI/QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

# 16-Bit, Low-Power, 2-Channel, Sigma-Delta ADCs

# **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND                            | Operating Temperature Range40°C to +85°C Storage Temperature Range60°C to +150°C Junction Temperature+150°C Lead Temperature (soldering, 10s)+300°C |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 16-Pin Wide SO (derate 9.5mW/°C above +70°C)762mW |                                                                                                                                                     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics—MAX1415**

$(V_{DD}=3V, GND=0, V_{REF+}=1.225V, V_{REF-}=GND, external f_{CLKIN}=2.4576MHz, CLKDIV bit=0, C_{REF+} to GND=0.1 \mu F, C_{REF-} to GND=0.1 \mu F, T_A=T_{MIN} to T_{MAX}, unless otherwise noted.)$

| PARAMETER                         | SYMBOL      | CONDITIONS                         | MIN TYP MA                                     | XX UNITS         |

|-----------------------------------|-------------|------------------------------------|------------------------------------------------|------------------|

| DC ACCURACY                       |             |                                    |                                                | •                |

| Resolution (No Missing Codes)     |             |                                    | 16                                             | Bits             |

| Output Noise                      |             |                                    | (Tables 1, 3)                                  | μV               |

| Integral Nonlinearity             | INL         | Gain = 1, bipolar mode, unbuffered | ±0.0                                           | 015 %FSR         |

| Unipolar Offset Error             |             | After calibration                  | (Note 1)                                       | μV               |

| Unipolar Offset Drift             |             | (Note 2)                           | 0.5                                            | μV/°C            |

| Bipolar Zero Error                |             | After calibration                  | (Note 1)                                       | μV               |

| Divides Zero Drift (Note 2)       |             | Gain = 1 to 4                      | 0.5                                            |                  |

| Bipolar Zero Drift (Note 2)       |             | Gain = 8 to 128                    | 0.1                                            | μV/°C            |

| Positive Full-Scale Error         |             | After calibration                  | (Notes 1, 3)                                   | μV               |

| Full-Scale Drift                  |             | (Notes 2, 4)                       | 0.5                                            | μV/°C            |

| Gain Error                        |             | After calibration                  | (Notes 1, 5)                                   | μV               |

| Gain Drift                        |             | (Notes 2, 6)                       | 0.5                                            | ppm of<br>FSR/°C |

| Bipolar Negative Full-Scale Error |             | After calibration                  | ±0.003                                         | %FSR             |

| Bipolar Negative Full-Scale Drift |             | Gain = 1 to 4                      | 1                                              | 1//00            |

| (Note 2)                          |             | Gain = 8 to 128                    | 0.6                                            | μV/°C            |

| ANALOG INPUTS (AIN1+, AIN1-,      | AIN2+, AIN2 | -)                                 |                                                | •                |

| AIN Differential Input Voltage    |             | Unipolar input range               | 0 V <sub>RI</sub>                              | JN               |

| Range (Note 7)                    |             | Bipolar input range                | -V <sub>REF</sub> / V <sub>RE</sub><br>GAIN GA |                  |

| AIN Absolute Input Voltage        |             | Unbuffered                         | GND - V <sub>DI</sub><br>30mV 30r              | mV               |

| Range (Note 8)                    |             | Buffered                           | GND + V <sub>D</sub><br>50mV 1.5               |                  |

| AIN DC Leakage Current            |             | Unselected input channel           | -                                              | nA               |

# **Electrical Characteristics—MAX1415 (continued)**

$(V_{DD}=3V,\,GND=0,\,V_{REF+}=1.225V,\,V_{REF-}=GND,\,external\,\,f_{CLKIN}=2.4576MHz,\,CLKDIV\,\,bit=0,\,C_{REF+}\,to\,\,GND=0.1\mu F,\,C_{REF-}\,to\,\,GND=0.1\mu F,\,T_{A}=T_{MIN}\,to\,\,T_{MAX},\,unless\,\,otherwise\,\,noted.)$

| PARAMETER                           | SYMBOL           | CONDITIONS                                                   | MIN  | TYP | MAX                        | UNITS |

|-------------------------------------|------------------|--------------------------------------------------------------|------|-----|----------------------------|-------|

|                                     |                  | Gain = 1                                                     |      | 34  |                            |       |

|                                     |                  | Gain = 2                                                     |      | 38  |                            | _     |

| AIN Input Capacitance               |                  | Gain = 4                                                     |      | 45  |                            | рF    |

|                                     |                  | Gain = 8 to 128                                              |      | 60  |                            |       |

| AIN Input Sampling Rate             | fs               | Gain = 1 to 128                                              |      |     | f <sub>CLKIN</sub> /<br>64 | MHz   |

|                                     |                  | Gain = 1                                                     |      | 105 |                            |       |

|                                     |                  | Gain = 2                                                     |      | 110 |                            |       |

| Input Common-Mode Rejection         | CMR              | Gain = 4                                                     |      | 120 |                            | dB    |

|                                     |                  | Gain = 8 to 128                                              |      | 130 |                            |       |

| Normal-Mode 50Hz Rejection          |                  | For filter notches of 25Hz, 50Hz, ±0.02 × f <sub>NOTCH</sub> |      | 98  |                            | dB    |

| Normal-Mode 60Hz Rejection          |                  | For filter notches of 20Hz, 60Hz, ±0.02 × f <sub>NOTCH</sub> |      | 98  |                            | dB    |

| Common-Mode 50Hz Rejection          |                  | For filter notches of 25Hz, 50Hz, ±0.02 × f <sub>NOTCH</sub> |      | 150 |                            | dB    |

| Common-Mode 60Hz Rejection          |                  | For filter notches of 20Hz, 60Hz, ±0.02 × f <sub>NOTCH</sub> |      | 150 |                            | dB    |

| EXTERNAL REFERENCE (REF+            | REF-)            |                                                              | •    |     |                            |       |

| REF Differential Input Range        | V <sub>REF</sub> | (Note 9)                                                     | 1.00 |     | 1.75                       | V     |

| REF Absolute Input Voltage<br>Range |                  |                                                              | GND  |     | V <sub>DD</sub>            | V     |

| REF Input Capacitance               |                  | Gain = 1 to 128                                              |      | 10  |                            | рF    |

| REF Input Sampling Rate             | f <sub>S</sub>   |                                                              |      |     | f <sub>CLKIN</sub> /<br>64 | MHz   |

| DIGITAL INPUTS (DIN, SCLK, CS       | S, RESET)        |                                                              | •    |     |                            |       |

| Input High Voltage                  | VIH              |                                                              | 2.0  |     |                            | V     |

| Input Low Voltage                   | VIL              |                                                              |      |     | 0.4                        | V     |

|                                     |                  | DIN, CS, RESET                                               |      | 250 |                            |       |

| Input Hysteresis                    | VHYST            | SCLK                                                         |      | 500 |                            | mV    |

| Input Current                       | I <sub>IN</sub>  |                                                              |      |     | ±1                         | μΑ    |

| Input Capacitance                   |                  |                                                              |      | 5   |                            | pF    |

| CLKIN INPUT                         | -                |                                                              | •    |     |                            |       |

| CLKIN Input High Voltage            | VCLKINH          |                                                              | 2.5  |     |                            | V     |

| CLKIN Input Low Voltage             | VCLKINL          |                                                              |      |     | 0.4                        | V     |

| CLKIN Input Current                 | ICLKIN           |                                                              |      |     | ±10                        | μΑ    |

| DIGITAL OUTPUTS (DOUT, DRD          |                  |                                                              |      |     |                            |       |

| •                                   |                  | DOUT and DRDY, ISINK = 100µA                                 |      |     | 0.4                        | ١.    |

| Output-Voltage Low                  | V <sub>OL</sub>  | CLKOUT, ISINK = 10µA                                         |      |     | 0.4                        | V     |

# **Electrical Characteristics—MAX1415 (continued)**

$(V_{DD}=3V,\,GND=0,\,V_{REF+}=1.225V,\,V_{REF-}=GND,\,external\,\,f_{CLKIN}=2.4576MHz,\,CLKDIV\,\,bit=0,\,C_{REF+}\,to\,\,GND=0.1\mu F,\,C_{REF-}\,to\,\,GND=0.1\mu F,\,T_{A}=T_{MIN}\,to\,\,T_{MAX},\,unless\,\,otherwise\,\,noted.)$

| PARAMETER                        | SYMBOL          | CONDITIO                                                                  | ONS                                | MIN                                   | TYP                       | MAX                                  | UNITS |    |

|----------------------------------|-----------------|---------------------------------------------------------------------------|------------------------------------|---------------------------------------|---------------------------|--------------------------------------|-------|----|

| Output-Voltage High              | Vari            | DOUT and DRDY, ISOURG                                                     | <br>CE = 100μΑ                     | V <sub>DD</sub> -<br>0.6V             |                           |                                      | V     |    |

| Output-voitage riigii            | Voh             | CLKOUT, ISOURCE = 10µ                                                     | CLKOUT, ISOURCE = 10µA             |                                       | V <sub>DD</sub> -<br>0.6V |                                      | 7     |    |

| Tri-State Leakage Current        | ΙL              | DOUT only                                                                 |                                    |                                       |                           | ±10                                  | μΑ    |    |

| Tri-State Output Capacitance     | Cout            | DOUT only                                                                 |                                    |                                       | 9                         |                                      | рF    |    |

| SYSTEM CALIBRATION               |                 |                                                                           |                                    |                                       |                           |                                      |       |    |

| Full-Scale Calibration Range     |                 | GAIN = selected PGA ga<br>(Note 10)                                       | in (1 to 128)                      | -1.05 ×<br>V <sub>REF</sub> /<br>GAIN |                           | 1.05 ×<br>V <sub>REF</sub> /<br>GAIN | V     |    |

| Offset Calibration Range         |                 | GAIN = selected PGA gain (1 to 128) (Note 10)                             |                                    | -1.05 ×<br>V <sub>REF</sub> /<br>GAIN |                           | 1.05 ×<br>V <sub>REF</sub> /<br>GAIN | V     |    |

| Input Span                       |                 | GAIN = selected PGA gain (1 to 128)<br>(Notes 10, 11)                     |                                    | 0.8 ×<br>V <sub>REF</sub> /<br>GAIN   |                           | 2.1 ×<br>V <sub>REF</sub> /<br>GAIN  | V     |    |

| POWER REQUIREMENTS               |                 | •                                                                         |                                    |                                       |                           |                                      |       |    |

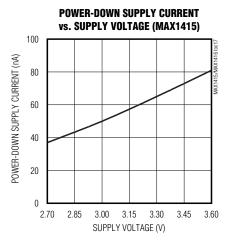

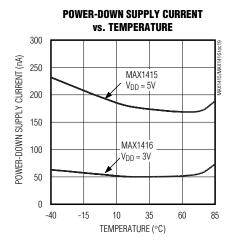

| Power-Supply Voltage             | V <sub>DD</sub> |                                                                           |                                    | 2.7                                   |                           | 3.6                                  | V     |    |

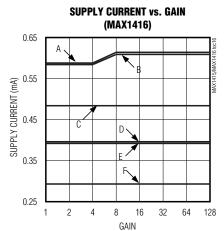

|                                  |                 | Unbuffered, f <sub>CLKIN</sub> = 1MHz, gain = 1 to 128                    |                                    |                                       |                           | 0.40                                 |       |    |

|                                  |                 | Buffered, f <sub>CLKIN</sub> = 1MHz,                                      | gain = 1 to 128                    |                                       |                           | 0.725                                |       |    |

|                                  |                 | Unbuffered,                                                               | Gain = 1 to 4                      |                                       |                           | 0.55                                 | m ^   |    |

| Power-Supply Current (Note 12)   | I <sub>DD</sub> | I <sub>DD</sub>                                                           | $f_{CLKIN} = 2.4576MHz$            | Gain = 8 to 128                       |                           |                                      | 0.55  | mA |

|                                  |                 |                                                                           | Buffered,                          | Gain = 1 to 4                         |                           |                                      | 0.825 |    |

|                                  |                 | $f_{CLKIN} = 2.4576MHz$                                                   | Gain = 8 to 128                    |                                       |                           | 1.0                                  |       |    |

|                                  |                 | Power-down mode (Note                                                     | 13)                                |                                       |                           | 8                                    | μΑ    |    |

| Power-Supply Rejection Ratio     | PSRR            | $V_{DD} = 2.7V \text{ to } 3.6V$                                          |                                    | (                                     | Note 14)                  |                                      | dB    |    |

| <b>EXTERNAL-CLOCK TIMING SPE</b> | CIFICATION      | S                                                                         |                                    |                                       |                           |                                      |       |    |

| CLKIN Frequency                  | fCLKIN          | (Note 15)                                                                 |                                    | 400                                   |                           | 2500                                 | kHz   |    |

| Duty Cycle                       |                 |                                                                           |                                    | 40                                    |                           | 60                                   | %     |    |

| INTERNAL-CLOCK TIMING SPE        | CIFICATIONS     | 3                                                                         |                                    |                                       |                           |                                      |       |    |

|                                  |                 | MAX1415AE,<br>f <sub>CLK</sub> = 1MHz (CLK = 0)<br>or 2.4576MHz (CLK = 1) | T <sub>A</sub> = -40°C to<br>+85°C |                                       |                           | ±4                                   |       |    |

| Internal-Clock Frequency         | fCLK            | MAX1415C,<br>f <sub>CLK</sub> = 1MHz (CLK = 0)<br>or 2.4576MHz (CLK = 1)  | T <sub>A</sub> = 0°C to<br>+70°C   |                                       |                           | ±4                                   | %     |    |

|                                  |                 | MAX1415E,<br>f <sub>CLK</sub> = 1MHz (CLK = 0)                            | $T_A = -40$ °C to 0°C              |                                       |                           | ±7                                   |       |    |

|                                  |                 | or 2.4576MHz (CLK = 1) T <sub>A</sub> = 0°C to +85°C                      |                                    |                                       |                           | ±4                                   |       |    |

## **Electrical Characteristics—MAX1415 (continued)**

$(V_{DD}=3V, GND=0, V_{REF+}=1.225V, V_{REF-}=GND, external \ f_{CLKIN}=2.4576MHz, CLKDIV \ bit=0, C_{REF+} \ to \ GND=0.1 \mu F, C_{REF-} \ to \ GND=0.1 \mu F, T_A=T_{MIN} \ to \ T_{MAX}, unless \ otherwise \ noted.)$

| PARAMETER                         | SYMBOL               | CONDITIONS    | MIN | TYP  | MAX | UNITS |

|-----------------------------------|----------------------|---------------|-----|------|-----|-------|

| Typical Conversion-Time Variation | $\Delta$ t $_{CONV}$ | tconv = 1/ODR |     | ±0.5 |     | %     |

# **Timing Characteristics—MAX1415**

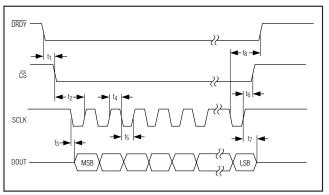

(Note 16) (Figures 8, 9)

| PARAMETER                                     | SYMBOL          | CONDITIONS | MIN                        | TYP | MAX | UNITS |

|-----------------------------------------------|-----------------|------------|----------------------------|-----|-----|-------|

| DRDY High Time                                |                 |            | 500/<br>f <sub>CLKIN</sub> |     |     | S     |

| Reset Pulse-Width Low                         |                 |            | 100                        |     |     | ns    |

| DRDY Fall to CS Fall Setup Time               | t <sub>1</sub>  |            | 0                          |     |     | ns    |

| CS Fall to SCLK Rise Setup Time               | t <sub>2</sub>  |            | 120                        |     |     | ns    |

| SCLK Fall to DOUT Valid Delay                 | t <sub>3</sub>  |            | 0                          |     | 100 | ns    |

| SCLK Pulse-Width High                         | t <sub>4</sub>  |            | 100                        |     |     | ns    |

| SCLK Pulse-Width Low                          | t <sub>5</sub>  |            | 100                        |     |     | ns    |

| CS Rise to SCLK Rise Hold Time                | t <sub>6</sub>  |            | 0                          |     |     | ns    |

| Bus Relinquish Time After SCLK<br>Rising Edge | t <sub>7</sub>  |            |                            |     | 100 | ns    |

| SCLK Fall to DRDY Rise Delay                  | t <sub>8</sub>  |            |                            |     | 100 | ns    |

| DIN to SCLK Setup Time                        | t9              |            | 30                         |     |     | ns    |

| DIN to SCLK Hold Time                         | t <sub>10</sub> |            | 20                         |     |     | ns    |

### **Electrical Characteristics—MAX1416**

$(V_{DD}=5V,~GND=0,~V_{REF+}=2.5V,~V_{REF-}=GND,~f_{CLKIN}=2.4576MHz,~CLKDIV~bit=0,~C_{REF+}~to~GND=0.1\mu F,~C_{REF-}~to~GND=0.1\mu F,~T_{A}=T_{MIN}~to~T_{MAX},~unless~otherwise~noted.)$

| PARAMETER                     | SYMBOL | CONDITIONS                         | MIN | TYP       | MAX     | UNITS |

|-------------------------------|--------|------------------------------------|-----|-----------|---------|-------|

| DC ACCURACY                   |        |                                    |     |           |         |       |

| Resolution (No Missing Codes) |        |                                    | 16  |           |         | Bits  |

| Output Noise                  |        |                                    | (   | Tables 1, | 3)      | μV    |

| Integral Nonlinearity         | INL    | Gain = 1, bipolar mode, unbuffered |     |           | ±0.0015 | %FSR  |

| Unipolar Offset Error         |        | After calibration                  |     | (Note 1)  |         | μV    |

| Unipolar Offset Drift         |        | (Note 2)                           |     | 0.5       |         | μV/°C |

| Bipolar Zero Error            |        | After calibration                  |     | (Note 1)  |         | μV    |

| Dipolar Zara Drift (Nota 2)   |        | Gain = 1 to 4                      |     | 0.5       |         | W//9C |

| Bipolar Zero Drift (Note 2)   |        | Gain = 8 to 128                    |     | 0.1       |         | μV/°C |

# **Electrical Characteristics—MAX1416 (continued)**

$(V_{DD}=5V,\,GND=0,\,V_{REF+}=2.5V,\,V_{REF-}=GND,\,f_{CLKIN}=2.4576MHz,\,CLKDIV\,\,bit=0,\,C_{REF+}\,to\,\,GND=0.1\mu F,\,C_{REF-}\,to\,\,GND=0.1\mu F,\,C_{REF-}\,t$

| PARAMETER                         | SYMBOL      | CONDITIONS                                                   | MIN TY                      | P MAX                      | UNITS            |

|-----------------------------------|-------------|--------------------------------------------------------------|-----------------------------|----------------------------|------------------|

| Positive Full-Scale Error         |             | After calibration                                            | (Notes                      | 1, 3)                      | μV               |

| Full-Scale Drift                  |             | (Notes 2, 4)                                                 | 0.5                         | 5                          | μV/°C            |

| Gain Error                        |             | After calibration                                            | (Notes                      | 1, 5)                      | μV               |

| Gain Drift                        |             | (Notes 2, 6)                                                 | 0.5                         | 5                          | ppm of<br>FSR/°C |

| Bipolar Negative Full-Scale Error |             | After calibration                                            | ±0.0                        | 03                         | %FSR             |

| Bipolar Negative Full-Scale Drift |             | Gain = 1 to 4                                                | 1                           |                            | μV/°C            |

| (Note 2)                          |             | Gain = 8 to 128                                              | 0.6                         | 6                          | μν/ С            |

| ANALOG INPUTS (AIN1+, AIN1-,      | AIN2+, AIN2 | -)                                                           |                             |                            |                  |

| AIN Differential Input Voltage    |             | Unipolar input range                                         | 0                           | V <sub>REF</sub> /<br>GAIN | V                |

| Range (Note 7)                    |             | Bipolar input range                                          | -V <sub>REF</sub> /<br>GAIN | V <sub>REF</sub> /<br>GAIN | V                |

| AIN Absolute Input Voltage        |             | Unbuffered                                                   | GND -<br>30mV               | V <sub>DD</sub> +<br>30mV  |                  |

| Range (Note 8)                    |             | Buffered                                                     | GND +<br>50mV               | V <sub>DD</sub> -<br>1.5V  | V                |

| AIN DC Leakage Current            |             | Unselected input channel                                     |                             | 1                          | nA               |

|                                   |             | Gain = 1                                                     | 34                          |                            |                  |

| AINI logust Connecitors           |             | Gain = 2                                                     | 38                          |                            |                  |

| AIN Input Capacitance             |             | Gain = 4                                                     | 45                          |                            | pF               |

|                                   |             | Gain = 8 to 128                                              | 60                          | 1                          |                  |

| AIN Input Sampling Rate           | fs          | Gain = 1 to 128                                              |                             | f <sub>CLKIN</sub> / 64    | MHz              |

|                                   |             | Gain = 1                                                     | 96                          | i                          |                  |

| Innut Common Made Dejection       | CMD         | Gain = 2                                                     | 109                         | 5                          | 4D               |

| Input Common-Mode Rejection       | CMR         | Gain = 4                                                     | 110                         | )                          | dB               |

|                                   |             | Gain = 8 to 128                                              | 130                         | )                          |                  |

| Normal-Mode 50Hz Rejection        |             | For filter notches of 25Hz, 50Hz, ±0.02 × f <sub>NOTCH</sub> | 98                          |                            | dB               |

| Normal-Mode 60Hz Rejection        |             | For filter notches of 20Hz, 60Hz, ±0.02 × fNOTCH             | 98                          |                            | dB               |

| Common-Mode 50Hz Rejection        |             | For filter notches of 25Hz, 50Hz, ±0.02 × fNOTCH             | 150                         | )                          | dB               |

| Common-Mode 60Hz Rejection        |             | For filter notches of 20Hz, 60Hz, ±0.02 × f <sub>NOTCH</sub> | 150                         | )                          | dB               |

# **Electrical Characteristics—MAX1416 (continued)**

$(V_{DD}=5V,\,GND=0,\,V_{REF+}=2.5V,\,V_{REF-}=GND,\,f_{CLKIN}=2.4576MHz,\,CLKDIV\,\,bit=0,\,C_{REF+}\,to\,\,GND=0.1\mu F,\,C_{REF-}\,to\,\,GND=0.1\mu F,\,C_{REF-}\,t$

| PARAMETER                    | SYMBOL           | CONDITIONS                                            | MIN                                   | TYP | MAX                                   | UNITS |

|------------------------------|------------------|-------------------------------------------------------|---------------------------------------|-----|---------------------------------------|-------|

| EXTERNAL REFERENCE (REF      | +, REF-)         | •                                                     | •                                     |     |                                       |       |

| REF Differential Input Range | V <sub>REF</sub> | (Note 9)                                              | 1                                     |     | 3.5                                   | V     |

| REF Absolute Input Voltage   |                  |                                                       | GND                                   |     | $V_{DD}$                              | V     |

| REF Input Capacitance        |                  | Gain = 1 to 128                                       |                                       | 10  |                                       | рF    |

| REF Input Sampling Rate      | f <sub>S</sub>   |                                                       |                                       |     | f <sub>CLKIN</sub> /<br>64            | MHz   |

| DIGITAL INPUTS (DIN, SCLK, ( | CS, RESET)       |                                                       |                                       |     |                                       |       |

| Input High Voltage           | VIH              |                                                       | 2                                     |     |                                       | V     |

| Input Low Voltage            | VIL              |                                                       |                                       |     | 0.8                                   | V     |

| Input Hysteresis             | VHYST            | DIN, CS, RESET                                        |                                       | 250 |                                       | mV    |

| Input Hysteresis             | VHYSI            | SCLK                                                  |                                       | 500 |                                       | 1110  |

| Input Current                | I <sub>IN</sub>  |                                                       |                                       |     | ±1                                    | μΑ    |

| Input Capacitance            |                  |                                                       |                                       | 5   |                                       | рF    |

| CLKIN INPUT                  |                  |                                                       |                                       |     |                                       |       |

| CLKIN Input High Voltage     | VCLKINH          |                                                       | 3.5                                   |     |                                       | V     |

| CLKIN Input Low Voltage      | VCLKINL          |                                                       |                                       |     | 0.8                                   | V     |

| CLKIN Input Current          | ICLKIN           |                                                       |                                       |     | ±10                                   | μΑ    |

| DIGITAL OUTPUTS (DOUT, DR    | DY, CLKOUT)      |                                                       |                                       |     |                                       |       |

| Output-Voltage Low           | V <sub>OL</sub>  | DOUT and $\overline{DRDY}$ , ISINK = 800 $\mu$ A      |                                       |     | 0.4                                   | V     |

| Output-voitage Low           | VOL              | CLKOUT, ISINK = 10µA                                  |                                       |     | 0.4                                   | V     |

| Output-Voltage High          | V <sub>OH</sub>  | DOUT and $\overline{DRDY}$ , ISOURCE = 200 $\mu$ A    | 4.0                                   |     |                                       | V     |

| Output-voitage riigir        | VOH              | CLKOUT, I <sub>SOURCE</sub> = 10µA                    | 4.0                                   |     |                                       | V     |

| Tri-State Leakage Current    | Ι <u></u>        | DOUT only                                             |                                       |     | ±10                                   | μΑ    |

| Tri-State Output Capacitance | Cout             | DOUT only                                             |                                       | 9   |                                       | рF    |

| SYSTEM CALIBRATION           |                  |                                                       | •                                     |     |                                       |       |

| Full-Scale Calibration Range |                  | GAIN = selected PGA gain (1 to 128)<br>(Note 10)      | -1.05 ×<br>V <sub>REF</sub> /<br>GAIN |     | +1.05 ×<br>V <sub>REF</sub> /<br>GAIN | V     |

| Offset Calibration Range     |                  | GAIN = selected PGA gain (1 to 128)<br>(Note 10)      | -1.05 ×<br>V <sub>REF</sub> /<br>GAIN |     | +1.05 ×<br>V <sub>REF</sub> /<br>GAIN | V     |

| Input Span                   |                  | GAIN = selected PGA gain (1 to 128)<br>(Notes 10, 11) | 0.8 ×<br>V <sub>REF</sub> /<br>GAIN   |     | 2.1 ×<br>V <sub>REF</sub> /<br>GAIN   | V     |

| POWER REQUIREMENTS           |                  |                                                       |                                       |     |                                       |       |

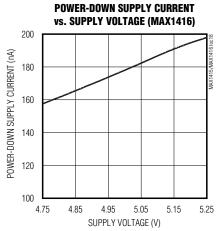

| Power-Supply Voltage         | V <sub>DD</sub>  |                                                       | 4.75                                  |     | 5.25                                  | V     |

|                              |                  | 1                                                     |                                       |     |                                       |       |

# **Electrical Characteristics—MAX1416 (continued)**

$(V_{DD}=5V,~GND=0,~V_{REF+}=2.5V,~V_{REF-}=GND,~f_{CLKIN}=2.4576MHz,~CLKDIV~bit=0,~C_{REF+}~to~GND=0.1\mu F,~C_{REF-}~to~GND=0.1\mu F,~C_{REF-}~to~GND=0$

| PARAMETER                            | SYMBOL      | CONDITIO                                                                  | ONS                                                | MIN | TYP       | MAX  | UNITS |

|--------------------------------------|-------------|---------------------------------------------------------------------------|----------------------------------------------------|-----|-----------|------|-------|

|                                      |             | Unbuffered, f <sub>CLKIN</sub> = 1MHz, gain = 1 to 128                    |                                                    |     |           | 0.45 |       |

|                                      |             | Buffered, f <sub>CLKIN</sub> = 1MHz,                                      | gain = 1 to 128                                    |     |           | 0.78 |       |

|                                      |             | Unbuffered,                                                               | Gain = 1 to 4                                      |     |           | 0.6  |       |

| Power-Supply Current (Note 12)       | IDD         | f <sub>CLKIN</sub> = 2.4576MHz                                            | Gain = 8 to 128                                    |     |           | 0.6  | mA    |

|                                      |             | Buffered,                                                                 | Gain = 1 to 4                                      |     |           | 0.95 |       |

|                                      |             | f <sub>CLKIN</sub> = 2.4576MHz                                            | Gain = 8 to 128                                    |     |           | 1.1  |       |

|                                      |             | Power-down mode (Note                                                     | 13)                                                |     |           | 16   | μΑ    |

| Power-Supply Rejection Ratio         | PSRR        | $V_{DD} = 4.75V \text{ to } 5.25V$                                        |                                                    |     | (Note 14) |      | dB    |

| EXTERNAL-CLOCK SPECIFICAT            | IONS        |                                                                           |                                                    |     |           |      |       |

| CLKIN Frequency                      | fCLKIN      | (Note 15)                                                                 |                                                    | 400 |           | 2500 | kHz   |

| Duty Cycle                           |             |                                                                           |                                                    | 40  |           | 60   | %     |

| INTERNAL-CLOCK TIMING SPEC           | CIFICATIONS |                                                                           |                                                    |     |           |      |       |

|                                      |             | MAX1416AE,<br>f <sub>CLK</sub> = 1MHz (CLK = 0)<br>or 2.4576MHz (CLK = 1) | $T_A = -40^{\circ}\text{C to} +85^{\circ}\text{C}$ |     |           | ±4   |       |

| Internal-Clock Frequency             | fCLK        | MAX1416C,<br>f <sub>CLK</sub> = 1MHz (CLK = 0)<br>or 2.4576MHz (CLK = 1)  | T <sub>A</sub> = 0°C to<br>+70°C                   |     |           | ±4   | %     |

|                                      |             | MAX1416E,<br>f <sub>CLK</sub> = 1MHz (CLK = 0)                            | $T_A = -40$ °C to 0°C                              |     |           | ±7   |       |

|                                      |             | or 2.4576MHz (CLK = 0)                                                    | $T_A = 0$ °C to +85°C                              |     |           | ±4   |       |

| Typical Conversion-Time<br>Variation | Δtconv      | t <sub>CONV</sub> = 1/ODR,<br>CLK = 0 (1MHz), INTCLK                      | = 1                                                |     | ±0.5      |      | %     |

# **Timing Characteristics—MAX1416**

(Note 16) (Figures 8, 9)

| PARAMETER                                     | SYMBOL         | CONDITIONS | MIN                         | TYP | MAX | UNITS |

|-----------------------------------------------|----------------|------------|-----------------------------|-----|-----|-------|

| DRDY High Time                                |                |            | 500 /<br>f <sub>CLKIN</sub> |     |     | S     |

| Reset Pulse-Width Low                         |                |            | 100                         |     |     | ns    |

| DRDY Fall to CS Fall Setup Time               | t <sub>1</sub> |            | 0                           |     |     | ns    |

| CS Fall to SCLK Rise Setup Time               | t <sub>2</sub> |            | 120                         |     |     | ns    |

| SCLK Fall to DOUT Valid Delay                 | t <sub>3</sub> |            | 0                           |     | 80  | ns    |

| SCLK Pulse-Width High                         | t <sub>4</sub> |            | 100                         |     |     | ns    |

| SCLK Pulse-Width Low                          | t <sub>5</sub> |            | 100                         |     |     | ns    |

| CS Rise to SCLK Rise Hold Time                | t <sub>6</sub> |            | 0                           |     |     | ns    |

| Bus Relinquish Time After SCLK<br>Rising Edge | t <sub>7</sub> |            |                             |     | 60  | ns    |

| SCLK Fall to DRDY Rise Delay                  | t <sub>8</sub> |            |                             |     | 100 | ns    |

## **Timing Characteristics—MAX1416 (continued)**

(Note 16) (Figures 8, 9)

| PARAMETER              | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |

|------------------------|-----------------|------------|-----|-----|-----|-------|

| DIN to SCLK Setup Time | t9              |            | 30  |     |     | ns    |

| DIN to SCLK Hold Time  | t <sub>10</sub> |            | 20  |     |     | ns    |

- **Note 1:** These errors are in the order of the conversion noise shown in Tables 1 and 3. This applies after calibration at the given temperature.

- Note 2: Recalibration at any temperature removes these drift errors.

- Note 3: Positive full-scale error includes zero-scale errors (unipolar offset error or bipolar zero error) and applies to both unipolar and bipolar input ranges.

- Note 4: Full-scale drift includes zero-scale drift (unipolar offset drift or bipolar zero drift) and applies to both unipolar and bipolar input ranges.

- Note 5: Gain error does not include zero-scale errors. It is calculated as (full-scale error unipolar offset error) for unipolar ranges, and (full-scale error bipolar zero error) for bipolar ranges.

- **Note 6:** Gain-error drift does not include unipolar offset drift or bipolar zero drift. Effectively, it is the drift of the part if only zero-scale calibrations are performed.

- Note 7: The analog input voltage range on AIN+ is given here with respect to the voltage on AIN- on the MAX1415/MAX1416.

- **Note 8:** This common-mode voltage range is allowed, provided that the input voltage on the analog inputs does not go more positive than (V<sub>DD</sub> + 30mV) or more negative than (GND 30mV). Parts are functional with voltages down to (GND 200mV), but with increased leakage at high temperature.

- Note 9: The REF differential voltage, VREF, is the voltage on REF+ referenced to REF- (VREF = VREF+ VREF-).

- Note 10: Guaranteed by design.

- Note 11: These calibration and span limits apply, provided that the absolute voltage on the analog inputs does not exceed (V<sub>DD</sub> + 30mV) or go more negative than (GND 30mV). The offset-calibration limit applies to both the unipolar zero point and the bipolar zero point.

- **Note 12:** When using a crystal or ceramic resonator across the CLKIN and CLKOUT as the clock source for the device, the supply current and power dissipation varies depending on the crystal or resonator type. Supply current is measured with the digital inputs connected to 0 or V<sub>DD</sub>, CLKIN connected to an external clock source, and CLKDIS = 1.

- Note 13: If the external master clock continues to run in power-down mode, the power-down current typically increases to 67μA at 3V. When using a crystal or ceramic resonator across the CLKIN and CLKOUT as the clock source for the device, the clock generator continues to run in power-down mode and the power dissipation depends on the crystal or resonator type (see the *Power-Down Modes* section).

- **Note 14:** Measured at DC and applied in the selected passband. PSRR at 50Hz exceeds 120dB with filter notches of 25Hz or 50Hz. PSRR at 60Hz exceeds 120dB with filter notches of 20Hz or 60Hz.

PSRR depends on both gain and V<sub>DD</sub>.

| GAIN     | PSRR (V <sub>DD</sub> = 5V) | PSRR (V <sub>DD</sub> = 3V)<br>(dB) |

|----------|-----------------------------|-------------------------------------|

| 1        | 90                          | 86                                  |

| 2        | 78                          | 78                                  |

| 4        | 84                          | 85                                  |

| 8 to 128 | 91                          | 93                                  |

- **Note 15:** Provide f<sub>CLKIN</sub> whenever the MAX1415/MAX1416 are not in power-down mode. If no clock is present, the device can draw higher-than-specified current and can possibly become uncalibrated.

- **Note 16:** All input signals are specified with  $t_f = t_f = 5$ ns (10% to 90% of V<sub>DD</sub>) and timed from a voltage level of 1.6V.

Table 1. MAX1415—Output RMS Noise vs. Gain and Output Data Rate (3V)

| FILTER FIRST NOTCH               | O ID EDECLIENCY |        |        | TYPICA | L OUTPU | RMS NO | ISE (μV) |      |      |  |

|----------------------------------|-----------------|--------|--------|--------|---------|--------|----------|------|------|--|

| AND OUTPUT DATA                  | -3dB FREQUENCY  |        | GAIN   |        |         |        |          |      |      |  |

| RATE (Hz)                        | (Hz)            | 1      | 2      | 4      | 8       | 16     | 32       | 64   | 128  |  |

| BUFFERED (f <sub>CLKIN</sub> = 1 | MHz)            |        |        |        |         |        |          |      |      |  |

| 20                               | 5.24            | 2.85   | 1.63   | 2.16   | 0.70    | 0.67   | 0.63     | 0.64 | 0.62 |  |

| 25                               | 6.55            | 3.46   | 1.92   | 1.13   | 6.05    | 0.75   | 0.73     | 0.70 | 0.70 |  |

| 100                              | 26.2            | 48.94  | 26.98  | 11.99  | 0.85    | 3.44   | 2.27     | 1.66 | 1.72 |  |

| 200                              | 52.4            | 270.91 | 161.33 | 66.19  | 32.64   | 16.89  | 8.34     | 4.98 | 4.86 |  |

| UNBUFFERED (fcLKIN =             | = 1MHz)         |        |        |        |         |        |          |      |      |  |

| 20                               | 5.24            | 3.09   | 1.70   | 1.05   | 0.72    | 0.66   | 0.64     | 0.60 | 0.60 |  |

| 25                               | 6.55            | 3.58   | 1.94   | 1.23   | 0.80    | 0.77   | 0.73     | 0.70 | 0.70 |  |

| 100                              | 26.2            | 51.92  | 24.54  | 11.47  | 6.14    | 3.26   | 2.16     | 1.67 | 1.64 |  |

| 200                              | 52.4            | 263.86 | 136.78 | 65.40  | 34.51   | 16.64  | 8.97     | 4.96 | 4.80 |  |

| BUFFERED (fcLKIN = 2.            | 4576MHz)        |        |        |        |         |        |          |      |      |  |

| 50                               | 13.1            | 3.03   | 1.97   | 1.34   | 1.01    | 0.95   | 0.93     | 0.96 | 0.95 |  |

| 60                               | 15.72           | 3.62   | 2.14   | 1.52   | 1.05    | 0.98   | 1.03     | 1.04 | 1.00 |  |

| 250                              | 65.5            | 51.02  | 25.44  | 12.95  | 6.19    | 3.84   | 2.70     | 2.35 | 2.23 |  |

| 500                              | 131             | 280.58 | 138.29 | 70.21  | 34.60   | 18.44  | 9.45     | 5.40 | 5.34 |  |

| UNBUFFERED (fcLKIN =             | = 2.4576MHz)    |        |        |        |         |        |          |      |      |  |

| 50                               | 13.1            | 3.76   | 1.63   | 0.96   | 0.69    | 0.66   | 0.64     | 0.59 | 0.61 |  |

| 60                               | 15.72           | 3.11   | 1.86   | 1.12   | 0.78    | 0.75   | 0.71     | 0.71 | 0.69 |  |

| 250                              | 65.5            | 48.28  | 25.13  | 12.75  | 6.18    | 3.32   | 2.12     | 1.59 | 1.62 |  |

| 500                              | 131             | 280.67 | 143.15 | 75.84  | 34.70   | 17.88  | 9.19     | 4.90 | 4.98 |  |

Table 2. MAX1415—Peak-to-Peak Resolution vs. Gain and Output Data Rate

| FILTER FIRST NOTCH               |                |      | TY | PICAL PE | AK-TO-PE | AK RESOL | UTION (BI | TS) |     |  |

|----------------------------------|----------------|------|----|----------|----------|----------|-----------|-----|-----|--|

| AND OUTPUT DATA                  | -3dB FREQUENCY | GAIN |    |          |          |          |           |     |     |  |

| RATE<br>(Hz)                     | (Hz)           | 1    | 2  | 4        | 8        | 16       | 32        | 64  | 128 |  |

| BUFFERED (f <sub>CLKIN</sub> = 1 | MHz)           |      |    |          |          | I        |           |     | 1   |  |

| 20                               | 5.24           | 16   | 16 | 16       | 16       | 15       | 14        | 13  | 12  |  |

| 25                               | 6.55           | 16   | 16 | 16       | 12       | 15       | 14        | 13  | 12  |  |

| 100                              | 26.2           | 12   | 12 | 12       | 16       | 12       | 12        | 11  | 11  |  |

| 200                              | 52.4           | 10   | 10 | 10       | 10       | 10       | 10        | 10  | 9   |  |

| UNBUFFERED (fCLKIN               | = 1MHz)        |      |    |          |          |          |           |     |     |  |

| 20                               | 5.24           | 16   | 16 | 16       | 16       | 15       | 14        | 13  | 12  |  |

| 25                               | 6.55           | 16   | 16 | 16       | 16       | 15       | 14        | 13  | 12  |  |

| 100                              | 26.2           | 12   | 12 | 12       | 12       | 12       | 12        | 12  | 11  |  |

| 200                              | 52.4           | 10   | 10 | 10       | 10       | 10       | 10        | 10  | 9   |  |

| BUFFERED (f <sub>CLKIN</sub> = 2 | .4576MHz)      |      |    |          |          |          |           |     |     |  |

| 50                               | 13.1           | 16   | 16 | 16       | 15       | 15       | 14        | 13  | 12  |  |

| 60                               | 15.72          | 16   | 16 | 16       | 15       | 14       | 13        | 12  | 11  |  |

| 250                              | 65.5           | 12   | 12 | 12       | 12       | 12       | 12        | 11  | 10  |  |

| 500                              | 131            | 10   | 10 | 10       | 10       | 10       | 10        | 10  | 9   |  |

| UNBUFFERED (fclkin               | = 2.4576MHz)   |      |    |          |          |          |           |     |     |  |

| 50                               | 13.1           | 16   | 16 | 16       | 16       | 15       | 14        | 13  | 12  |  |

| 60                               | 15.72          | 16   | 16 | 16       | 16       | 15       | 14        | 13  | 12  |  |

| 250                              | 65.5           | 12   | 12 | 12       | 12       | 12       | 12        | 12  | 11  |  |

| 500                              | 131            | 10   | 10 | 10       | 10       | 10       | 10        | 10  | 9   |  |

Table 3. MAX1416—Output RMS Noise vs. Gain and Output Data Rate (5V)

|                                   |                |        |        | TVDICA | LOUTDU | L DMC NO | CE (\/\ |      |       |

|-----------------------------------|----------------|--------|--------|--------|--------|----------|---------|------|-------|

| FILTER FIRST NOTCH                | -3dB FREQUENCY |        |        | TYPICA |        | RMS NO   | SE (μν) |      |       |

| AND OUTPUT DATA                   | (Hz)           | GAIN   |        |        |        |          |         |      |       |

| RATE (Hz)                         | . ,            | 1      | 2      | 4      | 8      | 16       | 32      | 64   | 128   |

| BUFFERED (f <sub>CLKIN</sub> = 1  | MHz)           |        |        |        |        |          |         |      |       |

| 20                                | 5.24           | 3.51   | 1.87   | 1.11   | 0.75   | 0.70     | 0.71    | 0.67 | 0.65  |

| 25                                | 6.55           | 4.46   | 2.39   | 1.32   | 0.90   | 0.83     | 0.81    | 0.75 | 0.74  |

| 100                               | 26.2           | 92.29  | 47.60  | 28.62  | 11.60  | 6.40     | 3.70    | 2.34 | 2.30  |

| 200                               | 52.4           | 552.57 | 295.67 | 105.50 | 69.01  | 35.15    | 17.37   | 9.04 | 9.05  |

| UNBUFFERED (fcLKIN                | = 1MHz)        | •      |        |        |        |          | •       |      | •     |

| 20                                | 5.24           | 3.88   | 1.92   | 1.17   | 0.76   | 0.72     | 0.70    | 0.65 | 0.65  |

| 25                                | 6.55           | 5.00   | 2.60   | 1.41   | 0.87   | 0.83     | 0.81    | 0.73 | 0.74  |

| 100                               | 26.2           | 98.13  | 48.60  | 24.35  | 11.89  | 6.00     | 3.66    | 2.51 | 2.46  |

| 200                               | 52.4           | 551.95 | 275.15 | 134.65 | 69.82  | 33.34    | 16.77   | 9.04 | 9.36  |

| BUFFERED (f <sub>CLKIN</sub> = 2. | 4576MHz)       |        |        |        |        |          | •       |      | •     |

| 50                                | 13.1           | 4.10   | 2.56   | 1.68   | 1.23   | 1.19     | 1.21    | 1.15 | 1.19  |

| 60                                | 15.72          | 4.52   | 2.96   | 1.89   | 1.32   | 1.32     | 1.27    | 1.28 | 1.31  |

| 250                               | 65.5           | 96.62  | 47.35  | 26.33  | 12.42  | 7.10     | 4.30    | 3.16 | 3.19  |

| 500                               | 131            | 568.80 | 292.49 | 151.10 | 71.96  | 36.61    | 19.18   | 9.95 | 10.23 |

| UNBUFFERED (fcLKIN                | = 2.4576MHz)   |        |        |        |        |          |         |      |       |

| 50                                | 13.1           | 3.21   | 1.84   | 1.14   | 0.76   | 0.73     | 0.72    | 0.64 | 0.65  |

| 60                                | 15.72          | 3.93   | 2.21   | 1.37   | 0.87   | 0.81     | 0.77    | 0.74 | 0.73  |

| 250                               | 65.5           | 99.77  | 52.91  | 26.56  | 12.31  | 5.95     | 3.50    | 2.37 | 2.38  |

| 500                               | 131            | 520.55 | 302.42 | 136.54 | 68.66  | 36.94    | 18.64   | 9.34 | 9.49  |

Table 4. MAX1416—Peak-to-Peak Resolution vs. Gain and Output Data Rate

| FILTER FIRST NOTCH               |                |    | TYPICAL PEAK-TO-PEAK RESOLUTION (BITS)  GAIN |    |    |    |    |    |     |  |  |

|----------------------------------|----------------|----|----------------------------------------------|----|----|----|----|----|-----|--|--|

| AND OUTPUT DATA                  | -3dB FREQUENCY |    |                                              |    |    |    |    |    |     |  |  |

| RATE (Hz)                        | (Hz)           | 1  | 2                                            | 4  | 8  | 16 | 32 | 64 | 128 |  |  |

| BUFFERED (fcLKIN = 1             | MHz)           |    |                                              |    |    |    |    |    |     |  |  |

| 20                               | 5.24           | 16 | 16                                           | 16 | 16 | 16 | 15 | 14 | 13  |  |  |

| 25                               | 6.55           | 16 | 16                                           | 16 | 16 | 16 | 15 | 14 | 13  |  |  |

| 100                              | 26.2           | 12 | 12                                           | 12 | 12 | 12 | 12 | 12 | 11  |  |  |

| 200                              | 52.4           | 10 | 10                                           | 11 | 10 | 10 | 10 | 10 | 9   |  |  |

| UNBUFFERED (f <sub>CLKIN</sub>   | = 1MHz)        |    |                                              |    |    |    |    |    |     |  |  |

| 20                               | 5.24           | 16 | 16                                           | 16 | 16 | 16 | 15 | 14 | 13  |  |  |

| 25                               | 6.55           | 16 | 16                                           | 16 | 16 | 16 | 15 | 14 | 13  |  |  |

| 100                              | 26.2           | 12 | 12                                           | 12 | 12 | 12 | 12 | 12 | 11  |  |  |

| 200                              | 52.4           | 10 | 10                                           | 10 | 10 | 10 | 10 | 10 | 9   |  |  |

| BUFFERED (f <sub>CLKIN</sub> = 2 | .4576MHz)      |    |                                              |    |    |    |    |    |     |  |  |

| 50                               | 13.1           | 16 | 16                                           | 16 | 16 | 15 | 14 | 13 | 12  |  |  |

| 60                               | 15.72          | 16 | 16                                           | 16 | 16 | 15 | 14 | 13 | 12  |  |  |

| 250                              | 65.5           | 12 | 12                                           | 12 | 12 | 12 | 12 | 12 | 10  |  |  |

| 500                              | 131            | 10 | 10                                           | 10 | 10 | 10 | 10 | 10 | 9   |  |  |

| UNBUFFERED (fCLKIN               | = 2.4576MHz)   |    |                                              |    |    |    |    |    |     |  |  |

| 50                               | 13.1           | 16 | 16                                           | 16 | 16 | 16 | 15 | 14 | 13  |  |  |

| 60                               | 15.72          | 16 | 16                                           | 16 | 16 | 16 | 15 | 14 | 13  |  |  |

| 250                              | 65.5           | 12 | 12                                           | 12 | 12 | 12 | 12 | 12 | 11  |  |  |

| 500                              | 131            | 10 | 10                                           | 10 | 10 | 10 | 10 | 10 | 9   |  |  |

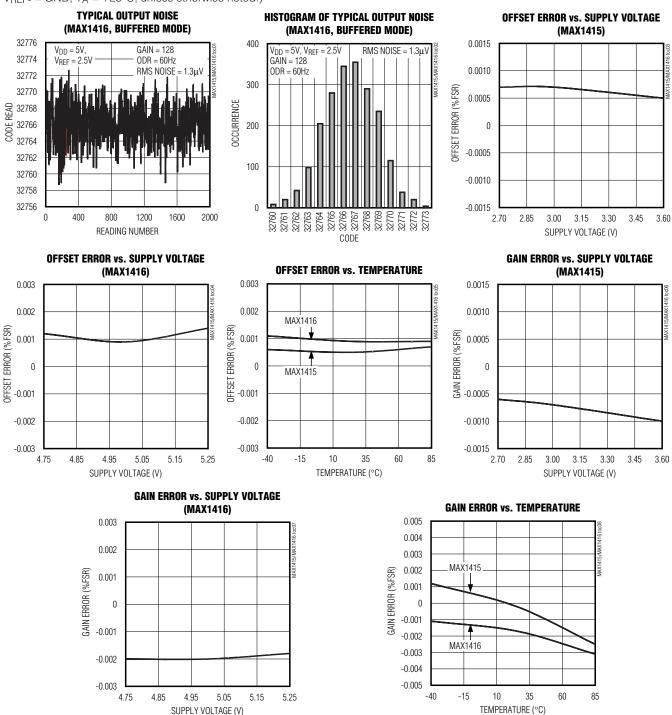

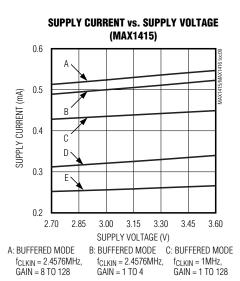

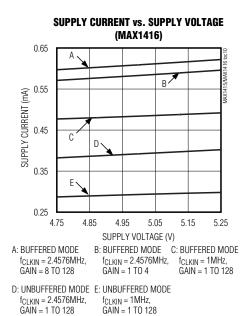

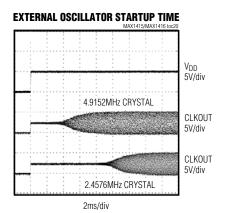

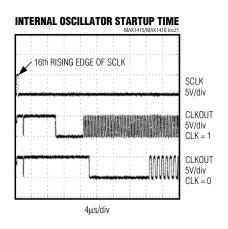

# **Typical Operating Characteristics**

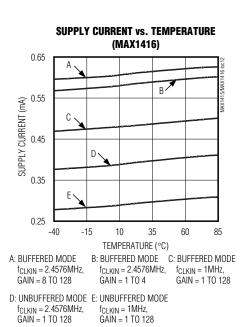

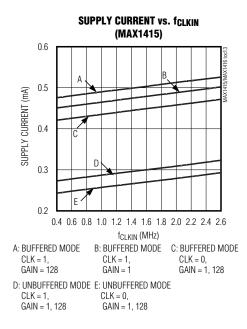

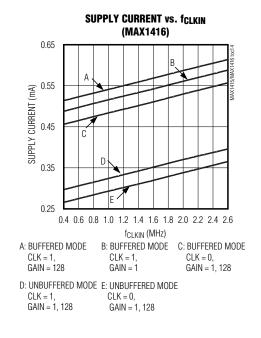

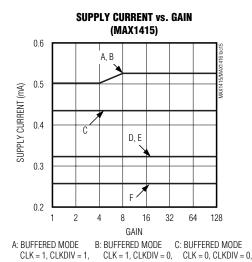

(MAX1415:  $V_{DD} = 5V$ ,  $V_{REF+} = 2.5V$ ,  $V_{REF+} = GND$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (MAX1416:  $V_{DD} = 3V$ ,  $V_{REF+} = 1.225V$ ,  $V_{REF-} = GND$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# **Typical Operating Characteristics (continued)**

(MAX1415:  $V_{DD} = 5V$ ,  $V_{REF+} = 2.5V$ ,  $V_{REF+} = GND$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (MAX1416:  $V_{DD} = 3V$ ,  $V_{REF+} = 1.225V$ ,  $V_{REF-} = GND$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

D: UNBUFFERED MODE E: UNBUFFERED MODE  $\begin{array}{ll} \text{f}_{\text{CLKIN}} = 2.4576 \text{MHz}, \\ \text{GAIN} = 1 \text{ TO } 128 \end{array} \qquad \begin{array}{ll} \text{f}_{\text{CLKIN}} = 1 \text{MHz}, \\ \text{GAIN} = 1 \text{ TO } 128 \end{array}$

**SUPPLY CURRENT vs. TEMPERATURE** (MAX1415) 0.6 0.5  $\overline{B}$ SUPPLY CURRENT (mA) 0.4 0.3 0.2 -40 -15 TEMPERATURE (°C) A: BUFFERED MODE  $f_{CLKIN} = 2.4576MHz,$  $f_{CLKIN} = 2.4576MHz$ , GAIN = 8 TO 128 GAIN = 1 TO 4 GAIN = 1 TO 128

D: UNBUFFERED MODE f<sub>CLKIN</sub> = 2.4576MHz, GAIN = 1 TO 128 E: UNBUFFERED MODE f<sub>CLKIN</sub> = 1MHz, GAIN = 1 TO 128

# **Typical Operating Characteristics (continued)**

(MAX1415:  $V_{DD} = 5V$ ,  $V_{REF+} = 2.5V$ ,  $V_{REF+} = GND$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (MAX1416:  $V_{DD} = 3V$ ,  $V_{REF+} = 1.225V$ ,  $V_{REF-} = GND$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# **Typical Operating Characteristics (continued)**

(MAX1415:  $V_{DD}$  = 5V,  $V_{REF+}$  = 2.5V,  $V_{REF+}$  = GND,  $T_A$  = +25°C, unless otherwise noted.) (MAX1416:  $V_{DD}$  = 3V,  $V_{REF+}$  = 1.225V,  $V_{REF-}$  = GND,  $T_A$  = +25°C, unless otherwise noted.)

# 16-Bit, Low-Power, 2-Channel, Sigma-Delta ADCs

# **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                    |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SCLK            | Serial Clock Input. Apply an external serial clock to transfer data to and from the device at data rates up to 5MHz.                                                                                                                                                                                                        |

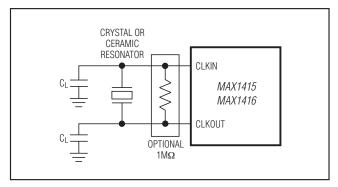

| 2   | CLKIN           | Clock Input. Connect a crystal/resonator between CLKIN and CLKOUT, or drive CLKIN externally with a CMOS-compatible clock source. Connect CLKIN to GND when using the internal oscillator.                                                                                                                                  |

| 3   | CLKOUT          | Clock Output. Connect a crystal/resonator between CLKIN and CLKOUT. When enabled, CLKOUT provides a CMOS-compatible, inverted clock output. CLKOUT can drive one CMOS load. Set CLKDIS = 0 in the clock register to enable CLKOUT. Set CLKDIS = 1 in the clock register to disable CLKOUT.                                  |

| 4   | CS              | Active-Low Chip-Select Input. $\overline{CS}$ selects the active device in systems with more than one device on the serial bus. Drive $\overline{CS}$ low to clock data in on DIN and to clock data out on DOUT. When $\overline{CS}$ is high, DOUT is high impedance. Connect $\overline{CS}$ to GND for 3-wire operation. |

| 5   | RESET           | Active-Low Reset Input. Drive RESET low to reset the MAX1415/MAX1416 to power-on reset status.                                                                                                                                                                                                                              |

| 6   | AIN2+           | Channel 2 Positive Analog Input                                                                                                                                                                                                                                                                                             |

| 7   | AIN1+           | Channel 1 Positive Analog Input                                                                                                                                                                                                                                                                                             |

| 8   | AIN1-           | Channel 1 Negative Analog Input                                                                                                                                                                                                                                                                                             |

| 9   | REF+            | Positive Reference Input                                                                                                                                                                                                                                                                                                    |

| 10  | REF-            | Negative Reference Input                                                                                                                                                                                                                                                                                                    |

| 11  | AIN2-           | Channel 2 Negative Analog Input                                                                                                                                                                                                                                                                                             |

| 12  | DRDY            | Active-Low Data Ready Output. $\overline{DRDY}$ goes low when a new conversion result is available in the data register. When a read operation of a full output word completes, $\overline{DRDY}$ returns high.                                                                                                             |

| 13  | DOUT            | Serial Data Output. DOUT outputs serial data from the data register. DOUT changes on the falling edge of SCLK and is valid on the rising edge of SCLK. When $\overline{\text{CS}}$ is high, DOUT is high impedance.                                                                                                         |

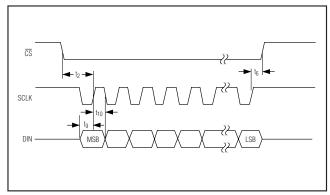

| 14  | DIN             | Serial Data Input. Data on DIN is clocked in on the rising edge of SCLK when $\overline{\text{CS}}$ is low.                                                                                                                                                                                                                 |

| 15  | V <sub>DD</sub> | Power Input. Connect V <sub>DD</sub> to a 2.7V to 3.6V power supply for the MAX1415, and connect V <sub>DD</sub> to a 4.75V to 5.25V power supply for the MAX1416.                                                                                                                                                          |

| 16  | GND             | Ground                                                                                                                                                                                                                                                                                                                      |

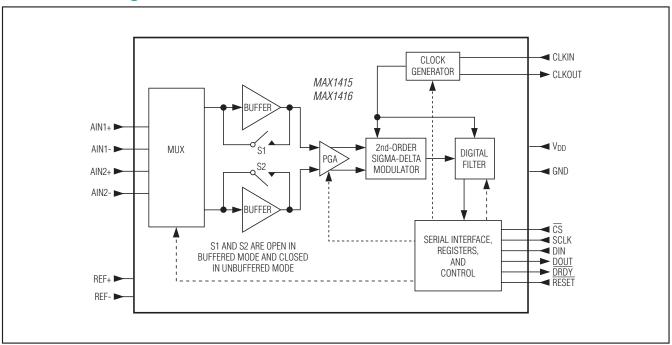

### **Functional Diagram**

# **Detailed Description**

The MAX1415/MAX1416 low-power, 2-channel serial output ADCs use a sigma-delta modulator with a digital filter to achieve 16-bit resolution with no missing codes. Each device includes a PGA, an on-chip input buffer, an internal oscillator, and a bidirectional communications port. The MAX1415 operates with a 2.7V to 3.6V single supply, and the MAX1416 operates with a 4.75V to 5.25V single supply.

Fully differential inputs, an internal input buffer, and an on-chip PGA (gain = 1 to 128) allow low-level signals to be directly measured, minimizing the requirements for external signal conditioning. Self-calibration corrects for gain and offset errors. A programmable digital filter allows for the selection of the output data rate and first notch frequency from 20Hz to 500Hz.

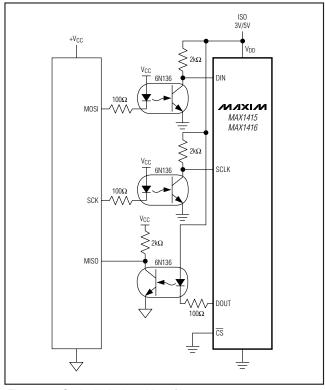

The bidirectional serial SPI-/QSPI-/MICROWIRE-compatible interface consists of four digital control lines (SCLK,  $\overline{\text{CS}}$ , DOUT, and DIN) and provides an easy interface to microcontrollers ( $\mu$ Cs). Connect  $\overline{\text{CS}}$  to GND to configure the MAX1415/MAX1416 for 3-wire operation.

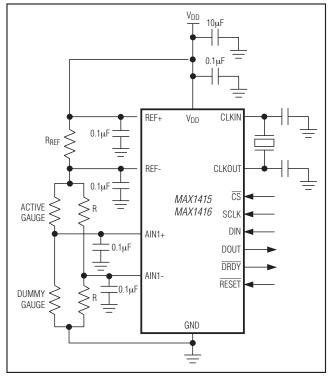

#### **Analog Inputs**

The MAX1415/MAX1416 accept four analog inputs (AIN1+, AIN1-, AIN2+, and AIN2-) in buffered or unbuffered mode. Use Table 8 to select the positive and negative input pair for a fully differential channel. The input buffer isolates the inputs from the capacitive load presented by the PGA/modulator, allowing for high source-impedance analog transducers. The value of the BUF bit in the setup register (see the *Setup Register* section) determines whether the input buffer is enabled or disabled.

Internal protection diodes, which clamp the analog input to VDD and/or GND, allow the input to swing from (GND - 0.3V) to (VDD + 0.3V), without damaging the device. If the analog input exceeds 300mV beyond the supplies, limit the input current to 10mA.

#### Input Buffers

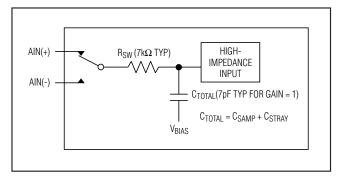

When the analog input buffer is disabled, the analog input drives a typical 7pF (gain = 1) capacitor, C<sub>TOTAL</sub>, in series with the  $7k\Omega$  typical on-resistance of the track and hold (T/H) switch (Figure 1). C<sub>TOTAL</sub> is comprised of the sampling capacitor, C<sub>SAMP</sub>, and the stray capacitance, C<sub>STRAY</sub>. During the conversion, C<sub>SAMP</sub> charges to (AIN+ - AIN-). The gain determines the value of C<sub>SAMP</sub> (see Table 5).

# 16-Bit, Low-Power, 2-Channel, Sigma-Delta ADCs

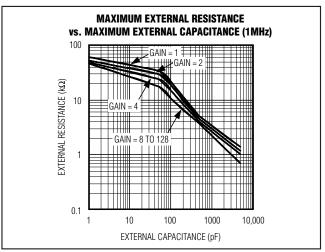

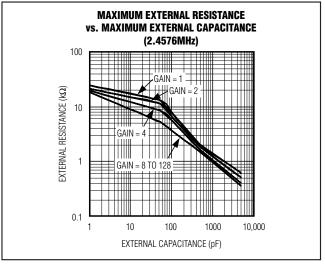

To minimize gain errors in unbuffered mode, select a source impedance less than the maximum values shown in Figures 2 and 3. These are the maximum external resistance/capacitance combinations allowed before gain errors greater than 1 LSB are introduced in unbuffered mode.

Enable the internal input buffer for a high source impedance. This isolates the inputs from the sampling capacitor and reduces the sampling-related gain error. When using the internal buffer, limit the absolute input voltage range to ( $V_{GND}$  + 50mV) to ( $V_{DD}$  - 1.5V). Properly set up the gain and common-mode voltage range to minimize linearity errors.

#### Input Voltage Range

In unbuffered mode, the absolute analog input voltage range is from (GND - 30mV) to (VDD + 30mV) (see the *Electrical Characteristics* section). In buffered mode, the analog input voltage range is reduced to (GND + 50mV) to (VDD - 1.5V). In both buffered and unbuffered modes, the differential analog input range (VAIN+ - VAIN-) decreases at higher gains (see the *Programmable Gain Amplifier* and *Unipolar and Bipolar Modes* sections).

#### Reference

The MAX1415/MAX1416 provide differential inputs, REF+ and REF-, for an external reference voltage. Connect the external reference directly across REF+ and REF- to obtain the differential reference voltage, VREF. The common-mode voltage range for VREF+ and VREF- is between GND and VDD. For specified operation, the nominal voltage, VREF is 1.225V for the MAX1415 and 2.5V for the MAX1416.

The MAX1415/MAX1416 sample REF+ and REF- at fCLKIN/64 (CLKDIV = 0) or fCLKIN/128 (CLKDIV = 1) with an internal 10pF (typ for gain = 1) sampling capacitor in series with a  $7k\Omega$  (typ) switch on-resistance.

#### **Programmable Gain Amplifier**

A PGA provides selectable levels of gain: 1, 2, 4, 8, 16, 32, 64, and 128. Bits G0, G1, and G2 in the setup register control the gain (see Table 9). As the gain increases, the value of the input sampling capacitor, CSAMP, also increases (see Table 5). The dynamic load presented to the analog inputs increases with clock frequency and gain in unbuffered mode (see the *Input Buffers* section and Figure 1).

Figure 1. Unbuffered Analog Input Structure

Figure 2. Maximum External Resistance vs. Maximum External Capacitance for Unbuffered Mode (1MHz)

Figure 3. Maximum External Resistance vs. Maximum External Capacitance for Unbuffered Mode (2.4576MHz)

**Table 5. Input Sampling Capacitor**

| GAIN  | INPUT SAMPLING CAPACITOR (CSAMP) (pF) |

|-------|---------------------------------------|

| 1     | 3.75                                  |

| 2     | 7.5                                   |

| 4     | 15                                    |

| 8–128 | 30                                    |

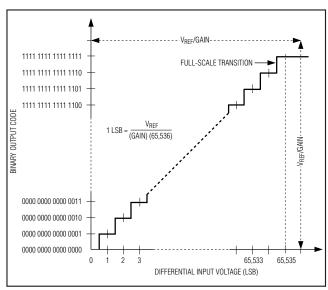

Increasing the gain increases the resolution of the ADC (LSB size decreases), but reduces the differential input voltage range. Calculate 1 LSB in unipolar mode using the following equation:

1 LSB=

$$\frac{V_{REF}}{GAIN (65.536)}$$

where: VRFF = VRFF+ - VRFF-

For a gain of 1 and VREF = 2.5V, the full-scale voltage in unipolar mode is 2.5V and 1 LSB  $\approx$  38.1µV. For a gain of 4, the full-scale voltage in unipolar mode is 0.625V (VREF/GAIN) and 1 LSB  $\approx$  9.5µV. The differential input voltage range in this example reduces from 2.5V to 0.625V, and the resolution increases since the LSB size decreases from 38.1µV to 9.5µV.

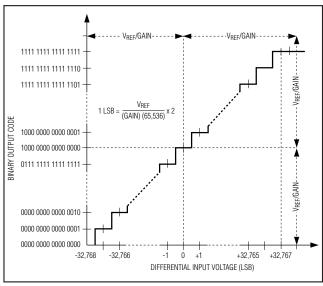

Calculate 1 LSB in bipolar mode using the following equation:

1 LSB =

$$\frac{V_{REF}}{GAIN (65,536)} \times 2$$

where:  $V_{REF} = V_{REF+} - V_{REF-}$

#### **Unipolar and Bipolar Modes**

The B/U bit in the setup register (Table 9) configures the MAX1415/MAX1416 for unipolar or bipolar transfer functions. Figures 4 and 5 illustrate the unipolar and bipolar transfer functions, respectively.

In unipolar mode, the digital output code is straight binary. When AIN+ = AIN-, the outputs are at zero scale, which is the lower endpoint of the transfer function. The full-scale endpoint is given by AIN+ - AIN- =  $V_{REF}$  / GAIN, where  $V_{REF}$  =  $V_{REF+}$  -  $V_{REF-}$ .

In bipolar mode, the digital output code is in offset binary. Positive full scale is given by AIN+ - AIN- =  $+V_{REF}$  / GAIN and negative full scale is given by AIN+ - AIN- =  $-V_{REF}$  / GAIN. When AIN+ = AIN-, the outputs are at zero scale, which is the midpoint of the bipolar transfer function.

Figure 4. MAX1415/MAX1416 Unipolar Transfer Function

Figure 5. MAX1415/MAX1416 Bipolar Transfer Function

When the MAX1415/MAX1416 are in buffered mode, the absolute and common-mode analog input voltage ranges reduce to between (GND + 50mV) and (VDD - 1.5V). The differential input voltage range is not affected in buffered mode.

#### Modulator

The MAX1415/MAX1416 perform analog-to-digital conversions using a single-bit, 2nd-order, switched-capacitor, sigma-delta modulator. The sigma-delta modulator converts the input signal into a digital pulse train whose average duty cycle represents the digitized signal information. A single comparator within the modulator quantizes the input signal at a much higher sample rate than the bandwidth of the input.

The MAX1415/MAX1416 modulator provides 2nd-order frequency shaping of the quantization noise resulting from the single-bit quantizer. The modulator is fully differential for maximum signal-to-noise ratio and minimum susceptibility to power-supply and common-mode noise. A single-bit data stream is then presented to the digital filter for processing to remove the frequency-shaped quantization noise.

The modulator sampling frequency is fCLKIN / 128, regardless of gain, where fCLKIN (CLKDIV = 0) is the frequency of the signal at CLKIN.

#### **Digital Filtering**

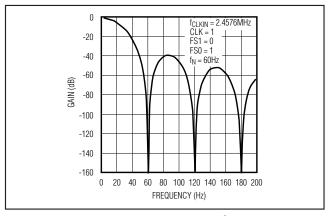

The MAX1415/MAX1416 contain an on-chip, digital low-pass filter that processes the 1-bit data stream from the modulator using a SINC<sup>3</sup> (sinx/x)<sup>3</sup> response. The SINC<sup>3</sup> filter has a settling time of three output data periods.

#### **Filter Characteristics**