## Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

#### **General Description**

The MAX14670–MAX14673 provide protection to valuable consumer circuits against positive voltage faults up to  $+28V_{DC}$ . An internal clamp also protects the devices from surges up to +100V. The device is able to disconnect the system from its output terminal when wrong input conditions are detected.

The MAX14670–MAX14673 overvoltage protection devices feature low 65m $\Omega$  (typ), WLP package on-resistance (R<sub>ON</sub>) internal FETs, effectively minimizing the voltage drop across the device. When the input voltage exceeds the overvoltage threshold, the internal FET is turned off to prevent damage to the protected components.

The overvoltage protection threshold can be adjusted with optional external resistors to any voltage between 5V and 22V. The devices automatically choose the accurate internal trip thresholds when the overvoltage lockout input (OVLO) is set lower than the external OVLO select voltage. The internal OVLO are preset to typical 6.8V (MAX14670), 15.5V (MAX14671), 5.825V (MAX14672), or 22V (MAX14673).

The MAX14670–MAX14673 feature reverse bias blocking capability. Unlike other overvoltage protectors, when the MAX14670–MAX14673 are disabled, the voltage applied to OUT does not feed back into IN. These devices also feature an OTG enable pin that allows OUT voltage to supply IN. The MAX14670–MAX14673 also have thermal shutdown protection against over load conditions.

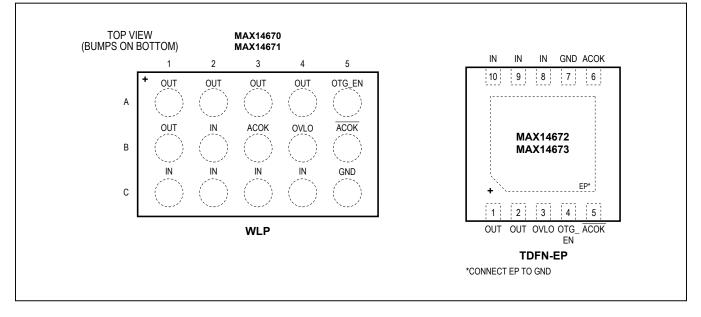

The MAX14670–MAX14673 are specified over the extended -40°C to +85°C temperature range. The MAX14670/ MAX14671 are available in a 15-bump WLP package and the MAX14672/MAX14673 are available in a 10-pin TDFN package.

Ordering Information/Selector Guide and Typical Operating Circuit appear at end of data sheet.

#### **Benefits and Features**

- Protect High-Power Portable Devices

- Wide Operating Input Voltage Protection from +3V to +28V

- +100V Surge Capability

- 4.5A Continuous Current Capability (WLP Package)

- Integrated 65mΩ (typ) n-Channel MOSFET Switch (WLP Package)

- Flexible Overvoltage Protection Design

- Wide +5V to +22V Adjustable OVLO Threshold Range

- · ACOK and ACOK Indicate Input is in Range

- OTG Enable Allows OUT to Supply IN

- Preset Accurate Internal OVLO Thresholds: 6.8V ±3% (MAX14670) 15.5V ±3% (MAX14671) 5.825V ±3% (MAX14672) 22V ±3% (MAX14673)

- Additional Protection Features Increase System Reliability

- OUT-IN Reverse Bias Blocking Capability

- Soft-Start to Minimize Inrush Current

- Internal 15ms Startup Debounce

- Thermal Shutdown Protection

- Space Saving

- 15-Bump, 1.6mm x 2.1mm, WLP Package

- 10-Pin, 3mm x 3mm, TDFN Package

#### **Applications**

- Tablets

- Smart Phones

- E-Readers

- PC Notebooks

- Charging USB Hosts

## Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

#### **Absolute Maximum Ratings**

| (All voltages referenced to GND.) |              |

|-----------------------------------|--------------|

| IN (Note 1)                       | 0.3V to +29V |

| OUT                               | 0.3V to +26V |

| IN - OUT                          | 26V to +29V  |

| OTG_EN, ACOK, ACOK                | 0.3V to +6V  |

| OVLO                              | 0.3V to +26V |

| Continuous Current into IN, OUT   |              |

| WLP (Note 2)                      | ±4.5A        |

| TDFN                              |              |

|                                   |              |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

|-------------------------------------------------------|-----------------|

| WLP (derate 16.4mW/°C above +70°C)                    | 1312mW          |

| TDFN (derate 24.4mW/°C above +70°C)                   | 1951mW          |

| Operating Temperature Range                           | 40°C to +85°C   |

| Storage Temperature Range                             | -65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C          |

| Soldering Temperature (reflow)                        | +260°C          |

Note 1: Survives burst pulses up to 100V with  $2\Omega$  series resistance and hot plug events. Above the input clamp voltage, the IN must be a surge in nature with a limited energy.

Note 2: Limited by the PCB thermal design.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Package Thermal Characteristics (Note 3)

| WLP                                            |      |

|------------------------------------------------|------|

| Junction-to-Ambient Thermal Resistance (0JA)52 | °C/W |

TDFN

Note 3: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

#### **Electrical Characteristics**

$(V_{IN} = +3V \text{ to } +28V, V_{OUT} = +3V \text{ to } +24V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{IN} = +5V, T_A = +25^{\circ}\text{C}.)$  (Note 4)

| PARAMETER                 | SYMBOL            | CONDITIONS                                                                                                   | MIN | TYP   | MAX | UNITS |

|---------------------------|-------------------|--------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| Input Startup Voltage     | V <sub>INBT</sub> |                                                                                                              |     | 2.17  | 3   | V     |

| Input Sustaining Voltage  | V <sub>INBU</sub> | I <sub>OUT</sub> = 0A                                                                                        |     | 1.5   | 2.3 | V     |

| Input Clamp Voltage       | VIN_CLAMP         | I <sub>IN</sub> = 10mA, T <sub>A</sub> = +25°C                                                               |     | 33.7  |     | V     |

| Input Supply Current      | I <sub>IN</sub>   | $V_{OVLO}$ = 0V, $V_{IN}$ = 5V, ACOK is unconnected, $I_{OUT}$ = 0mA                                         |     | 100   | 190 | μA    |

| Output Startup Voltage    | VOUTBT            |                                                                                                              |     | 2.15  | 3   | V     |

| Output Sustaining Voltage | VOUTBU            | I <sub>IN</sub> = 0A                                                                                         |     | 1.5   | 2.3 | V     |

| Output Supply Current     | IOUT              | $V_{OVLO} = 0V$ , $V_{OUT} = 5V$ , $I_{IN} = 0mA$ ,<br>$V_{OTG_{EN}} = 1.8V$                                 |     | 83    | 170 | μA    |

| Output Shutdown Current   |                   | $V_{OVLO} = 3V$ , $V_{OUT} = 5V$ , $V_{IN} = 0V$ ,<br>$V_{OTG_{EN}} = 0V$                                    |     | 6     | 12  | μA    |

| IN Leakage Voltage        |                   | V <sub>OUT</sub> = 21V, IN unconnected,<br>V <sub>OTG_EN</sub> = 0V                                          |     | 0.001 | 0.1 | V     |

| IN Discharge Current      |                   | V <sub>IN</sub> = V <sub>OUT</sub> = 5V, IN discharge current after<br>an OTG_EN transition from high to low |     | 100   | 150 | mA    |

## Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

#### **Electrical Characteristics (continued)**

$(V_{IN} = +3V \text{ to } +28V, V_{OUT} = +3V \text{ to } +24V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{IN} = +5V, T_A = +25^{\circ}C.)$  (Note 4)

| PARAMETER                                | SYMBOL                | CO                                                                                                                | NDITIONS                                                         | MIN  | TYP   | MAX     | UNITS |

|------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------|-------|---------|-------|

| OVP (IN TO OUT)                          |                       |                                                                                                                   |                                                                  |      |       |         |       |

| On Desistance (IN to OUT)                | D                     | V <sub>IN</sub> = 5V,                                                                                             | WLP, T <sub>A</sub> = +25°C                                      |      | 65    | 87      |       |

| On-Resistance (IN to OUT)                | R <sub>ON</sub>       | I <sub>OUT</sub> = 100mA                                                                                          | TDFN, T <sub>A</sub> = +25°C                                     |      | 85    | 110     | - mΩ  |

|                                          |                       | MAX14670                                                                                                          | V <sub>IN</sub> rising                                           | 6.6  | 6.8   | 6.8 7.0 |       |

|                                          |                       | MAX 14070                                                                                                         | V <sub>IN</sub> falling                                          | 6.5  |       |         |       |

| Internal Quanturity of Trial and         |                       | MAX14671                                                                                                          | V <sub>IN</sub> rising                                           | 15.0 | 15.5  | 16.0    |       |

| Internal Overvoltage Trip Level          | VIN_OVLO              | MAX 1407 1                                                                                                        | V <sub>IN</sub> falling                                          | 14.5 |       |         | V     |

|                                          |                       | MAX14672                                                                                                          | V <sub>IN</sub> rising                                           | 5.65 | 5.825 | 6.0     |       |

|                                          |                       | WAX 14072                                                                                                         | V <sub>IN</sub> falling                                          | 5.55 |       |         |       |

| OVLO Set Threshold                       | V <sub>OVLO_TH</sub>  |                                                                                                                   |                                                                  | 1.18 | 1.221 | 1.26    | V     |

| Adjustable OVLO Threshold Range          | V <sub>OVLO_EXT</sub> |                                                                                                                   |                                                                  | 5    |       | 22      | V     |

| External OVLO Select Threshold           | VOVLO_SEL             |                                                                                                                   |                                                                  | 0.2  | 0.25  | 0.3     | V     |

| DIGITAL SIGNALS (ACOK, ACO               | K, OTG_EN)            |                                                                                                                   |                                                                  |      |       |         |       |

| ACOK Output High Voltage                 | V <sub>ACOK</sub>     | $I_{SOURCE} \le 100 \mu A, V_{IN} > 3V$                                                                           |                                                                  | 1.6  | 1.8   | 2.0     | V     |

| ACOK Leakage Current                     |                       | Pull down to ground, V <sub>OUT</sub> = 5V,<br>OTG_EN = high, ACOK deasserted                                     |                                                                  |      |       | 1       | μA    |

| ACOK Output Low Voltage                  | V <sub>OL</sub>       | V <sub>IO</sub> = 3.3V, I <sub>SINK</sub> = 1mA                                                                   |                                                                  |      |       | 0.4     | V     |

| ACOK Leakage Current                     |                       | V <sub>IO</sub> = 3.3V, ACOK deasserted                                                                           |                                                                  |      |       | 1       | μA    |

| OTG_EN Input Logic-High                  | VIH                   |                                                                                                                   |                                                                  | 1.6  |       |         | V     |

| OTG_EN Input Logic-Low                   | VIL                   |                                                                                                                   |                                                                  |      |       | 0.4     | V     |

| OTG_EN Input Leakage Current             | I <sub>IN</sub>       | $0V \le V_{IN} \le V_{IL}$ and $V_{IH} \le V_{IN} \le V_{CC}$ ,<br>$V_{CC} = 5.5V$                                |                                                                  | -1   |       | +1      | μA    |

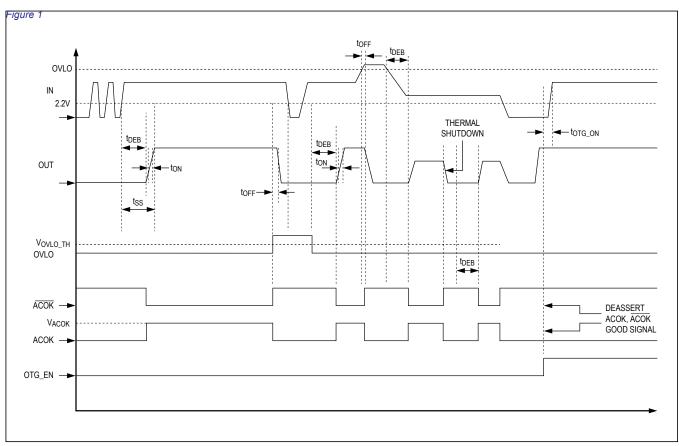

| TIMING CHARACTERISTICS (Fig              | gure 1)               | L                                                                                                                 |                                                                  |      |       |         |       |

| IN Debounce Time                         | t <sub>DEB</sub>      |                                                                                                                   | pump on (V <sub>OUT</sub> = 10%<br>00Ω, C <sub>LOAD</sub> = 10μF |      | 20    |         | ms    |

| IN/OUT Soft-Start Time                   | t <sub>SS</sub>       | $V_{IN} = 5V$ to $V_{OUT} = 90\%$ of $V_{IN}$ ,<br>$R_{LOAD} = 100\Omega$ , $C_{LOAD} = 10\mu F$                  |                                                                  |      | 25    |         | ms    |

| IN OVP Turn-On Time During<br>Soft-Start | ton                   | $V_{IN} = 5V$ , $R_{LOAD} = 100\Omega$ , $C_{LOAD} = 10\mu$ F,<br>$V_{OUT} = 20\%$ of $V_{IN}$ to 80% of $V_{IN}$ |                                                                  |      | 1.5   |         | ms    |

| IN OVP Turn-Off Response Time            | tOFF                  | From $V_{IN} > V_{OVLO}$ to $V_{OUT} = 80\%$ of $V_{IN}$ ,<br>R <sub>LOAD</sub> = 100Ω                            |                                                                  |      | 1     |         | μs    |

| OTG Turn-On Time                         | <sup>t</sup> otg_on   | Time from OTG_EN high to $V_{IN}$ = 80% of $V_{OUT}$ , $V_{OUT}$ = 5V, $C_{IN}$ = 10µF                            |                                                                  |      | 1.4   |         | ms    |

| In-Discharge Pulse Duration              |                       | $V_{IN} = V_{OUT} = 5V$ , current pulse duration<br>after an OTG_EN transition from high to low                   |                                                                  |      | 1.1   |         | ms    |

### Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

#### **Electrical Characteristics (continued)**

$(V_{IN} = +3V \text{ to } +28V, V_{OUT} = +3V \text{ to } +24V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{IN} = +5V, T_A = +25^{\circ}\text{C}.)$  (Note 4)

| PARAMETER                            | SYMBOL            | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------------------------|-------------------|------------|-----|-----|-----|-------|

| THERMAL PROTECTION                   |                   | ^          |     |     |     |       |

| Thermal Shutdown                     | T <sub>SHDN</sub> |            |     | 150 |     | °C    |

| Thermal Hysteresis                   | T <sub>HYST</sub> |            |     | 20  |     | °C    |

| ESD PROTECTION                       |                   |            |     |     |     |       |

| Human Body Model                     |                   | IN pin     |     | ±15 |     | kV    |

| IEC 61000-4-2 Contact Dis-<br>charge |                   | IN pin     |     | ±8  |     | kV    |

| IEC 61000-4-2 Air-Gap Discharge      |                   | IN pin     |     | ±8  |     | kV    |

**Note 4:** All devices are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design and not production tested.

Figure 1. Timing Diagram

## Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

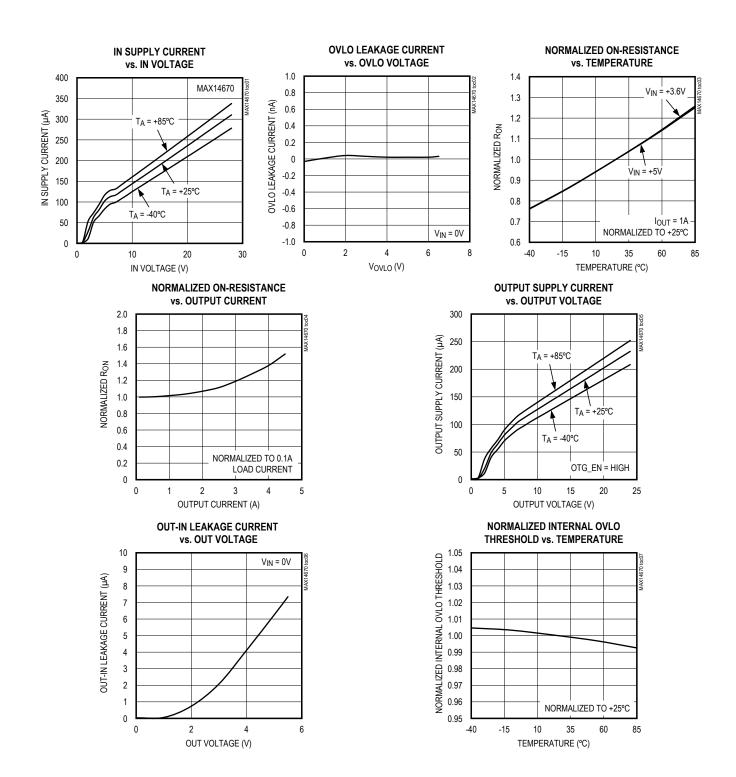

#### **Typical Operating Characteristics**

(V<sub>IN</sub> = +5V, OVLO = GND,  $C_{IN}$  = 0.1µF,  $C_{OUT}$  = 1µF,  $T_A$  = +25°C, unless otherwise noted.)

### Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

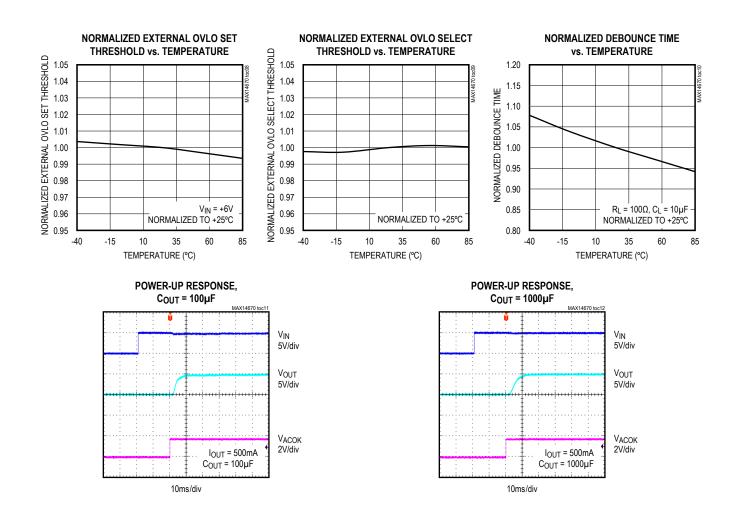

#### **Typical Operating Characteristicsc (continued)**

(V<sub>IN</sub> = +5V, OVLO = GND,  $C_{IN}$  = 0.1µF,  $C_{OUT}$  = 1µF,  $T_A$  = +25°C, unless otherwise noted.)

### Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

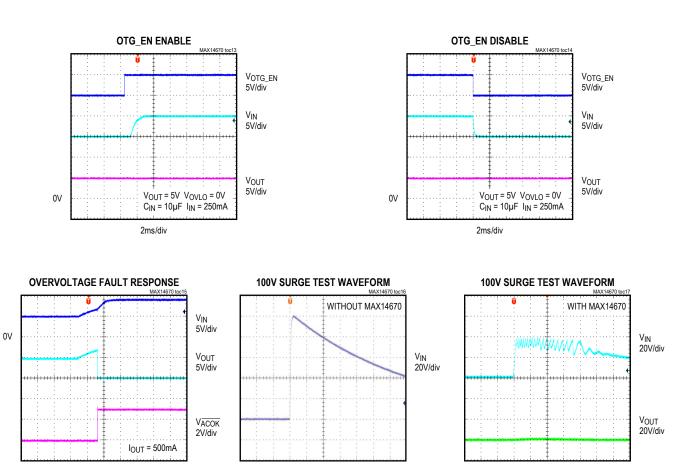

# **Typical Operating Characteristicsc (continued)**

(V<sub>IN</sub> = +5V, OVLO = GND,  $C_{IN}$  = 0.1µF,  $C_{OUT}$  = 1µF,  $T_A$  = +25°C, unless otherwise noted.)

10µs/div

10ms/div

10µs/div

## Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

## **Pin Configurations**

### **Pin Descriptions**

| BUMP                  | PIN                   |        |                                                                                                                                                                                                                                                                          |

|-----------------------|-----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX14670/<br>MAX14671 | MAX14672/<br>MAX14673 | NAME   | FUNCTION                                                                                                                                                                                                                                                                 |

| A1–A4, B1             | 1, 2                  | OUT    | Overvoltage Protection Output. Bypass OUT with a 1µF ceramic capacitor. Exter-<br>nally connect all OUT together.                                                                                                                                                        |

| A5                    | 4                     | OTG_EN | Enable Input for OTG Supply Operation                                                                                                                                                                                                                                    |

| B2, C1–C4             | 8–10                  | IN     | Overvoltage Protection Input. If desired, bypass IN with a $0.1\mu$ F ceramic capacitor as close to the device as possible. Externally connect all IN together.                                                                                                          |

| В3                    | 6                     | АСОК   | 1.8V Logic Output. ACOK is driven high after input voltage is stable between minimum $V_{IN}$ and $V_{OVLO}$ when OTG_EN = 0. Connect a pulldown resistor from ACOK to ground.                                                                                           |

| B4                    | 3                     | OVLO   | Overvoltage Lockout Input. Connect OVLO to GND to use internal OVLO threshold.<br>Connect OVLO to a resistor-divider for a different voltage threshold.                                                                                                                  |

| B5                    | 5                     | ACOK   | Open-Drain Flag Output. $\overline{\text{ACOK}}$ is driven low after input voltage is stable between minimum V <sub>IN</sub> and V <sub>OVLO</sub> when OTG_EN = 0. Connect a pullup resistor from $\overline{\text{ACOK}}$ to the logic I/O voltage of the host system. |

| C5                    | 7                     | GND    | Ground                                                                                                                                                                                                                                                                   |

|                       |                       | EP     | Exposed Pad (TDFN Only). Connect EP to ground.                                                                                                                                                                                                                           |

## Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

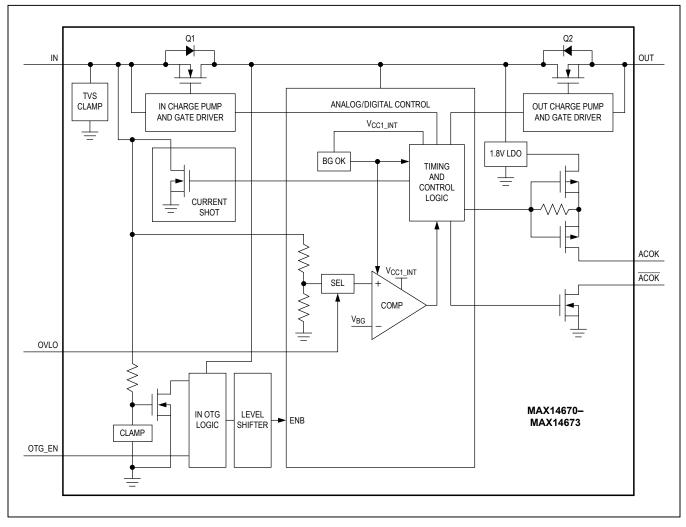

### **Functional Diagram**

#### **Detailed Description**

The MAX14670–MAX14673 overvoltage protection (OVP) devices feature low on-resistance ( $R_{ON}$ ) internal FETs (Q1+Q2) and protect low-voltage systems against voltage faults up to +28V<sub>DC</sub>. An internal clamp also protects the devices from surges up to +100V. If the input voltage exceeds the overvoltage threshold, the output is disconnected from the input to prevent damage to the protected components. The 15ms debounce time prevents false turn-on of the internal FETs during startup.

#### Soft-Start

To minimize inrush current, the devices feature a soft-start capability to slowly turn on Q1 and Q2. Soft-start begins when ACOK/ACOK is asserted and ends after 15ms (typ).

#### **Overvoltage Lockout (OVLO)**

Connect OVLO to ground to use the internal OVLO comparator with the internally set OVLO value. When IN goes above the overvoltage lockout threshold (V<sub>IN\_OVLO</sub>), OUT is disconnected from IN and  $\overline{ACOK}$ / ACOK is deasserted. When IN drops below V<sub>IN\_OVLO</sub>, the debounce time starts counting. After the debounce time, OUT follows IN again and  $\overline{ACOK}$ /ACOK is asserted.

#### **External OVLO Adjustment Functionality**

When an external resistor-divider is connected to OVLO and  $V_{OVLO}$  exceeds the OVLO select voltage ( $V_{OVLO}_{SEL}$ ), the internal OVLO comparator reads IN by the external resistor-divider.

R1 =  $1M\Omega$  is a good starting value for minimum current consumption. Since V<sub>IN\_OVLO</sub>, V<sub>OVLO\_TH</sub>, and R1 are known, R2 can be calculated from the following formula:

$$V_{IN}OVLO = V_{OVLO}TH \times \left[1 + \frac{R1}{R2}\right]$$

This external resistor-divider is completely independent from the internal resistor-divider.

#### **Reverse Bias Blocking**

The ICs feature reverse bias blocking. When IN voltage is below input startup voltage and OTG\_EN is low, the switch between IN and OUT is open and the two backto-back diodes of the two series switches block reverse bias. Therefore, when the voltage is applied at the output, current does not travel back to the input. When OVLO is high, the parts block against reverse bias as well.

### Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

#### **OTG Enable**

The devices feature reverse turn-on capability. OTG\_EN can be used to turn on the switch for OUT to feed back to IN when the voltage applied at OUT is above the minimum startup voltage. When OTG\_EN is high, ACOK and ACOK are deasserted. During the OTG operation, if IN goes above OVLO, the OVP switch turns off. It is recommended that the power is supplied to OUT prior to OTG operation and also the power is removed from OUT prior to disable OTG operation.

#### **Thermal Shutdown Protection**

The devices feature thermal shutdown protection to protect the devices from overheating. The internal FETs turn off when the junction temperature exceeds +150°C (typ), and the device returns to normal operation after the temperature drops by approximately 20°C (typ).

#### **Applications Information**

#### **IN Bypass Capacitor**

If desired, bypass IN to GND with a  $0.1\mu$ F ceramic capacitor as close to the device as possible. If the power source has significant inductance due to long lead length, the device prevents overshoots due to the LC tank circuit and provides protection by clamping the overshooting.

#### **Output Capacitor**

The slow turn-on time provides a soft-start function that allows the devices to charge an output capacitor up to  $1000\mu$ F without turning off due to an overcurrent condition. Bypass OUT to GND with a minimum of  $1\mu$ F ceramic capacitor.

#### **Extended ESD Protection**

ESD protection structures are incorporated on all pins to protect against electrostatic discharges up to  $\pm 2kV$ (Human Body Model) encountered during handling and assembly. IN is further protected against ESD up to  $\pm 15kV$ (HBM),  $\pm 15kV$  (Air-Gap Discharge method described in IEC 61000-4-2) and  $\pm 8kV$  (Contact Discharge Method described in IEC 61000-4-2) without damage.

The ESD structures withstand high ESD both in normal operation and when the device is powered down. After an ESD event, the MAX14670–MAX14673 continue to function without latchup.

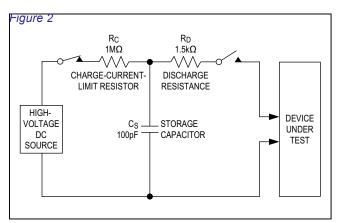

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

#### Human Body Model ESD Protection

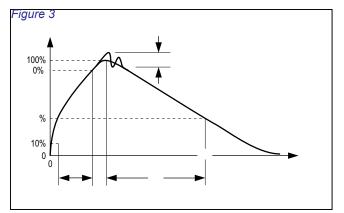

<u>Figure 2</u> shows the HBM and <u>Figure 3</u> shows the current waveform it generates when discharged into a lowimpedance state. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a  $1.5k\Omega$  resistor.

Figure 2. Human Body ESD Test Model

Figure 3. Human Body Current Waveform

## Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

#### IEC 61000-4-2

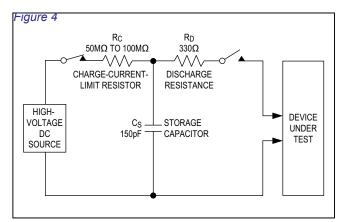

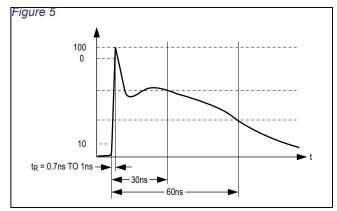

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. However, it does not specifically refer to integrated circuits. The major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2 because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD withstand voltage measured to IEC 61000-4-2 is generally lower than that measured using the Human Body Model. Figure 4 shows the IEC 61000-4-2 model, and Figure 5 shows the current waveform for the IEC 61000-4-2 ESD Contact Discharge test.

Figure 4. IEC 61000-4-2 ESD Test Model

Figure 5. IEC 61000-4-2 ESD Generator Current Waveform

## Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

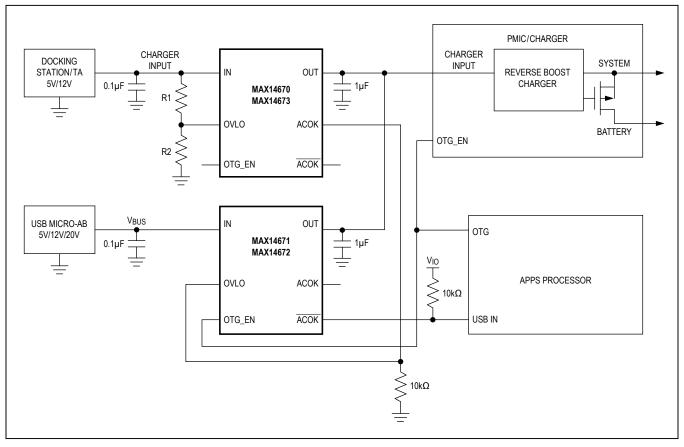

### **Typical Operating Circuit**

#### **Ordering Information/Selector Guide**

| PART            | OVLO<br>(V) | TOP MARK  | PIN-PACK-<br>AGE |

|-----------------|-------------|-----------|------------------|

| MAX14670EWL+T   | 6.8         | +14670EWL | 15 WLP           |

| MAX14671EWL+T   | 15.5        | +14671EWL | 15 WLP           |

| MAX14672ETB+T   | 5.825       | AZF       | 10 TDFN-EP*      |

| MAX14673ETB+T** | 22          | AZG       | 10 TDFN-EP*      |

**Note:** All devices are specified over  $-40^{\circ}$ C to  $+85^{\circ}$ C operating temperature range.

+Denotes a lead(Pb)-free package/RoHS-compliant package.

T = Tape and reel. \*EP = Exposed pad.

\*\*Future product—contact factory for availability.

#### **Chip Information**

PROCESS: BICMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO.                   |

|-----------------|-----------------|----------------|---------------------------------------|

| 10 TDFN         | T1033+1         | <u>21-0137</u> | <u>90-0003</u>                        |

| 15 WLP          | W151C2+1        | <u>21-0686</u> | Refer to Application <u>Note 1891</u> |

## Bidirectional Current-Blocking, High-Input Overvoltage Protector with Adjustable OVLO

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                        | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------------------------------------------------------|------------------|

| 0                  | 6/13             | Initial release                                                                    | —                |

| 1                  | 7/13             | Update Functional Diagram                                                          | 9                |

| 2                  | 8/13             | Included soldering lead time; corrected nFET and pFET arrows in Functional Diagram | 2, 9             |

| 3                  | 10/13            | Updated Functional Diagram                                                         | 9                |

| 4                  | 1/14             | Updated data sheet to reflect 100V surge protection capability                     | 1, 2, 7, 10      |

| 5                  | 9/16             | Updated Pin Descriptions table                                                     | 8                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Supervisory Circuits category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

CAT1161LI-25-G CAT853STBI-T3 CAT1026LI-30-G CAT1320LI-25-G TC54VN2402EMB713 MCP1316T-44NE/OT MCP1316MT-45GE/OT MCP1316MT-23LI/OT MAX8997EWW+ MAX6725AKASYD3-LF-T DS1232L NCV302HSN45T1G PT7M6130NLTA3EX PT7M7811STBEX-2017 S-1000N28-I4T1U CAT1161LI-28-G MCP1321T-29AE/OT MCP1319MT-47QE/OT S-1000N23-I4T1U S-1000N19-I4T1U CAT824UTDI-GT3 TC54VC2502ECB713 PT7M6133NLTA3EX PT7M6127NLTA3EX AP0809ES3-r HG811RM4/TR MD7030C MD7033C MD7019 MD7020 MD7021 MD7023 MD7024 MD7027 MD7030 MD7033 MD7035 MD7036 MD7039 MD7040 MD7044 MD7050 MD7015 MD7022 MD7028 MD7031 MD7042 MD7043 MD7047 MD7060