## Six-Channel Digital Isolator

#### **General Description**

The MAX14850 is a six-channel digital isolator utilizing Maxim's proprietary process technology, whose monolithic design provides a compact and low-cost transfer of digital signals between circuits with different power domains. The technology enables low power consumption and stable high-temperature performance.

The four unidirectional channels are each capable of DC to 50Mbps, with two of the four channels passing data across the isolation barrier in each direction. The two bidirectional channels are open-drain; each capable of data rates from DC to 2Mbps.

Independent 3.0V to 5.5V supplies on each side of the isolator also make it suitable for use as a level translator. The MAX14850 can be used for isolating SPI buses, I<sup>2</sup>C buses, RS-232, RS-485/RS-422 buses, and general-purpose isolation. When used as a bus isolator, extra channels are available for power monitoring and reset signals.

The MAX14850 is available in a narrow body,16-pin SOIC (10mm x 4mm) package (for which an evaluation kit is available) and 16-pin QSOP (3.9mm x 4.94mm) package. The packages are specified over the -40°C to +125°C temperature range.

For improved performance, refer to the MAX14851. The MAX14851 has the same functionality and pin configurations, and can be used as a footprint and functional replacement for the MAX14850.

## **Applications**

- Industrial Control Systems

- I2C, SPI, SMBus, PMBus™ Interfaces

- Isolated RS-232, RS-485/RS-422

- Telecommunication Systems

- Battery Management

- Medical Systems

#### **Benefits and Features**

- Protection from High-Voltage Environments

- 600V<sub>RMS</sub> Isolation for 60 Seconds

- Short-Circuit Protection on Unidirectional Outputs

- 200V<sub>RMS</sub> Working Isolation Voltage for 50 Years

- Complete Digital Isolation Solution

- · Four Unidirectional Signal Paths: 2-In/2-Out

- · Two Bidirectional Open-Drain Signal Paths

- 50Mbps (max) Unidirectional Data Rate

- · 2Mbps (max) Bidirectional Data Rate

- Compatible with Many Interface Standards

- I<sup>2</sup>C

- SPI

- RS-232, RS-422/RS-485

- · SMBus, PMBus Interfaces

Ordering Information appears at end of data sheet.

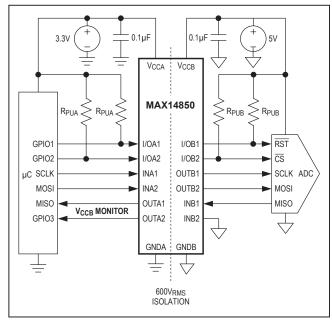

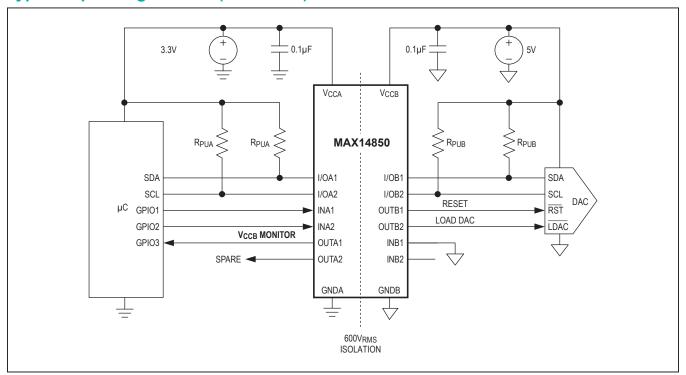

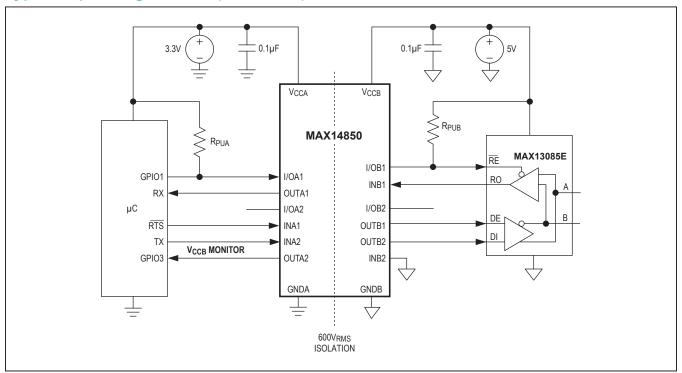

## **Typical Operating Circuits**

PMBus is a trademark of SMIF, Inc.

## **Absolute Maximum Ratings**

| V <sub>CCA</sub> to GNDA                               | 0.3V to +6V                   |

|--------------------------------------------------------|-------------------------------|

| V <sub>CCB</sub> to GNDB                               | 0.3V to +6V                   |

| OUTA1, OUTA2 to GNDA                                   | $-0.3V$ to $(V_{CCA} + 0.3V)$ |

| OUTB1, OUTB2 to GNDB                                   | $-0.3V$ to $(V_{CCB} + 0.3V)$ |

| INA1, INA2, I/OA1, I/OA2 to GNDA                       | 0.3V to +6V                   |

| INB1, INB2, I/OB1, I/OB2 to GNDB                       | 0.3V to +6V                   |

| Short-Circuit Duration (OUTA_ to GNDA                  | A or                          |

| V <sub>CCA</sub> , OUTB_ to GNDB or V <sub>CCB</sub> ) | Continuous                    |

| Continuous Current (I/OA , I/OB ) Pin                  | ±50mA                         |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| SOIC (derate 13.3mW/°C above +70°C)                   | 1067mW         |

| QSOP (derate 9.6mW/°C above +70°C)                    | 771.5mW        |

| Operating Temperature Range                           | 40°C to +125°C |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### **16 SOIC**

| Package Code                           | S16+3   |  |  |  |

|----------------------------------------|---------|--|--|--|

| Outline Number                         | 21-0041 |  |  |  |

| Land Pattern Number                    | 90-0097 |  |  |  |

| THERMAL RESISTANCE, MULTILAYER BOARD   |         |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 75°C/W  |  |  |  |

|                                        |         |  |  |  |

#### **16 QSOP**

| Package Code                           | E16+1     |  |  |  |  |

|----------------------------------------|-----------|--|--|--|--|

| Outline Number                         | 21-0055   |  |  |  |  |

| Land Pattern Number                    | 90-0167   |  |  |  |  |

| THERMAL RESISTANCE, MULTILAYER BOARD   |           |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 103.7°C/W |  |  |  |  |

| Junction to Case $(\theta_{JC})$       | 37°C/W    |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## **Electrical Characteristics**

$(V_{CCA} - V_{GNDA} = 3.0V \ to \ 5.5V, \ V_{CCB} - V_{GNDB} = 3.0V \ to \ 5.5V, \ T_A = -40^{\circ}C \ to \ +125^{\circ}C, \ unless otherwise noted. \ Typical values are at V_{CCA} - V_{GNDA} = 3.3V, \ V_{CCB} - V_{GNDB} = 3.3V, \ and \ T_A = +25^{\circ}C.) \ (Note \ 1)$

| PARAMETER                          | SYMBOL                            | CONDITIONS                                                                           |                                                                                               |                         | MIN     | TYP  | MAX                  | UNIT      |

|------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------|---------|------|----------------------|-----------|

| DC CHARACTERISTICS                 |                                   |                                                                                      |                                                                                               |                         |         |      |                      |           |

| Cupply Voltage                     | V <sub>CCA</sub>                  | Relative to GNDA                                                                     |                                                                                               |                         | 3.0     |      | 5.5                  | V         |

| Supply voltage                     | V <sub>CCB</sub> Relative to GNDB |                                                                                      | 3.0                                                                                           |                         | 5.5     | V    |                      |           |

|                                    |                                   | Unidirectional inputs at DC or 2Mbps;                                                | V <sub>CCA</sub> = 5'<br>V <sub>CCB</sub> = 5'                                                |                         |         | 7.2  | 11                   |           |

|                                    |                                   | bidirectional inputs at DC or switching at 2Mbps, no load                            | V <sub>CCA</sub> = 3.<br>V <sub>CCB</sub> = 3.                                                | .3V,<br>.3V             |         | 6.2  | 9.5                  |           |

| Supply Current                     | I <sub>CCA</sub> ,                |                                                                                      | V <sub>CCA</sub> = 5V,                                                                        | T <sub>A</sub> = +25°C  |         | 15   | 22                   | mA        |

|                                    | ICCB                              | All inputs switching at max data rate. No load.                                      | V <sub>CCB</sub> = 5V                                                                         | T <sub>A</sub> = +125°C |         | 17   | 24                   |           |

|                                    |                                   | (Note 2)                                                                             | V <sub>CCA</sub> = 3.3V,                                                                      | T <sub>A</sub> = +25°C  |         | 10   | 16                   |           |

|                                    | 3.3V +12t                         | T <sub>A</sub> = +125°C                                                              |                                                                                               | 11                      | 18      |      |                      |           |

| Undervoltage Lockout<br>Threshold  | V <sub>UVLO</sub>                 | V <sub>CCA</sub> - V <sub>GNDA</sub> , V <sub>CCB</sub> - V <sub>GNDB</sub> (Note 3) |                                                                                               |                         |         | 2    |                      | V         |

| Undervoltage Lockout<br>Hysteresis | V <sub>UVLOHYS</sub>              | V <sub>CCA</sub> - V <sub>GNDA</sub> , V <sub>CCB</sub> - V <sub>GNDB</sub> (Note 3) |                                                                                               |                         | 0.1     |      | V                    |           |

| ISOLATION CHARACTER                | RISTICS                           |                                                                                      |                                                                                               |                         |         |      |                      |           |

| Isolation Voltage                  | V <sub>ISO</sub>                  | t = 60s (Note 4)                                                                     |                                                                                               |                         | 600     |      |                      | $V_{RMS}$ |

| Working Isolation<br>Voltage       | V <sub>IOWM</sub>                 | V <sub>GNDB</sub> - V <sub>GNDA</sub> continuou expectancy ( <u>Figure 4</u> )       | V <sub>GNDB</sub> - V <sub>GNDA</sub> continuous (Note 2), 50-year life expectancy (Figure 4) |                         |         |      | 200                  | $V_{RMS}$ |

| ESD Protection                     |                                   | All pins                                                                             |                                                                                               |                         |         | ±2.5 |                      | kV        |

| LOGIC INPUTS AND OUT               | PUTS                              |                                                                                      |                                                                                               |                         |         |      |                      |           |

| Input Threshold Voltage            | V <sub>IT</sub>                   | I/OA1, I/OA2, relative to G                                                          | NDA                                                                                           |                         | 0.5     |      | 0.7                  | ٧         |

|                                    |                                   | INA1, INA2, relative to GN                                                           | DA                                                                                            |                         | 0.7 x V | CCA  |                      |           |

| Input Logic-High Voltage           | V                                 | INB1, INB2, relative to GNDB                                                         |                                                                                               |                         | 0.7 x V | ССВ  |                      | V         |

| input Logic-riight voltage         | V <sub>IH</sub>                   | I/OA1, I/OA2, relative to GNDA                                                       |                                                                                               | 0.7                     |         |      | ) V                  |           |

|                                    | I/OB1, I/OB2, relative to GNDB    |                                                                                      | 0.7 x V                                                                                       | ССВ                     |         |      |                      |           |

|                                    |                                   | INA1, INA2, relative to GN                                                           | DA                                                                                            |                         |         |      | 8.0                  |           |

| Input Logic Low Voltage            | V <sub>i</sub> ,                  | INB1, INB2, relative to GN                                                           | DB                                                                                            |                         |         |      | 0.8                  | V         |

| Input Logic-Low Voltage            | V <sub>IL</sub>                   | I/OA1, I/OA2, relative to G                                                          | NDA                                                                                           |                         |         |      | 0.5                  |           |

|                                    |                                   | I/OB1, I/OB2, relative to GNDB                                                       |                                                                                               |                         |         | 0.3  | 3 x V <sub>CCB</sub> |           |

## **Electrical Characteristics (continued)**

$(V_{CCA} - V_{GNDA} = 3.0V \ to \ 5.5V, \ V_{CCB} - V_{GNDB} = 3.0V \ to \ 5.5V, \ T_A = -40^{\circ}C \ to \ +125^{\circ}C, \ unless otherwise noted. \ Typical values are at V_{CCA} - V_{GNDA} = 3.3V, \ V_{CCB} - V_{GNDB} = 3.3V, \ and \ T_A = +25^{\circ}C.) \ (Note \ 1)$

| PARAMETER                                      | SYMBOL                  | CONDITI                                                                | ONS                                                                 | MIN              | TYP   | MAX  | UNIT     |

|------------------------------------------------|-------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|-------|------|----------|

| Output Logic-High                              | Vau                     | OUTA1, OUTA2, relative to GNDA, source current = 4mA                   |                                                                     | V <sub>CCA</sub> | - 0.4 |      | V        |

| Voltage VoH                                    |                         | OUTB1, OUTB2, relative to source current = 4mA                         | GNDB,                                                               | V <sub>CCB</sub> | - 0.4 |      | V        |

|                                                |                         | OUTA1, OUTA2, relative to sink current = 4mA                           | GNDA,                                                               |                  |       | 0.8  |          |

|                                                |                         | OUTB1, OUTB2, relative to sink current = 4mA                           | GNDB,                                                               |                  |       | 0.8  |          |

| Output Logic-Low<br>Voltage                    | V <sub>OL</sub>         | I/OA1, I/OA2, relative to GN sink current = 10mA                       | NDA,                                                                | 0.6              |       | 0.9  | V        |

|                                                |                         | I/OA1, I/OA2, relative to GN sink current = 0.5mA                      | NDA,                                                                | 0.6              |       | 0.85 |          |

|                                                |                         | I/OB1, I/OB2, relative to GN sink current = 30mA                       | NDB,                                                                |                  |       | 0.4  |          |

| Input/Output Logic-Low<br>Threshold Difference | ΔV <sub>TOL</sub>       | I/OA1, I/OA2 (Note 5)                                                  |                                                                     | 50               |       |      | mV       |

| Input Capacitance                              | C <sub>IN</sub>         | INA1, INA2, INB1, INB2, f                                              |                                                                     | 2                |       | pF   |          |

| DYNAMIC SWITCHING C                            | HARACTERIS <sup>®</sup> | TICS                                                                   |                                                                     |                  |       |      |          |

| Common-Mode<br>Transient Immunity              | CMTI                    | V <sub>IN</sub> = V <sub>CC</sub> or V <sub>GND</sub> (Not             | es 2, 6)                                                            |                  | 1.5   |      | kV/µs    |

| Maximum Data Rate                              | 20                      | INA1 to OUTB1, INA2 to OUTB2, INB1 to OUTA1, INB2 to OUTA2             |                                                                     | 50               |       |      | N.Alessa |

| (Note 2)                                       | DR <sub>MAX</sub>       | I/OA1 to I/OB1, I/OA2 to I/OB2, I/OB1 to I/OA1, I/OB2 to I/OA2         |                                                                     | 2                |       |      | Mbps     |

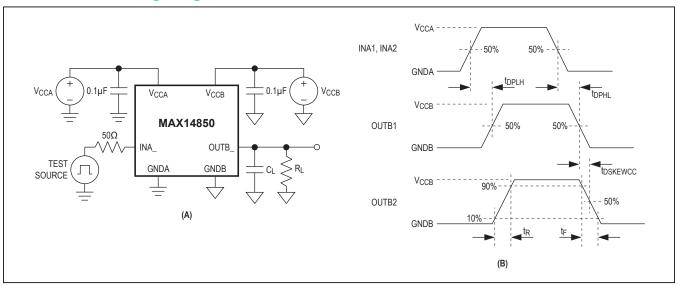

| Minimum Pulse Width                            | PW <sub>MIN</sub>       |                                                                        | INA1 to OUTB1, INA2 to OUTB2, INB1 to OUTA1, INB2 to OUTA2 (Note 2) |                  |       |      | ns       |

|                                                |                         | INA1 to OUTB1, INA2 to OUTB2, INB1 to OUTA1,                           | V <sub>CCA</sub> = V <sub>CCB</sub> = 3.3V                          |                  | 20    | 30   |          |

|                                                |                         | INB2 to OUTA2,<br>$R_L = 1M\Omega$ , $C_L = 15pF$ ,<br><u>Figure 1</u> | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V                            |                  | 18    | 26   | ns       |

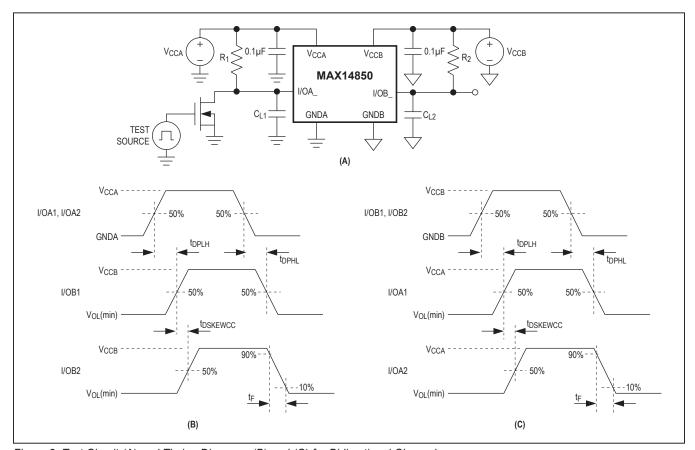

| Propagation Delay                              | t <sub>DPLH</sub>       | I/OA1 to I/OB1, I/OA2 to I/OB2, $R_1 = 1.6k\Omega$ ,                   | $V_{CCA} = V_{CCB} =$ 3.3V                                          |                  | 30    | 100  |          |

| (Note 2)                                       | <sup>t</sup> DPHL       | $R_2 = 180\Omega$ , $C_{L1} = CL2 = 15pF$ , Figure 2                   | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V                            |                  | 30    | 100  |          |

|                                                |                         | I/OB1 to I/OA1, I/OB2 to I/OA2, R <sub>1</sub> = 1kΩ,                  | V <sub>CCA</sub> = V <sub>CCB</sub> = 3.3V                          |                  | 60    | 100  |          |

|                                                |                         | $R_2 = 120\Omega$ , $C_{L1} = C_{L2} = 15pF$ , Figure 2                | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V                            |                  | 60    | 100  |          |

## **Electrical Characteristics (continued)**

$(V_{CCA} - V_{GNDA} = 3.0V \ to \ 5.5V, \ V_{CCB} - V_{GNDB} = 3.0V \ to \ 5.5V, \ T_A = -40^{\circ}C \ to \ +125^{\circ}C, \ unless otherwise noted. \ Typical values are at V_{CCA} - V_{GNDA} = 3.3V, \ V_{CCB} - V_{GNDB} = 3.3V, \ and \ T_A = +25^{\circ}C.) \ (Note \ 1)$

| PARAMETER                                           | SYMBOL               | CONDITIONS                                                        |                                            | MIN | TYP | MAX | UNIT |

|-----------------------------------------------------|----------------------|-------------------------------------------------------------------|--------------------------------------------|-----|-----|-----|------|

|                                                     |                      | INA1 TO OUTB1, INA2<br>TO OUTB2, INB1 TO<br>OUTA1, INB2 TO OUTA2, | V <sub>CCA</sub> = V <sub>CCB</sub> = 3.3V |     |     | 7   |      |

|                                                     |                      | $R_L = 1M\Omega$ ,<br>$C_L = 15pF$ , Figure 1                     | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V   |     |     | 7   |      |

| Pulse-Width Distortion  tDPLH - tDPHL  (Notes 2, 7) | PWD                  | I/OA1 to I/OB1, I/OA2 to I/OB2, $R_1 = 1.6k\Omega$ ,              | V <sub>CCA</sub> = V <sub>CCB</sub> = 3.3V |     |     | 12  | ns   |

|                                                     |                      | $R_2 = 180\Omega$ , $C_{L1} = CL2 = 15pF$ , Figure 2              | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V   |     |     | 12  |      |

|                                                     |                      | I/OB1 to I/OA1, I/OB2 to I/OA2, $R_1 = 1k\Omega$ ,                | V <sub>CCA</sub> = V <sub>CCB</sub> = 3.3V |     |     | 60  |      |

|                                                     |                      | $R_2 = 120\Omega, C_{L1} = C_{L2} = 15pF, Figure 2$               | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V   |     |     | 50  |      |

|                                                     |                      | OUTB1 to OUTB2 output                                             | $V_{CCA} = V_{CCB} =$ 3.3V                 |     |     | 3   |      |

|                                                     |                      | skew, Figure 1                                                    | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V   |     |     | 3   | ns   |

|                                                     | t <sub>DSKEWCC</sub> | OUTA1 to OUTA2 output                                             | $V_{CCA} = V_{CCB} =$ 3.3V                 |     |     | 3   |      |

| Channel-to-Channel                                  |                      | skew, Figure 1                                                    | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V   |     |     | 3   |      |

| Skew (Notes 2, 7)                                   |                      | I/OB1 to I/OB2 output                                             | V <sub>CCA</sub> = V <sub>CCB</sub> = 3.3V |     |     | 6   |      |

|                                                     |                      | skew, Figure 2                                                    | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V   |     |     | 5   |      |

|                                                     |                      | I/OA1 to I/OA2 output<br>skew, Figure 2                           | $V_{CCA} = V_{CCB} =$ 3.3V                 |     |     | 20  |      |

|                                                     |                      | Skew, I igure 2                                                   | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V   |     |     | 20  |      |

| Part-to-Part Skew (Notes 2, 7)                      | t <sub>DSKEWPP</sub> | Δt <sub>DPLH</sub> , Δt <sub>DPHL</sub>                           | Δt <sub>DPLH</sub> , Δt <sub>DPHL</sub>    |     |     | 8   | ns   |

| Rise Time (Note 2)                                  | t <sub>R</sub>       | OUTA1, OUTA2, OUTB1, O                                            |                                            |     | 5   | ns  |      |

|                                                     |                      | OUTA1, OUTA2, OUTB1, O                                            | OUTB2, 90% to 10%,                         |     |     | 5   |      |

|                                                     |                      | I/OA1, I/OA2, 90% to<br>10%, R <sub>1</sub> = 1.6kΩ,              | V <sub>CCA</sub> = V <sub>CCB</sub> = 3.3V |     | 30  | 60  |      |

| Fall Time (Note 2)                                  | t <sub>F</sub>       | $R_2 = 180\Omega$ , $C_{L1} = C_{L2} = 15pF$ , Figure 2           | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V   |     | 40  | 80  | ns   |

|                                                     |                      | I/OB1, I/OB2, 90% to<br>10%, R <sub>1</sub> = 1kΩ,                | V <sub>CCA</sub> = V <sub>CCB</sub> = 3.3V |     | 3   | 6   |      |

|                                                     |                      | $R_2 = 120\Omega$ , $C_{L1} = C_{L2} = 15pF$ , Figure 2           | V <sub>CCA</sub> = V <sub>CCB</sub> = 5V   |     | 3   | 5   |      |

## **Insulation and Safety Characteristics**

| PARAMETER                                        | SYMBOL            | CONDITIONS                                                   |                               | VALUE     | UNIT   |  |  |

|--------------------------------------------------|-------------------|--------------------------------------------------------------|-------------------------------|-----------|--------|--|--|

| IEC INSULATION AND SAFETY RE                     | LATED FOR         | SPECIFICATIONS FOR SOI                                       | C-16                          |           |        |  |  |

| External Tracking (Crooping)                     | CPG               | IEC 60664-1                                                  | SOIC-16                       | 4.2       | mm     |  |  |

| External Tracking (Creepage)                     | CPG               | 1EC 00004-1                                                  | QSOP-16                       | 3.81      | mm     |  |  |

| External Air Gap (Clearance)                     | CLR               | IEC 60664-1                                                  | SOIC-16                       | 4.2       | mm     |  |  |

| External Air Gap (Clearance)                     | CLR               | QSOP-16                                                      |                               | 3.81      | mm     |  |  |

| Minimum Internal Gap                             |                   | Insulation Thickness                                         |                               | 0.0026    | mm     |  |  |

| Tracking Resistance (Comparative Tracking Index) | СТІ               | IEC 112 / VDE 030 Part 1                                     | IEC 112 / VDE 030 Part 1      |           | V      |  |  |

| Insulation Resistance Across<br>Barrier          | R <sub>ISO</sub>  |                                                              | 1                             | GΩ        |        |  |  |

| Capacitance Across Isolation<br>Barrier          | C <sub>IO</sub>   | f = 1MHz                                                     | 12                            | pF        |        |  |  |

| VDE IEC INSULATION CHARACTERISTICS               |                   |                                                              |                               |           |        |  |  |

| Surge Isolation Voltage                          | V <sub>IOSM</sub> | IEC 60747-17, section 5.3.1.6 and 5.4.6 for basic insulation |                               | 1         | kVpeak |  |  |

| Repetitive Peak Isolation Voltage                | V <sub>IORM</sub> | IEC 60747-17, section 5.3.1                                  | IEC 60747-17, section 5.3.1.3 |           | Vpeak  |  |  |

| Rated Transient Isolation Voltage                | V <sub>IOTM</sub> | IEC 60747-17, section 5.3.1                                  | 1.4                           | 850       | Vpeak  |  |  |

| Safety Limiting Temperature                      | T <sub>S</sub>    | IEC 60747-17, section 7.2.1                                  |                               | 150       | °C     |  |  |

| Safety Limiting Side A Power Dissipation         | P <sub>SA</sub>   | IEC 60747-17, section 7.2.1                                  |                               | 0.75      | W      |  |  |

| Safety Limiting Side B Power Dissipation         | P <sub>SB</sub>   | IEC 60747-17, section 7.2.1                                  |                               | 0.75      | W      |  |  |

| Apparent Charge Method                           | q <sub>pd</sub>   | IEC 60747-17, section 7.4, method a & b                      |                               | 5         | pC     |  |  |

| Overvoltage Category                             |                   | IEC 60664-1, single or three phase 50V DC or AC              |                               | I,II      | _      |  |  |

| Overvoltage Category                             |                   | IEC 60664-1, single or three phase 100V DC or AC             |                               | 1         | _      |  |  |

| Climatic Category                                |                   |                                                              |                               | 40/125/21 | _      |  |  |

| Pollution Degree                                 |                   | DIN VDE 0110, Table 1                                        |                               | 2         | _      |  |  |

- Note 1: All units are production tested at T<sub>A</sub> = +25°C. Specifications over temperature are guaranteed by design. All voltages of side A are referenced to GNDA. All voltages of side B are referenced to GNDB, unless otherwise noted.

- Note 2: Guaranteed by design. Not production tested.

- **Note 3:** The undervoltage lockout threshold and hysteresis guarantee that the outputs are in a known state during a slump in the supplies. See the *Detailed Description* section for more information.

- Note 4: The isolation is guaranteed for t = 60s, and tested at 120% of the guaranteed value for 1s.

- Note 5:  $\Delta V_{TOL} = V_{OL} V_{IL}$ . This is the minimum difference between the output logic-low voltage and the input logic threshold for the same I/O pin. This ensures that the I/O channels are not latched low when any of the I/O inputs are driven low (see the *Bidirectional Channels* section).

- Note 6: The common-mode transient immunity guarantees that the device will hold its outputs stable when the isolation voltage changes at the specified rate.

- Note 7: Pulse-width distortion is defined as the difference in propagation delay between low-to-high and high-to-low transitions on the same channel. Channel-to-channel skew is defined as the difference in propagation delay between different channels on the same device. Part-to-part skew is defined as the difference in propagation delays (for unidirectional channels) between different devices, when both devices operate with the same supply voltage, at the same temperature and have identical package and test circuits.

## **Test Circuits/Timing Diagrams**

Figure 1. Test Circuit (A) and Timing Diagram (B) for Unidirectional Channels

Figure 2. Test Circuit (A) and Timing Diagrams (B) and (C) for Bidirectional Channels

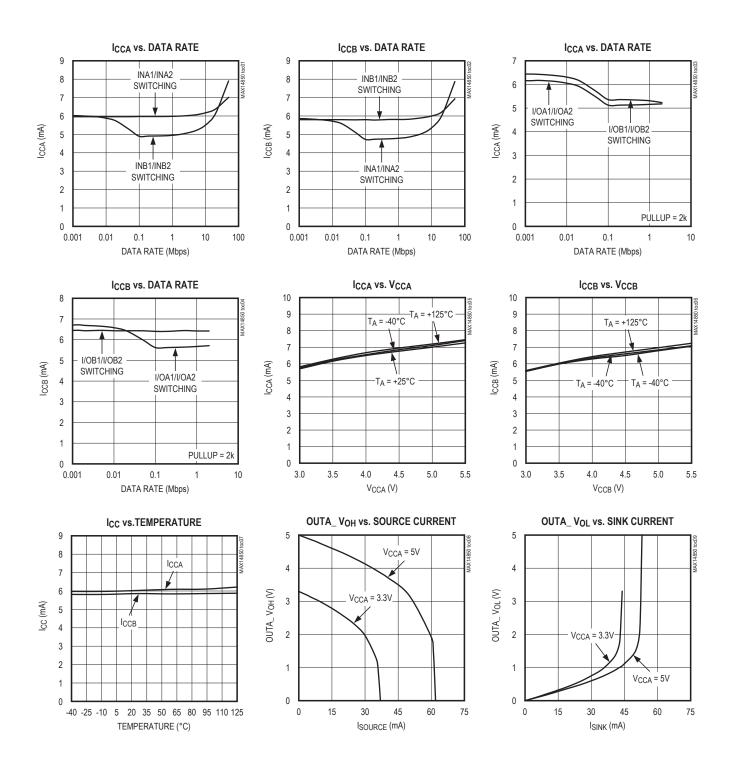

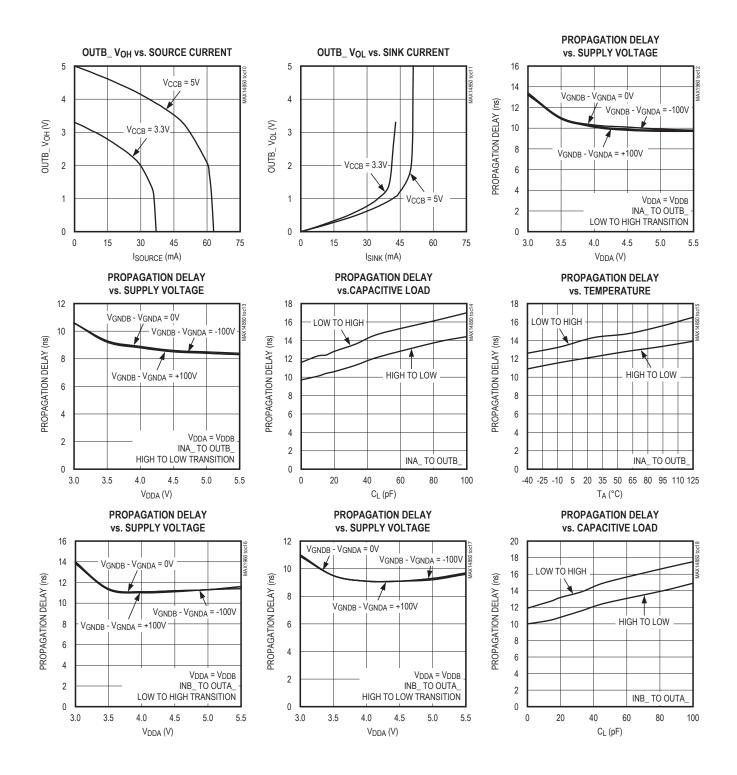

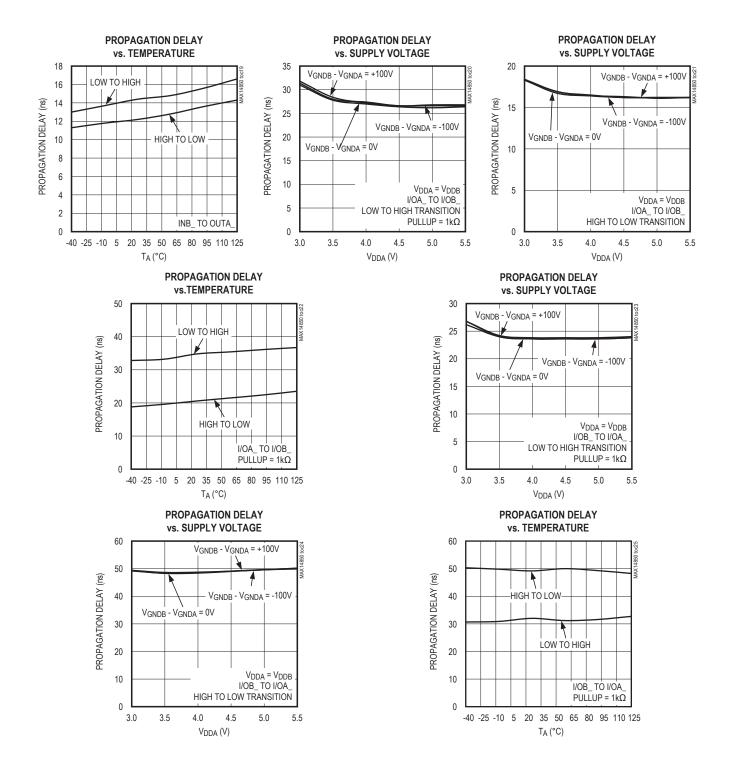

## **Typical Operating Characteristics**

$(V_{CCA} - V_{GNDA} = 3.3V, V_{CCB} - V_{GNDB} = 3.3V,$ all inputs idle,  $T_A = +25$ °C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

$(V_{CCA} - V_{GNDA} = 3.3V, V_{CCB} - V_{GNDB} = 3.3V,$ all inputs idle,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

$(V_{CCA} - V_{GNDA} = 3.3V, V_{CCB} - V_{GNDB} = 3.3V,$ all inputs idle,  $T_A = +25$ °C, unless otherwise noted.)

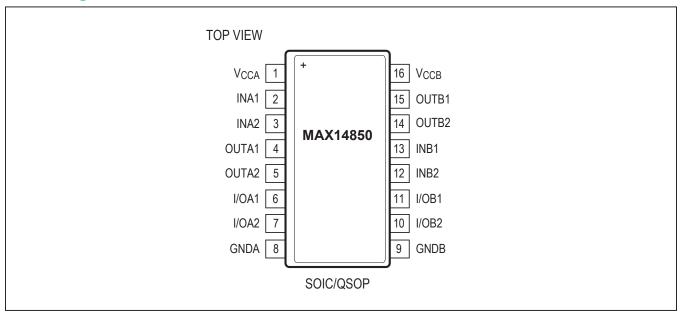

# **Pin Configuration**

## **Pin Description**

| PIN | NAME             | FUNCTION                                                                                                    | REFERENCE |

|-----|------------------|-------------------------------------------------------------------------------------------------------------|-----------|

| 1   | V <sub>CCA</sub> | Supply Voltage of Logic Side A. Bypass $V_{\text{CCA}}$ with a 0.1 $\mu\text{F}$ ceramic capacitor to GNDA. | GNDA      |

| 2   | INA1             | Logic Input 1 on Side A. INA1 is translated to OUTB1.                                                       | GNDA      |

| 3   | INA2             | Logic Input 2 on Side A. INA2 is translated to OUTB2.                                                       | GNDA      |

| 4   | OUTA1            | Logic Output 1 on Side A. OUTA1 is a push-pull output.                                                      | GNDA      |

| 5   | OUTA2            | Logic Output 2 on Side A. OUTA2 is a push-pull output.                                                      | GNDA      |

| 6   | I/OA1            | Bidirectional Input/Output 1 on Side A. I/OA1 is translated to/from I/OB1 and is a open-drain output.       | GNDA      |

| 7   | I/OA2            | Bidirectional Input/Output 2 on Side A. I/OA2 is translated to/from I/OB2 and is a open-drain output.       | GNDA      |

| 8   | GNDA             | Ground Reference for Side A                                                                                 | _         |

| 9   | GNDB             | Ground Reference for Side B                                                                                 | _         |

| 10  | I/OB2            | Bidirectional Input/Output 2 on Side B. I/OB2 is translated to/from I/OA2 and is a open-drain output.       | GNDB      |

| <b>Pin Description (continued)</b> | Pin | Descrip | otion ( | (continued | 1) |

|------------------------------------|-----|---------|---------|------------|----|

|------------------------------------|-----|---------|---------|------------|----|

| PIN | NAME             | FUNCTION                                                                                              | REFERENCE |

|-----|------------------|-------------------------------------------------------------------------------------------------------|-----------|

| 11  | I/OB1            | Bidirectional Input/Output 1 on Side B. I/OB1 is translated to/from I/OA1 and is a open-drain output. | GNDB      |

| 12  | INB2             | Logic Input 2 on Side B. INB2 is translated to OUTA2.                                                 | GNDB      |

| 13  | INB1             | Logic Input 1 on Side B. INB1 is translated to OUTA1.                                                 | GNDB      |

| 14  | OUTB2            | Logic Output 2 on Side B. OUTB2 is a push-pull output.                                                | GNDB      |

| 15  | OUTB1            | Logic Output 1 on Side B. OUTB1 is a push-pull output.                                                | GNDB      |

| 16  | V <sub>CCB</sub> | Supply Voltage of Logic Side B. Bypass V <sub>CCB</sub> with a 0.1μF ceramic capacitor to GNDB.       | GNDB      |

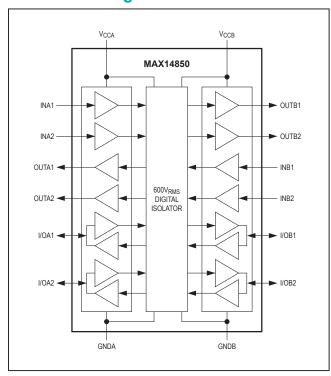

## **Functional Diagram**

#### **Detailed Description**

The MAX14850 is a six-channel digital isolator. The device is rated for  $600V_{RMS}$  isolation voltage for 60 seconds. This digital isolator offers a low-power, low-cost, high electromagnetic interference (EMI) immunity, and stable temperature performance through Maxim's proprietary process technology. The device uses a monolithic solution to isolate different ground domains and block high-voltage/high-current transients from sensitive or human interface circuitry. Four of the six channels are unidirectional, two in each direction. All four unidirectional channels support data rates of up to 50Mbps. The other two channels are bidirectional with data rates up to 2Mbps.

Isolation of I<sup>2</sup>C, SPI/MICROWIRE<sup>®</sup>, and other serial busses can be achieved with the MAX14850. The device features two supply inputs,  $V_{CCA}$  and  $V_{CCB}$ , that independently set the logic levels on either side of the device.  $V_{CCA}$  and  $V_{CCB}$  are referenced to GNDA and GNDB, respectively. The MAX14850 features a refresh mode to ensure accuracy of data when the inputs are DC.

#### **Digital Isolation**

The MAX14850 provides galvanic isolation for digital signals that are transmitted between two ground domains. Up to  $200V_{RMS}$  of continuous isolation is supported as well as transient differences of up to 850V.

MICROWIRE is a registered trademark of Texas Instruments.

#### Level Shifting

The MAX14850 tolerates a ground difference of  $600V_{RMS}$ . Therefore,  $V_{GNDA}$  can be  $850V_{DC}$  higher or lower than  $V_{GNDB}$ . In addition, the device translates logic levels when (VCCA–VGNDA) is higher or lower voltage than ( $V_{CCB}$ – $V_{GNDB}$ ), as long as each is within the valid 3.0V to 5.5V range.

#### **Unidirectional and Bidirectional Channels**

The MAX14850 operates both as a unidirectional device and bidirectional device simultaneously. Each unidirectional channel can only be used in the direction shown in the functional diagram. The bidirectional channels function without requiring a direction control input.

#### **Unidirectional Channels**

The device features four unidirectional channels that operate independently with guaranteed data rates from DC to 50Mbps. The output driver of each unidirectional channel is push-pull, eliminating the need for pullup resistors. The outputs are able to drive both TTL and CMOS logic inputs.

#### **Bidirectional Channels**

The device features two bidirectional channels that have open-drain outputs. The bidirectional channels do not require a direction control input. A logic-low on one side causes the corresponding pin on the other side to be pulled low while avoiding data latching within the device. I/OA1 and I/OA2 outputs comprise special buffers that regulate the logic-low voltage at approximately 0.7V. The input logic-low threshold (V<sub>IT</sub>) of I/OA1 and I/OA2 is at least 50mV lower than the output logic-low voltage of I/OA1 and I/OA2. This prevents an output logic-low on side A from being accepted as an input low and subsequently transmitted to side B, thus preventing a latching action. I/OB1 and I/OB2 are conventional outputs that do not regulate the logic-low output voltage.

Due to their nature, the MAX14850 A-side output buffers cannot be connected together or to a device with similar buffers or rise time accelerators. However, the MAX14850 B-side output buffers can be connected together or to any other bidirectional buffer or level translator.

The I/OA1, I/OA2, I/OB1, and I/OB2 pins have open-drain outputs, requiring pullup resistors to their respective supplies for logic-high outputs. The output low voltages are guaranteed for sink currents of up to 30mA for side B, and 10mA for side A (see the *Electrical Characteristics* table).

#### Startup and Undervoltage Lockout

The  $V_{CCA}$  and  $V_{CCB}$  supplies are both internally monitored for undervoltage conditions. Undervoltage events can occur during power-up, power-down, or during normal operation due to a slump in the supplies. When an undervoltage event is detected on either of the supplies, all outputs on both sides are automatically controlled, regardless of the status of the inputs. The bidirectional outputs become high impedance and are pulled high by the external pullup resistor on the open-drain output. The unidirectional outputs are pulled high internally to the voltage of the  $V_{CCA}$  or  $V_{CCB}$  supply during undervoltage conditions.

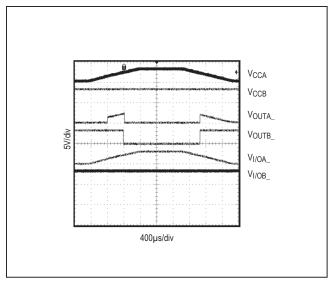

When an undervoltage condition is detected on either supply, all unidirectional outputs are pulled to the supplies (<u>Table 1</u>). The bidirectional outputs are high impedance and pulled to the supplies by the external pullup resistors. <u>Figure 3</u> shows the behavior of the outputs during power-up and power-down.

#### **Safety Regulatory Approvals**

The MAX14850 is safety certified by UL, CSA, and IEC 60747-5-2. Per UL1577, the MAX14850 is 100% tested at an equivalent  $V_{\rm ISO}$  of  $720V_{\rm RMS}$  for one second (see <u>Table 2</u>).

**Table 1. Output Behavior During Undervoltage Conditions**

| V <sub>IN</sub> | V <sub>CCA</sub> | V <sub>CCB</sub> | V <sub>OUTA</sub> _      | V <sub>OUTB</sub> _      |

|-----------------|------------------|------------------|--------------------------|--------------------------|

| 1               | Powered          | Powered          | 1                        | 1                        |

| 0               | Powered          | Powered          | 0                        | 0                        |

| X               | Undervoltage     | Powered          | Follows V <sub>CCA</sub> | 1                        |

| Х               | Powered          | Undervoltage     | 1                        | Follows V <sub>CCB</sub> |

#### **Table 2. Safety Regulatory Approvals**

| SAFETY AGENCY | STANDARD          | ISOLATION NUMBER                                     | FILE NUMBER |

|---------------|-------------------|------------------------------------------------------|-------------|

| UL            | UL1577 Recognized | 600V <sub>RMS</sub> isolation voltage for 60 seconds | E351759     |

Figure 3. Undervoltage Lockout Behavior

# Vs. WORKING ISOLATION VOLTAGE 1000 VIOWM = 200VRMS 10 0.001 0 100 200 300 400 500 600 700 800 WORKING ISOLATION VOLTAGE (VIOWM) - VRMS

Figure 4. Life Expectancy vs. Working Isolation Voltage

## **Applications Information**

# Affect of Continuous Isolation on Lifetime

High-voltage conditions cause insulation to degrade over time. Higher voltages result in faster degradation. Even the high-quality insulating material used in the MAX14850 can degrade over long periods of time with a constant high-voltage across the isolation barrier. Figure 4 shows the life expectancy of the MAX14850 vs. working isolation voltage.

#### **Power Supply Sequencing**

The MAX14850 does not require special power-supply sequencing. The logic levels are set independently on either side by  $V_{CCA}$  and  $V_{CCB}$ . Each supply can be present over the entire specified range regardless of the level or presence of the other.

#### **Power Supply Decoupling**

To reduce ripple and the chance of introducing data errors, bypass  $V_{CCA}$  and  $V_{CCB}$  with  $0.1\mu F$  ceramic capacitors to GNDA and GNDB, respectively. Place the bypass capacitors as close to the power-supply input pins as possible.

# **Typical Operating Circuits (continued)**

# **Typical Operating Circuits (continued)**

## **Ordering Information**

| PART          | TEMP RANGE      | PIN-PACKAGE |

|---------------|-----------------|-------------|

| MAX14850ASE+  | -40°C to +125°C | 16 SOIC     |

| MAX14850ASE+T | -40°C to +125°C | 16 SOIC     |

| MAX14850AEE+  | -40°C to +125°C | 16 QSOP     |

| MAX14850AEE+T | -40°C to +125°C | 16 QSOP     |

<sup>+</sup>Denotes lead(Pb)-free/RoHS-compliant package.

# **Chip Information**

PROCESS: BICMOS

T = Tape and Reel

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                   | PAGES<br>CHANGED       |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 0                  | 3/12             | Initial release                                                                                                                                                                                                               |                        |

| 1                  | 5/14             | Updated General Description, Benefits and Features, Bidirectional Channels section, Table 2, and Typical Operating Circuits                                                                                                   | 1, 13,<br>15, 16       |

| 2                  | 11/14            | Added QSOP package and related information Additional package and ordering information for QSOP                                                                                                                               | 1, 2, 6,<br>11, 13, 16 |

| 3                  | 9/19             | Updated General Description, Absolute Maximum Ratings, Electrical Characteristics, Pin Description table, Level Shifting, Bidirectional Channels, Startup and Undervoltage Lockout, Safety Regulatory Approvals, and Table 2. | 1–3, 11–13             |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Digital Isolators category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

NSI8120N1 NSI8021N1-DSPR IL3485-3E IL514E IL515E IL611-1E IL612A-3E IL710S-1E IL711-1E IL711-2E IL721VE IL814TE

ADN4652BRSZ-RL7 ADUM1441ARSZ ADUM1447ARSZ ADUM1447ARSZ-RL7 ADUM230D0BRIZ-RL ADUM230E1BRIZ-RL

ADUM230E0BRIZ-RL ISO7820DW ADUM1440ARSZ ADUM1445ARSZ ADUM1246ARSZ-RL7 ADUM4150ARIZ-RL

ADUM4150BRIZ-RL LTC4310IMS-1#PBF IL3522E IL260E IL261E IL3085E IL3422-3E IL3585-3E IL510-1E IL610-1E IL611-2E

IL613-3E IL710V-1E IL712-1E IL716-1E ISO7310FCQDRQ1 ISO7342CDWR ISO7810FDW ISO7820FDW IL611-3E ADN4655BRWZ

ADUM2211SRIZ-RL ADUM1440ARSZ-RL7 ADUM3473ARSZ ADUM6210ARSZ ADUM3474ARSZ