## Industrial Octal High-Side Switch

#### **General Description**

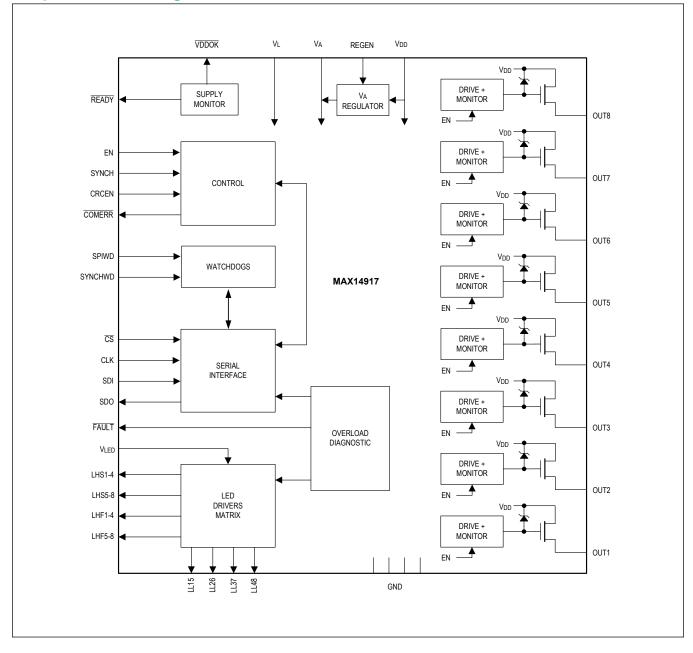

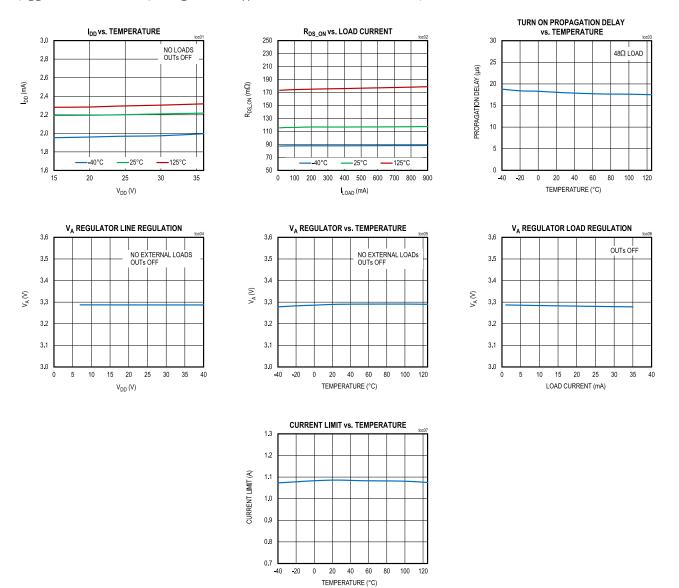

The MAX14917 has eight high-side switches specified to deliver up to 700mA (min) continuous current per channel. The high-side switches have on-resistance of  $120m\Omega$  (typ) at  $25^{\circ}C$  ambient temperature.

The device has an SPI interface that can be daisy chained, allowing communication with multiple MAX14917 devices utilizing a common SPI chip select ( $\overline{CS}$ ). There are also per-channel overload diagnostics provided through the SPI interface. Two watchdog timers provide an additional safety check of the master-to-device connectivity.

The MAX14917 features a 4 x 4 LED cross-bar matrix, which provides a visual indication of channel status and overload conditions for each channel, and an integrated line-to-ground and line-to-line surge protection provides robustness to the electrical stress as per IEC 61000-4-5 and requires only one TVS on V<sub>DD</sub>. The MAX14917 is available in a compact 48-pin 6mm x 6mm FC2QFN package.

#### **Applications**

- Industrial Digital Outputs

- PLC Systems

- Factory Automation

- Building Automation

- Industrial IoT

#### **Benefits and Features**

- Robust Solutions

- 65V Absolute Maximum Supply Range

- · CRC Error Checking on the SPI Interface

- · Watchdog Timers for Monitoring SPI and SYNCH

- Per Channel Overload Diagnostic and Protection

- Loss of V<sub>DD</sub> or GND Protection

- Thermal Shutdown Protection

- Integrated ±1kV / 42Ω IEC 61000-4-5 Surge Protection

- ±7kV / IEC 61000-4-2 Contact Discharge Method

- ±30kV / IEC 61000-4-2 Air Discharge Method

- -40°C to +125°C Operating Ambient Temperature

- Reduces Power and Heat Dissipation

- 120m $\Omega$  (typ) On-Resistance at T<sub>A</sub> = 25°C

- 2.5mA (typ) Supply Current

- Accurate Output Current Limiting

- Flexible

- · SYNCH Input for Simultaneous Update of Switches

- LED Driver Matrix for 16 LEDs, Powered from 3.0V to 36V

- Internal Clamps for Fast Inductive Load

Demagnetization

- · Daisy Chainable SPI

- Flexible Logic Voltage Interface from 2.5V to 5.5V

- Pin Compatible with the MAX14915 and MAX14916 in Daisy-Chain Configuration

- Compact 6mm x 6mm FC2QFN Package

Ordering Information appears at end of datasheet.

# Industrial Octal High-Side Switch

## Simplified Block Diagram

### **Absolute Maximum Ratings**

| V <sub>DD</sub>              | 0.3V to +65V                    |

|------------------------------|---------------------------------|

| OUT                          |                                 |

| $V_A, \overline{V_L}$        |                                 |

| SDO, READY, COMERR           | 0.3V to (V <sub>L</sub> + 0.3V) |

| REGEN                        |                                 |

| FAULT                        |                                 |

| SDI, CS, CLK, EN, SYNCH, CRC | CEN, SPIWD, SYNCHWD0.3V         |

|                              | to +6V                          |

| V <sub>LED</sub>             | 0.3V to +70V                    |

|                              |                                 |

| LH_, LL_, VDDOK                        | 0.3V to (V <sub>LED</sub> + 0.3V)   |

|----------------------------------------|-------------------------------------|

| OUT_Load Current                       | Internally Limited                  |

| Continuous Power Dissipation (Multilag | yer Board) ( $T_A = +70^{\circ}C$ , |

| derate 50mW/°C above +70°C)            | 3900mW                              |

| Operating Temperature Range            | 40°C to +125°C                      |

| Junction Temperature                   | +150°C                              |

| Storage Temperature Range              |                                     |

| Soldering Temperature (reflow)         |                                     |

Note 1: All voltages relative to GND.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 48 F2CQFN

| Package Code                          | F486A6F+1         |  |

|---------------------------------------|-------------------|--|

| Outline Number                        | <u>21-100232</u>  |  |

| Land Pattern Number                   | <u>90-100077</u>  |  |

| Thermal Resistance, Four-Layer Board: |                   |  |

| Junction to Ambient $(\theta_{JA})$   | 20.5°C/W          |  |

| Junction to Case $(\theta_{JC})$      | 0.39°C/W (bottom) |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

### **Electrical Characteristics**

$(V_{DD} = +10V \text{ to } +36V, V_{LED} = +3.0V \text{ to } 36V, V_A = +3.0V \text{ to } +5.5V, V_L = +2.5V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted}.$ Typical values are at  $V_{DD} = V_{LED} = 24V, V_A = 3.3V, T_A = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                              | SYMBOL                 | CONDITIONS                                                                | MIN | TYP  | MAX | UNITS |

|----------------------------------------|------------------------|---------------------------------------------------------------------------|-----|------|-----|-------|

| DC Characteristics / SU                | PPLY                   |                                                                           |     |      |     |       |

| V <sub>DD</sub> Supply Voltage         | V <sub>DD</sub>        |                                                                           | 10  |      | 36  | V     |

| V <sub>DD</sub> Supply Current         | I <sub>DD</sub>        | EN = high, OUT_ switches on, no load, $V_A$ and $V_L$ supplied externally |     | 2    | 3   | mA    |

|                                        |                        | EN = low                                                                  |     |      | 3   |       |

| V <sub>DD</sub> UVLO Rise<br>Threshold | V <sub>DD_UVLO_R</sub> | V <sub>DD</sub> rising                                                    |     |      | 9.6 | V     |

| V <sub>DD</sub> UVLO Fall<br>Threshold | V <sub>DD_UVLO_F</sub> | V <sub>DD</sub> falling, OUT_ disabled                                    | 7.9 |      |     | V     |

| V <sub>DD</sub> UVLO Hysteresis        | V <sub>DD_UVLO_H</sub> |                                                                           |     | 0.35 |     | V     |

| V <sub>DD</sub> Warn Fall<br>Threshold | V <sub>DD_WARN_F</sub> | V <sub>DD</sub> falling, VDDOK pin set Hi-Z                               | 12  | 13   |     | v     |

| V <sub>DD</sub> Good Rise<br>Threshold | V <sub>DD_GOOD_R</sub> | $V_{DD}$ rising, $\overline{VDDOK}$ pin set low                           |     |      | 17  | V     |

### **Electrical Characteristics (continued)**

$(V_{DD} = +10V \text{ to } +36V, V_{LED} = +3.0V \text{ to } 36V, V_A = +3.0V \text{ to } +5.5V, V_L = +2.5V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$ Typical values are at  $V_{DD} = V_{LED} = 24V, V_A = 3.3V, T_A = +25^{\circ}\text{C}.$  (Note 2)

| PARAMETER                                         | SYMBOL                 | CONDITIONS                                                           | MIN                  | TYP                      | MAX              | UNITS |

|---------------------------------------------------|------------------------|----------------------------------------------------------------------|----------------------|--------------------------|------------------|-------|

| V <sub>DD</sub> Good Fall<br>Threshold            | V <sub>DD_GOOD_F</sub> | V <sub>DD</sub> falling                                              | 15                   |                          |                  | V     |

| V <sub>DD</sub> Good Hysteresis                   | V <sub>DD_GOOD_H</sub> |                                                                      |                      | 0.4                      |                  | V     |

| V <sub>DD</sub> POR Rise<br>Threshold             | V <sub>DD_POR_R</sub>  | V <sub>DD</sub> rising                                               |                      |                          | 6.8              | V     |

| V <sub>DD</sub> POR Falling<br>Threshold          | V <sub>DD_POR_F</sub>  | V <sub>DD</sub> falling                                              | 5.6                  |                          |                  | V     |

| V <sub>A</sub> Supply Voltage                     | VA                     | When V <sub>A</sub> is supplied externally; REGEN = GND.             | 3.0                  |                          | 5.5              | V     |

| V <sub>A</sub> Supply Current                     | I <sub>VA</sub>        | EN = high, OUT_are turned on, no load,<br>no LEDs connected          |                      | 0.5                      | 0.85             | mA    |

| V <sub>A</sub> Undervoltage<br>Lockout Threshold  | V <sub>A_UV</sub>      | $V_{DD}$ = 24V, $V_A$ rising                                         | 2.45                 |                          | 2.9              | V     |

| V <sub>A</sub> Undervoltage<br>Lockout Hysteresis | VA_UVHYST              | V <sub>DD</sub> = 24V                                                |                      | 0.1                      |                  | V     |

| V <sub>L</sub> Supply Voltage                     | VL                     |                                                                      | 2.5                  |                          | 5.5              | V     |

| V <sub>L</sub> Supply Current                     | I <sub>VL</sub>        | All logic inputs high or low                                         |                      | 13                       | 34               | μA    |

| V <sub>L</sub> POR Threshold                      | V <sub>VL_POR</sub>    | V <sub>L</sub> falling                                               | 0.87                 | 1.32                     | 1.5              | V     |

| DC Characteristics / SW                           | TCH OUTPUTs            | (OUT_)                                                               |                      |                          |                  |       |

| On-Resistance                                     | R <sub>OUT HS</sub>    | I <sub>OUT</sub> = -600mA                                            |                      | 120                      | 250              | mΩ    |

| Current Limit                                     | I <sub>LIM</sub>       |                                                                      | 0.7                  | 1                        | 1.3              | А     |

| Off Leakage Current                               | I <sub>LKG</sub>       | Switch off, OUT_ = 0V                                                | -10                  |                          | +10              | μA    |

| DC Characteristics / LIN                          | EAR REGULAT            | DR                                                                   | 1                    |                          |                  |       |

| Output Voltage                                    | VA                     | REGEN open, C <sub>LOAD</sub> = 1µF, 0mA < I <sub>VA</sub><br>< 20mA | 3.0                  | 3.3                      | 3.6              | V     |

| Current Limit                                     | I <sub>CL_VA</sub>     | REGEN open                                                           | 25                   |                          |                  | mA    |

| Short Current                                     | I <sub>SHRT_VA</sub>   | REGEN open, V <sub>A</sub> = 0V                                      |                      |                          | 60               | mA    |

| REGEN Threshold                                   | VT <sub>REGEN</sub>    |                                                                      | 0.2                  |                          |                  | V     |

| REGEN Leakage<br>Current                          | ILK_REGEN              | REGEN = 0V                                                           | -50                  |                          |                  | μA    |

| DC Characteristics / LO                           | GIC I/O                |                                                                      | 1                    |                          |                  |       |

| Input Voltage High                                | VIH                    |                                                                      | 0.7 x V <sub>L</sub> |                          |                  | V     |

| Input Voltage Low                                 | VIL                    |                                                                      |                      |                          | $0.3 \times V_L$ | V     |

| Input Threshold<br>Hysteresis                     | VIHYS                  |                                                                      |                      | 0.11 x<br>V <sub>L</sub> |                  | V     |

| Input Pulldown Resistor                           | R <sub>IN_PD</sub>     | All logic input pins except SYNCH and CS                             |                      | 200                      |                  | kΩ    |

| Input Pullup Resistor                             | R <sub>IN_PU</sub>     | SYNCH and $\overline{CS}$                                            |                      | 200                      |                  | kΩ    |

| Output Logic-High<br>(SDO)                        | V <sub>OH</sub>        | I <sub>LOAD</sub> = -5mA                                             | V <sub>L</sub> - 0.6 |                          |                  | V     |

| Output Logic-Low                                  | V <sub>OL</sub>        | I <sub>LOAD</sub> = +5mA                                             |                      |                          | 0.33             | V     |

## **Electrical Characteristics (continued)**

$(V_{DD} = +10V \text{ to } +36V, V_{LED} = +3.0V \text{ to } 36V, V_A = +3.0V \text{ to } +5.5V, V_L = +2.5V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$ Typical values are at  $V_{DD} = V_{LED} = 24V, V_A = 3.3V, T_A = +25^{\circ}\text{C}.$  (Note 2)

| PARAMETER                               | SYMBOL                      | CONDITIONS                                                                                                                                         | MIN                       | TYP | MAX             | UNITS |

|-----------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|-----------------|-------|

| SDO Output Tristate<br>Leakage          | IL_SDO                      | CS = high                                                                                                                                          | -1                        |     | +1              | μA    |

| DC Characteristics / OP                 | EN-DRAIN OUTF               | PUT (FAULT, COMERR, READY, VDDOK)                                                                                                                  |                           |     |                 |       |

| READY Output Logic-<br>High             | V <sub>ODH</sub>            | I <sub>LOAD</sub> = -5mA                                                                                                                           | V <sub>L</sub> - 0.6      |     |                 | V     |

| Output Logic-Low                        | V <sub>ODL</sub>            | I <sub>LOAD</sub> = +5mA                                                                                                                           |                           |     | 0.33            | V     |

| Leakage                                 | I <sub>ODL</sub>            | Open-drain output off, V <sub>OD</sub> = 5.5V                                                                                                      | -1                        |     | +1              | μA    |

| DC Characteristics / LEI                | D Drivers (LH_, L           | L_)                                                                                                                                                | •                         |     |                 |       |

| LED Supply Voltage                      | V <sub>VLED</sub>           |                                                                                                                                                    | 3.0                       |     | V <sub>DD</sub> | V     |

| LH Voltage High                         | V <sub>OH_LH</sub>          | LH = on, V <sub>LED</sub> = V <sub>DD</sub> , I <sub>VLED</sub> = -5mA                                                                             | V <sub>LED</sub> -<br>0.3 |     |                 | V     |

| LH Off Leakage Current                  | IL_LH                       | $LH_ = off, V_{LED} = 0V$                                                                                                                          |                           |     | 5               | μA    |

| LL Output Voltage Low                   | V <sub>OH_LL</sub>          | LL = on, I <sub>VLED</sub> = 5mA                                                                                                                   |                           |     | 0.3             | V     |

| LL Off Leakage Current                  |                             | $LL = off, V_{LED} = V_{DD}$                                                                                                                       | -1                        |     | +1              | μA    |

| DC Characteristics / PR                 | OTECTION                    |                                                                                                                                                    |                           |     |                 |       |

| OUT_ Clamp Voltage                      | V <sub>CL</sub>             | $V_{CL} = V_{DD} - V_{OUT}$ , $I_{OUT} = -500$ mA,<br>OUT_ is off                                                                                  | 49                        | 56  |                 | V     |

| Channel Thermal<br>Shutdown Temperature | T <sub>JSHDN</sub>          | Junction temperature rising. Per channel.                                                                                                          |                           | 150 |                 | °C    |

| Channel Thermal<br>Shutdown Hysteresis  | T <sub>JSHDN_HYST</sub>     |                                                                                                                                                    |                           | 15  |                 | °C    |

| Chip Thermal Shutdown                   | T <sub>CSHDN</sub>          | Temperature rising.                                                                                                                                |                           | 150 |                 | °C    |

| Chip Thermal Shutdown<br>Hysteresis     | T <sub>CSHDN_HYS</sub><br>T |                                                                                                                                                    |                           | 10  |                 | °C    |

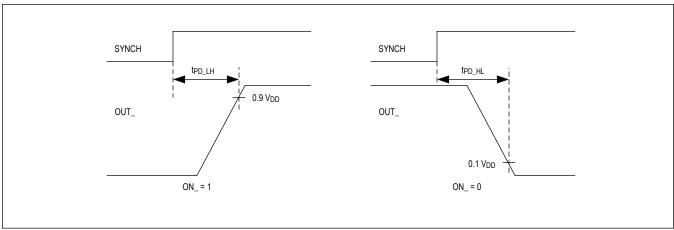

| Timing Characteristics /                | OUT_                        |                                                                                                                                                    |                           |     |                 |       |

| Prop Delay LH                           | <sup>t</sup> PD_LH          | Delay from rising SYNCH edge to V <sub>OUT</sub> _<br>rising to 90%. R <sub>L</sub> = 48 $\Omega$ . V <sub>DD</sub> = 24V.<br><u>Figure 2</u>      |                           | 11  | 30              | μs    |

| Prop Delay HL                           | <sup>t</sup> PD_HL          | Delay from rising SYNCH edge to V <sub>OUT</sub> falling to 10% of V <sub>DD</sub> , V <sub>DD</sub> = 24V, R <sub>L</sub> = $48\Omega$ , Figure 2 |                           | 11  | 30              | μs    |

| Rise Time                               | t <sub>R</sub>              | 20% to 80% V <sub>DD</sub> , V <sub>DD</sub> = 24V, R <sub>L</sub> = 48 $\Omega$ , Figure 2                                                        |                           | 8   |                 | μs    |

| Fall Time                               | t <sub>F</sub>              | 80% to 20% V <sub>DD</sub> , V <sub>DD</sub> = 24V, R <sub>L</sub> = 48 $\Omega$ , Figure 2                                                        |                           | 8   |                 | μs    |

| Timing Characteristics /                | GLITCH FILTER               | S                                                                                                                                                  |                           |     |                 |       |

| Pulse Length of<br>Rejected Glitch      | <sup>t</sup> FPL_GF         | EN, SYNCH, SPIWD, SYNCHWD,<br>CRCEN                                                                                                                | 0                         |     | 80              | ns    |

| Passed Pulse Length                     | t <sub>FD_GF</sub>          | EN, SYNCH, SPIWD, SYNCHWD,<br>CRCEN                                                                                                                | 300                       |     |                 | ns    |

## **Electrical Characteristics (continued)**

$(V_{DD} = +10V \text{ to } +36V, V_{LED} = +3.0V \text{ to } 36V, V_A = +3.0V \text{ to } +5.5V, V_L = +2.5V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$ Typical values are at  $V_{DD} = V_{LED} = 24V, V_A = 3.3V, T_A = +25^{\circ}\text{C}.$  (Note 2)

| PARAMETER                     | SYMBOL              | CONDITIONS                                                                      | MIN | TYP | MAX | UNITS |

|-------------------------------|---------------------|---------------------------------------------------------------------------------|-----|-----|-----|-------|

| Clitch Filter Dolou Time      | <sup>t</sup> D_GF   | EN, SYNCH                                                                       |     | 140 | 300 |       |

| Glitch Filter Delay Time      | <sup>t</sup> D_GFL  | SPIWD, SYNCHWD, CRCEN                                                           |     | 290 | 600 | - ns  |

| Timing Characteristics /      | WATCHDOG            |                                                                                 |     |     |     |       |

| Watchdogs Timeout<br>Accuracy | <sup>t</sup> WD_ACC | SPIWD/SYNCHWD = 1                                                               | -30 |     | +30 | %     |

| Timing Characteristics /      | LED Matrix          |                                                                                 |     |     |     |       |

| LED Driver Scan rate          | FLED                | Update rate for each LED                                                        |     | 1   |     | kHz   |

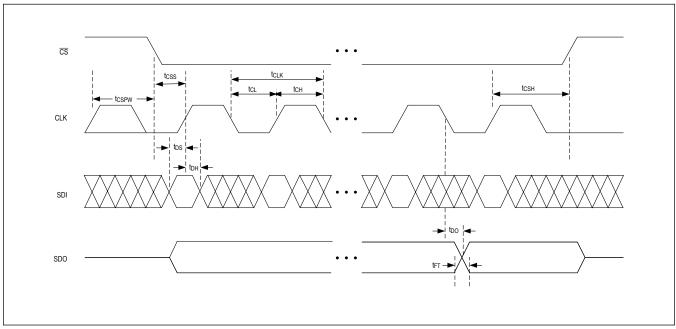

| Timing Characteristics /      | SPI                 |                                                                                 |     |     |     |       |

| CLK Clock Period              | t <sub>CH+CL</sub>  |                                                                                 | 100 |     |     | ns    |

| CLK Pulse Width High          | t <sub>CH</sub>     |                                                                                 | 40  |     |     | ns    |

| CLK Pulse Width Low           | t <sub>CL</sub>     |                                                                                 | 40  |     |     | ns    |

| CS Fall to CLK Rise<br>Time   | tcss                |                                                                                 | 40  |     |     | ns    |

| SDI Hold Time                 | t <sub>DH</sub>     |                                                                                 | 10  |     |     | ns    |

| SDI Setup Time                | t <sub>DS</sub>     |                                                                                 | 10  |     |     | ns    |

| SDO Propagation Delay         | t <sub>DO</sub>     | C <sub>LOAD</sub> = 10pF, CLK falling edge to SDO stable                        |     |     | 30  | ns    |

| SDO Rise and Fall<br>Times    | t <sub>FT</sub>     |                                                                                 |     | 1   |     | ns    |

| CS Hold Time                  | t <sub>CSH</sub>    |                                                                                 | 40  |     |     | ns    |

| CS Pulse Width High           | tCSPW               | (Note 3)                                                                        | 40  |     |     | ns    |

| EMC                           |                     |                                                                                 |     |     |     |       |

|                               | V <sub>ESD_C</sub>  | OUT_ to GND, IEC 61000-4-2 Contact<br>Discharge                                 |     | ±7  |     |       |

| ESD                           | V <sub>ESD_A</sub>  | OUT_ to GND, IEC 61000-4-2 Air<br>Discharge                                     |     | ±30 |     | kV    |

|                               | V <sub>ESD</sub>    | All other pins. Human Body Model (Note 4)                                       |     | ±2  |     |       |

| Surge Tolerance               | V <sub>SURGE</sub>  | OUT_ to GND, IEC 61000-4-5 with 42 $\Omega$ , TVS on V <sub>DD</sub> . (Note 5) |     | ±1  |     | kV    |

**Note 2:** All units are production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by characterization.

**Note 3:** Specification is guaranteed by design; not production tested.

Note 4: Bypass  $V_{DD}$  pin to GND with 1µF capacitor as close as possible to the device for high ESD protection.

**Note 5:** At typical application value of  $V_{DD}$  = 24V with a TVS protection on  $V_{DD}$  to GND.

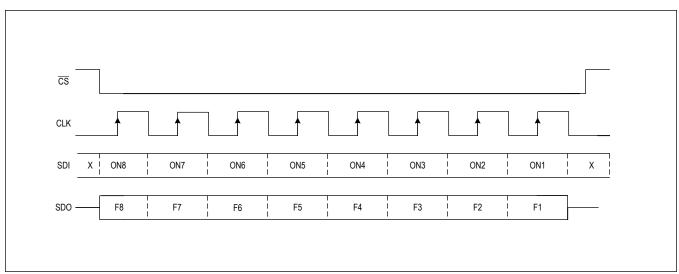

Figure 1. SPI TIming Diagram

Figure 2. SYNCH to OUT\_ Propagation Delay

# Industrial Octal High-Side Switch

### **Typical Operating Characteristics**

(V<sub>DD</sub> = +24V, REGEN = open,  $V_L$  = +3.3V,  $T_A$  = +25°C, unless otherwise noted.)

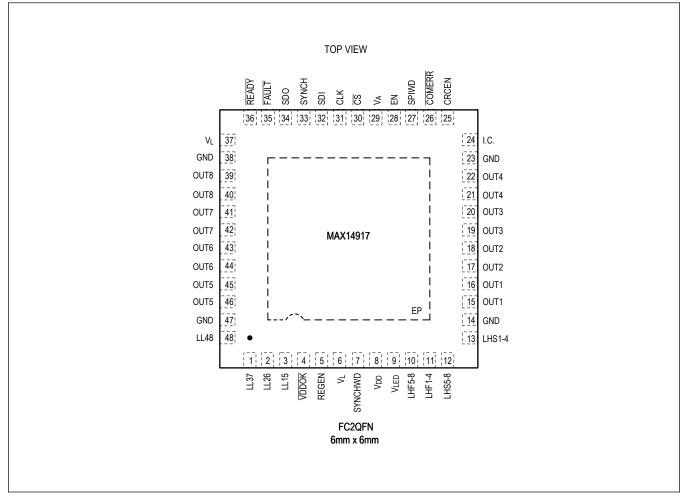

### **Pin Configuration**

#### MAX14917

### **Pin Description**

| PIN            | NAME            | FUNCTION                                                                                                                                                                                  | REF<br>SUPPLY | TYPE   |

|----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------|

| Power Supply   |                 |                                                                                                                                                                                           |               |        |

| EP, 8          | V <sub>DD</sub> | Supply Voltage, Nominally 24V. Connect all $V_{DD}$ together. Bypass $V_{DD}$ to GND through a $1\mu F$ capacitor.                                                                        | GND           | Supply |

| 29             | V <sub>A</sub>  | Analog Supply Input. Connect an external 3.0V to 5.5V supply to $V_A$ or use the internal linear regulator by leaving REGEN open.<br>Bypass $V_A$ to GND through a 1µF ceramic capacitor. | GND           | Supply |

| 5              | REGEN           | $V_A$ Regulator Enable Input. Connect REGEN to GND to disable $V_A$ regulator. Leave REGEN open to enable the $V_A$ regulator, which internally supplies $V_A$ with 3.3V.                 | GND           | Supply |

| 14, 23, 38, 47 | GND             | Ground. Connect all GND pins together.                                                                                                                                                    | GND           | GND    |

## **Pin Description (continued)**

| PIN            | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                 | REF<br>SUPPLY   | TYPE   |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|

| 6, 37          | VL      | Logic Supply Input. V <sub>L</sub> defines the logic levels on all logic interface pins. Bypass V <sub>L</sub> to GND through a 100nF ceramic capacitor.                                                                                                                                                                                                                                                 | GND             | Supply |

| 4              | VDDOK   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                    | GND             | Logic  |

| Switch Outpu   | its     |                                                                                                                                                                                                                                                                                                                                                                                                          |                 |        |

| 15, 16         | OUT1    | High-Side Switch Output 1                                                                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> | Power  |

| 17, 18         | OUT2    | High-Side Switch Output 2                                                                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> | Power  |

| 19, 20         | OUT3    | High-Side Switch Output 3                                                                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> | Power  |

| 21, 22         | OUT4    | High-Side Switch Output 4                                                                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> | Power  |

| 45, 46         | OUT5    | High-Side Switch Output 5                                                                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> | Power  |

| 43, 44         | OUT6    | High-Side Switch Output 6                                                                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> | Power  |

| 41, 42         | OUT7    | High-Side Switch Output 7                                                                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> | Power  |

| 39, 40         | OUT8    | High-Side Switch Output 8                                                                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> | Power  |

| Control Interf | face    |                                                                                                                                                                                                                                                                                                                                                                                                          |                 |        |

| 28             | EN      | Enable Logic Input. Drive EN high for normal operation. Drive EN low to disable/three-state all OUT_ drivers. Internal weak pulldown.                                                                                                                                                                                                                                                                    | VL              | Logic  |

| 35             | FAULT   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                    | VL              | Logic  |

| 33             | SYNCH   | SYNCH Input. All eight output switches are updated<br>simultaneously on the rising edge of SYNCH, as determined by<br>the content of the SPI command. The OUT_states do not change<br>when SYNCH is held Iow. When SYNCH is high, the output states<br>change immediately after a new SPI command. SYNCH has a<br>weak pullup.                                                                           | VL              | Logic  |

| 25             | CRCEN   | CRC Enable Select Input. Drive CRCEN high to enable CRC generation and error detection on the serial data. CRC has a weak pulldown.                                                                                                                                                                                                                                                                      | VL              | Logic  |

| 36             | READY   | Open-Drain Output. $\overline{\text{READY}}$ is passive low when the internal logic chip supply and V <sub>L</sub> I/O supply are both higher than their respective UVLO thresholds, indicating that the part is ready for SPI communication. When the internal register supply falls below the UVLO threshold the OUTs are off and READY transitions active-high. Connect a pulldown resistor to READY. | VL              | Logic  |

| 26             | COMERR  | SPI Error Open-Drain Output. The $\overline{\text{COMERR}}$ transistor turns on low when an error occurs during a SPI transaction. Connect a pullup resistor to VL.                                                                                                                                                                                                                                      | VL              | Logic  |

| 7              | SYNCHWD | SYNCH Watchdog Enable Logic Input. Set SYNCHWD high to enable the SYNCH watchdog.                                                                                                                                                                                                                                                                                                                        | VL              | Logic  |

| 27             | SPIWD   | SPI Watchdog Enable Logic Input. Set SPIWD high to enable the SPI watchdog.                                                                                                                                                                                                                                                                                                                              | VL              | Logic  |

## **Pin Description (continued)**

| PIN            | NAME             | FUNCTION                                                                                                                  | REF<br>SUPPLY | TYPE  |

|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------|---------------|-------|

| Serial Interfa | ice              |                                                                                                                           | ·             |       |

| 32             | SDI              | Serial Data Input. SPI MOSI data from controller. SDI has a weak pulldown.                                                | VL            | Logic |

| 34             | SDO              | Serial Data Output. SPI MISO data output to controller.                                                                   | VL            | Logic |

| 31             | CLK              | Serial Clock Input. CLK has a weak pulldown.                                                                              | VL            | Logic |

| 30             | CS               | Chip Select Input. CS has a weak pullup.                                                                                  | VL            | Logic |

| ED DRIVER      | MATRIX           |                                                                                                                           |               |       |

| 9              | V <sub>LED</sub> | Supply for LED Drivers. Apply supply voltage of 3.0V to V <sub>DD</sub> .                                                 |               |       |

| 3              | LL15             | OUTs 1, 5 Status/Fault LED Cathode Output (Open-drain Low-<br>Side). Connect a resistor in series to set the LED current. |               |       |

| 2              | LL26             | OUTs 2, 6 Status/Fault LED Cathode Output (Open-Drain Low-<br>Side). Connect a resistor in series to set the LED current. |               |       |

| 1              | LL37             | OUTs 3, 7 Status/Fault LED Cathode Output (Open-Drain Low-<br>Side). Connect a resistor in series to set the LED current. |               |       |

| 48             | LL48             | OUTs 4, 8 Status/Fault LED Cathode Output (Open-Drain Low-<br>Side). Connect a resistor in series to set the LED current. |               |       |

| 13             | LHS1-4           | OUTs 1-4 Status LED Anode Outputs (Open-Drain High-Side).<br>Connect a resistor in series to set the LED current.         |               |       |

| 12             | LHS5-8           | OUTs 5-8 Status LED Anode Outputs (Open-Drain High-Side).<br>Connect a resistor in series to set the LED current.         |               |       |

| 11             | LHF1-4           | OUTs 1-4 Fault LED Anode Connections (Open-Drain High-Side).<br>Connect a resistor in series to set the LED current       |               |       |

| 10             | LHF5-8           | OUTs 5-8 Fault LED Anode Connections (Open-Drain High-Side).<br>Connect a resistor in series to set the LED current.      |               |       |

|                | т                | · · · · · · · · · · · · · · · · · · ·                                                                                     |               |       |

| 24             | I.C.             | Internally Connected. Do not connect.                                                                                     |               |       |

### **Detailed Description**

The MAX14917 is an octal high-side switch. The state of the high-side switches (OUT[1:8]) are set through the SPI interface. The OUT\_ high-side switches have an on-resistance of  $120m\Omega$  (typ) at 700mA and  $T_A = 25^{\circ}$ C, and  $250m\Omega$  (max) on-resistance at 700mA and  $T_A = 125^{\circ}$ C. Watchdog timers (SPIWD and/or SYNCHWD) monitor SPI and/or SYNCH activity, and automatically turn the OUT\_ pins off in case of missing SPI/SYNCH activity when enabled.

#### Global OUT Disable

When the EN pin input is low, all OUT\_ switches are off independent of the level of the SYNCH input or the ON\_ bits in the SPI command (Figure 6). Logic low on the EN pin also allows quick disable of all OUT\_ switches in case of emergency. Note: logic high on the EN pin is required for normal operation.

#### Power-Up and Undervoltage Lockout

When the  $V_{DD}$ ,  $V_A$ ,  $V_L$ , or  $V_{INT}$  supply voltages are under their respective UVLO thresholds, all OUT\_ switches are off.  $V_{INT}$  is an internal supply for the registers and logic that is derived from the  $V_A$  or  $V_{DD}$  supply.

When the V<sub>DD</sub> supply or V<sub>A</sub> supply rises, the internal logic supply (V<sub>INT</sub>) rises. If V<sub>L</sub> and V<sub>INT</sub> are both above their UVLO thresholds, the chip is ready for communication and the READY pin becomes passive low to indicate that the part is ready to communicate through the SPI interface.

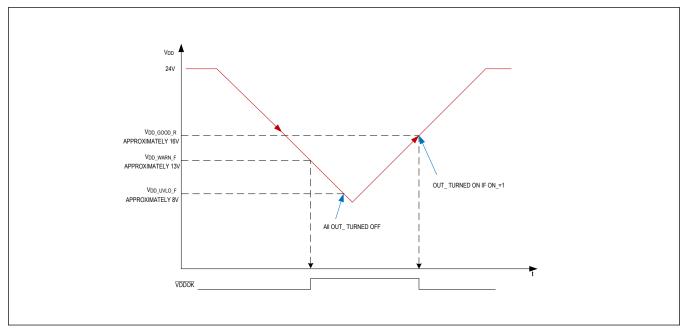

When  $V_{DD}$  rises above  $V_{DD\_GOOD\_R}$  the  $\overline{VDDOK}$  pin is turned active-low, indicating that the  $V_{DD}$  supply is high enough so the OUT\_ switches can be operated normally.

When  $V_{DD}$  falls below 13V (typ) the  $\overline{VDDOK}$  is turned high, but all the OUT\_ switches continue operate normally until  $V_{DD}$  falls below the  $V_{DD\_UVLO\_F}$  threshold. All OUT\_ switches are off until  $V_{DD}$  reaches the  $V_{DD\_GOOD\_R}$  threshold again as shown in Figure 3.

The READY and VDDOK pins are always active, but the FAULT pin does not signal supply conditions.

Figure 3. V<sub>DD</sub> Supply Monitoring

#### Watchdog

The MAX14917 provides two watchdog timers to monitor activity: one on the SPI interface and the other on the SYNCH pin. SPIWD logic high input enables SPI watchdog functions and the SYNCHWD logic high input enables the SYNCH watchdog function.

- The SPI watchdog timer monitors clock activity on the CLK and inputs. At least one valid SPI cycle must be detected in the watchdog-timeout period. This means that the CLK input must have a multiple of 8 clock-cycles during a low period.

- The SYNCH pin watchdog checks if SYNCH is stuck low. At least a 1µs SYNCH pin high level must be present in the watchdog-timeout period. Driving the SYNCH pin high if SYNCH is not used ensures that the SYNCH watchdog is disabled.

If either watchdog criteria is not met, all OUT\_ switches are automatically turned off. The watchdog timeout is 1.2s (typ). Note: the FAULT pin does not indicate the watchdog-timeout error. The CMERR bit is visible only on the second byte if CRC is enabled (CRCEN pin is high). If CRC is not enabled, the second byte is not reported and CMERR is not signaled through SPI, as shown in Figure 7 and Figure 9.

#### **Chip Thermal Protection**

When the chip temperature rises to above the thermal shutdown threshold of 150°C, the chip enters shutdown protection and all overloaded OUT switches are kept off until chip temperature drops below 140°C.

If an overload occurs on the V<sub>A</sub> regulator or on the LED matrix, i.e., if the chip temperature rises above 165°C due to a short, then the V<sub>A</sub> regulator and all OUT switches, as well as the LED matrix are shut down to prevent chip damage. In this condition, the FAULT pin output is driven low. All F<sub>b</sub> bits in the SPI SDO data stream are set to 1. When the chip temperature then falls by the hysteresis amount, the V<sub>A</sub> regulator turns on, and the LED matrix and OUT switches are restored to normal operation.

#### **Channel Thermal Management**

Every OUT switch temperature is constantly monitored. If the temperature of a switch rises above the thermal shutdown threshold of 150°C (typ), that OUT\_ is automatically turned off for protection. After the temperature drops by 15°C, the OUT\_ is turned on again. When an OUT\_ turns off due to thermal shutdown, its associated F\_ bit in the SDO stream and the FAULT pin is driven low.

#### **Current Limiting**

Each high-side switch features active current limiting. When the load current exceeds 1A (typ), the load current is limited by the high-side switch. If the load current exceeds the current limit, the voltage across the high-side FET switch increases and the temperature of the FET increases in accordance with the FET power dissipation. Increase of the switch temperature generally leads to thermal shutdown of that OUT switch.

#### Lamp Load Turn On

Incandescent lamps initially draw high currents while their filament is cold, then this turn-on current reduces as the filament heats up. The MAX14917 automatically detects the presence of a lamps loads. When a lamp load is detected, the overload signaling is masked for a duration of 200ms (typ).

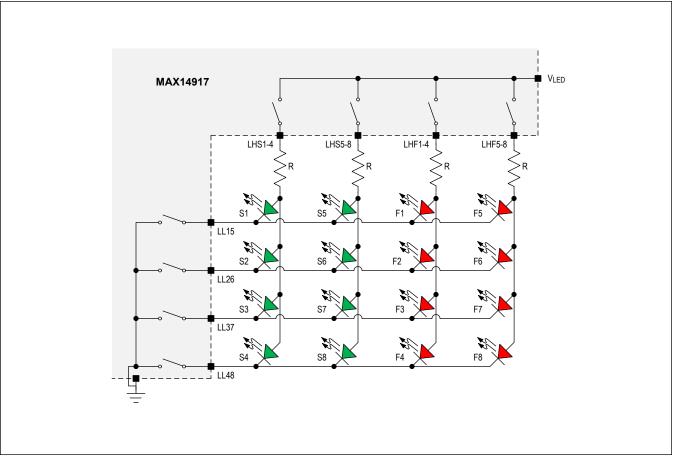

#### **LED Drivers**

The 4x4 LED driver crossbar matrix offers an efficient configuration for driving up to 16 LEDs as shown in Figure 4. The LEDs are controlled by the MAX14917 autonomously to indicate per-channel status and fault conditions. A channel status LED (SLED) is automatically turned on when the corresponding OUT\_ switch is on and there is no fault condition. If a fault is detected, its associated fault LED (FLED) is turned on and its associated status LED (SLED) is automatically turned off. For any OUT\_ channel, its SLED and its FLED are never on simultaneously. The fault LEDs signal thermal overload shutdown of the switches and they are stretched by 2s (typ). The LED matrix is powered through the V<sub>LED</sub> supply input, which can be in the range of the 3.0V (min) up to the V<sub>DD</sub> field supply voltage.

For every current limiting resistor (R) each of the four LEDs in a column string is pulsed for a quarter of the time, so that current only flows through one LED and resistor at any one time. Thus, the resistors (R) determine the LED current through one LED during the pulse. Each LED is pulsed on at a rate of 1kHz (typ) and is on for 25% of the 1ms period. Thus, the average current flowing through a LED that is turned on is about 0.25 x ( $V_{LED} - V_F$ )/R.  $V_F$  is the forward voltage of the LED. The resistor value should be chosen according to the LED current/light intensity requirements.

Figure 4. LED Matrix Scheme

#### **Serial Interface**

The MAX14917 communicates with the host controller through a high-speed SPI serial interface. The interface has three logic inputs: clock (CLK), chip select ( $\overline{CS}$ ), serial data in (SDI), and one data out (SDO). The SDO is three-stated when  $\overline{CS}$  is high. The maximum SPI clock rate is 10MHz. The SPI interface logic complies with SPI clock polarity CPOL = 0 and clock phase CPHA = 0.

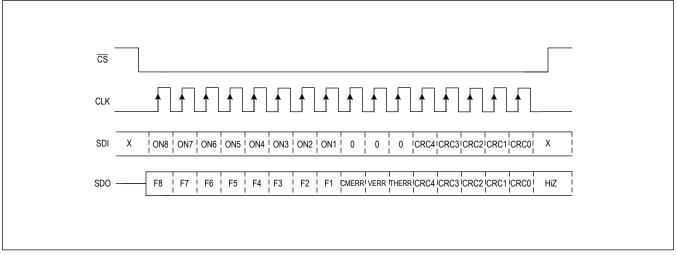

The basic SPI command is 8 clock cycles and is extended to 16 clocks when CRC is enabled (CRCEN = high).

Note: while Figure 1, Figure 6, and Figure 7 show CLK to be low at the beginning of the SPI cycle, on the falling  $\overline{CS}$  edge, the CLK can also be logic high. The MAX14917 ignores the initial CLK logic state and only acts on the first rising CLK edge and samples the first SDI bit.

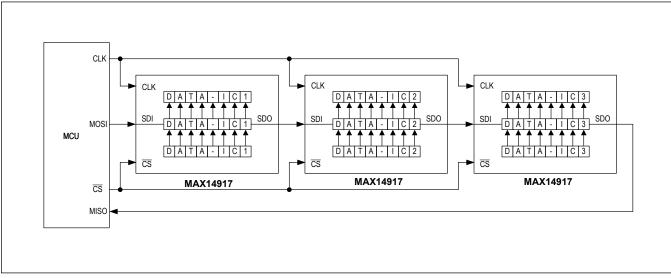

#### Daisy-Chained SPI

Daisy-chained SPI mode allows communication with multiple MAX14917 devices using a common  $\overline{CS}$  signal in one SPI cycle (refer to Figure 5). Figure 6 shows a single SPI cycle without CRC enabled (CRCEN = low) for one device.

If the ON\_ bit is a 1 the high-side switch is turned on, and if it is 0, the high-side switch is turned off. The F\_ bits are per-channel faults. The F\_ bits are latched and are, therefore, only cleared on the following SPI cycle if the fault has disappeared before the following SPI cycle. The F\_ bits do not go active when a lamp load is detected. In thermal chip shutdown, all F\_ bits are set to 1.

CRC error detection is supported if the CRCEN pin is high, which lengthens the minimum SPI cycle to 16 CLK clocks per MAX14917. A single SPI command with CRC enabled is shown in Figure 7.

Figure 5. Diagram of Three MAX14917 Devices Daisy-Chained

Figure 6. Single SPI Command

Figure 7. Single SPI Command with CRC

### Checking of Clocks on the Serial Interface

The MAX14917 checks that the number of clock cycles in one SPI cycle (from falling edge of  $\overline{CS}$  to rising edge of  $\overline{CS}$ ) is a multiple of 8. The expected number of clocks is scaled according to CRCEN setting. If the number of clock cycles differs from the expected, then the SPI command is not executed and an SPI error is signaled through the  $\overline{COMERR}$  pin.

### **CRC Error Detection on the Serial Interface**

CRC error detection of the serial data can be enabled to minimize incorrect operation/misinformation due to data corruption of the SDI/SDO signals. If error detection is enabled, then the MAX14917:

- 1. Performs error detection on the SDI data that it receives from the controller, and

- 2. Calculates a CRC on the SDO data and appends a check byte to the SDO diagnostics/status data that it sends to the controller.

This ensures that both the data that it receives from the controller (OUT\_ setting) and the data that it sends to the controller (F\_ diagnostic) have a low likelihood of undetected errors.

## Industrial Octal High-Side Switch

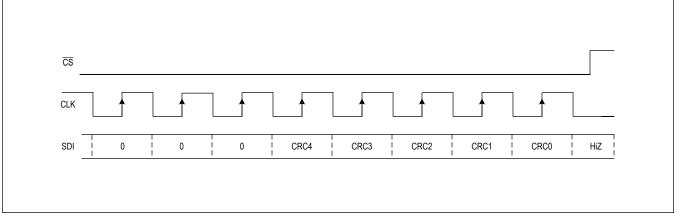

Setting the CRCEN input high enables CRC error detection. A CRC frame check sequence (FCS) is then sent along with each serial transaction. The 5-bit FCS is based on the generator polynomial X5 + X4 + X2 + 1 with CRC starting value = 11111. When CRC is enabled, the MAX14917 expects a check byte appended to the SDI program/configure data that it receives. The check byte has the format shown in Figure 8. The five FCS bits (CR\_) are calculated on all the data sent in one SPI command including the three "0" in the MSBs of the check byte. Therefore, the CRC is calculated from 8 bits + 3 bits. CR0 is the LSB of the FCS.

The MAX14917 verifies the received FCS. If no error is detected, the MAX14917 sets the OUT\_ output switches per the SDI data. If a CRC error is detected, then the MAX14917 does not change the OUT\_ outputs, but sets the COMERR logic output low (i.e., the open-drain COMERR NMOS output transistor is turned on).

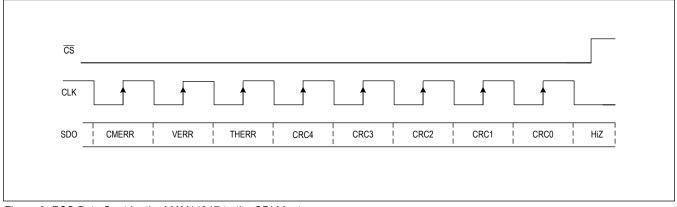

In Figure 9, the format of the check byte that the device appends to the SDO data is shown: the CMERR bit is set when either an SPI or SYNCH watchdog event has occurred; the VERR bit is set if either of the  $V_{DD}$ ,  $V_A$ , or internal voltages is below its nominal operational thresholds; and, the THERR bit is set when a chip thermal shutdown event has occurred. The CR\_ are the CRC bits that the MAX14917 calculate on the SDO data, including the CMERR, VERR, and THERR bits. This allows the controller to check for errors on the SDO data received from the MAX14917.

Figure 8. FCS Byte Expected from the SPI Master

Figure 9. FCS Byte Sent by the MAX14917 to the SPI Master

### **Applications Information**

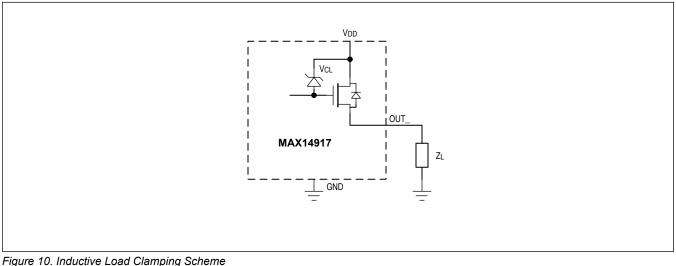

#### Inductive Load Turn-Off Energy Clamping

During turn-off of inductive loads, the free-wheel energy is clamped by the internal V<sub>CL</sub> clamps. This energy must be limited to 150mJ (max) at  $T_J$  = +125°C and I<sub>OUT</sub> = -600mA per channel, all channels switching simultaneously. Refer to Figure 10.

#### Figure TO. Inductive Load Clamping Sch

#### Surge Protection

The MAX14917 has internal protection against  $\pm 1$ kV  $42\Omega/0.5\mu$ F  $1.2\mu$ s/50 $\mu$ s surges on the OUT\_ pins to GND, if the V<sub>DD</sub> pins are protected with one TVS. Ensure that the peak voltage of the V<sub>DD</sub> TVS is below 65V.

#### **RF Conducted Immunity**

To ensure that the OUT\_ pins do not produce wrong logic conditions while being off, during IEC61000-4-6 RF immunity testing, connect 10nF capacitors at each OUT\_ to GND.

#### Reverse Currents into OUT\_

If currents flow into the OUT\_ pins, the device heats up due to internal currents that flow through the device from  $V_{DD}$  to GND. The internal currents are proportional to the reverse current into OUT\_. The allowed reverse OUT\_ current depends on  $V_{DD}$ , the ambient temperature and the thermal resistance. At 25°C ambient temperature, the reverse current into one OUT should be limited to 1A at  $V_{DD}$  = 36V and 1.5A at  $V_{DD}$  = 24V. Driving higher currents into OUT\_ can destroy the device thermally.

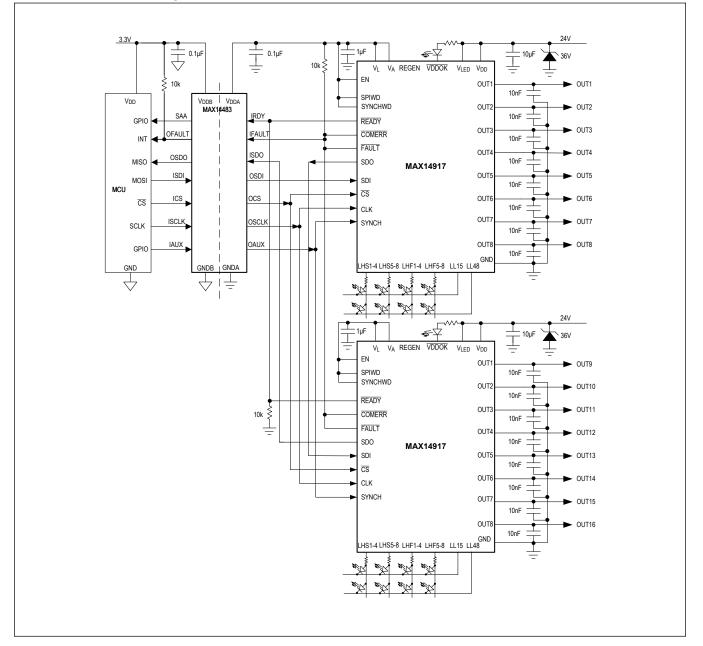

## **Typical Application Circuits**

#### 16-Channel Isolated High-Side Switch

# Industrial Octal High-Side Switch

## **Ordering Information**

| PART          | TEMP RANGE      | PACKAGE                   | TOP MARKING | LEAD PITCH |

|---------------|-----------------|---------------------------|-------------|------------|

| MAX14917AFM+  | -40°C to +125°C | 48-Pin F2CQFN (6mm x 6mm) | MAX14917AFM | 0.4mm      |

| MAX14917AFM+T | -40°C to +125°C | 48-Pin F2CQFN (6mm x 6mm) | MAX14917AFM | 0.4mm      |

+ Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

## Industrial Octal High-Side Switch

### **Revision History**

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 2/20     | Initial release | —       |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Switch ICs - Power Distribution category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

TCK111G,LF(S\_FPF1018\_DS1222\_TCK2065G,LF\_SZNCP3712ASNT3G\_MIC2033-05BYMT-T5\_MIC2033-12AYMT-T5\_MIC2033-05BYM6-T5\_SLG5NT1437VTR\_SZNCP3712ASNT1G\_DML1008LDS-7\_KTS1670EDA-TR\_KTS1640QGDV-TR\_KTS1641QGDV-TR U6513A\_MIC2012YM-TR\_MP5095GJ-P\_TPS2021IDRQ1\_TPS2104DBVR\_TPS22958NDGKR\_MIC2098-1YMT-TR\_MIC94062YMT\_TR MP6231DN-LF\_MIC2015-1.2YM6\_TR\_MIC2075-2YM\_MIC94068YML-TR\_SIP32461DB-T2-GE1\_NCP335FCT2G\_TCK105G,LF(S\_AP2411S-13\_AP2151DSG-13\_AP2172MPG-13\_MIC94094YC6-TR\_MIC94093YC6-TR\_MIC94064YC6-TR\_MIC94061YMT-TR\_MIC2505-1YM\_MIC94085YFT-TR\_MIC94042YFL-TR\_MIC2005-1.2YM6-TR\_NCP333FCT2G\_NCP331SNT1G\_TPS2092DR\_TPS2063DR MIC2008YML-TR\_MIC94084YFT-TR\_MIC2040-1YMM\_DI01280WL12\_AP22814ASN-7\_MIC2043-2YTS