### **High-Accuracy 12-/16-Cell Measurement AFEs**

### **General Description**

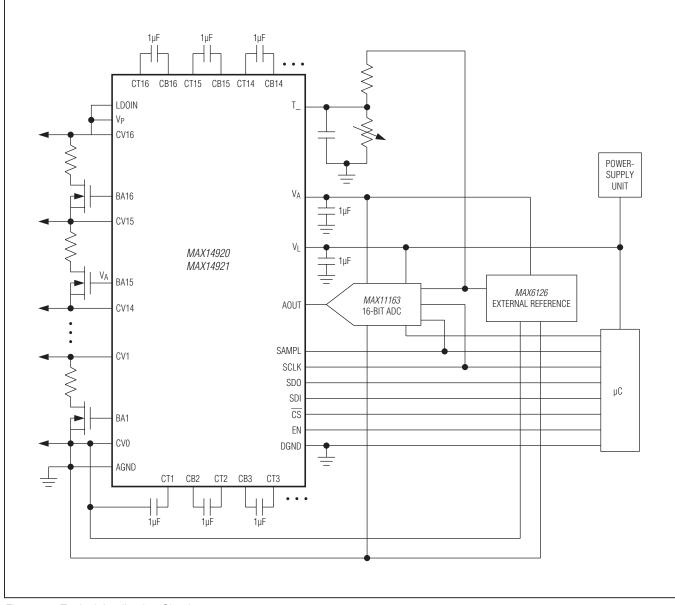

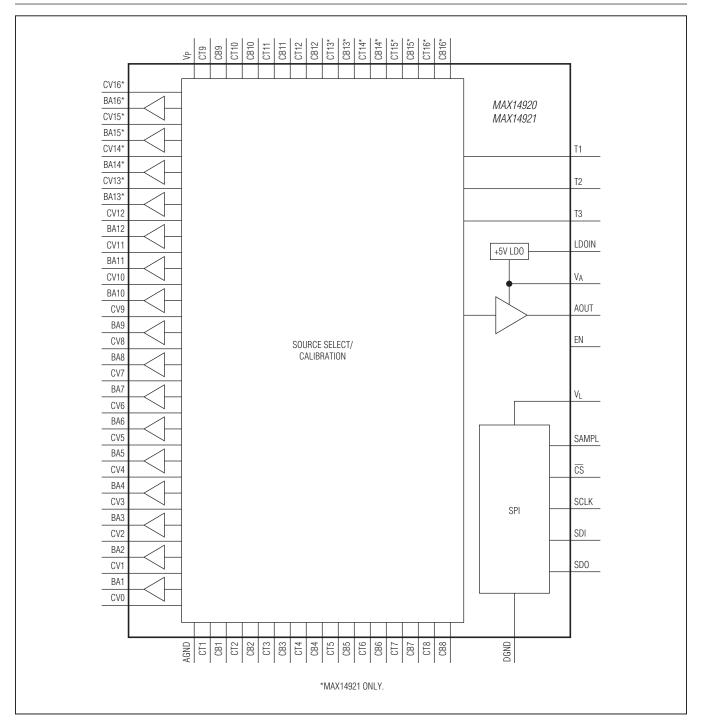

The MAX14920/MAX14921 battery measurement analog front-end devices accurately sample cell voltages and provide level shifting for primary/secondary battery packs up to 16 cells/+65V (max). The MAX14920 monitors up to 12 cells, while the MAX14921 monitors up to 16 cells. Both devices simultaneously sample all cell voltages, allowing accurate state-of-charge and source-resistance determination. All cell voltages are level shifted to ground reference with unity gain, simplifying external ADC data conversion.

The devices have a low-noise, low-offset amplifier that buffers differential voltages of up to +5V, allowing monitoring of all common lithium-ion (Li+) cell technologies. The resulting cell voltage error is  $\pm 0.5$ mV.

The devices' high accuracy make them ideal for monitoring cell chemistries with very flat discharge curves, such as lithium-metal phosphate.

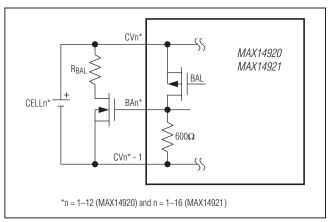

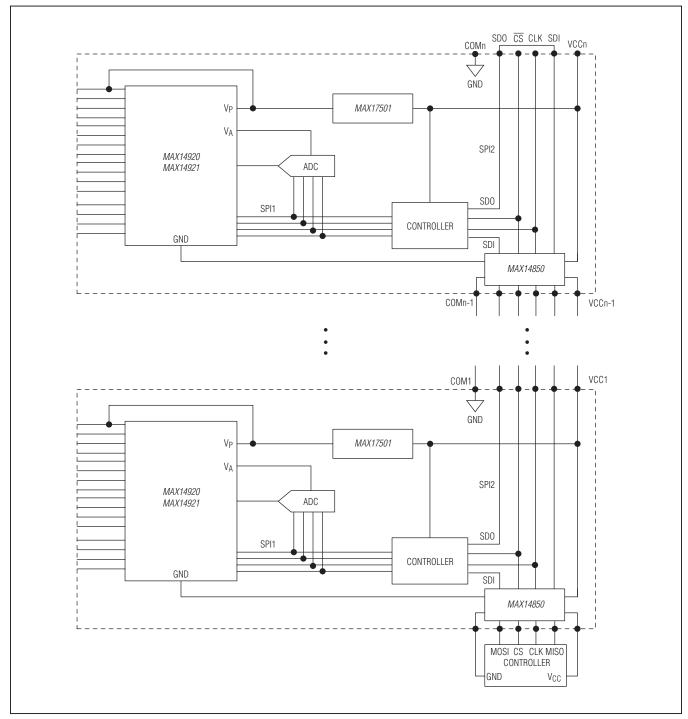

Passive-cell balancing is supported by external FET drivers. Integrated diagnostics in the devices allow open-wire detection and undervoltage/overvoltage alarms. The devices are controlled by a daisy-chainable SPI interface.

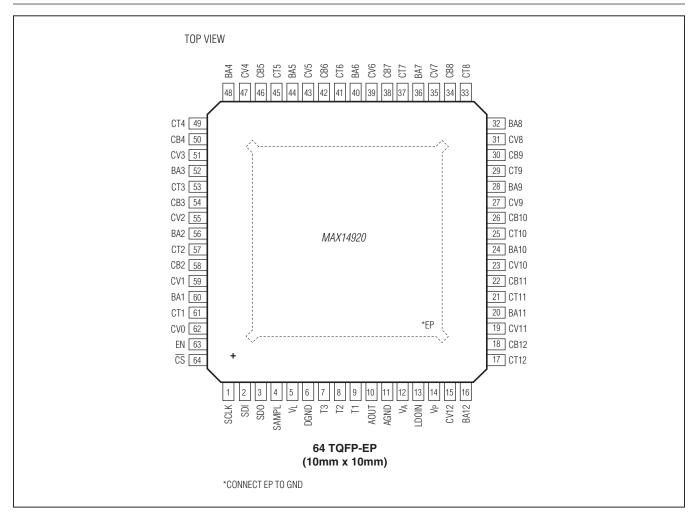

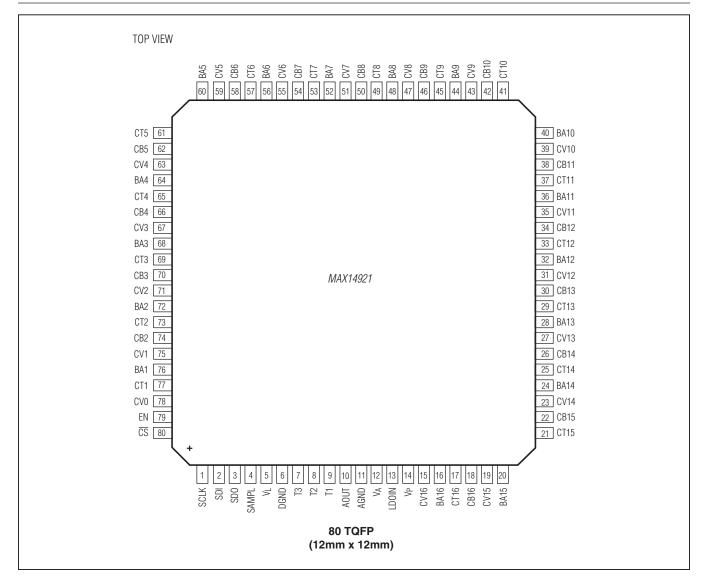

The MAX14920 is available in a 64-pin (10mm x 10mm) TQFP package with an exposed pad. The MAX14921 is available in an 80-pin (12mm x 12mm) TQFP package. Both devices are specified over the  $-40^{\circ}$ C to  $+85^{\circ}$ C extended temperature range.

### **Applications**

Industrial Battery Backup Systems Telecom Battery Backup Systems Energy Storage Packs e-Transportation Energy Packs

### **Benefits and Features**

- High Accuracy

- Simultaneous Cell Voltage Sampling

- ♦ Self-Calibration

- Integrated Diagnostics

- ♦ Open-Wire and Short Fault Detection

- Overvoltage Warning

- Thermal Shutdown

- High Flexibility

- $\diamond$  SPI Interface

- 12-Cell and 16-Cell Versions

- ♦ +6V Minimum (3 Cells) Operation

- ♦ +0.5V to +4.5V Cell Voltage Range

- ♦ Integrated Cell-Balancing FET Drivers

- ♦ Integrated 5V LDO

- Low Power

Ordering Information appears at end of data sheet.

<u>Functional Diagram</u> appears at end of data sheet.

For related parts and recommended products to use with this part, refer to <u>www.maximintegrated.com/MAX14920.related</u>.

## **High-Accuracy 12-/16-Cell Measurement AFEs**

### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to AGND.)                                           | BA1 to AGND0.3V to (V <sub>CV1</sub> + 0.3V)                                   |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| V <sub>P</sub> to AGND0.3V to +70V                                           | BA2–BA12 to                                                                    |

| LDOIN to AGND $(V_A - 0.3V)$ to $(V_P + 0.3V)$                               | AGND(V <sub>CV(n* - 1)</sub> - 0.3V) to min((V <sub>CVn*</sub> + 0.3V) or +6V) |

| V <sub>A</sub> to AGND0.3V to +6V                                            | BA2–BA16 to AGND                                                               |

| CV0, DGND to AGND0.3V to +0.3V                                               | (MAX14921 only)(V <sub>CV(m** - 1)</sub> - 0.3V) to min                        |

| SCLK, SDI, CS, EN0.3V to +6V                                                 | ((V <sub>CVm**</sub> + 0.3V) or +6V)                                           |

| SDO, SAMPL0.3V to (V <sub>L</sub> + 0.3V)                                    | AOUT, T1, T2, T3 to AGND0.3V to (V <sub>A</sub> + 0.3V)                        |

| CV1 to AGND0.3V to +6V                                                       | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                          |

| CV2–CV12 to AGND(V <sub>CV</sub> (n* - 1) - 0.3V) to (V <sub>P</sub> + 0.3V) | 64-Pin TQFP-EP (derate 31.3mW/°C above +70°C)2508mW                            |

| CT1–CT12 to AGND0.3V to (V <sub>CV1</sub> –V <sub>CV12</sub> + 0.3V)         | 80-Pin TQFP (derate 23.3mW/°C above +70°C) 1860mW                              |

| CB2–CB12 to AGND0.3V to (V <sub>CV(n* - 1)</sub> + 0.3V)                     | Operating Temperature Range40°C to +85°C                                       |

| CV2–CV16 to AGND                                                             | Maximum Junction Temperature+150°C                                             |

| (MAX14921 only)(V <sub>CV(m** - 1)</sub> - 0.3V) to (V <sub>P</sub> + 0.3V)  | Storage Temperature Range65°C to +150°C                                        |

| CT1–CT16 to AGND                                                             | Lead Temperature (soldering, 10s)+300°C                                        |

| (MAX14921 only)0.3V to (V <sub>CV1</sub> -V <sub>CV16</sub> + 0.3V)          | Soldering Temperature (reflow)+260°C                                           |

| CB2–CB16 to AGND                                                             | *n = 2–12                                                                      |

| (MAX14921 only)0.3V to (V <sub>CV(m** - 1)</sub> + 0.3V)                     | ** <i>m</i> = 2–16                                                             |

|                                                                              |                                                                                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) |          | Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) |        |

|----------------------------------------------------------|----------|-------------------------------------------------------|--------|

| 64-Pin TQFP-EP                                           | 31.9°C/W | 64-Pin TQFP-EP                                        | .1°C/W |

| 80-Pin TQFP                                              | 43°C/W   | 80-Pin TQFP                                           | .8°C/W |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

### DC ELECTRICAL CHARACTERISTICS

(V<sub>P</sub> = +65V, DGND = AGND, V<sub>L</sub> = V<sub>EN</sub> = +3.3V, V<sub>A</sub> = +5V, C<sub>SAMPLE</sub> = 1 $\mu$ F, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                            | SYMBOL             | CONDITIONS                                               | MIN   | TYP | MAX   | UNITS |  |  |  |

|--------------------------------------|--------------------|----------------------------------------------------------|-------|-----|-------|-------|--|--|--|

| POWER SUPPLIES                       |                    |                                                          |       |     |       |       |  |  |  |

| V <sub>P</sub> Supply Voltage        | V <sub>P</sub>     |                                                          | +6    |     | +65   | V     |  |  |  |

|                                      | IP_OFF             | EN = Iow  or  LOPW = 1                                   |       |     | 1     |       |  |  |  |

| V <sub>P</sub> Supply Current        | IP_ON              | EN = high                                                |       | 65  | 150   | - μΑ  |  |  |  |

| LDOIN Supply Voltage                 | V <sub>LDOIN</sub> |                                                          | +6    |     | +65   | V     |  |  |  |

|                                      | ILDOIN_OFF         | $EN = Iow, I_A = 0A$                                     |       | 75  | 125   | μA    |  |  |  |

| LDOIN Supply Current                 | ILDOIN_ON          | $EN = high, I_A = 0A$                                    |       | 350 | 500   |       |  |  |  |

| V <sub>A</sub> Analog Supply Voltage | VA                 | $V_A$ supply externally, $V_A = V_{LDOIN}$               | +4.75 | +5  | +5.25 | V     |  |  |  |

| V Apolog Supply Current              | I <sub>A_OFF</sub> | $EN = Iow, V_A = V_{LDOIN}$                              |       | 50  | 75    |       |  |  |  |

| V <sub>A</sub> Analog Supply Current | I <sub>A_ON</sub>  | $EN = high, V_A = V_{LDOIN}$                             |       | 350 | 450   | μA    |  |  |  |

| V <sub>L</sub> Supply Voltage        | VL                 |                                                          | +1.62 |     | +5.5  | V     |  |  |  |

| V <sub>L</sub> Supply Current        | ΙL                 | All logic inputs static, held at logic-low or logic-high |       | 2.5 | 5     | μA    |  |  |  |

# **High-Accuracy 12-/16-Cell Measurement AFEs**

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_P = +65V, DGND = AGND, V_L = V_{EN} = +3.3V, V_A = +5V, C_{SAMPLE} = 1\mu F, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                  | SYMBOL                 | CONDITIONS                                            | MIN   | ТҮР  | MAX    | UNITS |  |

|------------------------------------------------------------|------------------------|-------------------------------------------------------|-------|------|--------|-------|--|

| V <sub>P</sub> UVLO                                        | UV_V <sub>PVTH</sub>   | V <sub>P</sub> rising                                 |       |      | +6     | V     |  |

| UVLO Hysteresis                                            | UV_V <sub>PHYST</sub>  |                                                       |       | 200  |        | mV    |  |

| LDOIN UVLO                                                 | UV_LDOIN <sub>VT</sub> | V <sub>LDOIN</sub> rising                             | +5.25 |      | +6     | V     |  |

| V <sub>A</sub> UVLO                                        | UV_V <sub>AVTH</sub>   | V <sub>A</sub> rising                                 |       |      | +4.7   | V     |  |

| V <sub>L</sub> UVLO                                        | UV_V <sub>LVTH</sub>   | V <sub>L</sub> rising                                 |       |      | +1.6   | V     |  |

| LDO Output Voltage                                         | V <sub>A_LDO_OUT</sub> | $0 < I_{LOAD} < 10 mA$                                | +4.75 | +5   | +5.25  | V     |  |

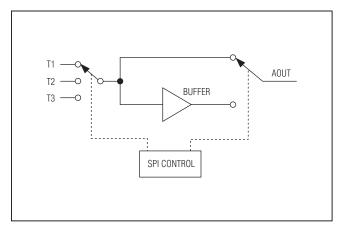

| ANALOG INPUTS (T1, T2, T3)                                 | <u>.</u>               |                                                       |       |      |        |       |  |

| Input Signal Range                                         | VT                     | Reference to AGND                                     | 0     |      | VA     | V     |  |

| On-Resistance                                              | R <sub>ONA</sub>       |                                                       |       |      | 200    | Ω     |  |

| Insuit Lookage Ourrent                                     | 1                      | T_ route to buffer amplifier                          | -1    |      | +1     |       |  |

| Input Leakage Current                                      | IT_LEAK                | T_ route to AOUT                                      | -1    |      | +1     | μA    |  |

| CAPACITOR INPUTS (CT_)                                     | •<br>•                 | -                                                     |       |      |        |       |  |

| Capacitor Discharge Current                                | I <sub>LT_</sub>       | Hold phase, SAMPL = low                               | -1    |      | +1     | μA    |  |

| ANALOG INPUTS (CV_)                                        | ^<br>                  |                                                       |       |      |        |       |  |

| Differential Input Signal Range<br>for Guaranteed Accuracy | V <sub>Dn</sub>        | V <sub>CVn</sub> – V <sub>CVn-1</sub> (Note 3)        | +0.5  |      | +4.5   | V     |  |

| CV1 Input Voltage Range                                    | V <sub>CV1</sub>       |                                                       | 0     |      | +5     | V     |  |

| CV2–CV12 Input Voltage Range<br>(MAX14920)                 | V <sub>CVn</sub>       | $n \ge 2$ , $V_{CVn} \ge V_{CVn-1}$ (Note 3)          | +1.5  |      | +65    | V     |  |

| CV2–CV16 Input Voltage Range<br>(MAX14921)                 | V <sub>CVm</sub>       | $m \ge 2$ , $V_{CVm} \ge V_{CVm-1}$ (Note 3)          | +1.5  |      | +65    | V     |  |

|                                                            | I <sub>LS_</sub>       | During sampling phase                                 | -1    |      | +1     | 1     |  |

|                                                            | I <sub>LH</sub> _      | During holding phase                                  | -1    |      | +10    |       |  |

| Input Leakage Current                                      | I <sub>LC_</sub>       | During calibration                                    | -1    |      | +10    | μA    |  |

|                                                            | I <sub>LD_</sub>       | During diagnostics, DIAG = 1                          |       | 10   |        |       |  |

| Balancing Input Current                                    | I <sub>LB</sub> _      | BA_ active, $V_{CVn} - V_{CVn-1} = +4.5V$<br>(Note 3) |       | 6.5  | 12     | mA    |  |

|                                                            | 5                      | $V_{CVn} > +2V$ , $I_{SINK} = 2mA$ (Note 3)           |       | 80   | 150    | Ω     |  |

| Sample Switch On-Resistance                                | R <sub>SAMPLE</sub>    | $V_{CVn} > +1.5V$ , $I_{SINK} = 1mA$ (Note 3)         |       | 90   |        |       |  |

|                                                            | R <sub>SWCAL</sub>     | $V_{CVn} > +2V$ , $I_{SINK} = 2mA$ (Note 3)           |       | 800  | 16,000 |       |  |

| Cell Undervoltage Threshold                                | UV_V <sub>CVTH</sub>   | An undervoltage sets the associated SPI<br>Cn bit     | +1.4  | +1.5 | +1.6   | V     |  |

| Cell Overvoltage Threshold                                 | OV_V <sub>CVTH</sub>   | An overvoltage sets the associated SPI<br>Cn bit      |       | VA   |        | V     |  |

# **High-Accuracy 12-/16-Cell Measurement AFEs**

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_P = +65V, DGND = AGND, V_L = V_{EN} = +3.3V, V_A = +5V, C_{SAMPLE} = 1\mu F, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                       | SYMBOL                | CONDITIONS                                                                                                              |                      | MIN                   | TYP                                      | MAX                             | UNITS |

|---------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|------------------------------------------|---------------------------------|-------|

| ANALOG OUTPUT (AOUT)            |                       | 1                                                                                                                       |                      | 1                     |                                          |                                 |       |

| Output Signal Range             | V <sub>AOUT</sub>     | Reference to AGND                                                                                                       |                      | +0.3                  |                                          | V <sub>A</sub> - 0.3            | V     |

| Amplifier Offset Voltage        | VOFFSET               | V <sub>AOUT</sub> = +3.3V, after se<br>(Note 5)                                                                         | lf-calibration       |                       | ±50                                      | ±100                            | μV    |

| Temperature Offset Drift        |                       | If not recalibrated                                                                                                     |                      |                       | ±1.5                                     |                                 | µV/°C |

| Gain                            | A_V                   | Gain = $V_{AOUT}/V_D$                                                                                                   |                      |                       | 1                                        |                                 | V/V   |

| Output Error                    | V <sub>O_ERR</sub>    | (Note 4)                                                                                                                |                      | -0.5                  |                                          | +0.5                            | mV    |

| Amplifier Gain Error            | V <sub>GAIN_ERR</sub> | $R_{OUT} = 100 k\Omega$ , $V_D = 2V t$                                                                                  | o 4.5V (Note 6)      | -0.2                  |                                          | +0.2                            | mV    |

| V <sub>P</sub> Monitor Voltage  | VPMON                 | [SC0, SC1, SC2, SC3]<br>= [0, 0, 1, 1]                                                                                  | MAX14920<br>MAX14921 |                       | V <sub>P</sub> /12<br>V <sub>P</sub> /16 |                                 | V     |

| V <sub>P</sub> Monitor Accuracy | V <sub>PMONA</sub>    | [SC0, SC1, SC2, SC3] =<br>[0, 0, 1, 1]                                                                                  |                      | -0.25                 | 0                                        | +2.5                            | %     |

| CHARGE-BALANCE DRIVER           | IS (BA_)              |                                                                                                                         |                      | 1                     |                                          |                                 |       |

| Output Low                      | V <sub>BAL</sub>      | $I_{BA_} = 1mA, V_{CV(n)} - V_{CV(n)}$<br>(Note 3)                                                                      | V(n - 1) = +3.3V     | V <sub>CV(n - 1</sub> | )                                        | V <sub>CV(n - 1)</sub><br>+ 0.9 | V     |

| Output High                     | V <sub>BAH</sub>      | I <sub>BA</sub> = -1mA, V <sub>CV(n)</sub> - V <sub>CV(n - 1)</sub> = +3.3V<br>(Note 3)                                 |                      | V <sub>CV(n)</sub> -  | 1.5                                      | V <sub>CV(n)</sub>              | V     |

| Pulldown Resistance             | R <sub>PDWN</sub>     |                                                                                                                         |                      |                       | 0.65                                     | 0.9                             | kΩ    |

| LOGIC OUTPUT (SDO)              |                       | ÷                                                                                                                       |                      |                       |                                          |                                 |       |

| Output Low Voltage              | V <sub>OL</sub>       | I <sub>SINK</sub> = 10mA                                                                                                |                      |                       |                                          | +0.9                            | V     |

| Output High Voltage             | V <sub>OH</sub>       | I <sub>SOURCE</sub> = 0.5mA                                                                                             |                      | V <sub>L</sub> - 0.25 |                                          |                                 | V     |

| Output Leakage Current          | ١L                    | $V_{\overline{CS}} = V_L$                                                                                               |                      | -1                    |                                          | +1                              | μΑ    |

| LOGIC INPUTS (SDI, SCLK, E      | EN, SAMPL)            |                                                                                                                         |                      |                       |                                          |                                 |       |

| Input Low Voltage               | V                     | V <sub>L</sub> < +2.3V                                                                                                  |                      |                       |                                          | $0.2 \times V_L$                | V     |

| Input Low Voltage               | V <sub>IL</sub>       | $+2.3V < V_{L} < +5.5V$                                                                                                 |                      |                       |                                          | $0.3 \times V_L$                | V     |

| Input High Voltage              |                       | $V_{L} < +2.3V$                                                                                                         |                      | $0.8 \times V_L$      |                                          |                                 | V     |

| input high voltage              | V <sub>HL</sub>       | $+2.3V < V_{L} < +5.5V$                                                                                                 |                      | $0.7 \times V_L$      | .7 x VL                                  |                                 | V     |

| Input Leakage Current           | ۱L                    |                                                                                                                         |                      | -1                    |                                          | +1                              | μΑ    |

| DYNAMIC CHARACTERISTIC          | cs                    |                                                                                                                         |                      |                       |                                          |                                 |       |

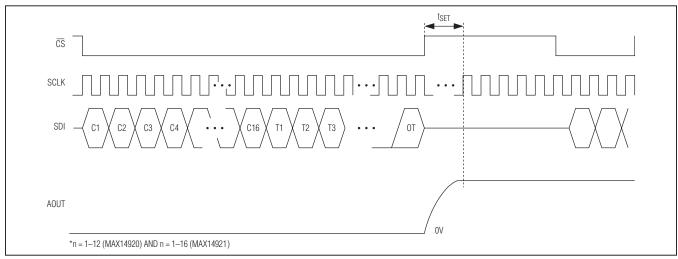

| AOUT Settling Time              | tSET                  | Measured between channels with<br>+4V signal change. Settling to ±1mV<br>accuracy, C <sub>LOAD</sub> = 100pF (Figure 1) |                      |                       | 5                                        |                                 | μs    |

| Sampling Time                   | +-                    | $C_{SAMPLE} = 1 \mu F$                                                                                                  |                      | 4                     |                                          |                                 |       |

| Sampling Time                   | <sup>t</sup> SAMPL    | $C_{SAMPLE} = 1\mu F$ , error calibration                                                                               |                      | 40                    |                                          | ms                              |       |

| Holding Delay Time              | t <sub>HD</sub>       | Delay from SMPLB set to falling edge to holding of                                                                      |                      |                       | 0.5                                      |                                 | μs    |

# **High-Accuracy 12-/16-Cell Measurement AFEs**

### DC ELECTRICAL CHARACTERISTICS (continued)

(V<sub>P</sub> = +65V, DGND = AGND, V<sub>L</sub> = V<sub>EN</sub> = +3.3V, V<sub>A</sub> = +5V, C<sub>SAMPLE</sub> = 1 $\mu$ F, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                    | SYMBOL                                                                                                                                                                                                                        | CONDITIONS                                                                                                           | MIN | ТҮР  | MAX | UNITS |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Level-Shifting Delay Time    | <sup>t</sup> LS_DELAY                                                                                                                                                                                                         | Delay from SMPLB set to 1 or SAMPL falling edge to shifting of all cell voltages to ground and available for reading | 25  |      | 50  | μs    |

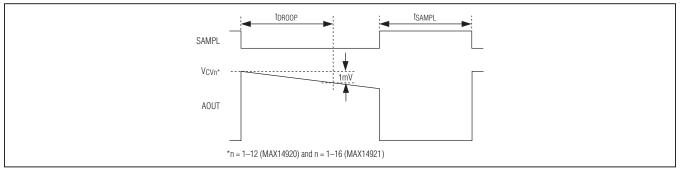

| AOUT Voltage-Droop Time      | t <sub>DROOP</sub>                                                                                                                                                                                                            | Droop to -1mV (Figure 2)                                                                                             | 1   |      |     | ms    |

| T_ Settling Time             | t <sub>TS</sub>                                                                                                                                                                                                               | Measured between T_ input selection<br>and AOUT settling to +1mV accuracy,<br>$C_{LOAD} = 100$ pF, SC2 = 1           |     | 5    |     | μs    |

| T_Turn-On Delay Time         | t <sub>TD</sub>                                                                                                                                                                                                               |                                                                                                                      |     |      | 0.2 | μs    |

| V <sub>P</sub> Settling Time | types $ \begin{array}{c} \text{Measured between V}_{p}/12 \text{ (MAX14920),} \\ V_{p}/16 \text{ (MAX14921) input selection and} \\ \text{AOUT, settling to 2.5\%,} \\ C_{\text{LOAD}} = 100 \text{pF, SC3} = 1 \end{array} $ |                                                                                                                      | 25  | 60   | μs  |       |

| Self-Calibration Time        |                                                                                                                                                                                                                               |                                                                                                                      |     |      | 8   | ms    |

| THERMAL DETECTION            | <u>^</u>                                                                                                                                                                                                                      |                                                                                                                      |     |      |     |       |

| Thermal Shutdown             |                                                                                                                                                                                                                               |                                                                                                                      |     | +140 |     | °C    |

| Thermal-Shutdown Hysteresis  |                                                                                                                                                                                                                               |                                                                                                                      |     | 15   |     | °C    |

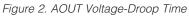

| SPI TIMINGS (Figure 3)       |                                                                                                                                                                                                                               |                                                                                                                      |     |      |     |       |

| SDI to SCLK Setup            | t <sub>DS</sub>                                                                                                                                                                                                               |                                                                                                                      | 50  |      |     | ns    |

| SDI to SCLK Hold             | t <sub>DH</sub>                                                                                                                                                                                                               |                                                                                                                      |     |      | 12  | ns    |

| SCLK to SDO Valid            | t <sub>DO</sub>                                                                                                                                                                                                               |                                                                                                                      |     |      | 100 | ns    |

| CS Fall to SDO Enable        | t <sub>DV</sub>                                                                                                                                                                                                               |                                                                                                                      |     |      | 100 | ns    |

| CS Rise to SDO Disable       | t <sub>TR</sub>                                                                                                                                                                                                               |                                                                                                                      |     |      | 80  | ns    |

| CS Pulse Width               | t <sub>CSW</sub>                                                                                                                                                                                                              |                                                                                                                      | 50  |      |     | ns    |

| CS Fall to SCLK Rise Setup   | t <sub>CSS</sub>                                                                                                                                                                                                              |                                                                                                                      | 100 |      |     | ns    |

| CS Rise to SCLK Rise Hold    | t <sub>CSH</sub>                                                                                                                                                                                                              |                                                                                                                      |     |      | 0   | ns    |

| SCLK High Pulse Width        | tCH                                                                                                                                                                                                                           |                                                                                                                      | 65  |      |     | ns    |

| SCLK Low Pulse Width         | t <sub>CL</sub>                                                                                                                                                                                                               |                                                                                                                      | 65  |      |     | ns    |

| SCLK Period                  | t <sub>CP</sub>                                                                                                                                                                                                               |                                                                                                                      | 208 |      |     | ns    |

**Note 2:** All devices are 100% production tested at  $T_A = +25^{\circ}$ C. Limits over the operating temperature range are guaranteed by design. **Note 3:** Where n = 1-12 (MAX14920) and n = 1-16 (MAX14921).

**Note 5:** Buffer amplifier self-calibrates its offset at power-up and every time it is requested. Due to possible thermal drift after power-up phase, it is suggested to run self-calibration on a regular basis to get best performance (see the *Buffer Amplifier Offset Calibration* section for a detailed explanation).

Note 6: Amplifier error is the sum of all errors including amplifier offset and gain error.

**Note 4:** Output error  $V_{O\_ERR}$  is the difference between the input cell difference voltage ( $V_D = V_{CV(n)} - V_{CV(n - 1)}$ ) and the output voltage  $V_{AOUT}$ . Where n = 1–12 (MAX14920) and n = 1–16 (MAX14921). Output error depends on buffer amplifier errors and parasitic capacitance charge injection error. Since parasitic capacitance error is PCB dependent, output error is guaranteed by design for a sampling capacitor of 1µF and parasitic capacitance less than 2.5pF on CTn (see the *Measurement Accuracy* section for a detailed explanation).

# **High-Accuracy 12-/16-Cell Measurement AFEs**

### **Timing Diagrams**

Figure 1. AOUT Delay from SPI Select

Figure 3. SPI Timing

### **High-Accuracy 12-/16-Cell Measurement AFEs**

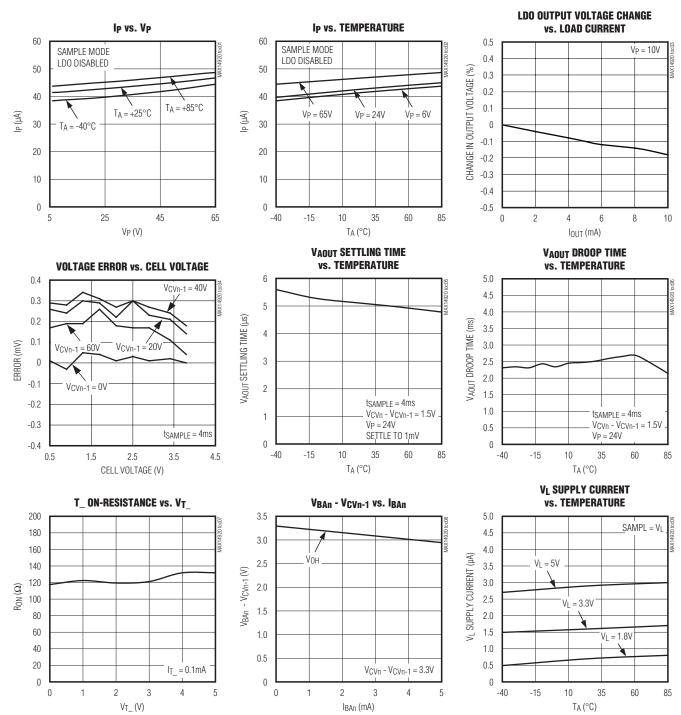

### **Typical Operating Characteristics**

$(V_{CVn} - V_{CV(n-1)} = +3.3V \text{ (where } n = 1-12 \text{ (MAX14920) and } n = 1-16 \text{ (MAX14921)}), T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

Maxim Integrated

# **High-Accuracy 12-/16-Cell Measurement AFEs**

### **Pin Configurations**

# **High-Accuracy 12-/16-Cell Measurement AFEs**

### **Pin Configurations (continued)**

# **High-Accuracy 12-/16-Cell Measurement AFEs**

### **Pin Description**

| PIN                      |                       |                |                                                                                                                                                                                                                                        |  |

|--------------------------|-----------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX14920<br>(64 TQFP-EP) | MAX14921<br>(80 TQFP) | NAME           | FUNCTION                                                                                                                                                                                                                               |  |

| 1                        | 1                     | SCLK           | SPI Clock Input                                                                                                                                                                                                                        |  |

| 2                        | 2                     | SDI            | SPI Data Line Input                                                                                                                                                                                                                    |  |

| 3                        | 3                     | SDO            | SPI Data Line Output                                                                                                                                                                                                                   |  |

| 4                        | 4                     | SAMPL          | Sample Control Input. Voltages at CV_ inputs are tracked when SAMPL is logic-<br>high. When SAMPL transitions from high to low, the differential voltages on CV_ are<br>held internally and made ready for readout at the AOUT output. |  |

| 5                        | 5                     | VL             | Logic Supply Input. Bypass $V_{L}$ to DGND with a 0.1 $\mu F$ capacitor as close as possible to the device.                                                                                                                            |  |

| 6                        | 6                     | DGND           | Digital Ground                                                                                                                                                                                                                         |  |

| 7                        | 7                     | Т3             | Single-Ended Voltage Input. T3 can be connected to a temperature sensor or other analog voltage.                                                                                                                                       |  |

| 8                        | 8                     | T2             | Single-Ended Voltage Input. T2 can be connected to a temperature sensor or other analog voltage.                                                                                                                                       |  |

| 9                        | 9                     | T1             | Single-Ended Voltage Input. T1 can be connected to a temperature sensor or other analog voltage.                                                                                                                                       |  |

| 10                       | 10                    | AOUT           | Buffered Amplifier Output                                                                                                                                                                                                              |  |

| 11                       | 11                    | AGND           | Analog Ground. AGND is a low-noise ground. Connect CV0 to AGND. Connect DGND to AGND.                                                                                                                                                  |  |

| 12                       | 12                    | VA             | +5V LDO Output. Bypass $V_A$ to AGND with a $1\mu\text{F}$ capacitor as close as possible to the device.                                                                                                                               |  |

| 13                       | 13                    | LDOIN          | +5V LDO Power Supply. Connect LDOIN to $V_P$ to enable the LDO. Connect LDOIN to $V_A$ to disable the LDO and use an external +5V supply.                                                                                              |  |

| 14                       | 14                    | V <sub>P</sub> | Power Supply. Connect to the highest voltage of the battery cell stack. Bypass $V_P$ to AGND with a $0.1\mu F$ capacitor as close as possible to the device.                                                                           |  |

| 15                       | 31                    | CV12           | Cell Voltage Input 12. Connect CV12 to cell anode/cathode. Connect CV12 to the highest voltage of the battery cell stack if not used.                                                                                                  |  |

| 16                       | 32                    | BA12           | Cell-Balancing Gate Driver Output 12. Connect BA12 to the gate of the external n-channel FET. Leave BA12 unconnected if not used.                                                                                                      |  |

| 17                       | 33                    | CT12           | Sampling Capacitor 12 High Terminal. CT12 internally connects to CV12 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT12 and CB12. Leave CT12 unconnected if not used.                                                |  |

| 18                       | 34                    | CB12           | Sampling Capacitor 12 Low Terminal. CB12 internally connects to CV11 when SAMPL is logic-high. Connect a 1µF capacitor between CT12 and CB12. Leave CB12 unconnected if not used.                                                      |  |

| 19                       | 35                    | CV11           | Cell Voltage Input 11. Connect CV11 to cell anode/cathode. Connect CV12 to the highest voltage of the battery cell stack if not used.                                                                                                  |  |

| 20                       | 36                    | BA11           | Cell-Balancing Gate Driver Output 11. Connect BA11 to the gate of the external n-channel FET. Leave BA11 unconnected if not used.                                                                                                      |  |

# **High-Accuracy 12-/16-Cell Measurement AFEs**

#### PIN NAME **FUNCTION** MAX14920 MAX14921 (64 TQFP-EP) (80 TQFP) Sampling Capacitor 11 High Terminal. CT11 internally connects to CV11 when 37 CT11 SAMPL is logic-high. Connect a 1µF capacitor between CT11 and CB11. Leave 21 CT11 unconnected if not used. Sampling Capacitor 11 Low Terminal. CB11 internally connects to CV10 when 22 38 CB11 SAMPL is logic-high. Connect a 1µF capacitor between CT11 and CB11. Leave CB11 unconnected if not used. Cell Voltage Input 10. Connect CV10 to cell anode/cathode. Connect CV10 to the CV10 23 39 highest voltage of the battery cell stack if not used. Cell-Balancing Gate Driver Output 10. Connect BA10 to the gate of the external BA10 24 40 n-channel FET. Leave BA10 unconnected if not used. Sampling Capacitor 10 High Terminal. CT10 internally connects to CV10 when 25 41 CT10 SAMPL is logic-high. Connect a 1µF capacitor between CT10 and CB10. Leave CT10 unconnected if not used. Sampling Capacitor 10 Low Terminal. CB10 internally connects to CV9 when CB10 SAMPL is logic-high. Connect a 1µF capacitor between CT10 and CB10. Leave 26 42 CB10 unconnected if not used. Cell Voltage Input 9. Connect CV9 to cell anode/cathode. Connect CV9 to the 27 43 CV9 highest voltage of the battery cell stack if not used. Cell-Balancing Gate Driver Output 9. Connect BA9 to the gate of the external 28 BA9 44 n-channel FET. Leave BA9 unconnected if not used. Sampling Capacitor 9 High Terminal. CT9 internally connects to CV9 when CT9 SAMPL is logic-high. Connect a 1µF capacitor between CT9 and CB9. Leave CT9 29 45 unconnected if not used. Sampling Capacitor 9 Low Terminal. CB9 internally connects to CV8 when SAMPL is logic-high. Connect a 1µF capacitor between CT9 and CB9. Leave CB9 CB9 30 46 unconnected if not used. Cell Voltage Input 8. Connect CV8 to cell anode/cathode. Connect CV8 to the CV8 31 47 highest voltage of the battery cell stack if not used. Cell-Balancing Gate Driver Output 8. Connect BA8 to the gate of the external BA8 32 48 n-channel FET. Leave BA8 unconnected if not used. Sampling Capacitor 8 High Terminal. CT8 internally connects to CV8 when 33 49 CT8 SAMPL is logic-high. Connect a 1µF capacitor between CT8 and CB8. Leave CT8 unconnected if not used. Sampling Capacitor 8 Low Terminal. CB8 internally connects to CV7 when 34 50 CB8 SAMPL is logic-high. Connect a 1µF capacitor between CT8 and CB8. Leave CB8 unconnected if not used. Cell Voltage Input 7. Connect CV7 to cell anode/cathode. Connect CV7 to the 35 51 CV7 highest voltage of the battery cell stack if not used.

### **Pin Description (continued)**

# **High-Accuracy 12-/16-Cell Measurement AFEs**

### **Pin Description (continued)**

| PIN                      | PIN                   |      |                                                                                                                                                                                   |  |

|--------------------------|-----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX14920<br>(64 TQFP-EP) | MAX14921<br>(80 TQFP) | NAME | FUNCTION                                                                                                                                                                          |  |

| 36                       | 52                    | BA7  | Cell-Balancing Gate Driver Output 7. Connect BA7 to the gate of the external n-channel FET. Leave BA7 unconnected if not used.                                                    |  |

| 37                       | 53                    | CT7  | Sampling Capacitor 7 High Terminal. CT7 internally connects to CV7 when SAMPL is logic-high. Connect a $1\mu F$ capacitor between CT7 and CB7. Leave CT7 unconnected if not used. |  |

| 38                       | 54                    | CB7  | Sampling Capacitor 7 Low Terminal. CB7 internally connects to CV6 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT7 and CB7. Leave CB7 unconnected if not used.  |  |

| 39                       | 55                    | CV6  | Cell Voltage Input 6. Connect CV6 to cell anode/cathode. Connect CV6 to the highest voltage of the battery cell stack if not used.                                                |  |

| 40                       | 56                    | BA6  | Cell-Balancing Gate Driver Output 6. Connect BA6 to the gate of the external n-channel FET. Leave BA6 unconnected if not used.                                                    |  |

| 41                       | 57                    | CT6  | Sampling Capacitor 6 High Terminal. CT6 internally connects to CV6 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT6 and CB6. Leave CT6 unconnected if not used. |  |

| 42                       | 58                    | CB6  | Sampling Capacitor 6 Low Terminal. CB6 internally connects to CV7 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT6 and CB6. Leave CB6 unconnected if not used.  |  |

| 43                       | 59                    | CV5  | Cell Voltage Input 5. Connect CV5 to cell anode/cathode. Connect CV5 to the highest voltage of the battery cell stack if not used.                                                |  |

| 44                       | 60                    | BA5  | Cell-Balancing Gate Driver Output 5. Connect BA5 to the gate of the external n-channel FET. Leave BA5 unconnected if not used.                                                    |  |

| 45                       | 61                    | CT5  | Sampling Capacitor 5 High Terminal. CT5 internally connects to CV5 when SAMPL is logic-high. Connect a $1\mu F$ capacitor between CT5 and CB5. Leave CT5 unconnected if not used. |  |

| 46                       | 62                    | CB5  | Sampling Capacitor 5 Low Terminal. CB5 internally connects to CV4 when SAMPL is logic-high. Connect a $1\mu F$ capacitor between CT5 and CB5. Leave CB5 unconnected if not used.  |  |

| 47                       | 63                    | CV4  | Cell Voltage Input 4. Connect CV4 to cell anode/cathode. Connect CV4 to the highest voltage of the battery cell stack if not used.                                                |  |

| 48                       | 64                    | BA4  | Cell-Balancing Gate Driver Output 4. Connect BA4 to the gate of the external n-channel FET. Leave BA4 unconnected if not used.                                                    |  |

| 49                       | 65                    | CT4  | Sampling Capacitor 4 High Terminal. CT4 internally connects to CV4 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT4 and CB4. Leave CT4 unconnected if not used. |  |

| 50                       | 66                    | CB4  | Sampling Capacitor 4 Low Terminal. CB4 internally connects to CV3 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT4 and CB4. Leave CB4 unconnected if not used.  |  |

# **High-Accuracy 12-/16-Cell Measurement AFEs**

### **Pin Description (continued)**

| PIN                      |                       |      |                                                                                                                                                                                                   |  |  |

|--------------------------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX14920<br>(64 TQFP-EP) | MAX14921<br>(80 TQFP) | NAME | FUNCTION                                                                                                                                                                                          |  |  |

| 51                       | 67                    | CV3  | Cell Voltage Input 3. Connect CV3 to cell anode/cathode. Connect CV3 to the highest voltage of the battery cell stack if not used.                                                                |  |  |

| 52                       | 68                    | BA3  | Cell-Balancing Gate Driver Output 3. Connect BA3 to the gate of the external n-channel FET. Leave BA3 unconnected if not used.                                                                    |  |  |

| 53                       | 69                    | CT3  | Sampling Capacitor 3 High Terminal. CT3 internally connects to CV3 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT3 and CB3. Leave CT3 unconnected if not used.                 |  |  |

| 54                       | 70                    | CB3  | Sampling Capacitor 3 Low Terminal. CB3 internally connects to CV2 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT3 and CB3. Leave CB3 unconnected if not used.                  |  |  |

| 55                       | 71                    | CV2  | Cell Voltage Input 2. Connect CV2 to cell anode/cathode. Connect CV2 to the highest voltage of the battery cell stack if not used.                                                                |  |  |

| 56                       | 72                    | BA2  | Cell-Balancing Gate Driver Output 2. Connect BA2 to the gate of the external n-channel FET. Leave BA2 unconnected if not used.                                                                    |  |  |

| 57                       | 73                    | CT2  | Sampling Capacitor 2 High Terminal. CT2 internally connects to CV2 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT2 and CB2. Leave CT2 unconnected if not used.                 |  |  |

| 58                       | 74                    | CB2  | Sampling Capacitor 2 Low Terminal. CB2 internally connects to CV1 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT2 and CB2. Leave CB2 unconnected if not used.                  |  |  |

| 59                       | 75                    | CV1  | Cell Voltage Input 1. Connect CV1 to cell anode/cathode.                                                                                                                                          |  |  |

| 60                       | 76                    | BA1  | Cell-Balancing Gate Driver Output 1. Connect BA1 to the gate of the external n-channel FET. Leave BA1 unconnected if not used.                                                                    |  |  |

| 61                       | 77                    | CT1  | Sampling Capacitor Connection 1 High Terminal. CT1 internally connects to CV1 when SAMPL is logic-high. Connect a $1\mu$ F capacitor between CT1 and CV0. Leave CT1 unconnected if not used.      |  |  |

| 62                       | 78                    | CV0  | Cell Voltage Input 0. Connect CV0 to AGND.                                                                                                                                                        |  |  |

| 63                       | 79                    | EN   | Enable Input. Drive EN low to put the device into shutdown mode and reset the SPI registers. The +5V LDO remains active in the shutdown mode. Drive EN high for normal operation.                 |  |  |

| 64                       | 80                    | CS   | SPI Chip-Select Input. Active low.                                                                                                                                                                |  |  |

|                          | 15                    | CV16 | Cell Voltage Input 16. Connect CV16 to cell anode/cathode. Connect CV16 to the highest voltage of the battery cell stack if not used.                                                             |  |  |

|                          | 16                    | BA16 | Cell-Balancing Gate Driver Output 16. Connect BA16 to the gate of the external n-channel FET. Leave BA16 unconnected if not used.                                                                 |  |  |

| _                        | 17                    | CT16 | Sampling Capacitor Connection 16 High Terminal. CT16 internally connects to CV16 when SAMPL is logic-high. Connect $a1\mu$ F capacitor between CT16 and CB16. Leave CT16 unconnected if not used. |  |  |

# **High-Accuracy 12-/16-Cell Measurement AFEs**

#### PIN NAME **FUNCTION** MAX14920 MAX14921 (64 TQFP-EP) (80 TQFP) Sampling Capacitor Connection 16 Low Terminal. CB16 internally connects to CV15 CB16 when SAMPL is logic-high. Connect a 1µF capacitor between CT16 and CB16. 18 Leave CB16 unconnected if not used. Cell Voltage Input 15. Connect CV15 to cell anode/cathode. Connect CV15 to the CV15 19 highest voltage of the battery cell stack if not used. Cell-Balancing Gate Driver Output 15. Connect BA15 to the gate of the external BA15 20 n-channel FET. Leave BA15 unconnected if not used. Sampling Capacitor Connection 15 High Terminal. CT15 internally connects to CT15 CV15 when SAMPL is logic-high. Connect a 1µF capacitor between CT15 and 21 CB15. Leave CT15 unconnected if not used. Sampling Capacitor Connection 15 Low Terminal. CB15 internally connects to CV14 22 CB15 when SAMPL is logic-high. Connect a 1µF capacitor between CT15 and CB15. Leave CB15 unconnected if not used. Cell Voltage Input 14. Connect CV14 to cell anode/cathode. Connect CV14 to the 23 CV14 highest voltage of the battery cell stack if not used. Cell-Balancing Gate Driver Output 14. Connect BA14 to the gate of the external 24 BA14 n-channel FET. Leave BA14 unconnected if not used. Sampling Capacitor Connection 14 High Terminal. CT14 internally connects to 25 CT14 CV14 when SAMPL is logic-high. Connect a 1µF capacitor between CT14 and CB14. Leave CT14 unconnected if not used. Sampling Capacitor Connection 14 Low Terminal. CB14 internally connects to CV13 CB14 when SAMPL is logic-high. Connect a 1µF capacitor between CT14 and CB14. 26 Leave CB14 unconnected if not used. Cell Voltage Input 13. Connect CV13 to cell anode/cathode. Connect CV13 to the 27 CV13 highest voltage of the battery cell stack if not used. Cell-Balancing Gate Driver Output 13. Connect BA13 to the gate of the external 28 BA13 n-channel FET. Leave BA13 unconnected if not used. Sampling Capacitor Connection 13 High Terminal. CT13 internally connects to CV13 when SAMPL is logic-high. Connect a 1µF capacitor between CT13 and 29 CT13 CB13. Leave CT13 unconnected if not used. Sampling Capacitor Connection 13 Low Terminal. CB13 internally connects to CV12

Leave CB13 unconnected if not used.

Exposed Pad (MAX14920 Only). Connect EP to AGND.

when SAMPL is logic-high. Connect a 1µF capacitor between CT13 and CB13.

### **Pin Description (continued)**

\_\_\_\_

30

\_

CB13

EΡ

### **High-Accuracy 12-/16-Cell Measurement AFEs**

### **Detailed Description**

The MAX14920/MAX14921 analog front-end devices are used in multicell battery measurement systems to monitor primary/secondary battery packs up to 16 cells/+65V (max). The devices perform the signal conditioning required for enabling accurate cell voltage measurement. Both devices simultaneously sample all cell voltages, allowing accurate state-of-charge and source-resistance determination, even under transient load current conditions. The cell voltage measurements are shifted down to ground reference with unity gain, simplifying external ADC data conversion. The devices enable passive cell balancing through drivers that control external discharge FETs.

A high-accuracy, low-offset amplifier buffers differential voltages up to +5V for monitoring of the common rechargeable cell technologies such as lithium-ion (Li+). The resulting cell measurement errors from the devices are below  $\pm 0.5mV$  (max). The devices' high accuracy make them ideal for monitoring cell chemistries with very flat discharge curves, such as a lithium-metal phosphate cell. Diagnostics detect open-wire and short conditions, and warn about overvoltage/undervoltage.

The SPI interface is used for control and monitoring through a host controller. The SPI interface is daisy-chainable. Both devices can operate with a minimum of +6V total stack voltage (typically equating to 3 cells).

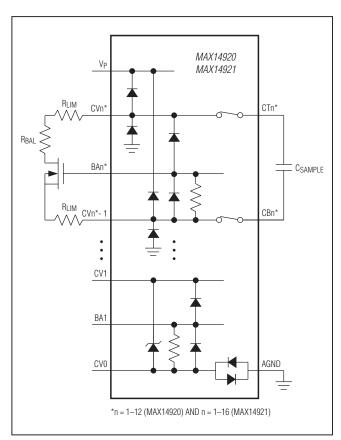

#### **Voltage Sampling**

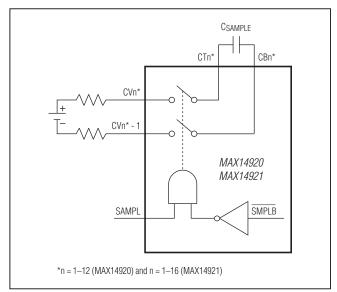

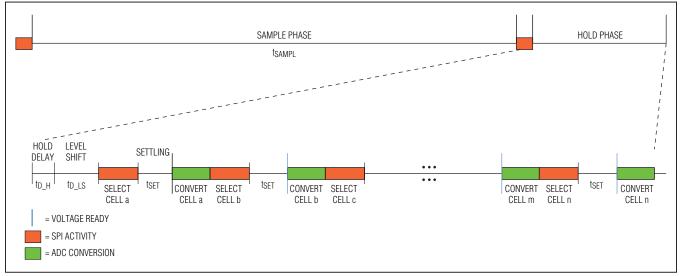

The voltages of all cells are tracked by the sampling capacitors connected between the CTn and CBn pins (where n = 1-12 (MAX14920) and n = 1-16 (MAX14921)), while the SMPLB bit is set to 0 and the SAMPL input is driven high (Figure 4). When the SMPLB bit is set to 1, and the SAMPL input transitions low, all cell voltages are simultaneously sampled on their associated capacitors. The voltages are held by the capacitors while the SMPLB bit is 1, or the SAMPL pin is held low. When sample and holding is controlled by the SAMPL input, set the SMPLB bit to 0. When sample and hold is controlled by the SAMPL pin thigh.

In sample phase selecting any cell voltage (ECS = 1), AOUT equals V<sub>P</sub>/12 (MAX14920) or V<sub>P</sub>/16 (MAX14921).

Resistors can be placed in series with the CV\_ inputs to filter transients and/or for protection. Consider the switches' on-resistance of  $150\Omega$  (max) when calculating

the filter and settling times. In the holding phase, each capacitor's voltage can be independently routed to the analog AOUT output under SPI control.

#### **Voltage Readout**

When the SMPLB bit is set high, or when the SAMPL input is driven low, the sampling switches are opened after 0.5µs (typ) and the cell voltages are held on the external sampling capacitors. Within the time of  $t_{LS_DELAY} < 50$ µs (max), the capacitors' voltages are all shifted to ground reference. Then the undervoltage/overvoltage monitoring of all cells is valid and the cell voltage is available for sequential readout under SPI control. The SPI control can select the readout of any cell voltages, in any order (Figure 5).

With the ECS bit set to 1, a selected cell's voltage appears at the AOUT output according to the cell selection (as defined by the SC\_ cell select bits). A low-leakage, low-noise, low-offset amplifier buffers the capacitor charge and provides the high-accuracy AOUT analog output. After a settling time of t<sub>SET</sub>, from the rising edge of the  $\overline{CS}$  signal, the voltage is available at AOUT with specified accuracy. An ADC can then sample and convert the AOUT voltage. The AOUT output voltage droops over time due to capacitor discharge. The droop time for 1mV of change is larger than t<sub>DROOP</sub> (> C<sub>SAMPLE</sub>/I<sub>CT LEAK</sub>).

Figure 4. Voltage Sampling

### **High-Accuracy 12-/16-Cell Measurement AFEs**

Figure 5. SPI Control Cells Voltage Readout

#### **Measurement Accuracy**

The accuracy of cell voltage monitoring (i.e., the difference of the AOUT voltage relative to the cell voltages) is determined by three factors:

- 1) Held voltage droop due to leakage on the CT\_ pins

- 2) Internal buffer amplifier's voltage errors

- 3) Capacitive level-shifting circuit error

The CT\_ leakage (1 $\mu$ A, max) is a current that mainly comes from the CV\_ pin and increases with temperature.

Neglecting the PCB leakage across the sampling capacitance, the voltage drift error is given by:

$$V_{\text{ERR\_LEAK}} = \frac{I_{\text{CT\_LEAK}}}{C_{\text{SAMPLE}}} \times t_{\text{READOUT}}$$

where:

C<sub>SAMPLE</sub> is the sampling capacitance

I<sub>CT LEAK</sub> is the leakage current on the CT\_ pin

$\ensuremath{\mathsf{t}_{\mathsf{READOUT}}}$  is the delay between hold starts and read-out of the cell voltage

For example, with 1µF sampling capacitors and an ADC conversion rate > 20kHz,  $V_{ERR\_LEAK}$  is less than 1mV. Cells with a higher common-mode voltage have a higher leakage. To reduce the voltage drift over time, start sequential voltage readout from the highest cell in the stack first.

The buffer amplifier errors are nondeterministic in nature, and vary from chip to chip. They are also affected by temperature. The buffer amplifier offset error can be calibrated out through an internal offset-calibration function. This calibration is automatically performed at power-up. The calibration can also be initiated under SPI control. Due to temperature drifts over time, it is best done on a regular basis. Once the buffer amplifier offset is calibrated out, the total error of the buffer is below 0.3mV. After power-up, if the devices do not calibrate regularly, a temperature offset drift of  $\pm 1.5\mu$ V/°C can occur.

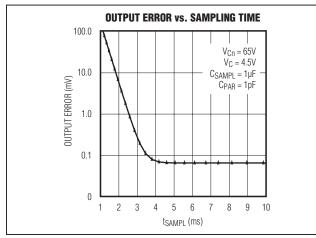

The level shifting is subject to deterministic errors due to charge injection by parasitic PCB-related capacitance on the CT\_ pins. The charge-injected sampling error can be calculated as follows:

$$V_{\text{ERR}_{\text{CHARGE}_{\text{INJECTION}}} = \frac{C_{\text{PAR}}}{C_{\text{SAMPLE}}} \times V_{\text{CTn}} \times \left(\frac{1}{1 - e^{-t_{\text{SAMPL}}/(2R_{\text{SW}} \times C_{\text{SAMPLE}})}\right)$$

where:

$\begin{array}{l} C_{PAR} \text{ is the parasitic capacitance of the CTn pin,} \\ \text{where n = 1-12 (MAX14920) and n = 1-16 (MAX14921)} \\ C_{SAMPLE} \text{ is the sampling capacitor} \\ R_{SW} \text{ is the sampling switch resistance} \\ V_{CTn} \text{ is the voltage of the CTn pin with respect to} \\ AGND, \text{ where n = 1-12 (MAX14920) and n = 1-16} \\ (MAX14921) \\ \end{array}$

tSAMPL is the sampling time

### **High-Accuracy 12-/16-Cell Measurement AFEs**

Figure 6. Charge Injection Sampling Error Voltage for 1pF Parasitic Capacitance

Figure 6 shows the charge-injected sampling error for 1pF of parasitic capacitance in worst-case conditions for a 1 $\mu$ F sampling capacitor.

Minimizing the parasitic capacitance on the CT\_ pins to a few picofarads, with a sampling capacitor of 1 $\mu$ F, is enough to achieve output error below 1mV target. This error can be further reduced by increasing the sampling capacitor value and consequently increasing the sampling time.

Alternatively, if a sampling capacitor lower than  $1\mu$ F or a parasitic capacitance of more than 15pF are present, these errors can be calibrated out to achieve a < 1mV accuracy level through a calibration procedure for each cell. These per-cell errors are simply subtracted from every cell voltage measurement (see the *Parasitic Capacitance Charge Injection Error Calibration* section).

#### Parasitic Capacitance Charge Injection Error Calibration

This calibration is performed with all cells connected to the CV\_ terminals. Setting the [ECS, SC0, SC1, SC2, SC3] bits to [0, 0, 0, 0, 0] configure the devices for parasitic capacitance charge-injection error calibration.

During the sampling phase, every capacitor's terminals are shorted by an internal calibration sampling switch (R<sub>SWCAL</sub> =  $800\Omega$  typ), so that only the parasitic capacitance is charged to the cell's common-mode voltage V<sub>CTn</sub>, where n = 1–12 (MAX14920) and n = 1–16 (MAX14921).

The subsequent cell voltage readout sequence then shows the value of  $V_{\mbox{\scriptsize ERR\_CHARGE\_INJECTION}}$  for

each of the 12/16 cells at AOUT, multiplied by 128. If V<sub>ERR\_CHARGE\_INJECTION</sub> is large enough to affect the required 1mV accuracy, this calibration method provides a measurement of the parasitic capacitance on each CT\_ pin so the microcontroller can use this to correct V<sub>ERR\_INJECTION</sub> in its readings.

Different correction algorithms are possible for the microcontroller using the calibration readout voltages. A simple way to correct cell voltages is to store the ADC data of each cell obtained during calibration (i.e., error values), divided by 128, and subtract these from the subsequently measured cell voltages.

#### **Buffer Amplifier Offset Calibration**

On power-up, the devices automatically go through a self-calibration phase to minimize the internal buffer's offset voltage. In addition, the offset voltage can be calibrated out at any time under host control. Offset calibration is configurable by setting the [ECS, SC0, SC1, SC2, SC3] bits to [0, 1, 0, 0] and is initiated on the low to high CS transition in sampling phase. This offset-calibration procedure takes 8ms to complete. The AOUT output is high impedance during this period. No regular cell voltage measurement can be taken during this time period. However, the SPI operates normally when communicating with other devices (e.g., in daisy-chain mode). So as not to affect calibration, do not take measurement and keep the devices in sample mode (ECS = 0, SC2  $= 0, \overline{SMPLB} = 0$ ). After power-up, if the devices do not calibrate regularly, a temperature offset drift of ±1.5µV/°C can occur.

#### Monitoring Less Than 12/16 Cells

The devices can monitor from 3 (V<sub>P</sub> > +6V) to 12/16 cells (V<sub>P</sub> < +65V). When monitoring less than the maximum number of possible cells per device, connect the most negative cell stack voltage to the bottom of the voltage input string (CV0). The unused CV\_ inputs at the top of the string should be shorted together and connected to V<sub>P</sub>. Leave the unused BA\_, CT\_, and CB\_ pins unconnected.

#### **Reading Total Cell Stack Voltage**

Besides monitoring the individual cell voltages, the devices can monitor the total voltage of the cell stack. An internal resistive voltage-divider between VP and AGND divides the stack voltage by 12 (MAX14920) or 16 (MAX14921). This provides a way to quickly determine the state of the total battery pack, as well as the average voltage of all cells. The settling time of AOUT is 60µs. To

### **High-Accuracy 12-/16-Cell Measurement AFEs**

read out the total cell stack voltage, set the [ECS, SC0, SC1, SC2, SC3] bits to [0, 0, 0, 1, 1]. The total cell stack voltage can be read during the sample or hold phase.

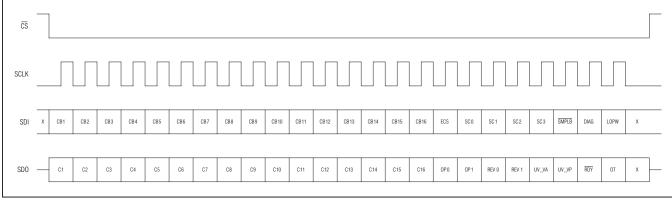

#### **SPI Serial Interface**

Control of the devices is done through a 24-bit SPI interface. The controller sends the serial data to the devices through the SDI input. The devices simultaneously send out monitoring data at the SDO output. This scheme allows daisy-chained operation with other daisy-chainable devices, such as ADC converters. Figure 7 shows the serial bit sequence. CB1 is the first bit expected from the controller and C1 is the first bit that the devices sent to the controller. The SDO data changes on the falling edge of the SCLK signals. The devices sample the SDI data on the rising edge of SCLK.

#### **SPI** Configuration/Control Bits

The configuration/control bits allow enabling of the charge-balance switches, sampling and holding of all the cell voltages, selecting the cell for voltage output, selecting the T\_ input channels, and enabling diagnostics mode. Table 1 describes the bits that the devices receive from the host controller for configuration and control through SDI.

Figure 7. SPI Serial Interface Bits

### Table 1. SPI Configuration/Control Bits

| NAME | BITS | ACCESS | RESET | DESCRIPTION            |     |   |                        |     |     |   |                       |

|------|------|--------|-------|------------------------|-----|---|------------------------|-----|-----|---|-----------------------|

| CB1  | 0    | W      | 0     | 0: Set BA1 output low  |     |   |                        |     |     |   |                       |

| CDI  | 0    | vv     | 0     | 1: Set BA1 output high |     |   |                        |     |     |   |                       |

| CB2  | 1    | W      | 0     | 0: Set BA2 output low  |     |   |                        |     |     |   |                       |

| UD2  | I    | vv     | 0     | 1: Set BA2 output high |     |   |                        |     |     |   |                       |

| CB3  | 2    | W      | 0     | 0: Set BA3 output low  |     |   |                        |     |     |   |                       |

| CDS  | 2    | VV     | 0     | 1: Set BA3 output high |     |   |                        |     |     |   |                       |

| CB4  | 3    | W      | 0     | 0: Set BA4 output low  |     |   |                        |     |     |   |                       |

| CB4  | 3    | VV     | 0     | 1: Set BA4 output high |     |   |                        |     |     |   |                       |

| CB5  | 4    | W      | 4 W   | 4 W                    | 4 W | 4 | 10/                    | 14/ | 14/ | 0 | 0: Set BA5 output low |

| CBD  | 4    |        |       |                        |     | 0 | 1: Set BA5 output high |     |     |   |                       |

| CB6  | 5    | W      | 0     | 0: Set BA6 output low  |     |   |                        |     |     |   |                       |

| CDO  | 5    | VV     | 0     | 1: Set BA6 output high |     |   |                        |     |     |   |                       |

| CB7  | 6    | W      | 0     | 0: Set BA7 output low  |     |   |                        |     |     |   |                       |

|      | 0    | VV     | 0     | 1: Set BA7 output high |     |   |                        |     |     |   |                       |

| CB8  | 7    | W      | 0     | 0: Set BA8 output low  |     |   |                        |     |     |   |                       |

|      | 1    | VV     | 0     | 1: Set BA8 output high |     |   |                        |     |     |   |                       |

# **High-Accuracy 12-/16-Cell Measurement AFEs**

| NAME  | BITS     | ACCESS | RESET | DESCRIPTION                                                                                                                                                                                                    |  |

|-------|----------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 000   | 0        | DAM    |       | 0: Set BA9 output low                                                                                                                                                                                          |  |

| CB9   | 8        | R/W    | 0     | 1: Set BA9 output high                                                                                                                                                                                         |  |

|       | 9        |        | 0     | 0: Set BA10 output low                                                                                                                                                                                         |  |

| CB10  | 9        | R/W    | 0     | 1: Set BA10 output high                                                                                                                                                                                        |  |

| CB11  | 10       | R/W    | 0     | 0: Set BA11 output low                                                                                                                                                                                         |  |

| CDII  | 10       | n/vv   | 0     | 1: Set BA11 output high                                                                                                                                                                                        |  |

| CB12* | 11       | R/W    | 0     | 0: Set BA12 output low                                                                                                                                                                                         |  |

| CDIZ  | 11       | n/ VV  | U     | 1: Set BA12 output high                                                                                                                                                                                        |  |

| CB13* | 12       | R/W    | 0     | 0: Set BA13 output low                                                                                                                                                                                         |  |

| CDIS  | 12       | n/ VV  | U     | 1: Set BA13 output high                                                                                                                                                                                        |  |

| CB14* | 13 R/W 0 |        | 0     | 0: Set BA14 output low                                                                                                                                                                                         |  |

| 0014  | 15       | 11/00  | 0     | 1: Set BA14 output high                                                                                                                                                                                        |  |

| CB15* | 14       | R/W    | 0     | 0: Set BA15 output low                                                                                                                                                                                         |  |

| 0015  | 14       | 11/00  | 0     | 1: Set BA15 output high                                                                                                                                                                                        |  |

| CB16* | 15       | R/W    | 0     | 0: Set BA16 output low                                                                                                                                                                                         |  |

| CDIO  | 10       | 11/00  | 0     | 1: Set BA16 output high                                                                                                                                                                                        |  |

| ECS   | 16       | R/W    | 0     | 0: Cell selection is disabled                                                                                                                                                                                  |  |

| L03   | 10       | 11/00  | 0     | 1: Cell selection is enabled                                                                                                                                                                                   |  |

| SC0   | 17       | R/W    | 0     | [ECS, SC0, SC1, SC2, SC3]<br>1 – SC0, SC1, SC2, SC3: Selects the cell for voltage readout during hold phase.**<br>The selected cell voltage is routed to AOUT after the rising CS edge. See Table 2.           |  |

| SC1   | 18       | R/W    | 0     | 0 - 0, 0, 0, 0: AOUT is three-stated and sampling switches are configured for parasitic capacitance error calibration.<br>0 - 1, 0, 0, 0: AOUT is three-stated and self-calibration of buffer amplifier offset |  |