### **DS1683**

## **Total-Elapsed-Time and Event Recorder with Alarm**

### **General Description**

The DS1683 is an integrated elapsed-time recorder containing a factory-calibrated, low-temperature-coefficient RC time base that eliminates the need for an external crystal. Using EEPROM technology to maintain data in the absence of power, the DS1683 requires no backup power source. The DS1683 detects and records the number of falling edge transitions on the EVENT pin as well as the total cumulative time that the EVENT pin is held high. The ALARM pin alerts the user when the total time accumulated equals or exceeds the user-programmed alarm value, or when the total number of events equals or exceeds the user-programmed alarm value. The polarity of the open-drain ALARM pin can be programmed to either drive low or become high impedance upon an alarm condition. The DS1683 is ideal for applications that monitor the total amount of time that a device has been in operation and/or the number of uses since inception service, repair, or last calibration.

### **Applications**

High-Temp, Rugged, Industrial Applications Where Vibration or Shock Could Damage a Quartz Crystal Any System Where Time-of-Use is Important to

Track

Power-on-Time Recorder

### **Benefits and Features**

- ♦ Records the Total Time the EVENT Input Has Been Active High and Number of Events (Falling Edges of EVENT) That Have Occurred

- ♦ 32-Bit, Nonvolatile, Elapsed Time Counter (ETC) Monitors Event Duration with Quarter Seconds Resolution and Provides 34 Years of Total Time Accumulation

- ♦ Nonvolatile 16-Bit Event Counter Records the Number of Falling Edges Seen by the EVENT Pin

- ◆ Calibrated, Low-Temperature-Coefficient RC Time Base

- ♦ 16 Bytes of User EEPROM

- **♦ Password Protection Scheme (4 Bytes)**

- ♦ I2C-Compatible Interface

- ♦ +2.5V to +5.5V Operating Voltage Range

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to <a href="https://www.maximintegrated.com/DS1683.related">www.maximintegrated.com/DS1683.related</a>.

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)                               | Maximum Junction Temperature+150°C         |

|-----------------------------------------------------------------|--------------------------------------------|

| Voltage Range on V <sub>CC</sub> , ALARM, SDA, SCL0.5V to +6.0V | Operating Temperature Range40°C to +85°C   |

| Voltage Range on EVENT0.5V to (V <sub>CC</sub> + 0.5V),         | Programming Temperature Range 0°C to +70°C |

| not to exceed +6.0V                                             | Storage Temperature Range55°C to +150°C    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )           | Lead Temperature (soldering, 10s)+300°C    |

| SO (derate 5.9mW/°C above +70°C)470.6mW                         | Soldering Temperature (reflow)+260°C       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                   | SYMBOL           | CONDITIONS | MIN                      | TYP MAX                     | UNITS |

|-----------------------------|------------------|------------|--------------------------|-----------------------------|-------|

| Supply Voltage              | V <sub>CC</sub>  | (Note 1)   | 2.5                      | 5.5                         | V     |

| Input Logic 1 (SCL, SDA)    | V <sub>IH</sub>  |            | 0.7 x V <sub>CC</sub>    | V <sub>CC</sub> + 0.3       | V     |

| Input Logic 0 (SCL, SDA)    | V <sub>IL</sub>  |            | -0.3                     | 0.3 x V <sub>CC</sub>       | V     |

| EVENT Input Trip Point      | V <sub>ETP</sub> |            | 0.3 x<br>V <sub>CC</sub> | 0.5 x 0.7 x V <sub>CC</sub> | V     |

| EVENT Trip Point Hysteresis | V <sub>HYS</sub> |            | 1% of V <sub>C</sub> (   | 0                           |       |

| Power-On Reset              | V <sub>POR</sub> |            |                          | 2.4                         | V     |

### DC ELECTRICAL CHARACTERISTICS

( $V_{CC}$  = 2.5V to 5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted.)

| PARAMETER                             | SYMBOL           | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------------------------|------------------|------------|-----|-----|-----|-------|

| Input Leakage                         | ILI              |            | -1  |     | +1  | μΑ    |

| ALARM Output (I <sub>OL</sub> = 10mA) | V <sub>OL</sub>  |            |     |     | 0.8 | V     |

| SDA Output (I <sub>OL</sub> = 4mA)    | V <sub>OL</sub>  |            |     |     | 0.4 | V     |

| Active Supply Current                 | I <sub>CCA</sub> | (Note 1)   |     | 180 | 300 | μΑ    |

| EEPROM Write Current                  | I <sub>EE</sub>  | (Note 1)   |     | 250 | 350 | μΑ    |

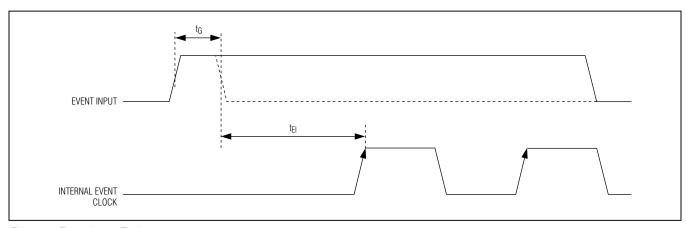

#### **EVENT TIMING**

(V<sub>CC</sub> = 2.5V to 5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted.)

| PARAMETER            | SYMBOL          | CONDITIONS | MIN   | TYP | MAX   | UNITS |

|----------------------|-----------------|------------|-------|-----|-------|-------|

| Time Event Minimum   | t <sub>G</sub>  | (Note 1)   | 10    | 35  | 70    | ms    |

| Time Event Increment | t <sub>EI</sub> | (Note 1)   | 237.5 | 250 | 262.5 | ms    |

| Time Event Max       | t <sub>EM</sub> | (Note 2)   |       |     | 34    | Years |

| CLR ALM to Alarm Set |                 | (Note 2)   | 10    |     | 150   | μs    |

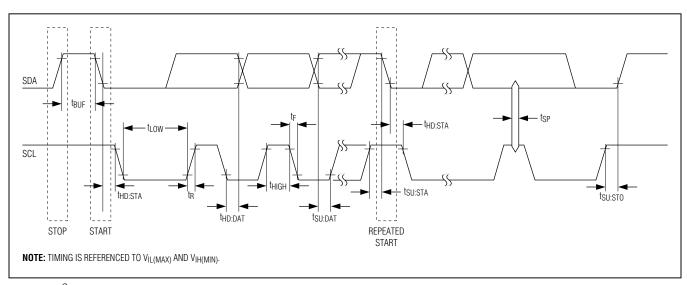

#### I<sup>2</sup>C AC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = 2.5V to 5.5V, T<sub>A</sub> = -40°C to +85°C, timing referenced to V<sub>IL(MAX)</sub> and V<sub>IH(MIN)</sub>, unless otherwise noted.) (Figure 7)

| PARAMETER                                       | SYMBOL              | CONDITIONS      | MIN                       | TYP | MAX | UNITS |

|-------------------------------------------------|---------------------|-----------------|---------------------------|-----|-----|-------|

| SCL Clock Frequency                             | f <sub>SCL</sub>    |                 |                           |     | 400 | kHz   |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>    |                 | 1.3                       |     |     | μs    |

| Hold Time (Repeated) START Condition            | <sup>t</sup> HD:STA |                 | 0.6                       |     |     | μs    |

| Low Period of SCL                               | t <sub>LOW</sub>    |                 | 1.3                       |     |     | μs    |

| High Period of SCL                              | tHIGH               |                 | 0.6                       |     |     | μs    |

| Data Hold Time                                  | t <sub>HD:DAT</sub> |                 | 0                         |     | 0.9 | μs    |

| Data Setup Time                                 | t <sub>SU:DAT</sub> |                 | 100                       |     |     | ns    |

| START Setup Time                                | t <sub>SU:STA</sub> |                 | 0.6                       |     |     | μs    |

| SDA and SCL Rise Time                           | t <sub>R</sub>      | (Note 3)        | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA and SCL Fall Time                           | t <sub>F</sub>      | (Note 3)        | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| STOP Setup Time                                 | t <sub>SU:STO</sub> |                 | 0.6                       |     |     | μs    |

| SDA and SCL Capacitive Loading                  | СВ                  | (Note 3)        |                           |     | 400 | pF    |

| EEPROM Write Time                               | t <sub>W</sub>      | (Notes 4, 5, 6) |                           | 10  | 20  | ms    |

#### NONVOLATILE MEMORY CHARACTERISTICS

$(V_{CC} = 2.5V \text{ to } 5.5V, \text{ unless otherwise noted.})$

| PARAMETER                     | SYMBOL | CONDITIONS                            | MIN     | MAX | UNITS  |

|-------------------------------|--------|---------------------------------------|---------|-----|--------|

| EEPROM Write Cycles           |        | $T_A = +70^{\circ}C \text{ (Note 7)}$ | 50,000  |     | Writes |

| EEPROM Write Cycles (4 Banks) |        | $T_A = +70$ °C (Note 8)               | 200,000 |     | Writes |

- Note 1: All voltages are referenced to ground. Currents entering the IC are specified as positive; currents exiting the IC are specified as negative.

- Note 2: Guaranteed by design.

- Note 3:  $C_B$ : Total capacitance of one bus line in pF.

- Note 4: EEPROM write time begins after a STOP condition occurs.

- Note 5: A decoupling capacitor to supply high instantaneous currents during EEPROM writes is recommended. A typical value is 0.01μF. V<sub>CC</sub> must be maintained above V<sub>CC(MIN)</sub>, including transients, during EEPROM writes.

- Note 6: V<sub>CC</sub> must be at or above 2.5V for t<sub>W</sub> after the end of an event to ensure data transfer to the EEPROM.

- Note 7: Memory locations to which this specification applies: User Memory, ETC Alarm Limit, Event Counter Alarm Limit, Configuration, Password Value.

- Note 8: Memory locations to which this specification applies: Event Counter register, ETC register.

## **DS1683**

## **Total-Elapsed-Time and Event Recorder with Alarm**

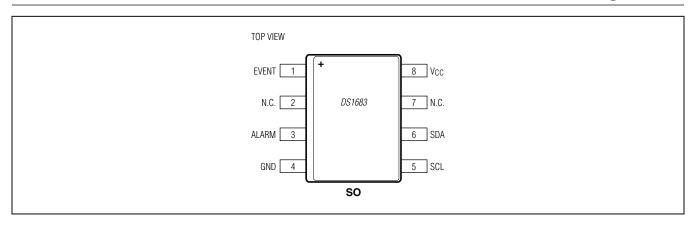

### **Pin Configuration**

### **Pin Description**

| PIN  | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                     |

|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | EVENT           | Event Input. The EVENT pin controls when the values in the Elapsed Time Counter (ETC) register and the Event Counter register are incremented. The EVENT pin also determines when the data in these registers is stored to EEPROM.                                                                                                                           |

| 2, 7 | N.C.            | No Connection. These pins are not connected internally.                                                                                                                                                                                                                                                                                                      |

| 3    | ALARM           | Alarm Output. The ALARM pin is an open drain structure, and is set active when an alarm condition is met. The active state of this pin is controlled by the ALRM POL bit located in the Configuration register. Once the ALARM pin is active, it will remain active until the alarm condition is cleared and the CLR ALM bit in the Command register is set. |

| 4    | GND             | Ground                                                                                                                                                                                                                                                                                                                                                       |

| 5    | SCL             | I <sup>2</sup> C Serial-Clock Input. The SCL pin is the serial-clock input for the I <sup>2</sup> C synchronous communications channel. The SCL pin is an input that requires an external pull-up resistor.                                                                                                                                                  |

| 6    | SDA             | I <sup>2</sup> C Serial-Data Input/Output. The SDA pin is the data input/output signal for the I <sup>2</sup> C synchronous communications channel. The SDA pin is an open-drain I/O, which requires an external pullup resistor.                                                                                                                            |

| 8    | V <sub>CC</sub> | +2.5V to +5.5V Input Supply                                                                                                                                                                                                                                                                                                                                  |

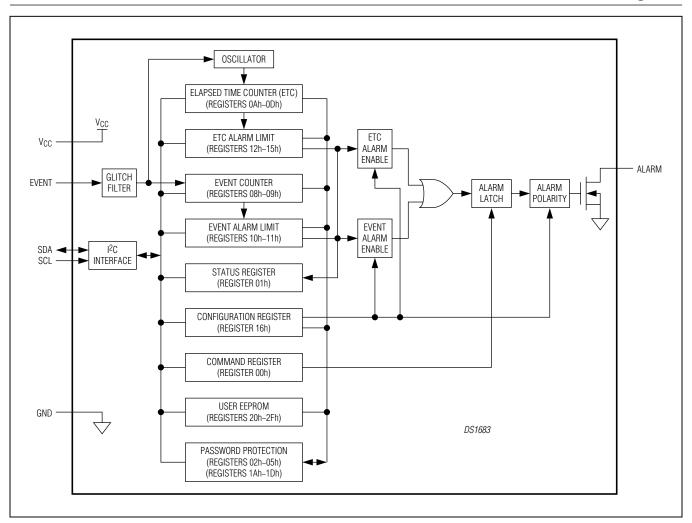

### **Block Diagram**

### **Detailed Description**

The DS1683 is an elapsed-time recorder that tracks the accumulated time the EVENT pin has been held high as well as the number of falling edge transitions seen by the EVENT pin. The main application is to track the accumulated on-time and number of power cycles of a device or system. Programmable alarm limits for both the accumulated on-time and number of falling edges of the EVENT pin are available so that the user can be alerted when these conditions are met. The accumulated elapsed time that the EVENT pin has been held high is stored in the 4-byte Elapsed Time Counter (ETC) register. The

number of times the EVENT pin sees a falling transition is stored in the 2-byte Event Counter register. The DS1683 includes password protection to prevent tampering with accumulated values, alarm limits, configuration settings, and user memory values.

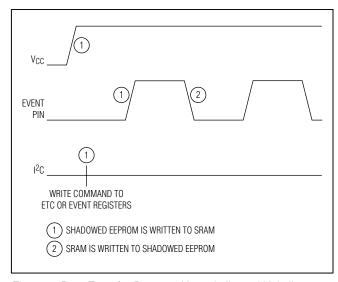

The ETC, ETC Alarm Limit, Event Counter, Event Counter Alarm Limit, Configuration, Password, and User Memory values are stored in shadowed EEPROM. On power-up, the values in the ETC and Event Counter are loaded into SRAM locations. When the state of the EVENT pin causes changes to the accumulated time and number of events, it is these SRAM registers that are incremented.

When the contents of the ETC and Event Counter registers match or exceed their programmable alarm limits, the ALARM pin can be driven to its active state as set by the polarity bit, ALRM POL, located in the Configuration register. Each of the alarm limits has an enable bit that should be used to determine whether or not the ALARM pin should be activated when the alarm conditions are met.

The DS1683 has an internal, low-temperature-coefficient, RC-based oscillator that is started on power-up. The DS1683 uses this RC time base to increment the ETC register in 250ms increments while the EVENT pin is held high. When the EVENT pin is driven low, the ETC register ceases to increment.

#### **EVENT Pin**

The DS1683 monitors the state of the EVENT pin to determine when an event occurs. When the pin is pulled high, the ETC and Event Counter values are transferred from shadowed EEPROM to SRAM. While the EVENT pin is held high, the value of the ETC SRAM begins incrementing once every 250ms. Incrementing the ETC SRAM value while EVENT is high allows the device to increment the ETC value without contributing to EEPROM wear out. When the EVENT pin falls to a logic 0, the Event Counter SRAM value increments by a value of one. Also at this time the ETC stops accumulating time. The values of the EVENT and ETC Counter SRAM locations are then stored in the ETC and EVENT Shadowed EEPROM array. The EVENT input is deglitched (t<sub>G</sub>) to prevent short noise spikes from triggering an event.

While the EVENT pin is high, the I<sup>2</sup>C bus is unavailable for write commands, though read commands can still be executed. When the EVENT pin transitions low, I<sup>2</sup>C communication is unavailable for t<sub>W</sub> (EEPROM write time), after which I<sup>2</sup>C writes are possible. However, if an I<sup>2</sup>C write operation is underway, and the EVENT pin transitions low to high, this operation is interrupted so that the ETC and Event Counter registers can be updated. So it is important to terminate all I<sup>2</sup>C write transactions before transitioning the level on the EVENT pin.

An I<sup>2</sup>C read command can be performed regardless of the state of the EVENT pin. On a low-to-high transition of the EVENT pin, the I<sup>2</sup>C read command is allowed to complete. However, it is strongly recommended that all I<sup>2</sup>C communication be terminated before transitioning the level on the EVENT pin.

When the EVENT pin is high and the device detects a START signal on the I<sup>2</sup>C bus, a snapshot of the data

in the ETC and Event Counter SRAM is made available on the I<sup>2</sup>C bus. When the EVENT pin is low and the device detects a START signal on the I<sup>2</sup>C bus, data is transferred from the ETC and Event Counter shadowed EEPROM bank memory.

# Elapsed Time Counter (ETC) Register

The Elapsed Time Counter (ETC) register is a 32-bit value that holds time in quarter-second resolution. The ETC register consists of 4 bytes of memory in the memory map. Once the counter reaches FFFFFFFFh, counting stops. The ETC register is backed by 4 banks of shadowed EEPROM, which allow for 200k+ write cycles to occur before a wearout condition. When an I<sup>2</sup>C read occurs while the EVENT pin is high, a snapshot of the value from the ETC SRAM is made available for the I<sup>2</sup>C bus. When the EVENT pin is logic 0, I<sup>2</sup>C reads take data from the shadowed EEPROM ETC bank memory.

On power-on reset (POR), the ETC value stored in the shadowed EEPROM bank memory is loaded into the ETC SRAM location (Figure 1). This also happens when a low-to-high transition occurs on the EVENT pin, or when an I<sup>2</sup>C write to the ETC register occurs. When data is written to the ETC register, the value is stored in the shadowed EEPROM bank memory and also in the corresponding ETC SRAM location. This data is transferred after the STOP of the I<sup>2</sup>C command.

Figure 1. Data Transfer Between Nonvolatile and Volatile Memory Types

On the falling edge of the EVENT signal, the contents of the ETC SRAM counter are written to the ETC shadowed EEPROM registers.

When the EVENT pin is low, the ETC register can be written by the I<sup>2</sup>C bus. For example, when it comes time to reset the time stored in the ETC register, an I<sup>2</sup>C write command can be issued to set all the bits to 0.

#### **ETC Alarm Register**

The ETC Alarm register is a 32-bit value and contains the value that is compared to the accumulated ETC value. When a nonzero value is programmed into the ETC Alarm register, the ETC alarm function is enabled and the DS1683 compares the value in the ETC SRAM counter with the programmed value in the ETC Alarm register. When the ETC SRAM Counter matches or exceeds the alarm value, the ETC alarm flag (ETC AF) is set.

**Note:** To disable the ETC alarm function, program the ETC Alarm register to a value of all 0s. An alarm value of all 0s disables the ETC alarm function.

### **Event Counter Register**

This 16-bit Event Counter stores the number of falling edges seen on the EVENT pin. Once the Event Counter reaches a value of FFFFh, event counting stops. The Event Counter register is backed by four banks of shadowed EEPROM, which allow for 200k+ write cycles occur before a wearout condition. When an I<sup>2</sup>C read occurs when the EVENT pin is high, a snapshot of the value from the Event Counter SRAM is made available for the I<sup>2</sup>C bus. When the EVENT pin is logic 0, I<sup>2</sup>C reads take data from the shadowed EEPROM Event Counter bank memory.

On POR, the Event Counter value stored in shadowed EEPROM bank memory is loaded into the Event Counter SRAM location. This also happens when a low-to-high transition occurs on the EVENT pin, or when an I<sup>2</sup>C write to the Event Counter register occurs. When data is written to the Event Counter register, the value is stored in the shadowed EEPROM bank memory, and also in the corresponding Event Counter SRAM location. This data is transferred after the STOP of the I<sup>2</sup>C command.

On the falling edge of the EVENT signal, the Event Counter SRAM register is incremented by a value of one,

and the contents of the Event Counter SRAM are written to the Event Counter shadowed EEPROM.

When the EVENT pin is low, the Event Counter register can be written by the I<sup>2</sup>C bus. For example, when it comes time to reset the accumulated number of events in the Event Counter register, an I<sup>2</sup>C write command can be issued to set all of the bits to 0.

### **Event Counter Alarm Register**

The Event Counter Alarm register is a 16-bit register, and contains the value that is compared to the accumulated Event Counter value. When a nonzero value is programmed into the Event Counter Alarm register, the Event Counter alarm function is enabled, and the DS1683 compares the value in the Event Counter SRAM with the programmed value in the EVENT Alarm register. When the Event Counter SRAM value matches or exceeds the alarm value, the Event Counter alarm flag (EVENT AF) is set.

**Note:** To disable the Event Counter alarm function, program the Event Counter Alarm register to a value of all 0s. An alarm value of all 0s disables the Event Counter alarm function.

### **Alarm Output**

The ALARM pin is an open-drain structure, and setting the alarm polarity bit (ALRM POL) located in the Configuration register determines if the ALARM output is active high or active low (default is active low). The DS1683 monitors the values in the ETC and Event Counter registers and compares them to the values in the ETC and Event Counter Alarm registers. When the ETC and Event Counter values match or exceed their corresponding alarm values, their alarm flags (EVENT AF and ETC AF, located in the Status register) are set to a value of 1, indicating an alarm condition. If the corresponding Enable bits (ETC ALRM EN and EVENT ALRM EN, located in the Configuration register) are active, then the ALARM output is driven to its active state and is latched.

Once the alarm condition has been cleared, the corresponding alarm flag (EVENT AF and/or ETC AF) automatically clears. Once the actual alarm condition is cleared, the CLR ALM bit must be used to clear an active ALARM pin state. If the alarm condition is still present when the CLR ALM bit is toggled, the ALARM simply reactivates and latches.

### **Event Logging**

When the DS1683 is powered up, the internal oscillator starts; the ETC and Event Counter values, which are recorded in the shadowed EEPROM bank memory, are transferred to the ETC and Event Counter SRAM locations; and the device waits for an event (rising edge of the EVENT signal). When an event triggers the input by transitioning the EVENT pin from a low to a high level, the following occur:

- 1) The ETC and Event Counter values are once again transferred from shadowed EEPROM bank memory to their SRAM counter locations.

- 2) After the glitch filtering and t<sub>EI</sub>, the ETC SRAM counter value increments. See <u>Figure 2</u> for timing. An event greater than time event minimum (t<sub>G</sub>) but less than t<sub>EI</sub> (i.e., a low-high-low transition on EVENT < t<sub>EI</sub>) increments the Event Counter SRAM value but not the ETC SRAM value

- 3) The ETC SRAM value increments every t<sub>EI</sub>. The ETC SRAM counter holds time in quarter-second resolution.

- 4) When the EVENT pin goes low, the Event Counter SRAM value increments by one, the ETC SRAM counter stops incrementing, and the values from the ETC and Event Counter SRAM locations are transferred to their Shadowed EEPROM counterparts. The I<sup>2</sup>C bus is not available for t<sub>W</sub>.

The ETC value does not roll over when FFFFFFFh, or approximately 34 years, is reached. The Event Counter

value does not roll over when reaching a value of FFFFh. While the EVENT pin is high, I<sup>2</sup>C write commands are ignored, though I<sup>2</sup>C read commands are still possible.

#### **Password Protection**

From the factory, the DS1683 powers up without password protection enabled. The intent is to provide a manufacturer an optional security feature to protect the Configuration register, Alarm registers, User EEPROM, ETC and Event Counter settings, and the Password Value (PWV). The customer is not able to alter the Configuration register, Alarm registers, ETC or Event Counter, User EEPROM or Password Value settings if the password conditions are not met.

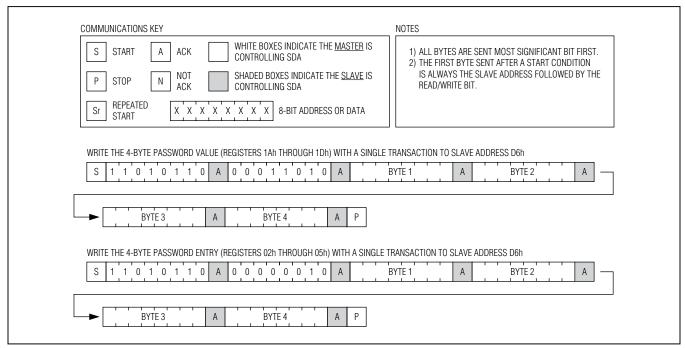

The DS1683 password is stored in the 4-byte readonly Password Value register, located at 1Ah–1Dh. The default value for this register is FFFFFFFh. To change this value, a 4-byte I<sup>2</sup>C write command must be issued. The 4 bytes of the new password must be issued with the same I<sup>2</sup>C write command. Once the STOP of the I<sup>2</sup>C write command is issued, the Password Value register is updated with the new 4-byte value.

The Password Entry bytes (PWE) are where the user enters the 4-byte password to unlock access to the DS1683's EEPROM locations. When writing the PWE value, the user must issue a 4-byte I<sup>2</sup>C write command starting at location 02h. This 4-byte value must match the 4-byte Password Value stored in registers 1Ah–1Dh.

Figure 2. Event Input Timing

Figure 3. Password Value and Password Entry I<sup>2</sup>C Examples

If the Password Value has been changed from the factory default setting, the user has to enter this new password value into the PWE registers after a power cycle in order to unlock the memory again.

See Figure 3 for examples of writing the 4-byte Password Value and the 4-byte Password Entry value.

### **User Memory**

The DS1683 has 16 bytes of user-programmable, EEPROM memory. User memory is set to read-only if the correct password is not entered into the Password Entry Bytes. If the correct password is entered into the Password Entry Bytes, the data can be written to the User Memory and stored in EEPROM with the correct I<sup>2</sup>C write command.

**Table 1. Register Memory Map**

| ADDRESS | READ/WRITE  | NAME                            | VOLATILE/<br>NONVOLATILE | FACTORY<br>DEFAULT/POWER-<br>UP DEFAULT | PASSWORD<br>PROTECTION | FUNCTION                                  |

|---------|-------------|---------------------------------|--------------------------|-----------------------------------------|------------------------|-------------------------------------------|

| 00h     | Read/Write  | COMMAND                         | V                        | 00h                                     | No                     | Command<br>Register                       |

| 01h     | Read        | STATUS                          | V                        | 00h                                     | No                     | Status Register                           |

| 02h-05h | Read*/Write | PWE                             | V                        | FFh                                     | No                     | Password Entry<br>Registers               |

| 06h–07h | _           | RSVD                            | _                        | _                                       | _                      | Reserved                                  |

| 08h-09h | Read/Write  | EVENT REG                       | NV                       | 00h                                     | Yes                    | Event Counter<br>Registers                |

| 0Ah-0Dh | Read/Write  | ETC REG                         | NV                       | 00h                                     | Yes                    | ETC Registers                             |

| 0Eh-0Fh | _           | RSVD                            | _                        | _                                       | _                      | Reserved                                  |

| 10h–11h | Read/Write  | EVENT<br>COUNTER<br>ALARM LIMIT | NV                       | 00h                                     | Yes                    | Event Counter<br>Alarm Limit<br>Registers |

| 12h-15h | Read/Write  | ETC ALARM<br>LIMIT              | NV                       | 00h                                     | Yes                    | ETC Alarm Limit<br>Registers              |

| 16h     | Read/Write  | CONFIG                          | NV                       | 00h                                     | Yes                    | Configuration<br>Register                 |

| 17h-19h | _           | RSVD                            | _                        | _                                       | _                      | Reserved                                  |

| 1Ah–1Dh | Read*/Write | PWV                             | NV                       | FFh                                     | Yes                    | Password Value                            |

| 1Eh-1Fh | _           | RSVD                            | _                        | _                                       | _                      | Reserved                                  |

| 20h-2Fh | Read/Write  | USER MEMORY                     | NV                       | 00h                                     | Yes                    | User EEPROM                               |

| 30h-FFh | _           | RSVD                            | _                        | _                                       | _                      | Reserved                                  |

**Note:** *I*<sup>2</sup>*C* reads from memory locations that do not exist report a value of FFh.

V: Volatile (SRAM); NV: Nonvolatile (EEPROM).

<sup>\*</sup>The PWE and PWV bytes read back 0s.

#### **REGISTER 00h: COMMAND REGISTER**

Factory Default/Power-On Value 00h

Read Access All

Write Access All

Memory Type SRAM, Volatile

Memory N/A N/A N/A N/A N/A N/A N/A R/W Access Reserved 00h Reserved Reserved Reserved Reserved Reserved Reserved CLR ALM BIT 7 BIT 0

7:1 Reserved Reserved

Clear Alarm Bit. This bit reads as a 0. Writing this bit to a 1 unlatches the active ALARM output, setting the ALARM pin to its inactive state if the alarm condition is no longer present. If the alarm condition persists, the ALARM pin once again asserts to its active state.

#### **REGISTER 01h: STATUS REGISTER**

Factory Default /Power-On Value 00h

Read Access All

Write Access N/A

Memory Type SRAM, Volatile

Memory N/A N/A N/A R/W R/W R/W R/W R/W Access 01h Reserved Reserved Reserved Reserved Reserved **EVENT EVENT AF** ETC AF BIT 7 BIT 0

7:3 Reserved Reserved 2 **EVENT** This bit indicates the status of the EVENT pin's logic level, detected after the t<sub>G</sub> glitch filter time. Default value = 0. If the value in the Event Counter SRAM value is greater than or equal to the Event Counter Alarm Limit value, then this bit is automatically set to a value of 1 to indicate an ALARM **EVENT AF** event. When the EVENT SRAM Counter value is less than the Event Counter Alarm Limit, this bit automatically set to a value of 0, indicating that there is no EVENT alarm. Default value = 0. If the value in the ETC SRAM value is greater than or equal to the ETC Alarm Limit value, then this bit is automatically set to a value of 1 to indicate an ALARM event. When the ETC ETC AF 0 SRAM value is less than the ETC Alarm Limit, this bit automatically set to a value of 0, indicating that there is no ETC alarm.

#### REGISTERS 02h-05h: PASSWORD ENTRY (PWE)

Factory Default FF FF FF FFh

Read Access N/A; Reads as all 0s

Write Access Al

Memory Type SRAM, Volatile

| Memory<br>Access | R/W | R/W | R/W            | R/W | R/W | R/W            | R/W            | R/W |

|------------------|-----|-----|----------------|-----|-----|----------------|----------------|-----|

| 02h              | 27  | 26  | 2 <sup>5</sup> | 24  | 23  | 2 <sup>2</sup> | 21             | 20  |

| 03h              | 215 | 214 | 213            | 212 | 211 | 210            | 2 <sup>9</sup> | 28  |

| 04h              | 223 | 222 | 221            | 220 | 219 | 218            | 217            | 216 |

| 05h              | 231 | 230 | 229            | 228 | 227 | 226            | 225            | 224 |

BIT 7

There is one 4-byte password for the DS1683. Entering the correct password into the Password Entry (PWE) bytes allows write access to the Event, ETC, Event Counter Alarm Limit, ETC Alarm Limit, Configuration, Password Value, and User Memory registers. This value is write-only, and reads from this location result in all 0s. On power-up, the PWE bits are set to 1 to match the factory default Password Value of all 1s.

#### **REGISTERS 08h-09h: EVENT COUNTER REGISTER**

Factory Default 00 00h

Read Access All

Write Access PW

Memory Type Shadowed EEPROM, Nonvolatile

| Memory<br>Access | R/W             | R/W | R/W            | R/W | R/W | R/W            | R/W            | R/W   |

|------------------|-----------------|-----|----------------|-----|-----|----------------|----------------|-------|

| 08h              | 27              | 26  | 2 <sup>5</sup> | 24  | 23  | 2 <sup>2</sup> | 21             | 20    |

| 09h              | 2 <sup>15</sup> | 214 | 213            | 212 | 211 | 210            | 2 <sup>9</sup> | 28    |

|                  | BIT 7           |     |                |     |     |                |                | BIT 0 |

The Event Counter register is a shadowed EEPROM register that contains the number of times a falling edge of the EVENT pin has occurred. On power-up, on every rising edge of the EVENT pin, and after an I<sup>2</sup>C write to the Event Counter register, the value from the shadowed EEPROM is loaded up into the Event Counter memory (SRAM). It is this memory that is incremented on the falling edge of the EVENT pin. On the falling edge of the EVENT pin, this value in SRAM memory is then written to the shadowed EEPROM memory to store the number of times there has been a falling edge on the EVENT pin.

#### REGISTERS 0Ah-0Dh: ETC REGISTER

Factory Default 00 00 00 00h

Read Access All Write Access PW

Memory Type Shadowed EEPROM, Nonvolatile

| Memory<br>Access | R/W            | R/W | R/W            | R/W | R/W | R/W            | R/W            | R/W |

|------------------|----------------|-----|----------------|-----|-----|----------------|----------------|-----|

| 0Ah              | 2 <sup>7</sup> | 26  | 2 <sup>5</sup> | 24  | 23  | 2 <sup>2</sup> | 21             | 20  |

| 0Bh              | 215            | 214 | 213            | 212 | 211 | 210            | 2 <sup>9</sup> | 28  |

| 0Ch              | 223            | 222 | 221            | 220 | 219 | 218            | 217            | 216 |

| 0Dh              | 231            | 230 | 229            | 228 | 227 | 226            | 225            | 224 |

BIT 0

The ETC register is a shadowed EEPROM register that contains the accumulated time in 250ms increments that the EVENT pin has been held high. On power-up, on every rising edge of the EVENT pin, and after an I<sup>2</sup>C write to the ETC register, the value from the shadowed EEPROM location is loaded into the ETC counter memory (SRAM). When the EVENT pin is high, it is this SRAM memory that is incremented once every 250ms. On the falling edge of the EVENT pin, this value in SRAM memory is then written to the shadowed EEPROM memory to store the accumulated time in 250ms increments.

#### REGISTERS 10h-11h: EVENT COUNTER ALARM LIMIT REGISTER

Factory Default 00 00h

Read Access All

Write Access PW

Memory Type Shadowed EEPROM, Nonvolatile

| Memory<br>Access | R/W   | R/W | R/W | R/W             | R/W | R/W | R/W            | R/W   |

|------------------|-------|-----|-----|-----------------|-----|-----|----------------|-------|

| 10h              | 27    | 26  | 25  | 24              | 23  | 22  | 21             | 20    |

| 11h              | 215   | 214 | 213 | 2 <sup>12</sup> | 211 | 210 | 2 <sup>9</sup> | 28    |

| _                | BIT 7 |     |     |                 |     |     |                | BIT 0 |

The Event Counter Alarm Limit is a shadowed EEPROM register, and when the Event Counter register value equals or exceeds the Event Counter Alarm Limit value, the EVENT flag bit (EVENT AF bit, Register 01h, bit 1) goes active high. When the Event Counter register value drops below the Event Counter Alarm Limit value, the EVENT AF bit automatically clears.

#### **REGISTERS 12h-15h: ETC ALARM LIMIT REGISTER**

Factory Default 00 00 00 00h

Read Access All Write Access PW

Memory Type Shadowed EEPROM, Nonvolatile

| Memory<br>Access | R/W | R/W | R/W            | R/W | R/W            | R/W            | R/W            | R/W |

|------------------|-----|-----|----------------|-----|----------------|----------------|----------------|-----|

| 12h              | 27  | 26  | 2 <sup>5</sup> | 24  | 2 <sup>3</sup> | 2 <sup>2</sup> | 21             | 20  |

| 13h              | 215 | 214 | 213            | 212 | 211            | 210            | 2 <sup>9</sup> | 28  |

| 14h              | 223 | 222 | 221            | 220 | 219            | 218            | 217            | 216 |

| 15h              | 231 | 230 | 229            | 228 | 227            | 226            | 225            | 224 |

BIT 7

The ETC Alarm Limit is a shadowed EEPROM, and when the ETC register value equals or exceeds the ETC Alarm Limit value, the ETC flag bit (ETC AF bit, Register 01h, bit 0) goes active high. When the ETC register value drops below the ETC Alarm Limit value, the EVENT AF bit automatically clears.

#### **REGISTER 16h: CONFIGURATION REGISTER**

Factory Default /Power-On Value 00h

Read Access All

Write Access PW

Memory Type Shadowed EEPROM, Nonvolatile

| Memory<br>Access | N/A      | N/A      | N/A      | R/W      | R/W      | R/W            | R/W              | R/W      |

|------------------|----------|----------|----------|----------|----------|----------------|------------------|----------|

| 01h              | Reserved | Reserved | Reserved | Reserved | Reserved | ETC ALRM<br>EN | EVENT<br>ALRM EN | ALRM POL |

| •                | BIT 7    |          |          |          |          |                |                  | BIT 0    |

| 7:3                                                                                                                                                           | Reserved | Reserved                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| than the ETC Alarm limit, then this device triggers the ETC Alar goes to its active state.  Default value = 0, which is disabled. When set to a 1, and if the |          | Default value = 0, which is disabled. When set to a 1, and if the ETC register is equal to or greater than the ETC Alarm limit, then this device triggers the ETC Alarm Flag (ETC AF), and the ALARM pin goes to its active state.                                 |

|                                                                                                                                                               |          | Default value = 0, which is disabled. When set to a 1, and if the Event Counter register is equal to or greater than the Event Counter Alarm limit, then this device triggers the Event Counter Alarm Flag (EVENT AF), and the ALARM pin goes to its active state. |

| 0                                                                                                                                                             | ALRM POL | Default value = 0, which sets the ALARM output active low. When set to a 1, the ALARM output is active high.                                                                                                                                                       |

#### REGISTERS 1Ah-1Dh: PASSWORD VALUE (PWV)

Factory Default FF FF FF FFh

Read Access N/A; Reads as all 0s

Write Access PW

Memory Type Shadowed EEPROM, Nonvolatile

| Memory<br>Access | R/W            | R/W | R/W            | R/W | R/W | R/W            | R/W            | R/W |

|------------------|----------------|-----|----------------|-----|-----|----------------|----------------|-----|

| 1Ah              | 2 <sup>7</sup> | 26  | 2 <sup>5</sup> | 24  | 23  | 2 <sup>2</sup> | 21             | 20  |

| 1Bh              | 215            | 214 | 213            | 212 | 211 | 210            | 2 <sup>9</sup> | 28  |

| 1Ch              | 223            | 222 | 221            | 220 | 219 | 218            | 217            | 216 |

| 1Dh              | 231            | 230 | 229            | 228 | 227 | 226            | 225            | 224 |

|                  |                |     |                |     |     |                |                |     |

BIT 7

The default value for the four Password Value (PWV) is all 1s (FF FF FF FFh). The intent is to provide a manufacturer with a security feature to protect the Configuration register, Alarm registers, User EEPROM, ETC and Event Counter registers, and the Password Setting (PWV). The customer is not able to alter the Configuration register, Alarm registers, User EEPROM, ETC or Event Counter registers, or Password Setting if the password conditions are not met.

#### REGISTERS 20h-2Fh: USER MEMORY

Factory Default 00h for All Locations

Read Access All Write Access PW

Memory Type EEPROM, Nonvolatile

There are 16 bytes of user-programmable EEPROM memory. User memory is set to read-only if the correct password is not entered into the Password Entry bytes. If the correct password is entered into the Password Entry bytes, the data can be written to the User Memory and stored in EEPROM with the correct I<sup>2</sup>C write command. The User Memory locations can be read regardless of the password protection.

### **Sample Applications**

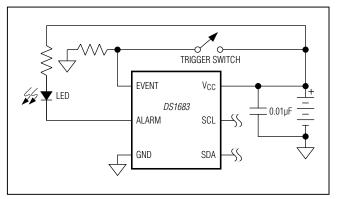

Figure 4 shows the DS1683 measuring total run time and operating from a battery with the ALARM pin connected to an LED. When the trigger switch is closed, the EVENT pin is pulled high and the ETC register begins incrementing. When the trigger switch is opened, the EVENT pin is pulled low by the resistor, the ETC register stops incrementing, the Event Counter register is incremented by one, and the values of both the ETC and Event Counter are stored in shadowed EEPROM. When the ETC or Event Counter alarm conditions are met, the ALARM pin pulls active low (the factory default setting), and current flows through the LED, indicating an alarm condition.

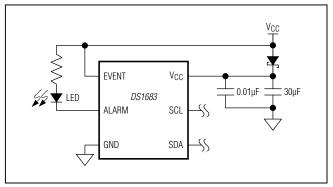

Figure 5 shows the DS1683 in a total time-of-use application where power may be removed at the same time as the end of the event. The  $V_{CC}$  slew rate at power-down is fast with respect to  $t_W$ . A capacitor maintains  $V_{CC}$  on the DS1683 above 2.5V until the EEPROM write completes. A Schottky diode blocks current from the capacitor to other devices connected to  $V_{CC}$ .

The  $V_{CC}$  holding capacitor value of 30µF is calculated using the maximum EEPROM write current and EEPROM write time. This assumes that the  $V_{CC}$  slew rate allows time from EVENT trip point to  $V_{CC}$  at 2.5V on the DS1683 is at least  $t_W$

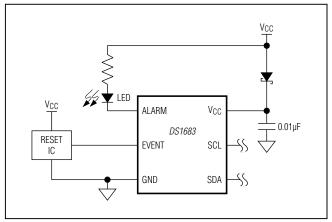

Figure 6 shows the DS1683 in a total time-of-use application with power that can be removed at the same time as the end of the event. In this application, the  $V_{CC}$  slew rate at power-down is slow with respect to  $t_W$ . The external RST IC ends the event as  $V_{CC}$  begins to drop.  $V_{CC}$  must remain above 2.5V until the end of  $t_W$ .

Both circuits in Figure 5 and Figure 6 are read-only because the state of the EVENT pin is tied  $V_{CC}$ . Because the EVENT pin is a logic 1 while  $V_{CC}$  is applied, I<sup>2</sup>C write commands are disabled, thus only I<sup>2</sup>C read commands are possible in these configurations.

Figure 4. Total Run Time

Figure 5. Total Time-of-Use Application with Fast  $V_{CC}$  Slew Rate (Read-Only)

Figure 6. Total Time-of-Use Application with Slow  $V_{CC}$  Slew Rate (Read-Only)

### I<sup>2</sup>C Serial Interface Description

#### **I<sup>2</sup>C** Definitions

The following terminology is commonly used to describe I<sup>2</sup>C data transfers. See <u>Figure 7</u> and the <u>I<sup>2</sup>C AC Electrical Characteristics</u> table for additional information.

**Master Device:** The master device controls the slave devices on the bus. The master device generates SCL clock pulses and START and STOP conditions.

**Slave Devices:** Slave devices send and receive data at the master's request.

**Bus Idle or Not Busy:** Time between STOP and START conditions when both SDA and SCL are inactive and in their logic-high states. Depending on the device, when the bus is idle it initiates a low-power mode for slave devices.

**START Condition:** A START condition is generated by the master to initiate a new data transfer with a slave. Transitioning SDA from high to low while SCL remains high generates a START condition.

**STOP Condition:** A STOP condition is generated by the master to end a data transfer with a slave. Transitioning SDA from low to high while SCL remains high generates a STOP condition.

**Repeated START Condition:** The master can use a repeated START condition at the end of one data transfer to indicate that it will immediately initiate a new data

transfer following the current one. Repeated STARTs are commonly used during read operations to identify a specific memory address to begin a data transfer. A repeated START condition is issued identically to a normal START condition.

**Bit Write:** Transitions of SDA must occur during the low state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL plus the setup and hold time requirements. Data is shifted into the device during the rising edge of the SCL.

**Bit Read:** At the end of a write operation, the master must release the SDA bus line for the proper amount of setup time before the next rising edge of SCL during a bit read. The device shifts out each bit of data on SDA at the falling edge of the previous SCL pulse and the data bit is valid at the rising edge of the current SCL pulse. Remember that the master generates all SCL clock pulses including when it is reading bits from the slave.

Acknowledgement (ACK and NACK): An acknowledgement (ACK) or not-acknowledge (NACK) is always the 9th bit transmitted during a byte transfer. The device receiving data (the master during a read or the slave during a write operation) performs an ACK by transmitting a zero during the 9th bit. A device performs a NACK by transmitting a one (done by releasing SDA) during the 9th bit. Timing (Figure 7) for the ACK and NACK is identical to all other bit writes. An ACK is the acknowledgment that the device is properly receiving

Figure 7. I<sup>2</sup>C Timing Diagram

Figure 8. DS1683 I<sup>2</sup>C Slave Address

data. A NACK is used to terminate a read sequence or as an indication that the device is not receiving data.

**Byte Write:** A byte write consists of 8 bits of information transferred from the master to the slave (most significant bit first) plus a 1-bit acknowledgement from the slave to the master. The 8 bits transmitted by the master are done according to the bit write definition and the acknowledgement is read using the bit read definition.

**Byte Read:** A byte read is an 8-bit information transfer from the slave to the master plus a 1-bit ACK or NACK from the master to the slave. The 8 bits of information that are transferred (most significant bit first) from the slave to the master are read by the master using the bit read definition, and the master transmits an ACK using the bit write definition to receive additional data bytes. The master must NACK the last byte read to terminate communication so the slave returns control of SDA to the master.

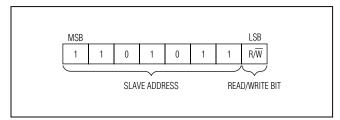

**Slave Address Byte:** Each slave on the  $I^2C$  bus responds to a slave address byte sent immediately following a START condition. The slave address byte contains the slave address in the most significant 7 bits and the  $R/\overline{W}$  bit in the least significant bit.

The DS1683's slave address is D6h (1101 011R $\overline{W}$ , where R/ $\overline{W}$  is 0). When the R/ $\overline{W}$  bit is 0 (such as in D6h), the master is indicating it will write data to the slave. If R/ $\overline{W}$  is set to a 1 (D7h in this case), the master is indicating it wants to read from the slave. See Figure 8.

If an incorrect (nonmatching) slave address is written, the DS1683 assumes the master is communicating with another I<sup>2</sup>C device and ignores the communication until the next START condition is sent.

**Memory Address:** During an I<sup>2</sup>C write operation to the DS1683, the master must transmit a memory address to identify the memory location where the slave is to store the data. The memory address is always the second byte transmitted during a write operation following the slave address byte.

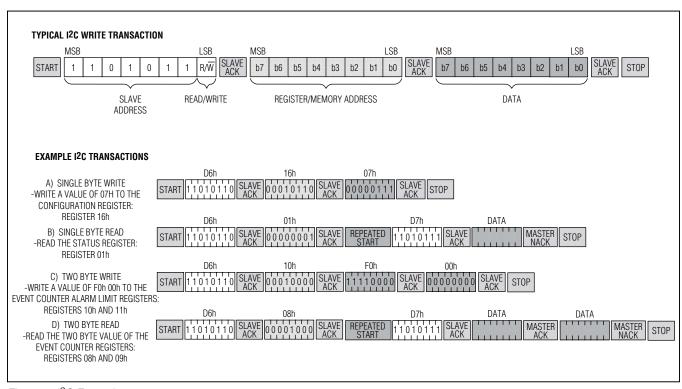

#### I<sup>2</sup>C Communication

Writing a Single Byte to a Slave: The master must generate a START condition, write the slave address byte  $(R\overline{W}=0)$ , write the memory address, write the byte of data, and generate a STOP condition. The master must read the slave's acknowledgement during all byte write operations.

When writing to the DS1683, EEPROM is written following the STOP condition at the end of the write command. To change the setting without changing the EEPROM, terminate the write with a repeated START condition before the next STOP condition occurs. Using a repeated START condition prevents the two delay required for the EEPROM write cycle to finish.

For a write command, data is transferred after receiving a STOP.

Writing Multiple Bytes to a Slave: To write multiple bytes to a slave, the master generates a START condition, writes the slave address byte ( $R/\overline{W} = 0$ ), writes the memory address, writes up to 8 data bytes, and generates a STOP condition. The DS1683 writes 1 to 8 bytes (one page or row) with a single write transaction. This is internally controlled by an address counter that allows data to be written to consecutive addresses without transmitting a memory address before each data byte is sent. The address counter limits the write to one 8-byte page (one row of the memory map). Attempts to write to additional pages of memory without sending a STOP condition between pages result in the address counter wrapping around to the beginning of the present row. For example, a 3-byte write starts at address 06h and writes 3 data bytes (11h, 22h, and 33h) to three "consecutive" addresses. The result is that addresses 06h and 07h would contain 11h and 22h, respectively, and the third data byte, 33h, would be written to address 00h. To prevent address wrapping from occurring, the master must send a STOP condition at the end of the page, then wait for the bus-free or EEPROM write time to elapse. Then the master can generate a new START condition and write the slave address byte ( $R/\overline{W} = 0$ ) and the first memory address of the next memory row before continuing to write data.

**Acknowledge Polling:** Any time a EEPROM byte is written, the DS1683 requires the EEPROM write time (t<sub>W</sub>) after the STOP condition to write the contents of the byte to EEPROM. During the EEPROM write time, the device does not acknowledge its slave address because it is busy. It is possible to take advantage

of this phenomenon by repeatedly addressing the DS1683, which allows communication to continue as soon as the DS1683 is ready. The alternative to acknowledge polling is to wait for a maximum period of tw to elapse before attempting to access the device.

**EEPROM Write Cycles:** The DS1683's EEPROM write cycles are specified in the *Nonvolatile Memory Characteristics* table. The specification shown is at the worst-case temperature (hot). It can handle many additional writes at room temperature.

**Reading a Single Byte from a Slave:** Unlike the write operation that uses the specified memory address byte to define where the data is to be written, the read operation occurs at the present value of the memory address counter. To read a single byte from the slave, the master generates a START condition, writes the slave address byte with  $R/\overline{W}=1$ , reads the data byte with a NACK to indicate the end of the transfer, and generates a STOP condition. However, since requiring the master to keep track of the memory address counter is impractical, the following method should be used to perform reads from a specified memory location.

Manipulating the Address Counter for Reads: A dummy write cycle can be used to force the address counter (or pointer) to a particular value. To do this, the master generates a START condition, writes the slave address byte ( $R\overline{W} = 0$ ), writes the memory address where it desires to read, generates a repeated START condition, writes the slave address byte ( $R\overline{W} = 1$ ),

reads data with ACK or NACK as applicable, and generates a STOP condition. Recall that the master must NACK the last byte to inform the slave that no additional bytes will be read. See <a href="Figure 9">Figure 9</a> for I<sup>2</sup>C communication examples.

Reading Multiple Bytes from a Slave: The read operation can be used to read multiple bytes with a single transfer. When reading bytes from the slave, the master simply ACKs the data byte if it desires to read another byte before terminating the transaction. After the master reads the last byte it must NACK to indicate the end of the transfer and generates a STOP condition.

### **Applications Information**

#### **Power-Supply Decoupling**

To achieve best results, it is recommended that the power supply is decoupled with a  $0.01\mu F$  or a  $0.1\mu F$  capacitor. Use high-quality, ceramic, surface-mount capacitors, and mount the capacitors as close as possible to the  $V_{CC}$  and GND pins to minimize lead inductance.

#### **SDA and SCL Pullup Resistors**

SDA is an open-collector output on the DS1683 that requires a pullup resistor to realize high-logic levels. An I<sup>2</sup>C master using either an open-collector output with a pullup resistor or a push-pull output driver can be used for SCL. Pullup resistor values should be chosen to ensure that the rise and fall times listed in the I<sup>2</sup>C AC Electrical Characteristics are within specification.

Figure 9. I<sup>2</sup>C Examples

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| DS1683S+    | -40°C to +85°C | 8 SO        |

| DS1683S+T&R | -40°C to +85°C | 8 SO        |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. T&R = Tape and reel.

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE | LAND        |

|---------|---------|---------|-------------|

| TYPE    | CODE    | NO.     | PATTERN NO. |

| 8 SO    | S8+4    | 21-0041 |             |

### **Revision History**

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 6/12     | Initial release | _       |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Analog to Digital Converters - ADC category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

ADC0804LCD ADC0808 MCP37211-200I/TE MAX15511TGTL+ MCP3202T-CI/MS ADE1201ACCZ ADE1202ACCZ LTC1090CN

LTC1605IG LTC2238IUH LTC1418AIG LTC1605ACG LTC1605AIG LTC2208IUP ADS1282HPW LTC1297DCN8 LTC1741CFW

MCP3422A0-E/MS MCP3426A2-E/MC MCP3426A3-E/MC MCP3427-E/MF TLC0820ACN TLC2543IN TLV2543IDW

NCD9830DBR2G ADS5231IPAG ADS7807U ADS7891IPFBT ADS8328IBPW AMC1204BDWR ADS7959QDBTRQ1

ADS7955QDBTRQ1 ADS7807UB ADS7805UB ADS1220IPWR MCP3426A0-E/MS MCP3422A0-E/MC AD9220AR MAX11212AEUB+

TLV1570CDW TLC3574IDWR TLC1542IDWR TLC0838CDWR AD7914BRUZ-REEL7 AD977ABRZ ADC12130CIWM/NOPB

MCP3426A1-EMC MCP3426A0-EMC AD7192BRUZ-REEL AD7193BRUZ-REEL