# Integrated Protection IC on a High-Power 12V Bus with an Integrated MOSFET and Lossless Current Sensing

## **General Description**

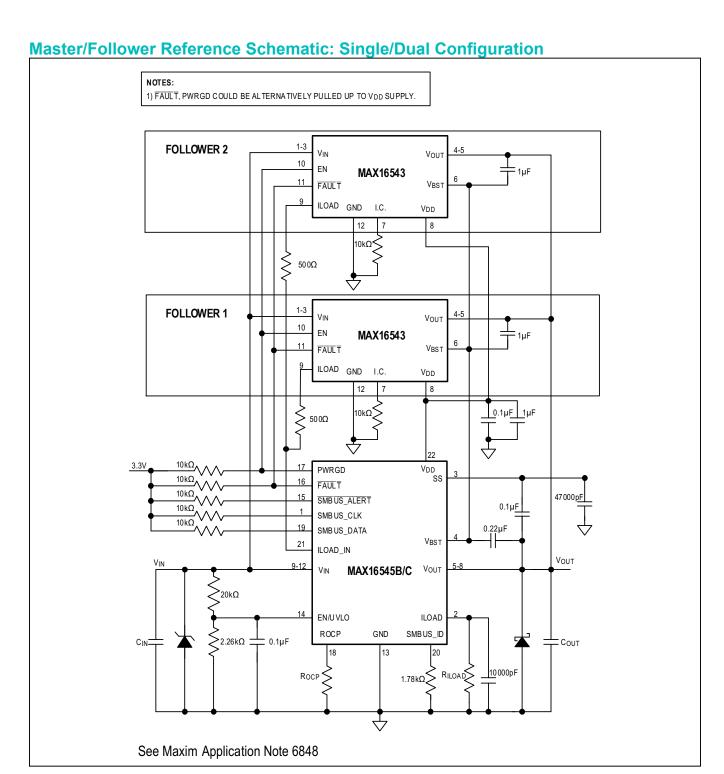

The MAX16543 is an integrated follower protection IC that is used in parallel with a Maxim MAX16545B/MAX16545C master integrated protection IC for distribution, control, monitoring and protection of a system's 12V bus. The MAX16543 increases the current capability of the MAX16545B/MAX16545C. The MAX16545B/MAX16545C provide the reporting and fault protection circuits for the combined chipset. Up to two MAX16543s can be added to a MAX16545B/MAX16545C IC to provide DC current capability of more than 60A. The 1.8V bias supply and gate drive voltage supply of the MAX16543 are powered by the MAX16545B/MAX16545C.

All features of the MAX16545B/MAX16545C remain available when a MAX16543 is added to the circuit. The chipset provides monotonic startup with programmable ramp and delay to limit inrush current during startup. The total current is monitored and reported. Programmable system overcurrent protection is provided with several levels of protection.

The MAX16543 includes Maxim's patented lossless current sense to provide high accuracy current sensing through the MAX16545B/MAX16545C IC. The MAX16543 reports its current to the MAX16545B/MAX16545C, which then reports the total current.

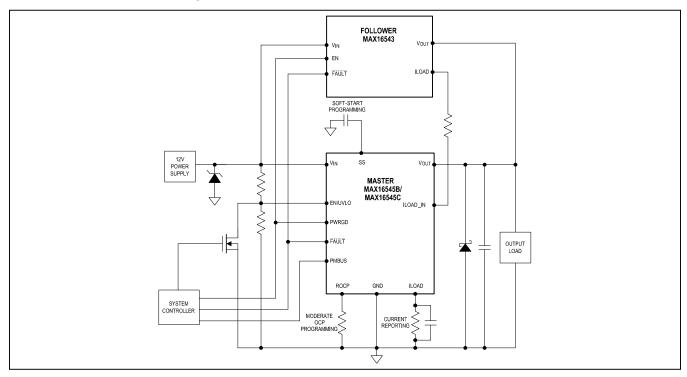

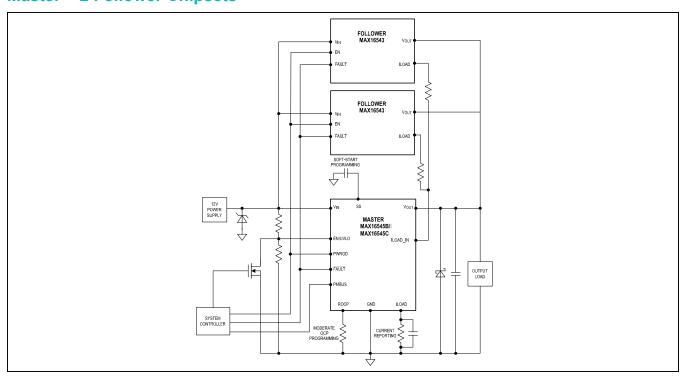

The MAX16543 is controlled entirely by the MAX16545B/MAX16545C IC. The chipset input and output voltage fault protection is provided by the MAX16545B/MAX16545C, which enables and disables the MAX16543 as commanded by circuit conditions and command signals. *Master* + 1 Follower Chipset and Master + 2 Follower Chipsets show the basic application circuits for the master/follower chipset, with single and dual MAX16543s working in tandem to provide higher current ratings than a single MAX16545B/MAX16545C.

## **Benefits and Features**

- Used with the MAX16545B/MAX16545C to Provide Integrated Protection for Loads > 60A On 12V Bus

- High Density: Industry's Smallest Circuit Breaker Solution Provides More Than 75% Board Area Savings

- · 12-Lead QFN Package

- Integrated Power MOSFET with 1.5mΩ Total Resistance in 12V Power Path (R<sub>DS(ON)</sub>, Including Package), Not Including Any Parallel Devices

- Lossless, Precise Total System Current Sensing and Reporting

- PMBus/SMBus Control and Reporting Through the MAX16545B/MAX16545C

- Increases Power-Supply Reliability with IC Self-Protection Features

- · Very Fast Fault Detection and Isolation

- V<sub>IN</sub> to V<sub>OLIT</sub> Short Protection During Startup

- Overtemperature Protection

- Three Levels of Overcurrent Protection (OCP)

- · Programmable Moderate OCP

- Programmable Severe OCP Provides Isolation

5µs

- Fail-Safe Safe OCP Provides Isolation < 250ns</li>

- Modular Design, MAX16545B/MAX16545C with Single or Dual MAX16543 in Parallel Provide Different DC Current Capabilities

- MAX16545B/MAX16545C + 1 MAX16543: 90A DC Capability

- MAX16545B/MAX16545C + 2 MAX16543: 120A DC Capability

## **Systems and Applications**

Servers, Networking, Storage, Communication Equipment and AC/DC Power Supplies

Integrated Protection IC on 12V: Circuit Breaker/ E-Fuse, Hot Swap

Ordering Information appears at end of data sheet.

## **Master + 1 Follower Chipset**

## **Master + 2 Follower Chipsets**

# Integrated Protection IC on a High-Power 12V Bus with an Integrated MOSFET and Lossless Current Sensing

## **Absolute Maximum Ratings**

| Supply Voltage (V <sub>IN</sub> ) DC       | 0.3V to +16V     | Output Voltage (V <sub>OUT</sub> ) DC            | 0.3V to +16V   |

|--------------------------------------------|------------------|--------------------------------------------------|----------------|

| Supply Voltage (V <sub>IN</sub> ) 150µs    | +22V             | V <sub>BST</sub> (Relative to V <sub>OUT</sub> ) | 0.3V to +2.5V  |

| Bias Supply Pin Voltage (V <sub>DD</sub> ) | 0.3V to +2.5V    | Junction Temperature (T <sub>J</sub> )           | +150°C         |

| EN                                         | 0.3V to +5.5V    | Storage Temperature Range                        | 65°C to +165°C |

| FAULT                                      | 0.3V to +5.5V    | Peak Reflow Temperature                          | +260°C         |

| ΙΙ ΟΔΠ                                     | -0 3\/ to +2 5\/ |                                                  |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Operating Ratings**

| Supply Voltage (V <sub>IN</sub> ) | +10.8V to +13.2V | Bias Supply Voltage (V <sub>DD</sub> ) | +1.75V to +1.94V |

|-----------------------------------|------------------|----------------------------------------|------------------|

| EN                                | 0V to +5.5V      | Junction Temperature (T <sub>J</sub> ) | 0°C to +125°C    |

## **Package Information**

## 12 FCQFN

| Package Code                              | P123A4F+2 |

|-------------------------------------------|-----------|

| Outline Number                            | 21-0973   |

| Land Pattern Number                       | 90-0477   |

| THERMAL RESISTANCE                        |           |

| Junction to Case (θ <sub>JC</sub> ) (max) | 0.56°C/W  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

## **Electrical Characteristics**

$(V_{IN} = 12V \pm 10\%$ , unless otherwise specified.  $T_J = 0^{\circ}C$  to +125°C, unless otherwise specified. Specifications are 100% production tested at  $T_A = +32^{\circ}C$ . Limits over operating temperature range are guaranteed by design and characterization.)

| PARAMETER                              | SYMBOL            | CONDITIONS MIN TYP M               |      | MAX  | UNITS |    |  |  |  |

|----------------------------------------|-------------------|------------------------------------|------|------|-------|----|--|--|--|

| 12V SUPPLY (V <sub>IN</sub> )          |                   |                                    |      |      |       |    |  |  |  |

| Supply Voltage Range                   | V <sub>IN</sub>   | (Note 1)                           | 10.8 | 12   | 13.2  | V  |  |  |  |

| Supply Current                         | I <sub>IN</sub>   | FET ON, I <sub>OUT</sub> = 0A      |      | 1.3  | 1.8   | mA |  |  |  |

| 1.8V LINEAR REGULATOR (V               | / <sub>DD</sub> ) |                                    |      |      |       |    |  |  |  |

| Supply Voltage Range                   | $V_{DD}$          | Supplied by the master IC (Note 1) | 1.75 | 1.85 | 1.94  | V  |  |  |  |

| Supply Current                         | I <sub>DD</sub>   | FET ON, I <sub>OUT</sub> = 0A      |      | 1.7  | 2.3   | mA |  |  |  |

| UNDERVOLTAGE LOCKOUT                   | : 1.8V SUPPLY (V  | ( <sub>DD</sub> )                  |      |      |       |    |  |  |  |

| V <sub>DD</sub> UVLO Rising Threshold  |                   |                                    | 1.55 | 1.6  | 1.65  | V  |  |  |  |

| V <sub>DD</sub> UVLO Falling Threshold |                   |                                    | 1.50 | 1.55 | 1.60  | V  |  |  |  |

| V <sub>DD</sub> UVLO Hysteresis        |                   |                                    | 20   | 50   | 80    | mV |  |  |  |

| V <sub>DD</sub> UVLO Response Time     |                   | From below threshold to FET OFF    |      | 2    |       | μs |  |  |  |

## **Electrical Characteristics (continued)**

$(V_{IN} = 12V \pm 10\%$ , unless otherwise specified.  $T_J = 0^{\circ}C$  to +125°C, unless otherwise specified. Specifications are 100% production tested at  $T_A = +32^{\circ}C$ . Limits over operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                       | SYMBOL              | CONDITIONS                                                              | MIN  | TYP | MAX  | UNITS |

|-------------------------------------------------|---------------------|-------------------------------------------------------------------------|------|-----|------|-------|

| BOOST VOLTAGE (V <sub>BST</sub> )               |                     |                                                                         |      |     |      |       |

| Supply Voltage Range                            | V <sub>BST</sub>    | BST voltage above V <sub>OUT</sub> . Supplied by the master IC (Note 1) |      | 1.8 |      | V     |

| UNDERVOLTAGE LOCKOUT                            | (V <sub>BST)</sub>  |                                                                         |      |     |      |       |

| V <sub>BST</sub> UVLO Rising Threshold          |                     |                                                                         | 1.2  | 1.3 | 1.4  | V     |

| V <sub>BST</sub> UVLO Falling Threshold         |                     |                                                                         | 0.9  | 1.1 | 1.3  | V     |

| V <sub>BST</sub> UVLO Hysteresis                |                     |                                                                         | 100  | 170 | 240  | mV    |

| V <sub>BST</sub> UVLO Response Time             |                     | From falling threshold to FET OFF                                       |      | 2   |      | μs    |

| V <sub>BST</sub> UVLO Digital Deglitch          |                     |                                                                         |      | 10  |      | μs    |

| INTEGRATED MOSFET CHAI                          | RACTERISTICS        |                                                                         |      |     |      |       |

| On-Resistance (Including Package Resistance)    | R <sub>DS(ON)</sub> | (Note 1)                                                                |      | 1.5 |      | mΩ    |

| OVERCURRENT PROTECTION                          | N (OCP)             |                                                                         |      |     |      |       |

| MAX16543 Safe OCP<br>Threshold                  | IOCP                | (Notes 2, 3)                                                            | 66   | 76  | 86   | А     |

| MAX16543 Safe OCP Delay                         | IOCP_Delay          | (Note 2)                                                                |      | 250 |      | ns    |

| CURRENT REPORTING (ILO                          | AD)                 |                                                                         |      |     |      | ,     |

| Linear Voltage Range                            |                     | (Note 4)                                                                | 0    |     | 1.35 | V     |

| Linear I <sub>OUT</sub> Reporting Current Range |                     | Current reporting range from a single MAX16543 device                   | 0    |     | 35   | А     |

| I <sub>OUT</sub> Reporting Gain                 | G <sub>ILOAD</sub>  | I <sub>LOAD</sub> current divided by I <sub>OUT</sub> current (Note 4)  |      | 5   |      | μΑ/Α  |

| ANALOG CURRENT REPORT                           | TING ACCURAC        | Υ                                                                       |      |     |      |       |

|                                                 |                     | I <sub>OUT</sub> = 5A (Note 3)                                          | -5.9 |     | +5.9 |       |

| Load Reporting Accuracy                         |                     | I <sub>OUT</sub> = 10A (Note 3)                                         | -4.1 |     | +4.1 | - %   |

| Load Reporting Accuracy                         |                     | I <sub>OUT</sub> = 16A (Note 3)                                         | -2.4 |     | +2.4 | 70    |

|                                                 |                     | I <sub>OUT</sub> = 35A (Note 3)                                         | -1.8 |     | +1.8 |       |

| OVERTEMPERATURE PROT                            | ECTION (OTP)        |                                                                         |      |     |      |       |

| Overtemperature Protection<br>Threshold         | T <sub>OTP</sub>    | (Notes 3, 5)                                                            | 130  | 138 | 146  | °C    |

| ENABLE PIN (EN)                                 |                     |                                                                         |      |     |      |       |

| Logic-High                                      | V <sub>IH</sub>     |                                                                         | 1.41 |     |      | V     |

| Logic-Low                                       | V <sub>IL</sub>     |                                                                         |      |     | 0.40 | V     |

| Hysteresis                                      |                     |                                                                         |      | 450 |      | mV    |

| Internal Pulldown                               | R <sub>PD_EN</sub>  | (Note 1)                                                                |      | 800 |      | kΩ    |

## **Electrical Characteristics (continued)**

(V<sub>IN</sub> = 12V ±10%, unless otherwise specified. T<sub>J</sub> = 0°C to +125°C, unless otherwise specified. Specifications are 100% production tested at T<sub>A</sub> = +32°C. Limits over operating temperature range are guaranteed by design and characterization.)

| PARAMETER                | SYMBOL              | CONDITIONS                                                               | MIN  | TYP | MAX  | UNITS |

|--------------------------|---------------------|--------------------------------------------------------------------------|------|-----|------|-------|

| FAULT PIN (I/O)          |                     |                                                                          |      |     |      |       |

| Logic High               | V <sub>IH</sub>     |                                                                          | 1.41 |     |      | V     |

| Logic Low                | V <sub>IL</sub>     |                                                                          |      |     | 0.40 | V     |

| Hysteresis               |                     |                                                                          |      | 450 |      | mV    |

| Input Delay              | t <sub>D(IN)</sub>  | From FAULT below V <sub>IL</sub> to FET V <sub>GS</sub> < V <sub>T</sub> |      | 100 |      | ns    |

| Internal Pulldown        | R <sub>PD_FB</sub>  | (Note 1)                                                                 |      | 26  |      | Ω     |

| FAULT Output Low Voltage | V <sub>OL</sub>     | Sinking 4mA                                                              |      |     | 0.4  | V     |

| Output Delay             | t <sub>D(OUT)</sub> | From fault to start of FAULT falling                                     |      | 100 |      | ns    |

- **Note 1:** Denotes specifications that apply for typical operation junction temperature ( $T_J = +32^{\circ}C$ ).

- Note 2: The protection IC system comprising master and follower devices has three additional types of OCP. Refer to the MAX16545B/MAX16545C data sheet.

- **Note 3:** Min/max limits are  $\geq 4\sigma$  above the mean.

- Note 4: Any current reported by the follower is added to the current reported by the master. The total protection IC system current reporting is 5µA/A.

- Note 5: Guaranteed by design; not production tested.

## **Typical Operating Characteristics**

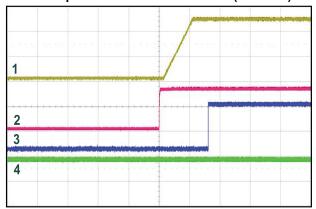

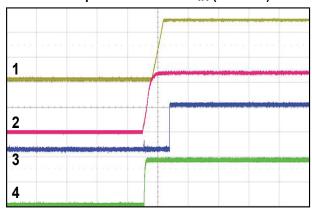

## Startup Controlled With EN/UVLO (No Load)

#### Time: 20ms/div

Conditions:  $C_{SS} = 47nF$  $C_{OUT} = 373 \mu F$ 1. V<sub>OUT</sub> (5V/div)

- 2. EN/UVLO (500mV/div)

- 3. PWRGD (1V/div)

- 4. FAULT (1V/div)

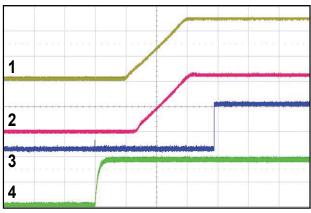

## Startup Into Load, Controlled with EN/UVLO, 10Ω Resistive Load

#### Time: 10ms/div

Conditions: C<sub>SS</sub> = 47nF,  $COUT = 373\mu F$

$R_{LOAD} = 10\Omega$ , Present at Startup

- 1. VOUT (5V/div) 2.  $I_{OUT}$  (500mA/div)

- 3. PWRGD (1V/div)

- 4. FAULT (1V/div)

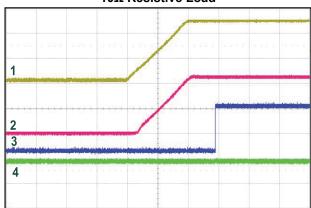

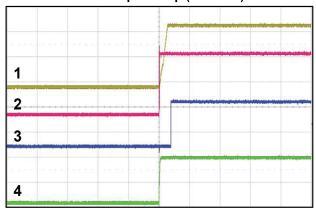

## Startup Controlled with VIN (No Load)

## Time: 50ms/div

4. FAULT (1V/div)

Conditions: Css = 47nF  $COUT = 373\mu F$ No Load at Startup 1. Vout (5V/div) 2. V<sub>IN</sub> (5V/div) 3. PWRGD (1V/div)

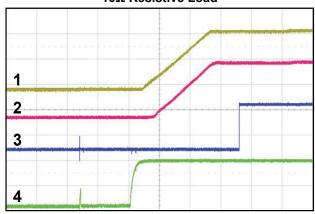

## Startup Into Load, Controlled with VIN, 10Ω Resistive Load

## Time: 10ms/div

Conditions: C<sub>SS</sub> = 47nF  $COUT = 373\mu F$

$R_{LOAD} = 10\Omega$  Present at Startup

- 1. VOUT (5V/div) 2. IOUT (500mA/div)

- 3. PWRGD (1V/div) 4. FAULT (1V/div)

## **Typical Operating Characteristics (continued)**

## Hot Swap Startup (No Load)

#### Time: 50ms/div

Conditions: Css = 47nF No Input Capacitors No Load Present at Startup

- 1. Vout (5V/div)

- 2. VIN (5V/div) 3. PWRGD (1V/div)

- 4. FAULT (1V/div)

## Hot Swap Startup Into Load, 10Ω Resistive Load

#### Time: 5ms/div

Conditions: C<sub>SS</sub> = 47nF

$R_{LOAD} = 10\Omega$  Present at Startup

No Input Capacitors

1. Vout (5V/div)

2. I<sub>OUT</sub> (5V/div) 3. PWRGD (1V/div)

4. FAULT (1V/div)

## **PWRGD Response**

#### Time: 50ms/div

Conditions: Css = 47nF PWR\_GD Threshold = 10V No Load

- 1. Vout (5V/div)

- 2. V<sub>IN</sub> (5V/div)

- 3. PWRGD (1V/div)

- 4. FAULT (1V/div)

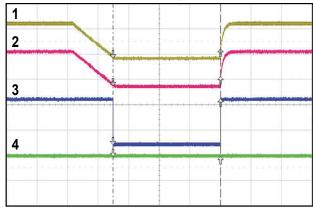

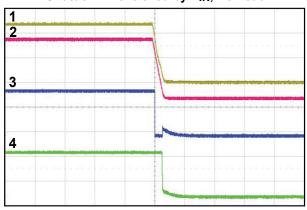

## Moderate OCP - On-the-Fly

#### Time: 200ms/div

Conditions: I<sub>OUT</sub> = 100A - 110A, 0.05A/µs t = 300ms Moderate OCP Timeout = 100ms 1. VIN (10V/div)

2. V<sub>OUT</sub> (5V/div)

3. <u>IOUT (20A/div)</u> 4. <u>FAULT</u> (1V/div)

Master + Two Followers

## **Typical Operating Characteristics (continued)**

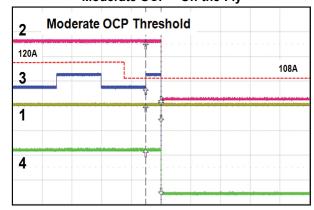

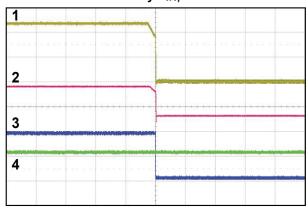

#### Moderate OCP - Timeout

#### Time: 50ms/div

Conditions: IOUT = 50 - 125A

Moderate OCP Timeout = 250ms Moderate OCP Threshold = 120A

- 1. V<sub>IN</sub> (5V/div)

- 2. VOUT (5V/div)

- 3. IOUT (50A/div)

- 4. FAULT (1V/div)

Master + Two Followers

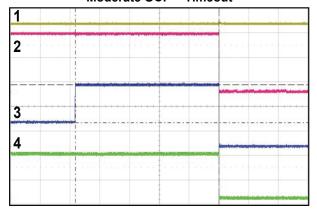

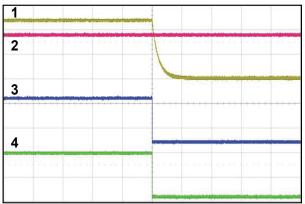

## Severe OCP

#### Time: 2ms/div

Conditions: IOUT = 50 - 150A

Moderate OCP Timeout = 250ms Moderate OCP Threshold = 108A Severe OCP Setting = 130%

- 1. V<sub>IN</sub> (10V/div)

- 2. Vout (5V/div)

- 3. IOUT (20A/div)

- 4. FAULT (1V/div)

Master + Two Followers

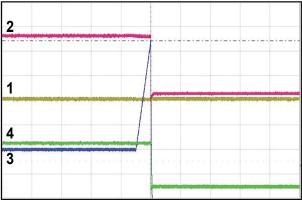

## Shutdown Controlled by VIN, No Load

#### Time: 1s/div

Conditions: IOUT = 0A

FAULT and PWRGD Pull-Up Voltages Derived From 12V Supply

- 1. Vout (5V/div)

- 2. VIN (5V/div)

- 3. PWRGD (1V/div)

- 4. FAULT (1V/div)

## **Typical Operating Characteristics (continued)**

## Shutdown Controlled by $V_{IN}$ , $10\Omega$ Resistive Load

#### Time: 20ms/div

Conditions: IOUT = 0A

$R_{LOAD} = 1\Omega$

1. Vout (5V/div) 2. IOUT (10A/div)

3. PWRGD (1V/div)

4. FAULT (1V/div)

#### **MAX16543 Fault Detection**

#### Time: 50ms/div

Conditions: Overtemperature Fault Detected by MAX16543

1. Vout (5V/div)

2. V<sub>IN</sub> (5V/div) 3. <u>PWRGD</u> (1V/div)

4. FAULT (1V/div)

0

20 30 40

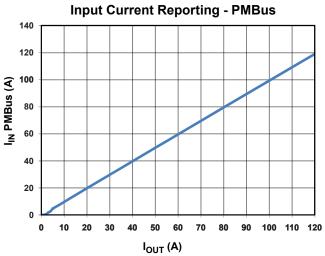

## **Typical Operating Characteristics (continued)**

# Output Current Monitoring and Reporting - Analog 1.6 1.4 1.2 0.6 0.4 0.2

$I_{OUT}$  (A)

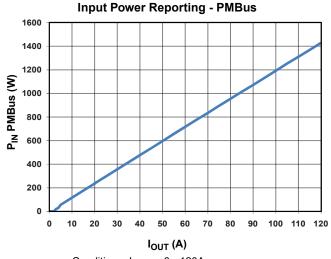

Conditions:  $I_{OUT}$  = 0 - 120A  $R_{ILOAD}$  = 2.26kΩ MAX16545B/C + 2 x MAX16543

Master + Two Followers

60

80 90

100 110 120

Conditions: I<sub>OUT</sub> = 0 - 120A MAX16545B/C + 2 x MAX16543 Master + Two Followers Reporting of PMBus Register 89h

Conditions: I<sub>OUT</sub> = 0 - 120A V<sub>IN</sub> =12V MAX16545B/C + 2 x MAX16543 Master + Two Followers Reporting of PMBus Register 97h

## **Typical Operating Characteristics (continued)**

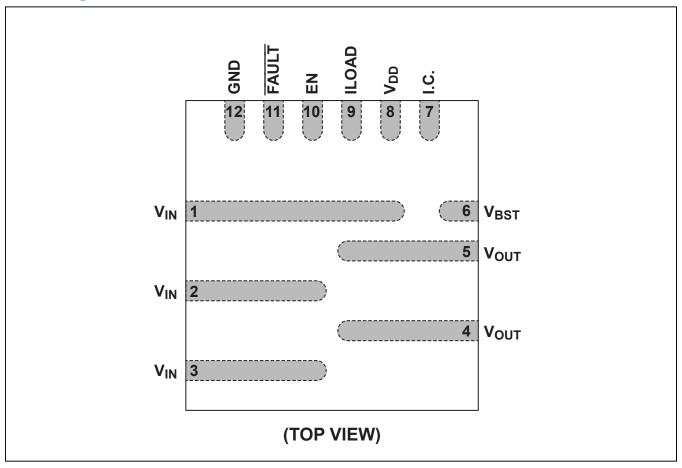

## **Pin Configuration**

## **Pin Description**

| PIN  | NAME             | DESCRIPTION                                                                                                                                                                                                                                                 |

|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–3  | V <sub>IN</sub>  | 12V Input Power Pins, Power-Supply Side                                                                                                                                                                                                                     |

| 4, 5 | V <sub>OUT</sub> | 12V Output Power Pins, Load Side                                                                                                                                                                                                                            |

| 6    | V <sub>BST</sub> | Power-Supply Pin for the Integrated FET Gate Drive. Connect this pin to the $V_{BST}$ pin of MAX16545B/ MAX16545C. Place a 1µF bypass capacitor between $V_{BST}$ and $V_{OUT}$ as close as possible, one for each MAX16543 device.                         |

| 7    | I.C.             | Internally Connected. Connect this pin to GND through a 10kΩ resistor.                                                                                                                                                                                      |

| 8    | $V_{DD}$         | Bias Supply Input. Connect this pin to the V <sub>DD</sub> pin of the MAX16545B/MAX16545C.                                                                                                                                                                  |

| 9    | ILOAD            | Analog Current Representation of the Load Current. Connect this pin to the ILOAD_IN pin of the MAX16545B/MAX16545C through a $500\Omega$ resistor.                                                                                                          |

| 10   | EN               | Enable Pin for MAX16543. Connect EN to the PWRGD pin of the MAX16545B/MAX16545C.                                                                                                                                                                            |

| 11   | FAULT            | Fault Communication, Bidirectional Pin. FAULT is used to indicate/receive detection of latching faults. Connect this pin to the FAULT pin of the MAX16545B/MAX16545C, and to the system bias supply rail through a 10kΩ resistor. This pin is 5V compliant. |

| 12   | GND              | IC Ground. Connect this pin to ground for proper device operation.                                                                                                                                                                                          |

## **Detailed Description**

## **Theory of Operation**

The MAX16543 is designed to operate in conjunction with the MAX16545B/MAX16545C Integrated Protection IC to provide the same features as the MAX16545B/MAX16545C but for higher currents. The MAX16543 provides an analog load current signal output that is connected to the input on the MAX16545B/MAX16545C to allow the MAX16545B/MAX16545C to accurately report total system current using the lossless current sensing in both the MAX16545B/MAX16545C and MAX16543. In the event of a system fault, the MAX16545B/MAX16545C disable the MAX16543. The MAX16543 also includes a local fast overcurrent protection (safe OCP) and an overtemperature shutdown.

## Startup

The MAX16545B/MAX16545C controls the output voltage ramp. The MAX16543 remains fully off until the output voltage has settled and the MAX16545B/MAX16545C power good signal goes high. The MAX16543 will then be enabled.

#### **System Current Distribution**

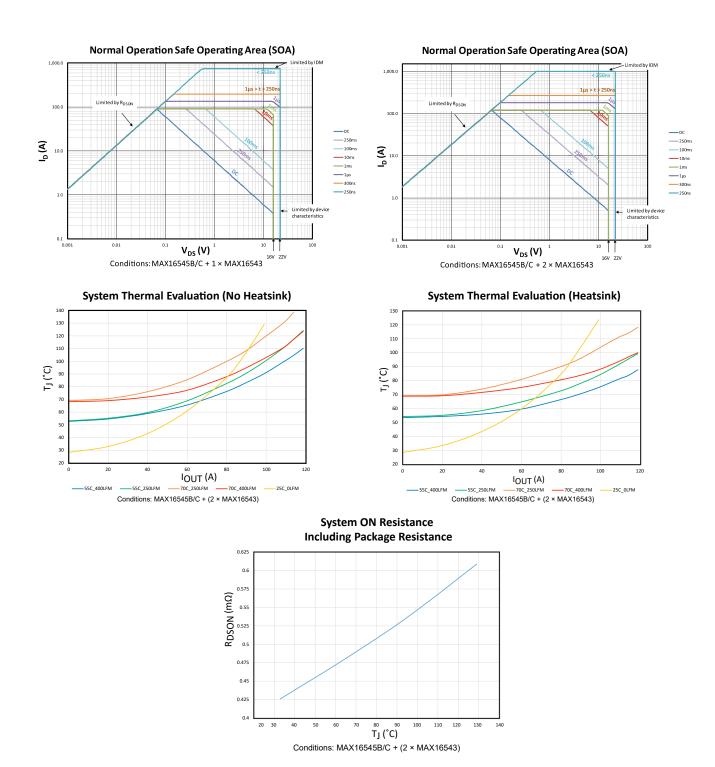

The distribution of the total input current between MAX16543 and MAX16545B/MAX16545C is determined by the on-resistances of both MAX16543 and MAX16545B/MAX16545C. See Maxim *Application Note 6754*. Under typical operation conditions:

- MAX16543 RDS<sub>ON</sub> = 1.5mΩ (including package resistance)

- MAX16545B/MAX16545C RDS<sub>ON</sub> = 0.9mΩ (including package resistance)

## V<sub>DD</sub> UVLO

Bias supply of MAX16543 is provided by MAX16545B/ MAX16545C. MAX16543 implements  $V_{DD}$  UVLO fault monitor and protection.  $V_{DD}$  is monitored at all times. If  $V_{DD}$  falls below  $V_{DD}$  UVLO during normal operation, the MAX16543 turns off and recovers as soon as  $V_{DD}$  returns to normal value, if no other faults are detected.

## V<sub>BOOST</sub>, V<sub>GS</sub> UVLO

Boost voltage is provided by the MAX16545B/MAX16545C. VBOOST UVLO is checked by MAX16543 when EN and FAULT are above the enable threshold and remains active while the device is enabled.

#### **Overcurrent Detection (Safe OCP)**

The MAX16543 features a local, independent level of protection against severe overload faults with internally-fixed thresholds. It assures that the integrated FET is protected from exceeding its safe operating condition at all times. If

at any time the load current through MAX16543 exceeds this safe OCP threshold, the MAX16543 turns the integrated FET off, asserts the FAULT low, and reports it to the MAX16545B/MAX16545C.

## **Overtemperature Protection (OTP)**

The MAX16543 includes protection against overtemperature conditions. If the junction temperature exceeds the overtemperature threshold, the IC latches the integrated FET OFF and asserts the FAULT output low indicating it to the MAX16545B/MAX16545C.

## **FAULT** Fault Reporting

The MAX16543 provides a dedicated pin for fault reporting,  $\overline{\text{FAULT}}$ . If at any time a latching fault is detected,  $\overline{\text{FAULT}}$  pin is immediately latched LOW  $\overline{\text{FAULT}}$ \_MS and reported to MAX16545B/MAX16545C. A MAX16545B/MAX16545C EN/UVLO or V<sub>IN</sub> toggling, or a restart through the OPERATIONS command is required to reset the chipset after latching fault detection.

## Fault Input and FAULT Pullup

FAULT pin is a bidirectional open-drain pin that can be used for fault communication, from the MAX16545B/MAX16545C or from an external circuitry to the MAX16543. To communicate a fault to the MAX16543, the FAULT pin must be pulled low. If FAULT is pulled low by an external circuit or by the MAX16545B/MAX16545C, the MAX16543 open its PASSFET until FAULT and PWRGD return high. The pullup voltage source must be considered to ensure the rail is operational and pulled high before the MAX16545B/MAX16545C and MAX16543 startup cycle.

Table 1. MAX16543 Faults Detected and Actions

| PARAM-<br>ETER             | DESCRIPTION                                    | FAULT<br>ASSERTED | LATCH-<br>ING |

|----------------------------|------------------------------------------------|-------------------|---------------|

| V <sub>BOOST</sub><br>UVLO | UVLO For V <sub>BOOST</sub><br>Voltage         | Yes               | Yes           |

| MAX16543<br>Safe OCP       | MAX16543 Safe<br>Overcurrent Fault<br>Detected | Yes               | Yes           |

| ОТР                        | Overtemperature<br>Fault Threshold<br>Exceeded | Yes               | Yes           |

**Note:** Refer to the MAX16545B/MAX16545C data sheet for chipset/system faults and actions.

## Integrated Protection IC on a High-Power 12V Bus with an Integrated MOSFET and Lossless Current Sensing

These are the options for the pullup rail:

- MAX16543 V<sub>DD</sub>: 1.8V internal LDO (MAX16545B/ MAX16545C) rail. This rail is limited to 1.8V, thus the external system has to be compliant with that rail.

- System 3.3V or 5V Rail. FAULT is 5V compliant, and therefore an external higher voltage rail can be used for pullup. This rail has to be stable when the MAX16543 is initiating its startup procedure. If it is not, a potential false fault communication can occur.

## ILOAD Reporting

The load current measured by the MAX16543 is sent as an analog signal to the MAX16545B/MAX16545C which then reports the total load. Refer to the MAX16545B/ MAX16545C data sheet for more information. Equation 1 and Equation 2 apply to the total load and can be used whether one or two MAX16543s are present.

## **Equation 1:**

$$V_{ILOAD} = R_{ILOAD} \times I_{LOAD} \times G_{ILOAD}$$

#### **Equation 2:**

$$R_{ILOAD} = \frac{V_{ILOAD}}{I_{LOAD} \ FSD \times G_{ILOAD}}$$

where:

V<sub>ILOAD</sub> = current reporting voltage (V)

$R_{II OAD}$  = external current reporting resistor ( $\Omega$ )

I<sub>I OAD</sub> = load current I<sub>OUT</sub> = I<sub>IN</sub> (A)

I<sub>LOAD</sub> FSD = desired full scale of current reporting (A)

G<sub>ILOAD</sub> = current reporting gain from *Electrical* Characteristics table

For example to set the full-scale system current reported to 100A.

#### Equation 3:

$$R_{ILOAD} = \frac{1.35V}{100A \times (5 \times 10^{-6})}$$

$$= 2.7kO$$

## **Programming Moderate OCP Threshold**

The system moderate OCP threshold is externally programmable through a resistor connected to the R OCP pin on the MAX16545B/MAX16545C. The value should be set to the correct system value taking into account the MAX16543 and MAX16545B/MAX16545C. Refer to the MAX16545B/MAX16545C data sheet for more details.

## Equation 4:

$$I_{OCP} = \frac{V_{OCPM}}{R_{OCP}} \times GOCP$$

where:

I<sub>OCP</sub> = moderate overcurrent protection threshold (A)

V<sub>OCPM</sub> = overcurrent protection reference voltage shown in the MAX16545B/MAX16545C Electrical Characteristics table (V)

GOCP = overcurrent protection gain shown in the MAX16545B/MAX16545C Electrical Characteristics table (A/A)

R<sub>OCP</sub> = Value of overcurrent protection programming  $resistor(\Omega)$

#### Equation 5:

$$R_{OCP} = \frac{V_{OCPM}}{I_{OCP}} \times GOCP$$

where:

I<sub>OCP</sub> = moderate overcurrent protection threshold (A)

V<sub>OCPM</sub> = overcurrent protection reference voltage shown in the MAX16545B/MAX16545C Electrical Characteristics table (V)

GOCP = overcurrent protection gain shown in the MAX16545B/MAX16545C Electrical Characteristics table

R<sub>OCP</sub> = Value of overcurrent protection programming resistor  $(\Omega)$

#### **Design Example:**

To set system moderate OCP to 100A nominal, using values from the MAX16545B/MAX16545C data sheet, see Equation 6.

#### **Equation 6:**

$$R_{OCP} = \frac{0.8V}{100A} \times \left(8 \times 10^6\right)$$

$$= 64k\Omega$$

## Input Capacitance (CIN) Selection

Use of input capacitance is highly recommended to guarantee the input voltage is stable and noise free.

For applications requiring no input capacitors before the MAX16545B/MAX16545C + MAX16543 system, the input voltage ripple should be less than 300mV peak-to-peak.

## **Output Capacitance (COUT) Selection**

The maximum output capacitance can be calculated as in Equation 7.

## Equation 7:

$$C_{OUT} = \frac{I_{INRUSH} \times C_{SS}}{I_{SS}}$$

where:

C<sub>SS</sub> = Soft-start programming capacitance.

I<sub>SS</sub> = Soft-start current, 30µA typical.

C<sub>OUT</sub> = Maximum load capacitance that can be used at soft-start with purely capacitive load

$I_{INRUSH}$  = Desired maximum inrush current during startup. Select  $I_{INRUSH}$  lower than programmed MAX16545B/MAX16545C startup OCP ( $I_{OCP(STARTUP)}$ ) and within MAX16545B/MAX16545C startup SOA.

#### Design Example

Assume a design value for maximum inrush current of 10A, and a soft-start capacitance of 25nF.

Assume 12V application and typical  $30\mu A$  soft-start current; soft-start time in this case is 0.01ms. The maximum safe-operating output current is 22A at 0.01ms. Assume the default startup OCP level is 16A.

The designed maximum inrush current of 10A is lower than 16A startup OCP and within startup SOA.

The designed value is valid. Hence, the maximum load capacitance is as shown in Equation 8.

## **Equation 8:**

$$C_{OUT} = \frac{\left(10A \times 25nF\right)}{30\mu A} = 8.33mF\left(max\right)$$

Additionally, the recommended output capacitance should be less than 10mF to prevent false triggering of self-check during startup into precharged output.

## Input TVS Diode Selection

The use of a transient voltage suppression (TVS) diode at input is necessary to clamp input-voltage transient within rating of the  $V_{\text{IN}}$  pins.

A general guide to select the proper TVS diode is:

- Choose a TVS diode with reverse-standoff voltage (V<sub>RWM</sub>) ≥ operating voltage of MAX16545B/MAX16545C + MAX16543 system (12V typ).

- Choose a TVS diode with peak-pulse current (I<sub>PPM</sub>) ≥ maximum transient peak-pulse current of MAX16545B/ MAX16545C + MAX16543 system (90A/120A typ).

- Choose a TVS diode with clamping voltage (V<sub>C</sub>) ≤ maximum voltage handling capability of MAX16545B/ MAX16545C + MAX16543 system (22V for 150µs typ)

2 × SMCJ13A is recommended based on selection criteria above.

#### **Output Schottky Diode Selection**

The use of Schottky diode at output is necessary to clamp the negative output-voltage spike within the Absolute Maximum rating of the  $V_{OUT}$  pin. Select the proper Schottky diode with low-forward voltage drop ( $V_F$ ) and peak forward surge current ( $I_{FSM}$ ) higher than the expected inductive current.

## **Layout Recommendations**

(See Maxim Application Note 6848)

## **VIN and VOUT**

- Minimize input and output trace inductance by using wide and multiple V<sub>IN</sub> and V<sub>OUT</sub> planes for optimal thermal performance.

- Use multiple vias to connect interlaying power planes.

- Place input capacitors (where applicable) as close to the IC as possible.

- Place output capacitors as close to the IC as possible.

- Place TVS and Schottky diodes close to the IC for tighter coupling to V<sub>OUT</sub> and GND; V<sub>IN</sub> and GND.

## Example

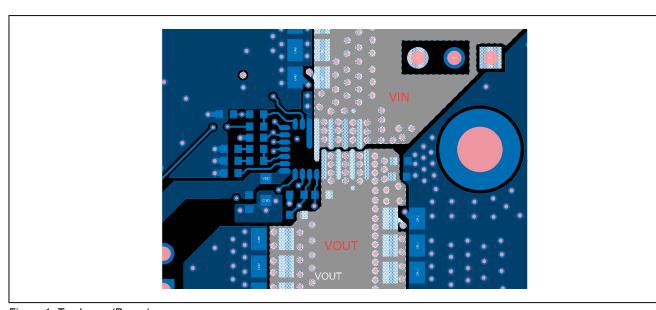

The EV kit layout in Figure 1 shows use of large, wide power planes for  $V_{IN}$  and  $V_{OUT}$  on the top layer.  $C_{IN}$  and  $C_{OUT}$  are close to the IC. The other  $V_{IN}$  and  $V_{OUT}$  power layers are connected with multiple vias between the pins.

## V<sub>BST</sub> and SS

Place the  $V_{\mbox{\footnotesize{BST}}}$  and SS capacitors on the top layer as close to the pins as possible.

## $V_{DD}$

- Add a V<sub>DD</sub> plane on the top layer to decouple the V<sub>DD</sub> caps close to the IC to form a tighter loop to ground.

- Create a quiet ground trace/plane connecting V<sub>DD</sub> ground and GND pin together.

## **ROCP and ILOAD**

The ROCP and ILOAD resistors should be placed as close to the IC as possible.

## **IC PIN**

Connect a 10k resistor to ground.

Figure 1. Top Layer (Power)

# Integrated Protection IC on a High-Power 12V Bus with an Integrated MOSFET and Lossless Current Sensing

## **Ordering Information**

| PART NUMBER   | DESCRIPTION   | PACKAGE  | SHIPPING METHOD   | PACKAGE MARKING |

|---------------|---------------|----------|-------------------|-----------------|

| MAX16543GPC+  | Integrated    | 42 FCOEN | Trays             | MAV46542        |

| MAX16543GPC+T | Protection IC | 12 FCQFN | 2.5ku Tape & Reel | MAX16543        |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS compliant package.

T = Tape and reel.

## Integrated Protection IC on a High-Power 12V Bus with an Integrated MOSFET and Lossless Current Sensing

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                             | PAGES<br>CHANGED             |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 0                  | 12/16            | Initial release                                                                                                                                                                                                                                                                                                                                                                         | _                            |

| 1                  | 4/17             | General Description section, Master + 1 Follower Chipset and Master +2 Follower Chipsets diagrams, Typical Operating Characteristics, Pin Description table, Figure 1, Input Capacitance (C <sub>IN</sub> ) Selection, Output Capacitance (C <sub>OUT</sub> ) Selection, and Input TVS Diode Selection sections. Added VT505/MAX16545 + MAX16543 System Layout Recommendations section. | 1–2, 6–8,<br>10–11,<br>16–19 |

| 2                  | 9/18             | Updated Figure 1                                                                                                                                                                                                                                                                                                                                                                        | 18                           |

| 3                  | 3/19             | Change master IC part number to support MAX16543 and MAX16545B public introduction. Changed layout recommendations to align with AN6848. Changed N.C. pin to I.C. to indicate internal connection.                                                                                                                                                                                      | 1–19                         |

For information on other Maxim Integrated products, visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

AZ7500EP-E1 NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81205MNTXG

SJE6600 SMBV1061LT1G SG3845DM NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG NCP81203MNTXG

NCP81206MNTXG NX2155HCUPTR UBA2051C MAX8778ETJ+ NTBV30N20T4G NCP1240AD065R2G NCP1240FD065R2G

NCP1361BABAYSNT1G NTC6600NF TC105333ECTTR NCP1230P100G NCP1612BDR2G NX2124CSTR SG2845M

NCP81101MNTXG IFX81481ELV NCP81174NMNTXG NCP4308DMTTWG NCP4308DMNTWG NCP4308AMTTWG

NCP1251FSN65T1G NCP1246BLD065R2G NTE7154 NTE7242 LTC7852IUFD-1#PBF LTC7852EUFD-1#PBF MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G MCP1633T-E/MG NCV1397ADR2G

AZ494AP-E1 UTC3843D XDPL8219XUMA1