## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

### **General Description**

**Features**

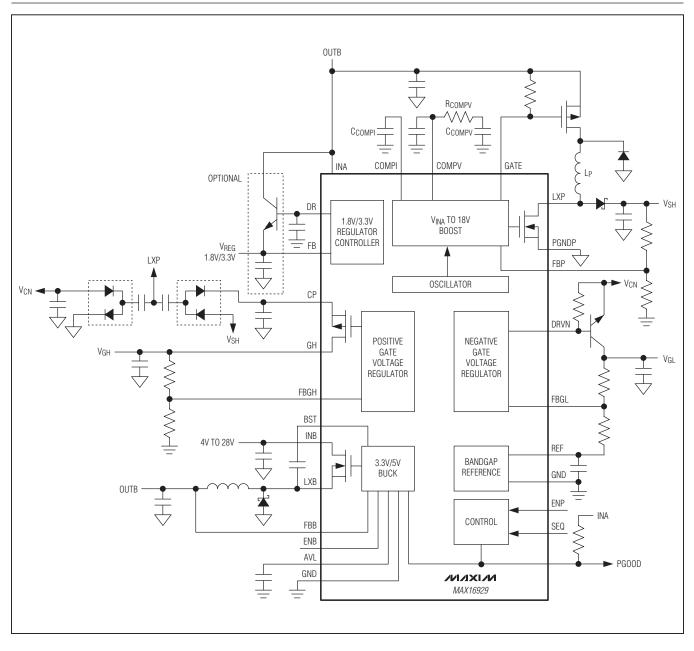

The MAX16929 is a highly integrated power supply for automotive TFT-LCD applications. The device integrates one buck converter, one boost converter, one 1.8V/3.3V regulator controller, and two gate voltage regulators. The device comes in several versions to satisfy common automotive power-supply requirements (see the Ordering Information/Selector Guide table).

Designed to operate from a single 4V to 28V supply or 5.5V to 28V supply, the device is ideal for automotive TFT-LCD applications.

Both the buck and boost converters use spread-spectrum modulation to reduce peak interference and to optimize EMI performance.

The sequencing input (SEQ) allows flexible sequencing of the positive-gate and negative-gate voltage regulators. The power-good indicator (PGOOD) indicates a failure on any of the converters or regulator outputs. Integrated thermal shutdown circuitry protects the device from overheating.

The MAX16929 is available in a 28-pin TSSOP package with exposed pad, and operates over the -40°C to +105°C temperature range.

### **Applications**

Automotive Dashboards Automotive Central Information Displays **Automotive Navigation Systems**

♦ Operating Voltage Range of 4V to 28V (Buck) or 3V to 5.5V (Boost)

- ♦ Independent 28V Input Buck Converter Powers **TFT Bias Supply Circuitry and External Circuitry**

- ♦ High-Power (Up to 6W) Boost Output Providing Up

- ♦ 1.8V or 3.3V Regulator Provides 500mA with **External npn Transistor**

- ♦ One Positive-Gate Voltage Regulator Capable of Delivering 20mA at 28V

- ♦ One Negative-Gate Voltage Regulator

- **♦** High-Frequency Operation

- ♦ 2.1MHz (Buck Converter)

- ♦ Flexible Stand-Alone Sequencing

- **♦** True Shutdown™ Boost Converter

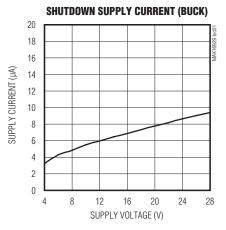

- ♦ 6µA Low-Current Shutdown Mode (Buck)

- ♦ Internal Soft-Start

- **♦** Overtemperature Shutdown

- ♦ -40°C to +105°C Operation

Ordering Information/Selector Guide appears at end of data

Typical Application Circuit appears at end of data sheet.

True Shutdown is a trademark of Maxim Integrated Products, Inc.

For related parts and recommended products to use with this part, refer to: www.maxim-ic.com/MAX16929.related

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

#### **ABSOLUTE MAXIMUM RATINGS**

| INB, ENB to GND                  | 0.3V to +42V | ENP, DR, FB, GATE, COMPI, FBGH,                        |

|----------------------------------|--------------|--------------------------------------------------------|

| BST to GND                       | 0.3V to +47V | FBGL, REF, SEQ to GND0.3V to (V <sub>INA</sub> + 0.3V) |

| BST to LXB                       | 0.3V to +6V  | GND to PGNDP0.3V to +0.3V                              |

| LXB to GND                       | 6V to +42V   | Continuous Power Dissipation (T <sub>A</sub> = +70°C)  |

| AVL, PGOOD to GND                | 0.3V to +6V  | TSSOP (derate 27mW/°C above +70°C)2162mW               |

| FBB to GND                       | 0.5V to +12V | Operating Temperature Range40°C to +105°C              |

| CP, GH to GND                    | 0.3V to +31V | Junction Temperature Range40°C to +150°C               |

| CP, GH to GND $(V_{INA} = 3.3V)$ | 0.3V to +29V | Storage Temperature Range65°C to +150°C                |

| LXP to GND                       | 0.3V to +20V | Lead Temperature (soldering, 10s)+300°C                |

| DRVN to GND                      | 25V to +0.3V | Soldering Temperature (reflow)+260°C                   |

| INA, COMPV, FBP to GND           | 0.3V to +6V  |                                                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

**TSSOP**

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>)......37°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......2°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial.

#### **ELECTRICAL CHARACTERISTICS**

(VINB = 12V, VINA = 5V, VGND = VPGNDP = 0V, TA = TJ = -40°C to +105°C, typical values are at TA = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                         | SYMBOL                  | CC                                       | MIN                        | TYP | MAX | UNITS |                   |

|-----------------------------------|-------------------------|------------------------------------------|----------------------------|-----|-----|-------|-------------------|

| BUCK CONVERTER                    |                         |                                          |                            |     |     |       |                   |

|                                   |                         | V <sub>OUTB</sub> = 5V (No               | ote 3)                     | 5.5 |     | 28    |                   |

| Supply Voltage Range              | V <sub>INB</sub>        | V <sub>OUTB</sub> = 3.3V (1              | Note 3)                    | 4   |     | 28    | V                 |

|                                   |                         | t < 500ms                                |                            |     |     | 42    |                   |

| Consolio Company                  |                         | V <sub>ENB</sub> = 0V                    |                            |     | 6   | 9     |                   |

| Supply Current                    | I <sub>INB</sub>        | V <sub>ENB</sub> = V <sub>INB</sub> , no | load, $T_A = +25^{\circ}C$ |     | 70  |       | μA                |

| Undervoltage Lockout              | V <sub>INB,UVLO</sub>   | AVL rising                               |                            |     | 3.1 | 3.5   | V                 |

| Undervoltage Lockout Hysteresis   |                         |                                          |                            |     | 0.5 |       | V                 |

| PWM Switching Frequency           | f <sub>SWB</sub>        |                                          |                            | 1.9 | 2.1 | 2.3   | MHz               |

| Spread-Spectrum Range             | SSR                     |                                          |                            |     | +6  |       | %                 |

|                                   |                         |                                          | 5V, continuous mode        | -3% | 5   | +3%   |                   |

| Output Voltage Acquirecy          | .,,                     | $6V \le V_{INB} \le 18V$                 | 5V, skip mode              | -3% | 5   | +6%   | V                 |

| Output-Voltage Accuracy           | V <sub>OUTB</sub>       | I <sub>LOAD</sub> < full load            | 3.3V, continuous mode      | -3% | 3.3 | +3%   |                   |

|                                   |                         |                                          | 3.3V, skip mode            | -3% | 3.3 | +6%   |                   |

| High-Side DMOS R <sub>DS_ON</sub> | R <sub>DS_ON(LXB)</sub> | I <sub>LXB</sub> = 1A                    |                            |     | 180 | 400   | mΩ                |

| Skip-Current Threshold            | I <sub>SKIP</sub>       |                                          |                            |     | 16  |       | %I <sub>MAX</sub> |

| Current-Limit Threshold           | 1                       | I <sub>OUTB</sub> = 1.2A or              | otion                      | 1.6 | 2   | 2.4   | А                 |

| Current-Limit Threshold           | I <sub>MAX</sub>        | I <sub>OUTB</sub> = 2.0A or              | otion                      | 2.7 | 3.4 | 4.08  |                   |

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{INB} = 12V, V_{INA} = 5V, V_{GND} = V_{PGNDP} = 0V, T_A = T_J = -40^{\circ}C$  to  $+105^{\circ}C$ , typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                             | SYMBOL                | CONDITIONS                                                                                | MIN   | TYP                 | MAX   | UNITS |

|---------------------------------------|-----------------------|-------------------------------------------------------------------------------------------|-------|---------------------|-------|-------|

| Soft-Start Ramp Time                  |                       |                                                                                           |       | 3.9                 |       | ms    |

| Maximum Duty Cycle                    |                       | Continuous mode                                                                           |       | 80                  |       | %     |

| Minimum Duty Cycle                    |                       | Continuous mode                                                                           |       | 20                  |       | %     |

| Maximum Duty Cycle in Dropout         |                       | Dropout                                                                                   |       | 95                  |       | %     |

| Thermal Shutdown Temperature          |                       |                                                                                           |       | +175                |       | °C    |

| Thermal Shutdown Hysteresis           |                       |                                                                                           |       | 15                  |       | °C    |

| POWER GOOD (PGOOD)                    |                       |                                                                                           |       |                     |       |       |

| PGOOD Threshold                       |                       | Rising                                                                                    |       | 94                  |       | %     |

| FGOOD THESHOID                        |                       | Falling                                                                                   | 90    | 92                  | 95    | 70    |

| PGOOD Debounce Time                   |                       |                                                                                           |       | 13                  |       | μs    |

| Output High-Leakage Current           |                       |                                                                                           |       |                     | 0.2   | μΑ    |

| Output Low Level                      |                       |                                                                                           |       |                     | 0.4   | V     |

| LOGIC LEVELS                          |                       |                                                                                           |       |                     |       |       |

| ENB Threshold                         |                       | ENB rising                                                                                | 1.4   | 1.8                 | 2.2   | V     |

| ENB Hysteresis                        |                       |                                                                                           |       | 0.2                 |       | V     |

| ENB Input Current                     |                       |                                                                                           | 3     | 5                   | 9     | μΑ    |

| BOOST, POSITIVE (GH), NEGATIV         | /E (GL), 1.8V/        | 3.3V CONVERTERS                                                                           |       |                     |       |       |

| INA Input Supply Range                | V <sub>INA</sub>      |                                                                                           | 3     |                     | 5.5   | V     |

| INA Supply Current                    | I <sub>INA</sub>      | V <sub>FBP</sub> = V <sub>FBGH</sub> = 1.3V, V <sub>FBGL</sub> = 0V,<br>LXP not switching |       | 1.5                 | 2.0   | mA    |

| INA Undervoltage Lockout<br>Threshold | V <sub>INA,UVLO</sub> | V <sub>INA</sub> rising, hysteresis = 200mV,<br>T <sub>A</sub> = +25°C                    | 2.5   | 2.7                 | 2.9   | V     |

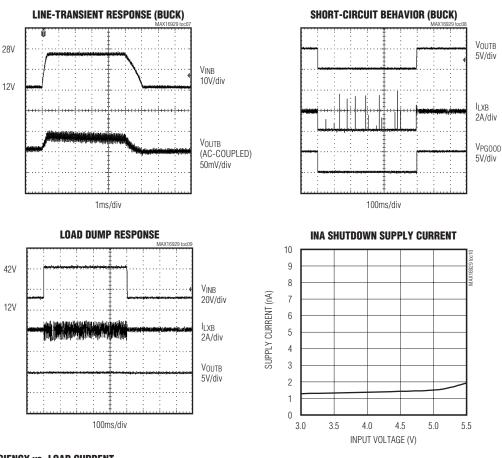

| INA Shutdown Current                  | ISHDN                 | V <sub>ENP</sub> = 0V, T <sub>A</sub> = +25°C                                             |       | 0.5                 |       | μΑ    |

| Thermal Shutdown Temperature          | T <sub>SHDN</sub>     | Temperature rising                                                                        |       | +165                |       | °C    |

| Thermal Shutdown Hysteresis           | TH                    |                                                                                           |       | 15                  |       | °C    |

| Duration to Trigger Fault Condition   |                       | V <sub>FBP</sub> , V <sub>FBGH</sub> , or V <sub>FBGL</sub> below its threshold           |       | 238                 |       | ms    |

| Autoretry Time                        |                       |                                                                                           |       | 1.9                 |       | S     |

| REFERENCE (REF)                       |                       |                                                                                           |       |                     |       |       |

| REF Output Voltage                    | V <sub>REF</sub>      | No output current                                                                         | 1.236 | 1.25                | 1.264 | V     |

| REF Load Regulation                   |                       | 0 < I <sub>REF</sub> < 80μA, REF sourcing                                                 | -2    |                     | +2    | %     |

| REF Undervoltage Lockout<br>Threshold |                       | Rising edge, hysteresis = 200mV                                                           |       |                     | 1.165 | V     |

| OSCILLATOR                            |                       |                                                                                           |       |                     |       |       |

| Internal Oscillator Frequency         | fosc                  | $T_A = +25^{\circ}C$                                                                      | 3.96  | 4.40                | 4.84  | MHz   |

| Spread-Spectrum Modulation Frequency  | f <sub>SS</sub>       |                                                                                           |       | f <sub>OSC</sub> /2 |       | MHz   |

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{INB} = 12V, V_{INA} = 5V, V_{GND} = V_{PGNDP} = 0V, T_A = T_J = -40^{\circ}C$  to  $+105^{\circ}C$ , typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                     | SYMBOL                  | COND                                                     | ITIONS                                               | MIN              | TYP   | MAX       | UNITS  |  |

|-------------------------------|-------------------------|----------------------------------------------------------|------------------------------------------------------|------------------|-------|-----------|--------|--|

| Spread-Spectrum Factor        | SSR                     | As a percentage of $f_{SW}$                              | switching frequency,                                 |                  | ±4    |           | %      |  |

| BOOST CONVERTER               |                         |                                                          |                                                      |                  |       |           |        |  |

| Switching Frequency           | f <sub>SW</sub>         |                                                          |                                                      | 1.98             | 2.20  | 2.42      | MHz    |  |

| Maximum Duty Cycle            |                         |                                                          |                                                      | 82               |       | 93.5      | %      |  |

| LXP Current Limit             | 1                       | Duty cycle = 70%, limit option                           |                                                      | 0.625            | 0.78  |           |        |  |

| LAF Guilent Limit             | I <sub>LIM</sub>        | C <sub>COMPI</sub> = 220pF                               | High boost current-<br>limit option                  | 1.25             | 1.56  | 56 1.87 A |        |  |

| LXP On-Resistance             | R <sub>DS_ON(LXP)</sub> | I <sub>LXP</sub> = 200mA                                 |                                                      |                  | 110   | 250       | mΩ     |  |

| LXP Leakage Current           | I <sub>LK_LXP</sub>     | $V_{LXP} = 20V, T_A = +2$                                | 5°C                                                  |                  | 8.5   | 20        | μΑ     |  |

| Soft-Start Time               |                         | (Note 4)                                                 |                                                      |                  | 30    |           | ms     |  |

| Output Voltage Range          | V <sub>SH</sub>         |                                                          |                                                      | V <sub>INA</sub> |       | 18        | V      |  |

| FBP Regulation Voltage        | \/                      | $V_{INA} = +3V \text{ to } +5.5V,$                       | $T_A = +25^{\circ}C$                                 | 0.985            | 1.0   | 1.015     | .015 V |  |

| rbr negulation voltage        | V <sub>FBP</sub>        | 0 < I <sub>LOAD</sub> < full load                        | $T_A = -40^{\circ}\text{C to} + 105^{\circ}\text{C}$ | 0.98             | 1.0   | 1.02      | V      |  |

| PGOOD Threshold               | V <sub>PG_FBP</sub>     | Measured at FBP                                          |                                                      | 0.74             | 0.85  | 0.96      | V      |  |

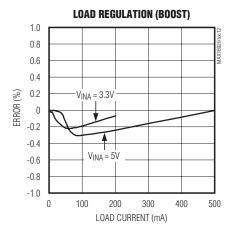

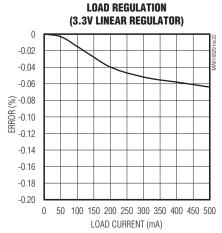

| FBP Load Regulation           |                         | 0 < I <sub>LOAD</sub> < full load                        |                                                      |                  | -1    |           | %      |  |

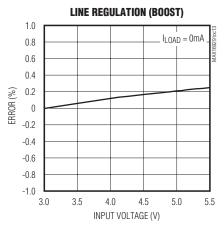

| FBP Line Regulation           |                         | $V_{INA} = +3V \text{ to } +5.5V$                        |                                                      |                  | 0.1   |           | %/V    |  |

| FBP Input Bias Current        |                         | V <sub>FBP</sub> = +1V, T <sub>A</sub> = +25°C           |                                                      |                  |       | ±1        | μΑ     |  |

| FBP to COMPV Transconductance |                         | $\Delta I = \pm 2.5 \mu A$ at COM                        | $1PV, T_A = +25^{\circ}C$                            |                  | 400   |           | μS     |  |

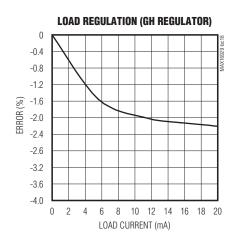

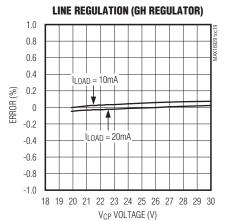

| POSITIVE-GATE VOLTAGE REGU    | JLATOR (GH)             |                                                          |                                                      |                  |       |           |        |  |

| Output Voltage Range          | V <sub>GH</sub>         | With external charge (maximum V <sub>CP</sub> = 29       | e pump, T <sub>A</sub> = +25°C<br>0.5V)              | 5                |       | 29        | V      |  |

| CP Overvoltage Threshold      |                         | $T_A = +25^{\circ}C$ (Note 6                             | )                                                    | 29.5             | 30.5  |           | V      |  |

| FBGH Regulation Voltage       | V <sub>FBGH</sub>       | I <sub>GH</sub> = 1mA                                    |                                                      | 0.98             | 1.0   | 1.034     | V      |  |

| PGOOD Threshold               | V <sub>PG_FBGH</sub>    | Measured at FBGH                                         |                                                      | 0.83             | 0.85  | 0.87      | V      |  |

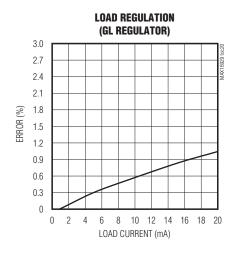

| FBGH Load Regulation          |                         | $I_{GH} = 0$ to 20mA                                     |                                                      |                  | 2     |           | %      |  |

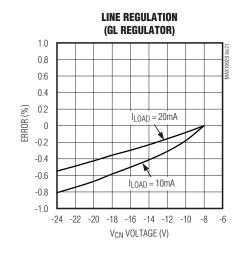

| FBGH Line Regulation          |                         | $V_{CP}$ = 12V to 20V at $V_{GH}$ = 10V, $I_{GH}$ = 10mA |                                                      |                  | 2     |           | %      |  |

| FBGH Input Bias Current       |                         | V <sub>FBGH</sub> = 1V, T <sub>A</sub> = +25°C           |                                                      |                  |       | ±1        | μΑ     |  |

| GH Output Current             | I <sub>GH</sub>         | $V_{CP} - V_{GH} = 2V$                                   |                                                      | 20               |       | -         | mA     |  |

| GH Current Limit              | I <sub>LIM_GH</sub>     |                                                          |                                                      | 35               | 56    |           | mA     |  |

| GH Soft-Start Time            |                         |                                                          |                                                      |                  | 7.45  |           | ms     |  |

| NEGATIVE-GATE VOLTAGE REG     | ULATOR (GL)             |                                                          |                                                      |                  |       |           |        |  |

| Output Voltage Range          | V <sub>DRVN</sub>       |                                                          |                                                      | -24              |       | -2        | V      |  |

| FBGL Regulation Voltage       | V <sub>FBGL</sub>       | I <sub>DRVN</sub> = 100µA                                |                                                      | 0.212            | 0.242 | 0.271     | V      |  |

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{INB} = 12V, V_{INA} = 5V, V_{GND} = V_{PGNDP} = 0V, T_A = T_J = -40^{\circ}C$  to  $+105^{\circ}C$ , typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                              | SYMBOL               | CONDITIONS                                                                                             |                                                  | MIN                   | TYP   | MAX                    | UNITS |

|----------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------|-------|------------------------|-------|

| PGOOD Threshold                        | V <sub>PG_FBGL</sub> | Measured at FBG                                                                                        | àL                                               | 0.38                  | 0.4   | 0.42                   | V     |

| FBGL Input Bias Current                |                      | $V_{FBGL} = +0.25V$                                                                                    |                                                  |                       |       | ±1                     | μΑ    |

| DRVN Source Current                    |                      | $V_{FBGL} = +0.5V$ , $V_{DRVN} = -10V$                                                                 |                                                  | 2                     |       |                        | mA    |

| DRVN Source Current Limit              |                      |                                                                                                        |                                                  | 2.5                   | 4     |                        | mA    |

| GL Soft-Start Time                     |                      |                                                                                                        |                                                  |                       | 7.45  |                        | ms    |

| 1.8V/3.3V REGULATOR CONTROL            | LER                  |                                                                                                        |                                                  |                       |       |                        |       |

| Output Voltage                         | \/                   | \/ \/                                                                                                  | 3.3V regulator option                            | 3.18                  | 3.3   | 3.38                   | V     |

| Output Voltage                         | V <sub>FB</sub>      | $V_{DR} = V_{FB}$                                                                                      | 1.8V regulator option                            | 1.746                 | 1.8   | 1.854                  | V     |

| FB PGOOD Threshold                     | V <sub>PG FB</sub>   | V <sub>PG_FB</sub> Measured at FB (Notes 5, 7)  3.3V regulator option, FB rising 1.8V regulator option | 2.4                                              | 2.57                  | 2.7   | V                      |       |

|                                        | _                    |                                                                                                        | 1.364                                            | 1.38                  | 1.396 |                        |       |

| FB Input Bias Current                  |                      | V <sub>FB</sub> = 1.8V                                                                                 |                                                  |                       | 2.5   |                        | μΑ    |

| PB IIIput bias Current                 |                      | V <sub>FB</sub> = 3.3V                                                                                 |                                                  |                       | 4.5   |                        | μΑ    |

| DR Drive Current                       |                      | $V_{FB} = 1.8V$                                                                                        |                                                  | 4.5                   | 6     |                        | mA    |

| INPUT SERIES SWITCH CONTRO             | L                    |                                                                                                        |                                                  |                       |       |                        |       |

| p-Channel FET GATE Sink Current        |                      | $V_{GATE} = 0.5V$                                                                                      |                                                  | 33                    | 55    | 75                     | μΑ    |

| GATE Voltage Threshold                 |                      |                                                                                                        | E; below this voltage, the IFET is considered on |                       | 1.25  |                        | V     |

| DIGITAL LOGIC                          |                      |                                                                                                        |                                                  |                       |       |                        |       |

| ENP, SEQ Input Pulldown Resistor Value | R <sub>PD</sub>      |                                                                                                        |                                                  |                       | 500   |                        | kΩ    |

| ENP, SEQ Input-Voltage Low             | V <sub>IL</sub>      |                                                                                                        |                                                  |                       | (     | ).3 x V <sub>INA</sub> | V     |

| ENP, SEQ Input-Voltage High            | V <sub>IH</sub>      |                                                                                                        |                                                  | 0.7 x V <sub>IN</sub> | A     |                        | V     |

| PGOOD Leakage Current                  | I <sub>LK_IN</sub>   | $T_A = +25^{\circ}C$                                                                                   |                                                  |                       |       | ±1                     | μΑ    |

| PGOOD Output-Voltage Low               | V <sub>OL</sub>      | 2mA sink current                                                                                       | , T <sub>A</sub> = +25°C                         |                       |       | 0.4                    | V     |

- Note 2: Specifications over temperature are guaranteed by design and not production tested.

- Note 3: Operation in light-load conditions or at extreme duty cycles result in skipped cycles, resulting in lower operating frequency and possibly limited output accuracy and load response.

- Note 4: 50% of the soft-start voltage time is due to the soft-start ramp, and the other 50% is due to the settling of the output voltage.

- **Note 5:** Guaranteed by design: not production tested.

- Note 6: After the voltage at CP exceeds this overvoltage threshold, the entire circuit switches off and autoretry is started.

- Note 7: FB power good is indicated by PGOOD. The condition VFB < VPG FB does not shutdown/restart the device.

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

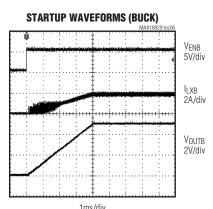

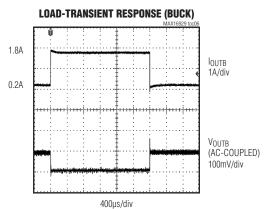

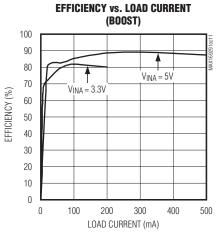

### **Typical Operating Characteristics**

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

## **Typical Operating Characteristics (continued)**

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

### **Typical Operating Characteristics (continued)**

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

## **Typical Operating Characteristics (continued)**

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

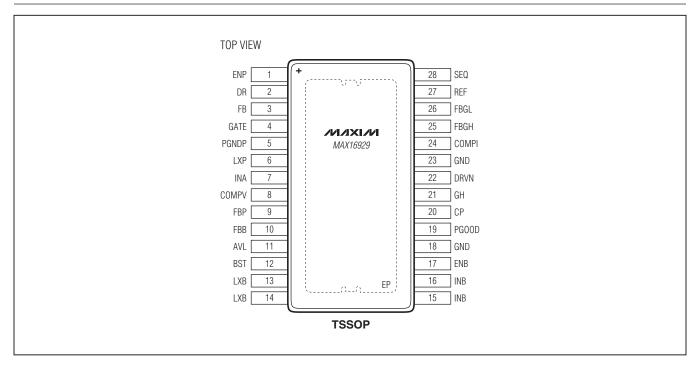

## **Pin Configuration**

## **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                         |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ENP   | Boost Circuitry and 1.8V/3.3V Regulator Controller Enable Input. ENP has an internal $500k\Omega$ pulldown resistor. Drive high for normal operation and drive low to place the device (except buck converter) in shutdown.                                                      |

| 2   | DR    | 1.8V or 3.3V Regulator Output. DR has a 4.5mA (min) drive capability. For greater output current capability, use an external npn bipolar transistor whose base is connected to DR.                                                                                               |

| 3   | FB    | 1.8V or 3.3V Regulator Feedback Input. FB is regulated to 1.8V or 3.3V. Connect FB to DR when powering loads demanding less than 4.5mA. For greater output current capability, use an external npn bipolar transistor whose emitter is connected to FB.                          |

| 4   | GATE  | External p-Channel FET Gate Drive. GATE is an open-drain driver connected to the gate of the external input series p-channel FET. Connect a pullup resistor between GATE and INA. During a fault condition, the gate driver turns off and the pullup resistor turns off the FET. |

| 5   | PGNDP | Boost Converter Power Ground                                                                                                                                                                                                                                                     |

| 6   | LXP   | Boost Converter Switching Node. Connect LXP to the inductor and catch diode of the boost converter.                                                                                                                                                                              |

| 7   | INA   | Boost Circuitry and 1.8V/3.3V Regulator Controller Power Input. Connect INA to a 3V to 5.5V supply.                                                                                                                                                                              |

| 8   | COMPV | Boost Error Amplifier Compensation Connection. Connect a compensation network between COMPV to GND.                                                                                                                                                                              |

| 9   | FBP   | Boost Converter Feedback Input. FBP is regulated to 1V. Connect FBP to the center of a resistive divider connected between the boost output and GND.                                                                                                                             |

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

## **Pin Description (continued)**

| PIN    | NAME  | FUNCTION                                                                                                                                                                                                                                      |

|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10     | FBB   | Buck Converter Feedback Input. FBB is regulated to either 3.3V or 5V. Connect FBB to the output-voltage node, OUTB, as shown in the <i>Typical Application Circuit</i> .                                                                      |

| 11     | AVL   | Buck Converter Internal 5V Regulator. Connect a 1µF capacitor between AVL and the analog ground plane. Do not use AVL to power external circuitry.                                                                                            |

| 12     | BST   | Buck Converter Bootstrap Capacitor Connection. Connect a 0.1µF capacitor between BST and LXB.                                                                                                                                                 |

| 13, 14 | LXB   | Buck Converter Inductor Connection. Connect the inductor, boost capacitor, and catch diode at this node.                                                                                                                                      |

| 15, 16 | INB   | Buck Converter Power Input. Connect to a 4V to 28V supply. Connect a 1µF or larger ceramic capacitor in parallel with a 47µF bulk capacitor from INB to the power ground plane. Connect both INB power inputs together.                       |

| 17     | ENB   | Buck Converter Enable Input. ENB is a high-voltage compatible input. Connect to INB for normal operation and connect to ground to disable the buck converter.                                                                                 |

| 18, 23 | GND   | Analog Ground                                                                                                                                                                                                                                 |

| 19     | PGOOD | Open-Drain Power-Good Output. Connect PGOOD to INA through an external pullup resistor.                                                                                                                                                       |

| 20     | СР    | Positive-Gate Voltage Regulator Power Input. Connect CP to the positive output of the external charge pump. Ensure that V <sub>CP</sub> does not exceed the CP overvoltage threshold as given in the <u>Electrical Characteristics</u> table. |

| 21     | GH    | Positive-Gate Voltage Regulator Output                                                                                                                                                                                                        |

| 22     | DRVN  | Negative-Gate Voltage Regulator Driver Output. DRVN is the open drain of an internal p-channel FET. Connect DRVN to the base of an external npn pass transistor.                                                                              |

| 24     | COMPI | Boost Slope Compensation Connection. Connect a capacitor between COMPI and GND to set the slope compensation.                                                                                                                                 |

| 25     | FBGH  | Positive-Gate Voltage Regulator Feedback Input. FBGH is regulated to 1V. Connect FBGH to the center of a resistive divider connected between GH and GND.                                                                                      |

| 26     | FBGL  | Negative-Gate Voltage Regulator Feedback Input. FBGL is regulated to 0.25V. Connect FBGL to the center of a resistive divider connected between REF and the output of the negative-gate voltage regulator.                                    |

| 27     | REF   | 1.25V Reference Output. Bypass REF to GND with a 0.1µF ceramic capacitor.                                                                                                                                                                     |

| 28     | SEQ   | Sequencing Input. SEQ has an internal $500k\Omega$ pulldown resistor. SEQ determines the sequence in which $V_{GH}$ and $V_{GL}$ power-up. See <u>Table 1</u> for supply sequencing options.                                                  |

| _      | EP    | Exposed Pad. Connect to a large contiguous copper ground plane for optimal heat dissipation. Do not use EP as the only electrical ground connection.                                                                                          |

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

### **Detailed Description**

The MAX16929 is a highly integrated power supply for automotive TFT-LCD applications. The device integrates one buck converter, one boost converter, one 1.8V/3.3V regulator controller, one positive-gate voltage regulator, and one negative-gate voltage regulator.

The device achieves enhanced EMI performance through spread-spectrum modulation. Digital input control allows the device to be placed in a low-current shutdown mode and provides flexible sequencing of the gate voltage regulators.

Internal thermal shutdown circuitry protects the device from overheating. The buck converter is designed to shut down when its die temperature reaches +175°C (typ), while the boost circuitry does so at +165°C (typ). Each resumes normal operation once its die temperature has fallen 15°C below its respective thermal shutdown

The device is factory-trimmed to provide a variety of power options to meet the most common automotive TFT-LCD display power requirements, as outlined in the Ordering Information/Selector Guide table.

#### **Buck Converter**

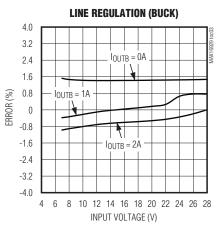

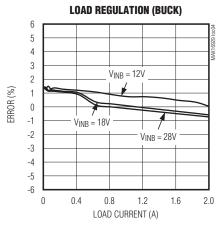

The device features a current-mode buck converter with an integrated high-side FET, which requires no external compensation network. The buck converter regulates the output voltage to within ±3% in continuous mode over line and load conditions. The high 2.1MHz (typ) switching frequency allows for small external components, reduced output ripple, and guarantees no AM interference.

A power-good (PGOOD) indicator is available to monitor output-voltage quality. The enable input allows the device to be placed in shutdown, reducing supply current to 70µA.

The buck converter comes with a preset output voltage of either 3.3V or 5V, and can deliver either 1.2A or 2A to the output.

#### Enable (ENB)

Connect ENB to INB for always-on operation. ENB is also compatible with 3.3V logic systems and can be controlled through a microcontroller or by automotive KEY or CAN inhibit signals.

#### Internal 5V Regulator (AVL)

AVL is an internal 5V regulator that supplies power to the buck controller and charges the boost capacitor. After enabling the buck converter, VAVL begins to rise. Once V<sub>AVI</sub> exceeds the undervoltage lockout voltage of 3.5V (max), LXB starts switching. Bypass AVL to GND with a 1µF ceramic capacitor.

#### Spread-Spectrum Modulation

The buck converter features spread-spectrum operation that varies the internal operating frequency of the buck converter by +6% relative to the switching frequency of 2.1MHz (typ).

#### Soft-Start

The buck converter features an internal soft-start timer. The output voltage takes 3.9ms to ramp up to its set voltage. If a short circuit or undervoltage is encountered after the soft-start timer has expired, the device enters hiccup mode, during which soft-start is reattempted every 16ms. This process repeats until the short circuit has been removed.

#### **Overcurrent Protection**

The device enters hiccup mode in one of three ways. If eight consecutive current limits are detected and the output is below 77% of its nominal value, the buck converter enters hiccup mode. The converter enters hiccup mode immediately if the output is short circuited to ground (output below 1V). Additionally, the device enters hiccup mode if 256 consecutive overcurrent events are detected when the output is greater than 77% of its nominal value. In hiccup mode, the buck controller idles for 16ms before reattempting soft-start.

#### **Power Good (PGOOD)**

When an overcurrent condition causes the buck output to fall below 92% of its set voltage, the open-drain powergood indicator output (PGOOD) asserts low. PGOOD deasserts once the output voltage has risen above 95% of its set voltage.

PGOOD serves as a general fault indicator for all the converters and regulators. Besides indicating an undervoltage on the buck output, it also indicates any of the faults listed in the Fault Conditions and PGOOD section.

#### **Boost Converter**

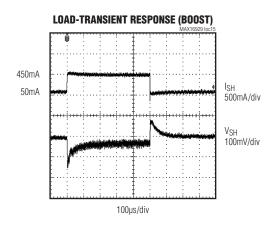

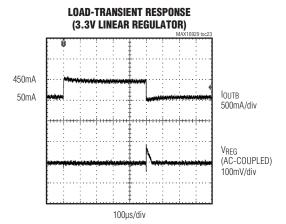

The boost converter employs a current-mode, fixedfrequency PWM architecture to maximize loop bandwidth and provide fast transient response to pulsed loads typical of TFT-LCD panel source drivers. The 2.2MHz switching frequency allows the use of low-profile inductors and ceramic capacitors to minimize the thickness of LCD panel designs. The integrated low on-resistance MOSFET and

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

the device's built-in digital soft-start functions reduce the number of external components required while controlling inrush currents. The output voltage can be set from VINA to 18V with an external resistive voltage-divider. The regulator controls the output voltage by modulating the duty cycle (D) of the internal power MOSFET in each switching cycle. The duty cycle of the MOSFET is approximated by:

$$D = 1 - \frac{\eta V_{IN}}{V_{O}}$$

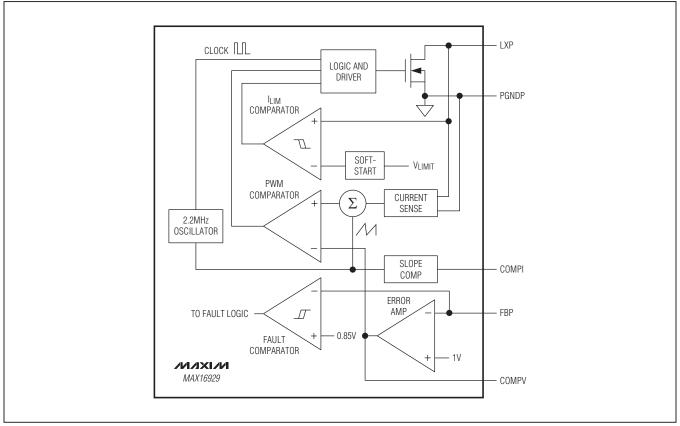

where  $V_{IN}$  is the voltage at INA,  $V_O$  =  $V_{SH}$  (the boost output voltage), and  $\eta$  is the efficiency of the boost converter, as shown in the Typical Operating Characteristics. Figure 1 shows the functional diagram of the boost

regulator. An error amplifier compares the signal at FBP

to 1V and changes the COMPV output. The voltage at COMPV sets the peak inductor current. As the load varies, the error amplifier sources or sinks current to the COMPV output accordingly to produce the peak inductor current necessary to service the load. To maintain stability at high duty cycles, a slope-compensation signal (set by the capacitor at COMPI) is summed with the current-sense signal. On the rising edge of the internal clock, the controller turns on the n-channel MOSFET and applies the input voltage across the inductor. The current through the inductor ramps up linearly, storing energy in its magnetic field. Once the sum of the current feedback signal and the slope compensation exceeds the COMPV voltage, the controller turns off the MOSFET. The inductor current then flows through the diode to the output. The MOSFET remains off for the rest of the clock cycle.

Figure 1. Boost Converter Functional Diagram

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

The external p-channel FET controlled by GATE protects the output during fault conditions and provides True Shutdown of the converter. Connect a pullup resistor between GATE and INA (see the Boost Converter section to select the value for the pullup resistor). Under normal operation, GATE turns on the p-channel FET, connecting the supply to the boost input. During a fault condition or in shutdown, GATE is off and the pullup resistor turns off the p-channel FET, disconnecting the supply from the boost input.

#### Spread-Spectrum Modulation

The high-frequency 2.2MHz operation of the boost converter keeps switching noise outside of the AM band. The device achieves enhanced EMI performance by modulating the switching frequency by ±4%. The modulating signal is pseudorandom and changes each switching period (i.e.,  $f_{SS} = 2.2MHz$ ).

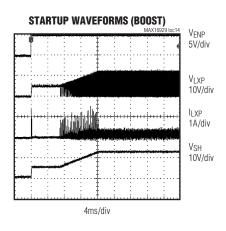

#### Startup

Immediately after power-up, coming out of shutdown, or going into autoretry, the boost converter performs a short-circuit detection test on the output by connecting the input (INA) to the switching node (LXP) through an internal  $50\Omega$  resistor.

If the resulting voltage on LXP exceeds 1.2V, the device turns on the external pMOS switch by pulling GATE low. The boost output ramps to its final value in 15ms.

An overloaded or shorted output is detected if the resulting voltage on LXP is below 1.2V. The external pMOS switch remains off and the converter does not switch. After the fault blanking period of 238ms, the device pulls PGOOD low and starts the autoretry timer.

The short-circuit detection feature places a lower limit on the output load of approximately  $46\Omega$  when the input voltage is 3V.

#### Fault Conditions and PGOOD

PGOOD signals whether all the regulators and the boost converter are operating normally. PGOOD is an opendrain output that pulls low if any of the following faults

- 1) The boost output voltage falls below 85% of its set value.

- 2) The positive-gate voltage regulator output (V<sub>GH</sub>) falls below 85% of its set value.

- 3) The negative-gate voltage regulator output (VGI) falls below 85% of its set value.

- 4) The LXP voltage is greater than 21V (typ).

- 5) The positive charge-pump voltage (V<sub>CP</sub>) is greater than 30.5V (typ).

- 6) The 1.8V/3.3V regulator output voltage falls below 85% of its nominal value.

- 7) The buck output voltage falls below 92% of its nominal value.

If any of the first three fault conditions persists for longer than the 238ms fault blanking period, the device pulls PGOOD low, turns off all outputs, and starts the autoretry

If either condition 4 or 5 occurs, the device pulls PGOOD low and turns off all outputs immediately. The device initiates startup only after the fault has cleared.

If condition 6 occurs, the device pulls PGOOD low, but does not turn off any of the outputs.

During startup, PGOOD is masked and goes high as soon as the 1.8V/3.3V regulator controller turns on. This regulator turns on as soon as  $V_{\mbox{\scriptsize INA}}$  exceeds the INA undervoltage lockout threshold.

#### Autoretry

When the autoretry counter finishes incrementing after 1.9s, the device attempts to turn on the boost converter and gate voltage regulators in the order shown in Table 1. The device continues to autoretry as long as the fault condition persists. A fault on the 1.8V/3.3V regulator output causes PGOOD to go low, but does not result in the device shutting down and going into autoretry.

#### **Current Limit**

The effective current limit of the boost converter is reduced by the internally injected slope compensation by an amount dependent on the duty cycle of the converter. The effective current limit is given by:

$$I_{LIM(EFF)} = 192 \times 10^{-12} \times I_{LIM\_DC\_0} \times \frac{D}{C_{COMPI}}$$

where  $I_{LIM(EFF)}$  is the effective current limit,  $I_{LIM DC 0} =$ 1.1A or 2.2A depending on the boost converter currentlimit option, D is the duty cycle of the boost converter, and C<sub>COMPI</sub> is the value of the capacitor at the COMPI input. Estimate the duty cycle of the converter using the formulas shown in the *Design Procedure* section.

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

#### 1.8V/3.3V Regulator Controller

The 1.8V/3.3V regulator controller delivers 4.5mA (min) to an external load. Connect FB to DR for a regulated 1.8V/3.3V output.

For higher output capability, use an external npn transistor as shown in the Typical Application Circuit. The drive capability of the regulator is then increased by the current gain of the transistor (hFF). When using an external transistor, use DR as the base drive and connect FB to the transistor's emitter. Bypass the base to ground with a 0.1µF ceramic capacitor.

If the boost output current is greater than 300mA, connect a  $30k\Omega$  resistor between DR and GND.

### Positive-Gate Voltage Regulator (GH)

The positive-gate voltage regulator includes a p-channel FET output stage to generate a regulated output between +5V and V<sub>CP</sub> - 2V. The regulator maintains accuracy over wide line and load conditions. It is capable of at least 20mA of output current and includes current-limit protection. VGH is typically used to provide the TFT-LCD gate drivers' gate-on voltage.

The regulator derives its positive supply voltage from a noninverting charge pump, a single-stage example of which is shown in the Typical Application Circuit. A higher voltage using a multistage charge pump is possible, as described in the Charge Pumps section.

#### **Negative-Gate Voltage Regulator (GL)**

The negative-gate voltage regulator is an analog gain block with an open-drain p-channel output. It drives an external npn pass transistor with a  $6.8k\Omega$  base-to-emitter resistor (see the Pass Transistor Selection section). Its guaranteed base drive source current is at least 2mA. VGI is typically used to provide the TFT-LCD gate drivers' gate-off voltage.

The output of the negative-gate voltage regulator (i.e., the collector of the external npn pass transistor) has loaddependent bypassing requirements. Connect a ceramic capacitor between the collector and ground with the value shown in Table 3.

The regulator derives its negative supply voltage from an inverting charge pump, a single-stage example of which is shown in the Typical Application Circuit. A more negative voltage using a multistage charge pump is possible as described in the Charge Pumps section.

The external npn transistor is not short-circuit protected. To maintain proper pulldown capability of external npn transistor and optimal regulation, a minimum load of at least 500µA is recommended on the output of the GL regulator.

#### Enable (ENP)

Use the enable input (ENP) to enable and disable the boost section of the device. Connect ENP to INA for normal operation and to GND to place the device in shutdown. In shutdown, the INA supply current is reduced to  $0.5 \mu A.$

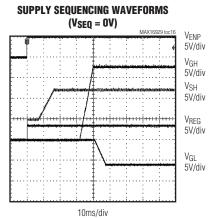

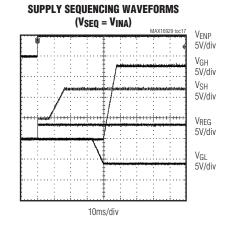

#### Soft-Start and Supply Sequencing (SEQ)

When enabled, the boost output ramps up from VINA to its set voltage. Once the boost output reaches 85% of the set voltage and the soft-start timer expires, the gate voltage regulators turn on in the order shown in Table 1. The 1.8V/3.3V regulator controller is enabled at the beginning of the boost converter's soft-start.

Both gate voltage regulators have a 7.45ms soft-start time. The second one turns on as soon as the output of the first reaches 85% of its set voltage.

#### Thermal Shutdown

Internal thermal shutdown circuitry shuts down the device immediately when the die temperature exceeds +165°C. A 15°C thermal shutdown hysteresis prevents the device from resuming normal operation until the die temperature falls below +150°C.

**Table 1. Supply Sequencing**

| CONTR | ROL INPUTS | SUPPLY SEQUENCING                               |                       |                 |  |  |  |

|-------|------------|-------------------------------------------------|-----------------------|-----------------|--|--|--|

| ENP   | SEQ        | FIRST SECOND THIRD                              |                       |                 |  |  |  |

| 0     | X          |                                                 | Device is in shutdown |                 |  |  |  |

| 1     | 0          | V <sub>SH</sub> V <sub>GH</sub> V <sub>GL</sub> |                       |                 |  |  |  |

| 1     | 1          | V <sub>SH</sub>                                 | V <sub>GL</sub>       | V <sub>GH</sub> |  |  |  |

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

### **Design Procedure**

#### **Buck Converter** Inductor Selection

Three key inductor parameters must be specified for operation with the device: inductance value (L), inductor saturation current (I<sub>SAT</sub>), and DC resistance (R<sub>DC</sub>). To determine the inductance value, select the ratio of inductor peak-to-peak ripple current to average output current (LIR) first. For LIR values that are too high, the RMS currents are high, and therefore I<sup>2</sup>R losses are high. Use high-valued inductors to achieve low LIR values. Typically, inductance is proportional to resistance for a given package type, which again makes I<sup>2</sup>R losses high for very low LIR values. A good compromise between size and loss is to select a 30%-to-60% peak-to-peak ripple current to average-current ratio. If extremely thin high-resistance inductors are used, as is common for LCD-panel applications, the best LIR can increase between 0.5 and 1.0. The size of the inductor is determined as follows:

$$L = \frac{(V_{INB} - V_O) \times D}{LIR \times I_O \times f_{SWB}}$$

and

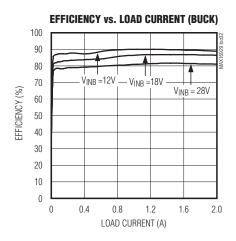

$$D = \frac{V_O}{\eta \times V_{INIB}}$$

where  $V_{\mbox{\scriptsize INB}}$  is the input voltage,  $V_{\mbox{\scriptsize O}}$  is the output voltage,  $I_O$  is the output current,  $\eta$  is the efficiency of the buck converter, D is the duty cycle, and fSWB is 2.1MHz (the switching frequency of the buck converter). The efficiency of the buck converter can be estimated from the Typical Operating Characteristics and accounts for losses in the internal switch, catch diode, inductor RDC, and capacitor ESR.

To ensure the buck converter does not shut down during load dump input-voltage transients to 42V, an inductor value larger than calculated above should be used. Table 2 lists the minimum inductance that should be used for proper operation during load dump. The saturation current rating (ISAT) must be high enough to ensure that saturation can occur only above the maximum current-limit value. Find a low-loss inductor having the lowest possible DC resistance that fits in the allotted dimensions.

Table 2. Minimum Buck Inductor Value **Required for Normal Operation During Load Dump**

| BUCK V <sub>OUTB</sub> (V) | BUCK I <sub>OUTB</sub> (A) | L <sub>MIN</sub> (μH) |

|----------------------------|----------------------------|-----------------------|

| 3.3                        | 1.2                        | 3.3                   |

| 3.3                        | 2                          | 6.8                   |

| 5                          | 1.2                        | 3.3                   |

| 5                          | 2                          | 4.7                   |

#### Capacitor Selection

The input and output filter capacitors should be of a low-ESR type (tantalum, ceramic, or low-ESR electrolytic) and should have I<sub>RMS</sub> ratings greater than:

$$I_{INB(RMS)} = I_{OV} \sqrt{D \times (1-D + \frac{LIR^2}{12})}$$

for the input capacitor

$$I_{OUTB(RMS)} = \frac{LIR \times I_O}{\sqrt{12}}$$

for the output capacitor

where D is the duty cycle given above.

The output voltage contains a ripple component whose peak-to-peak value depends on the value of the ESR and capacitance of the output capacitor, and is approximately given by:

$$\Delta V_{RIPPLE} = \Delta V_{ESR} + \Delta V_{CAP}$$

$$\Delta V_{ESR} = LIR \times I_O \times R_{ESR}$$

$$\Delta V_{CAP} = \frac{LIR \times I_O}{8 \times C \times f_{SWB}}$$

#### **Diode Selection**

The catch diode should be a Schottky type to minimize its voltage drop and maximize efficiency. The diode must be capable of withstanding a reverse voltage of at least the maximum input voltage in the application. The diode should have an average forward current rating greater than:

$$I_D = I_O \times (1-D)$$

where D is the duty cycle given above. In addition, ensure that the peak current rating of the diode is greater than:

$$I_{OUTB} \times \left(1 + \frac{LIR}{2}\right)$$

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

### **Boost Converter**

#### Inductor Selection

Three key inductor parameters must be specified for operation with the device: inductance value (L), inductor saturation current (I<sub>SAT</sub>), and DC resistance (R<sub>DC</sub>). To determine the inductance value, select the ratio of inductor peak-to-peak ripple current to average input current (LIR) first. For LIR values that are too high, the RMS currents are high, and therefore I<sup>2</sup>R losses are high. Use high-valued inductors to achieve low LIR values. Typically, inductance is proportional to resistance for a given package type, which again makes I<sup>2</sup>R losses high for very low LIR values. A good compromise between size and loss is to select a 30%-to-60% peak-to-peak ripple current to average-current ratio. If extremely thin high-resistance inductors are used, as is common for LCD-panel applications, the best LIR can increase between 0.5 and 1.0. The size of the inductor is determined as follows:

$$L = \frac{V_{INA} \times D}{LIR \times I_{INP} \times f_{SW}} \text{ and } I_{INP} = \frac{V_O \times I_O}{\eta V_{INA}}$$

$$D = 1 - \frac{\eta V_{INA}}{V_{O}}$$

where V<sub>INA</sub> is the input voltage, V<sub>O</sub> is the output voltage, IO is the output current, IINP is the average boost input current,  $\eta$  is the efficiency of the boost converter, D is the duty cycle, and f<sub>SW</sub> is 2.2MHz (the switching frequency of the boost converter). The efficiency of the boost converter can be estimated from the Typical Operating Characteristics and accounts for losses in the internal switch, catch diode, inductor RDC, and capacitor ESR.

#### Capacitor Selection

The input and output filter capacitors should be of a low-ESR type (tantalum, ceramic, or low-ESR electrolytic) and should have I<sub>RMS</sub> ratings greater than:

$$I_{RMS} = \frac{LIR \times I_{INP}}{\sqrt{12}}$$

for the input capacitor

$$I_{RMS} = I_{O} \sqrt{\frac{D + \frac{LIR^{2}}{12}}{1 - D}}$$

for the output capacitor

where I<sub>INP</sub> and D are the input current and duty cycle given above.

The output voltage contains a ripple component whose peak-to-peak value depends on the value of the ESR and capacitance of the output capacitor and is approximately given by:

$$\Delta V_{RIPPLE} = \Delta V_{ESR} + \Delta V_{CAP}$$

$$\Delta V_{ESR} = I_{INP} \times (1 + \frac{LIR}{2}) \times R_{ESR}$$

$$\Delta V_{CAP} = \frac{I_O \times D}{C_{OUT} \times f_{SW}}$$

where I<sub>INP</sub> and D are the input current and duty cycle given above.

#### Rectifier Diode

The catch diode should be a Schottky type to minimize its voltage drop and maximize efficiency. The diode must be capable of withstanding a reverse voltage of at least V<sub>SH</sub>. The diode should have an average forward current rating greater than:

$$I_D = I_{INP} \times (1-D)$$

where I<sub>INP</sub> and D are the input current and duty cycle given above. In addition ensure that the peak current rating of the diode is greater than:

$$I_{\text{INP}} \times \left(1 + \frac{\text{LIR}}{2}\right)$$

### **Output-Voltage Selection**

The output voltage of the boost converter can be adjusted by using a resistive voltage-divider formed by RTOP and RBOTTOM. Connect RTOP between the output and FBP and connect  $R_{\mbox{\footnotesize{BOTTOM}}}$  between FBP and GND. Select  $R_{\mbox{\footnotesize{BOTTOM}}}$  in the  $10\mbox{\footnotesize{k}}\Omega$  to  $50\mbox{\footnotesize{k}}\Omega$  range. Calculate R<sub>TOP</sub> with the following equation:

$$R_{TOP} = R_{BOTTOM} \times (\frac{V_O}{V_{FBP}} - 1)$$

where V<sub>FBP</sub>, the boost converter's feedback set point, is 1V. Place both resistors as close as possible to the device and connect RBOTTOM to the analog ground plane.

#### Loop Compensation

Choose R<sub>COMPV</sub> to set the high-frequency integrator gain for fast transient response. Choose C<sub>COMPV</sub> to set the integrator zero to maintain loop stability. For low-ESR output capacitors, use Table 3 to select the initial values for R<sub>COMPV</sub> and C<sub>COMPV</sub>. Use a 22pF capacitor in parallel with RCOMPV + CCOMPV.

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

Table 3. Compensation Component Values

| V <sub>SH</sub> (V)     | 8    | 18   |

|-------------------------|------|------|

| I <sub>SH</sub> (mA)    | 200  | 200  |

| V <sub>INA</sub> (V)    | 3.3  | 5    |

| P <sub>IN</sub> (W)     | 1.75 | 3.75 |

| L (µH)                  | 5    | 5    |

| R <sub>COMPV</sub> (kΩ) | 33   | 39   |

| C <sub>COMPV</sub> (pF) | 220  | 180  |

| C <sub>COMPI</sub> (pF) | 820  | 330  |

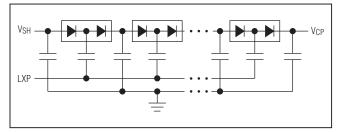

Figure 2. Multistage Charge Pump for Positive Output Voltage

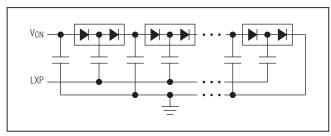

Figure 3. Multistage Charge Pump for Negative Output Voltage

To further optimize transient response, vary R<sub>COMPV</sub> in 20% steps and C<sub>COMPV</sub> in 50% steps while observing transient-response waveforms. The ideal transient response is achieved when the output settles quickly with little or no overshoot. Connect the compensation network to the analog ground plane.

Use the following formula to calculate the value for C<sub>COMPI</sub>:

CCOMPI ≤ 950 × 10-6 × L/(V<sub>SH</sub> + V<sub>SCHOTTKY</sub> - V<sub>INA</sub>)

#### p-Channel FET Selection

The p-channel FET used to gate the boost converter's input should have low on-resistance. Connect a resistor (RSG) between the source and gate of the FET. Under normal operation, RSG carries a gate drive current of

55µA and the resulting gate source voltage (VGS) turns on the FET. When the gate drive is removed under a fault condition or in shutdown, RSG bleeds off charge to turn off the FET. Size RSG to produce the VGS needed to turn on the FET.

### 1.8V/3.3V Regulator Controller npn Bipolar Transistor Selection

There are two important considerations in selecting the pass npn bipolar transistor: current gain (hFF) and power dissipation. Select a transistor with an hFF high enough to ensure adequate drive capability. This condition is satisfied when IDR x (hFE + 1) is greater than the maximum load current. The regulator can source  $I_{DR} = 4.5 \text{mA}$  (min). The transistor should be capable of dissipating:

$P_{NPN\_REG} = (V_{INA} - V_{REG\_OUT}) \times I_{LOAD(MAX)}$ where  $V_{RFG}$  OUT = 1.8V or 3.3V. Bypass DR to ground with a 0.1µF ceramic capacitor. For applications in which the boost output current exceeds 300mA, connect a  $30k\Omega$  resistor from DR to ground.

#### Supply Considerations

INA needs to be at least 4.5V for the 3.3V regulator to operate properly.

#### **Charge Pumps**

#### Selecting the Number of Charge-Pump Stages

For most applications, a single charge-pump stage is sufficient, as shown in the Typical Application Circuit. Connect the flying capacitors to LXP. The output voltages generated on the storage capacitors are given by:

$$V_{CP} = 2 \times V_{SH} + V_{SCHOTTKY} - 2 \times V_{D}$$

$V_{CN} = -(V_{SH} + V_{SCHOTTKY} - 2 \times V_{D})$

where V<sub>CP</sub> is the positive supply for the positive-gate voltage regulator, and V<sub>CN</sub> is the negative supply for the negative-gate voltage regulator. Where larger output voltages are needed, use multistage charge pumps (however, the maximum charge-pump voltage is limited by the absolute maximum ratings of CP and DRVN). Figure 2 and Figure 3 show the configuration of a multistage charge pump for both positive and negative output voltages.

For mutistage charge pumps the output voltages are:

$$V_{CP} = V_{SH} + n \times (V_{SH} + V_{SCHOTTKY} - 2 \times V_D)$$

$V_{CN} = -n \times (V_{SH} + V_{SCHOTTKY} - 2 \times V_D)$

For highest efficiency, choose the lowest number of charge-pump stages that meets the output requirement.

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

The number of positive charge-pump stages needed is given by:

$$n_{CP} = \frac{V_{GH} + V_{DROPOUT} - V_{SH}}{V_{SH} + V_{SCHOTTKY} - 2 \times V_{D}}$$

and the number of negative charge-pump stages is given by:

$$n_{CN} = \frac{|V_{GL}| + V_{DROPOUT}}{V_{SH} + V_{SCHOTTKY} - 2 \times V_{D}}$$

where n<sub>CP</sub> is the number of positive charge-pump stages, n<sub>CN</sub> is the number of negative charge-pump stages, V<sub>GH</sub> is the positive-gate voltage regulator output voltage, V<sub>GL</sub> is the negative-gate voltage regulator output voltage, V<sub>SH</sub> is the boost converter's output voltage, V<sub>D</sub> is the forward-voltage drop of the charge-pump diode, V<sub>SCHOTTKY</sub> is the forward drop of the Schottky diode of the boost converter, and VDROPOUT is the dropout margin for the regulator. Use  $V_{DROPOUT} = 0.3V$  for the negative voltage regulator and VDROPOLIT = 2V at 20mA for the positive-gate voltage regulator.

#### Flying Capacitors

Increasing the flying capacitor (C<sub>X</sub>) value lowers the effective source impedance and increases the output current capability. Increasing the capacitance indefinitely has a negligible effect on output current capability because the internal switch resistance and the diode impedance place a lower limit on the source impedance. A 0.1µF ceramic capacitor works well in most low-current applications. The voltage rating of the flying capacitors for the positive charge pump should exceed VCP, and that for the negative charge pump should exceed the magnitude of V<sub>CN</sub>.

#### Charge-Pump Output Capacitor

Increasing the output capacitance or decreasing the ESR reduces the output-ripple voltage and the peak-to-peak transient voltage. With ceramic capacitors, the outputvoltage ripple is dominated by the capacitance value. Use the following equation to approximate the required output capacitance for the noninverting charge pump connected to CP:

$$C_{OUT\_CP} \ge \frac{D \times I_{LOAD\_CP}}{f_{SW} \times V_{RIPPLE}}$$

where COUT CP is the output capacitor of the charge pump, D is the duty cycle of the boost converter, ILOAD CP is the load current of the charge pump, fsw is the switching frequency of the boost converter, and VRIPPLE CP is the peak-to-peak value of the output ripple.

For the inverting charge pump connected to CN, use the following equation to approximate the required output capacitance:

$$C_{OUT\_CN} \ge \frac{(1-D) \times I_{LOAD\_CN}}{f_{SW} \times V_{RIPPLE\_CN}}$$

where C<sub>OUT</sub> c<sub>N</sub> is the output capacitor of the charge pump. D is the duty cycle of the boost converter. ILOAD CN is the load current of the charge pump, fsw is the switching frequency of the boost converter, and VRIPPLE CN is the peak-to-peak value of the output ripple.

#### Charge-Pump Rectifier Diodes

Use high-speed silicon switching diodes with a current rating equal to or greater than two times the average charge-pump input current. If it helps avoid an extra stage, some or all of the diodes can be replaced with Schottky diodes with an equivalent current rating.

### **Positive-Gate Voltage Regulator Output-Voltage Selection**

The output voltage of the positive-gate voltage regulator can be adjusted by using a resistive voltage-divider formed by RTOP and RBOTTOM. Connect RTOP between the output and FBGH, and connect RBOTTOM between FBGH and GND. Select  $R_{BOTTOM}$  in the  $10k\Omega$  to  $50k\Omega$ range. Calculate R<sub>TOP</sub> with the following equation:

$$R_{TOP} = R_{BOTTOM} \times (\frac{V_{GH}}{V_{EBGH}} - 1)$$

where  $V_{GH}$  is the desired output voltage and  $V_{FBGH} = 1V$ (the regulated feedback voltage for the regulator). Place both resistors as close as possible to the device.

Avoid excessive power dissipation within the internal pMOS device of the regulator by paying attention to the voltage drop across the drain and source. The amount of power dissipation is given by:

$$P_{GL} = (V_{CP} - V_{GH}) \times I_{LOAD(MAX)}$$

where V<sub>CP</sub> is the noninverting charge-pump output voltage applied to the drain, VGH is the regulated output voltage, and I<sub>LOAD(MAX)</sub> is the maximum load current.

#### Stability Requirements

The positive-gate voltage regulator (GH) requires a minimum output capacitance for stability. For an output

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

voltage of 5V to (VCP - 2V) and an output current of 10mA to 15mA, use a minimum capacitance of 0.47µF.

### **Negative-Gate Voltage Regulator Output-Voltage Selection**

The output voltage of the negative-gate voltage regulator can be adjusted by using a resistive voltage-divider formed by R<sub>TOP</sub> and R<sub>BOTTOM</sub>. Connect R<sub>TOP</sub> between REF and FBGL, and connect RBOTTOM between FBGL and the collector of the external npn transistor. Select  $R_{TOP}$  greater than  $20k\Omega$  to avoid loading down the reference output. Calculate RBOTTOM with the following equation:

$$R_{BOTTOM} = R_{TOP} \times \frac{V_{FBGL} - V_{GL}}{V_{REF} - V_{FBGL}}$$

where  $V_{GL}$  is the desired output voltage,  $V_{REF}$  = 1.25V, and  $V_{FBGL} = 0.25V$  (the regulated feedback voltage of the regulator).

#### Pass Transistor Selection

The pass transistor must meet specifications for current gain (hFF), input capacitance, collector-emitter saturation voltage, and power dissipation. The transistor's current gain limits the guaranteed maximum output current to:

$$I_{LOAD(MAX)} = (I_{DRVN} - \frac{V_{BE}}{R_{BE}}) \times h_{FE(MIN)}$$

where IDRVN is the minimum guaranteed base-drive current, V<sub>BF</sub> is the transistor's base-to-emitter forward voltage drop, and RBE is the pulldown resistor connected between the transistor's base and emitter. Furthermore, the transistor's current gain increases the regulator's DC loop gain (see the Stability Requirements section), so excessive gain destabilizes the output.

The transistor's saturation voltage at the maximum output current determines the minimum input-to-output voltage differential that the regulator can support. Also, the package's power dissipation limits the usable maximum input-to-output voltage differential. The maximum powerdissipation capability of the transistor's package and mounting must exceed the actual power dissipated in the device. The power dissipated equals the maximum load current (I<sub>LOAD(MAX)</sub> GL) multiplied by the maximum input-to-output voltage differential:

$$P_{NPN\_GL} = (V_{GL} - V_{CN}) \times I_{LOAD(MAX)\_GL}$$

where V<sub>GL</sub> is the regulated output voltage on the collector of the transistor, V<sub>CN</sub> is the inverting charge-pump output voltage applied to the emitter of the transistor, and I<sub>LOAD(MAX)</sub> GL is the maximum load current. Note that the external transistor is not short-circuit protected.

#### Stability Requirements

The device's negative-gate voltage regulator uses an internal transconductance amplifier to drive an external pass transistor. The transconductance amplifier, the pass transistor, the base-emitter resistor, and the output capacitor determine the loop stability.

The transconductance amplifier regulates the output voltage by controlling the pass transistor's base current. The total DC loop gain is approximately:

$$A_{V\_GL} \cong (\frac{4}{V_T}) \times (1 + \frac{I_{BIAS} \times h_{FE}}{I_{LOAD}}) \times V_{REF}$$

where V<sub>T</sub> is 26mV at room temperature, and I<sub>BIAS</sub> is the current through the base-to-emitter resistor (RBE). For the device, the bias current for the negative-gate voltage regulator is 0.1mA. Therefore, the base-to-emitter resistor should be chosen to set 0.1mA bias current:

$$R_{BE} = \frac{V_{BE}}{0.1 \text{mA}} = \frac{0.7 \text{V}}{0.1 \text{mA}} = 7 \text{k}\Omega$$

Use the closest standard resistor value of  $6.8k\Omega$ . The output capacitor and the load resistance create the dominant pole in the system. However, the internal amplifier delay, pass transistor's input capacitance, and the stray capacitance at the feedback node create additional poles in the system, and the output capacitor's ESR generates a zero. For proper operation, use the following equations to verify that the regulator is properly compensated:

1) First, determine the dominant pole set by the regulator's output capacitor and the load resistor:

$$f_{POLE\_GL} = \frac{I_{LOAD(MAX)\_GL}}{2\pi \times C_{OUT\ GL} \times V_{OUT\ GL}}$$

The unity-gain crossover frequency of the regulator is:

2) The pole created by the internal amplifier delay is approximately 1MHz:

$$f_{POLE\_AMP} = 1MHz$$

3) Next, calculate the pole set by the transistor's input capacitance, the transistor's input resistance, and the base-to-emitter pullup resistor:

## **Automotive TFT-LCD Power Supply with Boost Converter and Gate Voltage Regulators**

$$f_{POLE\_IN} = \frac{1}{2\pi \times C_{IN} \times (R_{BE}/R_{IN})}$$

where:

$$C_{IN} = \frac{g_m}{2\pi f_T}, R_{IN} = \frac{h_{FE}}{g_m}$$

gm is the transconductance of the pass transistor, and f<sub>T</sub> is the transition frequency. Both parameters can be found in the transistor's data sheet. Because RBE is much greater than RIN, the above equation can be simplified:

$$f_{POLE\_IN} = \frac{1}{2\pi \times C_{IN} \times R_{IN}}$$

Substituting for CIN and RIN yields:

$$f_{POLE} = \frac{f_T}{h_{FE}}$$

4) Next, calculate the pole set by the regulator's feedback resistance and the capacitance between FBGL and GND (including stray capacitance):

$$f_{POLE\_FBGL} = \frac{1}{2\pi \times C_{FBGL} \times (R_{TOP}/R_{BOTTOM})}$$

where CFBGL is the capacitance between FBGL and GND and is equal to 30pF, R<sub>TOP</sub> is the upper resistor of the regulator's feedback divider, and R<sub>BOTTOM</sub> is the lower resistor of the divider.

5) Next, calculate the zero caused by the output capacitor's ESR:

$$f_{ZERO\_ESR} = \frac{1}{2\pi \times C_{OUT}} \frac{1}{LR \times R_{ESR}}$$

where R<sub>ESR</sub> is the equivalent series resistance of COUT LR. To ensure stability, make COUT LR large enough so the crossover occurs well before the poles and zero calculated in steps 2 to 5. The poles in steps 3 and 4 generally occur at several MHz and using ceramic capacitors ensures the ESR zero also occurs at several MHz. Placing the crossover frequency below 500kHz is sufficient to avoid the amplifier delay pole and generally works well, unless unusual component choices or extra capacitances move one of the other poles or the zero below 1MHz.