### Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **General Description**

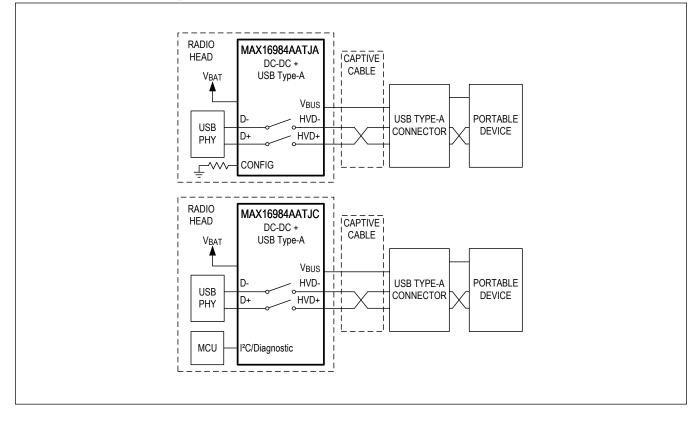

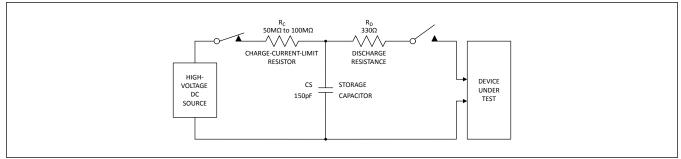

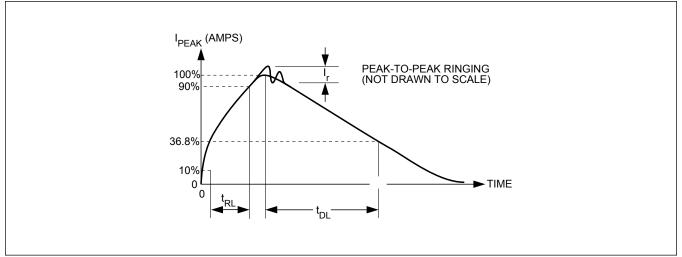

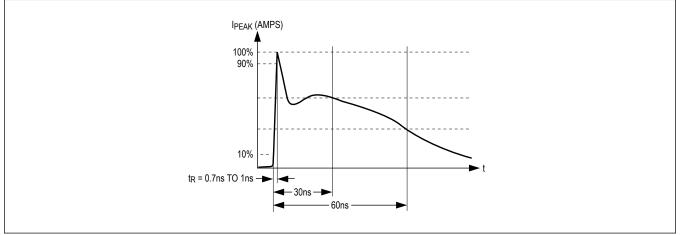

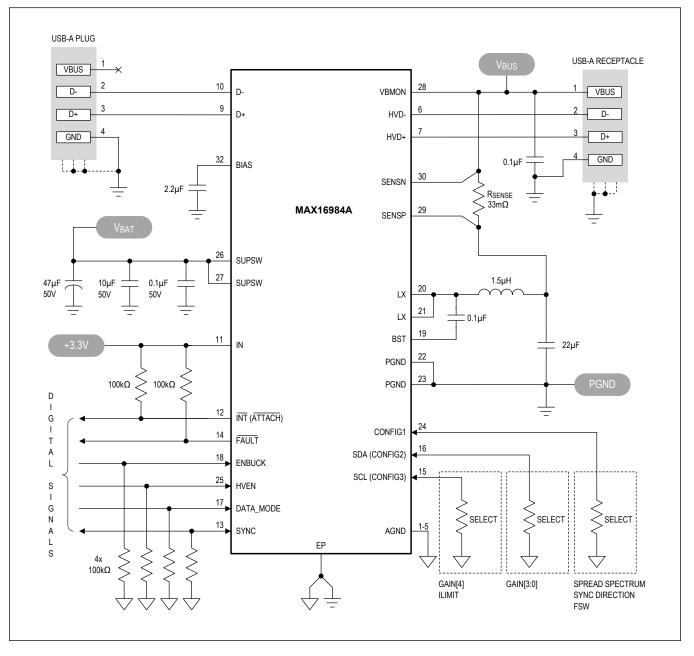

The MAX16984A combines a 5V automotive-grade stepdown converter capable of driving up to 3.0A, a USB host charger adapter emulator, and USB protection switches for automotive USB host applications. The USB protection switches provide high-ESD, short-circuit protection and feature integrated host-charger port-detection circuitry adhering to the USB 2.0 BC 1.2 Battery Charging Specification, Samsung® and Chinese Telecommunication Industry Standard YD/T 1591-2009. They also include circuitry for Samsung 2.0A, iPod®/iPhone®/iPad® 2.4A dedicated charging modes. The HVD+ and HVD- ESD protection features include protection to  $\pm$ 15kV Air/ $\pm$ 8kV Contact on the HVD+ and HVD- outputs to the IEC 61000-4-2 model and 330 $\Omega$ , 330pF ISO model.

The high-efficiency step-down DC-DC converter operates from a voltage up to 28V and is protected from load dump transients up to 40V. The device is optimized for high-frequency operation and includes I<sup>2</sup>C or resistor-programmable frequency selection from 310kHz to 2.2MHz to allow optimization of efficiency, noise, and board space based on application requirements. The fully synchronous DC-DC converter integrates high-side and low-side MOSFETs with an external SYNC input/output, and can be configured for spread-spectrum operation. Skip mode is available in light/no-load conditions to minimize quiescent current. The converter can deliver up to 3A of continuous current at 105°C. The MAX16984A has an integrated spreadspectrum oscillator to improve EMI performance.

The MAX16984A also includes a USB load current-sense amplifier and configurable feedback adjustment circuit designed to provide automatic USB voltage adjustment to compensate for voltage drops in captive cables associated with automotive applications. The MAX16984A limits the USB load current using both a fixed internal peak current threshold of the DC-DC converter and a user-configurable external USB load current-sense amplifier threshold.

### **Applications**

- Automotive Radio and Navigation

- USB Port for Host and Hub Applications

- Automotive Connectivity

- Telematics

- Dedicated USB Power Charger

### **Benefits and Features**

- Integrated DC-DC and USB Host Charge Emulator Enables 1-Chip Solution Directly from Car Battery to Portable Device

- 4.5V to 28V (40V Load Dump) Operating Voltage

- 5V, 3.0A Output Current Capability

- · Low-Q Current Skip and Shutdown Modes

- Soft-Start Reduces Inrush Current

- Low-Noise Features Prevent Interference with AM Band and Portable Devices

- Fixed-Frequency 310kHz to 2.2MHz Operation

- Forced-PWM Option at No Load

- Spread Spectrum for EMI Reduction

- SYNC Input/Output for Frequency Parking

- Optimal USB Power and Communication for Portable

Devices

- User-Adjustable Voltage Gain Adjusts Output Between 5V and 7V for Cable Compensation

- ±5% Accuracy User-Adjustable USB Current Limit

- 4Ω USB 2.0 1GHz Data Switches

- Integrated Samsung/iPod/iPhone/iPad Charge-Detection Termination Resistors

- Supports USB BC1.2 Charging Downstream Port (CDP) and Dedicated Charging Port (DCP) Modes

- Supports Chinese Telecommunication Industry Standard YD/T 1591-2009

- · Compatible with USB On-the-Go Specification

- High-Speed Pass-Through Mode (SDP)

- Robust Design Keeps Vehicle System and Portable

Devices Safe in Automotive Environment

- Short-to-Battery Protection on DC-DC Converter

- Short-to-Battery Protection on USB Pins

- ±15kV Air/±8kV Contact ISO 10605\*

- ±15kV Air/±8kV Contact IEC 61000-4-2\*

- ±15kV Air/±8kV Contact (330Ω, 330pF)\*

- Advanced Diagnostics Through I<sup>2</sup>C Bus

- Reduced Inrush Current with Soft-Start

- Over-temperature Protection

- -40°C to +125°C Operating Temperature Range

- 32-Pin, 5mm x 5mm, TQFN Package

\*Tested in Typical Application Circuit as used on the MAX16984A Evaluation Kit

<u>Ordering Information</u> and <u>Typical Application Circuit</u> appear at end of data sheet.

Apple, iPod, iPhone, iPad and CarPlay are registered trademarks of Apple, Inc. Samsung is a registered trademark of Samsung Electronics Co., Ltd.

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

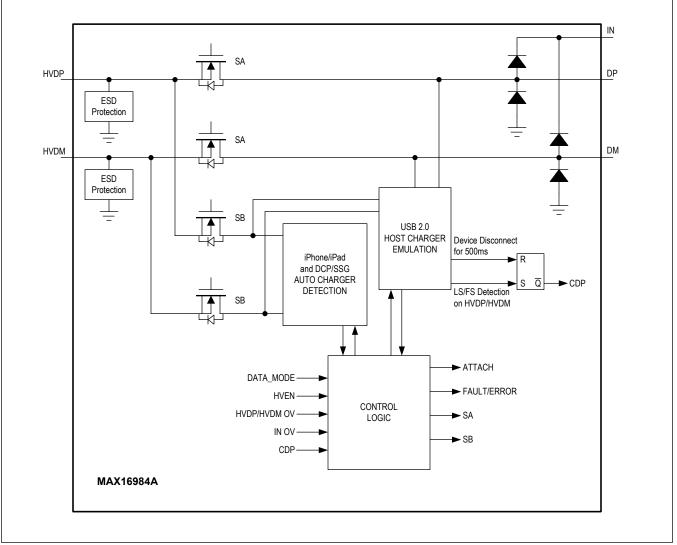

### Simplified Block Diagram

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **Absolute Maximum Ratings**

| SUPSW to PGND                  | 0.3V to +40V                       | LX Continuous RMS Current                             | 3.5A           |

|--------------------------------|------------------------------------|-------------------------------------------------------|----------------|

| HVEN to PGND                   | -0.3V to V <sub>SUPSW</sub> + 0.3V | Output Short-Circuit Duration                         |                |

| LX to PGND (Note 1)            | -0.3V to V <sub>SUPSW</sub> + 0.3V | Thermal Characteristics                               |                |

| SYNC to AGND                   | 0.3V to V <sub>BIAS</sub> + 0.3V   | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                |

| SENSN, SENSP, VBMON to AGND    | -0.3V to V <sub>SUPSW</sub> + 0.3V | TQFN Single-Layer Board                               |                |

| AGND to PGND                   | 0.3V to +0.3V                      | (derate 21.3mW/°C above +70°C)                        |                |

| BST to PGND                    | 0.3V to +46V                       | TQFN Multilayer Board                                 |                |

| BST to LX                      | 0.3V to +6V                        | (derate 34.5mW/°C above +70°C)                        | 2758.6mW       |

| IN, CONFIG1, ENBUCK, SDA (CONF | FIG2), SCL (CONFIG3),              | Operating Temperature Range                           |                |

| BIAS, DATA_MODE, FAULT, SHIEL  | D, INT (ATTACH) to                 | Junction Temperature                                  | +150°C         |

| AGND                           | 0.3V to +6V                        | Storage Temperature Range                             | 40°C to +150°C |

| HVDP, HVDM to AGND             | 0.3V to +18V                       | Lead Temperature (soldering, 10s)                     |                |

| DP, DM to AGND                 | 0.3V to V <sub>IN</sub> + 0.3V     | Soldering Temperature (reflow)                        | +260°C         |

Note 1: Self-protected from transient voltages exceeding these limits ≤ 50ns in circuit under normal operation.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 32-Pin TQFN

| Package Code                                          | T3255+4C       |  |  |  |  |  |

|-------------------------------------------------------|----------------|--|--|--|--|--|

| Outline Number                                        | <u>21-0140</u> |  |  |  |  |  |

| Land Pattern Number                                   | <u>90-0012</u> |  |  |  |  |  |

| THERMAL RESISTANCE, SINGLE-LAYER BOARD                |                |  |  |  |  |  |

| Junction-to-Ambient (0 <sub>JA</sub> )                | 47°C/W         |  |  |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 1.70°C/W       |  |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                  |                |  |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 29°C/W         |  |  |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 1.70°C/W       |  |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/</u> <u>thermal-tutorial</u>.

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **Electrical Characteristics**

$(V_{SUPSW} = 14V, V_{ENBUCK} = V_{IN} = 3.3V$ , temperature =  $T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are  $T_A = +25^{\circ}C$  under normal conditions.) (Note 3)

| PARAMETER                                           | SYMBOL                | CONDITIONS                                                                                                                                                                 | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| POWER SUPPLY AND E                                  | NABLE                 |                                                                                                                                                                            |      |      |      |       |

| Supply Voltage Range                                | V <sub>SUPSW</sub>    | (Note 2)                                                                                                                                                                   | 4.5  |      | 28   | V     |

| Load Dump Event<br>Supply Voltage Range             | V <sub>SUPSW_LD</sub> | t < 1s                                                                                                                                                                     |      |      |      | V     |

|                                                     |                       | $V_{SUPSW}$ = 18V; $V_{HVEN}$ = 0V; $V_{IN}$ = 0V; $V_{CONN}$ = 0V, Off State                                                                                              |      | 10   | 20   | μA    |

| Supply Current                                      | ISUPSW                | HVEN = 14V; buck switching; no load;<br>skip mode                                                                                                                          |      | 1.8  |      |       |

|                                                     |                       | HVEN = 14V; buck switching; no load;<br>FPWM mode                                                                                                                          |      | 28   |      | mA    |

| BIAS Voltage                                        | VBIAS                 | 5.75V ≤ V <sub>SUPSW</sub> ≤ 28V                                                                                                                                           | 4.5  | 4.7  | 5.25 | V     |

| BIAS Current Limit                                  |                       |                                                                                                                                                                            | 50   | 150  |      | mA    |

| BIAS Undervoltage<br>Lockout                        | V <sub>UV_BIAS</sub>  | V <sub>BIAS</sub> rising                                                                                                                                                   | 3.0  | 3.3  | 3.6  | V     |

| BIAS Undervoltage<br>Lockout Hysteresis             |                       |                                                                                                                                                                            |      | 0.2  |      | V     |

| SUPSW Undervoltage<br>Lockout                       |                       | V <sub>SUPSW</sub> rising                                                                                                                                                  | 3.9  |      | 4.42 | V     |

| SUPSW Undervoltage<br>Lockout Hysteresis            |                       |                                                                                                                                                                            |      | 0.2  |      | V     |

| IN Voltage Range                                    | V <sub>IN</sub>       |                                                                                                                                                                            | 3    |      | 3.6  | V     |

| IN Overvoltage Lockout                              | VIN_OVLO              | V <sub>IN</sub> rising                                                                                                                                                     | 3.8  | 4    | 4.3  | V     |

| IN Input Current                                    | I <sub>IN</sub>       |                                                                                                                                                                            |      |      | 10   | μA    |

| HVEN Rising Threshold                               | V <sub>HVEN</sub> R   |                                                                                                                                                                            | 0.6  | 1.5  | 2.4  | V     |

| HVEN Falling Threshold                              | V <sub>HVEN_</sub> F  |                                                                                                                                                                            |      |      | 0.4  | V     |

| HVEN Hysteresis                                     | V <sub>HVEN</sub>     |                                                                                                                                                                            |      | 0.2  |      | V     |

| HVEN Delay Rising                                   | <sup>t</sup> HVEN_R   |                                                                                                                                                                            | 2.5  |      | 15   | μs    |

| HVEN Delay Falling                                  | <sup>t</sup> HVEN_F   |                                                                                                                                                                            | 5    | 12   | 25   | μs    |

| HVEN Input Leakage                                  |                       | V <sub>HVEN</sub> = V <sub>SUPSW</sub> = 18V, V <sub>HVEN</sub> = 0V                                                                                                       |      |      | 10   | μA    |

| DP, DM ANALOG USB S                                 | WITCHES               |                                                                                                                                                                            |      |      |      |       |

| On-Channel -3dB<br>Bandwidth                        | BW                    | $R_L = R_S = 50\Omega$                                                                                                                                                     |      | 1000 |      | MHz   |

| Analog Signal Range                                 |                       |                                                                                                                                                                            | 0    |      | 3.6  | V     |

| Protection Trip<br>Threshold                        | V <sub>OV_D</sub>     |                                                                                                                                                                            | 3.65 | 3.85 | 4.1  | V     |

| Protection Response<br>Time                         | t <sub>FP_D</sub>     | $ \begin{array}{l} V_{IN} = 4.0V,  V_{HVD\pm} = 3.3V \text{ to } 4.3V \text{ step}, \\ R_L = 15 k\Omega \text{ on } D^{\pm},  \text{delay to } V_{D\pm} < 3V \end{array} $ |      | 2    |      | μs    |

| On-Resistance Switch A                              | R <sub>ON_SA</sub>    | $I_L = 10$ mA, $V_D = 0$ V to $V_{IN}$ , $V_{IN} = 3.0$ V to 3.6V                                                                                                          |      | 4    | 8    | Ω     |

| On-Resistance Match<br>between Channels<br>Switch A | ∆R <sub>ON_SA</sub>   | I <sub>L</sub> = 10mA, V <sub>D</sub> _= 1.5V or 3.0V                                                                                                                      |      |      | 0.2  | Ω     |

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **Electrical Characteristics (continued)**

$(V_{SUPSW} = 14V, V_{ENBUCK} = V_{IN} = 3.3V, temperature = T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are T\_A = +25°C under normal conditions.) (Note 3)

| PARAMETER                                             | SYMBOL                  | CONDITIONS                                                                                     | MIN  | TYP   | MAX  | UNITS |  |  |  |

|-------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------|------|-------|------|-------|--|--|--|

| On-Resistance Flatness<br>Switch A                    | R <sub>FLAT(ON)</sub> A | I <sub>L</sub> = 10mA,V <sub>D</sub> _= 0V or 0.4V                                             |      | 0.01  |      | Ω     |  |  |  |

| On-Resistance of<br>HVD+/HVD- short                   | R <sub>SHORT</sub>      | V <sub>DP</sub> = 1V, I <sub>DM</sub> = 500µA                                                  |      | 90    | 180  | Ω     |  |  |  |

| HVD+/HVD- On-<br>Leakage Current                      | IHVD_ON                 | V <sub>HVD±</sub> = 3.6V or 0V                                                                 | -7   |       | +7   | μA    |  |  |  |

| HVD+/HVD- Off-<br>Leakage Current                     | I <sub>HVD_OFF</sub>    | $V_{HVD+} \rightarrow 18V \text{ or } V_{HVD-} = 18V, V_{D\pm} = 0V$                           |      |       | 150  | μA    |  |  |  |

| D+/D- Off-Leakage<br>Current                          | ID_OFF                  | V <sub>HVD±</sub> = 18V, V <sub>D±</sub> = 0V                                                  | -1   |       | +1   | μA    |  |  |  |

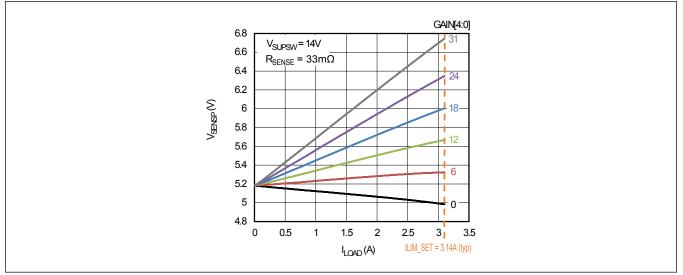

| CURRENT-SENSE AMPL                                    | IFIER (SENSP,           | SENSN) AND ANALOG INPUTS (VBMON)                                                               |      |       |      |       |  |  |  |

| Gain                                                  |                         | 10mV < V <sub>SENSP</sub> - V <sub>SENSN</sub> < 110mV,<br>GAIN[4:0] = 0b11111                 |      | 19.4  |      | V/V   |  |  |  |

| Cable Compensation<br>LSB                             | R <sub>LSB</sub>        |                                                                                                |      | 18    |      | mΩ    |  |  |  |

|                                                       |                         | ILIM[2:0] = 0b111, R <sub>SENSE</sub> = 33mΩ                                                   | 3.04 | 3.14  | 3.30 |       |  |  |  |

|                                                       |                         | ILIM[2:0] = 0b110, R <sub>SENSE</sub> = 33mΩ                                                   | 2.6  | 2.75  | 2.9  | -     |  |  |  |

|                                                       | ILIM_SET                | ILIM[2:0] = 0b101, R <sub>SENSE</sub> = 33mΩ                                                   | 2.1  | 2.25  | 2.4  |       |  |  |  |

| Our second at The sheld                               |                         | ILIM[2:0] = 0b100, R <sub>SENSE</sub> = 33mΩ                                                   | 1.62 | 1.7   | 1.78 | A     |  |  |  |

| Overcurrent Threshold                                 |                         | ILIM[2:0] = 0b011, R <sub>SENSE</sub> = 33mΩ                                                   | 1.05 | 1.13  | 1.21 |       |  |  |  |

|                                                       |                         | ILIM[2:0] = 0b010, R <sub>SENSE</sub> = 33mΩ                                                   | 0.8  | 0.86  | 0.92 |       |  |  |  |

|                                                       |                         | ILIM[2:0] = 0b001, R <sub>SENSE</sub> = 33mΩ                                                   | 0.55 | 0.6   | 0.65 | -     |  |  |  |

|                                                       |                         | ILIM[2:0] = 0b000, R <sub>SENSE</sub> = 33mΩ                                                   | 0.3  | 0.33  | 0.36 |       |  |  |  |

| SENSN Discharge<br>Current                            | ISENSN_DIS              |                                                                                                | 11   | 18    | 32   | mA    |  |  |  |

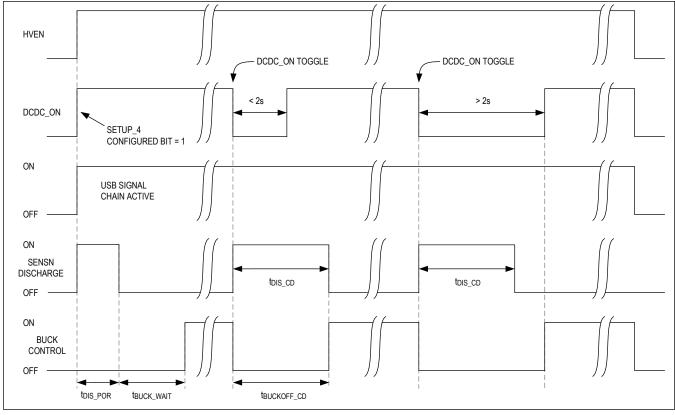

| Startup Wait Time                                     | <sup>t</sup> BUCK_WAIT  |                                                                                                |      | 100   |      | ms    |  |  |  |

|                                                       | t <sub>DIS_POR</sub>    | Discharge after POR                                                                            |      | 10    |      | ms    |  |  |  |

| SENSN Discharge Time                                  | t <sub>DIS_CD</sub>     | DATA_MODE or CD[1] toggle (into and out of DCP mode), DCDC_ON toggle                           |      | 2     |      | s     |  |  |  |

| Forced Buck Off-Time                                  | <sup>t</sup> BUCKOFF_CD | DATA_MODE or CD[1] toggle (into and<br>out of DCP mode), DCDC_ON toggle;<br>see reset criteria |      | 2     |      | s     |  |  |  |

| Attach Comparator Load<br>Current Rising<br>Threshold |                         | Common mode input = 5.15V                                                                      | 5    | 16    | 28   | mA    |  |  |  |

| Attach Comparator<br>Hysteresis                       |                         | Common mode input = 5.15V                                                                      |      | 2.5   |      | mA    |  |  |  |

| SENSN Undervoltage<br>Threshold (Falling)             | V <sub>UV_SENSN</sub>   |                                                                                                | 4    | 4.375 | 4.75 | V     |  |  |  |

| SENSN Overvoltage<br>Threshold (Rising)               | V <sub>OV_SENSN</sub>   |                                                                                                | 7    | 7.46  | 7.9  | V     |  |  |  |

| SENSN Short-Circuit<br>Threshold (Falling)            |                         |                                                                                                | 1.75 | 2     | 2.25 | V     |  |  |  |

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **Electrical Characteristics (continued)**

$(V_{SUPSW} = 14V, V_{ENBUCK} = V_{IN} = 3.3V)$ , temperature =  $T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are  $T_A = +25^{\circ}C$  under normal conditions.) (Note 3)

| PARAMETER                                 | SYMBOL                  | CONDITIONS                                                                                                    | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| SENSN Undervoltage<br>Fault Blanking Time |                         |                                                                                                               |       | 16   |       | ms    |

| SENSN Overvoltage<br>Fault Blanking Time  | tb,ov_sensn             | From overvoltage condition to FAULT asserted                                                                  |       | 3    | 6     | μs    |

| SENSN Discharge<br>Threshold Falling      |                         | V <sub>SENSN</sub> falling                                                                                    | 0.47  | 0.51 | 0.57  | V     |

| REMOTE FEEDBACK A                         | DJUSTMENT               |                                                                                                               |       |      |       |       |

| SHIELD Input Voltage<br>Range             |                         |                                                                                                               | 0.1   |      | 0.75  | V     |

| Gain                                      |                         |                                                                                                               | 1.935 | 2    | 2.065 | V/V   |

| Input Referred Offset<br>Voltage          |                         |                                                                                                               |       | ±2.0 |       | mV    |

| DIGITAL INPUTS (SDA,                      | SCL, ENBUCK, I          | DATA_MODE)                                                                                                    |       |      |       |       |

| Input Leakage Current                     |                         | V <sub>PIN</sub> = 5.5V, 0V                                                                                   | -5    |      | +5    | μA    |

| Logic-High                                | VIH                     |                                                                                                               | 1.6   |      |       | V     |

| Logic-Low                                 | VIL                     |                                                                                                               |       |      | 0.5   | V     |

| USB 2.0 HOST CHARGE                       | R EMULATOR (            | HVD+/HVD-, D+/D-)                                                                                             |       |      |       |       |

| Input Logic-High                          | VIH                     |                                                                                                               | 2.0   |      |       | V     |

| Input Logic-Low                           | VIL                     |                                                                                                               |       |      | 0.8   | V     |

| Data Sink Current                         | IDAT_SINK               | V <sub>DAT_SINK</sub> = 0.25V to 0.4V                                                                         | 50    | 100  | 150   | μA    |

| Data Detect Voltage<br>High               | V <sub>DAT_REFH</sub>   |                                                                                                               | 0.4   |      |       | v     |

| Data Detect Voltage<br>Low                | VDAT_REFL               |                                                                                                               |       |      | 0.25  | v     |

| Data Detect Voltage<br>Hysteresis         | V <sub>DAT_HYST</sub>   |                                                                                                               |       | 60   |       | mV    |

| Data Source Voltage                       | V <sub>DAT_SRC</sub>    | I <sub>SRC</sub> = 200μA                                                                                      | 0.5   |      | 0.7   | V     |

| SYNCHRONOUS STEP-                         | DOWN DC-DC C            | ONVERTER                                                                                                      |       |      |       |       |

| PWM Output Voltage                        | V <sub>SENSP</sub>      | $7V \le V_{SUPSW} \le 28V$ , no load                                                                          |       | 5.15 |       | V     |

| Skip Mode Output<br>Voltage               | V <sub>SENSP_SKIP</sub> | $7V \le V_{SUPSW} \le 18V$ , no load (Note 2)                                                                 |       | 5.25 |       | v     |

| Load Regulation                           |                         | $7V \le V_{SUPSW} \le 18V$ , for 5V nominal output setting                                                    |       | 51   |       | mΩ    |

| Output Voltage<br>Accuracy                |                         | $8V \le V_{SUPSW} \le 18V$ , 2.4A, $V_{SENSP} - V_{SENSN} = 79.2mV$ , GAIN[4:0] = 0b11111 cable compensation. | 6.33  |      | 6.68  | v     |

| Spread-Spectrum<br>Range                  |                         | SS enabled                                                                                                    |       | ±3.4 |       | %     |

| SYNC Switching<br>Threshold High          | V <sub>SYNC_HI</sub>    | Rising                                                                                                        | 1.4   |      |       | V     |

| SYNC Switching<br>Threshold Low           | V <sub>SYNC_LO</sub>    | Falling                                                                                                       |       |      | 0.4   | V     |

| SYNC Internal Pulldown                    |                         |                                                                                                               |       | 200  |       | kΩ    |

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **Electrical Characteristics (continued)**

$(V_{SUPSW} = 14V, V_{ENBUCK} = V_{IN} = 3.3V$ , temperature =  $T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are  $T_A = +25^{\circ}C$  under normal conditions.) (Note 3)

| PARAMETER                                             | SYMBOL               | CONDITIONS                              | MIN                        | TYP | MAX  | UNITS  |

|-------------------------------------------------------|----------------------|-----------------------------------------|----------------------------|-----|------|--------|

| SYNC Input Clock<br>Acquisition Time                  | <sup>t</sup> SYNC    | (Note 3)                                |                            | 1   |      | Cycles |

| High-Side Switch On-<br>Resistance                    | R <sub>ONH</sub>     | I <sub>LX</sub> = 1A                    | 1A 54 95                   |     |      |        |

| Low-Side Switch On-<br>Resistance                     | R <sub>ONL</sub>     | I <sub>LX</sub> = 1A                    |                            | 72  | 135  | mΩ     |

| BST Input Current                                     | I <sub>BST</sub>     | $V_{BST}$ - $V_{LX}$ = 5V, high-side on |                            | 2.2 |      | mA     |

| LX Current-Limit                                      |                      | All Other Variants                      |                            | 5   |      | - A    |

| Threshold                                             |                      | MAX16984AATJM, MAX16984AATJN            |                            | 6   |      |        |

| Skip Mode Peak Current<br>Threshold                   | I <sub>SKIP_TH</sub> |                                         |                            | 1   |      | A      |

| Negative Current Limit                                |                      |                                         |                            | 1.2 |      | A      |

| Soft-Start Ramp Time                                  | t <sub>SS</sub>      |                                         |                            | 8   |      | ms     |

| LX Rise Time                                          |                      | (Note 3)                                |                            | 3   |      | ns     |

| LX Fall Time                                          |                      | (Note 3)                                |                            | 4   |      | ns     |

| BST Refresh Algorithm<br>Low-Side Minimum On-<br>Time |                      |                                         |                            | 60  |      | ns     |

| FAULT, INT (ATTACH), S                                | YNC OUTPUTS          | 5                                       |                            |     |      |        |

| Output-High Leakage<br>Current                        |                      | FAULT, INT (ATTACH), = 5.5V             | -10                        |     | +10  | μA     |

| Output Low Level                                      |                      | Sinking 1mA                             |                            |     | 0.4  | V      |

| SYNC Output High<br>Level                             |                      | Sourcing 1mA, SYNC configured as output | V <sub>BIAS</sub> -<br>0.4 |     |      | V      |

| CONFIG RESISTORS CO                                   | NVERTER              |                                         |                            |     |      |        |

| CONFIG1-3 Current<br>Leakage                          |                      | V <sub>CONFIG</sub> = 0V to 4V          |                            |     | ±5   | μA     |

| Minimum Window<br>Amplitude                           |                      |                                         | -4                         |     | +4   | %      |

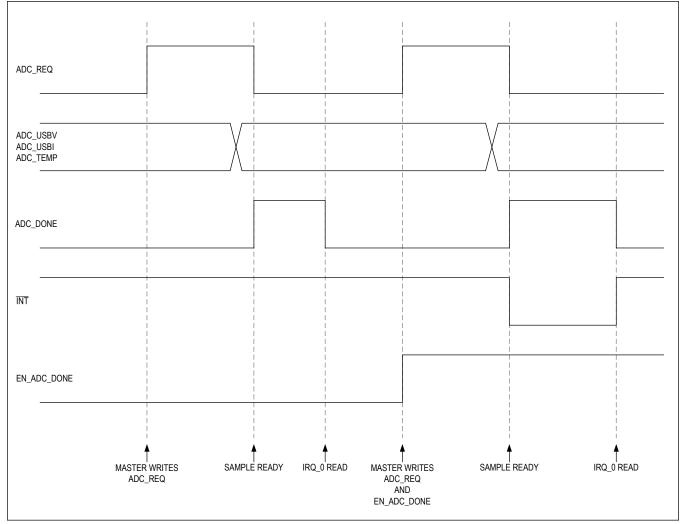

| ADC                                                   |                      |                                         |                            |     |      |        |

| Resolution                                            |                      |                                         |                            | 8   |      | Bits   |

| ADC Gain Error                                        |                      |                                         |                            | ±2  |      | LSBs   |

| Offset Error                                          | Offset_ADC           |                                         |                            | ±1  |      | LSB    |

| OSCILLATORS                                           |                      |                                         |                            |     |      |        |

| Internal High-Frequency<br>Oscillator                 | HFOSC                |                                         | 7                          | 8   | 9    | MHz    |

| Buck Oscillator<br>Frequency                          | f <sub>SW</sub>      | FSW[2:0] = 0b000                        | 1.95                       | 2.2 | 2.45 | MHz    |

| Buck Oscillator<br>Frequency                          | f <sub>SW</sub>      | FSW[2:0] = 0b101                        | 340                        | 410 | 480  | kHz    |

| THERMAL OVERLOAD                                      |                      |                                         |                            |     |      |        |

| Thermal Warning<br>Temperature                        |                      |                                         |                            | 140 |      | °C     |

|                                                       |                      | -                                       | •                          |     |      |        |

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **Electrical Characteristics (continued)**

$(V_{SUPSW} = 14V, V_{ENBUCK} = V_{IN} = 3.3V, temperature = T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are T\_A = +25°C under normal conditions.) (Note 3)

| PARAMETER                                            | SYMBOL              | CONDITIONS                          | MIN | TYP | MAX  | UNITS |

|------------------------------------------------------|---------------------|-------------------------------------|-----|-----|------|-------|

| Thermal Warning<br>Hysteresis                        |                     |                                     |     | 10  |      | °C    |

| Thermal Shutdown<br>Temperature                      |                     |                                     |     | 165 |      | °C    |

| Thermal Shutdown<br>Hysteresis                       |                     |                                     |     | 10  |      | °C    |

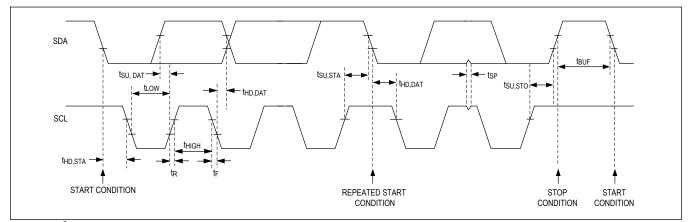

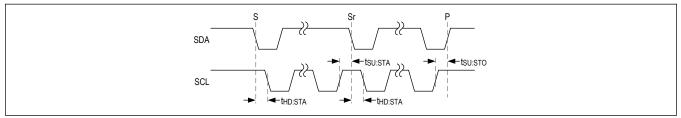

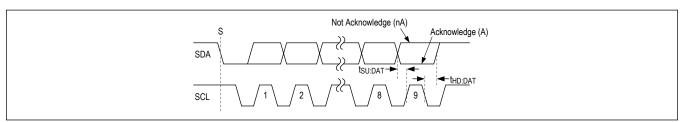

| l <sup>2</sup> C                                     |                     |                                     |     |     |      |       |

| Serial Clock Frequency                               | f <sub>SCL</sub>    |                                     |     |     | 400  | kHz   |

| Bus Free Time Between<br>STOP and START<br>Condition | <sup>t</sup> BUF    |                                     | 1.3 |     |      | μs    |

| START Condition Setup<br>Time                        | <sup>t</sup> SU:STA |                                     | 0.6 |     |      | μs    |

| START Condition Hold<br>Time                         | <sup>t</sup> HD:STA |                                     | 0.6 |     |      | μs    |

| STOP Condition Setup<br>Time                         | <sup>t</sup> su:sto |                                     | 0.6 |     |      | μs    |

| Clock Low Period                                     | t <sub>LOW</sub>    |                                     | 1.3 |     |      | μs    |

| Clock High Period                                    | t <sub>HIGH</sub>   |                                     | 0.6 |     |      | μs    |

| Data Setup Time                                      | <sup>t</sup> SU:DAT |                                     | 100 |     |      | ns    |

| Data Hold Time                                       | t <sub>HD:DAT</sub> | From 50% SCL falling to SDA change  | 0.3 |     | 0.6  | μs    |

| Pulse Width of Spike<br>Suppressed                   | t <sub>SP</sub>     |                                     |     | 50  |      | ns    |

| ESD PROTECTION (ALL                                  | PINS)               |                                     |     |     |      |       |

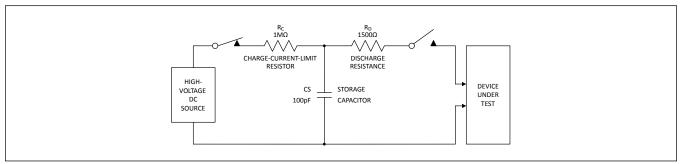

| ESD Protection Level                                 | V <sub>ESD</sub>    | Human Body Model                    |     | ±2  |      | kV    |

| ESD PROTECTION (HVD                                  | P, HVDM)            |                                     |     |     |      |       |

|                                                      |                     | ISO 10605 Air-Gap (330pF, 2kΩ)      |     | ±15 |      |       |

| FOD Destastion Lovel                                 |                     | ISO 10605 Contact (330pF, 2kΩ)      |     | ±8  |      |       |

|                                                      | V <sub>ESD</sub>    | IEC 61000-4-2 Air-Gap (150pF, 330Ω) |     | ±15 |      | - kV  |

| ESD Protection Level                                 |                     | IEC 61000-4-2 Contact (150pF, 330Ω) | ±8  |     | - KV |       |

|                                                      |                     | ISO 10605 Air-Gap (330pF, 330Ω)     | ±15 |     |      |       |

|                                                      |                     | ISO 10605 Contact (330pF, 330Ω)     |     | ±8  |      |       |

Note 2: Device is designed for use in applications with continuous operation of 14V. Device meets electrical table up to maximum supply voltage.

Note 3: Specification with minimum and maximum limits are 100% production tested at  $T_A = 25^{\circ}C$  and are guaranteed over the operating temperature range by design and characterization. Actual typical values may vary and are not guaranteed.

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

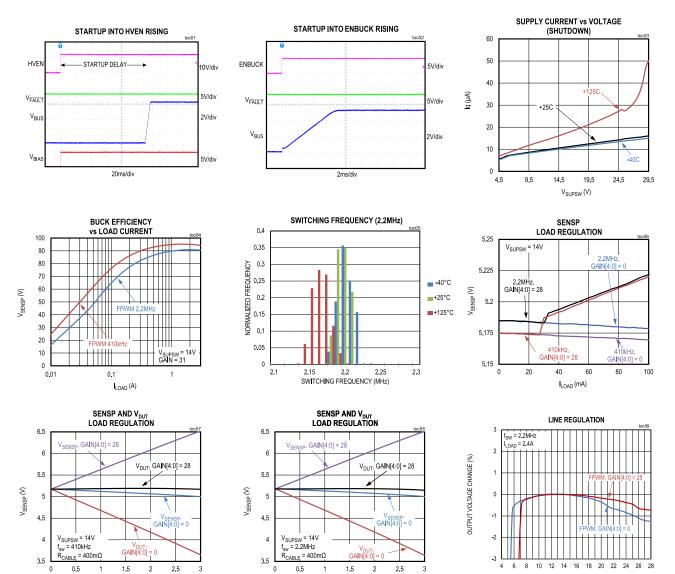

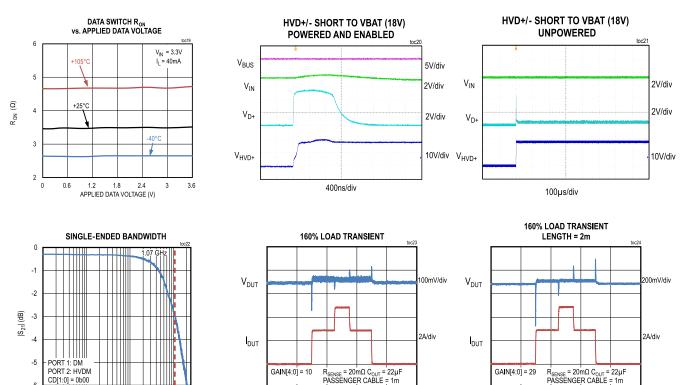

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

I<sub>LOAD</sub> (A)

$\mathbf{I}_{\text{LOAD}}\left(\mathsf{A}\right)$

V<sub>SUPSW</sub> (V)

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

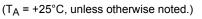

### **Typical Operating Characteristics (continued)**

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

0

2

4

6

TIME (ms)

8

10

0

2

4

6

TIME (ms)

8

10

-6

10

FREQUENCY (MHz)

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

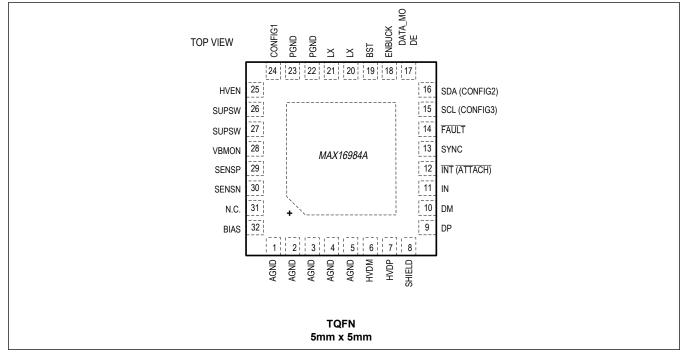

### **Pin Configuration**

### **Pin Description**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                          |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–5 | AGND             | Analog Ground                                                                                                                                                                                                                     |

| 6   | HVDM             | High-Voltage-Protected USB Differential Data D- Output. Connect HVD- to the downstream USB connector D- pin.                                                                                                                      |

| 7   | HVDP             | High-Voltage-Protected USB Differential Data D+ Output. Connect HVD+ to the downstream USB connector D+ pin.                                                                                                                      |

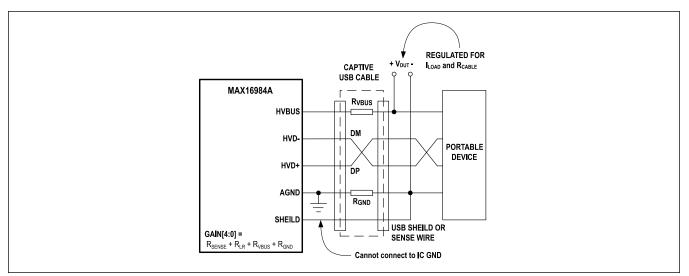

| 8   | SHIELD           | Remote feedback input, special order only. See Figure 2.                                                                                                                                                                          |

| 9   | DP               | USB Differential Data D+ Input. Connect D+ to the low-voltage USB transceiver D+ pin.                                                                                                                                             |

| 10  | DM               | USB Differential Data D- Input. Connect D- to the low-voltage USB transceiver D- pin.                                                                                                                                             |

| 11  | IN               | Logic Enable Input. Connect to I/O voltage of USB transceiver. IN is also used for clamping during overvoltage events on HVD+ or HVD Connect a $1\mu$ F– $10\mu$ F ceramic capacitor from IN to GND.                              |

| 12  | (ATTACH)         | In I <sup>2</sup> C variants, functions as an active-low INT pin. In standalone variants, functions as active-low Attach. Connect a 100k $\Omega$ pullup resistor to IN.                                                          |

| 13  | SYNC             | Switching Frequency Input/Output for Synchronization with Other DC-DC Supplies. See <u>Applications Information</u> section.                                                                                                      |

| 14  | FAULT            | Active-Low, Open-Drain Fault Indicator Output. Connect a $100k\Omega$ pullup resistor to the IN pin. Tie to AGND if not used.                                                                                                     |

| 15  | SCL<br>(CONFIG3) | SCL/Configuration 3. For the I <sup>2</sup> C variants, this serves as the SCL pin. For the standalone variants, this serves as CONFIG3 pin. Connect a resistor to AGND to configure gain and current limit. See <u>Table 6</u> . |

| 16  | SDA<br>(CONFIG2) | SDA/Configuration 2. For the l <sup>2</sup> C variants, this serves as the SDA pin. For the standalone variants, this serves as the CONFIG2 pin. Connect a resistor to AGND to configure cable compensation. See <u>Table 6</u> . |

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

## **Pin Description (continued)**

| PIN                                       | NAME                                                                                                                                                                                                                                                                   | FUNCTION                                                                                                                                                                                                                                               |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 17                                        | DATA_MODE                                                                                                                                                                                                                                                              | Selects Between the Two Default Modes of Data Switch Operation. See Table 3.                                                                                                                                                                           |  |  |

| 18                                        | ENBUCK                                                                                                                                                                                                                                                                 | DC-DC Enable Input. Drive high/low to enable/disable the buck converter.                                                                                                                                                                               |  |  |

| 19                                        | BST                                                                                                                                                                                                                                                                    | High-Side Driver Supply. Connect a 0.1µF capacitor from BST to LX.                                                                                                                                                                                     |  |  |

| 20, 21                                    | LX                                                                                                                                                                                                                                                                     | Inductor Connection. Connect an inductor from LX to the DC-DC converter output (SENSP).                                                                                                                                                                |  |  |

| 22, 23                                    | PGND                                                                                                                                                                                                                                                                   | Power Ground                                                                                                                                                                                                                                           |  |  |

| 24                                        | CONFIG1                                                                                                                                                                                                                                                                | Config1 input. Connect a resistor to GND or directly to BIAS. See <u>Table 4</u> and <u>Table 5</u> .                                                                                                                                                  |  |  |

| 25                                        | HVEN                                                                                                                                                                                                                                                                   | Active-High System Enable. HVEN is battery-voltage tolerant.                                                                                                                                                                                           |  |  |

| 26, 27                                    | SUPSW Internal High-Side Switch Supply Input. V <sub>SUPSW</sub> provides power to the internal switch and Connect a 10µF ceramic capacitor in parallel with a 47µF electrolytic capacitor from SUPS PGND. See the <u>DC-DC Switching Frequency Selection</u> section. |                                                                                                                                                                                                                                                        |  |  |

| 28                                        | VBMON                                                                                                                                                                                                                                                                  | USB V <sub>BUS</sub> Monitor.                                                                                                                                                                                                                          |  |  |

| 29 SENSP DC-DC Convert<br>capacitance pla |                                                                                                                                                                                                                                                                        | DC-DC Converter Feedback Input and Current-Sense Amplifier Positive Input. DC-DC bulk capacitance placed here. Connect to positive terminal of current-sense resistor and the main output of the converter. Used for internal voltage regulation loop. |  |  |

| 30                                        | SENSN                                                                                                                                                                                                                                                                  | Current-Sense Amp Negative Input. Connect to negative terminal of current sense resistor.                                                                                                                                                              |  |  |

| 31                                        | N.C.                                                                                                                                                                                                                                                                   | No Connection                                                                                                                                                                                                                                          |  |  |

| 32                                        | BIAS                                                                                                                                                                                                                                                                   | 5V Linear Regulator Output. Connect a 2.2 $\mu$ F ceramic capacitor from BIAS to GND. BIAS powers the internal circuitry.                                                                                                                              |  |  |

|                                           | EP                                                                                                                                                                                                                                                                     | Exposed Pad. Connect EP to multiple GND planes with 3 x 3 via grid (minimum).                                                                                                                                                                          |  |  |

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **Functional Diagrams**

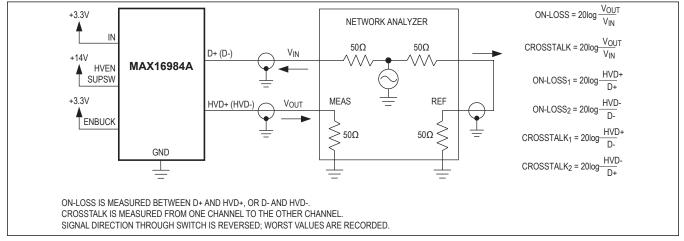

### **On-Channel -3dB Bandwidth and Crosstalk**

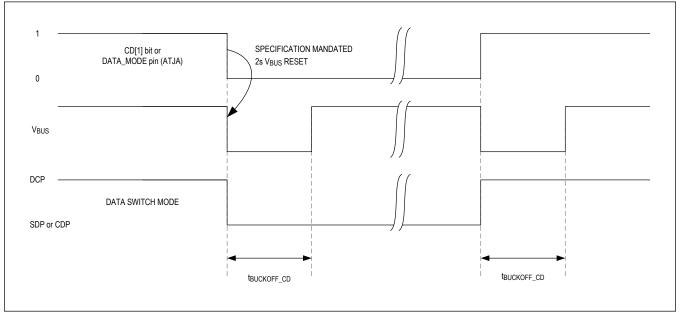

### **DCP Reset Behavior and Timing Diagram**

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### DCDC\_ON Reset Behavior and Timing Diagram

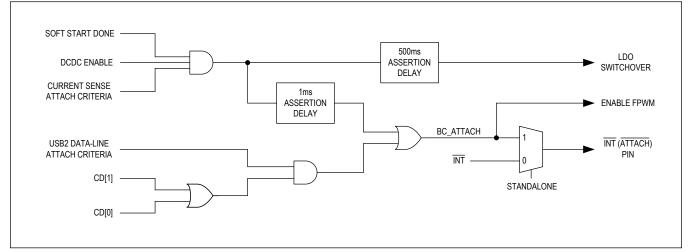

### ATTACH Logic Diagram

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### ADC Timing Diagram

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **Detailed Description**

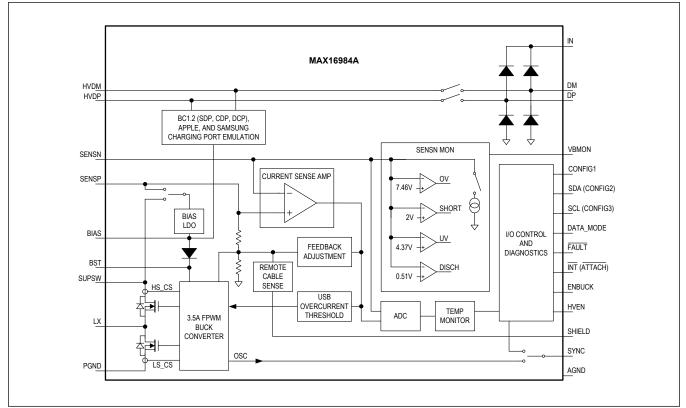

The MAX16984A combines a 5V/3A automotive grade step-down converter, a USB host charger adapter emulator, and USB protection switches. The device variants offer options for both standalone/GPIO and I<sup>2</sup>C configuration and control. This device family is designed for high-power USB ports in automotive radio, navigation, connectivity, USB hub, and dedicated charging applications.

The USB protection switches provide high-ESD and short- circuit protection for the low-voltage internal data lines of the multimedia processor's USB transceiver and support USB Hi-Speed (480Mbps) and USB Full-Speed (12Mbps) pass-through operation. The MAX16984A features integrated host-charger port-detection circuitry adhering to the USB 2.0 Battery Charging Specification BC1.2 and also includes dedicated bias resistors for Samsung 2.0A/iPod/iPhone/iPad 2.4A dedicated charging modes.

The high-efficiency step-down DC-DC converter operates from a voltage up to 28V and is protected from load-dump transients up to 40V. The device includes resistor-programmable frequency selection from 310kHz to 2.2MHz to allow optimization of efficiency, noise, and board space based on the application requirements. The converter can deliver up to 3A of continuous current at 125°C.

The MAX16984A also includes a high-side current-sense amplifier and configurable feedback-adjustment circuit designed to provide automatic USB voltage adjustment to compensate for voltage drops in captive cables associated with automotive applications.

### Detailed Block Diagram

Figure 1. Detailed Block Diagram

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

### **Power-Up and Enabling**

#### System Enable (HVEN)

HVEN is used as the main enable to the device and initiates system start-up and configuration. If HVEN is at a logic-low level, SUPSW power consumption is reduced and the device enters a standby, low quiescent current level. HVEN is compatible with inputs from 3.3V logic up to automotive battery. After a system reset (e.g., HVEN toggle, BIAS UV), the I<sup>2</sup>C variant asserts the INT pin to indicate that the IC has not been configured. The buck converter is forced off until the CONFIGURED bit of SETUP\_4 is written to a 1. This ensures that a portable device cannot attach before the IC registers are correctly set for the application.

#### **DC-DC Enable (ENBUCK)**

The buck regulator on the MAX16984A is controlled by the ENBUCK pin for standalone variants, and by both the ENBUCK pin and the I<sup>2</sup>C interface for I<sup>2</sup>C variants. DCDC\_ON, the logical AND of ENBUCK and EN\_DCDC, determines if the buck converter can be enabled. On standalone variants, EN\_DCDC is always high and only ENBUCK can be used to enable the buck converter. On I<sup>2</sup>C variants, setting ENBUCK low overrides an I<sup>2</sup>C EN\_DCDC enable command, which allows compatibility with USB hub controllers. For a typical USB hub application, connect ENBUCK to the enable output of the USB hub controller. This allows the USB hub controller to enable and disable the USB power port using software commands. ENBUCK can be directly connected to the BIAS or IN pin for applications that do not require GPIO control of the DC-DC converter enable.

#### 3.3V Input (IN)

IN is used to clamp the D+ and D- pins during an ESD or overvoltage event on the HVD+ and HVD- pins. This clamping protects the downstream USB transceiver. The presence of these clamping diodes requires that IN remain set to 3.3V at all times for USB communication to occur. The IN pin features an overvoltage lockout that disables the data switches if IN is above  $V_{IN}$ \_OVLO. Bypass IN with a 1µF ceramic capacitor, place it close to the IN pin, and connect it to the same 3.3V supply that is shared with the multimedia processor or hub transceiver.

#### Linear Regulator Output (BIAS)

BIAS is the output of a 5V linear regulator that powers the internal logic and control circuitry for the device. BIAS is internally powered from SUPSW or SENSP and automatically powers up when HVEN is high and SUPSW voltage exceeds  $V_{UV}$  SUPSW. The BIAS output contains an undervoltage lockout that keeps the internal circuitry disabled when BIAS is below  $V_{UV}$  BIAS. The linear regulator automatically powers down when HVEN is low, and a low shutdown current mode is entered. Bypass BIAS to GND with a 2.2µF ceramic capacitor.

#### **Power-On Sequencing**

HVEN, ENBUCK, and IN do not have a power-up sequence requirement by design. However, the desired system behavior should be considered for the state of these pins at startup. The D+ and D- pins are clamped to IN, therefore IN should be set to 3.3V before any USB communication is required. It is recommended that IN is set to 3.3V before HVEN is set high. ENBUCK acts as the master disable for the DC-DC converter. If ENBUCK is low when HVEN is set high, all variants keep the buck converter in the disabled state until ENBUCK is set high.

#### Step-Down DC-DC Regulator

#### **Step-Down Regulator**

The MAX16984A features a current-mode, step-down converter with integrated high-side and low-side MOSFETs. The low-side MOSFET enables fixed-frequency, forced-PWM operation under light loads. The DC-DC regulator features a cycle-by-cycle current limit and intelligent transition from skip mode to forced-PWM mode that makes the device ideal for automotive applications.

#### Wide Input Voltage Range

The device is specified for a wide 4.5V to 28V input voltage range. SUPSW provides power to the internal BIAS linear

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

regulator and internal power switch. Certain conditions such as cold cranking can cause the voltage at the output to drop below the programmed output voltage. Under such conditions, the device operates in a high duty-cycle mode to facilitate minimum dropout from input to output.

### Maximum Duty-Cycle Operation

The MAX16984A has a maximum duty cycle of 98% (typ). The IC monitors the off-time (time for which the low-side FET is on) in both PWM and skip modes for every switching cycle. Once the off-time of 150ns (typ) is detected continuously for 7.5µs, the low-side FET is forced on for 60ns (typ) every 7.5µs. The input voltage at which the device enters dropout changes depending on the input voltage, output voltage, switching frequency, load current, and design efficiency. The input voltage at which the devices enter dropout can be approximated as:

$$V_{SUPSW} = \frac{V_{OUT} + \left(I_{LOAD} \times R_{ONH}\right)}{0.98}$$

**Note:** The equation above does not take into account the efficiency and switching frequency but will provide a good first-order approximation. Use the R<sub>ONH</sub> number from the maximum column in the <u>*Electrical Characteristics*</u> table.

### Output Voltage (SENSP)

The device features a precision internal feedback network that is connected to SENSP and that is used to set the output voltage of the DC-DC converter. The network nominally sets the average DC-DC converter output voltage to 5.15V in forced-PWM and 5.25V in skip mode.

#### Soft-Start

When the DC-DC converter is enabled, the regulator soft-starts by gradually ramping up the output voltage from 0V to 5.15V over approximately 8ms. This soft-start feature reduces inrush current during startup. Soft-start is guaranteed into compliant USB loads (see the <u>USB Loads</u> section).

#### **Reset Behavior**

The MAX16984A implements a discharge function on SENSN any time that the DC-DC regulator is disabled for any reason. When the discharge function is activated, current (I<sub>SENSN\_DIS</sub>) is drained through a current-limited FET, and a reset timer is also started. This timer prevents the DC-DC regulator from starting up again until the timer has expired. This allows for easy compatibility with USB specifications and removes the need for long discharge algorithms to be implemented in system software. See the relevant *Functional Diagrams* for reset timer details.

#### **Reset Criteria**

The MAX16984A DC-DC converter automatically resets for all undervoltage, overvoltage, overcurrent and overtemperature fault conditions. See <u>Table 8</u> for details. The fault retry timer is configurable in the SETUP\_3 register. This timer is activated after a fault condition is removed and prevents the buck converter from switching on until the timer expires.

Another internal retry timer is enabled after DCDC\_ON is set low or a transition of the CD[1] bit (switching between a data mode and a dedicated charging mode). DCDC\_ON toggle causes buck shutdown and prevent the buck from switching on until tbuckOFF CD expires.

#### Switching Frequency Configuration

The DC-DC switching frequency can be referenced to an internal oscillator or from an external clock signal on the SYNC pin. The internal oscillator frequency is set by the FSW[2:0] bits of the SETUP\_1 register, which has a POR value corresponding to 2.2MHz. The internal oscillator can be programmed through I<sup>2</sup>C to eight discrete values from 310kHz to 2.2MHz. For standalone variants, the f<sub>SW</sub> configuration value is loaded from the CONFIG1 pin at startup with four discrete values from 310kHz to 2.2MHz available.

#### Switching Frequency Synchronization (SYNC Pin)

When the SYNC pin is configured to operate as an output, skip mode operation is disallowed, and the internal oscillator frequency is driven by the SYNC pin. This allows other devices to synchronize with the MAX16984A 180 degrees out of

### Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

phase for EMI reduction.

When SYNC is configured as an input, the SYNC pin becomes a logic-level input that can be used for both operatingmode selection and frequency control. Connecting SYNC to GND or an external clock enables fixed-frequency, forced-PWM mode. Connecting SYNC to a logic-high signal allows intelligent skip-mode operation. The device can be externally synchronized to frequencies within ±20% of the programmed internal oscillator frequency.

#### **Forced-PWM Operation**

In forced-PWM mode, the device maintains fixed-frequency PWM operation over all load conditions, including no-load conditions.

#### Intelligent Skip-Mode Operation and Attach Detection

When the SYNC pin is configured as an input, but neither a clocked signal nor a logic-low level exists on the SYNC pin, the MAX16984A operates in skip mode at very light load/no load conditions. Intelligent device attach detection is used to determine when a device is attached to the USB port. The device intelligently exits skip mode and enters forced-PWM mode when a device is attached and remains in forced-PWM mode as long as the attach signal persists. This minimizes the EMI concerns caused by automotive captive USB cables and poorly shielded consumer USB cables. The device attach event is also signaled by the ATTACH pin (standalone variants) or ATTACH bits (I<sup>2</sup>C variants). The criteria for device attach detection and intelligent skip-mode operation are shown in <u>Table 1</u>.

### Table 1. DC-DC Converter Intelligent Skip Mode Truth Table

| SYNC<br>PIN | SYNC_DIR | DATA SWITCH<br>CHARGE DETECTION<br>MODE | CDP ATTACH<br>DETECTION | DCP ATTACH<br>DETECTION | CURRENT SENSE<br>ATTACH DETECTION | DC-DC<br>CONVERTER<br>OPERATION                    |

|-------------|----------|-----------------------------------------|-------------------------|-------------------------|-----------------------------------|----------------------------------------------------|

| x           | OUT      | x                                       | x                       | x                       | x                                 | Forced-PWM<br>Mode:<br>Continuous                  |

| 0           | IN       | x                                       | x                       | x                       | x                                 | Forced-PWM<br>Mode:<br>Continuous                  |

| Clocked     | IN       | x                                       | x                       | x                       | x                                 | Forced-PWM<br>Mode:<br>Continuous                  |

| 1           | IN       | High-Speed Pass<br>Through (SDP) Mode   | x                       | x                       | 0                                 | Intelligent Skip<br>Mode:<br>No Device<br>Attached |

| 1           | IN       | High-Speed Pass<br>Through (SDP) Mode   | x                       | x                       | 1                                 | Forced-PWM<br>Mode:<br>Device Attached             |

| 1           | IN       | BC1.2 Auto CDP Mode                     | 0                       | x                       | 0                                 | Intelligent Skip<br>Mode:<br>No Device<br>Attached |

| 1           | IN       | BC1.2 Auto CDP Mode                     | 1                       | x                       | x                                 | Forced-PWM<br>Mode:<br>Device Attached             |

| 1           | IN       | BC1.2 Auto CDP Mode                     | x                       | x                       | 1                                 | Forced-PWM<br>Mode:<br>Device Attached             |

| 1           | IN       | 2.4A Auto DCP Mode                      | x                       | 0                       | 0                                 | Intelligent Skip<br>Mode:<br>No Device<br>Attached |

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

| SYNC<br>PIN | SYNC_DIR | DATA SWITCH<br>CHARGE DETECTION<br>MODE | CDP ATTACH<br>DETECTION | DCP ATTACH<br>DETECTION | CURRENT SENSE<br>ATTACH DETECTION | DC-DC<br>CONVERTER<br>OPERATION        |

|-------------|----------|-----------------------------------------|-------------------------|-------------------------|-----------------------------------|----------------------------------------|

| 1           | IN       | 2.4A Auto DCP Mode                      | x                       | 1                       | x                                 | Forced-PWM<br>Mode:<br>Device Attached |

| 1           | IN       | 2.4A Auto DCP Mode                      | x                       | x                       | 1                                 | Forced-PWM<br>Mode:<br>Device Attached |

### Table 1. DC-DC Converter Intelligent Skip Mode Truth Table (continued)

### Spread-Spectrum Option

Spread-spectrum operation is offered to improve the EMI performance of the MAX16984A. Spread-spectrum operation is enabled by the SS\_EN bit of the SETUP\_0 register, which is preloaded on startup from the CONFIG1 pin for both standalone and I<sup>2</sup>C variants. The internal operating frequency modulates the switching frequency by up to  $\pm 3.4\%$  relative to the internally generated operating frequency. This results in a total spread-spectrum range of 6.8%. Spread-spectrum mode is only active when operating from the internal oscillator. Spread-spectrum clock dithering is not possible when operating from an external clock.

### **Current Limit**

The MAX16984A limits the USB load current using both a fixed internal peak current threshold of the DC-DC converter, as well as a user-programmable external DC load current-sense amplifier threshold. This allows the current limit to be adjusted between 500mA to 3A depending on the application requirements, while protecting the system in the event of a fault. Upon exceeding either the DC-DC peak or user-programmable current thresholds, the high-side FET is immediately switched off and current-limit algorithms are initiated. When the external current limit lasts for longer than 16ms, the FAULT pin asserts and the VBUS\_ILIM bit of the IRQ\_1 register is set. Once the load current exceeds the programmed threshold, the DC-DC converter acts as a constant-current source. This may cause the output voltage to droop. The ILIM\_ITRIP bit of the SETUP\_2 register determines the output voltage droop required to initiate a DC-DC converter reset during VBUS\_ILIM. When ILIM\_ITRIP = 0, the USB current limit is detected for 16ms and the output voltage falls below  $V_{UV\_SENSN}$ , the DC-DC converter resets. The DC-DC converter also resets if the internal LX peak current threshold is exceeded for four consecutive switching cycles and the output voltage droops to less than 2.0V.

In some cases, the designer may want to increase the load to 160%, refer to USB Output Current Limit for details.

### **Output Short-Circuit Protection**

The DC-DC converter output (SENSP, SENSN) is protected against both short-to-ground and short-to-battery conditions. If a short-to-ground or undervoltage condition is encountered, the DC-DC converter immediately resets, asserts the FAULT pin, flags the fault in the IRQ\_1 register, and then reattempts soft-start after the 2s reset delay. This pattern repeats until the short circuit has been removed. If a short-to-battery is encountered ( $V_{SENSN} > V_{OV_SENSN}$ ), the buck converter shuts down, the FAULT pin is asserted, and the fault is flagged in the IRQ\_1 register. The buck converter stays shut down until the fault condition resolves and the 2s timer expires.

#### **Thermal Overload Protection**

Thermal-overload protection limits the total power dissipated by the device. A thermal protection circuit monitors the die temperature. If the die temperature exceeds +165°C, the device shuts down, so it can cool. Once the device has cooled by 10°C, the device is enabled again. This results in a pulsed output during continuous thermal-overload conditions, protecting the device during fault conditions. For continuous operation, do not exceed the absolute maximum junction temperature of +150°C. See the Thermal Considerations section for more information.

#### **Pre-Thermal Overload Warning**

The MAX16984A I<sup>2</sup>C variants feature a thermal overload warning flag which sets the THM\_WARN bit of the IRQ\_2 register when the die temperature crosses +140°C. This allows a system software implementation of thermal foldback or load shedding algorithms to prevent a thermal overload condition.

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

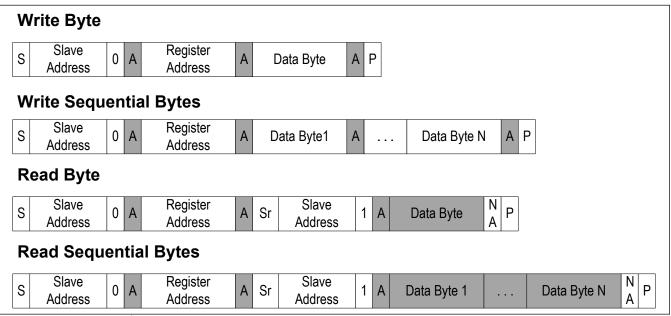

### **USB Current Limit and Output Voltage Adjustment**

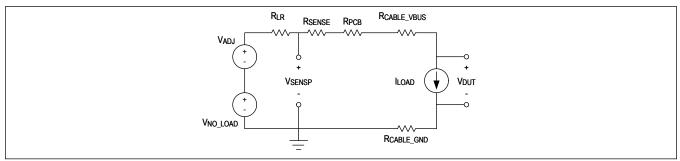

#### Current-Sense Amplifier (SENSP, SENSN)

MAX16984A features an internal USB load current-sense amplifier to monitor the DC load current delivered to the USB port. The V<sub>SENSE</sub> voltage (V<sub>SENSP</sub> - V<sub>SENSN</sub>) is used internally to provide precision DC current-limit and voltage-compensation functionality. A 33m $\Omega$  sense resistor should be placed between SENSP and SENSN.

In some cases, the designer may want to increase the load to 160%, refer to USB Output Current Limit for details.

#### **USB DC Current Limit Configuration**

The MAX16984A allows configuration of the precision DC current limit by the ILIM[2:0] bits of the SETUP\_2 register. I<sup>2</sup>C configuration enables selection of eight discrete DC current limit values. See SETUP\_2 for current limit configuration values.

Standalone variants of the device allow selection of a subset of the eight available current limit options by reading the CONFIG3 resistor. See <u>Table 6</u> and the <u>Applications Information</u> section for more information.

In some cases, the designer may want to increase the load to 160%, refer to USB Output Current Limit for details.

#### Voltage Feedback Adjustment Configuration

The MAX16984A compensates voltage drop for up to  $474m\Omega$  of USB cable in typical USB charging applications. I<sup>2</sup>C variants of the device allow this configuration by the GAIN[4:0] bits of the SETUP\_1 register. See GAIN[4:0] for voltage gain configuration. Standalone variants of the device allow configuration by the CONFIG2 resistor, which sets GAIN[3:0], and the CONFIG3 resistor, which sets GAIN[4]. See the SETUP\_1 register map and the <u>Applications Information</u> section for more information.

In some cases, the designer may want to increase the load to 160%, refer to USB Output Current Limit for details.

#### **Remote-Sense Feedback Adjustment**

The remote-sense feature (available by custom order only) provides another option to adjust the output voltage by sensing the ground node on the USB port at the far-end of the captive cable; either with the cable shield or with an additional sensing wire. This feature automatically senses the cable resistance and adjusts the voltage compensation without changing the GAIN[4:0] setting.

The user needs to compensate the voltage drop because of the sense resistor, the load line behavior of the buck, and any difference between the  $V_{BUS}$  and GND conductors. See <u>Figure 2</u> and contact the factory for support and how to order.

Figure 2. Remote Cable-Sense Diagram

## Automotive High-Current Step-Down Converter with USB Protection/Host Charger Adapter Emulator

#### USB Protection Switches and BC1.2 Host Charger Emulation

#### **USB Protection Switches**

MAX16984A provides automotive-grade ESD and shortcircuit protection for the low-voltage USB data lines of highintegration multimedia processors. HVDP/HVDM protection consists of ESD and OVP (overvoltage protection) for 1.5Mbps, 12Mbps, and 480Mbps USB transceiver applications. This is accomplished with a very low-capacitance FET in series with the D+ and D- data paths.

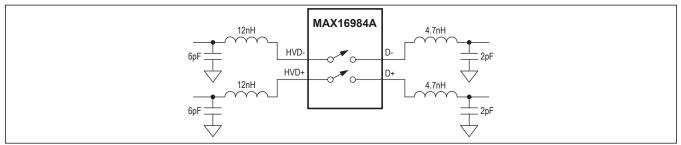

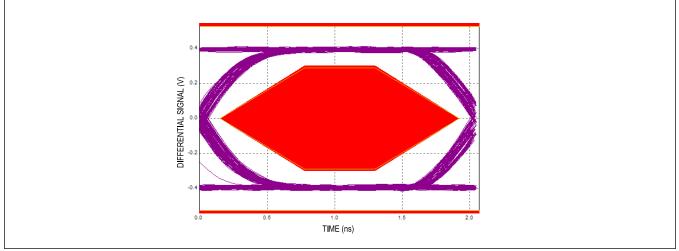

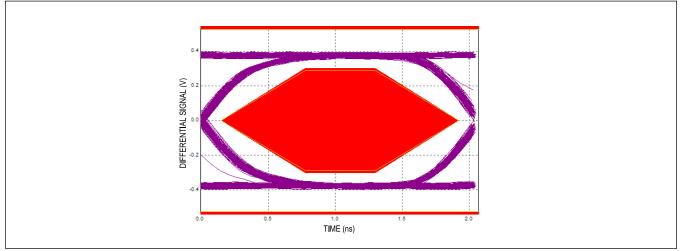

The MAX16984A high-voltage variant does not require an external ESD array, and protects the HVD+ and HVD pins to  $\pm 15$ kV Air-Gap/ $\pm 8$ kV Contact Discharge with the 150pF/330 $\Omega$  IEC 61000-4-2 model and the 330pF/330 $\Omega$  model, as well as protecting up to  $\pm 15$ kV Air-Gap/ $\pm 8$ kV Contact Discharge with the 330pF/2k $\Omega$  ISO 10605 model. The MAX16984A provides robust, automotive-grade protection while maintaining a 1GHz -3dB insertion loss. This ensures optimum eye diagram at the end of a captive cable. The HVD+ and HVD- short-circuit protection features include protection for a short to the USB +5V BUS and a short to the +18V car battery. These protection features prevent damage to the low-voltage USB transceiver when shorts occur in the vehicle harness or customer USB connector/cable. Short-to-GND protection is provided by the upstream USB transceiver.

#### **USB Host Charger Emulator**