#### **General Description**

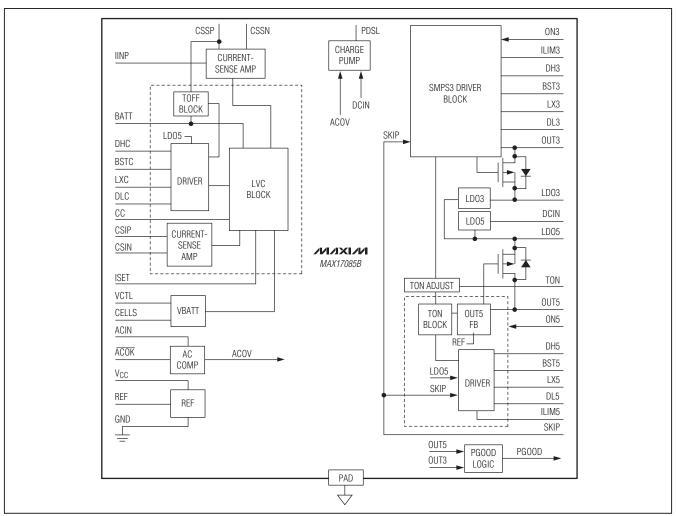

The MAX17085B is an all-in-one notebook power solution integrating a multichemistry battery charger, dual fixedoutput Quick-PWM™ step-down controllers, and dual keep-alive linear regulators:

Charger: The high-frequency (~1.4MHz) multichemistry battery charger uses a current-mode, fixed inductor current ripple architecture that significantly reduces component size and cost. Low-offset sense amplifiers allow the use of low-value sense resistors for charging and input current limit.

The charger uses n-channel switching MOSFETs. Adjustable charge current, charge voltage, and cell selection allow for flexible use with different battery packs. Charge current is set by an analog control input, or a PWM input. High-accuracy current-sense amplifiers provide fast cycle-by-cycle current-mode control to protect against short circuits to the battery and respond quickly to system load transients. Additionally, the charger provides a high-accuracy analog output that is proportional to the adapter current.

An integrated charge pump controls an n-channel adapter selector switch. The charge pump remains active even when the charger is off. When the adapter is absent, a p-channel MOSFET selects the battery.

Main SMPS: The dual Quick-PWM step-down controllers with synchronous rectification generate the 5V and 3.3V main power in a notebook. Lowside MOSFET sensing provides a simple low-cost, highly efficient valley current-limit protection. The MAX17085B also includes output undervoltage, output overvoltage, and thermal-fault protection.

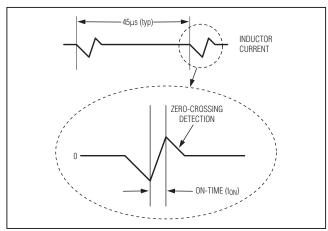

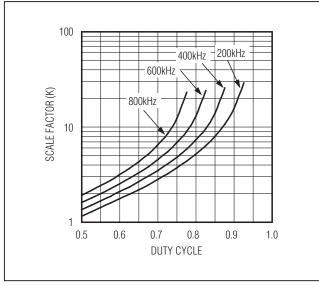

Separate enable inputs for each SMPS and a combined open-drain power-good output allow flexible power sequencing. Voltage soft-start reduces inrush current, while passive shutdown discharges the output through an internal switch. Fast transient response, with an extended on-time feature reduces output capacitance requirements. Selectable pulseskipping mode and ultrasonic mode improve lightload efficiency. Ultrasonic mode operation maintains a minimum switching frequency at light loads, minimizing audible noise effects.

**Dual LDO Regulators:** An internal 5V/100mA LDO5 with switchover can be used to either generate the 5V bias needed for power-up or other lower power "always-on" suspend supplies. Another 3.3V/50mA LDO3 provides "always-on" power to a system microcontroller.

#### **Features**

- ♦ All-in-One Charger Plus Dual Main Step-Down Controllers

- ♦ 5V/100mA and 3.3V/50mA LDO Regulators

**Dual Quick-PWM with Fast Transient Response** and Extended On-Time 300kHz to 800kHz Switching Frequency Fixed 5V and 3.3V SMPS Outputs Low-Noise Ultrasonic Mode **Autoretry Fault Protection**

**♦** Charger

**High Switching Frequency (1.4MHz)** Selectable 2-, 3-, and 4-Cell Battery Voltage **Automatic Selection of System Power Source Internal Charge-Pump for Adapter n-Channel MOSFETs Drive**

- ±0.4% Accurate Charge Voltage

- ±2.5% Accurate Input Current Limiting

- ±3% Accurate Charge Current

- ♦ Monitor Outputs for AC Adapter Current (±2% Accuracy) **Battery Discharge Current (±2% Accuracy) AC Adapter OK**

- ♦ Analog/PWM (100Hz to 500kHz) Adjustable **Charge Current Setting**

- **♦** AC Adapter Overvoltage and Overcurrent **Protection**

### **Applications**

**Notebook Computers** PDAs and Mobile Communicators 5V and 3.3V Supplies 2-to-4, Li+-Cell, Battery-Powered Devices

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAX17085BETL+ | -40°C to +85°C | 40 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package.

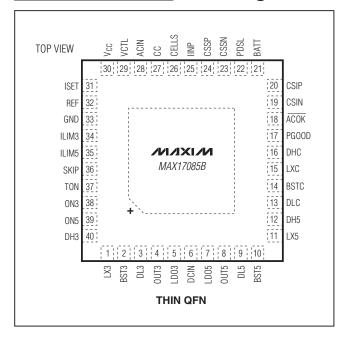

Pin Configuration appears at end of data sheet.

Quick-PWM is a trademark of Maxim Integrated Products, Inc.

MIXIM

Maxim Integrated Products 1

<sup>\*</sup>EP = Exposed pad.

#### ABSOLUTE MAXIMUM RATINGS (Note 1)

|                                    | (                              |

|------------------------------------|--------------------------------|

| TON, DCIN, CSSP, BATT, CSIP to GND | ),                             |

| LX_ to GND                         | 0.3V to +28V                   |

| CSIP to CSIN, CSSP to CSSN         | -0.3V to +0.3V                 |

| LDO3, LDO5, VCC to GND (Note 2)    | 0.3V to +6V                    |

| ISET, VCTL, ACIN, ACOK to GND      | 0.3V to +6V                    |

| OUT3, OUT5 to GND (Note 2)         | 0.3V to +6V                    |

| ON3, ON5, PGOOD to GND             | 0.3V to +6V                    |

| ILIM3, ILIM5, SKIP, REF to GND     | 0.3V to (VCC + 0.3V)           |

| GND to EP                          | -0.3V to +0.3V                 |

| DL_ to EP                          | $-0.3V$ to $(V_{LDO5} + 0.3V)$ |

| BST_ to GND                        | 0.3V to +34V                   |

| BST_ to LDO5                       | 0.3V to +28V                   |

| DH3 to LX3                         | $-0.3V$ to $(V_{BST3} + 0.3V)$ |

| BST3 to LX3                        | 0.3V to +6V                    |

| DH5 to LX5                         | $-0.3V$ to $(V_{BST5} + 0.3V)$ |

| BST5 to LX5                        | 0.3V to +6V                    |

|                                    |                                |

| DHC to LXC                      | 0.3V to (V <sub>BSTC</sub> + 0.3V) |

|---------------------------------|------------------------------------|

| PDSL to GND                     | 0.3V to + 36V                      |

| BSTC to LXC                     | 0.3V to +6V                        |

| CELLS, CC, IINP to GND          | 0.3V to (V <sub>LDO5</sub> + 0.3V) |

| LDO_ Short Circuit to GND       | Momentary                          |

| LDO5 Current (Internal Regulato | r) Continuous+100mA                |

| LDO3 Current (Internal Regulato | r) Continuous+50mA                 |

| LDO_ Current (Switched Over) C  | Continuous+200mA                   |

| Continuous Power Dissipation (T | $A = +70^{\circ}C$                 |

| 40-Pin Thin QFN (derate 34.5r   | mW/°C above +70°C) 2857mW          |

| Operating Temperature Range     | 40°C to +85°C                      |

| Junction Temperature            | +150°C                             |

| Storage Temperature Range       | 65°C to +150°C                     |

| Lead Temperature (soldering, 10 | 0s)+300°C                          |

| Soldering Temperature (reflow). | +260°C                             |

|                                 |                                    |

Note 1: Absolute Maximum Ratings valid using 20MHz bandwidth limit.

Note 2: LDO5 has a weak leakage to VCC when LDO5 is more than 0.5V above VCC. OUT5 has a weak leakage to VCC when OUT5 is more than 0.5V above VCC.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

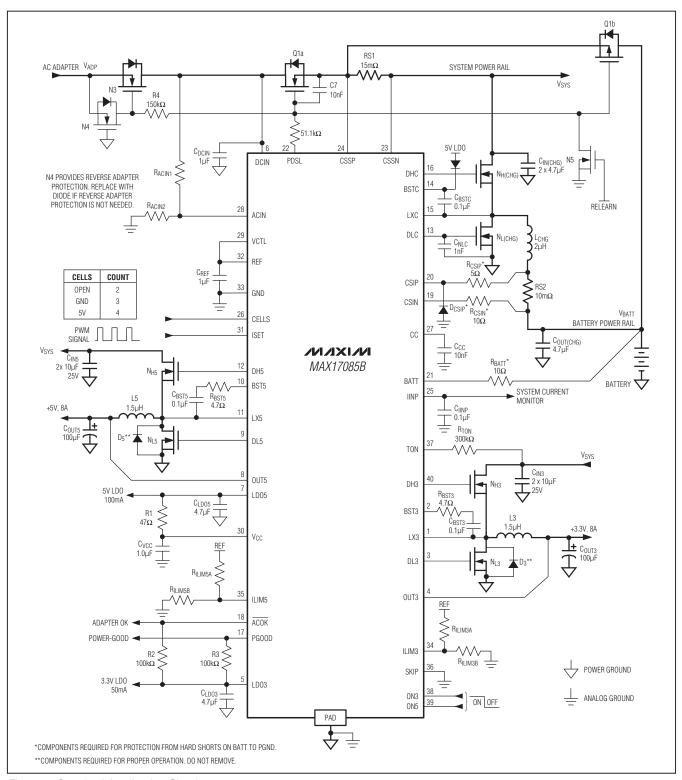

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF,  $V_{CC} = 5V$ , ON3 = ON5 =  $V_{CC}$ ,  $V_{DCIN} = V_{LXC} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BSTC} - V_{LXC} = 5V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 12.6V$ ,  $V_{VCTL} = V_{ISET} = 1.8V$ , CELLS = open,  $T_A = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                        | SYMBOL | CONDITIONS                                                                                     |                            | MIN | TYP | MAX | UNITS |

|----------------------------------|--------|------------------------------------------------------------------------------------------------|----------------------------|-----|-----|-----|-------|

| INPUT SUPPLIES                   |        |                                                                                                |                            |     |     |     |       |

| Adapter Present Quiescent        |        | IDCIN + ICSSP + ICSSN,<br>ON3 = ON5 = SKIP = VCC.                                              | Charging enabled           |     | 3   | 6   | mA    |

| Current                          |        | VOUT3 = 3.5V, VOUT5 = 5.3V                                                                     | Charging disabled          |     | 1.5 | 2.5 | IIIA  |

| Adapter Absent Quiescent Current |        | IDCIN + ICSSP + ICSSN,<br>ON3 = ON5 = SKIP = V <sub>CC</sub> ,                                 | VISET = 2.4V,<br>IINP ON   |     | 1.5 | 2.5 | mA    |

| Current                          |        | VOUT3 = 3.5V, VOUT5 = 5.3V                                                                     | ISET = GND                 |     | 1.2 | 2.2 |       |

| CSSN Input Current               |        | VCSSP = VCSSN = 24V, TA =                                                                      | +25°C                      |     | 0.1 | 2   | μΑ    |

| BATT + CSIP + CSIN + LXC         |        | VBATT = 16.8V, adapter abse                                                                    | nt, T <sub>A</sub> = +25°C |     |     | 4   |       |

| Input Current                    |        | VBATT = 2V to 19V, adapter p                                                                   | resent                     |     | 200 | 650 | μΑ    |

| DCIN Input Current               | IDCIN  | ON3 = ON5 = SKIP = V <sub>CC</sub> , cl<br>disabled; V <sub>OUT3</sub> = 3.5V, V <sub>OU</sub> | 9                          |     | 0.1 | 0.2 | mA    |

| DCIN Standby Supply Current      |        | V <sub>DCIN</sub> = 5V to 24V, ON3 = OI                                                        | N5 = GND                   |     | 130 | 270 | μΑ    |

| VCC Supply Current               | lcc    | ON3 = ON5 = SKIP = V <sub>CC</sub> , cl<br>disabled; V <sub>OUT3</sub> = 3.5V, V <sub>OU</sub> |                            |     | 1.0 | 1.5 | mA    |

| DCIN Input Voltage Range         |        | Note: LDO5 is NOT guarante regulation until DCIN is above                                      |                            | 4.5 |     | 24  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF,  $V_{CC} = 5V$ ,  $ON3 = ON5 = V_{CC}$ ,  $V_{DCIN} = V_{LXC} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BSTC} - V_{LXC} = 5V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 12.6V$ ,  $V_{VCTL} = V_{ISET} = 1.8V$ , CELLS = open,  $T_A = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                             | SYMBOL            | CONDI                                              | TIONS                              | MIN   | TYP   | MAX   | UNITS |

|---------------------------------------|-------------------|----------------------------------------------------|------------------------------------|-------|-------|-------|-------|

| DCIN Undervoltage-Lockout             | \/                | VDCIN falling                                      |                                    | 7.0   | 7.2   |       | \/    |

| Trip Point for Charger                | VDCIN(UVLO)       | V <sub>DCIN</sub> rising                           | V <sub>DCIN</sub> rising           |       | 7.7   | 7.9   | V     |

| DCIN POR Threshold                    | VDCIN(POR)        | Falling edge of VDCIN                              |                                    |       | 2.0   |       | V     |

| VCC Undervoltage Lockout              | Vcc(UVLO)         | Falling edge of V <sub>CC</sub> , P this threshold | WM disabled below                  | 3.8   | 4.0   | 4.3   | V     |

| Threshold                             |                   | Rising edge of VCC                                 |                                    |       | 4.2   |       |       |

| VCC POR Threshold                     |                   | Falling edge of VCC                                |                                    |       | 1.5   |       | V     |

| LINEAR REGULATORS                     |                   |                                                    |                                    |       |       |       |       |

| LDO_ Output-Voltage Accuracy          | V <sub>LDO5</sub> | VDCIN = 6V to 24V, ON<br>0mA < ILDO5 < 100mA       |                                    | 4.90  | 5.00  | 5.10  | V     |

| LDO_ Output-voltage Accuracy          | V <sub>LDO3</sub> | VLDO5 = 5V, ILDO5 = 0<br>0mA < ILDO3 < 50mA,       |                                    | 3.23  | 3.30  | 3.37  | V     |

| Internal LDO Voltage After            | V <sub>LDO5</sub> | Not production tested                              |                                    | 4.4   | 4.5   | 4.6   | V     |

| Switchover                            | VLD03             | Not production tested                              |                                    | 2.7   | 2.8   | 2.9   | V     |

| LDO3 Short-Circuit Current            |                   | LDO3 = GND                                         |                                    | 50    |       | 130   | mA    |

| LDO5 Short-Circuit Current            |                   | LDO5 = GND                                         |                                    | 100   |       | 260   | mA    |

| LDO5 Bootstrap Switch<br>Resistance   |                   | LDO5 to OUT5, VOUT5                                | 5 = 5V, ILDO5 = 50mA               |       | 1.0   | 2.5   | Ω     |

| LDO3 Bootstrap Switch<br>Resistance   |                   | LDO3 to OUT3, VOUT3                                | 3 = 3.3V,                          |       | 1.5   | 3     | Ω     |

| Thermal-Shutdown Threshold            | tshdn             | Hysteresis = 50°C                                  |                                    |       | +160  |       | °C    |

| REFERENCE                             |                   |                                                    |                                    |       |       |       |       |

| REF Output Voltage                    | V <sub>REF</sub>  | IREF = 50µA                                        |                                    | 2.09  | 2.10  | 2.11  | V     |

| REF Undervoltage-Lockout<br>Threshold | VREF_UVLO         | V <sub>REF</sub> falling                           |                                    |       | 2.0   |       | V     |

| MAIN SMPS                             |                   |                                                    |                                    |       |       |       |       |

| OUT5 Output Voltage Accuracy          | VOUT5             | VIN = 6V to 28V, SKIP                              | = REF                              | 5.033 | 5.083 | 5.135 | V     |

| OUT3 Output Voltage Accuracy          | Vout3             | $V_{IN} = 6V$ to 28V, SKIP                         | = REF                              | 3.267 | 3.300 | 3.333 | V     |

|                                       |                   | Either SMPS, VSKIP = 2                             | 2V, ILOAD = 0 to 5A                |       | -0.1  |       |       |

| Load Regulation Error                 |                   | Either SMPS, SKIP = G                              | GND, ILOAD = 0 to 5A               |       | -1.7  |       | %     |

|                                       |                   | Either SMPS, SKIP = V                              | CC, ILOAD = 0 to 5A                |       | -1.5  |       |       |

| Line Regulation Error                 |                   | Either SMPS, V <sub>IN</sub> = 6V                  | to 28V                             |       | 0.005 |       | %/V   |

| DUE On Time                           | tous              | V <sub>IN</sub> = 12V,                             | RTON = $549k\Omega$ (300kHz + 10%) | 1073  | 1263  | 1452  |       |

| DH5 On-Time                           | tON5              | V <sub>OUT5</sub> = 5.0V (Note 3)                  | RTON = $202k\Omega$ (800kHz + 10%) | 402   | 473   | 545   | ns    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF, V<sub>CC</sub> = 5V, ON3 = ON5 = V<sub>CC</sub>, V<sub>DCIN</sub> = V<sub>LXC</sub> = V<sub>CSSP</sub> = V<sub>CSSN</sub> = 19V, V<sub>BSTC</sub> - V<sub>LXC</sub> = 5V, V<sub>BATT</sub> = V<sub>CSIP</sub> = V<sub>CSIN</sub> = 12.6V, V<sub>VCTL</sub> = V<sub>ISET</sub> = 1.8V, CELLS = open, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                                                 | SYMBOL      | CONI                                                                        | DITIONS                                  | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------|------------------------------------------|------|------|------|-------|

| DH3 On-Time                                                               | tonio       | V <sub>IN</sub> = 12V,                                                      | $R_{TON} = 549k\Omega$<br>(300kHz - 10%) | 866  | 1019 | 1171 | no    |

| DAS ON-TIME                                                               | tON3        | V <sub>OUT3</sub> = 3.3V (Note                                              | 3) $R_{TON} = 202k\Omega$ (800kHz - 10%) | 325  | 382  | 439  | ns    |

| Minimum Off-Time                                                          | toff(MIN)   | (Note 3)                                                                    |                                          | 210  | 270  | 330  | ns    |

| Extended On-Time Blanking                                                 |             | Duty cycle > 50%; no                                                        | ot for production test                   |      | 300  | 360  | ns    |

| Soft-Start Time                                                           | tss         | Rising edge on ON_                                                          |                                          |      | 2    |      | ms    |

| Ultrasonic Operating Frequency                                            | fsw(usonic) | SKIP = GND                                                                  |                                          | 15   | 22   |      | kHz   |

| MAIN SMPS FAULT DETECTION                                                 | ON          |                                                                             |                                          |      |      |      |       |

| OUT_ Overvoltage Trip<br>Threshold (PGOOD Pulled Low<br>Above This Level) |             | With respect to error                                                       | comparator threshold                     | 13   | 16   | 19   | %     |

| OUT_Overvoltage Fault<br>Propagation Delay                                | tovp        | V <sub>FB</sub> forced 50mV al                                              | pove trip threshold                      |      | 10   |      | μs    |

| OUT_ Undervoltage Protection<br>Trip Threshold                            |             | With respect to error comparator threshold                                  |                                          | 65   | 70   | 75   | %     |

| OUT_ Output Undervoltage<br>Fault Propagation Delay                       | tuvp        |                                                                             |                                          |      | 10   |      | μs    |

| PGOOD Lower Trip Threshold                                                |             | With respect to error comparator threshold, falling edge, hysteresis = 15mV |                                          | -350 | -250 | -150 | mV    |

| PGOOD Propagation Delay                                                   | tpgood      | OUT5 or OUT3 forced 50mV beyond PGOOD trip threshold, falling edge          |                                          |      | 10   |      | μs    |

| PGOOD Output Low Voltage                                                  |             | PGOOD low impeda<br>GND, ISINK = 4mA                                        | nce, ON5 = ON3 =                         |      |      | 0.3  | V     |

| PGOOD Leakage Current                                                     | IPGOOD      | PGOOD high impedate regulation, PGOOD for TA = +25°C                        |                                          |      |      | 1    | μΑ    |

| Fault Reset Timer                                                         |             |                                                                             |                                          | 7    | 10   |      | ms    |

| MAIN SMPS CURRENT LIMIT                                                   |             |                                                                             |                                          |      |      |      |       |

| ILIM_ Adjustment Range                                                    |             |                                                                             |                                          | 0.2  |      | 2.1  | V     |

| ILIM_ Leakage Current                                                     |             | T <sub>A</sub> = +25°C                                                      |                                          | -0.1 |      | +0.1 | μΑ    |

| Vallay Current I imit Threat -1-1                                         |             |                                                                             | VILIM_ = 0.5V                            | 40   | 50   | 60   |       |

| Valley Current-Limit Threshold (Adjustable)                               | VLIM_ (VAL) | VAGND - VLX_                                                                | VILIM_ = 1.00V                           | 87   | 100  | 113  | mV    |

| (                                                                         |             |                                                                             | V <sub>ILIM</sub> _ = 2.10V              | 184  | 210  | 236  |       |

| Ultrasonic Negative<br>Current-Limit Threshold                            | INEG(US)    |                                                                             |                                          |      | 72   |      | mV    |

| Current-Limit Threshold (Zero Crossing)                                   | Vzx         | VAGND - VLX_, SKIP<br>VILIM = 1V                                            | = V <sub>CC</sub> or GND,                |      | 1.5  |      | mV    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF,  $V_{CC} = 5V$ , ON3 = ON5 =  $V_{CC}$ ,  $V_{DCIN} = V_{LXC} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BSTC} - V_{LXC} = 5V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 12.6V$ ,  $V_{VCTL} = V_{ISET} = 1.8V$ , CELLS = open, **TA = 0°C to +85°C**, unless otherwise noted. Typical values are at TA = +25°C.)

| PARAMETER                                                         | SYMBOL                              | CONDITIONS                                                                               | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| MAIN SMPS INPUTS AND OUT                                          | PUTS                                |                                                                                          |     |     |     |       |

|                                                                   |                                     | High = SKIP                                                                              | 2.3 |     | Vcc |       |

| SKIP Threshold Voltage                                            | VSKIP                               | Mid = PWM                                                                                | 1.5 |     | 1.9 | V     |

|                                                                   |                                     | Low = ultrasonic                                                                         | 0   |     | 0.8 |       |

| SKIP Leakage Current                                              |                                     | VSKIP = 0 or 5V, TA = +25°C                                                              | -2  |     | +2  | μΑ    |

| ON_ Input Logic Levels                                            |                                     | High (SMPS on)                                                                           | 2.4 |     |     | V     |

| ON_ Input Logic Levels                                            |                                     | Low (SMPS off)                                                                           |     |     | 0.8 | \ \ \ |

| ON_ Leakage Current                                               |                                     | V <sub>ON3</sub> = V <sub>ON5</sub> = 0 or 5V, T <sub>A</sub> = +25°C                    | -2  |     | +2  | μΑ    |

| OUT_ Discharge-Mode On-Resistance                                 | RDSCHG                              | ON_ = GND                                                                                | 7.5 | 20  | 50  | Ω     |

| SMPS GATE DRIVERS                                                 |                                     |                                                                                          |     |     |     |       |

| DH3, DH5 Gate Driver                                              | Davis Davis                         | BST3 - LX3 and BST5 - LX5 forced to 5V;<br>high state                                    |     | 1.6 | 3.8 |       |

| On-Resistance                                                     | R <sub>DH3</sub> , R <sub>DH5</sub> | BST3 - LX3 and BST5 - LX5 forced to 5V; low state                                        |     | 1.6 | 3.8 | Ω     |

| DL3, DL5 Gate Driver                                              | Doug Doug                           | DL3, DL5; high state                                                                     |     | 1.5 | 3.5 |       |

| On-Resistance                                                     | RDL3, RDL5                          | DL3, DL5; low state                                                                      |     | 0.6 | 1.5 | Ω     |

| DH3, DH5 Gate Driver Source/<br>Sink Current                      | IDH                                 | DH3, DH5 forced to 2.5V,<br>BST3 - LX3 and BST5 - LX5 forced to 5V                       |     | 2   |     | А     |

| DL3, DL5 Gate Driver<br>Source Current                            | IDL(SOURCE)                         | DL3, DL5 forced to 2.5V                                                                  |     | 1.7 |     | А     |

| DL3, DL5 Gate Driver<br>Sink Current                              | IDL(SINK)                           | DL3, DL5 forced to 2.5V                                                                  |     | 3.3 |     | А     |

| DHC Gate Driver On-                                               | D                                   | High state, IDHC = 10mA                                                                  |     | 1.5 | 3   |       |

| Resistance                                                        | RDHC                                | Low state, I <sub>DHC</sub> = -10mA                                                      |     | 0.8 | 2.1 | Ω     |

| DLC Gate Driver                                                   | 5                                   | High state, IDLC = 10mA                                                                  |     | 3   | 6   |       |

| On-Resistance                                                     | RDLC                                | Low state, I <sub>DLC</sub> = -10mA                                                      |     | 3   | 6   | Ω     |

| Internal BST_ Switch On-Resistance                                | R <sub>BST</sub>                    | I <sub>BST</sub> _ = 10mA, V <sub>DD</sub> = 5V                                          |     | 5   |     | Ω     |

| BST_ Leakage Current                                              | IBST                                | V <sub>BST</sub> = 24V, OUT3 and OUT5 above regulation threshold, T <sub>A</sub> = +25°C |     | 2   | 20  | μА    |

| CHARGER SMPS                                                      |                                     |                                                                                          |     |     |     |       |

| DHC Off-Time K Factor                                             |                                     | VDCIN = 19V, VBATT = 10V                                                                 | 30  | 35  | 40  | ns/V  |

| Sense Voltage for Minimum<br>Discontinuous Mode Ripple<br>Current |                                     | VCSIP - VCSIN                                                                            |     | 5   |     | mV    |

| Zero Crossing Comparator<br>Threshold                             |                                     | VCSIP - VCSIN                                                                            |     | 10  |     | mV    |

| Cycle-by-Cycle Current- Limit<br>Sense Voltage                    |                                     | VCSIP - VCSIN                                                                            | 120 | 125 | 130 | mV    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF, VCC = 5V, ON3 = ON5 = VCC, VDCIN = VLXC = VCSSP = VCSSN = 19V, VBSTC - VLXC = 5V, VBATT = VCSIP = VCSIN = 12.6V, VVCTL = VISET = 1.8V, CELLS = open, **TA = 0°C to +85°C**, unless otherwise noted. Typical values are at TA = +25°C.)

| PARAMETER                             | SYMBOL     | CON                                                | NDITIONS                                         | MIN          | TYP  | MAX          | UNITS   |

|---------------------------------------|------------|----------------------------------------------------|--------------------------------------------------|--------------|------|--------------|---------|

| CHARGE-VOLTAGE REGULA                 | TION       |                                                    |                                                  |              |      |              |         |

| B B . I V                             |            | CELLS = open, VC                                   | TL = REF, 2 cells                                | -0.5         |      | +0.5         |         |

| Battery-Regulation Voltage            | VBATT      | CELLS = GND, VC                                    | TL = REF, 3 cells                                | -0.5         |      | +0.5         | %       |

| Accuracy                              |            | CELLS = LDO3, VO                                   | CTL = REF, 4 cells                               | -0.5         |      | +0.5         |         |

| VCTL Range                            |            | CELLS = open, 2 c                                  | ells                                             | 1.0          |      | 3.5          | V       |

| VCTL Input Bias Current               |            | VCTL = GND or VC                                   | VCTL = GND or VCTL = REF, T <sub>A</sub> = +25°C |              |      | +1           | μΑ      |

| CELLS 3-Cell Threshold                |            |                                                    |                                                  |              |      | 0.8          | V       |

| CELLS 2-Cell Level                    |            | CELLS = open                                       |                                                  | 1.9          | 2.1  | 2.3          | V       |

| CELLS 4-Cell Threshold                |            |                                                    |                                                  | 2.8          |      |              | V       |

| CELLS Input Bias Current              |            | CELLS = GND or V<br>+25°C                          | CELLS = 3.6V, T <sub>A</sub> =                   | -2           |      | +2           | μΑ      |

| CHARGE-CURRENT REGULA                 | TION       | 1                                                  |                                                  |              |      |              |         |

| ISET Range                            |            | Charging current, a                                | analog setting                                   | 0            |      | REF          | V       |

| Full-Charge-Current Accuracy          | .,,        | VBATT = 4V to                                      | VISET = V <sub>REF</sub> , or<br>PWM = 100%      | 97           | 100  | 103          | /       |

| (CSIP to CSIN)                        | VCSI       | 16.8V                                              | VISET = 0.6 x VREF, or PWM = 60%                 | 57.6         | 60.0 | 62.4         | mV      |

| Trickle Charge-Current<br>Accuracy    | Vcsi       | VBATT = 4V to 16.8V, VISET = VREF/36 or PWM = 2.7% |                                                  | 1.25         | 2.70 | 4.30         | mV      |

| Charge-Current Gain Error             |            |                                                    |                                                  | -1.5         |      | +1.5         | %       |

| Charge-Current Offset Error           |            | Based on VISET = \                                 | /REF and VISET = 0.6 x                           | -1.4         |      | +1.4         | mV      |

| CSIP/CSIN/BATT<br>Input-Voltage Range |            |                                                    |                                                  | 0            |      | 24           | V       |

| CSIP Leakage Current                  |            | VCSIP = VCSIN = 24                                 | 4V, T <sub>A</sub> = +25°C                       | -0.2         |      | +0.2         | μΑ      |

| CSIN Leakage Current                  |            | VCSIP = VCSIN = 24                                 | 4V, T <sub>A</sub> = +25°C                       | 1            |      | 4            | μΑ      |

| ISET Power-Down Mode                  | Viort opvi | ISET falling                                       |                                                  | 20           | 26   | 32           | m\/     |

| Threshold                             | VISET-SDN  | ISET rising                                        |                                                  | 32           | 38   | 46           | mV      |

| ISET Input Bias Current               |            | $V_{ISET} = V_{REF}/2$ and $T_{A} = +25^{\circ}C$  | VISET = VREF,                                    | -0.15        |      | +0.15        | μΑ      |

| ISET PWM Threshold                    |            | ISET rising                                        |                                                  |              |      | 2.4          | V       |

|                                       |            | ISET falling                                       |                                                  | 0.8          |      | -            | v       |

| ISET Frequency                        | fISET      |                                                    |                                                  | 0.128        |      | 500          | kHz     |

| ISET Effective Resolution             |            | fiset = 100kHz                                     |                                                  |              | 8    |              | Bit     |

| INPUT SOURCE-CURRENT RE               | GULATION   |                                                    |                                                  |              |      |              |         |

| Input Source Current-Limit Threshold  | VCSS       | VCSSP - VCSSN                                      |                                                  | 58.5<br>-2.5 | 60.0 | 61.5<br>+2.5 | mV<br>% |

| CSSP/CSSN<br>Input-Voltage Range      |            |                                                    |                                                  | 5            |      | 26           | V       |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF,  $V_{CC} = 5V$ , ON3 = ON5 =  $V_{CC}$ ,  $V_{DCIN} = V_{LXC} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BSTC} - V_{LXC} = 5V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 12.6V$ ,  $V_{VCTL} = V_{ISET} = 1.8V$ , CELLS = open,  $T_A = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                    | SYMBOL              | CONDITIONS                                                              | MIN            | TYP                   | MAX           | UNITS   |

|----------------------------------------------|---------------------|-------------------------------------------------------------------------|----------------|-----------------------|---------------|---------|

| IINP Current-Sense Amplifier<br>Voltage Gain | GIINP               |                                                                         | 59.1           | 60.0                  | 60.9          | V/V     |

| IINP Output-Voltage Range                    |                     |                                                                         | 0              |                       | 4             | V       |

|                                              |                     | VCSSP - VCSSN = 60mV                                                    | -2             |                       | +2            |         |

| IINP Accuracy                                |                     | VCSSP - VCSSN = 40mV                                                    | -3             |                       | +3            | %       |

|                                              |                     | VCSSP - VCSSN = 20mV                                                    | -4             |                       | +4            |         |

| IINP Gain Error                              |                     | Measured at VCSSP - VCSSN = 60mV and VCSSP - VCSSN = 20mV               | -1.25          |                       | +1.25         | %       |

| IINP Offset Error                            |                     | Measured at VCSSP - VCSSN = 60mV and VCSSP - VCSSN = 20mV               | -0.6           |                       | +0.6          | mV      |

| ADAPTER OVERCURRENT (A                       | COC) DETECT         | TION                                                                    |                |                       |               |         |

| ACOCP Threshold                              | VCSIN-OCP           | With respect to VCSSP_VCSSN                                             |                | 78                    |               | mV      |

|                                              | *03111-001          | Will respect to 10331 _103311                                           |                | 130                   |               | %       |

| ACOCP Blanking Time                          |                     |                                                                         |                | 16                    |               | ms      |

| ACOCP Waiting Time                           |                     | When ACOCP comparator is high and at the time the blanking time expires |                | 0.6                   |               | S       |

| ACIN, ACOK, AND ACOV                         |                     |                                                                         |                |                       |               |         |

| ACIN Rising Debounce                         |                     |                                                                         |                | 44                    |               | ms      |

| ACIN Falling Delay                           |                     |                                                                         |                | 10                    |               | μs      |

| ACIN Input Bias Current                      |                     | $T_A = +25$ °C                                                          | -1             |                       | +1            | μΑ      |

| ACOK Detect Threshold                        | VACINOK             | Measured at ACIN rising, hysteresis = 40mV                              | 1.47           | 1.50                  | 1.53          | V       |

| ACON Detect Tilleshold                       | VACINON             | (typ)                                                                   | -2             |                       | +2            | %       |

| ACOV Detect Threshold                        | Vacinov             | Measured at ACIN rising, hysteresis = 40mV (typ)                        | 2.05           | 2.10                  | 2.15<br>+2.38 | V<br>%  |

| ACOK Sink Current                            |                     | VACOK = 0.4V, VACIN = 1.7V                                              | 1              |                       |               | mA      |

| ACOK Leakage Current                         |                     | VACOK = 5.5V, VACIN = 1.3V, TA = +25°C                                  |                |                       | 1             | μΑ      |

| ADAPTER PRESENT DETECT                       | ION                 |                                                                         |                |                       |               |         |

| Adapter Absence<br>Detect Threshold          |                     | VDCIN - VBATT, VDCIN falling                                            | 0              | 100                   | 200           | mV      |

| Adapter Detect Threshold                     |                     | VDCIN - VBATT, VDCIN rising                                             | 300            | 440                   | 600           | mV      |

| CHARGE-PUMP MOSFET DRI                       | VER                 |                                                                         |                |                       |               |         |

| PDSL Gate-Driver Source<br>Current           | IPDSL-SRC           | V <sub>PDSL</sub> - V <sub>DCIN</sub> = 3V, V <sub>DCIN</sub> = 19V     |                | 60                    |               | μА      |

| PDSL Gate-Driver Output<br>Voltage High      | V <sub>PDSL-H</sub> | V <sub>DCIN</sub> = 19V                                                 | VDCIN<br>+ 5.3 | V <sub>DCIN</sub> + 8 |               | V       |

| PDSL SWITCH CONTROL                          | 1                   |                                                                         |                |                       |               | 1       |

| PDSL Turn-Off Resistance                     | RPDSL               | Measured from PDSL to GND                                               |                | 2.5                   |               | kΩ      |

| BATTERY OVERVOLTAGE                          |                     |                                                                         |                |                       |               |         |

| BATT Overvoltage Threshold                   | VCELL(OV)           | V <sub>BATT</sub> rising, hysteresis = 20mV (typ)                       |                | +100                  |               | mV/cell |

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF, VCC = 5V, ON3 = ON5 = VCC, VDCIN = VLXC = VCSSP = VCSSN = 19V, VBSTC - VLXC = 5V, VBATT = VCSIP = VCSIN = 12.6V, VVCTL = VISET = 1.8V, CELLS = open, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 4)

| PARAMETER                            | SYMBOL            | CONDITIONS                                                                                                   |                                       | MIN   | TYP | MAX   | UNITS |

|--------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-----|-------|-------|

| INPUT SUPPLIES                       |                   |                                                                                                              |                                       |       |     |       |       |

| Adapter Present Quiescent            |                   | IDCIN + ICSSP +<br>ICSSN, ON3 = ON5 =                                                                        | Charging enabled                      |       |     | 6     | - mA  |

| Current                              |                   | SKIP = VCC, VOUT3 = 3.5V, VOUT5 = 5.3V                                                                       | Charging disabled                     |       |     | 2.5   | IIIA  |

| Adapter Absent Quiescent             |                   | IDCIN + ICSSP +<br>ICSSN, ON3 = ON5 =                                                                        | VISET = 2.4V,<br>IINP ON              |       |     | 2.5   | mA    |

| Current                              |                   | SKIP = V <sub>CC</sub> , V <sub>OUT3</sub> = 3.5V, V <sub>OUT5</sub> = 5.3V                                  | ISET = GND                            |       |     | 2.2   | IIIA  |

| CSSN Input Current                   |                   | VCSSP = VCSSN = 24V                                                                                          |                                       |       |     | 2     | μA    |

| BATT + CSIP + CSIN + LXC Input       |                   | V <sub>BATT</sub> = 16.8V, adapte                                                                            | er absent                             |       |     | 4     |       |

| Current                              |                   | VBATT = 2V to 19V, ad                                                                                        | apter present                         |       |     | 650   | μΑ    |

| DCIN Input Current                   | IDCIN             | ON3 = ON5 = SKIP = disabled; Vout3 = 3.5                                                                     |                                       |       |     | 0.2   | mA    |

| DCIN Standby Supply Current          |                   | VDCIN = 5V to 24V, ON                                                                                        | N3 = ON5 = GND                        |       |     | 300   | μΑ    |

| VCC Supply Current                   | Icc               | ON3 = ON5 = SKIP = V <sub>CC</sub> , charger<br>disabled; V <sub>OUT3</sub> = 3.5V, V <sub>OUT5</sub> = 5.3V |                                       |       |     | 1.5   | mA    |

| DCIN Input-Voltage Range             |                   | <b>Note:</b> LDO5 is NOT guaranteed to be regulation until DCIN is above 6V                                  |                                       | 4.5   |     | 24    | V     |

| DCIN Undervoltage-Lockout            | .,                | VDCIN falling                                                                                                |                                       | 6.9   |     |       | .,    |

| Trip Point for Charger               | VDCIN(UVLO)       | V <sub>DCIN</sub> rising                                                                                     |                                       |       |     | 7.9   | V     |

| VCC UndervoltageLockout<br>Threshold | VCC(UVLO)         | Falling edge of V <sub>CC</sub> , P this threshold                                                           | WM disabled below                     | 3.8   |     | 4.3   | V     |

| LINEAR REGULATORS                    |                   |                                                                                                              |                                       |       |     |       | ,     |

|                                      | V <sub>LDO5</sub> | VDCIN = 6V to 24V, ON<br>0mA < ILDO5 < 100mA                                                                 | *                                     | 4.85  |     | 5.15  |       |

| LDO_ Output-Voltage Accuracy         | V <sub>LDO3</sub> | VLDO5 = 5V, ILDO5 = 0<br>50mA, ON3 = GND                                                                     | )A, 0mA < 1LDO3 <                     | 3.20  |     | 3.40  | V     |

| LDO3 Short-Circuit Current           |                   | LDO3 = GND                                                                                                   |                                       |       |     | 130   | mA    |

| LDO5 Short-Circuit Current           |                   | LDO5 = GND                                                                                                   |                                       |       |     | 260   | mA    |

| REFERENCE                            |                   |                                                                                                              |                                       |       |     |       |       |

| REF Output Voltage                   | VREF              | IREF = 50µA                                                                                                  |                                       | 2.08  |     | 2.12  | V     |

| MAIN SMPS                            |                   |                                                                                                              |                                       |       |     |       |       |

| OUT5 Output-Voltage Accuracy         | Vout5             | VIN = 6V to 28V, SKIP                                                                                        | = REF                                 | 5.008 |     | 5.160 | V     |

| OUT3 Output-Voltage Accuracy         | Vout3             | $V_{IN} = 6V$ to 28V, SKIP                                                                                   | = REF                                 | 3.25  |     | 3.35  | V     |

| DUE O. T                             |                   | $V_{IN} = 12V,$                                                                                              | $RTON = 549k\Omega$ $(300kHz + 10\%)$ | 1073  |     | 1452  |       |

| DH5 On-Time                          | tON5              | (110te 0)                                                                                                    | RTON = 202kΩ<br>(800kHz + 10%)        | 402   |     | 545   | ns    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF, VCC = 5V, ON3 = ON5 = VCC, VDCIN = VLXC = VCSSP = VCSSN = 19V, VBSTC - VLXC = 5V, VBATT = VCSIP = VCSIN = 12.6V, VVCTL = VISET = 1.8V, CELLS = open, **T<sub>A</sub> = -40°C to +85°C**, unless otherwise noted.) (Note 4)

| PARAMETER                                                                 | SYMBOL           | CON                                  | DITIONS                                                                     | MIN | TYP | MAX  | UNITS    |

|---------------------------------------------------------------------------|------------------|--------------------------------------|-----------------------------------------------------------------------------|-----|-----|------|----------|

| DH3 On-Time                                                               | tonio            | VIN = 12V,<br>VOUT3 = 3.3V           | $R_{TON} = 549k\Omega$<br>(300kHz - 10%)                                    | 866 |     | 1171 | ns       |

| DOS ON-TIME                                                               | tON3             | (Note 3)                             | $R_{TON} = 202k\Omega$<br>(800kHz - 10%)                                    | 325 |     | 439  | 1115     |

| Minimum Off-Time                                                          | toff(MIN)        | (Note 3)                             |                                                                             |     |     | 330  | ns       |

| Extended On-Time Blanking                                                 |                  | Duty cycle > 50%; r                  | not for production test                                                     |     |     | 360  | ns       |

| Ultrasonic Operating Frequency                                            | fsw(usonic)      | SKIP = GND                           |                                                                             | 13  |     |      | kHz      |

| MAIN SMPS FAULT DETECTION                                                 | l                |                                      |                                                                             |     |     |      |          |

| OUT_ Overvoltage Trip Threshold<br>(PGOOD Pulled Low Above this<br>Level) |                  | With respect to erro                 | r comparator threshold                                                      | 12  |     | 20   | %        |

| OUT_ Undervoltage Protection<br>Trip Threshold                            |                  | With respect to erro                 | r comparator threshold                                                      | 63  |     | 77   | %        |

| PGOOD Lower Trip Threshold                                                |                  |                                      | With respect to error comparator threshold, falling edge, hysteresis = 15mV |     |     | -150 | mV       |

| PGOOD Output Low Voltage                                                  |                  | PGOOD low impeda<br>GND, ISINK = 4mA | ance, ON5 = ON3 =                                                           |     |     | 0.4  | V        |

| Fault Reset Timer                                                         |                  | Not for production t                 | est                                                                         | 7   |     |      | ms       |

| MAIN SMPS CURRENT LIMIT                                                   |                  |                                      |                                                                             |     |     |      |          |

| ILIM_ Adjustment Range                                                    |                  |                                      |                                                                             | 0.2 |     | 2.1  | V        |

| Valley Current-Limit Threshold                                            |                  |                                      | V <sub>ILIM</sub> _ = 0.5V                                                  | 40  |     | 60   |          |

| (Adjustable)                                                              | VLIM_ (VAL)      | VAGND - VLX_                         | V <sub>ILIM</sub> _ = 1.00V                                                 | 85  |     | 115  | mV       |

| (/ tajaotabio)                                                            |                  |                                      | V <sub>ILIM</sub> _ = 2.10V                                                 | 174 |     | 246  |          |

| MAIN SMPS INPUTS AND OUTP                                                 | UTS              |                                      |                                                                             |     |     |      |          |

|                                                                           |                  | High = SKIP                          |                                                                             | 2.3 |     | VCC  |          |

| SKIP Threshold Voltage                                                    | VSKIP            | Mid = PWM                            |                                                                             | 1.5 |     | 1.9  | V        |

|                                                                           |                  | Low = ultrasonic                     |                                                                             | 0   |     | 0.8  |          |

| SKIP Leakage Current                                                      |                  | VSKIP = 0 or 5V, TA                  | = +25°C                                                                     | -2  |     | +2   | μΑ       |

| ON_ Input Logic Levels                                                    |                  | High (SMPS on)                       |                                                                             | 2.4 |     |      | V        |

| ON_ Input Logic Lovelo                                                    |                  | Low (SMPS off)                       |                                                                             |     |     | 0.8  | <u> </u> |

| SMPS GATE DRIVERS                                                         |                  |                                      |                                                                             |     |     |      |          |

| DH3, DH5 Gate Driver On-                                                  | RDH3,            | BST3 - LX3 and BS high state         | T5 - LX5 forced to 5V;                                                      |     |     | 3.8  | Ω        |

| Resistance                                                                | R <sub>DH5</sub> | BST3 - LX3 and BS low state          | T5 - LX5 forced to 5V;                                                      |     |     | 3.8  | 22       |

| DL3, DL5 Gate-Driver On-                                                  | D D              | DL3, DL5; high state                 | e                                                                           |     |     | 3.5  |          |

| Resistance                                                                | RDL3, RDL5       | DL3, DL5; low state                  |                                                                             |     |     | 1.5  | Ω        |

| DHC Cata Driver On Basisters                                              | Davia            | High state, IDHC =                   | 10mA                                                                        |     |     | 3    |          |

| DHC Gate-Driver On-Resistance                                             | RDHC             | Low state, IDHC = -                  | 10mA                                                                        |     |     | 2.1  | Ω        |

### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                     | SYMBOL    | CONDIT                               | TIONS                               | MIN   | TYP | MAX  | UNITS |

|-----------------------------------------------|-----------|--------------------------------------|-------------------------------------|-------|-----|------|-------|

|                                               |           | High state, IDLC = 10m               | nA                                  |       |     | 6    |       |

| DLC Gate-Driver On-Resistance                 | RDLC      | Low state, IDLC = -10m               |                                     |       | ,   | 6    | Ω     |

| CHARGER SMPS                                  |           |                                      |                                     |       |     |      | 1     |

| DHC Off-Time K Factor                         |           | VDCIN = 19V, VBATT =                 | 10V                                 | 30    |     | 40   | ns/V  |

| Cycle-by-Cycle Current-Limit<br>Sense Voltage |           | VCSIP - VCSIN                        |                                     | 120   |     | 130  | mV    |

| CHARGE-VOLTAGE REGULATION                     | DN        | I                                    |                                     |       | ,   |      | 1     |

|                                               |           | CELLS = open, VCTL =                 | = REF, 2 cells                      | -0.5  |     | +0.5 |       |

| Battery-Regulation Voltage                    | VBATT     | CELLS = GND, VCTL =                  | = REF, 3 cells                      | -0.5  |     | +0.5 | %     |

| Accuracy                                      |           |                                      |                                     | -0.5  |     | +0.5 | 1     |

| VCTL Range                                    |           |                                      |                                     | 0     |     | 2.4  | V     |

| CELLS 3-Cell Threshold                        |           |                                      |                                     |       |     | 0.8  | V     |

| CELLS 2-Cell Level                            |           | CELLS = open                         |                                     | 1.9   |     | 2.3  | V     |

| CELLS 4-Cell Threshold                        |           |                                      |                                     | 2.8   |     |      | V     |

| CHARGE-CURRENT REGULATION                     | N         |                                      |                                     |       |     |      |       |

| ISET Range                                    |           | Charging current, anal-              | og setting                          | 0.0   |     | REF  | V     |

| Full-Charge-Current Accuracy                  | Vcsi      | V <sub>BATT</sub> = 4V to 16.8V      | VISET = VREF, or<br>PWM = 100%      | 97    |     | 103  | - mV  |

| (CSIP to CSIN)                                | VCSI      | VBATT = 4V to 10.0V                  | VISET = 0.6 x VREF,<br>or PWM = 60% | 57.6  |     | 62.4 | IIIV  |

| Trickle Charge-Current Accuracy               | Vcsı      | VBATT = 4V to 16.8V, V<br>PWM = 2.7% | ISET = VREF/36 or                   | 1.2   |     | 4.3  | mV    |

| Charge-Current Gain Error                     |           |                                      |                                     | -1.5  |     | +1.5 | %     |

| Charge-Current Offset Error                   |           | Based on VISET = VREF                | and and                             | -1.4  |     | +1.4 | mV    |

| CSIP/CSIN/BATT Input<br>Voltage Range         |           |                                      |                                     | 0     |     | 24   | V     |

| ISET Power-Down Mode                          | \/        | ISET falling                         |                                     | 20    |     | 32   | \/    |

| Threshold                                     | VISET-SDN | ISET rising                          |                                     | 32    |     | 46   | mV    |

| ISET PWM Threshold                            |           | ISET rising                          |                                     |       |     | 2.4  | V     |

| ISET LAMIN THESHOR                            |           | ISET falling                         |                                     | 0.8   |     |      |       |

| ISET Frequency                                | fISET     |                                      |                                     | 0.128 |     | 500  | kHz   |

MIXIM

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF,  $V_{CC} = 5V$ , ON3 = ON5 =  $V_{CC}$ ,  $V_{DCIN} = V_{LXC} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BSTC} - V_{LXC} = 5V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 12.6V$ ,  $V_{VCTL} = V_{ISET} = 1.8V$ , CELLS = open,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 4)

| PARAMETER                                    | PARAMETER SYMBOL CONDITIONS |                                                           | MIN            | TYP       | MAX   | UNITS |  |

|----------------------------------------------|-----------------------------|-----------------------------------------------------------|----------------|-----------|-------|-------|--|

| INPUT SOURCE-CURRENT REGULATION              |                             |                                                           |                |           |       |       |  |

| Input Source-Current Limit                   | Voce                        | VCSSP - VCSSN                                             | 58.5           |           | 61.5  | mV    |  |

| Threshold                                    | Vcss                        | VCSSP - VCSSN                                             | -2.5           |           | +2.5  | %     |  |

| CSSP/CSSN Input-Voltage Range                |                             |                                                           | 5              |           | 26    | V     |  |

| IINP Current-Sense Amplifier<br>Voltage Gain | GIINP                       |                                                           | 59.9           |           | 60.1  | V/V   |  |

| IINP Output-Voltage Range                    |                             |                                                           | 0              |           | 4     | V     |  |

|                                              |                             | VCSSP - VCSSN = 60mV                                      | -2             |           | +2    |       |  |

| IINP Accuracy                                |                             | VCSSP - VCSSN = 40mV                                      | -3             |           | +3    | %     |  |

|                                              |                             | VCSSP - VCSSN = 20mV                                      | -4             |           | +4    |       |  |

| IINP Gain Error                              |                             | Measured at VCSSP - VCSSN = 60mV and VCSSP - VCSSN = 20mV | -1.5           |           | +1.5  | %     |  |

| IINP Offset Error                            |                             | Measured at VCSSP - VCSSN = 60mV and VCSSP - VCSSN = 20mV | -0.65          |           | +0.65 | mV    |  |

| ACIN, ACOK, AND ACOV                         |                             |                                                           |                |           |       |       |  |

| ACOK Detect Threshold                        | Vacinok                     | Measured at ACIN rising, hysteresis = 40mV                | 1.47           | 1.47 1.53 |       | V     |  |

| ACON Detect Theshold                         | VACINON                     | (typ)                                                     | -2             |           | +2    | %     |  |

| ACOV Detect Threshold                        | Vacinov                     | Measured at ACIN rising, hysteresis = 40mV                | 2.05           |           | 2.15  | V     |  |

| 7.00 V Detect Theshold                       | VACINOV                     | (typ)                                                     | -2.38          |           | +2.38 | %     |  |

| ACOK Sink Current                            |                             | $V\overline{ACOK} = 0.4V, VACIN = 1.7V$                   | 1              |           |       | mA    |  |

| ADAPTER PRESENT DETECTION                    | N                           |                                                           |                |           |       |       |  |

| Adapter Absence Detect<br>Threshold          |                             | VDCIN - VBATT, VDCIN falling                              | 0              |           | 200   | mV    |  |

| Adapter Detect Threshold                     |                             | VDCIN - VBATT, VDCIN rising                               | 300            |           | 600   | mV    |  |

| CHARGE-PUMP MOSFET DRIVE                     | R                           |                                                           |                |           |       |       |  |

| PDSL Gate-Driver Output<br>Voltage High      | V <sub>PDSL_H</sub>         | V <sub>DCIN</sub> = 19V                                   | VDCIN +<br>5.3 |           |       | V     |  |

Note 3: On-time and off-time specifications are measured from 50% point to 50% point at the DH pin with LX = PGND, V<sub>BST</sub> = 5V, and a 500pF capacitor from DH to LX to simulate external MOSFET gate capacitance. Actual in-circuit times may be different due to MOSFET switching speeds.

**Note 4:** Specifications to  $T_A = -40^{\circ}C$  are guaranteed by design and not production tested.

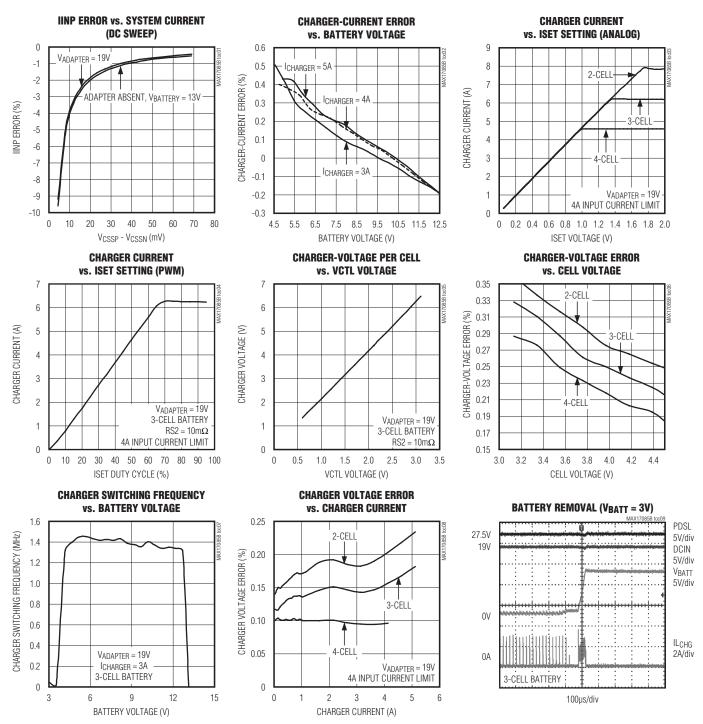

### **Typical Operating Characteristics**

(Circuit of Figure 1, VADP = VSYS = 20V, VBATT = 16.8V, VLDQ5 = VCC = 5V, VLDQ3 = 3.3V, TA = +25°C, unless otherwise noted.)

# MAX17085B

# Integrated Charger, Dual Main Step-Down Controllers, and Dual LDO Regulators

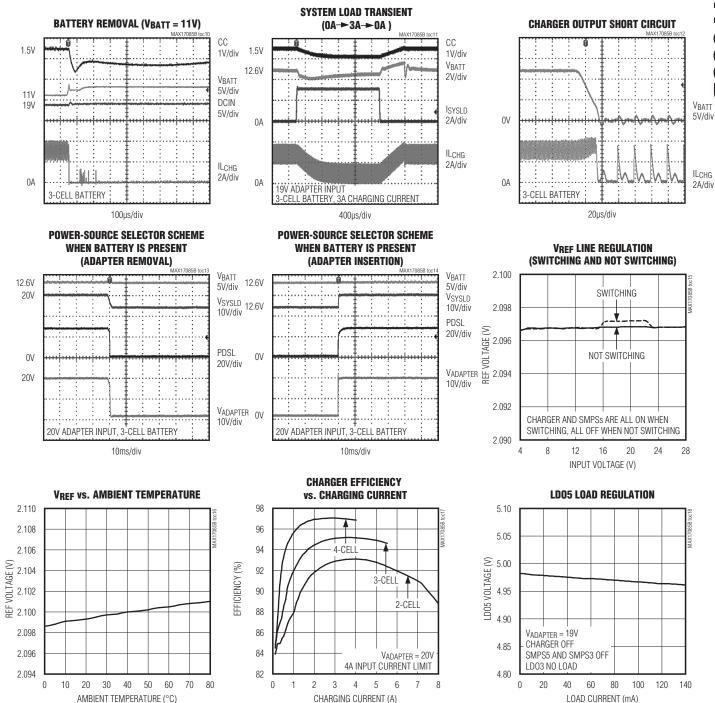

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1, VADP = VSYS = 20V, VBATT = 16.8V, VLDO5 = VCC = 5V, VLDO3 = 3.3V, TA = +25°C, unless otherwise noted.)

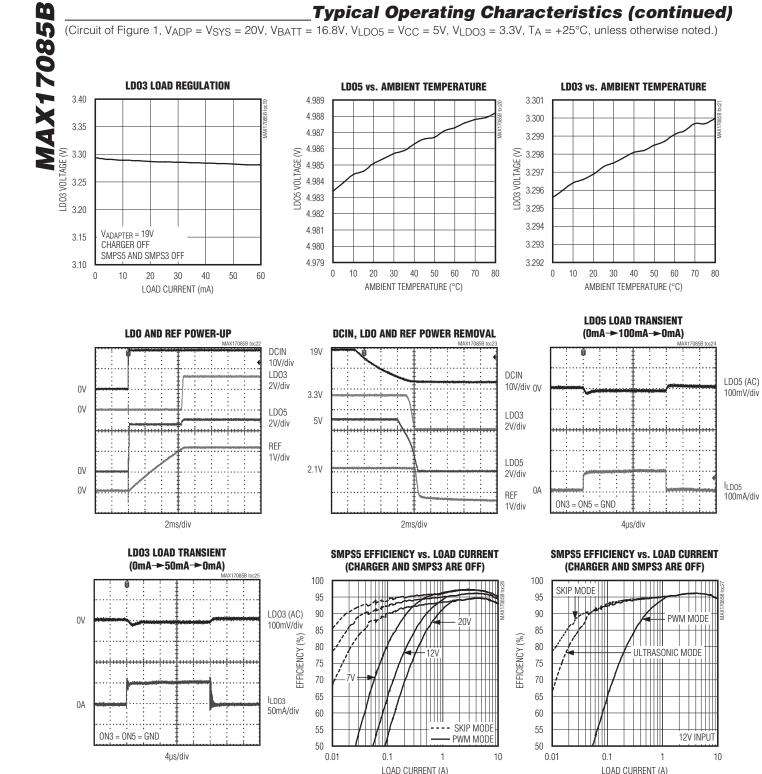

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1, VADP = VSYS = 20V, VBATT = 16.8V, VLDO5 = VCC = 5V, VLDO3 = 3.3V, TA = +25°C, unless otherwise noted.)

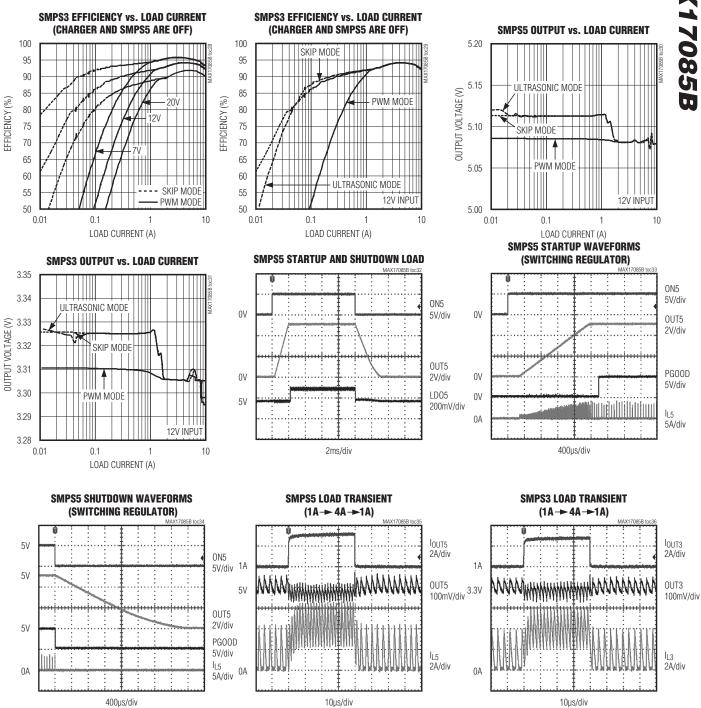

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1, VADP = VSYS = 20V, VBATT = 16.8V, VLDO5 = VCC = 5V, VLDO3 = 3.3V, TA = +25°C, unless otherwise noted.)

### Pin Description

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LX3   | Inductor Connection for SMPS3. Connect LX3 to the switched side of the inductor. LX3 is the lower supply rail for the DH3 high-side gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

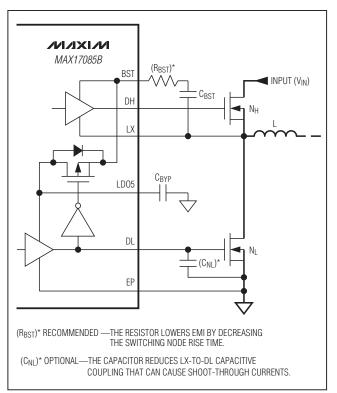

| 2   | BST3  | Boost Flying Capacitor Connection for SMPS3. Connect to an external capacitor as shown in Figure 1. An optional resistor in series with BST3 allows the DH3 turn-on current to be adjusted. A $4.7\Omega$ resistor is recommended to improve crosstalk between SMPSs.                                                                                                                                                                                                                                                                                                                                        |

| 3   | DL3   | Low-Side Gate-Driver Output for SMPS3. DL3 swings from PGND to LDO5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4   | OUT3  | Output Voltage-Sense Input for SMPS3. OUT3 is an input to the Quick-PWM on-time one-shot timer. OUT3 also serves as the feedback input for the preset 3.3V, and the discharge path when in shutdown. When OUT3 is in regulation, LDO3 is internally set to a lower level, and a bypass switch between OUT3 and LDO3 is enabled.                                                                                                                                                                                                                                                                              |

| 5   | LDO3  | 3.3V Linear Regulator Output. LDO3 is the output of the 3.3V linear regulator supplied from LDO5. LDO3 is switched over to OUT3 when SMPS3 is in regulation plus 200µs. Bypass LDO3 to PGND with a 4.7µF or greater ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                       |

| 6   | DCIN  | LDO5 Supply Input. Bypass DCIN with a 1µF capacitor to PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7   | LDO5  | 5V Linear Regulator Output. LDO5 provides the power to the MOSFET drivers. LDO5 is the output of the 5V linear regulator supplied from DCIN. LDO5 is switched over to OUT5 when SMPS5 is in regulation plus 200µs. Bypass LDO5 to PGND with a 4.7µF or greater ceramic capacitor.                                                                                                                                                                                                                                                                                                                            |

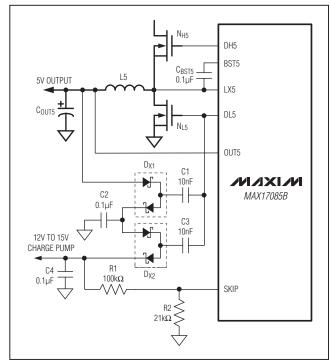

| 8   | OUT5  | Output Voltage-Sense Input for SMPS5. OUT5 is an input to the Quick-PWM on-time one-shot timer. OUT5 also serves as the feedback input for the preset 5V, and the discharge path when in shutdown. When OUT5 is in regulation, LDO5 is internally set to a lower level, and a bypass switch between OUT5 and LDO5 is enabled.                                                                                                                                                                                                                                                                                |

| 9   | DL5   | Low-Side Gate-Driver Output for SMPS5. DL5 swings from PGND to LDO5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |