#### **General Description**

The MAX1932 generates a low-noise, high-voltage output to bias avalanche photodiodes (APDs) in optical receivers. Very low output ripple and noise is achieved by a constant-frequency, pulse-width modulated (PWM) boost topology combined with a unique architecture that maintains regulation with an optional RC or LC post filter inside its feedback loop. A precision reference and error amplifier maintain 0.5% output voltage accuracy.

The MAX1932 protects expensive APDs against adverse operating conditions while providing optimal bias. Traditional boost converters measure switch current for protection, whereas the MAX1932 integrates accurate high-side current limiting to protect APDs under avalanche conditions. A current-limit flag allows easy calibration of the APD operating point by indicating the precise point of avalanche breakdown. The MAX1932 control scheme prevents output overshoot and undershoot to provide safe APD operation without data loss.

The output voltage can be accurately set with either external resistors, an internal 8-bit DAC, an external DAC, or other voltage source. Output span and offset are independently settable with external resistors. This optimizes the utilization of DAC resolution for applications that may require limited output voltage range, such as 4.5V to 15V, 4.5V to 45V, 20V to 60V, or 40V to 90V.

#### **Applications**

- Optical Receivers and Modules

- Fiber Optic Network Equipment

- Telecom Equipment

- Laser Range Finders

- PIN Diode Bias Supply

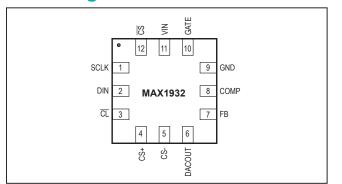

#### **Pin Configuration**

# Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

#### **Features**

- Unique Architecture Delivers Excellent Accuracy for Improved System Performance

- 0.5% Accurate Output

- Low Ripple Output (< 1mV)</li>

- Protection Features Guarantee Safe Operation

- Accurate High-Side Current Limit

- Avalanche Indicator Flag

- Output-Voltage Flexibility Facilitates Multiple Applications and Design Approaches

- 4.5V to 90V Output

- Set Output Voltage via 8-Bit SPI-Compatible Internal DAC, External DAC, or External Resistors

- Small Circuit Footprint Reduces Equipment Size

- 12-Pin, 4mm x 4mm Thin QFN Package

- Circuit Height < 2mm

- Commonly Available 2.7V to 5.5V Input Voltage Range

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1932ETC | -40°C to +85°C | 12 Thin QFN |

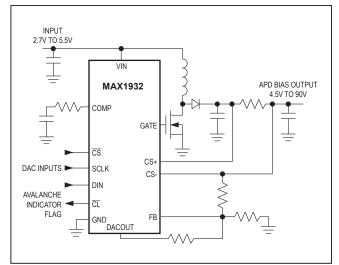

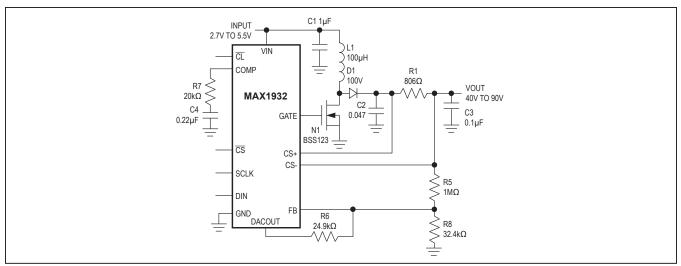

### **Typical Application Circuit**

# Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

### **Absolute Maximum Ratings**

| VIN to GND                                           | 0.3V to +6V                     |

|------------------------------------------------------|---------------------------------|

| DIN, SCLK, CS, FB to GND                             | 0.3V to +6V                     |

| COMP, DACOUT, GATE, CL to GND                        | 0.3V to (V <sub>IN</sub> +0.3V) |

| CS+, CS- to GND                                      |                                 |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C | C)                              |

| 12-Pin Thin QFN (derate 16.9mW/°C abov               | ve +70°C)1349mW                 |

| Operating Temperature Range      | 40°C to +85°C   |

|----------------------------------|-----------------|

| Junction Temperature             | +150°C          |

| Storage Temperature Range        | -65°C to +150°C |

| Lead Temperature (soldering 10s) | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{IN} = 3.3V, \overline{CS} = SCLK = D_{IN} = 3.3V, CS + = CS - = 45V, Circuit of <u>Figure 2</u>,$ **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted.)

| PARAMETER                                     | SYMBOL                | CONDITIONS                                           | MIN     | TYP    | MAX     | UNITS |

|-----------------------------------------------|-----------------------|------------------------------------------------------|---------|--------|---------|-------|

| GENERAL                                       |                       |                                                      |         |        |         |       |

| Input Supply Range                            | V <sub>IN</sub>       |                                                      | 2.7     |        | 5.5     | V     |

| V <sub>IN</sub> Undervoltage Lockout          | UVLO                  | Both rise/fall, hysteresis = 100mV                   | 2.1     |        | 2.6     | V     |

| Operating Supply Current                      | I <sub>IN</sub>       |                                                      |         | 0.5    | 1       | mA    |

| VIN Shutdown Supply Current                   | I <sub>SHDN</sub>     | 00 hex loaded to DAC                                 |         | 25     | 65      | μA    |

| Input Resistance for CS+/CS-                  |                       | Resistance from either pin to ground                 | 0.5     | 1      | 2.0     | MΩ    |

| Current-Limit Threshold<br>for CS+/CS-        |                       |                                                      | 1.80    | 2.00   | 2.20    | V     |

| Common-Mode Rejection<br>of Current Threshold |                       | CS+ = 3V to 100V                                     |         | ±0.005 |         | %/V   |

| Gate-Driver Resistance                        |                       | Gate high or low, I <sub>GATE</sub> = ±50mA          |         | 5      | 10      | Ω     |

| Input Bias Current                            |                       |                                                      | -25     |        | +25     | nA    |

|                                               | \/                    | T <sub>A</sub> = +25°C                               | 1.24375 | 1.2500 | 1.25625 | v     |

| FB Voltage                                    | V <sub>FB</sub>       | $T_A = 0^{\circ}C$ to +85°C                          | 1.24250 | 1.2500 | 1.25750 | v     |

| FB Voltage Temperature<br>Coefficient         | TCV <sub>FB</sub>     |                                                      |         | 0.0007 |         | %/°C  |

| FB to COMP Transconductance                   |                       | COMP = 1.5V                                          | 50      | 110    | 200     | μS    |

| COMP Pulldown Resistance<br>in Shutdown       |                       | DAC code = 00 hex                                    |         |        | 100     | Ω     |

| DACOUT to FB Voltage Difference               |                       | DAC code = FF hex                                    | -3      |        | +3      | mV    |

| DACOUT Differential Nonlinearity<br>(Note 1)  |                       | DAC Code = 01 to FF hex,<br>DAC guaranteed monotonic | -1      |        | +1      | LSB   |

| DACOUT Voltage Temperature<br>Coefficient     | TCV <sub>DACOUT</sub> |                                                      |         | 0.0007 |         | %/µC  |

| DACOUT Load Regulation                        |                       | DAC code = 0F to FF hex, source or sink 50µA         | -1      |        | +1      | mV    |

| Switching Frequency                           | fosc                  |                                                      | 250     | 300    | 340     | kHz   |

| GATE Maximum On-Time                          | t <sub>ON</sub>       |                                                      |         | 3      |         | μs    |

# Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, \overline{CS} = SCLK = D_{IN} = 3.3V, CS = CS = 45V, Circuit of <u>Figure 2</u>,$ **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted.)

| PARAMETER                                        | SYMBOL            | CONDITIONS                  | MIN                   | ТҮР | MAX | UNITS    |

|--------------------------------------------------|-------------------|-----------------------------|-----------------------|-----|-----|----------|

| DIGITAL INPUTS (DIN, SCLK, CS                    | <u>5</u> )        |                             | I                     |     |     |          |

| Input Low Voltage                                |                   |                             |                       |     | 0.6 | V        |

| Input High Voltage                               |                   |                             | 1.4                   |     |     | V        |

| Input Hysteresis                                 |                   |                             |                       | 200 |     | mV       |

|                                                  |                   | T <sub>A</sub> = +25°C      | -1                    |     | +1  | μA       |

| Input Leakage Current                            |                   | $T_A = 0^{\circ}C$ to +85°C |                       | 10  |     | nA       |

| Input Capacitance                                |                   |                             |                       | 5   |     | pF       |

| DIGITAL OUTPUT (CL)                              |                   |                             | ·                     |     |     | <u> </u> |

| Output Low Voltage                               |                   | I <sub>SINK</sub> = 1mA     |                       |     | 0.1 | V        |

| Output High Voltage                              |                   | I <sub>SOURCE</sub> = 0.5mA | V <sub>IN</sub> - 0.5 |     |     | V        |

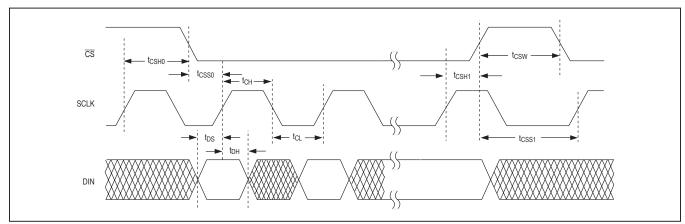

| SPI TIMING (Figure 5)                            |                   |                             |                       |     |     |          |

| SCLK Clock Frequency                             | f <sub>SCLK</sub> |                             |                       |     | 2   | MHz      |

| SCLK Low Period                                  | t <sub>CL</sub>   |                             | 125                   |     |     | ns       |

| SCLK High Period                                 | t <sub>CH</sub>   |                             | 125                   |     |     | ns       |

| Data Hold Time                                   | t <sub>DH</sub>   |                             | 0                     |     |     | ns       |

| Data Setup Time                                  | t <sub>DS</sub>   |                             | 125                   |     |     | ns       |

| CS Assertion to SCLK<br>Rising Edge Setup Time   | t <sub>CSS0</sub> |                             | 200                   |     |     | ns       |

| CS Deassertion to SCLK<br>Rising Edge Setup Time | t <sub>CSS1</sub> |                             | 200                   |     |     | ns       |

| SCLK Rising Edge to CS Deassertion               | tCSH1             |                             | 200                   |     |     | ns       |

| SCLK Rising Edge to CS Assertion                 | tCSH0             |                             | 200                   |     |     | ns       |

| CS High Period                                   | t <sub>CSW</sub>  |                             | 300                   |     |     | ns       |

### **Electrical Characteristics**

$(V_{IN} = 3.3V, \overline{CS} = SCLK = D_{IN} = 3.3V, CS + = CS - = 45V, Circuit of Figure 2, T_A = -40°C to +85°C, unless otherwise noted.) (Note 2)$

| PARAMETER                              | SYMBOL            | CONDITIONS                                  | MIN  | TYP | MAX  | UNITS |

|----------------------------------------|-------------------|---------------------------------------------|------|-----|------|-------|

| GENERAL                                |                   |                                             |      |     |      |       |

| Input Supply Range                     | V <sub>IN</sub>   |                                             | 2.7  |     | 5.5  | V     |

| V <sub>IN</sub> Undervoltage Lockout   | UVLO              | Both rise/fall, hysteresis = 100mV          | 2.1  |     | 2.6  | V     |

| Operating Supply Current               | I <sub>IN</sub>   |                                             |      |     | 1    | mA    |

| VIN Shutdown Supply Current            | I <sub>SHDN</sub> | 00 hex loaded to DAC                        |      |     | 65   | μA    |

| Input Resistance for CS+/CS-           |                   | Resistance from either pin to ground        | 0.5  |     | 2    | MΩ    |

| Current-Limit Threshold<br>for CS+/CS- |                   |                                             | 1.80 |     | 2.20 | V     |

| Gate-Driver Resistance                 |                   | Gate high or low, I <sub>GATE</sub> = ±50mA |      |     | 10   | Ω     |

| FB Input Bias Current                  |                   |                                             | -30  |     | +30  | nA    |

# Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, \overline{CS} = SCLK = D_{IN} = 3.3V, CS + = CS - = 45V, Circuit of Figure 2, T_A = -40°C to +85°C, unless otherwise noted.) (Note 2)$

| PARAMETER                                        | SYMBOL            | CONDITIONS                                        | MIN                   | TYP | MAX     | UNITS |

|--------------------------------------------------|-------------------|---------------------------------------------------|-----------------------|-----|---------|-------|

| GENERAL                                          |                   |                                                   |                       |     |         |       |

| PARAMETER                                        | SYMBOL            | CONDITIONS                                        | MIN                   | TYP | MAX     | UNITS |

| FB Voltage                                       | V <sub>FB</sub>   |                                                   | 1.23875               |     | 1.26125 | V     |

| FB to COMP Transconductance                      |                   | COMP = 1.5V                                       | 50                    |     | 200     | μS    |

| COMP Pulldown Resistance<br>in Shutdown          |                   | DAC code = 00 hex                                 |                       |     | 100     | Ω     |

| DACOUT to FB Voltage Difference                  |                   | DAC code = FF hex                                 | -4                    |     | +4      | mV    |

| DACOUT Differential Nonlinearity<br>(Note 1)     |                   | DAC Code = 01 to FF hex, DAC guaranteed monotonic | -1                    |     | +1      | LSB   |

| DACOUT Load Regulation                           |                   | DAC code = 0F to FF hex, source or sink $50\mu$ A | -1                    |     | +1      | mV    |

| Switching Frequency                              | fosc              |                                                   | 240                   |     | 360     | kHz   |

| DIGITAL INPUTS (DIN, SCLK, CS)                   |                   |                                                   |                       |     |         |       |

| Input Low Voltage                                |                   |                                                   |                       |     | 0.6     | V     |

| Input High Voltage                               |                   |                                                   | 1.4                   |     |         | V     |

| DIGITAL OUTPUT (CL)                              |                   |                                                   |                       |     |         |       |

| Output Low Voltage                               |                   | I <sub>SINK</sub> = 1mA                           |                       |     | 0.1     | V     |

| Output High Voltage                              |                   | I <sub>SOURCE</sub> = 0.5mA                       | V <sub>IN</sub> - 0.5 |     |         | V     |

| SPI TIMING (Figure 5)                            |                   |                                                   |                       |     |         | ,     |

| SCLK Clock Frequency                             | f <sub>SCLK</sub> |                                                   |                       |     | 2       | MHz   |

| SCLK Low Period                                  | t <sub>CL</sub>   |                                                   | 125                   |     |         | ns    |

| SCLK High Period                                 | t <sub>CH</sub>   |                                                   | 125                   |     |         | ns    |

| Data Hold Time                                   | t <sub>DH</sub>   |                                                   | 0                     |     |         | ns    |

| Data Setup Time                                  | t <sub>DS</sub>   |                                                   | 125                   |     |         | ns    |

| CS Assertion to SCLK<br>Rising Edge Setup Time   | t <sub>CSS0</sub> |                                                   | 200                   |     |         | ns    |

| CS Deassertion to SCLK<br>Rising Edge Setup Time | t <sub>CSS1</sub> |                                                   | 200                   |     |         | ns    |

| SCLK Rising Edge to CS Deassertion               | t <sub>CSH1</sub> |                                                   | 200                   |     |         | ns    |

| SCLK Rising Edge to CS Assertion                 | t <sub>CSH0</sub> |                                                   | 200                   |     |         | ns    |

| CS High Period                                   | t <sub>CSW</sub>  |                                                   | 300                   |     |         | ns    |

**Note 1:**DACOUT = DAC code x (1.25V/256) + 1.25V/256.

Note 2:Specifications to -40°C are guaranteed by design and not production tested.

# Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

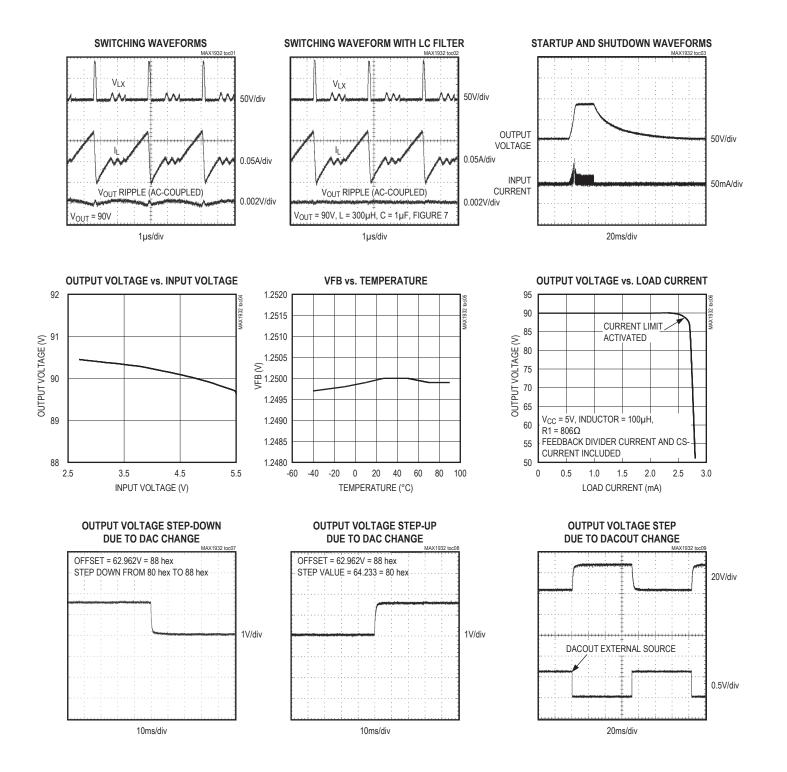

### **Typical Operating Characteristics**

(V<sub>IN</sub> = 5V, Circuit of Figure 2, T<sub>A</sub> =+25°C, unless otherwise noted)

# Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

### **Pin Description**

| PIN | NAME   | FUNCTION                                                                                                                                                                           |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SCLK   | DAC Serial Clock Input                                                                                                                                                             |

| 2   | DIN    | DAC Serial Data Input                                                                                                                                                              |

| 3   | CL     | Current-Limit Indicator Flag. $\overline{CL} = 0$ indicates that the part is in current limit. Logic high level = VIN.                                                             |

| 4   | CS+    | Current-Limit Plus Sense Input. Connect a resistor from CS+ to CS- in series with the output. The differential threshold is 2V. CS+ has typically $1M\Omega$ resistance to ground. |

| 5   | CS-    | Current-Limit Minus Sense Input. CS- has typically $1M\Omega$ resistance to ground.                                                                                                |

| 6   | DACOUT | Internal DAC Output. Generates a control voltage for adjustable output operation. DACOUT can source or sink 50µA.                                                                  |

| 7   | FB     | Feedback input. Connect to a resistive voltage-divider between the output voltage (V <sub>OUT</sub> ) and FB to set the output voltage. The feedback set point is 1.25V.           |

| 8   | COMP   | Compensation Pin. Compensates the DC-DC converter control loop with a series RC to GND. COMP is actively discharged to ground during shutdown or undervoltage conditions.          |

| 9   | GND    | Ground                                                                                                                                                                             |

| 10  | GATE   | Gate-Driver Output for External N-FET                                                                                                                                              |

| 11  | VIN    | IC Supply Voltage (2.7V to 5.5V). Bypass VIN with a 1µF or greater ceramic capacitor.                                                                                              |

| 12  | CS     | DAC Chip-Select Input                                                                                                                                                              |

### **Detailed Description**

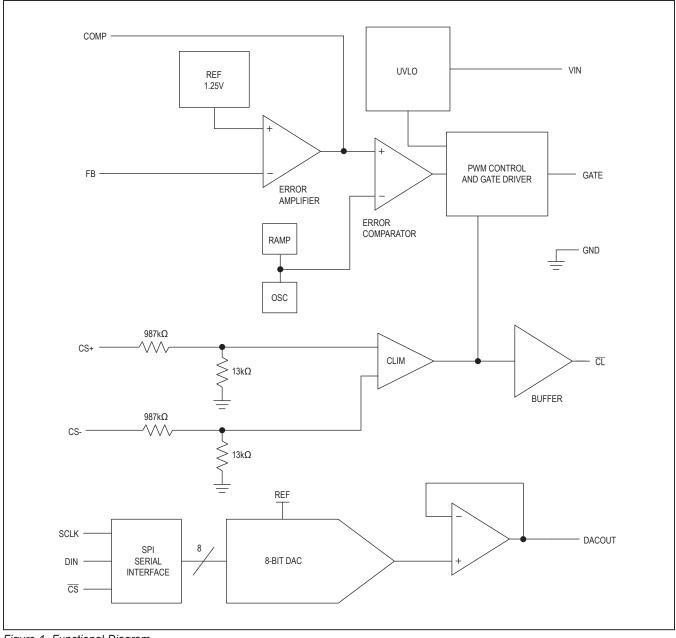

#### **Fixed Frequency PWM**

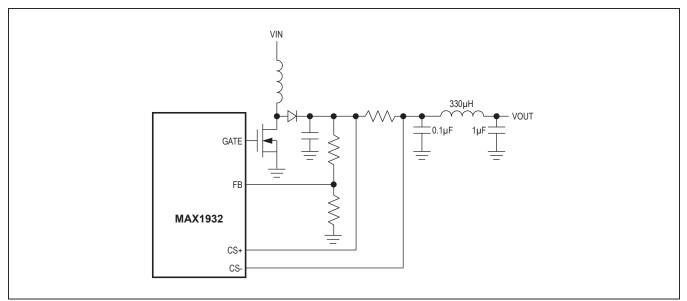

The MAX1932 uses a constant frequency, PWM, controller architecture. This controller sets the switch ontime and drives an external N-channel MOSFET (see Figure 1). As the load varies, the error amplifier sets the inductor peak current necessary to supply the load and regulate the output voltage.

#### **Output Current Limit**

The MAX1932 uses an external resistor at CS+ and CSto sense the output current (see Figure 2). The typical current-limit threshold is 2V.  $\overline{CL}$  is designed to help find the optimum APD bias point by going low to indicate when the APD reaches avalanche and that current limit has been activated. To minimize noise,  $\overline{CL}$  only changes state on an internal oscillator edge.

#### **Output Control DAC**

An internal digital-to-analog converter can be used to control the output voltage of the DC-DC converter (Figure 2). The DAC output is changed through an SPI<sup>TM</sup> serial interface using an 8-bit control byte. On power-up, the DAC defaults to FF hex (1.25V), which corresponds to a minimum boost converter output voltage.

Alternately, the output voltage can be set with external resistors, an external DAC, or a voltage source. Output

span and offset are independently settable with external resistors. See the <u>Applications Information</u> section for output control equations.

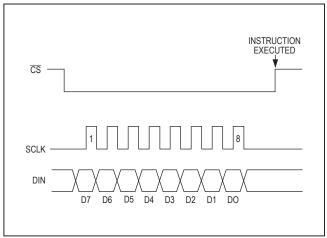

#### SPI Interface/Shutdown

Use an SPI-compatible 3-wire serial interface with the MAX1932 to control the DAC output voltage and to shut down the MAX1932. Figures 4 and 5 show timing diagrams for the SPI protocol. The MAX1932 is a write-only device and uses  $\overline{CS}$  along with SCLK and DIN to communicate. The serial port is always operational when the device is powered. To shut down the DC-DC converter portion only, update the DAC registers to 00 hex.

### **Applications Information**

#### **Voltage Feedback Sense Point**

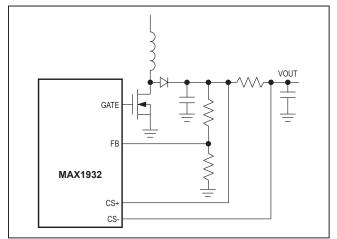

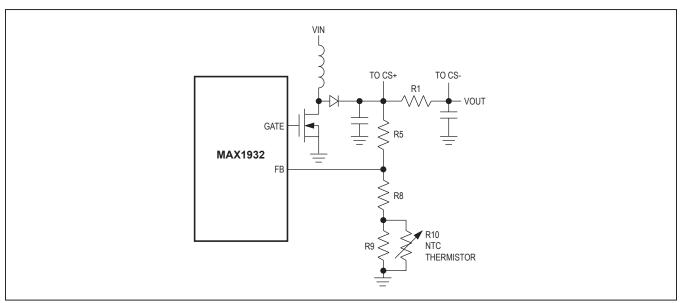

Feedback can be taken from in front of, or after, the currentlimit sense resistor. The current-limit sense resistor forms a lowpass filter with the output capacitor. Taking feedback after the current-limit sense resistor (see <u>Figure 2</u>), optimizes the output voltage accuracy, but requires overcompensation, which slows down the control loop response. For faster response, the feedback can be taken from in front of the current-sense resistor (see <u>Figure 3</u>). This configuration however, makes the output voltage more sensitive to load variation and degrades output accuracy by an amount equal to the load current times the current-sense resistor value.

#### **Output and DAC Adjustments Range**

Many biasing applications require an adjustable output voltage, which is easily obtained using the MAX1932's DAC output (Figure 2).

The DAC output voltage is given by the following equation:

On power-up, DACOUT defaults to FF hex or 1.25V, which corresponds to the minimum  $V_{OUT}$  output voltage.

The voltage generated at DACOUT is coupled to FB through R6. DACOUT can sink only  $50\mu A$  so:

$$R6 \ge \frac{1.25V}{50\mu A}$$

Select the minimum output voltage ( $V_{OUTFF}$ ), and the maximum output voltage ( $V_{OUT01}$ ) for the desired adjustment range. R5 sets the adjustment span using the following equation:

$$R5 = (V_{OUT01} - V_{OUTFF}) (R6/1.25V)$$

R8 sets the minimum output of the adjustment range with the following equation:

$$R8 = (1.25V \times R5)/(V_{OUTFF})$$

# Setting the Output Voltage without the DAC

Adjust the output voltage by connecting a voltagedivider from the output (V<sub>OUT</sub>) to FB (Figure 2 with R6 omitted). Select R8 between  $10k\Omega$  to  $50k\Omega$ . Calculate R5 with the following equation:

$$R5 = R8 \left( \frac{VOUT}{1.25V} - 1 \right)$$

#### **Inductor Selection**

Optimum inductor selection depends on input voltage, output voltage, maximum output current, switching frequency, and inductor size. Inductors are typically specified by their inductance (L), peak current ( $I_{PK}$ ), and resistance (LR).

### Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

The inductance value is given by:

$$L = \frac{(V_{IN})^2 \times D^2 \times T \times \eta}{2I_{OUT(MAX)} \times V_{OUT}}$$

where V<sub>IN</sub> is the input voltage,  $I_{OUT(MAX)}$  is the maximum output current delivered,  $V_{OUT}$  is the output voltage, and T is the switching period (3.3µs),  $\eta$  is the estimated power conversion efficiency, and D is the maximum duty cycle:

$D < (V_{OUT} - V_{IN})/V_{OUT}$  up to a maximum of 0.9

Since the L equation factors in efficiency, for inductor calculation purposes, an  $\eta$  of 0.5 to 0.75 is usually suitable.

For example, with a maximum DC load current of 2.5mA, a 90V output,  $V_{IN}$  = 5V, D = 0.9, T = 3.3µs, and  $\eta$  estimated at 0.75, the above equation yields an L of 111µH, so 100µH would be a suitable value.

The peak inductor current is given by:

$$I_{PK} = \frac{V_{IN} \times D \times T}{L}$$

These are typical calculations. For worst case, refer to the article titled "Choosing the MAX1932 External Indicator, Diode, Current Sense Resistor, and Output Filter Capacitor for Worst Case Conditions" located on the Maxim website in the Application Notes section (visit www.maximintegrated.com/an1805).

#### **External Power-Transistor Selection**

An N-FET power switch is required for the MAX1932. The N-FET switch should be selected to have adequate onresistance with the MOSFET  $V_{GS} = V_{IN(MIN)}$ . The breakdown voltage of the N-FET must be greater than  $V_{OUT}$ .

For higher-current output applications (such as 5mA at 90V), SOT23 high-voltage low-gate-threshold N-FETs may not have adequate current capability. For example, with a 5V input, a 90V, 5mA output requires an inductor peak of 240mA. For such cases it may be necessary to simply parallel two N-FETs to achieve the required current rating. With SOT23 devices this often results in smaller and lower cost than using a larger N-FET device.

#### **Diode Selection**

The output diode should be rated to handle the output voltage and the peak switch current. Make sure that the diode's peak current rating is at least  $I_{PK}$  and that its breakdown voltage exceeds  $V_{OUT}$ . Fast reverse recovery time ( $t_{rr} < 10$ ns) and low junction capacitance (<10pF) are recommended to minimize losses. A small-signal silicon switching diode is suitable if efficiency is not critical.

#### **Output Filter Capacitor Selection**

The output capacitors of the MAX1932 must have high enough voltage rating to operate with the  $V_{OUT}$  required. Output capacitor effective series resistance (ESR) determines the amplitude of the high-frequency ripple seen on the output voltage. In the typical application circuit, a second RC formed by R1 and C3 further reduces ripple.

#### Input Bypass Capacitor Selection

The input bypass capacitor reduces the peak currents drawn from the voltage source and reduces noise caused by the MAX1932's switching action. The input source impedance determines the size of the capacitor required at the input (VIN). A low ESR capacitor is recommended. A 1 $\mu$ F ceramic capacitor is adequate for most applications. Place the bypass capacitor as close as possible to the VIN and GND pins.

#### **Current-Sense Resistor Selection**

Current limit is used to set the maximum delivered output current. In the typical application circuit, MAX1932 is designed to current limit at:

$$R1 = \frac{2V}{I_{LIMIT}}$$

Note that  $I_{LIMIT}$  must include current drawn by the feedback divider (if sensing feedback after R1) and the input current of CS-.

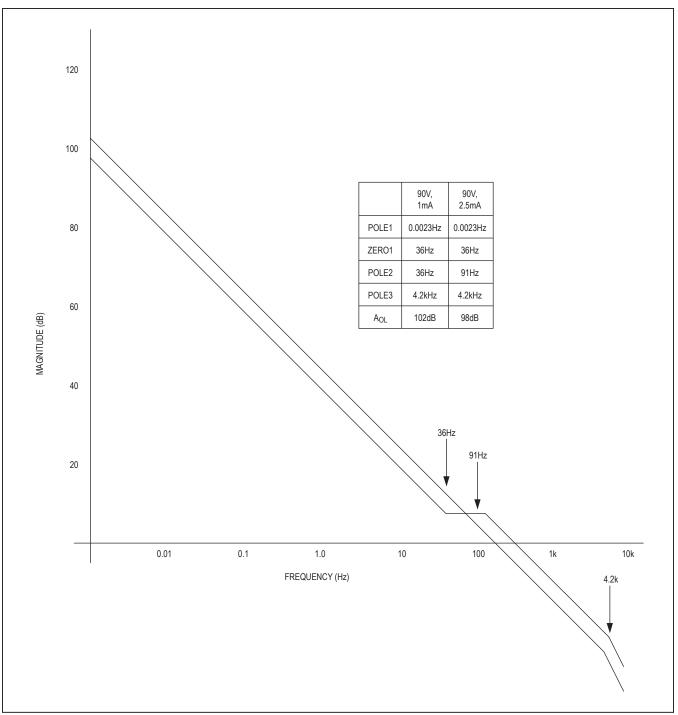

#### Stability and Compensation Component Selection

Compensation components, R7 and C4, introduce a pole and a zero necessary to stabilize the MAX1932 (see Figure 6). The dominant pole, POLE1, is formed by the output impedance of the error amplifier (R<sub>EA</sub>) and C4. The R7/C4 zero, ZERO1, is selected to cancel the pole formed by the output filter cap C3 and output load R<sub>LD</sub>, POLE2. The additional pole of R1/C3, POLE3, should be at least a decade past the crossover frequency to not affect stability:

POLE1 (dominant pole) =  $1 / (2\pi \times R_{EA} \times C4)$

ZERO1 (integrator zero) =  $1 / (2\pi \times R7 \times C4)$

POLE2 (output load pole) = K1 /  $(2\pi \times R_{LD} \times (C2 + C3))$

POLE3 (output filter pole) =  $1 / (2\pi \times R1 \times C3)$

## Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

The DC open-loop gain is given by:

$$A_{OL} = K2 \times Gm \times R_{EA}$$

where  $R_{EA} = 310M\Omega$ ,

$g_{M} = 110 \mu S$ ,

$R_{\mbox{\scriptsize LD}}$  is the parallel combination of feedback network and the load resistance.

$$K1 = \frac{2 \times V_{OUT} - V_{IN}}{V_{OUT} - V_{IN}}$$

$$K2 = \frac{V_{FB} (Volts)}{0.75 (Volts)} \times \frac{2 \times V_{IN}}{2 \times V_{OUT} - V_{IN}} \times \left( \sqrt{\left(\frac{V_{OUT}}{V_{OUT} - V_{IN}}\right) \frac{R_{LD} \times T(second)}{2 \times L(Henries)}} \right)$$

A properly compensated MAX1932 results in a gain vs. frequency plot that crosses 0dB with a single pole slope (20dB per decade). See Figure 6.

<u>Table 1</u> lists suggested component values for several typical applications.

#### **Further Noise Reduction**

The current-limit sense resistor is typically used as part of an output lowpass filter to reduce noise and ripple. For further reduction of noise, an LC filter can be added as shown in <u>Figure 7</u>. Output ripple and noise with and without the LC filter are shown in the <u>Typical Operating</u> <u>Characteristics</u>. If a post LC filter is used, it is best to use a coil with fairly large resistance (or a series resistor) so that ringing at the response peak of the LC filter is damped. For a 330µH and 1µF filter, 22Ω accomplishes this, but a resistor is not needed if the coil resistance is greater than 15Ω.

# Output Accuracy and Feedback Resistor Selection

The MAX1932 features 0.5% feedback accuracy. The total voltage accuracy of a complete APD bias circuit is the sum of the FB set-point accuracy, plus resistor ratio error and temperature coefficient. If absolute accuracy is critical, the best resistor choice is an integrated network with specified ratio tolerance and temperature coefficient. If using discrete resistors in high-accuracy applications, pay close attention to resistor tolerance and temperature coefficients.

# Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

| VIN, VOUT, IOUT(MAX)                               | INDUCTOR L1<br>(µH) | C <sub>SNS</sub><br>C2 (µF) | R <sub>SNS</sub><br>R1 (Ω) | С <sub>ОՍТ</sub><br>С3 (µF) | R <sub>COMP</sub><br>R7 (kΩ) | C <sub>COMP</sub><br>C4 (μF) |

|----------------------------------------------------|---------------------|-----------------------------|----------------------------|-----------------------------|------------------------------|------------------------------|

| 5V <sub>IN</sub> , 40-90V <sub>OUT</sub> at 2.5mA  | 100                 | 0.047                       | 806                        | 0.1                         | 20                           | 0.22                         |

| 5V <sub>IN</sub> , 20-60V <sub>OUT</sub> at 2.5mA  | 150                 | 0.10                        | 806                        | 0.047                       | 15                           | 0.22                         |

| 5V <sub>IN</sub> , 20-60V <sub>OUT</sub> at 5mA    | 82                  | 0.22                        | 392                        | 0.10                        | 10                           | 0.47                         |

| 3V <sub>IN</sub> , 40-90V <sub>OUT</sub> at 2.5mA  | 33                  | 0.047                       | 806                        | 0.1                         | 20                           | 0.22                         |

| 3V <sub>IN</sub> , 4.5-15V <sub>OUT</sub> at 2.5mA | 220                 | 0.47                        | 806                        | 0.01                        | 7.5                          | 0.47                         |

### Table 1. Compensation Components for Typical Circuits (Figure 2)

#### **Temperature Compensation**

APDs exhibit a change in gain as a function of temperature. This gain change can be compensated with an appropriate adjustment in bias voltage. For this reason it may be desirable to vary the MAX1932 output voltage as a function of temperature. This can be done in software by the system through the on-chip DAC, but can also be accomplished in hardware using an external thermistor or IC temperature sensor. <u>Figure 8</u> shows how an NTC thermistor can be connected to make the bias voltage increase with temperature.

#### PC Board Layout and Grounding

Careful PC board layout is important for minimizing ground bounce and noise. In addition, keep all connections to FB as a short as possible. In particular, locate feedback resistors (R5, R6, and R8) as close to FB as possible. Use wide, short traces to interconnect large current paths for N1, D1, L1, C1, C2. Do not share these connections with other signal paths. Refer to the MAX1932 EV kit for a PC board layout example.

Figure 1. Functional Diagram

Figure 2. Typical Operating Circuit

Figure 3. Taking Feedback Ahead of Output Filter

Figure 4. Serial Interface Timing Diagram

Figure 5. Detailed Serial Interface Timing Diagram

Figure 6. Loop Response

Figure 7. Adding a Post LC Filter

Figure 8. Adding an NTC Thermistor for Hardware Temperature Compensation; Output Voltage Increases with Temperature Rise

# Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

### **Chip Information**

TRANSISTOR COUNT: 1592 PROCESS: BICMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to **www.maximintegrated.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE        | LAND           |

|---------|---------|----------------|----------------|

| TYPE    | CODE    | NO.            | PATTERN NO.    |

| 12 TQFN | T1244-4 | <u>21-0139</u> | <u>90-0068</u> |

# Digitally Controlled, 0.5% Accurate, Safest APD Bias Supply

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                             | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------|------------------|

| 2                  | 5/15             | Updated Benefits and Features section                                                                   | 1                |

| 3                  | 10/19            | Corrected R5 equation per JIRA ticket MXDS-110.<br>Simplified V <sub>DACOUT</sub> equation for clarity. | 7                |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management Specialised - PMIC category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

LV5686PVC-XH FAN7710VN NCP391FCALT2G SLG7NT4081VTR SLG7NT4192VTR AP4313UKTR-G1 AS3729B-BWLM MB39C831QN-G-EFE2 LV56841PVD-XH AP4306BUKTR-G1 MIC5164YMM PT8A3252WE NCP392CSFCCT1G PT8A3284WE PI3VST01ZEEX PI5USB1458AZAEX PI5USB1468AZAEX MCP16502TAC-E/S8B MCP16502TAE-E/S8B MCP16502TAA-E/S8B MCP16502TAB-E/S8B TCKE712BNL,RF ISL91211AIKZT7AR5874 ISL91211BIKZT7AR5878 MCP16501TC-E/RMB ISL91212AIIZ-TR5770 ISL91212BIIZ-TR5775 CPX200D AX-3005D-3 TP-1303 TP-1305 TP-1603 TP-2305 TP-30102 TP-4503N MIC5167YML-TR LPTM21-1AFTG237C LR745N8-G MPS-3003L-3 MPS-3005D SPD-3606 STLUX383A TP-60052 ADN8834ACBZ-R7 LM26480SQ-AA/NOPB LM81BIMTX-3/NOPB LM81CIMT-3/NOPB MIC5166YML-TR GPE-4323 GPS-2303