**EVALUATION KIT AVAILABLE**

# Direct-Conversion to Low-IF Tuners for **Digital Audio Broadcast**

### **General Description**

The MAX2170/MAX2171 direct-conversion to low-IF tuners are designed for Digital Audio Broadcast (DAB) and Terrestrial Digital Multimedia Broadcast (T-DMB) applications, covering an input frequency range of 168MHz to 240MHz (VHF-III), 1452MHz to 1492MHz (L-Band), and also 87MHz to 108MHz (FM). The MAX2170/MAX2171 achieve a high level of component integration, allowing low-power, tuner-on-board designs. The direct-conversion to low-IF architecture eliminates the need for an IF-SAW filter while providing a balanced 2.048MHz center frequency baseband output to the demodulator.

The MAX2170 provides a buffered reference clock at the crystal frequency, while the MAX2171 outputs a reference at 1/3rd of the crystal frequency.

A sigma-delta fractional-N synthesizer is incorporated to optimize both close-in and wideband phase noise performances for OFDM applications where sensitivity to both 1kHz phase noise and wideband phase noise related to strong adjacents can be a problem.

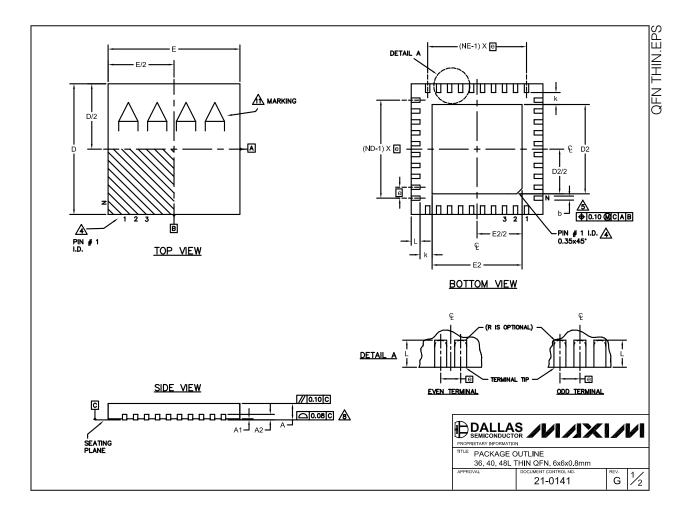

The MAX2170/MAX2171 are available in a 40-pin thin QFN package (6mm x 6mm) with an exposed paddle. Electrical performance is guaranteed over the extended -40°C to +85°C temperature range.

## **Applications**

Fixed and Mobile Digital Audio Broadcast (DAB)

Terrestrial Digital Multimedia Broadcast (T-DMB)

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-<br>PACKAGE                | PKG<br>CODE |

|-------------|----------------|--------------------------------|-------------|

| MAX2170ETL+ | -40°C to +85°C | 40 Thin QFN-EP*<br>(6mm x 6mm) | T4066+2     |

| MAX2171ETL+ | -40°C to +85°C | 40 Thin QFN-EP*<br>(6mm x 6mm) | T4066+2     |

<sup>+</sup>Denotes lead-free package.

#### Features

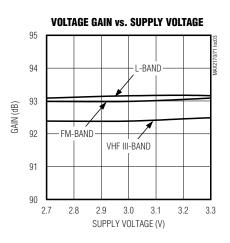

- ♦ +2.7V to +3.5V Supply Voltage Range

- ♦ Low-IF Output Eliminates IF-SAW Filter

- ♦ Integrated Low-IF Bandpass Filter

- **♦ Sigma-Delta Fractional-N Synthesizer**

- ♦ +45dB Digital ACPR

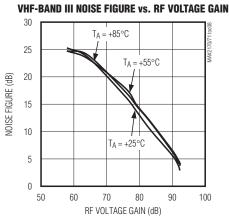

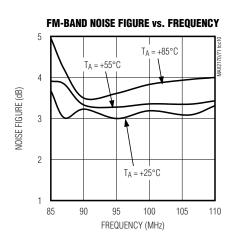

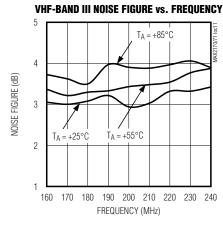

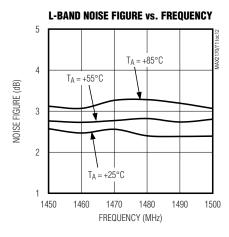

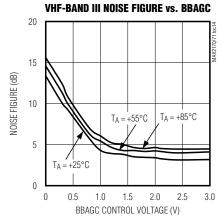

- ♦ 3.5dB Typical Noise Figure for VHF-III (Includes On-Chip Tracking Filter)

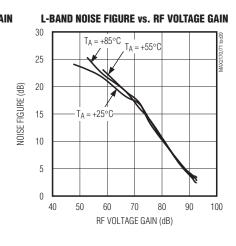

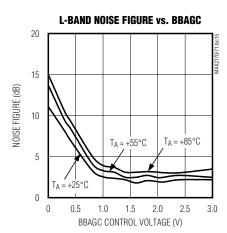

- ♦ 3.1dB Typical Noise Figure for L-Band

- ♦ VHF-III Sensitivity of -100dBm

- ♦ L-Band Sensitivity of -99dBm

- **♦ Baseband Overload Detector Controls RF AGC**

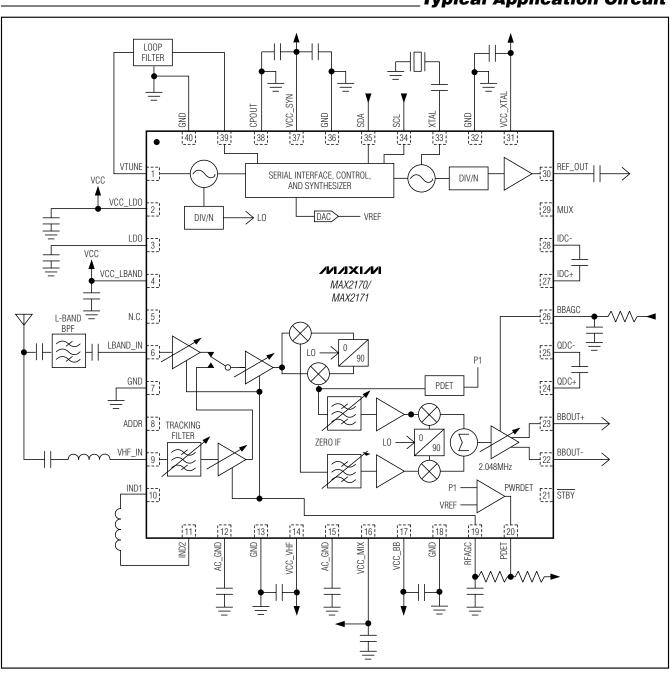

Typical Application Circuit appears at end of data sheet.

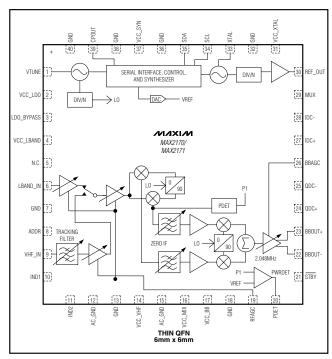

## Pin Configuration/ Functional Diagram

<sup>\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND                              | 0.3V to +3.6V        | Operating Temperature Range       | 40°C to +85°C |

|-----------------------------------------------------|----------------------|-----------------------------------|---------------|

| VHF_IN                                              | 0.3V to +1.9V        | Maximum Junction Temperature      | +150°C        |

| LBAND_IN, IND1, IND2                                | 0.3V to +0.9V        | θJA                               | +28°C/W       |

| Any Other Pins to GND0.3V                           | to $(V_{CC} + 0.3V)$ | θJC                               |               |

| BBOUT+, BBOUT- Short-Circuit Protection             | Indefinite           | Storage Temperature Range         |               |

| LBAND_IN, VHF_IN Input Power                        | +10dBm               | Lead Temperature (soldering, 10s) | +300°C        |

| Continuous Power Dissipation                        |                      |                                   |               |

| $(T_A = +70^{\circ}C)$ (derated 35.7mW/°C above +70 | )°C)2857mW           |                                   |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

CAUTION! ESD SENSITIVE DEVICE

### DC ELECTRICAL CHARACTERISTICS

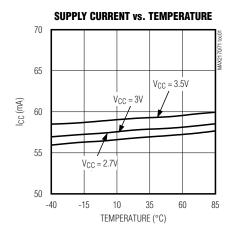

(MAX2170/MAX2171 Typical Application Circuit, VCC = +2.7V to +3.5V, GND = 0V, BBAGC = RFAGC = +2.4V, RF input terminated into  $50\Omega$ , BBOUT+ and BBOUT- are open, default register settings, no input signal, VCO locked to default channel, f<sub>REF</sub> = 24.576MHz, T<sub>A</sub> = -40°C to +85°C. Typical values are at V<sub>CC</sub> = +3.0V, T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                     | SYMBOL | CONDITIONS                                               | MIN                       | TYP  | MAX                      | UNITS |

|-----------------------------------------------|--------|----------------------------------------------------------|---------------------------|------|--------------------------|-------|

| SUPPLY VOLTAGE AND CURRE                      | NT     |                                                          |                           |      |                          | •     |

| Supply Voltage                                | Vcc    |                                                          | 2.7                       | 3.0  | 3.5                      | V     |

|                                               |        | Active mode, V <sub>CC</sub> = 3V                        |                           | 62   | 77                       | mA    |

| Supply Current                                | .      | Standby mode, STBY = 0V                                  |                           | 3    |                          | mA    |

| Supply Current                                | Icc    | Shutdown mode, STBY = 0V, SHDN_ALL bit set at logic-high |                           | 5    |                          | μA    |

| RFAGC AND BBAGC                               | •      |                                                          |                           |      |                          | •     |

| RFAGC Input Bias Current                      |        | At 0.4V and 2.4V                                         | -20                       |      | +10                      | μΑ    |

| BBAGC Input Bias Current                      |        | At 0.4V and 2.4V                                         | -20                       |      | +15                      | μΑ    |

| RF and Baseband AGC Control                   |        | Minimum attenuation                                      | 2.4                       |      |                          | V     |

| Voltage                                       |        | Maximum attenuation                                      |                           |      | 0.4                      | ] v   |

| SERIAL INTERFACE (SCL, SDA)                   |        |                                                          |                           |      |                          |       |

| Input Logic-Level Low                         |        |                                                          |                           |      | 0.3 x<br>V <sub>CC</sub> | V     |

| Input Logic-Level High                        |        |                                                          | 0.7 x<br>V <sub>C</sub> C |      |                          | ٧     |

| SDA, SCL Input Current                        |        |                                                          | -10                       |      | +10                      | μΑ    |

| Output Logic-Level Low                        |        | 3mA sink current                                         |                           |      | 0.4                      | V     |

| SYSTEM TIMING                                 | •      |                                                          |                           |      |                          |       |

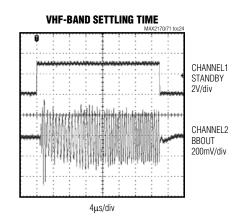

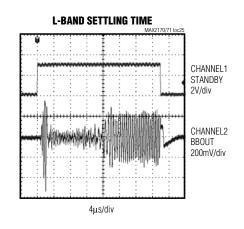

| Signal Path Settling Time                     |        | From standby mode to active, any band                    |                           | 0.02 |                          | ms    |

| Adjacent Channel Change                       |        | Any mode, including VCO tuning                           |                           | 0.5  |                          | ms    |

| Reference Oscillator<br>Turn-On Time to 50ppm |        | Using the MAX2170 EV kit                                 |                           | 0.6  |                          | ms    |

#### **AC ELECTRICAL CHARACTERISTICS**

(MAX2170/MAX2171 Typical Application Circuit,  $V_{CC}$  = 2.7V to 3.5V, GND = 0V. RFAGC = BBAGC = +2.4V, RF input terminated into 50 $\Omega$ , BBOUT+ and BBOUT- terminated into balanced 2k $\Omega$  II 10pF load, default register settings, VCO locked.  $T_A$  = -40°C to +85°C. Typical values are at  $V_{CC}$  = +3.0V,  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                    | SYMBOL | CONDITIONS                                                                                                      | MIN  | TYP   | MAX  | UNITS |  |

|----------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------|------|-------|------|-------|--|

|                                              |        | FM band gain specification met across this frequency band, BAND_SEL = "10"                                      | 87   |       | 108  |       |  |

| Operating Frequency Range                    |        | VHF-III band gain specification met across this frequency band, BAND_SEL = "00"                                 | 168  |       | 240  | MHz   |  |

|                                              |        | L-band gain specification met across this frequency band, BAND_SEL = "01"                                       | 1452 |       | 1492 |       |  |

| Input Power per Channel                      |        | All bands, output signal of at least 100mV <sub>P-P</sub> at minimum input level                                | -96  |       |      |       |  |

| Maximum Gain Mode<br>(LNA_BYP = 0)           |        | VHF-III and FM band, output signal not to exceed 1V <sub>P-P</sub> at maximum input level; RFAGC = BBAGC = 0.4V |      |       | -17  | dBm   |  |

| Overall Voltage Gain, Maximum                |        | All bands                                                                                                       | 80   |       |      | dB    |  |

| Gain Mode (LNA_BYP = 0)                      |        | RFAGC = BBAGC = 0.4V                                                                                            |      |       | 21   | a ab  |  |

| Input Power per Channel                      |        | All bands, output signal of at least 100mV <sub>P-P</sub> at minimum input level                                | -76  |       |      | dBm   |  |

| Low-Gain Mode (LNA_BYP = 1)                  |        | VHF-III and FM band, output signal not to exceed 1V <sub>P-P</sub> at maximum input level                       |      |       | 3    | ОБП   |  |

| Overall Voltage Gain,                        |        | All bands                                                                                                       | 60   |       |      | dB    |  |

| Low-Gain Mode (LNA_BYP = 1)                  |        | RFAGC = BBAGC = 0.4V                                                                                            |      |       | 1    | UD UD |  |

| RF Gain Flatness                             |        | Over selected input frequency band, RFAGC = 2.4V                                                                | -3   |       | +3   | dB    |  |

| Input Return Loss                            |        | Worst case across band selected (Note 1)                                                                        | 7    | 13    |      | dB    |  |

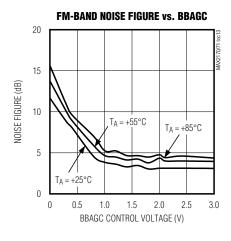

| Naisa Figura (DCD)                           |        | FM band, BAND_SEL = "10"                                                                                        |      | 3     |      |       |  |

| Noise Figure (DSB)<br>(LNA_BYP = 0) (Note 2) |        | VHF-III band, BAND SEL = "00"                                                                                   |      | 3.5   |      | dB    |  |

| (2.0.62)                                     |        | L-band, BAND_SEL = "01"                                                                                         |      | 3.1   |      |       |  |

| Noise Figure (DSB)                           |        | VHF-III band, BAND_SEL = "00"                                                                                   |      | 15.3  |      | dB    |  |

| $(LNA_BYP = 1)$                              |        | L-band, BAND_SEL = "01"                                                                                         | 12.8 |       | UD   |       |  |

| IIP2 (In-Band)                               |        | VHF_III, BAND_SEL = "00," LNA_BYP = 0                                                                           |      | 16.7  |      | ]     |  |

| (Note 3)                                     |        | RFAGC = 2.4V, BAND_SEL = "00,"<br>LNA_BYP = 1                                                                   |      | 27.8  |      | dBm   |  |

| IIP3 (In-Band)                               |        | All bands, LNA_BYP = 0                                                                                          |      | -19.8 |      | dBm   |  |

| (Note 4)                                     |        | VHF-III, BAND_SEL = "00," LNA_BYP = 1                                                                           |      | 1.7   |      | GDIII |  |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2170/MAX2171 Typical Application Circuit,  $V_{CC}$  = 2.7V to 3.5V, GND = 0V. RFAGC = BBAGC = +2.4V, RF input terminated into 50 $\Omega$ , BBOUT+ and BBOUT- terminated into balanced 2k $\Omega$  II 10pF load, default register settings, VCO locked.  $T_A$  = -40°C to +85°C. Typical values are at  $V_{CC}$  = +3.0V,  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                      | SYMBOL   | CONDITIONS                                                                                                                      | MIN    | TYP     | MAX  | UNITS    |  |

|------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------|--------|---------|------|----------|--|

| RF 1dB Desense                                 |          | PDESIRED = -90dBm and converted to f <sub>IF</sub> = (2.048 + fo) MHz, tone 10MHz higher; any input frequency band; LNA_BYP = 1 |        | -32.5   |      | - dBm    |  |

| (Note 2)                                       |          | PDESIRED = -75dBm and converted to (2.048 + fo) MHz, tone 10MHz higher; any input frequency band; LNA_BYP = 0                   |        | -11.5   |      | ubiii    |  |

| Adjacent Channel Protection                    |          | Adj. DAB (N ±1) (Note 5)                                                                                                        |        | > +45   |      | - dBc    |  |

| Ratio                                          |          | Adj. DAB (N ± 2) (Note 6)                                                                                                       |        | > +49   |      |          |  |

| Harmonic Rejection                             |          | FM, BAND_SEL = 01 and VHF-III,<br>BAND_SEL = "00" (N = 3 and 5) (Note 1)                                                        | 60     |         |      | dBc      |  |

| Beats within Output                            |          | Any input frequency, P <sub>IN</sub> = -78.75dBm (Note 2)                                                                       |        | < -22   |      | dBc      |  |

| Quadrature Accuracy                            |          | L-band                                                                                                                          |        | 46      |      | dB       |  |

|                                                |          | 50MHz to 470MHz                                                                                                                 |        |         | -20  |          |  |

| Spurious at the RF Input (Note 1)              |          | 470MHz to 878MHz                                                                                                                |        |         | -35  | dBmV     |  |

| (Note 1)                                       |          | 878MHz to 1732MHz                                                                                                               |        |         | -20  | 5        |  |

| Phase Noise                                    |          | At 1kHz (Note 1)                                                                                                                | -80    | -90     |      |          |  |

| (Single-Sideband, Closed Loop)                 |          | At 10kHz (Note 1)                                                                                                               | -80    | -90     |      | dBc/Hz   |  |

| L-Band, BAND_SEL = "01,"<br>1472MHz, ICP = "0" |          | At 100kHz                                                                                                                       |        | -105    |      |          |  |

| SIGMA-DELTA FRACTIONAL-N SY                    | NTHESIZE | R                                                                                                                               |        |         |      | <u> </u> |  |

| REFERENCE OSCILLATOR                           |          |                                                                                                                                 |        |         |      |          |  |

| Frequency                                      |          |                                                                                                                                 |        | 24.576  |      | MHz      |  |

| Load Capacitance                               |          | Present at XTAL to GND                                                                                                          |        | 18      |      | pF       |  |

| DIVIDERS                                       |          |                                                                                                                                 | •      |         |      | •        |  |

| N-Divider Ratio                                |          | To synthesizer                                                                                                                  | 35     |         | 251  |          |  |

| R-Divider Ratio                                |          | To synthesizer                                                                                                                  | 1      |         | 2    |          |  |

| Fractional-N Resolution                        |          | XTAL frequency / (220)                                                                                                          |        | 23.4375 |      | Hz       |  |

| LO PHASE DETECTOR AND CHAI                     | RGE PUMP |                                                                                                                                 |        |         |      | •        |  |

| fφ                                             |          | Phase-detector frequency                                                                                                        | 12.288 | 24.576  |      | MHz      |  |

| Charge Duran Current                           |          | ICP = "0"                                                                                                                       |        | 600     |      |          |  |

| Charge-Pump Current                            |          | ICP = "1"                                                                                                                       |        | 1200    |      | - μΑ     |  |

| Charge-Pump Tri-State Current                  |          |                                                                                                                                 | -10    |         | +10  | μA       |  |

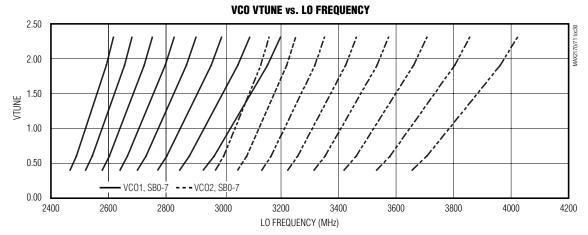

| LOCAL OSCILLATOR                               |          |                                                                                                                                 |        |         |      |          |  |

| Tune Range                                     |          | Tank frequency                                                                                                                  | 2688   |         | 3840 | MHz      |  |

| VCO Dividers                                   |          | Directly to LO buffers driving the mixer                                                                                        | 2      | 16      | 32   |          |  |

| VCO Tuning Gain                                |          | Tank oscillator gain, based on endpoint                                                                                         | 40     |         | 410  | MHz/V    |  |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2170/MAX2171 Typical Application Circuit,  $V_{CC} = 2.7V$  to 3.5V, GND = 0V. RFAGC = BBAGC = +2.4V, RF input terminated into 50 $\Omega$ , BBOUT+ and BBOUT- terminated into balanced 2k $\Omega$  II 10pF load, default register settings, VCO locked.  $T_A = -40^{\circ}$ C to +85°C. Typical values are at  $V_{CC} = +3.0V$ ,  $T_A = +25^{\circ}$ C, unless otherwise noted.)

| PARAMETER                              | SYMBOL     | CONDITIONS                                                                               | MIN  | TYP                  | MAX  | UNITS             |

|----------------------------------------|------------|------------------------------------------------------------------------------------------|------|----------------------|------|-------------------|

| LOW-IF STAGE                           | •          |                                                                                          | •    |                      |      | •                 |

| Nominal Output Voltage                 |            | Differential output load = $2k\Omega$ , differential output capacitance < $10pF$         |      | 1                    |      | V <sub>P-P</sub>  |

| 1dB Output Compression Point           |            | Differential voltage at f <sub>IF</sub> = 2.148MHz (Note 1)                              | 1.4  | 2.3                  |      | V <sub>P-P</sub>  |

| Output Impedance                       |            | Balanced                                                                                 |      | 27                   |      | Ω                 |

| Passband AGC Range                     |            | BBAGC = +2.4 to +0.4V                                                                    |      | 40                   |      | dB                |

| Passband Cutoff Attenuation            |            | $f_{\rm IF}$ = 2.048 ± 0.8MHz with nominal 3dB attenuation relative to 2.148MHz          | 1.3  | 3                    | 4.0  | dB                |

| Passband Flatness                      |            | $f_{IF} = 2.048 \pm 0.4 MHz$                                                             |      | 0.35                 |      | dB                |

|                                        |            | At -0.52MHz (RF tone at f <sub>C</sub> - 2.568MHz) (Note 1)                              | 50   | 57                   |      |                   |

| Rejection Ratio                        |            | At 4.616MHz (RF tone at f <sub>C</sub> + 2.568MHz) (Note 1)                              | 50   | 57                   |      | dB                |

|                                        |            | At > 21.7MHz                                                                             |      | 85                   |      |                   |

| DC Output Voltage                      |            | Common mode                                                                              |      | V <sub>CC</sub> / 2  |      | V <sub>DC</sub>   |

| AGC Gain Slope                         |            | BBAGC = $+0.4V$ to $+2.4V$                                                               | 14   |                      | 35   | dB/V              |

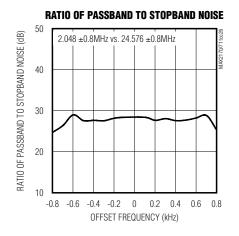

| Ratio of Passband to Stopband<br>Noise |            | BBAGC = $\pm 2.4$ V, $2.048 \pm 0.8$ MHz vs. $24.576 \pm 0.8$ MHz                        |      | 27                   |      | dB                |

| MIXER OVERLOAD DETECTOR (              | RSSI)      |                                                                                          | •    |                      |      | '                 |

| Attack-Point Accuracy                  |            | BAND_SEL = "00," f <sub>LO</sub> = 210MHz,<br>tone at 210.4MHz, P <sub>IN</sub> = -52dBm |      | ±1.5                 |      | dB                |

| Data atay Outaut Cial                  |            | Detector on, V <sub>OUT</sub> < 0.5V                                                     | 0.2  |                      |      | mA                |

| Detector Output Sink                   |            | Detector off, V <sub>OUT</sub> > 2.5V                                                    |      |                      | 5    | μΑ                |

| Detector Gain                          |            |                                                                                          |      | 36                   |      |                   |

| REFERENCE FREQUENCY OUT                | PUT BUFFEF | 7                                                                                        |      |                      |      |                   |

| Outrout Lavial                         |            | REFOUT_VPP = 0, load impedance of $10k\Omega$ and $10pF$                                 | 500  | 760                  | 1000 | ma\/              |

| Output Level                           |            | REFOUT_VPP = 1, load impedance of 10kΩ and 10pF                                          | 1500 |                      |      | mV <sub>P-P</sub> |

| DC Voltage                             |            |                                                                                          |      | 1.9                  |      | V                 |

| Puffor Output Froguesia                |            | MAX2170                                                                                  |      | F <sub>REF</sub>     |      |                   |

| Buffer Output Frequency                |            | MAX2171                                                                                  |      | F <sub>REF</sub> / 3 |      |                   |

| 2-WIRE INTERFACE                       |            |                                                                                          |      |                      |      |                   |

| Clock Rate                             |            |                                                                                          |      |                      | 400  | kHz               |

#### AC ELECTRICAL CHARACTERISTICS (continued)

(MAX2170/MAX2171 Typical Application Circuit,  $V_{CC}=2.7V$  to 3.5V, GND = 0V. RFAGC = BBAGC = +2.4V, RF input terminated into 50 $\Omega$ , BBOUT+ and BBOUT- terminated into balanced 2k $\Omega$  II 10pF load, default register settings, VCO locked. T<sub>A</sub> = -40°C to +85°C. Typical values are at  $V_{CC}=+3.0V$ , T<sub>A</sub> = +25°C, unless otherwise noted.)

- Note 1: Guaranteed by design characterization, not production tested.

- Note 2: BBAGC set at 1.4V and RFAGC set at 2.4V.

- Note 3: f<sub>LO</sub> at 177MHz. Desired tone at 177.1MHz at -70dBm with FM tones at 88.1MHz and 89.1MHz both at -35dBm. RFAGC = 1.4V for high-gain mode (LNA\_BYP = 0) and RFAGC = 2.4V for low-gain mode (LNA\_BYP = 1).

- **Note 4:** Two tones at  $(f_O 1.712)$  and  $(f_O 3.024)$  MHz. Measured at 2.448MHz.

- Note 5: Adjacent DAB channel with 1.712MHz channel spacing.

- Note 6: Second adjacent DAB channel.

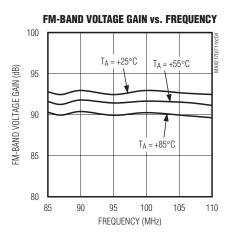

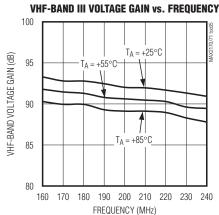

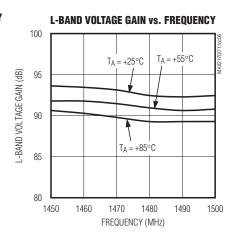

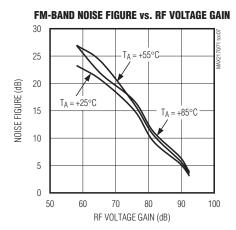

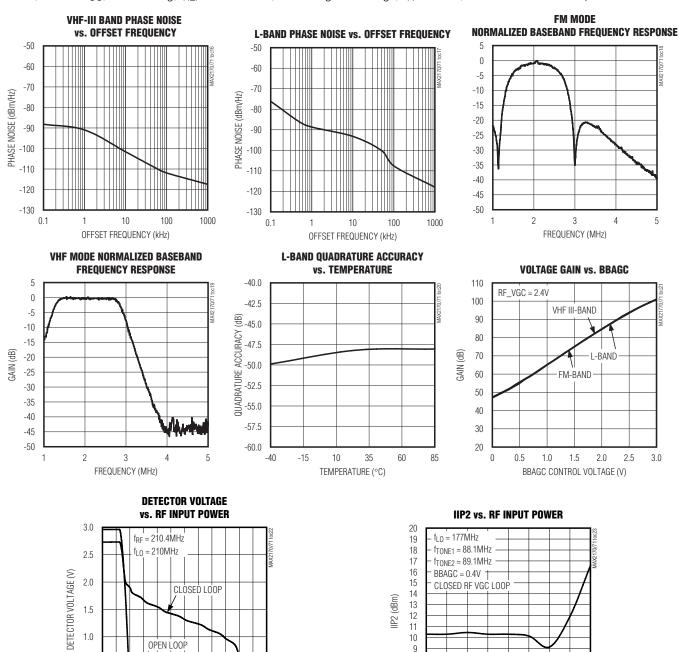

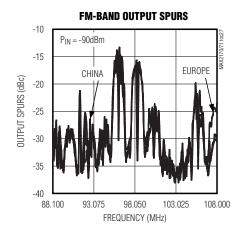

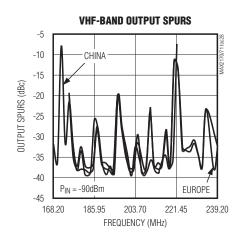

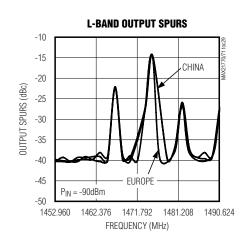

## Typical Operating Characteristics

## Typical Operating Characteristics (continued)

(MAX2170 EV kit,  $V_{CC}$  = +3.0V, FM = 108MHz, VHF band III = 239.2MHz, L-band = 1490.624MHz, IF = 2.148, RFAGC = BBAGC = 2.4V,  $\overline{STBY}$  =  $V_{CC}$ , VCO running, f<sub>REF</sub> = 24.576MHz, default register settings, T<sub>A</sub> = +25°C, unless otherwise noted.)

0.5

-60 -55 -50 -45 -40 -35 -30 -25 -20 -15 -10 -5 0

RF INPUT POWER (dBm)

# **Direct-Conversion to Low-IF Tuners for Digital Audio Broadcast**

## Typical Operating Characteristics (continued)

(MAX2170 EV kit,  $V_{CC}$  = +3.0V, FM = 108MHz, VHF band III = 239.2MHz, L-band = 1490.624MHz, IF = 2.148, RFAGC = BBAGC = 2.4V,  $\overline{STBY}$  =  $V_{CC}$ , VCO running,  $f_{REF}$  = 24.576MHz, default register settings,  $T_A$  = +25°C, unless otherwise noted.)

B \_\_\_\_\_\_ /VI/XI/M

8

-80

-75 -70

-65 -60 -55 -50

RF INPUT POWER (dBm)

## Typical Operating Characteristics (continued)

(MAX2170 EV kit,  $V_{CC}$  = +3.0V, FM = 108MHz, VHF band III = 239.2MHz, L-band = 1490.624MHz, IF = 2.148, RFAGC = BBAGC = 2.4V,  $\overline{STBY}$  =  $V_{CC}$ , VCO running, f<sub>REF</sub> = 24.576MHz, default register settings, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(MAX2170 EV kit,  $V_{CC} = +3.0V$ , FM = 108MHz, VHF band III = 239.2MHz, L-band = 1490.624MHz, IF = 2.148, RFAGC = BBAGC = 2.4V,  $\overline{STBY} = V_{CC}$ , VCO running, f<sub>REF</sub> = 24.576MHz, default register settings, T<sub>A</sub> = +25°C, unless otherwise noted.)

## **Pin Description**

| PIN                             | NAME       | FUNCTION                                                                                                                                                                              |

|---------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                               | VTUNE      | High-Impedance VCO Tune Input. Connect the PLL loop filter output directly to this pin with the shortest connection possible. Use pin 40 as the ground reference for the loop filter. |

| 2                               | VCC_LDO    | Internal LDO Supply. DC supply for the oscillator's internal regulator. Bypass to GND with a 1nF capacitor as close as possible to the pin.                                           |

| 3                               | LDO_BYPASS | VCO LDO Bypass. Connect 0.1µF capacitor as close as possible from this pin to GND.                                                                                                    |

| 4                               | VCC_LBAND  | DC Supply for the L-Band LNA. Connect a 100pF capacitor as close as possible from this pin to GND.                                                                                    |

| 5                               | N.C.       | No Connection. Do not connect to ground.                                                                                                                                              |

| 6                               | LBAND_IN   | RF Input for L-Band. Input to the L-Band LNA. AC-couple from the L-Band bandpass filter.                                                                                              |

| 7, 13, 18,<br>32, 36,<br>38, 40 | GND        | Ground                                                                                                                                                                                |

| 8                               | ADDR       | Address Line. Sets the device address. Connect to ground to set for device address $0xC0$ . Connect to $V_{CC}$ to set for device address $0xC2$ .                                    |

| 9                               | VHF_IN     | RF Input for VHF-III Band and FM Band. Input to the VHF-III and FM band tracking filter. AC-coupled.                                                                                  |

| 10                              | IND1       | Filter Inductor Pin 1                                                                                                                                                                 |

| 11                              | IND2       | Filter Inductor Pin 2                                                                                                                                                                 |

| 12, 15                          | AC_GND     | AC Ground. Connect a 1nF capacitor as close as possible to GND.                                                                                                                       |

| 14                              | VCC_VHF    | DC Supply for the VHF and FM LNA. Connect a 1nF capacitor as close as possible from this pin to GND.                                                                                  |

| 16                              | VCC_MIX    | DC Supply for the VHF and FM LNA. Connect a 1nF capacitor as close as possible from this pin to GND.                                                                                  |

| 17                              | VCC_BB     | DC Supply for Baseband. Connect a 100nF capacitor as close as possible from this pin to GND. Use pin 18 as the ground reference for VCC_BB pin's bypass capacitor.                    |

| 19                              | RFAGC      | Gain-Control Input for the RFVGA                                                                                                                                                      |

MIXIM

## Pin Description (continued)

| PIN | NAME     | FUNCTION                                                                                                                                                                                         |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | PDET     | Power-Detector Output. Provides a buffered and scaled output of the power detector's output voltage. Connect a $27k\Omega$ pullup resistor to $V_{CC}$ and a RC network to RFAGC.                |

| 21  | STBY     | Standby Enable. Set to logic "0" for standby mode. Set to logic "1" for normal operation.                                                                                                        |

| 22  | BBOUT-   | Inverted Baseband Output                                                                                                                                                                         |

| 23  | BBOUT+   | Noninverted Baseband Output                                                                                                                                                                      |

| 24  | QDC+     | Q-Channel DC Offset Bypass. Connect a 0.33µF capacitor as close as possible across pins 24                                                                                                       |

| 25  | QDC-     | and 25.                                                                                                                                                                                          |

| 26  | BBAGC    | Gain Control for Baseband VGA                                                                                                                                                                    |

| 27  | IDC+     | I-Channel DC Offset Bypass. Connect a 0.33µF capacitor as close as possible across pins 27                                                                                                       |

| 28  | IDC-     | and 28.                                                                                                                                                                                          |

| 29  | MUX      | Multiplex Output Line for Testing                                                                                                                                                                |

| 30  | REF_OUT  | Buffered Output of Reference Oscillator                                                                                                                                                          |

| 31  | VCC_XTAL | DC Supply for the Reference Oscillator. Connect a 100nF capacitor as close as possible from this pin to GND. Use pin 32 as the baseband ground reference for VCC_XTAL pin's bypass capacitor.    |

| 33  | XTAL     | Crystal-Oscillator Input. Connect to parallel resonant mode XTAL through a load-matching capacitor.                                                                                              |

| 34  | SCL      | Serial-Interface Clock Input Line. Requires a 2.7kΩ pullup resistor to V <sub>CC</sub> .                                                                                                         |

| 35  | SDA      | Serial-Interface Data Input Line. Requires a 2.7kΩ pullup resistor to V <sub>CC</sub> .                                                                                                          |

| 37  | VCC_SYN  | DC Supply for the Synthesizer and Serial Interface. Bypass to pins 36 and 38 grounds using 100nF capacitors. Make connections as short as possible. See the <i>Typical Application Circuit</i> . |

| 39  | CPOUT    | Output of Charge Pump. Connect the output to the PLL loop filter input with the shortest connection possible.                                                                                    |

| EP  | EP       | Exposed Paddle. Connect to GND with multiple vias for proper operation.                                                                                                                          |

## **Detailed Description**

The MAX2170/MAX2171 are direct-conversion to Zero-IF and an upconversion to Low-IF tuners targeting Digital Audio Broadcast (DAB) applications. These integrated tuners are designed to convert the 1452MHz to 1492MHz L-Band, the 168MHz to 240MHz VHF-III, and also the 87MHz to 108MHz FM frequencies to a centered 2.048MHz baseband frequency. This architecture eliminates the need for the SAW filter used in super-heterodyne architectures.

The MAX2170/MAX2171 integrated tuners include front-end tracking filters for VHF-III and FM band selection, low-noise VGA, direct-conversion mixers, I/Q channel filters, a mixer for upconversion to a low IF, and a VGA output driver. The devices also have a fully integrated fractional-N synthesizer for frequency generation, a power detector for automatic gain control, and DC offset-correction circuitry for the baseband signal.

The MAX2170 provides a buffered reference clock at the crystal frequency, while the MAX2171 outputs a reference at 1/3rd of the crystal frequency.

#### **Register Descriptions**

The MAX2170/MAX2171 include 13 user-programmable registers and 3 read-only registers. The register configuration of Table 1 shows each bit name and the bit usage information for all registers. "U" labeled under each bit name indicates that the bit value is user defined to meet specific application requirements. A "0" or "1" indicates that the bit must be set to the defined "0" or "1" value for proper operation. Operation is not tested or guaranteed if these bits are programmed to other values and is only for factory/bench evaluation. Note that all registers must be written after and no earlier than 100µs after device power-up.

Power-up defaults are provided for user convenience only and should not be relied on in the user's application. It is the responsibility of the user to supply all required register values when the device is first powered on.

**Table 1. Register Configuration**

| REGISTER  | DEGLOTED                      |     |                 | ı            | MSB           |             |              | LS            | В           |             |

|-----------|-------------------------------|-----|-----------------|--------------|---------------|-------------|--------------|---------------|-------------|-------------|

| ADDRESS   | REGISTER<br>NAME              | POR |                 |              |               | DATA        | BYTE         |               |             |             |

| ADDITIEGO | TVA2                          |     | D7              | D6           | D5            | D4          | D3           | D2            | D1          | D0          |

| 0x00      | N-DIVIDER<br>INTEGER          | H37 | N7<br>U         | N6<br>U      | N5<br>U       | N4<br>U     | N3<br>U      | N2<br>U       | N1<br>U     | N0<br>U     |

| 0x01      | CP CONTROL<br>AND FRAC2       | H05 |                 |              |               | CP_LIN<br>0 | F19<br>U     | F18<br>U      | F17<br>U    | F16<br>U    |

| 0x02      | FRAC1                         | H6A | F15<br>U        | F14<br>U     | F13<br>U      | F12<br>U    | F11<br>U     | F10<br>U      | F9<br>U     | F8<br>U     |

| 0x03      | FRAC0                         | HAB | F7<br>U         | F6<br>U      | F5<br>U       | F4<br>U     | F3<br>U      | F2<br>U       | F1<br>U     | F0<br>U     |

| 0x04      | TRACKING<br>FILTER            | HFF | <u> </u>        | <u> </u>     | TFC1<2>       | TFC1<1>     | TFC1<0>      | TFC2<2>       | TFC2<1>     | TFC2<0>     |

| 0x05      | PLL<br>CONFIG                 | H1E | RDIV<br>U       | ICP<br>0     | _<br>X        | X           | X            | X             | _<br>X      | X           |

| 0x06      | MODE<br>SELECT                | HE0 | FRAC_EN<br>1    | DUTY_EN<br>1 | _<br>1        | FSTCHG<br>U | LNA_BYP<br>U | SHDN_ALL<br>U | BAND_SEL<1> | BAND_SEL<0> |

| 0x07      | VCO<br>CONTROL                | H1C | _<br>X          | VCO_SB<3>    | VCO_SB<2>     | VCO_SB<1>   | VCO_SB<0>    | VAS_EN<br>1   | ADL<br>0    | ADE<br>0    |

| 0x08      | BASEBAND<br>CONTROL           | НЗС | PD_TH<2>        | PD_TH<1>     | PD_TH<0>      | FLBIAS<1>   | FLBIAS<0>    | BB_BW<2>      | BB_BW<1>    | BB_BW<0>    |

| 0x09      | VCO AND<br>MASTER<br>BIAS     | HE0 | REFOUT_VPP<br>U |              | VCO_BIAS<br>1 | BIAS<4>     | BIAS<3>      | BIAS<2>       | BIAS<1>     | BIAS<0>     |

| 0x0A      | ROM TABLE<br>ADDRESS          | H00 | _<br>0          | _<br>0       | _<br>0        | <u> </u>    | RTA<3>       | RTA<2>        | RTA<1>      | RTA<0>      |

| 0x0B      | ROM TABLE<br>DATA             | H00 | RTD<7>          | RTD<6>       | RTD<5>        | RTD<4>      | RTD<3>       | RTD<2>        | RTD<1>      | RTD<0>      |

| 0x0C      | TEST<br>FUNCTIONS             | H00 | CP_TST<2>       | CP_TST<1>    | CP_TST<0>     | LNA_BIAS<1> | LNA_BIAS<0>  | LD_MUX<2>     | LD_MUX<1>   | LD_MUX<0>   |

| 0x10      | ROM TABLE<br>DATA<br>READBACK | NA  | TFR<7>          | TFR<6>       | TFR<5>        | TFR<4>      | TFR<3>       | TFR<2>        | TFR<1>      | TFR<0>      |

| 0x11      | STATUS<br>READBACK            | NA  | POR             | VASA         | VASE          | _           | _            | _             | _           | PD_OVLD     |

| 0x12      | AUTOTUNER<br>READBACK         | NA  | _               | VCO_SBR<3>   | VCO_SBR<2>    | VCO_SBR<1>  | VCO_SBR<0>   | ADC<2>        | ADC<1>      | ADC<0>      |

Note: Power-up default is PLL tuned to 170MHz at 24.576MHz reference.

- U: User defined

- R: Read from ROM table

- 0: Set to "0" for factory-tested operation

- 1: Set to "1" for factory-tested operation

- X: Don't care

Table 2. RegisterAddress 0x00 N-Divider Integer

| BIT NAME | BIT LOCATION | FUNCTION                                                                                                                                                                |

|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N<7:0>   | 0            | Sets the integer portion of N-divider value. N-divider range can vary from 35 to 251. 00100011 = 35 (Minimum) 00110111 = (Default = 37h = 55d) 11111011 = 251 (Maximum) |

Table 3. Register Address 0x01 CP Control and FRAC2

| BIT NAME | BIT LOCATION | FUNCTION                                                                                                                                                                            |

|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F<19:16> | 3, 2, 1, 0   | Sets MSB of fractional divider value. Fractional divider value is F[19:0] / 1048576.  0000 = Minimum  0101 = Default = 5h  1111 = Maximum                                           |

| CP_LIN   | 4            | Sets charge-pump linearity 0 = Typically balanced CP source and sink currents, for FM and VHF-III operation (default) 1 = Typically +10% more CP sink current, for L-Band operation |

| _        | 7, 6, 5      | Unused bits                                                                                                                                                                         |

## Table 4. Register Address 0x02 FRAC1

| BIT NAME | BIT LOCATION           | FUNCTION                                                                                                                                                       |

|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F<15:8>  | 7, 6, 5, 4, 3, 2, 1, 0 | Sets middle portion of fractional divider value. Fractional divider value is F[19:0] / 1048576. 00000000 = Minimum 01101010 = Default = 6Ah 11111111 = Maximum |

## Table 5. Register Address 0x03 FRAC0

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                |

|----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| F<7:0>   | 7, 6, 5, 4, 3, 2, 1, 0    | Sets LSB of fractional divider value. Fractional divider value is F[19:0] / 1048576.  00000000 = Minimum  10101011 = Default = Abh  111111111 = Maximum |

## Table 6. Register Address 0x04 Tracking Filter

| BIT NAME  | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                   |

|-----------|---------------------------|------------------------------------------------------------------------------------------------------------|

| TFC2<2:0> | 2, 1, 0                   | Track Filter C2. Minimum weighting set for 000 and maximum weighting set for 111.  111 = Maximum (Default) |

| TFC1<2:0> | 5, 4, 3                   | Track Filter C1. Minimum weighting set for 000 and maximum weighting set for 111.  111 = Maximum (Default) |

| _         | 7, 6                      | Unused bits                                                                                                |

## Table 7. Register Address 0x05 PLL Configuration

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                 |

|----------|---------------------------|--------------------------------------------------------------------------|

| _        | 0, 1, 2, 3, 4, 5          | Unused bits                                                              |

| ICP      | 6                         | Charge-Pump Current<br>0 = 600μA typical (default)<br>1 = 1200μA typical |

| RDIV     | 7                         | PLL Reference Divider 0 = Divide by 1 (default) 1 = Divide by 2          |

## Table 8. Register Address 0x06 Mode Select

| BIT NAME      | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                |

|---------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAND_SEL<1:0> | 1, 0                      | Band Selection  00 = VHF band selected (default)  01 = L-Band selected  10 = FM band selected  11 = L-Band selected                                                                                                                     |

| SHDN_ALL      | 2                         | Shutdown Option when in Standby  0 = All circuitry shuts down except for the crystal oscillator and reference buffer when STBY is logic-low (default)  1 = All circuitry shuts down when STBY is logic-low                              |

| LNA_BYP       | 3                         | LNA Bypass Enable (Low LNA Gain) 0 = Disabled. Full LNA gain (default). 1 = Enabled. LNA turned off and bypassed.                                                                                                                       |

| FSTCHG        | 4                         | DC Correction Loop; Fast-Charge Enable 0 = Disabled. Highpass corner frequency is 100Hz and settling time is typically 10ms (default). 1 = Enabled. Highpass corner frequency is typically 800Hz and settling time is typically 1.25ms. |

| _             | 5                         | Unused                                                                                                                                                                                                                                  |

| DUTY_EN       | 6                         | Reference Buffer Output Duty-Cycle Correction Enable 0 = Disabled 1 = Enabled (default)                                                                                                                                                 |

| FRAC_EN       | 7                         | Fractional-N Synthesizer Enable 0 = Disabled. Integer-N mode. 1 = Enabled. Fractional-N mode (default).                                                                                                                                 |

Table 9. Register Address 0x07 VCO Control

| BIT NAME    | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                        |

|-------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADE         | 0                         | Enable VCO Autoselection (VAS) ADC (Sample VTUNE)  0 = Disabled (default)  1 = Enabled                                                                                          |

| ADL         | 1                         | Latch VCO Autoselection (VAS) ADC (Latch in VTUNE Value) 0 = Disabled (default) 1 = Enabled                                                                                     |

| VAS_EN      | 2                         | VCO Autoselection (VAS) Circuit 0 = Disabled. VCO selection must be programmed through I2C bus. 1 = Enabled. VCO selection controlled by autoselection circuit (VAS) (default). |

| VCO_SB<3:0> | 6, 5, 4, 3                | VCO Sub-Band Selection for 1 to 16 Bands 0000 = 1, lowest band 0001 = 2 0010 = 3 (default)                                                                                      |

| _           | 7                         | Unused                                                                                                                                                                          |

Table 10. Register Address 0x08 Baseband Control

| BIT NAME     | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BB_BW<2:0>   | 2, 1, 0                   | Baseband Lowpass Filter Bandwidth Setting  000 = Typically 0.75 x f <sub>C</sub> (f <sub>C</sub> is the -3dB corner frequency)  001 = Typically 0.8 x f <sub>C</sub> 010 = Typically 0.86 x f <sub>C</sub> 011 = Typically 0.92 x f <sub>C</sub> 100 = Nominal (f <sub>C</sub> ) (default)  101 = Typically 1.08 x f <sub>C</sub> 110 = Typically 1.19 x f <sub>C</sub> 111 = Typically 1.32 x f <sub>C</sub> |

| FL_BIAS<1:0> | 4, 3                      | Baseband Filter Bias Current  00 = Typically 50% of nominal  01 = Typically 66% of nominal  10 = Typically 75% of nominal  11 = Typically 100% (default)                                                                                                                                                                                                                                                      |

| PD_TH<2:0>   | 7, 6, 5                   | Power-Detector Threshold 000 = Minimum 001 010 011 100 101 110 111 = Maximum                                                                                                                                                                                                                                                                                                                                  |

## Table 11. Register Address 0x09 VCO and Master Bias

| BIT NAME      | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                   |

|---------------|---------------------------|--------------------------------------------------------------------------------------------|

| BIAS<br><2:0> | 4, 3, 2, 1, 0             | Master Bias Control 00000 = Nominal Current (default) 00001 11111                          |

| VCO_BIAS      | 5                         | VCO Bias Current Increase 0 = Typically +25% 1 = Nominal current (default)                 |

| _             | 6                         | Not used.                                                                                  |

| REFOUT_VPP    | 7                         | Reference Output Buffer (Pin 30) Voltage Swing $0 = 0.7V_{P-P}$ $1 = 1.5V_{P-P} (default)$ |

## Table 12. Register Address 0x0A ROM Table Address

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTA<3:0> | 3, 2, 1, 0                | ROM Table Register Address  0000 = Reg 0: Power Detector and Master Bias Trim (Default) 0001 = Reg 1: Tracking Filter Capacitor Weightings, VHF-III High-Frequency Setting 0010 = Reg 2: Tracking Filter Capacitor Weightings, FM Frequency Setting 0011 = Reg 3: Tracking Filter Capacitor Weightings, VHF-III Low-Frequency Setting 0100 = Reg 4: Baseband Lowpass Filter Bandwidth Setting 0101 = Reg 5: Unused 0110 = Reg 6: Unused 0111 = Reg 7: Read Only 1xxx = N/A |

| _        | 7, 6, 5, 4                | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

\_\_\_\_\_\_/N/XI/M

Table 13. Register Address 0x0C Test Mode

| BIT NAME      | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                                                                                                   |

|---------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LD_MUX<2:0>   | 2, 1, 0                   | MUX Output (N-Divider, R-Divider and Bias-Current Calibration)  000 = Normal Operation: Mux output logic-high (default)  001 = Monitor N-divider output, post divide by 2  010 = Monitor R-divider output  011 = Monitor test fractional vector output (factory use only)  1xx = Bias current-trim mode (factory use only) |

| LNA_BIAS<1:0> | 4, 3                      | LNA Bias Current Setting  OO = Nominal (Default)  O1 = -5% typical  10 = -10% typical  11 = -15% typical                                                                                                                                                                                                                   |

| CP_TST<2:0>   | 7, 6, 5                   | Charge-Pump Test Modes  000 = Normal operation (Default) 0xx = Normal operation 100 = Both source and sink currents enabled 101 = Source current enabled 110 = Sink current enabled 111 = High impedance (both source and sink currents disabled)                                                                          |

## Table 14. Register Address 0x10 ROM Table Data Readback

| BIT NAME | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                 |

|----------|---------------------------|----------------------------------------------------------|

| TFR<7:0> | 7, 6, 5, 4, 3, 2, 1, 0    | ROM Table Readback 00000000 = Minimum 11111111 = Maximum |

## Table 15. Register Address 0x11 Status

| BIT NAME       | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                           |

|----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD_OVLD        | 0                         | Power Detector over Load  0 = Below power-detector threshold  1 = Overload, above power-detector threshold                                                                                         |

| _              | 4, 3, 2, 1                | Unused                                                                                                                                                                                             |

| VASA :<br>VASE | 6, 5                      | VCO Autoselect (VAS) Status Bits  00 = Active and searching  01 = Unsuccessful acquisition  10 = Unused/don't care  11 = Successful acquisition                                                    |

| POR            | 7                         | Power-On Reset Status 0 = Chip-Status register has been read with stop condition since last power-on. 1 = Power-on reset (power cycle) has occurred. Default values have been loaded in registers. |

#### Table 16. VCO Autoselect (VAS) Read Register

| BIT NAME         | BIT LOCATION<br>(0 = LSB) | FUNCTION                                                                                                                                                                                                                                                 |

|------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC<2:0>         | 2, 1, 0                   | VAS ADC Output (VTUNE)  000 = VTUNE < 0.416V (unlocked)  001 = 0.416 VTUNE < 0.628V  010 = 0.628 VTUNE < 1.075V  101 = 1.075 VTUNE < 1.830V  110 = 1.830 VTUNE < VCC - 0.40V  111 = VTUNE > VCC - 0.40V (unlocked)  *ADC trip points are typical values. |

| VCO_SBR<br><3:0> | 6, 5, 4, 3                | VCO Sub-Band Readback (1 to 16 Bands)  0000 = 1, lowest band  0001 = 2  0001 = 3   1110 = 15  1111 = 16, highest band                                                                                                                                    |

|                  | 7                         | Not used                                                                                                                                                                                                                                                 |

#### Table 17. MAX2170/MAX2171 ROM Table

| REGISTER | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        | DESCRIPTION                                     |

|----------|----------|----------|----------|----------|----------|----------|----------|----------|-------------------------------------------------|

| 00       | PD_TH<2> | PD_TH<1> | PD_TH<0> | BIAS<4>  | BIAS<3>  | BIAS<2>  | BIAS<1>  | BIAS<0>  | Power Detector and Master Bias                  |

| 01       | Х        | Х        | TFC1H<2> | TFC1H<1> | TFC1H<0> | TFC2H<2> | TFC2H<1> | TFC2H<0> | VHF-III High-<br>Frequency<br>Capacitor Setting |

| 02       | X        | Х        | TFC1M<2> | TFC1M<1> | TFC1M<0> | TFC2M<2> | TFC2M<1> | TFC2M<0> | FM Frequency<br>Capacitor Setting               |

| 03       | Х        | Х        | TFC1L<2> | TFC1L<1> | TFC1L<0> | TFC2L<2> | TFC2L<1> | TFC2L<0> | VHF-III Low-<br>Frequency<br>Capacitor Setting  |

| 04       | Х        | Х        | Х        | Х        | Х        | BB_BW<2> | BB_BW<1> | BB_BW<0> | Baseband Filter<br>Bandwidth                    |

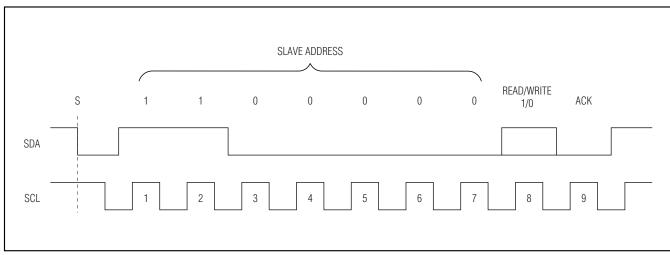

#### 2-Wire Serial Interface

The MAX2170/MAX2171 use a two-wire I<sup>2</sup>C-compatible serial interface consisting of a serial-data line (SDA) and a serial-clock line (SCL). SDA and SCL facilitate bidirectional communication between the device and the master at clock frequencies up to 400kHz. The master initiates a data transfer on the bus and generates the SCL signal to permit data transfer. The MAX2170/MAX2171 behave as an I<sup>2</sup>C slave device that transfers and receives data to and from the master. Pull

SDA and SCL high with external pullup resistors (1k $\Omega$  or greater) for proper I<sup>2</sup>C operation.

One bit is transferred during each SCL clock cycle. A minimum of nine clock cycles are required to transfer a byte in or out of the MAX2170/MAX2171 (8 bits and an ACK). The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high and stable are considered control signals (see the *START and STOP Conditions* section). Both SDA and SCL remain high when the bus is not busy.

18 \_\_\_\_\_\_ **//**| **//**| **//**|

Figure 1. Slave Address Byte with ADDR Pin Set at "0"

### **Table 18. Programmable Device Address**

| ADDR | READ/WRITE ADDRESS |

|------|--------------------|

| 0    | 0xC0               |

| 1    | 0xC2               |

#### START and STOP Conditions

The master initiates a transmission with a START condition (S), which is a high-to-low transition on SDA while SCL is high. The master terminates a transmission with a STOP condition (P), which is a low-to-high transition on SDA while SCL is high.

#### Acknowledge and Not-Acknowledge Conditions

Data transfers are framed with an acknowledge bit (ACK) or a not-acknowledge bit (NACK) after a byte is transferred in or out of the MAX2170/MAX2171. Both the master and the MAX2170/MAX2171 (slave) generate acknowledge bits. To generate an acknowledge, the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it low during the high period of the clock pulse.

To generate a not-acknowledge condition, the receiver allows SDA to be pulled high before the rising edge of the acknowledge-related clock pulse, and leaves SDA high during the high period of the clock pulse. Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer happens if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master must reattempt communication at a later time.

#### Slave Address

The MAX2170/MAX2171 continuously await a START condition followed by its slave address. The slave address is seven bits that must be sent to the device following a START condition to initiate communication. The slave address can be programmed to one of two possible addresses by the ADDR pin (Table 18). The eighth bit  $(R/\overline{W})$  following the 7-bit address determines whether a read or write operation occurs.

### Write Cycle

When addressed with a write command, the MAX2170/MAX2171 allow the master to write to a single register or to multiple successive registers.

A write cycle begins with the bus master issuing a START condition followed by the seven slave address bits and a write bit (LSB = "0"). The device issues an ACK if the slave address byte is successfully received. The bus master must then send the address of the first register it wishes to write to (see Table 1 for register addresses). The slave acknowledges the address, and the master can then write one byte of data to the register at the specified address. Data is written beginning with the most significant bit. The MAX2170/MAX2171 again issue an ACK if the data is successfully written to the register. The master can continue to write data to the successive internal registers with the device acknowledging each successful transfer, or the master can terminate transmission by issuing a STOP condition. The write cycle does not terminate until the master issues a STOP condition.

| START  | WRITE DEVICE<br>ADDRESS | R/W | ACK | WRITE REGISTER<br>ADDRESS | ACK | WRITE DATA TO<br>REGISTER 0x00 | ACK | WRITE DATA TO<br>REGISTER 0x01 | ACK | WRITE DATA TO<br>REGISTER 0x02 | ACK | STOP |

|--------|-------------------------|-----|-----|---------------------------|-----|--------------------------------|-----|--------------------------------|-----|--------------------------------|-----|------|

| On att | 110000[ADDR]            | 0   |     | 0x00                      |     | 0x0E                           |     | 0xD8                           |     | 0xE1                           |     | 0101 |

Figure 2. Example: Write registers 0 through 2 with 0x0E, 0xD8, and 0xE1, respectively.

| START | DEVICE<br>ADDRESS | R/W | V C K | REGISTER<br>ADDRESS | VCK | START | DEVICE<br>ADDRESS | R/W | ACK | REG 00<br>DATA | VCK | REG 01<br>DATA | V C K | REG 02<br>DATA | NACK  | STOP |

|-------|-------------------|-----|-------|---------------------|-----|-------|-------------------|-----|-----|----------------|-----|----------------|-------|----------------|-------|------|

| STANT | 11000[ADDR]       | 0   | AUN   | 00000000            | AUN | SIANI | 11000[ADDR]       | 1   | AUN | xxxxxxxx       | AUK | xxxxxxxx       | AUN   | XXXXXXXX       | IVACK | 3101 |

Figure 3. Example: Receive Data from Read Registers

Figure 2 shows an example in which registers 0 through 2 are written with 0x0E, 0xD8, and 0xE1, respectively.

#### Read Cycle

When addressed with a read command, the MAX2170/MAX2171 allow the master to read back a single register or multiple successive registers.

A read cycle begins with the bus master issuing a START condition followed by the seven slave address bits and a write bit (LSB = "0"). The MAX2170/ MAX2171 issue an ACK if the slave address byte is successfully received. The bus master must then send the address of the first register it wishes to read (see Table 1 for register addresses). The slave acknowledges the address. Then, a START condition is issued by the master, followed by the seven slave address bits and a read bit (LSB = "1"). The MAX2170/MAX2171 issue an ACK if the slave address byte is successfully received. The device starts sending data MSB first with each SCL clock cycle. At the 9th clock cycle, the master can issue an ACK, and continue to read successive registers, or the master can terminate the transmission by issuing a NACK. The read cycle does not terminate until the mastzer issues a STOP condition.

Figure 3 shows an example in which registers 0 through 2 are read back.

## Applications Information

#### **Band Selection and RF Input**

The MAX2170/MAX2171 are designed to be compatible for operation in the L-Band, VHF-III, and FM band. Band operation selection is selected by the bits BAND\_SEL<1:0> of the Mode Selection register. The L-Band option is possible using a LO at the VCO frequency divided by 2. An external bandpass filter is required at the L-Band RF input (LBAND\_IN) covering the 1452MHz to 1492MHz range for L-Band selection.

VHF-III and FM band operation use a divide by 16 and 32, respectively. An integrated tracking bandpass filter is provided to cover both the total tuning ranges of 168MHz to 240MHz for VHF-III and 87MHz to 108MHz for FM.

The MAX2170/MAX2171 VHF\_IN and LBAND\_IN inputs are internally matched to  $50\Omega$  and require a DC-blocking capacitor (for L-Band use a 33pF and for VHF-III/FM use a 1nF).

#### **RF Front-End Filters**

The MAX2170/MAX2171 integrate a narrowband RF tracking filter for the VHF and FM band. The filter response is determined by two external inductors and internal digitally controlled capacitors.

To set the filter's center frequency, the integrated RF tracking filter uses an external inductor between the IND1 and IND2 pins and another inductor in series with the VHF\_IN input. The inductor value must be 91nH±3% to achieve the targeted corner frequency response. The internal variable capacitors are factory calibrated to this particular inductor value. The value of the internal capacitors is set to compensate for process variation of each individual part and to receive the desired RF channel.

#### **Programming the Tracking Filter**

The tracking filter is a bandpass filter whose center frequency is user programmable through register 0x04, data bits D5–D0 (see Table 1). Note that bits D5–D3 are labeled TFC1<2,0>. These three bits set the value of tracking filter capacitor, C1. Bits D2–D0 are labeled TFC2<2,0>. These three bits set the value of tracking filter capacitor, C2.

For FM operation, the user should program bits D5–D0 of register 0x04 with bits 5–0 of ROM register 02. These ROM bits have been factory set to give the optimal filter setting for the entire FM band.

20 \_\_\_\_\_\_ /VI/XI/M

For VHF operation, the contents of ROM registers 01 and 03 have been factory set to optimize the tracking filter capacitors for 240MHz (VHF-III high-frequency capacitor setting) and 170MHz (VHF-III low-frequency capacitor setting), respectively. For frequencies between 170MHz and 240MHz, the user should linearly interpolate the ROM table values as described below:

# Interpolating tracking filter ROM table values for VHF-III frequencies:

- 1) Parse and convert ROM table values as follows:

- a. TFC1L = decimal equivalent of ROM register 03, bits 5–3.

- b. TTFC2L = decimal equivalent of ROM register 03, bits 2–0.

- c. TTFC1H = decimal equivalent of ROM register 01, bits 5–3.

- d. TTFC2H = decimal equivalent of ROM register 01, bits 2–0.

- 2) Interpolate the TFC1 and TFC2 decimal values using the formulas below:

- a. If Freq < 170MHz, then Freq = 170MHz</li>TFC1d = TFC1L round((Freq 170MHz) / 70MHz x (TFC1L TFC1H))

- b. TFC2d = TFC2L round((Freq 170MHz) / 70MHz x (TFC2L TFC2H))

- 3) Convert decimal values TFC1d and TFC2d to 3-bit binary bytes and program into register 0x04:

- a. D5-D3 of register 0x04 = TFC1b

- b. D2-D0 of register 0x04 = TFC2b

- 4) Example: The desired VHF-III frequency is 205MHz and ROM registers 01 and 03 are factory set to xx010000 and xx111110, respectively.

- a. TFC1H = 2d.

- b. TFC2H = 0d.

- c. TFC1L = 7d.

- d. TFC2L = 6d.

Now interpolating:

- a. TFC1d = 7 round(2.5) = 4.

- b. TFC2d = 6 round(3) = 3.

Thus, register 0x04 should be user programmed to xx100011 for the VHF-III frequency of 205MHz.

#### **Programming the Bias Registers**

The LNA and the RF mixer currents are referenced to a stable current calibrated in the factory. This information is stored in bits<4:0> of register 00 in the ROM table.

After power-up these five bits of data need to be loaded into bits<4:0> in register 09 to set the proper bias currents for the LNA and RF mixers.

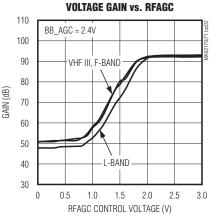

#### **Gain Control**

The MAX2170/MAX2171 feature an RFVGA and an IFVGA that can be used to achieve the optimum SNR. The RFVGA and IFVGA provide 40dB and 39dB of total gain range, respectively. The RFVGA can be programmed for either high-gain mode or low-gain mode. In low-gain mode, the RFVGA gain is reduced by 21dB. In typical application, the decision of which mode to use is determined during the initial channel selection and also by the power-detector information. For low-gain mode, set the LNA\_BYP bit to a logic "1" in the Mode Select register.

The RFVGA and the IFVGA circuits can be driven independently by the baseband controller. The RF gain control can also be configured for closed-loop automatic gain control when combined with the on-chip baseband power detector. See the Baseband Power Detector and Programming the Power-Detector Threshold section.

#### Baseband Power Detector and Programming the Power-Detector Threshold

The MAX2170/MAX2171 baseband power detector senses the differential baseband output power from the first gain stage of the baseband filter, and compares the sensed signal to the threshold value equivalent to the level produced by a -52dBm RF input signal. The power-detector threshold is factory calibrated to a typical input power of -52dBm. This information is stored in bits<7:5> of register 00 in the ROM table. After power-up, these three bits need to be loaded into bits<7:5> in register 08 to set the proper power-detector response.

Closed-loop RF automatic gain control can be implemented by connecting the current-sink power-detector output (PDET) to VCC with a 27k $\Omega$  pullup resistor. For closed-loop control, the resulting voltage at the power-detector output is fed to the RFAGC input by a RC network. See the *Typical Application Circuit* for details.

#### **Programming the Baseband Filters**