## Four-Channel 12-Bit Configurable Analog Output with Integrated Voltage Reference

### **General Description**

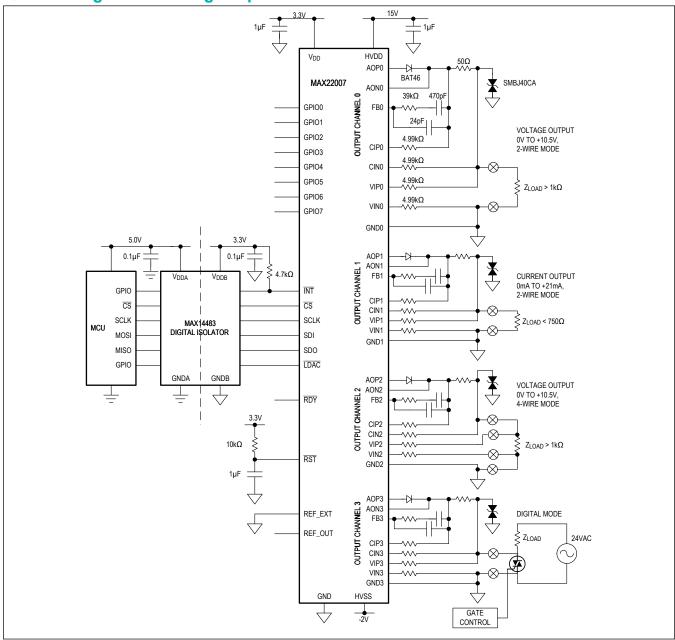

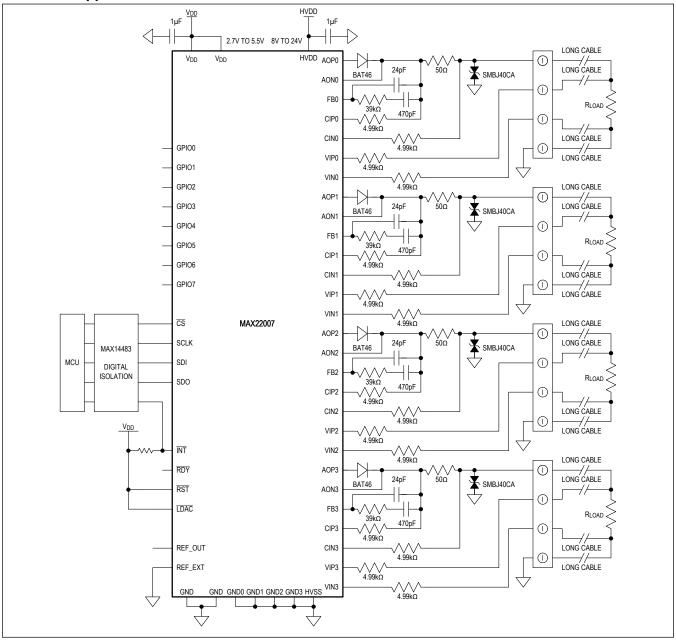

The MAX22007 is a software-configurable four-channel analog output device that drives a voltage or current output on each channel. All outputs are protected to  $\pm 42V_{P-P}$  for high-voltage supply of HVDD = 8V to 20V and HVSS = -2V to 0V.

Each output channel of the MAX22007 features a 12-bit DAC with fast settling time using a shared internal voltage reference. The device offers low-offset, high-voltage amplifiers to condition the signal from low-voltage DAC outputs to high-voltage or current outputs. If one output is miswired, all other outputs remain unaffected and function normally. For each channel, an internal comparator can be used to determine the load impedance and allows the microcontroller to intelligently select for voltage or current output mode. All outputs are kept safe by integrated current protection for functional and thermal robustness. The MAX22007 also includes a thermal shutdown circuit that protects the device when the junction temperature exceeds 165°C (typ).

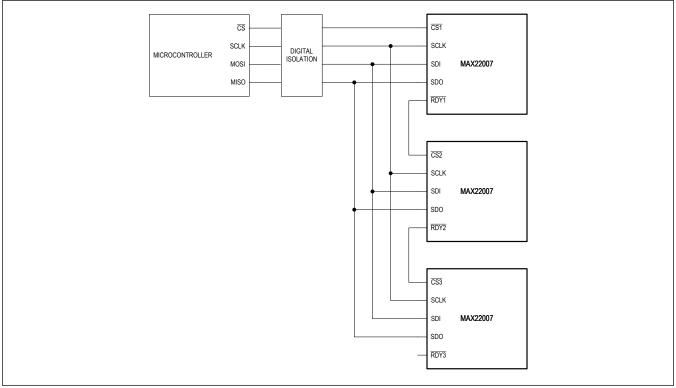

The MAX22007 communicates with a microcontroller using a SPI interface at clock rates up to 30MHz with an optional eight-bit CRC for improved data integrity. Eight GPIOs can be used to interface and control other resources in the application circuit. The MAX22007 operates from a 2.7V to 5.5V  $V_{\rm DD}$  low-voltage supply and an 8V to 24V HVDD positive high-voltage supply. The negative voltage supply HVSS can be set between -2V and 0V.

The MAX22007 is available in an 8mm x 8mm 56-pin TQFN package and operates over the -40°C to +85°C temperature range with 2.5kV HBM ESD protection on all pins.

### **Applications**

- Building Automation Analog Outputs

- Configurable Analog Output Cards

- Factory Automation Analog Outputs

- Process Automation

- Programmable Logic Controllers

### **Benefits and Features**

- Configurable Outputs

- · Each Output Individually Configurable

- Internal Comparator to Allow Calculating Load Impedance for Voltage-Mode or Current-Mode

- Voltage Mode is 0V to 10.5V Linear Range with 12.5V Overrange for Loads from 1kΩ to 1MΩ

- Current Mode is 0mA to 21mA Linear Range with 25mA Overrange for Loads from  $0\Omega$  to  $750\Omega$

- System Accuracy

- V/I Output Resolution is 12-Bits

- Factory Calibrated for Gain and Offset Error within ± 0.2% at +25°C

- V/I Total Unadjusted Error Less Than ± 1% from -40°C to +85°C

- · Robust with Integrated Diagnostics

- ±42V<sub>P-P</sub> Protection for Output Drivers

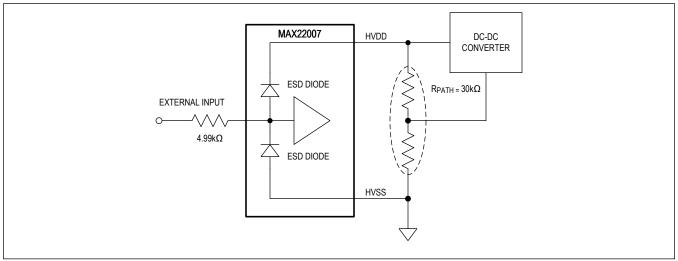

- ±1kV Surge Protection with 4.99kΩ Series Resistors at Input Pins

- ±2.5kV HBM ESD Protection on All Pins

- Outputs have Short-Circuit and Overvoltage Protection with External Diodes

- · Thermal Monitoring and Shutdown Protection

- Simple and Low-Cost Interface

- Up to 30MHz SPI Serial Interface with Optional 8-Bit CRC

- Daisy-Chain Mode to Reduce System Cost

- V<sub>DD</sub> = 2.7V to 5.5V for Easy Interface to the Microcontroller

- · High Voltage Output Supplies:

- HVDD: +8V to +24V

- HVSS: -2V to 0V

- Robust Performance in a Compact Package

- -40°C to 85°C Operating Temperature Range

- 56-pin TQFN, 8mm x 8mm

<u>Ordering Information</u> and <u>Typical Application Circuits</u> appear at the end of the datasheet.

## **Quad Configurable Analog Output**

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND0.3V to +6V                         | <u>AON_ to</u> HVSS70V to +70V                                  |

|-----------------------------------------------------------|-----------------------------------------------------------------|

| V <sub>DD</sub> to HVSS0.3V to +6V                        | INT, CS, SCLK, SDI to GND0.3V to +6V                            |

| GND_ to GND0.3V to +0.3V                                  | All Other Pins to GND0.3V to min(+6V, (V <sub>DD</sub> + 0.3V)) |

| HVDD to HVSS0.3V to +40V                                  | Maximum Current into AOP_, AON±100mA                            |

| HVDD to AON70V to +70V                                    | Maximum Current into Any Other Pin±50mA                         |

| HVDD to GND0.3V to +40V                                   | Continuous Power Dissipation (T <sub>A</sub> = +70°C)           |

| HVDD to GND0.3V to +40V                                   | 56-TQFN (derate 47.6mW/°C above +70°C)3809.5mW                  |

| GND to HVSS0.3V to +6V                                    | Operating Temperature Range40°C to +85°C                        |

| GND_ to HVSS0.3V to +6V                                   | Junction Temperature+150°C                                      |

| AOP to HVDD70V to +0.3V                                   | Storage Temperature Range65°C to +150°C                         |

| FB_, CIP_, CIN_, VIP_, VIN_ to HVSS0.3V to min(+40V,      | Lead Temperature (soldering, 10s)+300°C                         |

| ((V <sub>HVDD</sub> - V <sub>HVSS</sub> ) + 0.3V))        | Soldering Temperature (reflow)+260°C                            |

| CIP_, CIN_, VIP_, VIN_ to HVSS (with $4.99k\Omega$ series | ,                                                               |

| resistors)42V to +42V                                     |                                                                 |

|                                                           |                                                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

### **56-PIN TQFN**

| Package Code                           | T5688+4C       |  |  |  |

|----------------------------------------|----------------|--|--|--|

| Outline Number                         | <u>21-0135</u> |  |  |  |

| Land Pattern Number                    | 90-0047        |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 21°C/W         |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 1°C/W          |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{DD} = 3.3V, V_{HVDD} = +15V, V_{HVSS} = 0V, Internal Reference, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ ) (Note 1)

| PARAMETER            | SYMBOL           | L CONDITIONS                                                                                   |      | TYP       | MAX  | UNITS |

|----------------------|------------------|------------------------------------------------------------------------------------------------|------|-----------|------|-------|

| ANALOG OUTPUT-VOLT   | TAGE MODE        |                                                                                                |      |           |      |       |

|                      |                  | DAC full-scale range (Note 2)                                                                  |      | 0 to 12.5 |      |       |

| Output-Voltage Range | V <sub>OUT</sub> | Linear range, V <sub>HVSS</sub> = 0V (Notes 2, 3)                                              | 0.3  |           | 10.5 | V     |

|                      |                  | Linear Range, V <sub>HVSS</sub> = -2V (Notes 2, 3)                                             | 0.02 |           | 10.5 |       |

| Dropout Voltage      |                  | V <sub>OUT</sub> = 12.5V, sourcing 25mA, measured between HVDD and AOP_, gain compression < 1% |      |           | 1.0  | V     |

| Output-Current       |                  | Output shorted to HVDD or HVSS, threshold current (Note 4)                                     |      | 50        |      | mA.   |

| Protection           |                  | Output shorted to HVDD or HVSS, average current (Note 4)                                       | 7    |           |      | IIIA  |

## **Electrical Characteristics (continued)**

$(V_{DD}$  = 3.3V,  $V_{HVDD}$  = +15V,  $V_{HVSS}$  = 0V, Internal Reference,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C) (Note 1)

| PARAMETER                                           | SYMBOL           | CONDITIONS                                                                                                                                                                                                                                   | MIN                     | TYP     | MAX  | UNITS             |

|-----------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|------|-------------------|

| AOP_ and AON_ High-<br>Impedance Leakage<br>Current |                  | V <sub>OUT</sub> = 0V to +10.5V                                                                                                                                                                                                              |                         | ±25     |      | μΑ                |

| Offset Error                                        | V <sub>OFF</sub> | T <sub>A</sub> = +25°C, no load, extrapolated from the linear range (Note 5)                                                                                                                                                                 |                         |         | ±10  | mV                |

| Offset Drift                                        |                  | T <sub>A</sub> = -40°C to 85°C (Note 6)                                                                                                                                                                                                      |                         | ±10     |      | μV/°C             |

| Gain Error                                          |                  | T <sub>A</sub> = +25°C, no load (Note 5)                                                                                                                                                                                                     |                         |         | ±0.2 | %                 |

| Gain Drift                                          |                  | T <sub>A</sub> = -40°C to 85°C (Note 6)                                                                                                                                                                                                      |                         | ±10     |      | ppm/°C            |

| INL Error                                           | INL              | T <sub>A</sub> = +25°C, no load (Note 5)                                                                                                                                                                                                     | -1                      | ±0.5    | +1   | LSB               |

| INL Drift                                           |                  | T <sub>A</sub> = -40°C to 85°C (Note 6)                                                                                                                                                                                                      |                         | ±1      |      | μV/°C             |

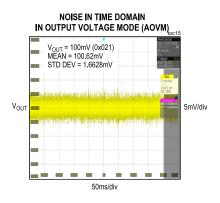

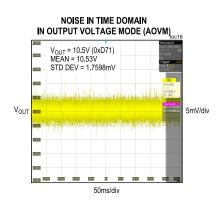

| Output Noise                                        | V <sub>n</sub>   | 10kHz BW                                                                                                                                                                                                                                     |                         | 100     |      | μV <sub>RMS</sub> |

| Voltage Output Total<br>Unadjusted Error            | V <sub>TUE</sub> | V <sub>OUT</sub> = 0.02V to 10.5V, no load (Notes 5, 7)                                                                                                                                                                                      |                         |         | ±100 | mV                |

| Voltage Crosstalk                                   | V <sub>CT</sub>  | Channel under test is in voltage mode with $V_{OUT}$ = 10.5V, $I_{OUT}$ = 10mA. All other channels are in current mode forcing 0mA and 20mA to a 0 $\Omega$ load. The crosstalk is the voltage variation of the channel under test. (Note 6) | 25                      |         | 25   | mV                |

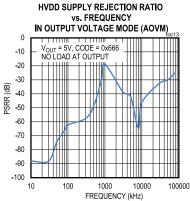

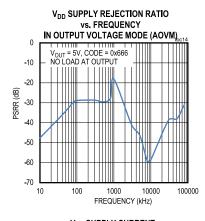

| Supply Rejection Ratio                              | PSRR             | DC, V <sub>OUT</sub> = 300mV, V <sub>HVDD</sub> = +8V to +24V                                                                                                                                                                                | 100                     |         |      | dB                |

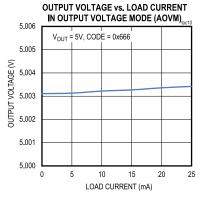

| Load Regulation                                     |                  | 0 ≤ I <sub>LOAD</sub> ≤ +10.5mA, measured at V <sub>OUT</sub> = +10.5V, output change due to selfheating excluded                                                                                                                            | ±0.1                    |         | mV   |                   |

| VIP_ and VIN_ Input-<br>Voltage Range               |                  | (Note 3)                                                                                                                                                                                                                                     | V <sub>HVDD</sub> - 2.5 |         |      | V                 |

| VIP_ and VIN_ Input<br>Current                      |                  | V <sub>VIP</sub> _, V <sub>VIN</sub> _ = 20mV to 10.5V                                                                                                                                                                                       |                         | ±2      |      | μA                |

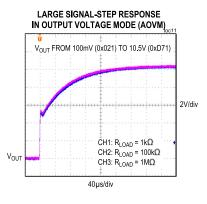

| Settling Time                                       |                  | Resistive load from 1k $\Omega$ to 10M $\Omega$ ; settling to 1% of step size for V <sub>OUT</sub> = 20mV to 10.5V                                                                                                                           |                         | 0.3     |      | ms                |

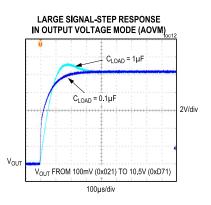

| -                                                   |                  | Capacitive load up to 1µF; settling to 1% of step size for V <sub>OUT</sub> = 20mV to 10.5V                                                                                                                                                  |                         | 1       |      |                   |

| ANALOG OUTPUT-CUR                                   | RENT MODE        |                                                                                                                                                                                                                                              |                         |         |      |                   |

|                                                     |                  | R <sub>SENSE</sub> = 50Ω, DAC full-scale range (Note 8)                                                                                                                                                                                      |                         | 0 to 25 |      |                   |

| Output-Current Range                                | lout             | Linear range, V <sub>HVSS</sub> = 0V (Notes 3, 8)                                                                                                                                                                                            | 1.5                     |         | 21   | mA                |

|                                                     |                  | Linear range, V <sub>HVSS</sub> = -2V (Notes 3, 8)                                                                                                                                                                                           | 0.04                    |         | 21   |                   |

| Dropout Voltage                                     |                  | V <sub>HVDD</sub> = 12V, Sourcing 25mA, measured between HVDD and AOP_, gain compression < 1%                                                                                                                                                |                         |         | V    |                   |

| Offset Error                                        | I <sub>OFF</sub> | $T_A$ = +25°C, $R_{LOAD}$ = 250Ω, extrapolated from the linear range (Note 5)                                                                                                                                                                |                         |         | ±20  | μΑ                |

|                                                     |                  |                                                                                                                                                                                                                                              |                         |         |      |                   |

## **Electrical Characteristics (continued)**

$(V_{DD}$  = 3.3V,  $V_{HVDD}$  = +15V,  $V_{HVSS}$  = 0V, Internal Reference,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C) (Note 1)

| PARAMETER                                       | SYMBOL               | CONDITIONS                                                                                                                                                                                                                                 | MIN             | TYP  | MAX                        | UNITS             |

|-------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|----------------------------|-------------------|

| Offset Drift                                    |                      | T <sub>A</sub> = -40°C to 85°C (Note 6)                                                                                                                                                                                                    |                 | ±20  |                            | nA/°C             |

| Gain Error                                      |                      | $T_A = +25^{\circ}C, R_{LOAD} = 250\Omega \text{ (Note 5)}$                                                                                                                                                                                |                 |      | ±0.2                       | %                 |

| Gain Drift                                      |                      | T <sub>A</sub> = -40°C to 85°C (Note 6)                                                                                                                                                                                                    |                 | ±10  |                            | ppm/°C            |

| INL Error                                       | INL                  | $TA = +25$ °C, $R_{LOAD} = 250Ω$ (Note 5)                                                                                                                                                                                                  | -1              | +0.5 | +1                         | LSB               |

| INL Drift                                       |                      | T <sub>A</sub> = -40°C to 85°C (Note 6)                                                                                                                                                                                                    |                 | ±5   |                            | nA/°C             |

| Output Noise                                    | In                   | 10kHz BW                                                                                                                                                                                                                                   |                 | 0.5  |                            | μA <sub>RMS</sub> |

| Current Output Total<br>Unadjusted Error        | ITUE                 | $I_{OUT}$ = 40μA to 21mA, $R_{LOAD}$ = 250Ω (Notes 5, 9)                                                                                                                                                                                   | 1 +/111         |      | ±200                       | μΑ                |

| Current Crosstalk                               | Іст                  | Channel under test is in current mode with $I_{OUT}$ = 21mA, $V_{OUT}$ = 10V. All other channels are in current mode forcing 0mA and 20mA to a 0 $\Omega$ load. The crosstalk is the current variation of the channel under test. (Note 6) |                 | 50   | μА                         |                   |

| Supply Rejection                                | PSR                  | DC, I <sub>OUT</sub> = 3mA, V <sub>HVDD</sub> = +8V to +24V                                                                                                                                                                                |                 | 0.1  |                            | μA/V              |

| CIP_ and CIN_ Input-<br>Voltage Range           |                      | (Note 3)                                                                                                                                                                                                                                   |                 |      | V <sub>HVDD</sub> -<br>2.5 | V                 |

| CIP_ and CIN_ Input<br>Current                  |                      | V <sub>CIP</sub> _, V <sub>CIN</sub> _ = 0V to +12V                                                                                                                                                                                        |                 | ±2   |                            | μΑ                |

| Common-Mode<br>Rejection                        | CMR                  | Current mode, V <sub>CIN</sub> _ = 0V to +11V, measured at I <sub>OUT</sub> = 1.5mA                                                                                                                                                        | / to +11V,<br>A |      | 10                         | μA/V              |

| CIP_ to CIN_<br>Differential-Input Range        |                      |                                                                                                                                                                                                                                            |                 | 1.25 |                            | V                 |

| CIP_ to CIN_<br>Differential-Input<br>Impedance |                      |                                                                                                                                                                                                                                            |                 | 100  |                            | kΩ                |

|                                                 |                      | Resistive load up to 250Ω; settling to 1% of step size for I <sub>OUT</sub> = 40μA to 21mA                                                                                                                                                 |                 | 0.5  |                            |                   |

| Settling Time                                   |                      | Resistive load up to 500Ω; settling to 1% of step size for I <sub>OUT</sub> = 40μA to 21mA                                                                                                                                                 |                 | 1.0  |                            | ms                |

|                                                 |                      | Inductive load up to 1mH; settling to 1% of step size for I <sub>OUT</sub> = 40µA to 21mA                                                                                                                                                  |                 | 0.5  |                            |                   |

| COMPARATOR                                      |                      |                                                                                                                                                                                                                                            |                 |      |                            |                   |

| Offset                                          | V <sub>OFF</sub>     |                                                                                                                                                                                                                                            |                 | ±50  |                            | mV                |

| Delay                                           | t <sub>DELAY</sub>   | 64                                                                                                                                                                                                                                         |                 |      | μs                         |                   |

| Nominal Trip Voltage                            | V <sub>TH</sub>      |                                                                                                                                                                                                                                            |                 | 500  |                            | mV                |

| REFERENCE                                       |                      |                                                                                                                                                                                                                                            |                 |      |                            |                   |

| REF_OUT Output<br>Voltage                       | V <sub>REF_OUT</sub> | T <sub>A</sub> = +25°C                                                                                                                                                                                                                     | 2.494           | 2.5  | 2.506                      | V                 |

| Output-Voltage<br>Temperature Coefficient       |                      | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C (Note 6)}$                                                                                                                                                                               |                 | ±10  | ±25                        | ppm/°C            |

## **Electrical Characteristics (continued)**

$(V_{DD}$  = 3.3V,  $V_{HVDD}$  = +15V,  $V_{HVSS}$  = 0V, Internal Reference,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C) (Note 1)

| PARAMETER                                                  | SYMBOL            | CONDITIONS                                               | MIN                      | TYP | MAX                      | UNITS |

|------------------------------------------------------------|-------------------|----------------------------------------------------------|--------------------------|-----|--------------------------|-------|

| DIGITAL INPUTS                                             |                   |                                                          |                          |     |                          |       |

| Input Logic-Low Voltage                                    | V <sub>IL</sub>   |                                                          |                          |     | 0.3 ×<br>V <sub>DD</sub> | V     |

| Input Logic-High Voltage                                   | $V_{IH}$          |                                                          | 0.7 ×<br>V <sub>DD</sub> |     |                          | V     |

| Input Hysteresis                                           | V <sub>HYS</sub>  |                                                          |                          | 300 |                          | mV    |

| Input Leakage Current                                      | I <sub>IN</sub>   |                                                          | -1                       |     | +1                       | μA    |

| Input Capacitance                                          | C <sub>IN</sub>   |                                                          |                          | 10  |                          | pF    |

| DIGITAL OUTPUTS                                            |                   |                                                          |                          |     |                          |       |

| Output Logic-Low<br>Voltage                                | $V_{OL}$          | I <sub>OL</sub> = 4mA, sinking                           |                          |     | 0.4                      | V     |

| Output Logic-High<br>Voltage (SDO, RDY,<br>GPIO7 to GPIO0) | V <sub>OH</sub>   | I <sub>OH</sub> = 4mA, sourcing                          | 0.9 ×<br>V <sub>DD</sub> |     |                          | V     |

| Three-State Leakage<br>Current                             |                   |                                                          | -10                      |     | +10                      | μΑ    |

| Three-State Output<br>Capacitance                          |                   |                                                          |                          | 10  |                          | pF    |

| SPI TIMEOUT                                                |                   |                                                          | <u>'</u>                 |     |                          |       |

| Timeout Interval<br>Accuracy                               |                   | With respect to nominal value                            | -50                      |     | +50                      | %     |

| SUPPLIES                                                   |                   |                                                          |                          |     |                          |       |

| Analog Supply Voltage                                      | $V_{DD}$          |                                                          | 2.7                      | 3.3 | V <sub>HVSS</sub> + 5.5  | V     |

| Positive High-Voltage                                      | V <sub>HVDD</sub> |                                                          | 8                        |     | V <sub>HVSS</sub> + 24   | V     |

| Supply                                                     | 11700             | ±42V <sub>P-P</sub> output protection (Note 6)           | 8                        |     | 20                       |       |

| Negative High-Voltage<br>Supply                            | V <sub>HVSS</sub> |                                                          | -2                       | 0   | 0                        | V     |

| Analog Supply Quiescent Current                            | I <sub>DD</sub>   | All channels and comparators powered up                  |                          | 1.5 |                          | mA    |

| High-Voltage Quiescent<br>Current                          | I <sub>HV</sub>   | All channels and comparators powered up, no load current |                          | 4.5 |                          | mA    |

| TIMING CHARACTERIST                                        | ICS               | •                                                        | 1                        |     |                          |       |

| SCLK Frequency                                             | f <sub>SCLK</sub> |                                                          |                          |     | 30                       | MHz   |

| SCLK Clock Period                                          | t <sub>CP</sub>   |                                                          | 33                       |     |                          | ns    |

| SCLK Pulse-Width High                                      | t <sub>CH</sub>   |                                                          | 13                       |     |                          | ns    |

| SCLK Pulse-Width Low                                       | t <sub>CL</sub>   | Read transactions must also meet t <sub>DOT</sub>        | 13                       |     |                          | ns    |

| CS Fall Setup Time                                         | t <sub>CSS0</sub> | CS falling edge to 1st SCLK rising edge setup time       | 10                       |     |                          | ns    |

### **Electrical Characteristics (continued)**

$(V_{DD}$  = 3.3V,  $V_{HVDD}$  = +15V,  $V_{HVSS}$  = 0V, Internal Reference,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C) (Note 1)

| PARAMETER                           | SYMBOL             | CONDITIONS                                                                                                                                                                            | MIN                                                                                                                          | TYP  | MAX | UNITS |

|-------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|

| CS Rise Setup Time                  | t <sub>CSS1</sub>  | SCLK rising edge to $\overline{\text{CS}}$ rising edge setup time                                                                                                                     | 5                                                                                                                            |      |     | ns    |

| CS Fall Hold Time                   | t <sub>CSH0</sub>  | SCLK rising edge to $\overline{\text{CS}}$ falling edge hold time                                                                                                                     |                                                                                                                              |      |     | ns    |

| CS Pulse-Width High                 | tcsw               | Minimum CS pulse-width high                                                                                                                                                           | 150                                                                                                                          |      |     | ns    |

| SDI Setup Time                      | t <sub>DS</sub>    | SDI setup time to SCLK rising edge                                                                                                                                                    | 10                                                                                                                           |      |     | ns    |

| SDI Hold Time                       | t <sub>DH</sub>    | SDI hold time after SCLK rising edge                                                                                                                                                  | 5                                                                                                                            |      |     | ns    |

| SDO Transition Time                 | t <sub>DOT</sub>   | SDO transition valid after SCLK falling edge                                                                                                                                          |                                                                                                                              |      | 20  | ns    |

| SDO Hold Time                       | t <sub>DOH</sub>   | Output remains valid after falling edge of SCLK                                                                                                                                       | 3                                                                                                                            |      |     | ns    |

| SDO Disable Time                    | t <sub>DOD</sub>   | Last SCLK falling edge to SDO disable,<br>C <sub>LOAD</sub> = 20pF                                                                                                                    |                                                                                                                              | 25   | ns  |       |

| RDY Fall Transition<br>Time         | t <sub>RT0</sub>   | Last SCLK falling edge to RDY falling edge                                                                                                                                            |                                                                                                                              |      | 40  | ns    |

| RDY Rise Transition<br>Time         | t <sub>RT1</sub>   | CS rise to RDY rise                                                                                                                                                                   |                                                                                                                              | 40   | ns  |       |

| THERMAL PROTECTION                  | I                  |                                                                                                                                                                                       |                                                                                                                              |      |     |       |

| Chip Thermal Shutdown Temperature   | T <sub>CSHDN</sub> | Temperature rising                                                                                                                                                                    |                                                                                                                              | 165  |     | °C    |

| Chip Thermal Warning<br>Temperature | T <sub>CWARN</sub> | Temperature rising                                                                                                                                                                    |                                                                                                                              | 145  |     | °C    |

| Chip Thermal Warning<br>Hysteresis  | T <sub>HYS</sub>   |                                                                                                                                                                                       |                                                                                                                              | 10   |     | °C    |

| EMC PROTECTION                      |                    |                                                                                                                                                                                       |                                                                                                                              |      |     |       |

| ESD                                 | V <sub>ESD</sub>   | All pins, Human Body Model                                                                                                                                                            |                                                                                                                              | ±2.5 |     | kV    |

| Surge                               | Vsurge             | AOP_, AON_, FB_, CIP_, CIN_, VIP_, VIN_ to GND, IEC 61000-4-5 with external 4.99kΩ series resistors on CIP_, CIN_, VIP_ and VIN_ pins, and a bidirectional TVS on AOP_ and AON_ pins. | _to GND, IEC 61000-4-5 with rnal 4.99kΩ series resistors on CIP_, _, VIP_ and VIN_ pins, and a ectional TVS on AOP_ and AON_ |      |     | kV    |

Note 1: Limits are 100% tested at  $T_A = +25$ °C, unless otherwise noted. Limits over the operating temperature range and relevant supply-voltage range are guaranteed by design and characterization.

Note 2: The output voltage is measured at the sense voltage input (VIP\_). The minimum supply voltage required is the sum of the output voltage V<sub>OUT</sub>, the voltage across the sense resistor, the diode forward voltage, and the dropout voltage. For a 25mA load current, a +12V output, a 50Ω sense resistor, and a diode forward voltage of 550mV (BAT46), the minimum required supply voltage is +14.8V.

Note 3: Offset Error, Gain Error, INL Error, and Settling Times are only guaranteed in the linear range. For Analog Output Current Mode Offset Error, Gain Error, INL Error, and Settling Times are only guaranteed in the specified Input Common-Mode Range (V<sub>CIP</sub> + V<sub>CIN</sub>)/2 of 0V to +12V. Offset Error, Gain Error, and INL Error are measured using the following DAC codes:

- Analog Output Voltage Mode:

VHVSS = 0V: code 98 and code 3441

VHVSS = -2V: code 6 and code 3441

- Analog Output Current Mode:

V<sub>HVSS</sub> = 0V: code 245 and code 3441

V<sub>HVSS</sub> = -2V: code 6 and code 3441

The minimum and maximum specification of the linear range and input-voltage range are guaranteed through Offset Error, Gain Error, and INL Error.

- Note 4: The threshold current specifies the typical current that triggers the short-circuit protection. The average current that accounts for self-heating of the device is significantly smaller due to the duty cycle when OVC\_CNFG is set to logic low.

- Note 5: Measured with only one channel powered up

- Note 6: Guaranteed by design and characterization. Not tested in production.

- Note 7: The Voltage Output Total Unadjusted Error (V<sub>TUF</sub>) does not include errors caused by Voltage Crosstalk and Load Regulation.

- Note 8: The minimum supply voltage required is the output current times the sum of the load and cable resistors, the voltage across the sense resistor, the diode forward voltage, and the dropout voltage. For a 25mA output current, a load resistor of  $500\Omega$ , a cable resistance of  $250\Omega$ , a  $50\Omega$  sense resistor, and a diode forward voltage of 550mV (BAT46), the minimum required supply voltages is +21.4V.

- Note 9: The Current Output Total Unadjusted Error (ITUE) does not include errors caused by Current Crosstalk and Common-Mode Rejection (if a load resistance other than  $250\Omega$  is used).

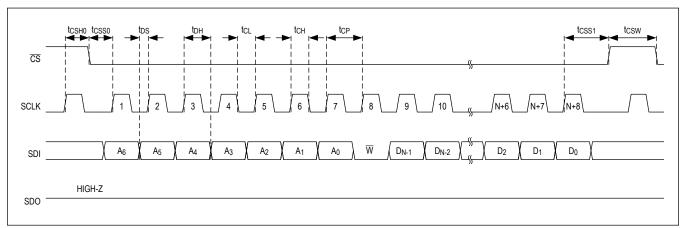

Figure 1. SPI Write Timing (N = 16 when CRC is disabled, and N = 24 when CRC is enabled)

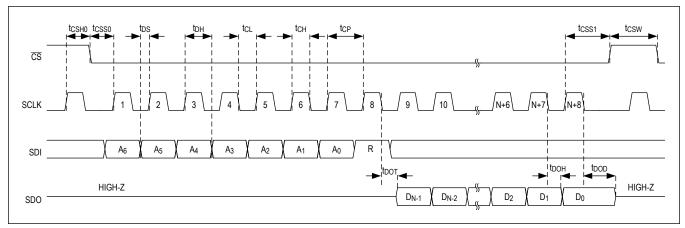

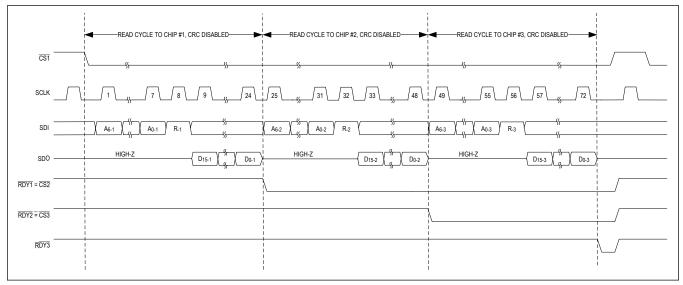

Figure 2. SPI Read Timing (N = 16 when CRC is disabled, and N = 24 when CRC is enabled)

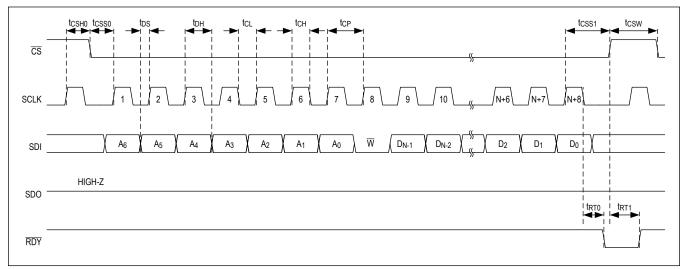

Figure 3. Elongated SPI Write Timing for Daisy-Chain Applications (N = 16 when CRC is disabled, and N = 24 when CRC is enabled)

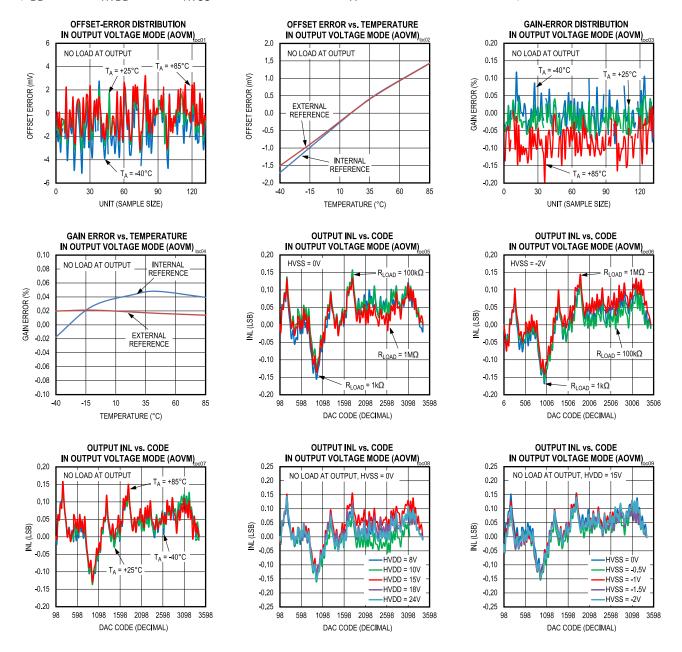

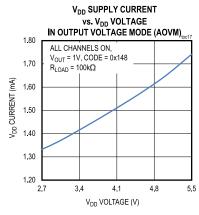

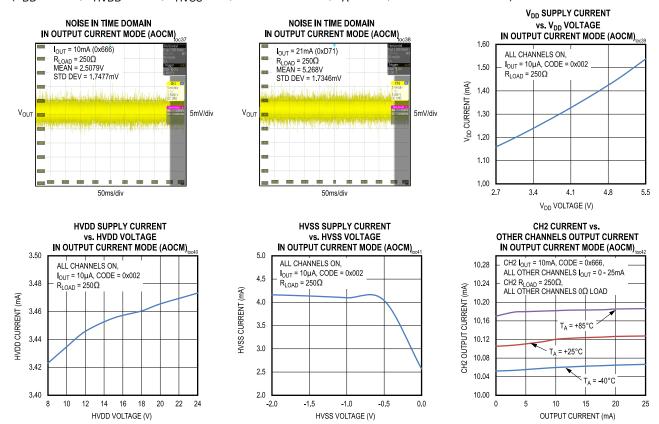

### **Typical Operating Characteristics**

$(V_{DD} = +3.3V, V_{HVDD} = +15V, V_{HVSS} = 0V, Internal Reference, T_A = 25$ °C, unless otherwise noted)

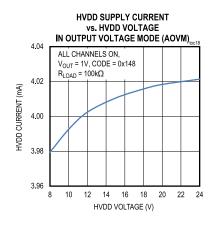

### **Typical Operating Characteristics (continued)**

$(V_{DD} = +3.3V, V_{HVDD} = +15V, V_{HVSS} = 0V, Internal Reference, T_A = 25$ °C, unless otherwise noted)

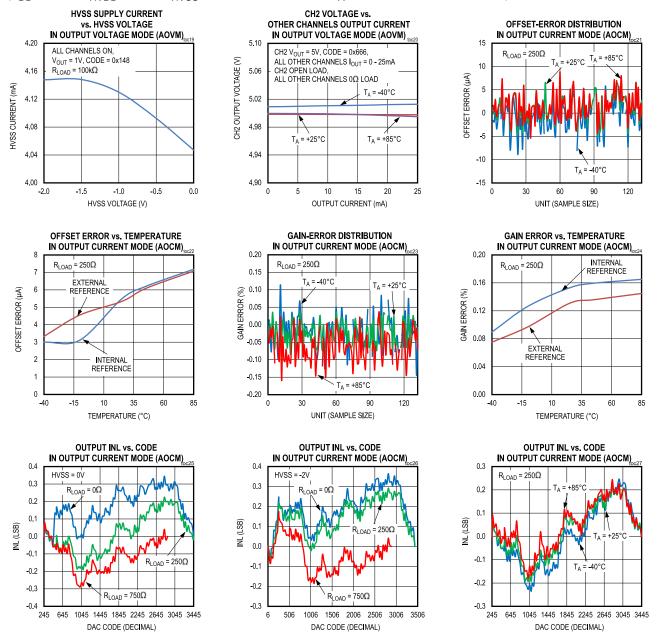

### **Typical Operating Characteristics (continued)**

$(V_{DD} = +3.3V, V_{HVDD} = +15V, V_{HVSS} = 0V, Internal Reference, T_A = 25$ °C, unless otherwise noted)

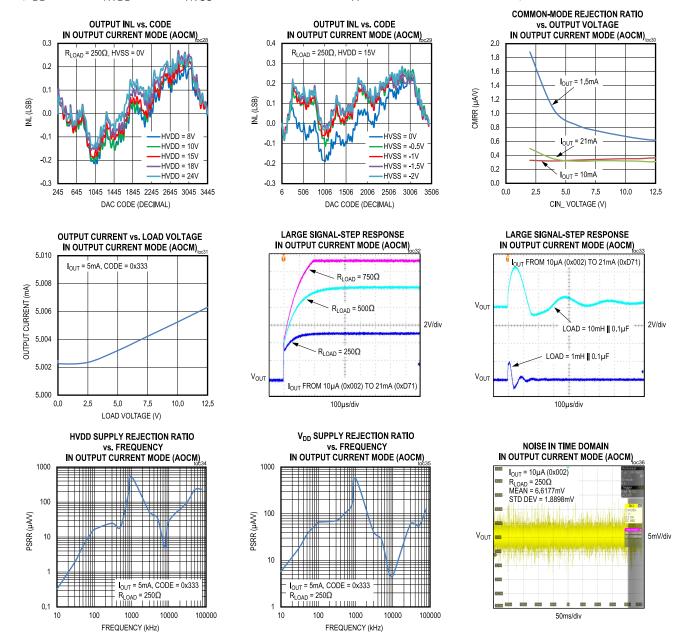

### **Typical Operating Characteristics (continued)**

$(V_{DD} = +3.3V, V_{HVDD} = +15V, V_{HVSS} = 0V, Internal Reference, T_A = 25$ °C, unless otherwise noted)

### **Typical Operating Characteristics (continued)**

$(V_{DD} = +3.3V, V_{HVDD} = +15V, V_{HVSS} = 0V, Internal Reference, T_A = 25$ °C, unless otherwise noted)

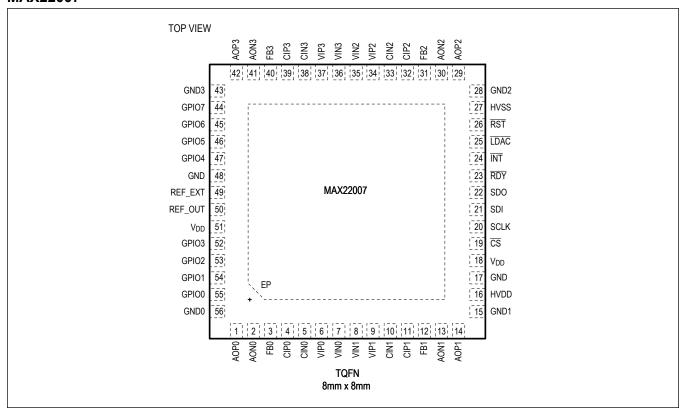

## **Pin Configuration**

### **MAX22007**

## **Pin Description**

| PIN        | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                          | REF<br>SUPPLY     | TYPE   |

|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------|

| POWER SUP  | PLY             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |        |

| 16         | HVDD            | Positive High-Voltage Power Supply from +8V to (HVSS +24V) for the Output Channels. Bypass HVDD to GND with a minimum 1µF ceramic capacitor as close to the device pin as possible.                                                                                                                                                                                                                                                                               | HVDD              | Power  |

| 17, 48     | GND             | Logic/Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>DD</sub>   | Ground |

| 18, 51     | V <sub>DD</sub> | Low-Voltage Power Supply from +2.7V to +5.5V. Connect both V <sub>DD</sub> pins together and bypass each pin to GND with a minimum 1µF ceramic capacitor as close to the device pin as possible.                                                                                                                                                                                                                                                                  | V <sub>DD</sub>   | Power  |

| 27         | HVSS            | Negative High-Voltage Power Supply from -2V to 0V for the Output Channels. For most applications connect HVSS to GND (0V), but in cases where the output must be down to 0V (or 0mA), connect HVSS to a -2V supply and in this case, bypass HVSS to GND with a minimum 1µF ceramic capacitor as close to the device pin as possible.                                                                                                                              | HVDD              | Power  |

| EP         | EP              | Exposed Pad. Connect the exposed pad on the bottom of the package to HVSS. Refer to the <u>PCB Layout Recommendations</u> section for layout recommendations.                                                                                                                                                                                                                                                                                                     | HVDD              | Power  |

| VOLTAGE RE | EFERENCE        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |        |

| 49         | REF_EXT         | External Reference Voltage Input. Instead of the internal voltage reference, an external precision 2.500V reference can be connected between REF_EXT and GND. The REF_SEL bit in the <i>Configuration</i> register must be set appropriately. If an external reference is connected to the REF_EXT pin, bypass it to GND with a minimum 1µF ceramic capacitor as close to the device pin as possible. If the internal reference is selected, tie this pin to GND. | $V_DD$            | Input  |

| 50         | REF_OUT         | Voltage Reference Output. The REF_OUT pin can be used to supply multiple devices from the same reference source. If not in use, leave REF_OUT unconnected.                                                                                                                                                                                                                                                                                                        | $V_{\mathrm{DD}}$ | Output |

| ANALOG OU  | TPUT CHANNE     | L 0                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |        |

| 1          | AOP0            | Channel 0 Positive Amplifier Output. Connect to the anode of an external diode.                                                                                                                                                                                                                                                                                                                                                                                   | HVDD              | Output |

| 2          | AON0            | Channel 0 Negative Amplifier Output. Connect to the cathode of an external diode.                                                                                                                                                                                                                                                                                                                                                                                 | HVDD              | Output |

| 3          | FB0             | Channel 0 Compensation Network Input. Refer to the <u>Feedback</u> ( <u>FB_</u> ) <u>Inputs</u> section for details.                                                                                                                                                                                                                                                                                                                                              | HVDD              | Input  |

| 4          | CIP0            | Channel 0 Positive Current-Sense Input                                                                                                                                                                                                                                                                                                                                                                                                                            | HVDD              | Input  |

| 5          | CIN0            | Channel 0 Negative Current-Sense Input                                                                                                                                                                                                                                                                                                                                                                                                                            | HVDD              | Input  |

| 6          | VIP0            | Channel 0 Positive Voltage-Sense Input                                                                                                                                                                                                                                                                                                                                                                                                                            | HVDD              | Input  |

| 7          | VIN0            | Channel 0 Negative Voltage-Sense Input                                                                                                                                                                                                                                                                                                                                                                                                                            | HVDD              | Input  |

| 56         | GND0            | Channel 0 Ground. Connect GND0 to GND.                                                                                                                                                                                                                                                                                                                                                                                                                            | HVDD              | Ground |

| ANALOG OU  | TPUT CHANNE     | L1                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |        |

| 14         | AOP1            | Channel 1 Positive Amplifier Output. Connect to the anode of an external diode.                                                                                                                                                                                                                                                                                                                                                                                   | HVDD              | Output |

## **Pin Description (continued)**

| PIN         | NAME          | FUNCTION                                                                                                          | REF<br>SUPPLY   | TYPE   |

|-------------|---------------|-------------------------------------------------------------------------------------------------------------------|-----------------|--------|

| 13          | AON1          | Channel 1 Negative Amplifier Output. Connect to the cathode of an external diode.                                 | HVDD            | Output |

| 12          | FB1           | Channel 1 Compensation Network Input. Refer to the <u>Feedback</u> ( <u>FB_) Inputs</u> section for details.      | HVDD            | Input  |

| 11          | CIP1          | Channel 1 Positive Current-Sense Input                                                                            | HVDD            | Input  |

| 10          | CIN1          | Channel 1 Negative Current-Sense Input                                                                            | HVDD            | Input  |

| 9           | VIP1          | Channel 1 Positive Voltage-Sense Input                                                                            | HVDD            | Input  |

| 8           | VIN1          | Channel 1 Negative Voltage-Sense Input                                                                            | HVDD            | Input  |

| 15          | GND1          | Channel 1 Ground. Connect GND1 to GND.                                                                            | HVDD            | Ground |

| ANALOG OUT  | PUT CHANNE    | L 2                                                                                                               |                 |        |

| 29          | AOP2          | Channel 2 Positive Amplifier Output. Connect to the anode of an external diode.                                   | HVDD            | Output |

| 30          | AON2          | Channel 2 Negative Amplifier Output. Connect to the cathode of an external diode.                                 | HVDD            | Output |

| 31          | FB2           | Channel 2 Compensation Network Input. Refer to the <u>Feedback</u> ( <u>FB_) Inputs</u> section for details.      | HVDD            | Input  |

| 32          | CIP2          | Channel 2 Positive Current-Sense Input                                                                            | HVDD            | Input  |

| 33          | CIN2          | Channel 2 Negative Current-Sense Input                                                                            | HVDD            | Input  |

| 34          | VIP2          | Channel 2 Positive Voltage-Sense Input                                                                            | HVDD            | Input  |

| 35          | VIN2          | Channel 2 Negative Voltage-Sense Input                                                                            | HVDD            | Input  |

| 28          | GND2          | Channel 2 Ground. Connect GND2 to GND.                                                                            | HVDD            | Ground |

| ANALOG OUT  | PUT CHANNE    | L 3                                                                                                               |                 |        |

| 42          | AOP3          | Channel 3 Positive Amplifier Output. Connect to the anode of an external diode.                                   | HVDD            | Output |

| 41          | AON3          | Channel 3 Negative Amplifier Output. Connect to the cathode of an external diode.                                 | HVDD            | Output |

| 40          | FB3           | Channel 3 Compensation Network Input. Refer to the <u>Feedback</u> ( <u>FB_) Inputs</u> section for details.      | HVDD            | Input  |

| 39          | CIP3          | Channel 3 Positive Current-Sense Input                                                                            | HVDD            | Input  |

| 38          | CIN3          | Channel 3 Negative Current-Sense Input                                                                            | HVDD            | Input  |

| 37          | VIP3          | Channel 3 Positive Voltage-Sense Input                                                                            | HVDD            | Input  |

| 36          | VIN3          | Channel 3 Negative Voltage-Sense Input                                                                            | HVDD            | Input  |

| 43          | GND3          | Channel 3 Ground. Connect GND3 to GND.                                                                            | HVDD            | Ground |

| LOGIC INTER | FACE          |                                                                                                                   |                 |        |

| 19          | <del>cs</del> | Active-Low Chip Select Input from Controller. The SPI interface responds only when $\overline{\text{CS}}$ is low. | V <sub>DD</sub> | Input  |

| 20          | SCLK          | Serial Clock Input from Controller                                                                                | $V_{DD}$        | Input  |

| 21          | SDI           | Serial Data Input. SPI MOSI data input from controller.                                                           | V <sub>DD</sub> | Input  |

| 22          | SDO           | Serial Data Output. SPI MISO data output to controller.                                                           | $V_{DD}$        | Output |

## **Pin Description (continued)**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                               | REF<br>SUPPLY     | TYPE   |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------|

| 23  | RDY   | Active-Low Ready Output. $\overline{\text{RDY}}$ is asserted low after the last SCLK falling edge of an SPI transaction and is used to drive the $\overline{\text{CS}}$ input of the next MAX22007 when used for daisy-chain applications. If the MAX22007 is not used in daisy-chain mode, or is the last device in the daisy chain, $\overline{\text{RDY}}$ can be left unconnected. | $V_{DD}$          | Output |

| 24  | ĪNT   | Active-Low Open-Drain Interrupt Output. INT is asserted low when any interrupt source is detected and flagged in the <u>Status &amp; Interrupts</u> register, provided that interrupt source has been enabled by setting the corresponding bit in the <u>Interrupt Enable</u> register. Connect a pullup resistor from INT to V <sub>DD</sub> .                                        | $V_{DD}$          | Output |

| 25  | LDAC  | Active-Low DAC Load Input. When asserted low, transfers the contents of the DAC Channel <u>Data</u> registers and updates all the DAC outputs simultaneously. <u>LDAC</u> is ignored whilst <u>RST</u> is low. Connect to V <sub>DD</sub> if not used.                                                                                                                                 | V <sub>DD</sub>   | Input  |

| 26  | RST   | Active-Low Reset Input. When asserted low, reconfigures all registers to their power-on default states, analog outputs go high impedance, and DAC conversions stop.                                                                                                                                                                                                                    | V <sub>DD</sub>   | Input  |

| 55  | GPIO0 | General Purpose Digital Input/Output 0                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$          | I/O    |

| 54  | GPIO1 | General Purpose Digital Input/Output 1                                                                                                                                                                                                                                                                                                                                                 | $V_{\mathrm{DD}}$ | I/O    |

| 53  | GPIO2 | General Purpose Digital Input/Output 2                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$          | I/O    |

| 52  | GPIO3 | General Purpose Digital Input/Output 3                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$          | I/O    |

| 47  | GPIO4 | General Purpose Digital Input/Output 4                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$          | I/O    |

| 46  | GPIO5 | General Purpose Digital Input/Output 5                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$          | I/O    |

| 45  | GPIO6 | General Purpose Digital Input/Output 6                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$          | I/O    |

| 44  | GPIO7 | General Purpose Digital Input/Output 7                                                                                                                                                                                                                                                                                                                                                 | $V_{DD}$          | I/O    |

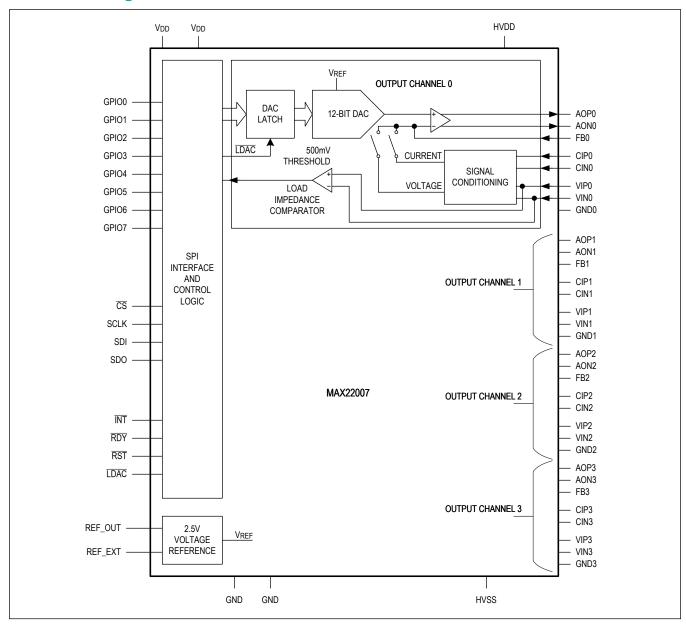

## **Functional Diagrams**

Note: Only one channel is shown for clarity.

### **Detailed Description**

The MAX22007 is a software-configurable four-channel analog output device that drives a voltage or current output on each channel. All outputs are protected to  $\pm 42V_{P-P}$  for high-voltage supply of HVDD = 8V to 20V and HVSS = -2V to 0V. Each output channel of the MAX22007 features a 12-bit DAC with fast settling time using a shared internal voltage reference.

The MAX22007 offers low-offset high-voltage amplifiers to condition the signal from low-voltage DAC outputs to high-voltage or current outputs. If one output is miswired, all other outputs remain unaffected and function normally. An internal comparator can be used to determine the load impedance and allows the microcontroller to intelligently select for voltage-or current-output mode. All outputs are kept safe by integrated current protection for functional and thermal robustness. The MAX22007 also includes a thermal shutdown circuit that protects the device when the junction temperature exceeds 165°C (typ).

The MAX22007 communicates to a microcontroller using an SPI interface at clock rates up to 30MHz with an optional eight-bit CRC for improved data integrity. Eight GPIOs can be used to interface and control other resources on the circuit board. The MAX22007 operates from a 2.7V to 5.5V low-voltage supply, a +8V to +24V high-voltage positive supply, and a -2V to 0V high-voltage negative supply. The MAX22007 is available in an 8mm x 8mm 56-pin TQFN package and operates over the -40°C to +85°C temperature range with ±2.5kV HBM ESD protection on all pins.

#### DAC

Each output channel features a separate low-power 12-bit DAC. The input value for each DAC is held in the corresponding Channel Data register. Each output channel uses a DAC latch between the Channel Data register and the DAC that contains the digital representation of the value that is currently presented at the channel output. The default configuration is to use the latch but it can be configured for transparent mode by setting the bits LD\_CNFG[3:0] in the <u>Configuration</u> register to 1. When LD\_CNFG[3:0] bits are set to 0, the operation of the latch is controlled by making the hardware pin LDAC active low, or by setting LD\_CTRL[3:0] bits in the <u>Control</u> register using a SPI write operation. The LD\_CTRL[3:0] bits are self-clearing.

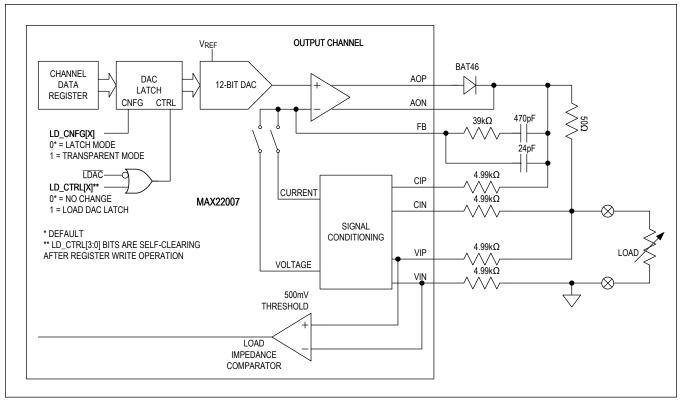

The MAX22007 offers several options to update the DAC output to accommodate different application requirements as shown in Figure 4. In order for any of the analog outputs to change value, the values contained in the Channel Data registers need to be transferred to the DAC latch output. In transparent latch mode (LD\_CNFG[3:0] bits = 1), a write to the Channel Data register automatically updates the channel output value. In latch mode, a write transaction to one or all of the Channel Data registers does not necessarily change the channel output value. The options of controlling the  $\overline{\text{LDAC}}$  pin or setting the LD\_CTRL[3:0] bits allow for individual or simultaneous update of the channel output values, and to be able to control the exact timing of the update. Using the  $\overline{\text{LDAC}}$  pin over an SPI transaction to update the DAC latches has the advantage that the exact timing of the update can be controlled.

If no tight control of the output update timing is required, the step of loading the DAC latch can be eliminated by setting bits LD\_CNFG[3:0] in the *Configuration* register to 1 (transparent mode) and if one of the LD\_CNFG[x] bits is set for a certain channel, then writing to the Channel x Data register immediately updates the analog output value, bypassing the DAC latch altogether. Alternatively, if the LDAC pin is tied to ground, the DAC latch automatically updates the DAC with the Channel Data register values.

Figure 4. MAX22007 Output Channel

### **High-Voltage Analog Output**

The MAX22007 offers the following modes of operation:

- Analog Output-Voltage Mode (AOVM)

- Analog Output-Current Mode (AOCM)

The nominal output voltage range in AOVM is 0V to +10V, while linearity is guaranteed up to +10.5V. The DAC full-scale range is 0V to +12.5V to offer 25% overrange of the nominal output voltage range. In AOVM, the load voltage is sensed through the VIP\_ and VIN\_ inputs.

The ideal output voltage is given as:

$$V_{\text{OUT}} = 5 \times V_{\text{REF}} \times \frac{D}{2^N}$$

where.

D = Input code in the Channel x Data register

V<sub>REF</sub> = Reference voltage

N = Resolution of the DAC (N = 12)

The MAX22007 is factory calibrated using the internal reference. The full-scale range in AOVM is calibrated to 12.5V based on the internal reference; thus,  $V_{\text{OUT}} = 12.5 \times \frac{D}{2^N}$ . When using the external reference,  $V_{\text{REF}}$  in the equation is the external reference voltage.

## Four-Channel 12-Bit Configurable Analog Output with Integrated Voltage Reference

The nominal output current range in AOCM is 0mA to +20mA, while linearity is guaranteed up to +21mA. The DAC full-scale range is 0mA to +25mA to offer 25% overrange of the nominal output current range. In AOCM, the load current is sensed through the CIP\_ and CIN\_ inputs using an external  $50\Omega$  resistor. A value of  $50\Omega$  is required to produce the correct output-current range.

The ideal output current is given as:

$$I_{\text{OUT}} = \frac{V_{\text{REF}}}{2 \times R_{\text{SENSE}}} \times \frac{D}{2^N}$$

where.

D = Input code in the Channel x Data register

V<sub>RFF</sub> = Reference voltage

$R_{SENSE}$  = External 50 $\Omega$  sense resistor

N = Resolution of the DAC (N = 12)

The MAX22007 is factory calibrated using the internal reference and an ideal  $50\Omega$  sense resistor. The full-scale range in AOCM is calibrated to 25mA based on the external sense resistor; thus,  $I_{OUT} = \frac{1.25}{R_{SENSE}} \times \frac{D}{2^N}$ . The accuracy and

temperature coefficient of the sense resistor contributes to the output accuracy. When using the external reference, V<sub>REF</sub> in the equation is the external reference voltage.

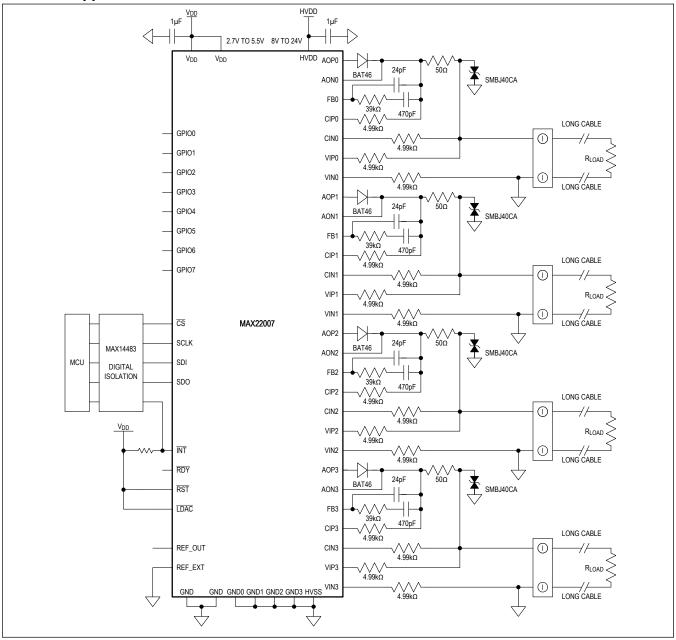

### Two-, Three-, and Four-Wire Operation

The MAX22007 can operate in two-wire, three-wire, or four-wire configurations, depending on the external connection of the CIN\_, VIP\_, and VIN\_ pins. Refer to the <u>Typical Application Circuits</u> section for examples of two-wire and four-wire applications.

#### Feedback (FB\_) Inputs

The MAX22007 offers a feedback input pin (FB\_) per channel that allows access to the inverting input of the output amplifier to add an external compensation network as shown in the <u>Typical Application Circuits</u>. The type of network and component values depend on the output load requirements. A recommended compensation network that offers stable amplifier performance over a wide range of resistive and capacitive loads for output voltage mode and a wide range of resistive and inductive loads for output current mode is shown in the <u>Typical Application Circuits</u>.

#### Comparator

The MAX22007 offers a comparator that monitors the output voltage through VIP\_ and VIN\_ per channel and sets a bit in the <u>Status & Interrupts</u> register if the output voltage exceeds a threshold of 500mV (typical). This comparator can be used to determine the load impedance to automatically detect whether a connected load requires output current mode or output voltage mode.

In order to determine the load impedance, set the output in question to output current mode. Increase the output current until the comparator trips, and the COMP\_INT[x] bit is set in the <u>Status & Interrupts</u> register. The load impedance is then simply the comparator threshold voltage of 500mV divided by the programmed output current.

The two bits COMP\_EDGE\_CNFG[1:0] in the <u>Configuration</u> register can be programmed to <u>select different operating</u> modes for the comparators, which in turn trigger the COMP\_INT[3:0] bits and assert the <u>INT</u> pin if enabled. This setting applies to all output channels. Programming COMP\_EDGE\_CNFG[1:0] to be 0b01 detects a rising edge at the comparator output, 0b10 detects a falling edge at the comparator output, and 0b11 shows the comparator output level, either a 0 or a 1, using the COMP\_INT[3:0] bits.

#### **Input and Output Protection**

The AOP\_ and AON\_ outputs feature devices with a maximum operating voltage of 65V. The outputs can therefore tolerate ±42V<sub>P-P</sub> for a high-voltage supply HVDD up to +20V. The AOP\_ output uses an external small-signal diode. This series protection limits the current flowing into the MAX22007 to very small amounts in the μA-range in case the output

voltage is pulled above HVDD. A suitable external diode is BAT46. If the output is pulled below HVSS, an internal diode prevents any large current from flowing.