### **MAX28200**

## 16-Bit Microcontroller with ADC and I2C

## **General Description**

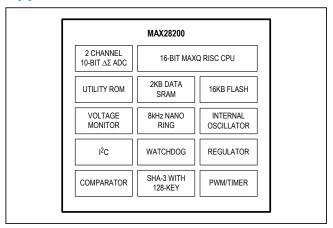

The MAX28200 is a low-power, 16-bit MAXQ<sup>®</sup> microcontroller (µC) designed for low-power applications, including smart phones and consumer electronics. The device combines a powerful 16-bit RISC microcontroller with a 10-bit, 93.75ksps ADC along with an I<sup>2</sup>C communications port. The device includes four GPIO pins. The device includes 16KB of flash memory and 2KB of data SRAM. Additional utility ROM space includes macros such as an I<sup>2</sup>C bootloader to enable flash memory firmware updates in the field. The device provides NIST SP 800-185 compliant secure hash algorithm (SHA-3) KMAC challenge and response authentication and can be paired with other SHA-3 devices.

For the ultimate in low-power battery-operated performance, the device includes an ultra-low-power stop mode. In this mode, the minimum amount of circuitry is powered. The device wakes up on a matching I<sup>2</sup>C address. Wake-up sources also include external interrupts, the power-fail warning, and a wake-up timer interrupts. The microcontroller runs from a wide 1.71V to 3.63V operating voltage.

## **Applications**

- Smartphones

- Consumer Electronics

Ordering Information appears at end of data sheet.

### **Benefits and Features**

- High-Performance, Low-Power, 16-Bit RISC Core

- Internal 12MHz Oscillator Requires No External Components

- Two-Channel, 10-Bit 93.75ksps ADC

- I<sup>2</sup>C Slave Peripheral

- 400kHz Operating Frequency

- · Flash Bootloader Function

- Wakeup from Ultra-Low Power Stop Mode on I<sup>2</sup>C Address Match

- 16-Bit PWM Timer Output

- Wake-Up Timer

- SHA-3 KMAC Secure Authentication with RNG

- 1.71V to 3.63V Operating Voltage

- 16-Bit Instruction Word, 16-Bit Data Bus

- Memory Features

- · 16KB Flash Memory

- 2KB Data SRAM

- -40°C to +85°C Operating Temperature

- Low Power Consumption

- 0.2μA (typ), 2.0μA (max) in Stop Mode,

T<sub>A</sub> = +25°C, Power-Fail Monitor Disabled

- · 2.7mA (typ) at 12MHz in Active Mode

- 1.7mm x 1.8mm x 0.5mm 12-Bump WLP Package

# **Applications**

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

## 16-Bit Microcontroller with ADC and I2C

# **Absolute Maximum Ratings**

| V <sub>DD</sub> 0.3V to +3.63V           | Storage Temperature Range65°C to +150°C |

|------------------------------------------|-----------------------------------------|

| Any Ball0.3V to +3.63V                   | Soldering Temperature (reflow)+260°C    |

| Operating Temperature Range40°C to +85°C |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

## **12 WLP**

| Package Code                           | N121C1+1                       |

|----------------------------------------|--------------------------------|

| Outline Number                         | 21-100300                      |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                                |

| Junction to Ambient (θ <sub>JA</sub> ) | 72.82°C/W                      |

| Junction to Case (θ <sub>JC</sub> )    | N/A                            |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## **Electrical Characteristics**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                    | SYMBOL                 | COND                                                                                                                                                      | ITIONS                                              | MIN                      | TYP                           | MAX                      | UNITS |

|----------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------|-------------------------------|--------------------------|-------|

| Supply Voltage                               | V <sub>DD</sub>        |                                                                                                                                                           |                                                     | V <sub>RST</sub>         |                               | 3.63                     | V     |

| 1.8V Internal Regulator                      | V <sub>REG18</sub>     |                                                                                                                                                           |                                                     | 1.62                     | 1.8                           | 1.98                     | V     |

|                                              |                        | Distant                                                                                                                                                   | CMPCN[4:3] = 00                                     |                          | 2.214                         |                          |       |

|                                              |                        | Rising V <sub>DD</sub>                                                                                                                                    | CMPCN[4:3] = 01                                     |                          | 2.503                         |                          | ] ,,  |

|                                              |                        | Rising V <sub>DD</sub>                                                                                                                                    | CMPCN[4:3] = 10                                     |                          | 2.805                         |                          | V     |

| Davida Fall Manaina Mallana                  | .,,                    | Rising V <sub>DD</sub>                                                                                                                                    | CMPCN[4:3] = 11                                     |                          | 3.005                         |                          | 1     |

| Power-Fail Warning Voltage                   | Itage V <sub>PFW</sub> |                                                                                                                                                           | CMPCN[4:3] = 00                                     |                          | 17                            |                          |       |

|                                              |                        | I bartana 'a                                                                                                                                              | CMPCN[4:3] = 01                                     |                          | 18                            |                          |       |

|                                              |                        | Hysteresis                                                                                                                                                | CMPCN[4:3] = 10                                     |                          | 22                            |                          | mV    |

|                                              |                        |                                                                                                                                                           | CMPCN[4:3] = 11                                     |                          | 25                            |                          |       |

| Power-Fail Reset Voltage                     | V <sub>RST</sub>       |                                                                                                                                                           |                                                     |                          | 1.71                          |                          | V     |

| Power-On Reset Voltage                       | V <sub>POR</sub>       | Monitors V <sub>DD</sub>                                                                                                                                  |                                                     |                          | 1.2                           |                          | V     |

| Active Current                               | I <sub>DD_1</sub>      | f <sub>SYSCLK</sub> = 12MHz, executing code from<br>flash memory, all inputs connected to GND/<br>V <sub>DD</sub> , outputs do not source or sink current |                                                     |                          | 2.7                           | 4.7                      | mA    |

| Ote a Maria O assess                         | I <sub>S1</sub>        | $T_A = +25^{\circ}C$ (power-fa                                                                                                                            | ail off)                                            |                          | 0.4                           | 2                        |       |

| Stop Mode Current                            | I <sub>S2</sub>        | T <sub>A</sub> = +25°C (power-fa                                                                                                                          | ail on)                                             |                          | 33                            | 50                       | μA    |

| Power Consumption During Power-On Reset      | I <sub>POR</sub>       | During POR while V <sub>D</sub>                                                                                                                           | During POR while V <sub>DD</sub> < V <sub>POR</sub> |                          | 450                           |                          | nA    |

| Stop Mode Resume Time                        | t <sub>ON</sub>        |                                                                                                                                                           |                                                     |                          | 375 +<br>(16t <sub>CK</sub> ) |                          | μs    |

| Input Low Voltage for All GPIO Pins          | V <sub>IL</sub>        |                                                                                                                                                           |                                                     | V <sub>GND</sub>         |                               | 0.3 x<br>V <sub>DD</sub> | V     |

| Input Low Voltage for SDA and SCL            | V <sub>IL_I2C</sub>    |                                                                                                                                                           |                                                     | V <sub>GND</sub>         |                               | 0.54                     | V     |

| Input High Voltage for All GPIO Pins         | V <sub>IH</sub>        |                                                                                                                                                           |                                                     | 0.7 x<br>V <sub>DD</sub> |                               | V <sub>DD</sub>          | V     |

| Input High Voltage for SDA and SCL           | V <sub>IH</sub> _I2C   |                                                                                                                                                           |                                                     | 1.35                     |                               | V <sub>DD</sub>          | V     |

| Input Hysteresis (Schmitt) for All GPIO Pins | V <sub>IHYS</sub>      | V <sub>DD</sub> = 3.3V, T <sub>A</sub> = +25                                                                                                              | 5°C                                                 |                          | 300                           |                          | mV    |

| Input Hysteresis (Schmitt) for SDA, SDL      | V <sub>IHYS_I2C</sub>  | V <sub>DD</sub> = 3.3V, T <sub>A</sub> = +25                                                                                                              | 5°C                                                 |                          | 250                           |                          | mV    |

# **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                      | SYMBOL             | CONDITIONS                                                                                        | MIN                   | TYP                | MAX                          | UNITS   |

|------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------|-----------------------|--------------------|------------------------------|---------|

|                                                |                    | V <sub>DD</sub> = 3.6V, I <sub>OL</sub> = 5.5mA                                                   |                       | 0.4                | 0.5                          |         |

| Output Low Voltage for All GPIO, SDA, SCL      | V <sub>OL</sub>    | V <sub>DD</sub> = 2.35V, I <sub>OL</sub> = 4mA                                                    |                       | 0.4                | 0.5                          | V       |

| 01 10, 0571, 002                               |                    | V <sub>DD</sub> = 1.8V, I <sub>OL</sub> = 2mA                                                     |                       | 0.4                | 0.5                          |         |

| Output High Voltage All<br>GPIO Pins           | V <sub>OH</sub>    | I <sub>OH</sub> = -2mA                                                                            | V <sub>DD</sub> - 0.5 |                    | V <sub>DD</sub>              | V       |

| Input/Output Pin<br>Capacitance                | C <sub>IO</sub>    |                                                                                                   |                       | 15                 |                              | pF      |

| Input Leakage Current for All Pins             | ΙL                 | V <sub>IN</sub> at 0V or V <sub>DD</sub> , internal pullup disabled                               | -100                  |                    | +100                         | nA      |

| Input Pullup Resistor for                      | В                  | V <sub>DD</sub> = 3.0V, V <sub>OL</sub> = 0.4V                                                    | 16                    | 28                 | 39                           | kΩ      |

| P0.1, P0.2, P0.3                               | R <sub>PU</sub>    | V <sub>DD</sub> = 1.8V, V <sub>OL</sub> = 0.4V                                                    | 18                    | 31                 | 43                           | KL2     |

| Internal Oscillator                            | fosc               |                                                                                                   | 10.8                  | 12                 | 13.2                         | MHz     |

| System Clock Period                            | t <sub>CK</sub>    |                                                                                                   |                       | 1/f <sub>OSC</sub> |                              | ns      |

| System Clock Frequency                         | f <sub>CK</sub>    |                                                                                                   |                       | 1/t <sub>CK</sub>  |                              | MHz     |

| Nanopower Ring Frequency                       | f <sub>NANO</sub>  | T <sub>A</sub> = +25°C                                                                            | 3.0                   | 8.0                | 20.0                         | kHz     |

| Wakeup Timer Interval                          | twakeup            |                                                                                                   | 1/f <sub>NANO</sub>   |                    | 65,535/<br>f <sub>NANO</sub> | s       |

| FLASH MEMORY                                   |                    |                                                                                                   |                       |                    |                              |         |

| System Clock During Flash<br>Programming/Erase | fFPSYSCLK          | f <sub>FPSYSCLK</sub> /(FCKDIV[3:0]+1) must equal 1MHz, verify PFI = 0 before calling utility ROM |                       | fosc               |                              | MHz     |

| Flash Erase Time                               | t <sub>ME</sub>    | Mass erase                                                                                        |                       | 40                 |                              | ma      |

| FIASII EI ASE TIITIE                           | t <sub>ERASE</sub> | Page erase                                                                                        |                       | 40                 |                              | ms      |

| Flash Programming Time<br>Per Word             | t <sub>PROG</sub>  | Excluding utility ROM overhead                                                                    |                       | 40                 |                              | μs      |

| Flash Endurance                                |                    |                                                                                                   | 20                    |                    |                              | kcycles |

| Data Retention                                 | t <sub>RET</sub>   | T <sub>A</sub> = +25°C                                                                            | 100                   |                    |                              | years   |

# **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                 | SYMBOL              | CONDITIONS                                                                      | MIN              | TYP                 | MAX             | UNITS             |

|---------------------------|---------------------|---------------------------------------------------------------------------------|------------------|---------------------|-----------------|-------------------|

| ADC (DELTA-SIGMA)         |                     |                                                                                 | -                |                     |                 | •                 |

| Resolution                |                     |                                                                                 |                  | 10                  |                 | bits              |

| ADC Clock Rate            | f <sub>ACLK</sub>   | f <sub>ACLK</sub> = f <sub>OSC</sub>                                            |                  | 12                  |                 | MHz               |

| ADC Clock Period          | t <sub>ACLK</sub>   |                                                                                 |                  | 1/f <sub>ACLK</sub> |                 | μs                |

| Input Voltage Range       | V <sub>AIN</sub>    |                                                                                 | V <sub>GND</sub> |                     | V <sub>DD</sub> | V                 |

| Analog Input Capacitance  | C <sub>AIN</sub>    |                                                                                 |                  | 1                   |                 | pF                |

| Integral Nonlinearity     | INL                 | V <sub>IN</sub> = -0.5dB full scale                                             |                  | ±3                  |                 | LSb               |

| Differential Nonlinearity | DNL                 | V <sub>IN</sub> = -0.5dB full scale                                             |                  | ±3                  |                 | LSb               |

| Offset Error              | Vos                 |                                                                                 |                  | ±3                  |                 | LSb               |

| ADC Active Current        | I <sub>ADC</sub>    | ADEN = 1                                                                        |                  | 280                 |                 | μA                |

| ADC Setup Time            | t <sub>ADC_SU</sub> | Settling time due to channel, reference or scale change (not production tested) |                  | 35                  |                 | μs                |

| ADC Oversampling Ratio    | OSR                 |                                                                                 |                  | 128                 |                 |                   |

| ADC Output Latency        | t <sub>ADC</sub>    |                                                                                 |                  | 2 x OSR<br>+ 1      |                 | t <sub>ACLK</sub> |

| ADC Throughtput           | f <sub>ADC</sub>    | f <sub>ADC</sub> = f <sub>ACLK</sub> /OSR                                       |                  | 93.75               |                 | ksps              |

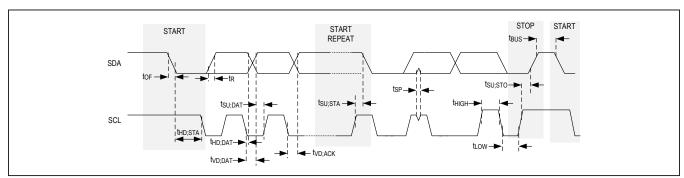

## Electrical Characteristics—I<sup>2</sup>C

(Timing specifications are guaranteed by design and not production tested.)

| PARAMETER                                  | SYMBOL              | CONDITIONS                                                       | MIN | TYP | MAX | UNITS |

|--------------------------------------------|---------------------|------------------------------------------------------------------|-----|-----|-----|-------|

| STANDARD MODE                              |                     |                                                                  |     |     |     |       |

| Output Fall Time                           | t <sub>OF</sub>     | Standard mode, from V <sub>IH(MIN)</sub> to V <sub>IL(MAX)</sub> |     | 150 |     | ns    |

| SCL Clock Frequency                        | f <sub>SCL</sub>    |                                                                  | 0   |     | 100 | kHz   |

| Low Period SCL Clock                       | t <sub>LOW</sub>    |                                                                  | 4.7 |     |     | μs    |

| High Time SCL Clock                        | t <sub>HIGH</sub>   |                                                                  | 4.0 |     |     | μs    |

| Setup Time for Repeated<br>Start Condition | <sup>t</sup> su;sta |                                                                  | 4.7 |     |     | μs    |

| Hold Time for Repeated<br>Start Condition  | t <sub>HD;STA</sub> |                                                                  | 4.0 |     |     | μs    |

| Data Setup Time                            | t <sub>SU;DAT</sub> |                                                                  |     | 300 |     | ns    |

| Data Hold Time                             | t <sub>HD;DAT</sub> |                                                                  |     | 10  |     | ns    |

| Rise Time for SDA and SCL                  | t <sub>R</sub>      |                                                                  |     | 800 |     | ns    |

| Fall Time for SDA and SCL                  | t <sub>F</sub>      |                                                                  |     | 200 |     | ns    |

| Setup Time for a Stop Condition            | t <sub>SU;STO</sub> |                                                                  | 4.0 |     |     | μs    |

# **Electrical Characteristics—I<sup>2</sup>C (continued)**

(Timing specifications are guaranteed by design and not production tested.)

| PARAMETER                                        | SYMBOL              | CONDITIONS                                        | MIN  | TYP | MAX | UNITS |

|--------------------------------------------------|---------------------|---------------------------------------------------|------|-----|-----|-------|

| Bus Free Time Between a Stop and Start Condition | t <sub>BUS</sub>    |                                                   | 4.7  |     |     | μs    |

| Data Valid Time                                  | t <sub>VD;DAT</sub> |                                                   | 3.45 |     |     | μs    |

| Data Valid Acknowledge Time                      | t <sub>VD;ACK</sub> |                                                   | 3.45 |     |     | μs    |

| FAST MODE                                        |                     |                                                   |      |     |     |       |

| Output Fall Time                                 | t <sub>OF</sub>     | From V <sub>IH(MIN)</sub> to V <sub>IL(MAX)</sub> |      | 150 |     | ns    |

| Pulse Width Suppressed by Input Filter           | t <sub>SP</sub>     |                                                   |      | 75  |     | ns    |

| SCL Clock Frequency                              | f <sub>SCL</sub>    |                                                   | 0    |     | 400 | kHz   |

| Low Period SCL Clock                             | t <sub>LOW</sub>    |                                                   | 1.3  |     |     | μs    |

| High Time SCL Clock                              | t <sub>HIGH</sub>   |                                                   | 0.6  |     |     | μs    |

| Setup Time for Repeated<br>Start Condition       | t <sub>SU;STA</sub> |                                                   | 0.6  |     |     | μs    |

| Hold Time for Repeated Start<br>Condition        | t <sub>HD;STA</sub> |                                                   | 0.6  |     |     | μs    |

| Data Setup Time                                  | t <sub>SU;DAT</sub> |                                                   |      | 125 |     | ns    |

| Data Hold Time                                   | t <sub>HD;DAT</sub> |                                                   |      | 10  |     | ns    |

| Rise Time for SDA and SCL                        | $t_{R}$             |                                                   |      | 30  |     | ns    |

| Fall Time for SDA and SCL                        | $t_{F}$             |                                                   |      | 30  |     | ns    |

| Setup Time for a Stop Condition                  | t <sub>SU;STO</sub> |                                                   | 0.6  |     |     | μs    |

| Bus Free Time Between a Stop and Start Condition | t <sub>BUS</sub>    |                                                   | 1.3  |     |     | μs    |

| Data Valid Time                                  | t <sub>VD;DAT</sub> |                                                   | 0.9  |     |     | μs    |

| Data Valid Acknowledge Time                      | t <sub>VD;ACK</sub> |                                                   | 0.9  |     |     | μs    |

Figure 1. I<sup>2</sup>C Timing Diagram

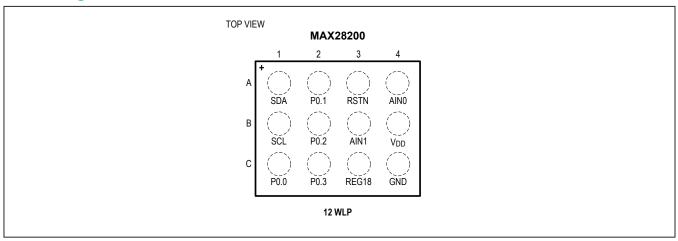

# **Pin Configuration**

# **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | SDA             | I <sup>2</sup> C Slave Data                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A2  | P0.1            | Digital GPIO. Alternately, this pin can be configured as a PWM output.                                                                                                                                                                                                                                                                                                                                                                                                              |

| A3  | RSTN            | Digital, Active-Low Reset Input. The device remains in reset as long as this pin is low and begins executing from the utility ROM at address 8000h when this pin returns to a high state. The pin includes pullup current source; if this pin is driven by an external device, it should be driven by an open-drain source capable of sinking in excess of 4mA. This pin can be left unconnected if there is no need to place the device in a reset state using an external signal. |

| A4  | AIN0            | Analog-to-Digital Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B1  | SCL             | I <sup>2</sup> C Slave Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| B2  | P0.2            | Digital GPIO. Alternately, this pin can be configured as CMP comparator negative input.                                                                                                                                                                                                                                                                                                                                                                                             |

| В3  | AIN1            | Analog-to-Digital Input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

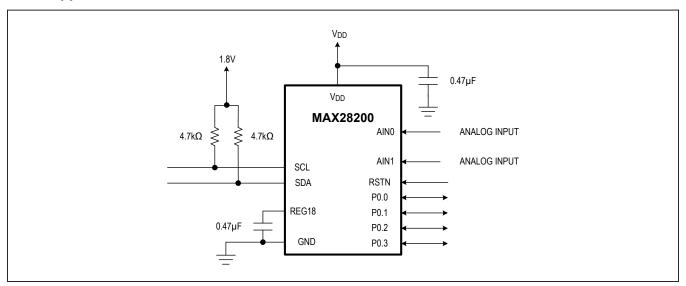

| B4  | V <sub>DD</sub> | Supply Voltage. This pin must be connected to ground through a 0.47µF external ceramic chip capacitor. The capacitor must be placed as close as possible to this pin.                                                                                                                                                                                                                                                                                                               |

| C1  | P0.0            | Digital GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C2  | P0.3            | Digital GPIO. Alternately, this pin can be configured as CMP comparator positive input.                                                                                                                                                                                                                                                                                                                                                                                             |

| СЗ  | REG18           | 1.8V Regulator Output. This pin must be connected to ground through a 0.47µF external ceramic chip capacitor. The capacitor must be placed as close as possible to this pin. No devices other than the capacitor should be connected to this pin.                                                                                                                                                                                                                                   |

| C4  | GND             | Ground. Connect directly to the ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## **Detailed Description**

The MAX28200 is a low-power, 16-bit MAXQ microcontroller ( $\mu$ C) designed for low-power applications including smartphones and consumer electronics. The device combines a powerful 16-bit RISC  $\mu$ C with a SP 800-185 compliant secure hash algorithm (SHA-3) challenge and response authentication system, 10-bit, 93.75ksps ADC, along with an I<sup>2</sup>C communications port. A general-purpose comparator can be configured for differential measurement or single-ended using the bandgap 1.23V as a reference. The device includes 4 GPIO pins.

The device includes 16KB of flash memory and 2KB of data SRAM. Additional utility ROM space includes macros such as an I<sup>2</sup>C bootloader to enable flash memory firmware updates in the field.

For the ultimate in low-power, battery-operated performance, the device includes an ultra-low-power stop mode (0.2 $\mu$ A typ). In this mode, the minimum amount of circuitry is powered. The device wakes up on a matching I<sup>2</sup>C address. Wake-up sources also include external interrupts, the power-fail warning, and a wake-up timer interrupts. The  $\mu$ C runs from a wide 1.71V to 3.63V operating voltage.

#### Microprocessor

The device is based on Maxim's low-power, 16-bit MAXQ20. The core supports the Harvard memory architecture with separate 16-bit program and data address buses. A fixed 16-bit instruction word is standard, but data can be arranged in 8 or 16 bits. The MAXQ core in the device is implemented as a pipe-lined processor with performance approaching 1MIPS per MHz. The 16-bit data path is implemented around register modules, and each register module contributes specific functions to the core. The accumulator module consists of sixteen 16-bit registers and is tightly coupled with the arithmetic logic unit (ALU). A configurable soft stack supports program flow.

Execution of instructions is triggered by data transfer between functional register modules or between a functional register module and memory. Because data movement involves only source and destination modules, circuit switching activities are limited to active modules only. For power-conscious applications, this approach localizes power dissipation and minimizes switching noise. The modular architecture also provides maximum flexibility and reusability that are important for a microprocessor used in embedded applications.

The MAXQ instruction set is highly orthogonal. All arithmetical and logical operations can use any register in conjunction with the accumulator. Data movement is supported from any register to any other register. Memory is accessed through specific data-pointer registers with autoincrement/decrement support.

#### Memory

This device includes several memory types:

- 16KB flash memory

- 2KB SRAM data memory

- Dedicated utility ROM, including I<sup>2</sup>C bootloader

- Soft stack

### **Operating Modes**

The lowest power mode of operation is stop mode. In this mode, CPU state and memories are preserved, but the CPU is not actively running. Wake-up sources include I<sup>2</sup>C address match, external I/O interrupts, the power-fail warning interrupt, wake-up timer, or a power-fail reset. Any time the microcontroller is in a state where code does not need to be executed, the user software can put the device into stop mode. The nanopower ring oscillator is an internal ultra low-power (400nA) 8kHz ring oscillator that can be used to drive a wake-up timer that exits stop mode. The wakeup timer is programmable by software in steps of 125µs up to approximately 8s.

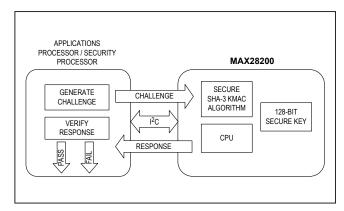

#### **SHA-3 Authentication**

The MAX28200 contains an SP 800-185 compliant hardware SHA-3 KMAC engine with preprogrammed 128-bit secret key for challenge and response secure authentication.

Figure 2. SHA-3 Authentication

#### **ADC**

The two-channel, 10-bit delta-sigma analog-to-digital converter (ADC) provides an integrated reference generator (bandgap).

#### I<sup>2</sup>C

The device supports the I<sup>2</sup>C slave protocol. The I<sup>2</sup>C bus is a 2-wire, bidirectional bus using a serial data line (SDA) and a serial clock line (SCL). Signals SDA and SCL are open-drain, allowing multiple devices to reside on the same bus. The microprocessor core can be awakened from its stop mode when an I<sup>2</sup>C address match (factory-programmed address) is received. External pullup resistors are required to pull the lines to a logic-high state.

An I<sup>2</sup>C master has ownership of the I<sup>2</sup>C bus, drives the clock, and generates the required protocol signals. This allows it to send data to a slave or receive data from a slave as required. One exception is when the MAX28200 performs clock-stretching. Slave devices that need some time to process a received byte or are not ready yet to send the next byte can pull the SCL low to signal to the master that it should wait. Once the clock is released the master can proceed with the next byte.

Alternatively, the device supports a technique where the master can effectively poll the device for the ACK bit to determine when the device is ready to send or receive more data bytes. To use this technique, clock-stretching must first be disabled and then the slave must pull down the SDA line during the acknowledge clock pulse so that it remains stable low during the high period of this clock pulse. When a slave does not acknowledge (NACK) a received data byte, the data line must be left high by the slave. The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer. Should the master choose to generate a repeated START condition and transmit the device address, it can then wait for the device to respond with ACK pulling down the SDA line during the ACK clock pulse.

The device also supports a direct memory access (DMA) mode of operation. When active, I<sup>2</sup>C slave read and write accesses will allow 256 bytes of system SRAM to be accessed directly by the I<sup>2</sup>C interface. The contiguous 256 byte block can be positioned anywhere within the 2Kbyte memory space on 256 byte boundaries. SRAM data is accessed one byte at a time. The I<sup>2</sup>C master controls the SRAM address written and read through a locally maintained pointer. The pointer must be initialized by the first data byte write following an initial START, with a DMA address, and the R/W bit indicating a write

operation. The initial START is defined as the first access after reset, or the first START issued after a STOP. The DMA state machine detects this sequence and directs the first byte of write data to the address pointer. All subsequent write or read data is directed to or from the SRAM. The pointer is incremented after any SRAM read or write operation, but can be reloaded at any time by issuing the STOP→START sequence.

The device supports two read modes. The default mode begins reading data during the I<sup>2</sup>C address acknowledge bit time. Data is read until the Tx FIFO is full. The DMA continues reading a new byte of data as soon as a byte is read from the FIFO. In this read ahead mode, unread data remains in the FIFO after the I<sup>2</sup>C master terminates the transaction. It is up to the host microcontroller to manage the residual data in the FIFO, by either letting it remain for the next read transaction or flushing the data from the FIFO. The second mode is an I2C EEPROM compatibility mode. In this mode, the DMA reads a single byte of SRAM data following an address ACK, and reads one additional byte after receipt of each master sourced TX\_DATA (read) acknowledge. If a NACK is received following a TX DATA operation, the read for the next byte of data is not initiated.

SRAM DMA writes are initiated once the entire byte is received through an I<sup>2</sup>C write. Writes are initiated one byte at a time, during the ACK bit time, once the data has been received. Writes are absolute and there is no bounds checking performed by the DMA if a address roll-over condition occurs.

#### **PWM/Timer**

The device provides a PWM/Timer as an alternate function on one of the GPIO pins. The PWM/Timer is an enhanced timer with modifications to support different input clock prescaling and set/reset/compare output functionality:

- 16-bit timer/counter

- 16-bit up/down autoreload

- Counter function of external pulse

- 16-bit timer with capture

- 16-bit timer with compare

- Input/output enhancements for pulse-width modulation

- Set/reset/toggle output state on comparator match

- Prescaler with 2n divider (for n = 0, 2, 4, 6, 8, 10)

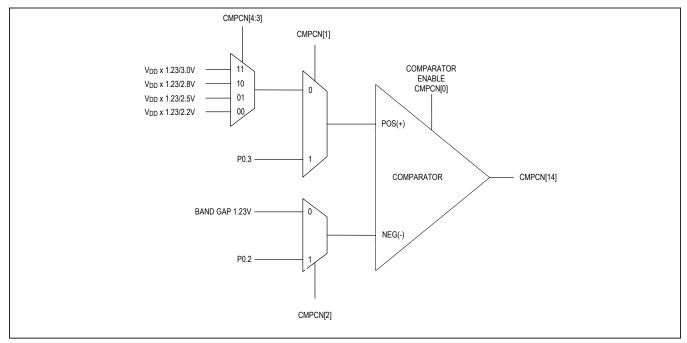

## Comparator

The comparator provided can be configured for differential measurement or single-ended comparison to the bandgap 1.23V reference. The comparator is also used to provide the power-fail warning voltage indicator. Interrupts can be generated when a comparator event is detected with the transition direction of the monitored signal being programmable.

#### **GPIO**

The microcontroller provides four port pins for general-purpose I/O that have the following features:

- · CMOS output drivers

- · Schmitt trigger inputs

- Optional weak pullup to V<sub>DD</sub> when operating in input mode

While the microcontroller is in a reset state, P0.1, P0.2, and P0.3 have weak pullups and their input buffers are disabled. P0.0 has a weak pulldown and its input buffer is disabled.

## System Clock

The device provides an internal 12MHz oscillator that requires no external components, thereby reducing system cost, PCB area, and radiated EMI.

#### **Watchdog Timer**

The internal watchdog timer greatly increases system reliability. The watchdog timer resets the device if software execution is disturbed. The watchdog timer is a free-running counter designed to be periodically reset by the application software. If software is operating correctly, the software periodically resets the counter so it never reaches its maximum count. However, if software operation is interrupted and the counter is not reset, a system reset is triggered and optionally a watchdog timer interrupt. This protects the system against electrical noise or electrostatic discharge (ESD) upsets that could cause uncontrolled processor operation. The internal watchdog timer is an upgrade to older designs with external watchdog devices, reducing system cost and simultaneously increasing reliability.

The watchdog timer functions as the source of both the watchdog timer timeout and the watchdog timer reset. The timeout period can be programmed in a range of 2<sup>15</sup> to 2<sup>24</sup> system clock cycles. An interrupt is generated when the timeout period expires if the interrupt is enabled. All watchdog timer resets follow the programmed interrupt timeouts by 512 system clock cycles. If the watchdog timer is not restarted for another full interval in this time period, a system reset occurs when the reset timeout expires. See Table 1

Figure 3. Comparator Configuration

**Table 1. Watchdog Timer Settings**

| WD<br>(CD = 00) | PERIOD                           | INTERRUPT<br>(F <sub>CK</sub> = 12MHZ) | RESET<br>(F <sub>CK</sub> = 12MHZ) |

|-----------------|----------------------------------|----------------------------------------|------------------------------------|

| 00              | 2 <sup>15</sup> /f <sub>CK</sub> | 2.7ms                                  | 2.7ms + 42.7µs                     |

| 01              | 2 <sup>18</sup> /f <sub>CK</sub> | 21.9ms                                 | 21.9ms + 42.7µs                    |

| 10              | 2 <sup>21</sup> /f <sub>CK</sub> | 174.7ms                                | 174.7ms + 42.7µs                   |

| 11              | 2 <sup>24</sup> /f <sub>CK</sub> | 1.4s                                   | 1.4s + 42.7µs                      |

# **Typical Application Circuits**

# **Basic Application**

# **Ordering Information**

| PART          | TEMP<br>RANGE  | PIN-<br>PACKAGE |

|---------------|----------------|-----------------|

| MAX28200EWC+T | -40°C to +85°C | 12 WLP          |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

# **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 8/18          | Initial release | _                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for 16-bit Microcontrollers - MCU category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

M30302FCPFP#U3

MB90F036APMC-GSE1

MB90F428GCPFR-GSE1

MB96F683RBPMC-GSAE1

R5F10MMGDFB#30

R5F111PGGFB#30

R5F117BCGNA#20

DF3026XBL25V

DF36014GFTV

DF36024GFTV

DF36034GFPV

R5F11B7EANA#U0

R5F21172DSP#U0

MB90092PF-G-BNDE1

MB90F335APMC1-G-SPE1

MB90F345CAPFR-GSE1

MB90F568PMCR-GSE1

GE1

MB90F882ASPMC-GE1

MB96F395RSAPMC-GSE2

DF36024GFXV

UPD78F1018F1-BA4-A

MB96F018RBPMC-GSE1

MB90F867ASPFR-GE1

DF2239FA20IV

R5F117BCGFP#30

LC88F58B0AU-SQFPH

MB90F548GPF-GE1

MB90214PF-GT-310-BND-AE1

MB90F342CESPQC-GSE2

MB90F428GAPF-GSE1

ML620Q504H-NNNTBWBX

UPD78F1500AGK-GAK-AX

HD64F3337SF16V

MB90F428GCPF-GSE1

MB90F342ESPMC-G-JNE1

MB90022PF-GS-358E1

MB96F395RWAPMC-GSE2

MB96395RSAPMC-GS-110E2

MB90F883CSPMC-GE1

S912ZVHY64F1VLQ

ST10F280

MB96F338RSAPMCR-GK5E2

CY90096PF-G-002-BND-ERE1

ML62Q1569-NNNGAZ0AX

NNGAZ0AX

ML62Q1739-NNNGAZ0AX

ML62Q1749-NNNGAZ0AX

ML62Q1559-NNNGAZ0AX