# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

# **General Description**

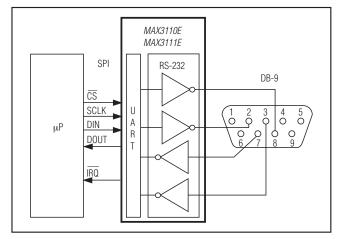

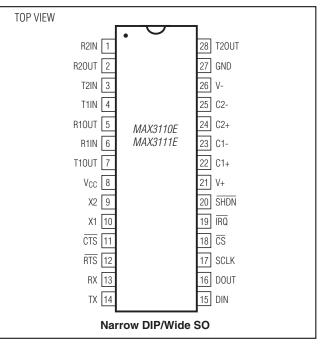

The MAX3110E/MAX3111E combine a full-featured universal asynchronous receiver/transmitter (UART) with  $\pm 15$ kV ESD-protected RS-232 transceivers and integrated charge-pump capacitors into a single 28-pin package for use in space-, cost-, and power-constrained applications. The MAX3110E/MAX3111E also feature an SPI/QSPI<sup>TM</sup>/MICROWIRE®-compatible serial interface to save additional board space and microcontroller ( $\mu$ C) I/O pins.

A proprietary low-dropout output stage enables the 2-driver/2-receiver interface to deliver true RS-232 performance down to  $V_{CC} = +3V$  (+4.5V for MAX3110E) while consuming only 600µA. The receivers remain active in a hardware/software-invoked shutdown, allowing external devices to be monitored while consuming only 10µA. Each device is guaranteed to operate at up to 230kbps while maintaining true EIA/TIA-232 output voltage levels.

The MAX3110E/MAX3111E's UART includes a crystal oscillator and baud-rate generator with software-programmable divider ratios for all common baud rates from 300baud to 230kbaud. The UART features an 8-word-deep receive FIFO that minimizes processor overhead and provides a flexible interrupt with four maskable sources. Two control lines (one input and one output) are included for hardware handshaking.

The UART and RS-232 functions can be used together or independently since the two functions share only supply and ground connections (the MAX3110E/ MAX3111E are hardware- and software-compatible with the MAX3100 and MAX3222E).

## **Applications**

Point-of-Sale (POS) Devices

- Handy-Terminals

- Telecom/Networking Diagnostic Ports

- Industrial Front-Panel Interfaces

- Hand-Held/Battery-Powered Equipment

## Pin Configuration appears at end of data sheet.

†Covered by U.S. Patent numbers 4,636,930; 4,679,134; 4,777,577; 4,797,899; 4,809,152; 4,897,774; 4,999,761; and other patents pending.

QSPI is a trademark of Motorola, Inc. MICROWIRE is a registered trademark of National Semiconductor Corp.

## **Benefits and Features**

- Integration Reduces Cost and Board Space

- Integrated RS-232 Transceiver and UART in a Single 28-Pin Package Guaranteed 230kbps Data Rate SPI/QSPI/MICROWIRE-Compatible µC Interface

- Internal Charge-Pump Capacitors—No External Components Required

- Low-Power Operation Reduces Thermal Dissipation

- True RS-232 Operation Down to V<sub>CC</sub> = +3V (MAX3111E)

- Single-Supply Operation

- +5V (MAX3110E)

- +3.3V (MAX3111E)

- 600µA Supply Current

- 10µA Shutdown Supply Current with Receiver Interrupt Active

- Hardware/Software-Compatible with MAX3100 and MAX3222E

# **Ordering Information**

| PART        | TEMP.<br>RANGE | PIN-<br>PACKAGE | V <sub>CC</sub><br>(V) |

|-------------|----------------|-----------------|------------------------|

| MAX3110ECWI | 0°C to +70°C   | 28 Wide SO      | 5                      |

| MAX3110ECNI | 0°C to +70°C   | 28 Plastic DIP  | 5                      |

Ordering Information continued at end of data sheet.

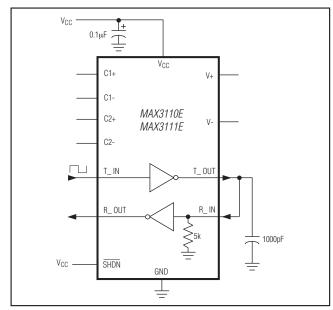

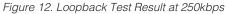

# **Typical Application Circuit**

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

## **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND (MAX3110E) | 0.3V to +6V                      |

|-----------------------------------|----------------------------------|

| V <sub>CC</sub> to GND (MAX3111E) |                                  |

| V+ to GND (Note 1)                | -0.3V to +7V                     |

| V- to GND (Note 1)                | +0.3V to -7V                     |

| V+ to V- (Note 1)                 | +13V                             |

| Input Voltages to GND             |                                  |

| CS, X1, CTS, RX, DIN, SCLK        | 0.3V to (V <sub>CC</sub> + 0.3V) |

| T_IN, SHDN                        | 0.3V to +6V                      |

| R_IN                              | ±25V                             |

| Output Voltage to GND             |                                  |

| DOUT, <u>RTS</u> , TX, X2         | 0.3V to (V <sub>CC</sub> + 0.3V) |

| ĪRQ                               | -0.3V to +6V                     |

| T_OUT                             | ±13.2V                           |

| R_OUT                             | 0.3V to (V <sub>CC</sub> + 0.3V) |

| TX, RTS Output Current            |                                  |

|                                   |                                  |

| Short-Circuit Duration                                 |

|--------------------------------------------------------|

| X2, DOUT, IRQ (to V <sub>CC</sub> or GND)Continuous    |

| T_OUT (to GND)Continuous                               |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )  |

| 28-pin Wide SO (derate 12.5mW/°C above +70°C)1W        |

| 28-pin Plastic DIP (derate 14.3mW/°C above +70°C)1.14W |

| Operating Temperature Ranges                           |

| MAX311_EC 0°C to +70°C                                 |

| MAX311_EE40°C to +85°C                                 |

| Storage Temperature Range65°C to +150°C                |

| Lead Temperature (soldering, 10s)+300°C                |

| Soldering Temperature (reflow)                         |

| PDIP lead(Pb)-free+225°C                               |

| PDIP containing lead(Pb)+240°C                         |

| Wide SO lead(Pb)-free+225°C                            |

| Wide SO containing lead(Pb)+240°C                      |

|                                                        |

Note 1: V+ and V- can have maximum magnitudes of 7V, but their absolute difference should not exceed 13V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Electrical Characteristics—MAX3110E**

(V<sub>CC</sub> = +4.5V to +5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are measured for baud rate set to 9600baud at V<sub>CC</sub> = +5V,  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                                          | PARAMETER SYMBOL CONDIT     |                                    |                      |                    |       | MAX                | UNITS |

|----------------------------------------------------|-----------------------------|------------------------------------|----------------------|--------------------|-------|--------------------|-------|

| DC CHARACTERISTICS (V <sub>CC</sub> =              | +5V, T <sub>A</sub> = +25°C | )                                  |                      |                    |       |                    |       |

| Supply Current                                     | Icc                         | $\overline{SHDN} = V_{CC}$ , no lo |                      | 0.6                | 2     | mA                 |       |

| Supply Current with Hardware Shutdown              | ICCSHDN(H)                  | SHDN = GND (Not                    | e 3)                 |                    | 0.48  | 1                  | mA    |

| Supply Current with Hardware and Software Shutdown | ICCSHDN(H+S)                | SHDN = GND, SHI                    | DNi bit = 1 (Note 4) |                    | 3     | 20                 | μΑ    |

| UART OSCILLATOR INPUT (X1                          | )                           |                                    |                      |                    |       |                    |       |

| Input High Voltage                                 | V <sub>IH1</sub>            |                                    |                      | 0.7V <sub>CC</sub> |       |                    | V     |

| Input Low Voltage                                  | VIL1                        |                                    |                      |                    |       | 0.2V <sub>CC</sub> | V     |

| Input Current                                      | linia                       | V <sub>X1</sub> = 0 or 5.5V        | SHDNi bit = 0        |                    |       | 25                 |       |

| Input Current                                      | liN1                        | $v_{X1} = 0.015.5v$                | SHDNi bit = 1        |                    |       | 2                  | μA    |

| Input Capacitance                                  | C <sub>IN1</sub>            |                                    |                      |                    | 5     |                    | рF    |

| UART LOGIC INPUTS (DIN, SCI                        | K, CS, CTS, RX)             |                                    |                      |                    |       |                    |       |

| Input High Voltage                                 | VIH2                        |                                    |                      | 0.7V <sub>CC</sub> |       |                    | V     |

| Input Low Voltage                                  | VIL2                        |                                    |                      |                    |       | 0.3Vcc             | V     |

| Input Hysteresis                                   | V <sub>HYST2</sub>          |                                    |                      |                    | 250   |                    | mV    |

| Input Leakage Current                              | I <sub>LKG1</sub>           |                                    |                      |                    |       | ±1                 | μΑ    |

| Input Capacitance                                  | C <sub>IN2</sub>            |                                    |                      |                    | 5     |                    | рF    |

| RS-232 LOGIC INPUTS (T_IN, S                       | HDN)                        |                                    |                      |                    |       |                    |       |

| Input High Voltage                                 | V <sub>IH3</sub>            | $V_{CC} = 5V$                      |                      | 2.4                |       |                    |       |

| Input Low Voltage                                  | VIL3                        |                                    |                      |                    |       | 0.8                | V     |

| Transmitter Input Hysteresis V <sub>HYST3</sub>    |                             |                                    |                      |                    | 500   |                    | mV    |

| Input Leakage Current                              | I <sub>IN3</sub>            |                                    |                      |                    | ±0.01 | ±1                 | μΑ    |

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

# **Electrical Characteristics—MAX3110E (continued)**

(V<sub>CC</sub> = +4.5V to +5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are measured for baud rate set to 9600baud at V<sub>CC</sub> = +5V,  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                       | SYMBOL            | CONDITIONS                                                                 | MIN       | TYP   | MAX | UNITS |

|---------------------------------|-------------------|----------------------------------------------------------------------------|-----------|-------|-----|-------|

| RS-232 RECEIVER INPUTS (R       | _IN)              | -                                                                          | <u> </u>  |       |     |       |

| Input Voltage Range             |                   |                                                                            | -25       |       | +25 | V     |

| Input High Voltage              | V <sub>IH4</sub>  | $T_A = +25^{\circ}C, V_{CC} = 5V$                                          | 2.4       |       |     | V     |

| Input Low Voltage               | VIL4              | $T_A = +25^{\circ}C, V_{CC} = 5V$                                          |           |       | 0.8 | V     |

| Input Hysteresis                | VHYST4            |                                                                            |           | 500   |     | mV    |

| Input Resistance                | R <sub>IN</sub>   | $T_A = +25^{\circ}C$                                                       | 3         | 5     | 7   | kΩ    |

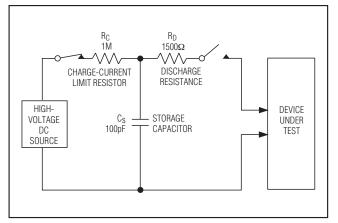

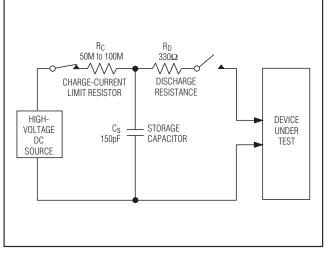

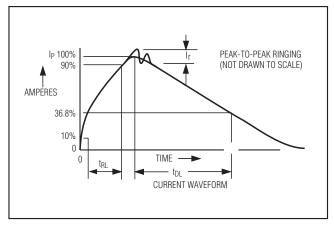

| RS-232 ESD PROTECTION (R_       | IN, T_OUT)        |                                                                            | <b>I</b>  |       |     |       |

|                                 |                   | Human Body Model                                                           |           | ±15   |     |       |

| ESD Protection                  |                   | IEC 1000-4-2 Air Discharge                                                 |           | ±15   |     | kV    |

|                                 |                   | IEC 1000-4-2 Contact Discharge                                             |           | ±8    |     |       |

| <b>RS-232 RECEIVER OUTPUTS</b>  | (R_OUT)           |                                                                            |           |       |     | 1     |

| Output High Voltage             |                   |                                                                            |           | ±0.05 | ±10 | μA    |

| Output Low Voltage              | VOL1              | I <sub>SINK</sub> = 1.6mA                                                  |           |       | 0.4 | V     |

| <b>RS-232 TRANSMITTER OUTPL</b> | JTS (T_OUT)       |                                                                            | I         |       |     | 1     |

| Output Voltage Swing            |                   | $3k\Omega$ load on all transmitter outputs                                 | 5         | ±5.4  |     | V     |

| Output Resistance               | Ro                | $V_{CC} = V + = V - = 0, V_{OUT} = \pm 2V$                                 | 300       | 10M   |     | Ω     |

| Output Short-Circuit Current    |                   |                                                                            |           |       | ±60 | mA    |

| Output Leakage Current          | ILKG2             | $V_{CC} = 0 \text{ or } 5.5V, V_{OUT} = \pm 12V,$<br>transmitters disabled |           |       | ±25 | μA    |

| UART OUTPUTS (DOUT, TX, R       | TS)               |                                                                            | I         |       |     | 1     |

| Output Leakage Current          | I <sub>LKG3</sub> | DOUT only, $\overline{CS} = V_{CC}$                                        |           |       | ±1  | μΑ    |

| Output High Voltage             | \/                | ISOURCE = 5mA; DOUT, RTS                                                   | Vcc - 0.5 | 5     |     | V     |

| Output High voltage             | V <sub>OH2</sub>  | ISOURCE = 10mA; TX only                                                    | Vcc - 0.5 | 5     |     | V     |

| Output Low Voltage              | Voia              | I <sub>SINK</sub> = 4mA; DOUT, RTS                                         |           |       | 0.4 | V     |

| Output Low Voltage              | V <sub>OL2</sub>  | I <sub>SINK</sub> = 25mA; TX only                                          |           |       | 0.9 | v     |

| Output Capacitance              | Cout1             |                                                                            |           | 5     |     | pF    |

| UART IRQ OUTPUTS (IRQ = op      | pen drain)        |                                                                            |           |       |     |       |

| Output Leakage Current          | I <sub>LKG4</sub> | $V \overline{IRQ} = 5.5 V$                                                 |           |       | ±1  | μΑ    |

| Output Low Voltage              | V <sub>OL3</sub>  | I <sub>SINK</sub> = 4mA                                                    |           |       | 0.4 | V     |

| Output Capacitance              | C <sub>OUT2</sub> |                                                                            |           | 5     |     | pF    |

| UART AC TIMING                  |                   |                                                                            |           |       |     |       |

| CS Low to DOUT Valid            | t <sub>DV</sub>   | $C_{LOAD} = 100 pF$                                                        |           |       | 100 | ns    |

| CS High to DOUT Tri-State       | tTR               | $C_{LOAD} = 100 \text{pF}, R_{\overline{CS}} = 10 \text{k}\Omega$          |           |       | 100 | ns    |

| CS to SCLK Setup Time           | tcss              |                                                                            | 100       |       |     | ns    |

| CS to SCLK Hold Time            | tCSH              |                                                                            | 0         |       |     | ns    |

| SCLK Fall to DOUT Valid         | tDO               | $C_{LOAD} = 100 pF$                                                        |           |       | 100 | ns    |

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

# **Electrical Characteristics—MAX3110E (continued)**

(V<sub>CC</sub> = +4.5V to +5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are measured for baud rate set to 9600baud at V<sub>CC</sub> = +5V,  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                          | SYMBOL                                                                                                 | COND                                                                                        | ITIONS                              | MIN | ТҮР | MAX | UNITS  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------|-----|-----|-----|--------|--|

| DIN to SCLK Setup Time                                                                                                                                                                                                                                                                                                                                                                                                                             | t <sub>DS</sub>                                                                                        |                                                                                             |                                     | 100 |     |     | ns     |  |

| DIN to SCLK Hold Time                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>DH</sub>                                                                                        |                                                                                             |                                     | 0   |     |     | ns     |  |

| SCLK Period                                                                                                                                                                                                                                                                                                                                                                                                                                        | tCP                                                                                                    |                                                                                             |                                     | 238 |     |     | ns     |  |

| SCLK High Time                                                                                                                                                                                                                                                                                                                                                                                                                                     | tсн                                                                                                    |                                                                                             |                                     | 100 |     |     | ns     |  |

| SCLK Low Time                                                                                                                                                                                                                                                                                                                                                                                                                                      | tCL                                                                                                    |                                                                                             |                                     | 100 |     |     | ns     |  |

| SCLK Rising Edge to CS Falling                                                                                                                                                                                                                                                                                                                                                                                                                     | tcso                                                                                                   |                                                                                             |                                     | ns  |     |     |        |  |

| SCLK Low TimetcL100SCLK Rising Edge to $\overline{CS}$ Fallingtcso100 $\overline{CS}$ Rising Edge to SCLK Rising<br>EdgetcS1200 $\overline{CS}$ High Pulse WidthtcSu200Output Rise TimetrTX, $\overline{RTS}$ , DOUT; $C_L = 100pF$ 10Output Fall TimetfTX, $\overline{RTS}$ , DOUT, $\overline{IRQ}$ ; $C_L = 100pF$ 10RS-232 AC TIMINGRL = 3k $\Omega$ , $C_L = 100pF$ ,<br>one transmitter switching250tehuReceiver input to receiver output150 |                                                                                                        |                                                                                             |                                     |     |     | ns  |        |  |

| CS High Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                                                | tcsw                                                                                                   |                                                                                             |                                     | 200 |     |     | ns     |  |

| Output Rise Time                                                                                                                                                                                                                                                                                                                                                                                                                                   | tr                                                                                                     | TX, RTS, DOUT; CL                                                                           | C <sub>L</sub> = 100pF 10           |     |     |     |        |  |

| Output Fall Time                                                                                                                                                                                                                                                                                                                                                                                                                                   | t <sub>f</sub> TX, $\overline{\text{RTS}}$ , DOUT, $\overline{\text{IRQ}}$ ; C <sub>L</sub> = 100pF 10 |                                                                                             |                                     |     |     |     | ns     |  |

| RS-232 AC TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |                                                                                             |                                     | -   |     |     |        |  |

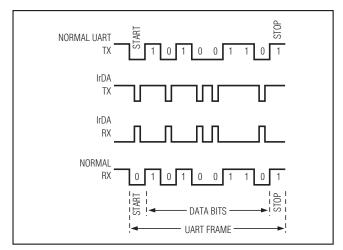

| Maximum Data Rate                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                        |                                                                                             |                                     | 250 |     |     | kbps   |  |

| Desciver Presention Delay                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>t</b> PHL                                                                                           | Receiver input to re                                                                        | eceiver output                      |     | 150 |     |        |  |

| Receiver Propagation Delay                                                                                                                                                                                                                                                                                                                                                                                                                         | t <sub>PLH</sub>                                                                                       | $C_{L} = 150 pF$                                                                            |                                     |     | 150 |     | ns     |  |

| Transmitter Skew                                                                                                                                                                                                                                                                                                                                                                                                                                   | Itphl - tplhI                                                                                          | (Note 5)                                                                                    |                                     |     | 100 |     | ns     |  |

| Receiver Skew                                                                                                                                                                                                                                                                                                                                                                                                                                      | Itphl - tplhI                                                                                          |                                                                                             |                                     |     | 50  |     | ns     |  |

| Transition-Region Slew Rate                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                        | $V_{CC} = 5V,$<br>$R_L = 3k\Omega$ to $7k\Omega,$<br>$T_A = +25^{\circ}C,$<br>measured from | C <sub>L</sub> = 150pF to<br>1000pF | 6   |     | 30  | V/µs   |  |

| Hanshor-negion diew hale                                                                                                                                                                                                                                                                                                                                                                                                                           | sition-Hegion Slew Hate                                                                                |                                                                                             | C <sub>L</sub> = 150pF to 4         |     |     |     | - v/µs |  |

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

## **Electrical Characteristics—MAX3111E**

(V<sub>CC</sub> = +3.0V to +3.6V, V<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are measured for baud rate set to 9600baud at V<sub>CC</sub> = +3.3V, T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                          | SYMBOL                         | CON                                       | DITIONS                                                    | MIN                | TYP   | MAX                | UNITS |

|----------------------------------------------------|--------------------------------|-------------------------------------------|------------------------------------------------------------|--------------------|-------|--------------------|-------|

| DC CHARACTERISTICS (V <sub>CC</sub> =              | = 3.3V, T <sub>A</sub> = +25°C | ;)                                        |                                                            | 1                  |       |                    |       |

| Supply Current                                     | ICC                            | $\overline{SHDN} = V_{CC}$ , no l         | oad                                                        |                    | 0.45  | 1.4                | mA    |

| Supply Current with Hardware Shutdown              | ICCSHDN(H)                     | SHDN = GND (No                            | te 3)                                                      |                    | 0.18  | 0.4                | mA    |

| Supply Current with Hardware and Software Shutdown | ICCSHDN(H+S)                   | $\overline{\text{SHDN}} = \text{GND SHE}$ | DNi bit = 1 (Note 4)                                       |                    | 1     | 20                 | μA    |

| UART OSCILLATOR INPUT (X                           | 1)                             |                                           |                                                            |                    |       |                    |       |

| Input High Voltage                                 | VIH1                           |                                           |                                                            | 0.7V <sub>CC</sub> |       |                    | V     |

| Input Low Voltage                                  | VIL1                           |                                           |                                                            |                    |       | 0.2V <sub>CC</sub> | V     |

| Input Current                                      | l <sub>IN1</sub>               | V <sub>X1</sub> = 0 or 3.6V               | V <sub>X1</sub> = 0 or 3.6V SHDNi bit = 0<br>SHDNi bit = 1 |                    |       | 25<br>2            | μA    |

| Input Capacitance                                  | C <sub>IN1</sub>               |                                           |                                                            |                    | 5     |                    | рF    |

| UART LOGIC INPUTS (DIN, SC                         | LK, CS, RX)                    |                                           |                                                            |                    |       |                    |       |

| Input High Voltage                                 | VIH2                           |                                           |                                                            | 0.7V <sub>CC</sub> |       |                    | V     |

| Input Low Voltage                                  | V <sub>IL2</sub>               |                                           |                                                            |                    |       | 0.3V <sub>CC</sub> | V     |

| Input Hysteresis                                   | V <sub>HYST2</sub>             |                                           |                                                            |                    | 165   |                    | mV    |

| Input Leakage Current                              | I <sub>LKG1</sub>              |                                           |                                                            |                    |       | ±1                 | μA    |

| Input Capacitance                                  | C <sub>IN2</sub>               |                                           |                                                            |                    | 5     |                    | рF    |

| RS-232 LOGIC INPUTS (T_IN,                         | SHDN)                          |                                           |                                                            |                    |       |                    |       |

| Input High Voltage                                 | VIH3                           | $V_{CC} = 3.3V$                           |                                                            | 2.0                |       |                    | V     |

| Input Low Voltage                                  | V <sub>IL3</sub>               |                                           |                                                            |                    |       | 0.8                | V     |

| Transmitter Input Hysteresis                       | V <sub>HYST3</sub>             |                                           |                                                            |                    | 500   |                    | mV    |

| Input Leakage Current                              | I <sub>IN3</sub>               |                                           |                                                            |                    | ±0.01 | ±1                 | μA    |

| RS-232 RECEIVER INPUTS (R                          | IN)                            |                                           |                                                            |                    |       |                    |       |

| Input Voltage Range                                |                                |                                           |                                                            | -25                |       | +25                | V     |

| Input High Voltage                                 | VIH4                           | $T_A = +25^{\circ}C, V_{CC} =$            | = 3.3V                                                     | 2.4                |       |                    | V     |

| Input Low Voltage                                  | VIL4                           | $T_A = +25^{\circ}C, V_{CC} =$            | = 3.3V                                                     |                    |       | 0.6                | V     |

| Input Hysteresis                                   | V <sub>HYST4</sub>             |                                           |                                                            |                    | 500   |                    | mV    |

| Input Resistance                                   | R <sub>IN</sub>                | $T_A = +25^{\circ}C$                      |                                                            | 3                  | 5     | 7                  | kΩ    |

| RS-232 ESD PROTECTION (R_                          | IN, T_OUT)                     |                                           |                                                            |                    |       |                    |       |

|                                                    |                                | Human Body Mod                            | el                                                         |                    | ±15   |                    |       |

| ESD Protection                                     |                                | IEC 1000-4-2 Air E                        | Discharge                                                  |                    | ±15   |                    | kV    |

|                                                    |                                | IEC 1000-4-2 Con                          | tact Discharge                                             |                    | ±8    |                    | ĺ     |

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

# **Electrical Characteristics—MAX3111E (continued)**

(V<sub>CC</sub> = +3.0V to +3.6V, V<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are measured for baud rate set to 9600baud at V<sub>CC</sub> = +3.3V, T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                          | SYMBOL            | CONDITION                                                            | MIN                   | TYP  | MAX | UNITS |

|----------------------------------------------------|-------------------|----------------------------------------------------------------------|-----------------------|------|-----|-------|

| RS-232 RECEIVER OUTPUTS (                          | R_OUT)            | -                                                                    |                       |      |     |       |

| Output High Voltage                                | V <sub>OH1</sub>  | I <sub>SOURCE</sub> = 1mA                                            | V <sub>CC</sub> - 0.6 |      |     | V     |

| Output Low Voltage                                 | VOL1              | I <sub>SINK</sub> = 1.6mA                                            |                       |      | 0.4 | V     |

| <b>RS-232 TRANSMITTER OUTPU</b>                    | TS (T_OUT)        |                                                                      |                       |      |     | 1     |

| Output Voltage Swing                               |                   | $3k\Omega$ load on all transmitter outputs                           | ±5                    | ±5.4 |     | V     |

| Output Resistance                                  | Ro                | $V_{CC} = V + = V - = 0, V_{OUT} = \pm 2V$                           | 300                   | 10M  |     | Ω     |

| Output Short-Circuit Current                       |                   |                                                                      |                       |      | ±60 | mA    |

| Output Leakage Current                             | I <sub>LKG2</sub> | $V_{CC} = 0$ or 3.6V, $V_{OUT} = \pm 12V$ ,<br>transmitters disabled |                       |      | ±25 | μA    |

| UART OUTPUTS (DOUT, TX, R                          | TS)               |                                                                      |                       |      |     |       |

| Output Leakage Current                             | I <sub>LKG3</sub> | DOUT only; $\overline{CS} = V_{CC}$                                  |                       |      | ±1  | μA    |

| Output High Voltage                                | Voue              | I <sub>SOURCE</sub> = 5mA; DOUT, RTS                                 | V <sub>CC</sub> - 0.5 |      |     | V     |

| Output High voltage                                | VOH2              | ISOURCE = 10mA, TX only                                              | V <sub>CC</sub> - 0.5 |      |     | 1     |

| Output Low Voltage                                 | Vol2              | $I_{SINK} = 4mA; DOUT, \overline{RTS}$                               |                       |      | 0.4 | V     |

| Output Low Voltage                                 | VOL2              | $I_{SINK} = 25 mA$ , TX only                                         |                       |      | 0.9 |       |

| Output Capacitance                                 | Cout1             |                                                                      |                       | 5    |     | pF    |

| UART IRQ OUTPUT (IRQ = open                        | n drain)          |                                                                      |                       |      |     |       |

| Output Leakage Current                             | I <sub>LKG4</sub> | $V_{\overline{IRQ}} = 3.6V$                                          |                       |      | ±1  | μA    |

| Output Low Voltage                                 | V <sub>OL3</sub>  | I <sub>SINK</sub> = 4mA                                              |                       |      | 0.4 | V     |

| Output Capacitance                                 | C <sub>OUT2</sub> |                                                                      |                       | 5    |     | pF    |

| UART AC TIMING                                     | 1                 | - I                                                                  |                       |      |     |       |

| CS Low to DOUT Valid                               | t <sub>DV</sub>   | $C_{LOAD} = 100 pF$                                                  |                       |      | 100 | ns    |

| CS High to DOUT Tri-State                          | t <sub>TR</sub>   | $C_{LOAD} = 100 \text{pF}, R_{\overline{CS}} = 10 \text{k}\Omega$    |                       |      | 100 | ns    |

| CS to SCLK Setup Time                              | tcss              |                                                                      | 100                   |      |     | ns    |

| CS to SCLK Hold Time                               | tCSH              |                                                                      | 0                     |      |     | ns    |

| SCLK Fall to DOUT Valid                            | tdo               | $C_{LOAD} = 100 pF$                                                  |                       |      | 100 | ns    |

| DIN to SCLK Setup Time                             | t <sub>DS</sub>   |                                                                      | 100                   |      |     | ns    |

| DIN to SCLK Hold Time                              | t <sub>DH</sub>   |                                                                      | 0                     |      |     | ns    |

| SCLK Period                                        | tCP               |                                                                      | 238                   |      |     | ns    |

| SCLK High Time                                     | tсн               |                                                                      | 100                   |      |     | ns    |

| SCLK Low Time                                      | t <sub>CL</sub>   |                                                                      | 100                   |      |     | ns    |

| SCLK Rising Edge to $\overline{\text{CS}}$ Falling | tCSO              |                                                                      | 100                   |      |     | ns    |

| CS Rising Edge to SCLK Rising Edge                 | tCS1              |                                                                      | 200                   |      |     | ns    |

| CS High Pulse Width                                | tcsw              |                                                                      | 200                   |      |     | ns    |

| Output Rise Time                                   | tr                | TX, $\overline{\text{RTS}}$ , DOUT; C <sub>LOAD</sub> = 100pF        |                       | 10   |     | ns    |

| Output Fall Time                                   | t <sub>f</sub>    | TX, RTS, DOUT, IRQ; CLOAD = 100pF                                    |                       | 10   |     | ns    |

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

# **Electrical Characteristics—MAX3111E (continued)**

(V<sub>CC</sub> = +3.0V to +3.6V, V<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are measured for baud rate set to 9600baud at V<sub>CC</sub> = +3.3V, T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                   | SYMBOL                                                 | COND                                                                                                                    | MIN                                 | TYP | MAX  | UNITS |      |

|-----------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----|------|-------|------|

| RS-232 AC TIMING            |                                                        |                                                                                                                         |                                     |     |      |       |      |

| Maximum Data Rate           | $R_L = 3k\Omega$ , $C_L = 100$<br>one-transmitter swit | 250                                                                                                                     |                                     |     | kbps |       |      |

| Pagaivar Propagation Dalay  | t <sub>PHL</sub>                                       | Receiver input to re                                                                                                    | ceiver output                       |     | 150  |       | ns   |

| Receiver Propagation Delay  | t <sub>PLH</sub>                                       | $C_L = 150 pF$                                                                                                          |                                     | 150 |      | 1 115 |      |

| Transmitter Skew            | Itphl - tplhI                                          | (Note 5)                                                                                                                |                                     | 200 |      | ns    |      |

| Receiver Skew               | Itphl - tplhI                                          |                                                                                                                         |                                     |     | 100  |       | ns   |

| Transition-Region Slew Rate |                                                        | $\label{eq:VCC} \begin{array}{l} V_{CC}=3.3V,\\ R_L=3k\Omega \text{ to }7k\Omega,\\ T_A=+25^\circ\text{C}, \end{array}$ | C <sub>L</sub> = 150pF to<br>1000pF | 6   |      | 30    | V/µs |

| Transition-negion olew hate |                                                        | measured from<br>+3V to -3V or<br>-3V to +3V                                                                            | C <sub>L</sub> = 150pF to<br>2500pF | 4   |      | 30    | v/µs |

Note 2: All currents into the device are positive; all currents out of the device are negative. All voltages are referred to device ground unless otherwise noted.

**Note 3:** I<sub>CCSHDN(H)</sub> represents a hardware-only shutdown. In hardware shutdown, the UART is in normal operation and the charge pumps for the RS-232 transmitters are shut down.

Note 4: I<sub>CCSHDN(H+S)</sub> represents a simultaneous software and hardware shutdown in which the UART and charge pumps are shut down.

Note 5: Transmitter skew is measured at the transmitter zero cross points.

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

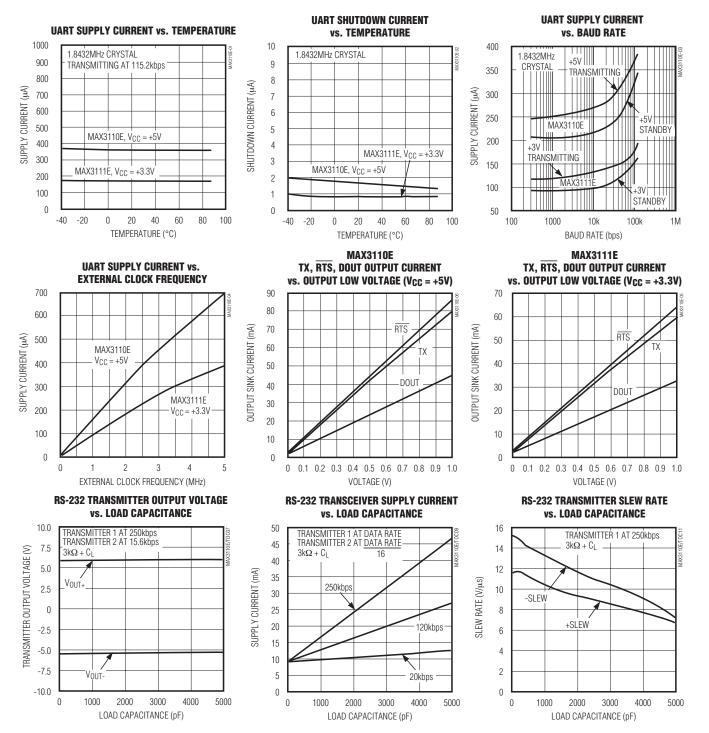

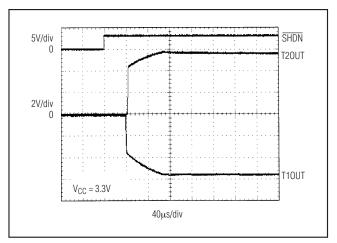

# **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

www.maximintegrated.com

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

# **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                         |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | R2IN  | RS-232 Receiver Input 2                                                                                                                                                          |

| 2   | R2OUT | RS-232 Receiver Output 2, TTL/CMOS                                                                                                                                               |

| 3   | T2IN  | RS-232 Transmitter Input 2, TTL/CMOS                                                                                                                                             |

| 4   | T1IN  | RS-232 Transmitter Input 1, TTL/CMOS                                                                                                                                             |

| 5   | R1OUT | RS-232 Receiver Output 1, TTL/CMOS                                                                                                                                               |

| 6   | R1IN  | RS-232 Receiver Input 1                                                                                                                                                          |

| 7   | T1OUT | RS-232 Transmitter Output 1                                                                                                                                                      |

| 8   | Vcc   | Positive Supply Voltage                                                                                                                                                          |

| 9   | X2    | UART Crystal Connection. Leave X2 unconnected when using an external CMOS clock. See the <i>Crystals, Oscillators, and Ceramic Resonators</i> section.                           |

| 10  | X1    | UART Crystal Connection. X1 also serves as an external CMOS clock input. See the <i>Crystals, Oscillators, and Ceramic Resonators</i> section.                                   |

| 11  | CTS   | UART Clear-to-Send Active-Low Input. Read via the CTS bit.                                                                                                                       |

| 12  | RTS   | UART Request-to-Send Active-Low Output. Controlled by the RTS bit. Also used to control the driver enable in RS-485 networks.                                                    |

| 13  | RX    | UART Asynchronous Serial-Data (receiver) Input. The serial information received from the RS-232 receiver. A transition on RX while in shutdown generates an interrupt (Table 1). |

| 14  | TX    | UART Asynchronous Serial-Data (transmitter) Output                                                                                                                               |

| 15  | DIN   | SPI/MICROWIRE Serial-Data Input. Schmitt-trigger Input.                                                                                                                          |

| 16  | DOUT  | SPI/MICROWIRE Serial-Data Output. High impedance when $\overline{CS}$ is high.                                                                                                   |

| 17  | SCLK  | SPI/MICROWIRE Serial-Clock Input. Schmitt-trigger input.                                                                                                                         |

| 18  | CS    | UART Active-Low Chip-Select Input. DOUT goes high impedance when $\overline{CS}$ is high. $\overline{IRQ}$ , TX, and $\overline{RTS}$ are always active. Schmitt-trigger input.  |

| 19  | ĪRQ   | UART Active-Low Interrupt Output. Open-drain interrupt output to microprocessor.                                                                                                 |

| 20  | SHDN  | Hardware Shutdown Input. Drive SHDN low to shut down the RS-232 transmitters and charge pump. Drive high for normal operation.                                                   |

| 21  | V+    | +5.5V generated by the internal charge pump. Do not make any connection to this terminal.                                                                                        |

| 22  | C1+   | Positive terminal of the internal voltage-doubler charge-pump capacitor. Do not make any connection to this terminal.                                                            |

| 23  | C1-   | Negative terminal of the internal voltage-doubler charge-pump capacitor. Do not make any connection to this terminal.                                                            |

| 24  | C2+   | Positive terminal of internal inverting charge-pump capacitor. Do not make any connection to this terminal.                                                                      |

| 25  | C2-   | Negative terminal of internal inverting charge-pump capacitor. Do not make any connection to this terminal.                                                                      |

| 26  | V-    | -5.5V generated by the internal charge pump. Do not make any connection to this terminal.                                                                                        |

| 27  | GND   | Ground                                                                                                                                                                           |

| 28  | T2OUT | RS-232 Transmitter Output 2                                                                                                                                                      |

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

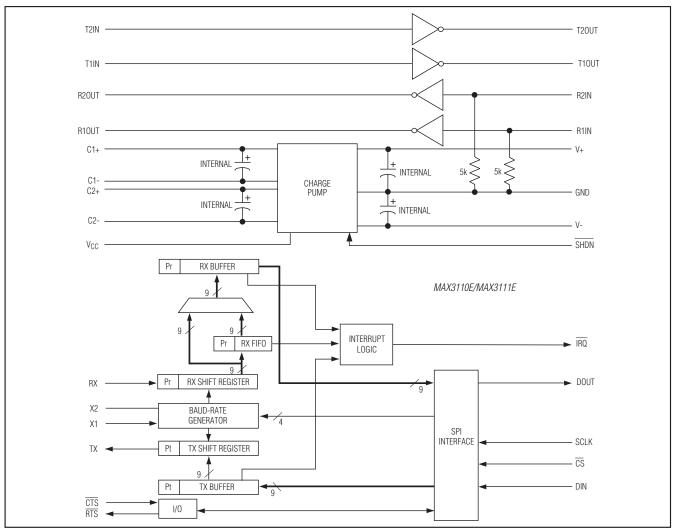

Figure 1. MAX3110E/MAX3111E Functional Diagram

## **Detailed Description**

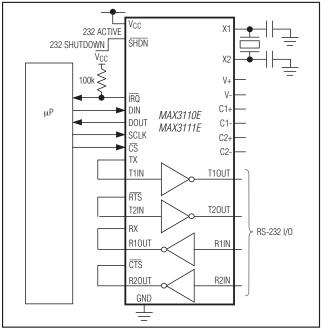

The MAX3110E/MAX3111E contain an SPI/QSPI/MICROWIREcompatible UART and an RS-232 transceiver with two drivers and two receivers. The UART is compatible with SPI and QSPI for CPOL = 0 and CPHA = 0. The UART supports data rates up to 230kbaud for standard UART bit streams as well as IrDA and includes an 8-word receive FIFO. Also included is a 9-bit-address recognition interrupt.

The RS-232 transceiver has electrostatic discharge (ESD) protection on the transmitter outputs and the receiver inputs. The internal charge-pump capacitors minimize the number of external components required. The RS-232 transceivers meet EIA/TIA-232 specifica-

tions for  $V_{CC}$  down to the minimum supply voltage and are guaranteed to operate for data rates up to 250kbps.

The UART and RS-232 functions operate as one device or independently since the two functions share only supply and ground connections.

## UART

The universal asynchronous receiver transmitter (UART) interfaces the SPI/QSPI/MICROWIRE-compatible synchronous serial data from a microprocessor ( $\mu$ P) to asynchronous, serial-data communication ports (RS-232, IrDA). Figure 1 shows the MAX3110E/MAX3111E functional diagram. Included in the UART function is an SPI/QSPI/MICROWIRE interface, a baud-rate generator, and an interrupt generator.

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

## **SPI Interface**

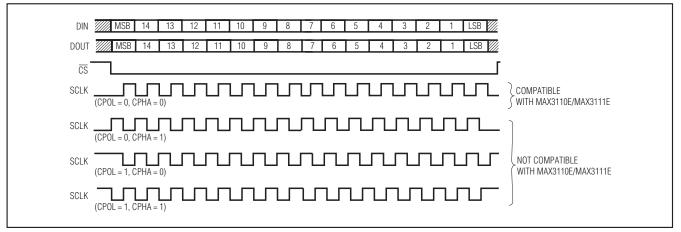

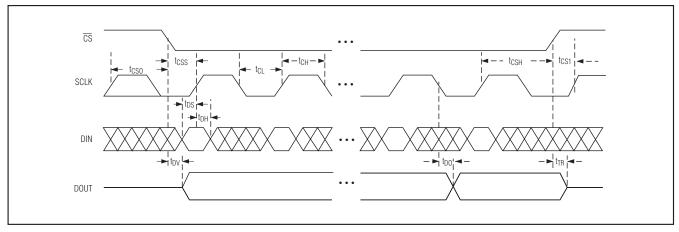

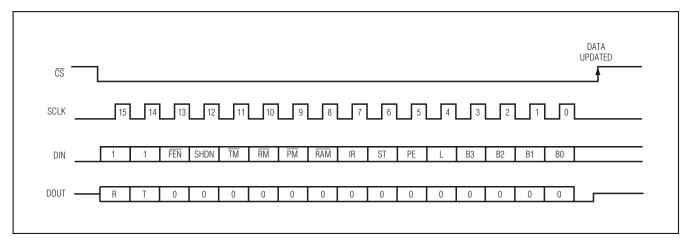

The MAX3110E/MAX3111E are compatible with SPI, QSPI (CPOL = 0, CPHA = 0), and MICROWIRE serialinterface standards (Figure 2). The MAX3110E/ MAX3111E have a unique full-duplex-only architecture that expects a 16-bit word for DIN and simultaneously produces a 16-bit word for DOUT regardless of which read/write register is used. The DIN stream is monitored for its first two bits to tell the UART the type of data transfer being executed (see the *Write Configuration Register*, *Read Configuration Register*, *Write Data Register*, and *Read Data Register* sections). DIN (MOSI) is latched on SCLK's rising edge. DOUT (MISO) should be read into the  $\mu$ P on SCLK's rising edge. The first bit (bit 15) of DOUT transitions on  $\overline{CS}$ 's falling edge, and bits 14–0 transition on SCLK's falling edge. Figure 3 shows the detailed serial timing specifications for the synchronous SPI port.

Only 16-bit words are expected. If  $\overline{CS}$  goes high in the middle of a transmission (any time before the 16th bit), the sequence is aborted (i.e., data does not get written to individual registers). Most operations, such as the clearing of internal registers, are executed only on  $\overline{CS}$ 's rising edge. Every time  $\overline{CS}$  goes low, a new 16-bit stream is expected. An example of using the Write Configuration Register is shown in Figure 4.

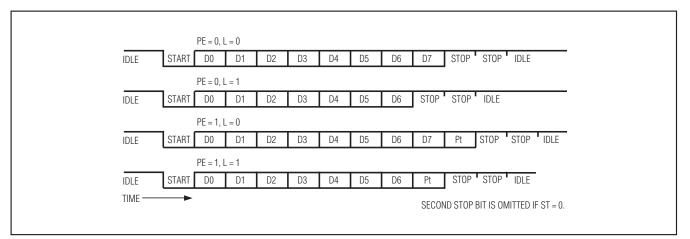

Table 1 describes the bits located in the Write Configuration, Read Configuration, Write Data, and Read Data Registers. This table also describes whether the bit is a read or a write bit and the power-on reset state (POR) of the bits. Figure 5 shows an example of parity and word-length control.

Figure 2. Compatible CPOL and CPHA Timing Modes

Figure 3. Detailed Serial Timing Specifications for the Synchronous SPI Port

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

Figure 4. Write Configuration Register Example

Figure 5. Parity and Word-Length Control

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

| BIT<br>NAME | BIT<br>TYPE | POR<br>STATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                         |

|-------------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B0–B3       | write       | 0000         | Baud-Rate Divisor Select Bits. Sets the baud clock's value (Table 6).                                                                                                                                                                                                                                                               |

| B0–B3       | read        | 0000         | Baud-Rate Divisor Select Bits. Reads the 4-bit baud clock value assigned to these registers.                                                                                                                                                                                                                                        |

| CTS         | read        | No<br>change | Clear-to-Send-Input. Records the state of the $\overline{\text{CTS}}$ pin (CTS bit = 0 implies $\overline{\text{CTS}}$ pin = logic high).                                                                                                                                                                                           |

| D0t–D7t     | write       | XXXXXXXX     | Transmit-Buffer Register. Eight data bits written into the transmit-buffer register. D7t is ignored when $L = 1$ .                                                                                                                                                                                                                  |

| D0r–D7r     | read        | 00000000     | Eight data bits read from the receive FIFO or the receive-buffer register. When L = 1, D7r is always 0.                                                                                                                                                                                                                             |

| FEN         | write       | 0            | FIFO Enable. Enables the receive FIFO when $\overline{\text{FEN}} = 0$ . When $\overline{\text{FEN}} = 1$ , FIFO is disabled.                                                                                                                                                                                                       |

| FEN         | read        | 0            | FIFO-Enable Readback. FEN's state is read.                                                                                                                                                                                                                                                                                          |

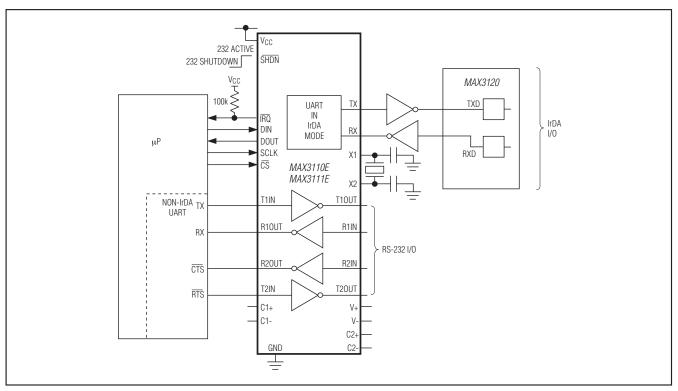

| IR          | write       | 0            | Enables the IrDA timing mode when IR = 1.                                                                                                                                                                                                                                                                                           |

| IR          | read        | 0            | Reads the value of the IR bit.                                                                                                                                                                                                                                                                                                      |

| L           | write       | 0            | Bit to set the word length of the transmitted or received data. $L = 0$ results in 8-bit words (9-bit words if PE = 1) (see Figure 5). $L = 1$ results in 7-bit words (8-bit words if PE = 1).                                                                                                                                      |

| L           | read        | 0            | Reads the value of the L bit.                                                                                                                                                                                                                                                                                                       |

| Pt          | write       | Х            | Transmit-Parity Bit. This bit is treated as an extra bit that is transmitted if PE = 1. In 9-bit net-<br>works, the MAX3110E/MAX3111E do not calculate parity. If PE = 0, then this bit (Pt) is ignored<br>in transmit mode (see the <i>9-Bit Networks</i> section).                                                                |

| Pr          | read        | Х            | Receive-Parity Bit. This bit is the extra bit received if $PE = 1$ . Therefore, $PE = 1$ results in 9-bit transmissions (L = 0). If $PE = 0$ , then Pr is set to 0. Pr is stored in the FIFO with the receive data (see the <i>9-Bit Networks</i> section).                                                                         |

| PE          | write       | 0            | Parity-Enable Bit. Appends the Pt bit to the transmitted data when $PE = 1$ , and sends the Pt bit as written. No parity bit is transmitted when $PE = 0$ . With $PE = 1$ , an extra bit is expected to be received. This data is put into the Pr register. $Pr = 0$ when $PE = 0$ . The MAX3110E/MAX3111E do not calculate parity. |

| PE          | read        | 0            | Reads the value of the Parity-Enable bit.                                                                                                                                                                                                                                                                                           |

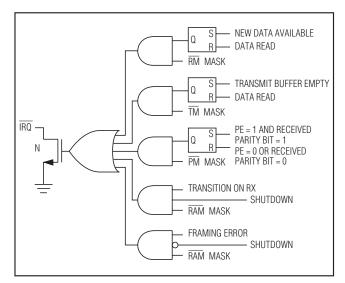

| PM          | write       | 0            | Mask for Pr bit. $\overline{IRQ}$ is asserted if $\overline{PM} = 1$ and Pr = 1 (Table 7).                                                                                                                                                                                                                                          |

| PM          | read        | 0            | Reads the value of the $\overline{PM}$ bit (Table 7).                                                                                                                                                                                                                                                                               |

| R           | read        | 0            | Receive Bit or FIFO Not Empty Flag. R = 1 means new data is available to be read or is being read from the receive register or FIFO. If performing a Read Data or Write Data operation, the R bit will clear on the falling edge of SCLK's 16th pulse if no new data is available.                                                  |

| RM          | write       | 0            | Mask for R bit. $\overline{IRQ}$ is asserted if $\overline{RM} = 1$ and R = 1 (Table 7).                                                                                                                                                                                                                                            |

| RM          | read        | 0            | Reads the value of the $\overline{\text{RM}}$ bit (Table 7).                                                                                                                                                                                                                                                                        |

| RAM         | write       | 0            | Mask for RA/FE bit. $\overline{IRQ}$ is asserted if $\overline{RAM} = 1$ and RA/FE = 1 (Table 7).                                                                                                                                                                                                                                   |

| RAM         | read        | 0            | Reads the value of the $\overline{RAM}$ bit (Table 7).                                                                                                                                                                                                                                                                              |

| RTS         | write       | 0            | Request-to-Send Bit. Controls the state of the $\overline{\text{RTS}}$ output. This bit is reset on power-up (RTS bit = 0 sets the $\overline{\text{RTS}}$ pin = logic high).                                                                                                                                                       |

# Table 1. Bit Descriptions

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

#### RIT BIT POR DESCRIPTION TYPE STATE NAME Receiver-Activity/Framing-Error Bit. In shutdown mode, this is the RA bit. In normal operation, this is the FE bit. In shutdown mode, a transition on RX sets RA = 1. In normal mode, a framing error sets FE = 1. A framing error occurs if a zero is received when the first stop bit is expected. FE is set when a framing error occurs, and cleared upon receipt of the next prop-RA/FE 0 read erly framed character independent of the FIFO being enabled. When the device wakes up, it is likely that a framing error will occur. This error is cleared with a Write Configuration. The FE bit is not cleared on a Read Data operation. When an FE is encountered, the UART resets itself to the state where it is looking for a start bit. Software-Shutdown Bit. Enter software shutdown with a Write Configuration where SHDNi = 1. Software shutdown takes effect after $\overline{CS}$ goes high, and causes the oscillator to stop as soon as the transmitter becomes idle. Software shutdown also clears R, T, RA/FE, D0r-D7r, D0t–D7t, Pr, Pt, and all data in the receive FIFO. RTS and CTS can be read and updated SHDNi write 0 while in shutdown. Exit software shutdown with a Write Configuration where SHDNi = 0. The oscillator restarts typically within 50ms of CS going high. RTS and CTS are unaffected. Refer to the Pin Description for hardware shutdown (SHDN input). Shutdown Read-Back Bit. The Read Configuration register outputs SHDNo = 1 when the UART is in shutdown. Note that this bit is not sent until the current byte in the transmitter is SHDNo read $\cap$ sent (T = 1). This tells the processor when it may shut down the RS-485/RS-422 driver. This bit is also set immediately when the device is shut down through the SHDN pin. Transmit-Stop Bit. One stop bit will be transmitted when ST = 0. Two stop bits will be transmit-ST 0 write ted when ST = 1. The receiver only requires one stop bit. ST read 0 Reads the value of the ST bit. Transmit-Buffer-Empty Flag. T = 1 means that the transmit buffer is empty and ready to Т 1 read accept another data word. Transmit-Enable Bit. If $\overline{TE} = 1$ , then only the $\overline{RTS}$ pin is updated on $\overline{CS}$ 's rising edge. The con-TE 0 write tents of $\overline{\text{RTS}}$ , Pt, and D0t–D7t transmit on $\overline{\text{CS}}$ 's rising edge when $\overline{\text{TE}} = 0$ . ΤM Mask for T Bit. $\overline{IRQ}$ is asserted if $\overline{TM} = 1$ and T = 1 (Table 7). 0 write ΤM 0 Reads the value of the $\overline{TM}$ bit (Table 7). read

# Table 1. Bit Descriptions (continued)

Notice to High-Level Programmers: The UART follows the SPI convention of providing a bidirectional data path for writes and reads. Whenever the data is written, data is also read back. This speeds operation over the SPI bus, and the UART needs this speed advantage when operating at high baud rates. In most high-level languages, such as C, there are commands for writing and reading stream I/O devices such as the console or serial port. In C specifically, there is a "PUTCHAR" command that transmits a character and a "GETCHAR" command that receives a character. If programmers were to write direct write and read commands in C with no underlying driver code, they would notice that a PUTCHAR command is really a PUTGETCHAR command. These C commands assume some form of BIOS-level support for these commands. The proper way to implement these commands is to write driver code, usually in the form of an assembly-language interrupt-service routine and a callable routine used by high-level routines. This driver

handles the interrupts and manages the receive and transmit buffers for the MAX3110E/MAX3111E. When a PUTCHAR executes, this driver is called and it safely buffers any characters received when the current character is transmitted. When a GETCHAR executes, it checks its own receive buffer before getting data from the UART. See the C-language *Outline for a MAX3110E/MAX3111E Software Driver* in Listing 1, which appears at the end of this data sheet.

Listing 1 is a C-language outline of an interrupt-driven software driver that interfaces to a MAX3110E/ MAX3111E, providing an intermediate layer between the bit-manipulation subroutine and the familiar PUTCHAR/GETCHAR subroutines.

The user must supply code for managing the transmit and receive queues as well as the low-level hardware interface itself. The interrupt control hardware must be initialized before this driver is called.

## Write Configuration Register (D15, D14 = 1, 1)

Configure the UART by writing a 16-bit word to the write configuration register, which programs the baud rate, data word length, parity enable, and enable of the 8word receive FIFO. In this mode, bits 15 and 14 of the DIN configuration word are both required to be 1 in order to enable the write configuration mode. Bits 13–0 of the DIN configuration word set the configuration of the UART. Table 2 shows the bit assignment for the write configuration register. The write configuration register allows selection between normal UART timing and IrDA timing, provides shutdown control, and contains four interrupt mask bits.

Using the write configuration register clears the receive FIFO and the R, T, RA/FE, D0r–D7r, D0t–D7t, Pr, and Pt registers. RTS and CTS remain unchanged. The new configuration is valid on  $\overline{CS}$ 's rising edge if the transmit buffer is empty (T = 1) and transmission is over. If the latest transmission has not been completed (T = 0), the registers are updated when the transmission is over.

The write configuration register bits (FEN, SHDNi, IR, ST, PE, L, B3–B0) take effect after the current transmission is over. The mask bits (TM, RM, PM, RAM) take effect immediately after SCLK's 16th rising edge.

Bits 15 and 14 of the DOUT write configuration (R and T) are sent out of the MAX3110E/MAX3111E along with 14 trailing zeros. The use of the R and T bits is optional, but ignore the 14 trailing zeros.

**Warning!** The UART requires stable crystal oscillator operation before configuration (typically ~25ms after power-up). Upon power-up, compare the write configuration bits with the read configuration bits in a software loop until both match. This ensures that the oscillator is stable and that the UART is configured correctly.

## Read Configuration Register (D15, D14 = 0, 1)

The read configuration register is used to read back the last configuration written to the UART. In this register, bits 15 and 14 of the DIN configuration word are required to be 0 and 1, respectively, to enable the read

# SPI/MICROWIRE-Compatible UART and ±15kV ESD-Protected RS-232 Transceivers with Internal Capacitors

configuration mode. Bits 13–1 of the DIN word should be zeros, and bit 0 is the test bit to put the UART in test mode (see the *Test Mode* section). Table 3 shows the bit assignment for the read configuration register.

## **Test Mode**