# Ultra-Low-Power Arm Cortex-M4F with Precision Analog Front-End for Industrial and Medical Sensors

#### **General Description**

The MAX32675 is a highly integrated, mixed-signal, ultralow-power microcontroller for industrial applications and is especially suitable for 4-20mA loop-powered sensors and transmitters. It is based on an ultra-low-power Arm® Cortex®- M4 with Floating Point Unit (FPU) and includes 384KB of flash and 160KB of SRAM. Error correction coding (ECC), capable of single error correction, double error detection (SEC-DED), is implemented over the entire flash, SRAM, and cache to ensure ultra-reliable code execution for demanding applications. An analog front-end (AFE) provides two 12-channel delta-sigma ( $\Delta$ - $\Sigma$ ) ADCs with features and specifications optimized for precision sensor measurement. Each  $\Delta$ - $\Sigma$  ADC can digitize external analog signals as well as system temperature. A PGA with gains of 1x to 128x precedes each ADC. ADC outputs can be optionally converted on the fly from integer to singleprecision floating-point format. A 12-bit DAC is also included. The device also provides robust security features such as an AES Engine, TRNG, and secure boot.

#### **Applications**

- 4-20mA Industrial Sensors and Transmitters

- Industrial Pressure, Temperature, Flow, and Level Sensors/Transmitters

- Medical Pressure, Temperature, and Flow Sensors

#### **Benefits and Features**

- Low-Power, High-Performance for Industrial Applications

- 100MHz Arm Cortex-M4 with FPU

- 384KB Internal Flash

- 160KB SRAM

- 128kB ECC Enabled

- 44.1µA/MHz ACTIVE Mode at 0.9V up to 12MHz Coremark<sup>®</sup>

- 64.5µA/MHz ACTIVE Mode at 1.1V up to 100MHz Coremark

- 2.84µA Full Memory Retention Current in BACKUP Mode at V<sub>DDIO</sub> = 3.3V

- · Ultra-Low-Power Analog Peripherals

- Smart Integration Reduces BOM, Cost, and PCB Size

- Two Δ-Σ ADCs

- · 12 Channels, Assignable to Either ADC

- · Flexible Resolution and Sample Rates

- · 24 Bits at 0.4ksps

- 16 Bits at 4ksps

- 12-Bit DAC

- · On-Die Temperature Sensor

- · Digital Peripherals

- SPI (M/S)

- Up to Two I<sup>2</sup>C

- Up to Two UARTs

- Up to 23 GPIOs

- Timers

- · Up to Five 32-Bit Timers

- · Two Windowed Watchdog Timers

- · 8-Channel Standard DMA Controller

- One I<sup>2</sup>S Slave for Digital Audio Interface

- · Robust Security and Reliability

- TRNG Compliant to SP800-90B

- Secure Nonvolatile Key Storage and AES-128/192/ 256

- Secure Bootloader to Protect IP/Firmware

- Wide, -40°C to +105°C Operating Temperature Range

Ordering Information appears at end of data sheet.

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. CoreMark is a registered trademark of EEMBC. Motorola is a trademark of Motorola Trademark Holdings, LLC.

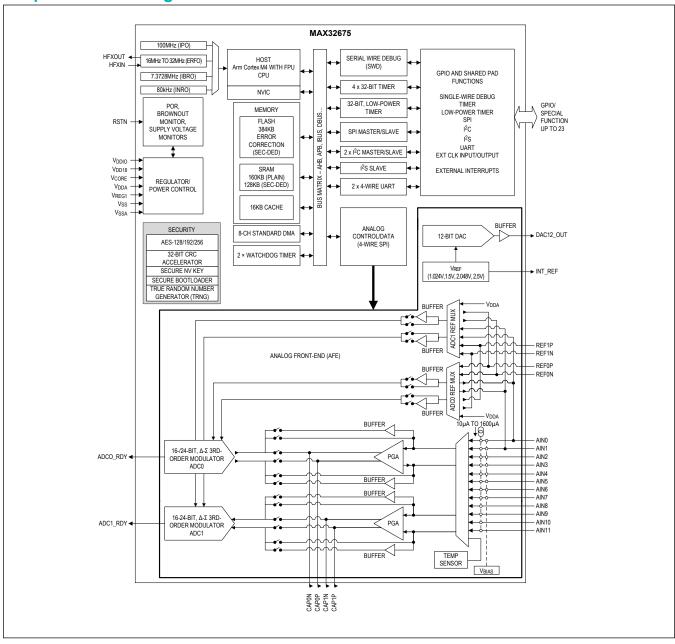

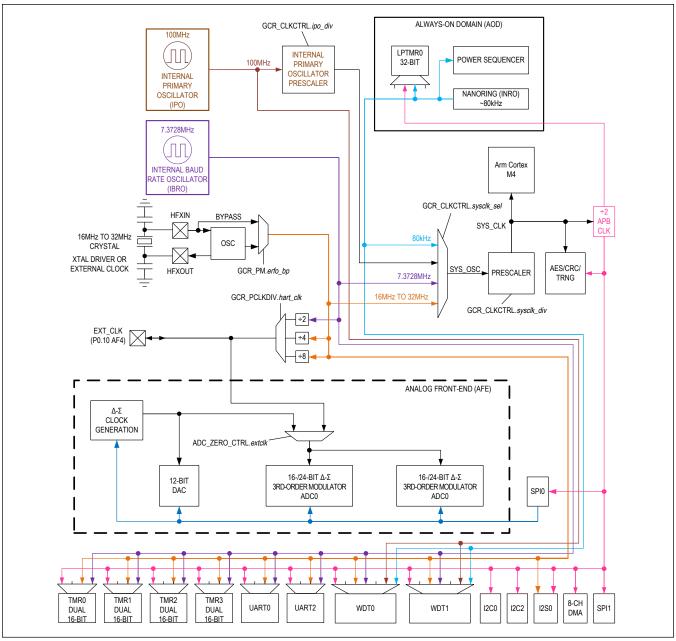

## **Simplified Block Diagram**

## **TABLE OF CONTENTS**

| General Description                                    |    |

|--------------------------------------------------------|----|

| Applications                                           | 1  |

| Benefits and Features                                  | 1  |

| Simplified Block Diagram                               | 2  |

| Absolute Maximum Ratings                               | 7  |

| Package Information                                    |    |

| Electrical Characteristics                             | 7  |

| Electrical Characteristics—16-/24-Bit Δ-Σ ADC with PGA | 17 |

| Electrical Characteristics—12-Bit DAC                  | 26 |

| Electrical Characteristics—Internal Voltage Reference  | 27 |

| Electrical Characteristics—SPI                         |    |

| Electrical Characteristics—I <sup>2</sup> C            |    |

| Electrical Characteristics—I <sup>2</sup> S            | 31 |

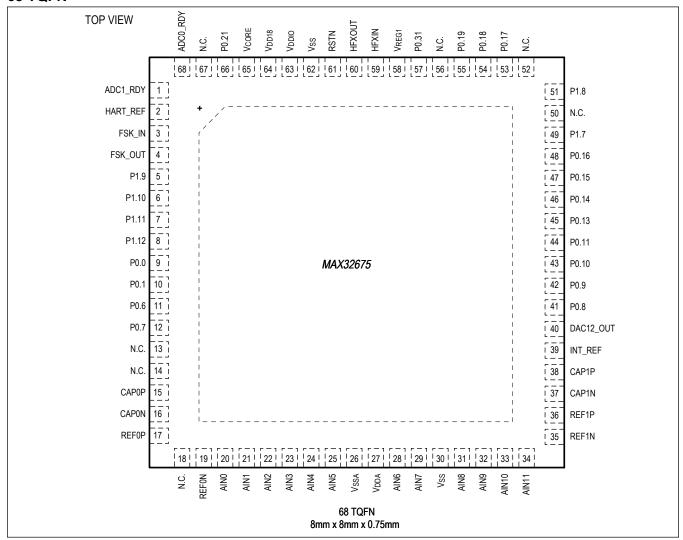

| Pin Configuration                                      |    |

| 68 TQFN                                                | 34 |

| Pin Description                                        | 34 |

| Functional Diagrams                                    | 41 |

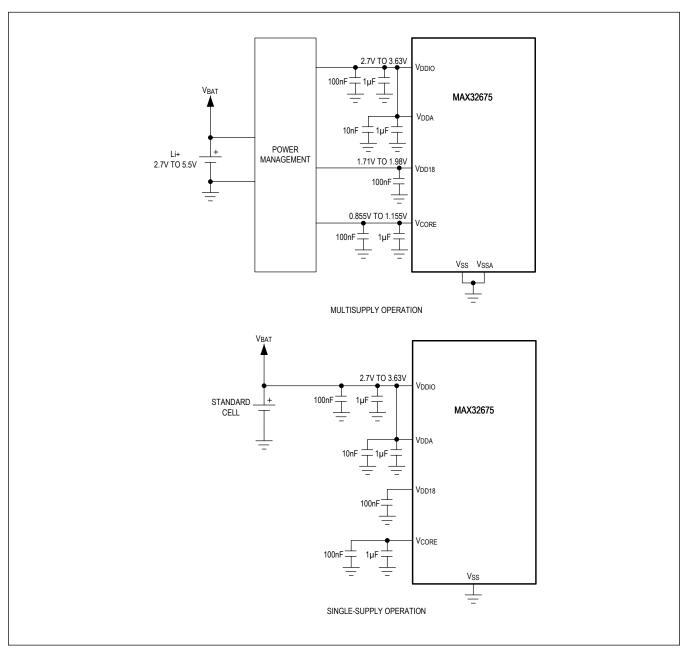

| Power Supply Operational Modes                         | 41 |

| Detailed Description                                   | 42 |

| Arm Cortex-M4 Processor with FPU Engine                | 42 |

| Memory                                                 | 42 |

| Internal Flash Memory                                  | 42 |

| Internal SRAM                                          | 42 |

| Clocking Scheme                                        | 42 |

| General-Purpose I/O and Special Function Pins          | 43 |

| Power Management                                       | 44 |

| Power Management Unit (PMU)                            | 44 |

| ACTIVE Mode                                            | 44 |

| SLEEP Mode                                             | 44 |

| DEEPSLEEP Mode                                         | 44 |

| BACKUP Mode                                            | 44 |

| STORAGE Mode                                           | 45 |

| Standard DMA Controller                                | 45 |

| Windowed Watchdog Timer (WDT)                          | 45 |

| 32-Bit Timer/Counter/PWM (TMR, LPTMR)                  | 46 |

| Serial Peripherals                                     | 46 |

| I <sup>2</sup> C Interface (I2C)                       | 46 |

| Serial Perinheral Interface (SPI)                      | 47 |

# Ultra-Low-Power Arm Cortex-M4F with Precision Analog Front-End for Industrial and Medical Sensors

# TABLE OF CONTENTS (CONTINUED)

| •                                                                                           |    |

|---------------------------------------------------------------------------------------------|----|

| I <sup>2</sup> S Interface (I2S)                                                            | 47 |

| UART                                                                                        | 47 |

| 16-/24-Bit $\Delta$ - $\Sigma$ Analog-to-Digital Converter with Programmable Gain Amplifier | 48 |

| 12-Bit Digital-to-Analog Converter                                                          | 49 |

| Security                                                                                    | 49 |

| AES                                                                                         | 49 |

| True Random Number Generator (TRNG)                                                         | 49 |

| CRC Module                                                                                  | 49 |

| Bootloader                                                                                  | 49 |

| Secure Boot                                                                                 | 50 |

| Debug and Development Interface (SWD)                                                       | 50 |

| Applications Information                                                                    | 51 |

| Bypass Capacitors                                                                           | 51 |

| Bootloader Activation                                                                       | 51 |

| Ordering Information                                                                        | 51 |

| Revision History                                                                            | 52 |

# Ultra-Low-Power Arm Cortex-M4F with Precision Analog Front-End for Industrial and Medical Sensors

|    | LI | 3 | I | L | ) | • | ı | I | ( | 7 | • | U | K | 1 | Ξ | 3 | ) |  |  |  |  |  |  |  |  |

|----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|--|--|--|--|--|

| ١. |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |  |  |  |  |  |

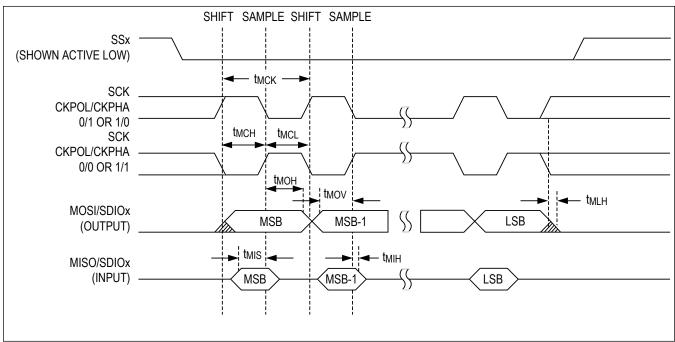

| Figure 1. SPI Master Mode Timing Diagram  |    |

|-------------------------------------------|----|

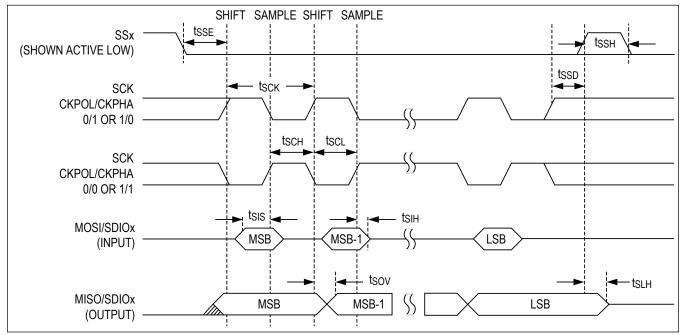

| Figure 2. SPI Slave Mode Timing Diagram   | 32 |

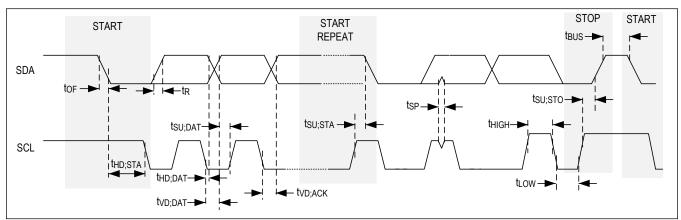

| Figure 3. I <sup>2</sup> C Timing Diagram | 32 |

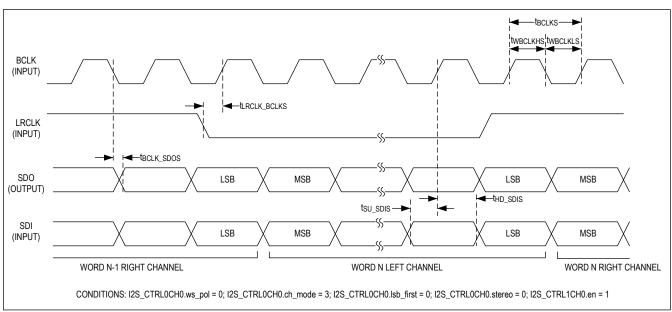

| Figure 4. I <sup>2</sup> S Timing Diagram | 33 |

| Figure 5. Power Supply Operation Modes    | 41 |

| Figure 6. Clocking Scheme Diagram         | 43 |

Maxim Integrated | 5 www.maximintegrated.com

# Ultra-Low-Power Arm Cortex-M4F with Precision Analog Front-End for Industrial and Medical Sensors

| LIST OF TABLES                                  |    |

|-------------------------------------------------|----|

| Table 1. BACKUP Mode RAM Retention              | 45 |

| Table 2. Timer Configuration Options            | 46 |

| Fable 3. I <sup>2</sup> C Configuration Options | 47 |

| Table 4. SPI Configuration Options              | 47 |

| Fable 5. UART Configuration Options             | 48 |

## **Absolute Maximum Ratings**

| (All voltages with respect to V <sub>SS</sub> , unle | ess otherwise noted.)              |

|------------------------------------------------------|------------------------------------|

| V <sub>CORE</sub>                                    | 0.3V to +1.21V                     |

| V <sub>DD18</sub>                                    |                                    |

| AIN[0-11]                                            |                                    |

| V <sub>DDIO</sub> , V <sub>DDA</sub>                 |                                    |

| HFXIN, HFXOUT                                        |                                    |

| RSTN, GPIO, ADC0_RDY, ADC1_RD                        | OY0.3V to V <sub>DDIO</sub> + 0.3V |

| REF1P, REF1N, REF0P, REF0N,                          |                                    |

| CAPON, CAPOP, DAC12 OUT                              | 0.3V to V <sub>DDA</sub> + 0.3V    |

| Total Current into All GPIO Combined                 | l (sink)100mA                      |

| V <sub>SS</sub> , V <sub>SSA</sub>      | 100mA               |

|-----------------------------------------|---------------------|

| Output Current (sink) by Any GPIO Pin   | 25mA                |

| Output Current (source) by Any GPIO Pin | 25mA                |

| Continuous Package Power Dissipation    | 68 TQFN (multilayer |

| board) $T_A = +70^{\circ}C$ ) (derate   | 45.21mW/°C above    |

| +70°C)                                  | 3616.64mW           |

| Operating Temperature Range             | 40°C to +105°C      |

| Storage Temperature Range               | 65°C to +150°C      |

| Soldering Temperature (reflow)          | +260°C              |

|                                         |                     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### **68 TQFN**

| Package Code                           | T6888MK+2      |  |  |  |  |  |  |

|----------------------------------------|----------------|--|--|--|--|--|--|

| Outline Number                         | <u>21-0510</u> |  |  |  |  |  |  |

| Land Pattern Number                    | <u>90-0354</u> |  |  |  |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                |  |  |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 22.12°C/W      |  |  |  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 0.7°C/W        |  |  |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                    | SYMBOL            | CONDITIONS                                                                             | MIN        | TYP | MAX   | UNITS |  |

|------------------------------|-------------------|----------------------------------------------------------------------------------------|------------|-----|-------|-------|--|

| POWER / BOTH SINGLE          | -SUPPLY AND       | MULTISUPPLY OPERATION                                                                  |            |     |       |       |  |

| Supply Voltage, Digital      | V <sub>DDIO</sub> | The V <sub>DDIO</sub> device pin must be connected to the V <sub>DDA</sub> device pin. | 2.7        | 3.3 | 3.63  | V     |  |

|                              | V <sub>DD18</sub> |                                                                                        | 1.71       | 1.8 | 1.98  |       |  |

| Supply Voltage, Core         |                   | OVR = [00]                                                                             | 0.855      | 0.9 | 0.945 |       |  |

|                              | V <sub>CORE</sub> | OVR = [01]                                                                             | 0.95       | 1.0 | 1.05  | V     |  |

|                              |                   | Default OVR = [10]                                                                     | [10] 1.045 |     | 1.155 |       |  |

| Supply Voltage, Analog       | V <sub>DDA</sub>  | The V <sub>DDIO</sub> device pin must be connected to the V <sub>DDA</sub> device pin. | 2.7        | 3.3 | 3.63  | V     |  |

| Dower Feil Beest             |                   | Monitors V <sub>DDIO</sub>                                                             | 1.55       |     | 2.4   |       |  |

| Power-Fail Reset<br>Voltage  | V <sub>RST</sub>  | Monitors V <sub>CORE</sub> during multisupply operation                                | 0.76       |     | 0.86  | V     |  |

| Power On Poset (POP)         |                   | Monitors V <sub>DDIO</sub>                                                             |            | 1.4 |       |       |  |

| Power-On-Reset (POR) Voltage | V <sub>POR</sub>  | Monitors V <sub>CORE</sub> during multisupply operation                                |            | 0.6 |       | V     |  |

## **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                             | SYMBOL               | COND                                                                                                                                                   | MIN                                                                                        | TYP | MAX  | UNITS |           |  |  |

|---------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|------|-------|-----------|--|--|

| POWER / SINGLE-SUPE                   | PLY OPERATION        | (V <sub>DDIO</sub> ONLY)                                                                                                                               |                                                                                            |     |      |       | 1         |  |  |

| V <sub>DDIO</sub> Current ACTIVE Mode |                      | Dynamic, IPO<br>enabled, total<br>current into V <sub>DDIO</sub>                                                                                       | OVR = [10],<br>internal regulator<br>set to 1.1V,<br>fSYS_CLK(MAX) =<br>100MHz             |     | 64.5 |       |           |  |  |

|                                       |                      | pin, V <sub>DDIO</sub> = 3.3V,<br>CPU in ACTIVE<br>mode, executing<br>Coremark, ECC<br>disabled, inputs                                                | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>fSYS_CLK(MAX) =<br>50MHz              |     | 62.5 |       |           |  |  |

|                                       | IDD_DACTS  IDD_FACTS | tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                                                                 | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz  |     | 59.5 |       | μΑ/MHz    |  |  |

|                                       |                      | Dynamic, IPO enabled, total current into V <sub>DDIO</sub> pin, V <sub>DDIO</sub> = 3.3V, CPU in ACTIVE mode, executing While(1), ECC disabled, inputs | OVR = [10],<br>internal regulator<br>set to 1.1V,<br>f <sub>SYS</sub> CLK(MAX) =<br>100MHz |     | 49.4 |       | μενίνιιτε |  |  |

|                                       |                      |                                                                                                                                                        | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>fsys_clk(MAX) =<br>50MHz              |     | 47   |       |           |  |  |

|                                       |                      | tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                                                                 | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz  |     | 44.1 |       | -         |  |  |

|                                       |                      | Fixed, IPO<br>enabled, total<br>current into V <sub>DDIO</sub>                                                                                         | OVR = [10],<br>internal regulator<br>set to 1.1V                                           | r   |      |       |           |  |  |

|                                       |                      | pin, V <sub>DDIO</sub> = 3.3V,<br>CPU in ACTIVE<br>mode, 0MHz<br>execution, ECC                                                                        | OVR = [01],<br>internal regulator<br>set to 1.0V                                           |     | 647  |       | μΑ        |  |  |

|                                       |                      | disabled, inputs<br>tied to V <sub>SS</sub> or<br>V <sub>DDIO</sub> , outputs<br>source/sink 0mA                                                       | OVR = [00],<br>internal regulator<br>set to 0.9V                                           |     | 475  |       |           |  |  |

## **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                          | SYMBOL                | COND                                                                                                                                | ITIONS                                                                                     | MIN TYP | MAX | UNITS  |  |

|----------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|-----|--------|--|

|                                                    |                       | Dynamic, IPO enabled, total                                                                                                         | OVR = [10],<br>internal regulator<br>set to 1.1V                                           | 39.2    |     |        |  |

|                                                    |                       | current into V <sub>DDIO</sub><br>pin, V <sub>DDIO</sub> = 3.3V,<br>CPU in SLEEP<br>mode, ECC<br>disabled, standard<br>DMA with two | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>f <sub>SYS</sub> CLK(MAX) =<br>50MHz  | 37.5    |     |        |  |

|                                                    |                       | channels active, inputs tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                      | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz  | 36.1    |     |        |  |

| V <sub>DDIO</sub> Current SLEEP<br>Mode            | IDD_DSLPS             | Dynamic, IPO enabled, total current into V <sub>DDIO</sub>                                                                          | OVR = [10],<br>internal regulator<br>set to 1.1V,<br>f <sub>SYS</sub> CLK(MAX) =<br>100MHz | 21.1    |     | μA/MHz |  |

|                                                    | I <sub>DD_FSLPS</sub> | pin, V <sub>DDIO</sub> = 3.3V,<br>CPU in SLEEP<br>mode, ECC<br>disabled, DMA<br>disabled, inputs                                    | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>fsys_clk(MAX) =<br>50MHz              | 19      |     |        |  |

|                                                    |                       | tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                                              | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz  | 17.2    |     |        |  |

|                                                    |                       | Fixed, IPO<br>enabled, total<br>current into V <sub>DDIO</sub>                                                                      | OVR = [10],<br>internal regulator<br>set to 1.1V                                           | 796     |     |        |  |

|                                                    |                       | pin, V <sub>DDIO</sub> = 3.3V,<br>CPU in SLEEP<br>mode, ECC<br>disabled, inputs                                                     | OVR = [01],<br>internal regulator<br>set to 1.0V                                           | 647     |     | μΑ     |  |

|                                                    |                       | tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                                              | OVR = [00],<br>internal regulator<br>set to 0.9V                                           | 475     |     |        |  |

| V <sub>DDIO</sub> Fixed Current,<br>DEEPSLEEP Mode | I <sub>DD_FDSLS</sub> | Standby state with<br>full data retention<br>and 160KB SRAM<br>retained                                                             | V <sub>DDIO</sub> = 3.3V                                                                   | 4.0     |     | μА     |  |

| V <sub>DDIO</sub> Fixed Current,<br>BACKUP Mode    | I <sub>DD_FBKUS</sub> | V <sub>DDIO</sub> = 3.3V                                                                                                            | 0KB SRAM<br>retained, retention<br>regulator disabled                                      | 0.32    |     | μА     |  |

## **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                        | SYMBOL                 | CON                               | DITIONS             | MIN | TYP   | MAX | UNITS |  |

|--------------------------------------------------|------------------------|-----------------------------------|---------------------|-----|-------|-----|-------|--|

| V <sub>DDIO</sub> Fixed Current,<br>BACKUP Mode  |                        |                                   | 20KB SRAM retained  |     | 1.04  |     |       |  |

|                                                  | la = ==                | \/ = 2 2\/                        | 40KB SRAM retained  |     | 1.37  |     | 1     |  |

|                                                  | I <sub>DD_</sub> FBKUS | $V_{DDIO} = 3.3V$                 | 80KB SRAM retained  |     | 1.90  |     | - μΑ  |  |

|                                                  |                        |                                   | 160KB SRAM retained |     | 2.84  |     |       |  |

| V <sub>DDIO</sub> Fixed Current,<br>STORAGE Mode | I <sub>DD_FSTOS</sub>  | V <sub>DDIO</sub> = 3.3V          |                     |     | 0.362 |     | μА    |  |

| SLEEP Mode Resume<br>Time                        | t <sub>SLP_ONS</sub>   |                                   |                     |     | 2.1   |     | μs    |  |

| DEEPSLEEP Mode                                   | t                      | fast_wk_en = 1                    |                     |     |       | us  |       |  |

| Resume Time                                      | t <sub>DSL_ONS</sub>   | fast_wk_en = 0                    |                     |     | 129   |     | us    |  |

| BACKUP Mode Resume<br>Time                       | t <sub>BKU_ONS</sub>   | Includes system in execution time | tialization and ROM |     | 1.25  |     | ms    |  |

| STORAGE Mode<br>Resume Time                      | tsto_ons               | Includes system in execution time | tialization and ROM |     | 1.5   |     | ms    |  |

## **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                 | SYMBOL                                                                                                                                | COND                                                                                                                                                                                                | ITIONS                                                                           | MIN | TYP  | MAX | UNITS         |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|------|-----|---------------|

| POWER / MULTISUPPLY                       | Y OPERATION                                                                                                                           |                                                                                                                                                                                                     |                                                                                  |     |      |     |               |

| V <sub>CORE</sub> Current,<br>ACTIVE Mode |                                                                                                                                       | Dynamic, IPO<br>enabled, total<br>current into V <sub>CORE</sub>                                                                                                                                    | OVR = [10],<br>V <sub>CORE</sub> = 1.1V,<br>f <sub>SYS</sub> CLK(MAX) = 100MHz   |     | 63.7 |     |               |

|                                           |                                                                                                                                       | executing Coremark, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                                                                     | OVR = [01], V <sub>CORE</sub><br>= 1.0V,<br>f <sub>SYS</sub> CLK(MAX) =<br>50MHz |     | 61.9 |     |               |

|                                           | ICORE_DACTD                                                                                                                           |                                                                                                                                                                                                     | OVR = [00], V <sub>CORE</sub><br>= 0.9V,<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz |     | 59.4 |     | A /A /A / I = |

|                                           |                                                                                                                                       | Dynamic, IPO enabled, total current into V <sub>CORE</sub> pin, CPU in ACTIVE mode, executing While(1), ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA | OVR = [10], V <sub>CORE</sub><br>= 1.1V,<br>f <sub>SYS</sub> CLK(MAX) = 100MHz   |     | 48.9 |     | - μA/MHz      |

|                                           |                                                                                                                                       |                                                                                                                                                                                                     | OVR = [01], V <sub>CORE</sub><br>= 1.0V,<br>f <sub>SYS</sub> CLK(MAX) =<br>50MHz |     | 46.6 |     |               |

|                                           |                                                                                                                                       |                                                                                                                                                                                                     | OVR = [00], V <sub>CORE</sub><br>= 0.9V,<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz |     | 44.5 |     |               |

|                                           |                                                                                                                                       | Fixed, IPO enabled, total                                                                                                                                                                           | OVR = [10],<br>V <sub>CORE</sub> = 1.1V                                          |     | 362  |     |               |

|                                           |                                                                                                                                       | current into V <sub>CORE</sub> pin, CPU in                                                                                                                                                          | OVR = [01],<br>V <sub>CORE</sub> = 1.0V                                          |     | 217  |     |               |

|                                           | ICORE_FACTD  ACTIVE mode, 0MHz execution, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA | OVR = [00],<br>V <sub>CORE</sub> = 0.9V                                                                                                                                                             |                                                                                  | 109 |      | μΑ  |               |

## **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                         | SYMBOL                                                                                                                                                                                                                | COND                                                                                                                                                                 | ITIONS                                               | MIN  | TYP  | MAX    | UNITS     |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|------|--------|-----------|

|                                   |                                                                                                                                                                                                                       | Dynamic, IPO<br>enabled, total<br>current into V <sub>DDIO</sub>                                                                                                     | OVR = [10],<br>f <sub>SYS_CLK(MAX)</sub> =<br>100MHz |      | 0.51 |        |           |

| V <sub>DDIO</sub> Current, ACTIVE |                                                                                                                                                                                                                       | mode, executing Coremark, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                                | OVR = [01],<br>f <sub>SYS</sub> CLK(MAX) =<br>50MHz  |      | 0.51 |        |           |

|                                   | <b>L</b>                                                                                                                                                                                                              |                                                                                                                                                                      | OVR = [00],<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz  |      | 0.51 |        | A /N/L-1- |

|                                   | IDD_DACTD                                                                                                                                                                                                             | enabled, total current into V <sub>DDIO</sub> pin, V <sub>DDIO</sub> = 3.3V, CPU in ACTIVE mode, executing While(1), ECC disabled, inputs tied to V <sub>SS</sub> or | OVR = [10],<br>f <sub>SYS_CLK(MAX)</sub> =<br>100MHz |      | 0.51 |        | - μA/MHz  |

|                                   |                                                                                                                                                                                                                       |                                                                                                                                                                      | OVR = [01],<br>fsys_clk(MAX) =<br>50MHz              |      | 0.51 |        |           |

|                                   |                                                                                                                                                                                                                       |                                                                                                                                                                      | OVR = [00],<br>f <sub>SYS_CLK(MAX)</sub> =<br>12MHz  |      | 0.51 |        |           |

| Mode                              | enable<br>curren<br>pin, V <sub>I</sub>                                                                                                                                                                               | Fixed, IPO<br>enabled, total<br>current into V <sub>DDIO</sub><br>pin, V <sub>DDIO</sub> = 3.3V,                                                                     | OVR = [10],<br>V <sub>CORE</sub> = 1.1V              |      | 367  |        |           |

|                                   |                                                                                                                                                                                                                       |                                                                                                                                                                      | OVR = [01],<br>V <sub>CORE</sub> = 1.0V              |      | 367  |        |           |

| IDD_FACTD  ICORE_DSLPD            | I <sub>DD_FACTD</sub>                                                                                                                                                                                                 | CPU in ACTIVE mode, 0MHz execution, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                      | OVR = [00],<br>V <sub>CORE</sub> = 0.9V              |      | 307  |        | μА        |

|                                   | Dynamic, IPO enabled, total current into V <sub>CORE</sub> pin, CPU in SLEEP mode, ECC disabled, standard DMA with two channels active, inputs tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA | OVR = [10],<br>V <sub>CORE</sub> = 1.1V,<br>f <sub>SYS</sub> CLK(MAX) =<br>100MHz                                                                                    |                                                      | 39.2 |      | μΑ/MHz |           |

## **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                             | SYMBOL                                                                                                                  | COND                                                                                                                                                       | ITIONS                                                                            | MIN                                             | TYP    | MAX | UNITS                                           |                                                 |                                                 |                                                                                  |  |      |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------|--------|-----|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------|--|------|--|--|

| V <sub>CORE</sub> Current, SLEEP Mode |                                                                                                                         | Dynamic, IPO<br>enabled, total<br>current into V <sub>CORE</sub><br>pin, CPU in SLEEP                                                                      | OVR = [01],<br>V <sub>CORE</sub> = 1.0V,<br>f <sub>SYS</sub> CLK(MAX) =<br>50MHz  |                                                 | 37.5   |     |                                                 |                                                 |                                                 |                                                                                  |  |      |  |  |

|                                       |                                                                                                                         | mode, ECC<br>disabled, standard<br>DMA with two<br>channels active,<br>inputs tied to V <sub>SS</sub><br>or V <sub>DDIO</sub> , outputs<br>source/sink 0mA | OVR = [00],<br>V <sub>CORE</sub> = 0.9V,<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz  |                                                 | 37     |     |                                                 |                                                 |                                                 |                                                                                  |  |      |  |  |

|                                       | ICORE_DSLPD                                                                                                             | Dynamic, IPO                                                                                                                                               | OVR = [10],<br>V <sub>CORE</sub> = 1.1V,<br>f <sub>SYS</sub> CLK(MAX) =<br>100MHz |                                                 | 21.1   | μ   | μA/MHz                                          |                                                 |                                                 |                                                                                  |  |      |  |  |

|                                       |                                                                                                                         | pin, CPU in SLEEP<br>mode, ECC<br>disabled, DMA<br>disabled, inputs                                                                                        |                                                                                   | pin, CPU in SLEEP<br>mode, ECC<br>disabled, DMA | p<br>n |     | pin, CPU in SLEEP<br>mode, ECC<br>disabled, DMA | pin, CPU in SLEEP<br>mode, ECC<br>disabled, DMA | pin, CPU in SLEEP<br>mode, ECC<br>disabled, DMA | OVR = [01],<br>V <sub>CORE</sub> = 1.0V,<br>f <sub>SYS</sub> CLK(MAX) =<br>50MHz |  | 19.2 |  |  |

|                                       |                                                                                                                         | tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                                                                     | OVR = [00],<br>V <sub>CORE</sub> = 0.9V,<br>SYS_CLK(MAX) =<br>12MHz               |                                                 | 17.9   |     |                                                 |                                                 |                                                 |                                                                                  |  |      |  |  |

|                                       |                                                                                                                         | Fixed, IPO enabled, total                                                                                                                                  | OVR [10],<br>V <sub>CORE</sub> = 1.1V                                             |                                                 | 362    |     |                                                 |                                                 |                                                 |                                                                                  |  |      |  |  |

|                                       | LOODE ESLAD                                                                                                             | current into V <sub>CORE</sub> pin, CPU in SLEEP mode, ECC                                                                                                 | OVR [01],<br>V <sub>CORE</sub> = 1.0V                                             |                                                 | 217    |     | μA                                              |                                                 |                                                 |                                                                                  |  |      |  |  |

|                                       | ICORE_FSLPD   mode, ECC   disabled, inputs   tied to V <sub>SS</sub> or   V <sub>DDIO</sub> , outputs   source/sink 0mA | disabled, inputs<br>tied to V <sub>SS</sub> or<br>V <sub>DDIO</sub> , outputs                                                                              | OVR [00],<br>V <sub>CORE</sub> = 0.9V                                             |                                                 | 109    |     | μ, ,                                            |                                                 |                                                 |                                                                                  |  |      |  |  |

## **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                        | SYMBOL                  | COND                                                                                                                                                                                                                                          | ITIONS                                                                            | MIN | TYP   | MAX | UNITS    |

|----------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|-------|-----|----------|

| VDDIO Current, SLEEP Mode        |                         | Dynamic, IPO enabled, total current into V <sub>DD</sub> pin, V <sub>DDIO</sub> = 3.3V, CPU in SLEEP mode, ECC disabled, standard DMA with two channels active, inputs tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA | OVR = [10],<br>V <sub>CORE</sub> = 1.1V,<br>f <sub>SYS</sub> CLK(MAX) =<br>100MHz |     | 0.001 |     |          |

|                                  | IDD_DSLPD               | Dynamic, IPO enabled, total current into V <sub>DDIO</sub> pin, V <sub>DDIO</sub> = 3.3V,                                                                                                                                                     | OVR = [01],<br>V <sub>CORE</sub> = 1.0V,<br>f <sub>SYS</sub> CLK(MAX) =<br>50MHz  |     | 0.001 |     | - μA/MHz |

|                                  |                         | CPU in SLEEP mode, ECC disabled, standard DMA with two channels active, inputs tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                                                                         | OVR = [00],<br>V <sub>CORE</sub> = 0.9V,<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz  |     | 0.001 |     |          |

|                                  |                         | Fixed, IPO enabled, total                                                                                                                                                                                                                     | OVR = [10],<br>V <sub>CORE</sub> = 1.1V                                           |     | 367   |     |          |

|                                  |                         | current into V <sub>DDIO</sub><br>pin, V <sub>DDIO</sub> = 3.3V,<br>CPU in SLEEP                                                                                                                                                              | OVR = [01],<br>V <sub>CORE</sub> = 1.0V                                           |     | 367   |     |          |

| ַםם ַ                            | IDD_FSLPD               | LPD CPU in SLEEP mode, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DDIO</sub> , outputs source/sink 0mA                                                                                                                            | OVR = [00],<br>V <sub>CORE</sub> = 0.9V                                           |     | 307   |     | μΑ       |

| V <sub>CORE</sub> Fixed Current, | I <sub>CORE_FDSLP</sub> | $V_{DDIO}$ = 3.3V, $V_{COF}$                                                                                                                                                                                                                  | RE = 1.1V                                                                         |     | 10    |     | μΑ       |

| DEEPSLEEP Mode                   | D                       | $V_{DDIO}$ = 3.3V, $V_{COF}$                                                                                                                                                                                                                  |                                                                                   |     | 3.8   |     | μΛ       |

| V <sub>DD</sub> Fixed Current,   | I <sub>DD_FDSLPD</sub>  | $V_{DDIO}$ = 3.3V, $V_{COF}$                                                                                                                                                                                                                  |                                                                                   |     | 0.34  |     | μΑ       |

| DEEPSLEEP Mode                   | 55_1 5051 5             | $V_{DDIO}$ = 3.3V, $V_{COF}$                                                                                                                                                                                                                  | <sub>RE</sub> = 0.855V                                                            |     | 0.34  |     |          |

## **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                        | SYMBOL      | COND                                       | ITIONS                                                  | MIN                                      | TYP   | MAX   | UNITS |   |

|----------------------------------|-------------|--------------------------------------------|---------------------------------------------------------|------------------------------------------|-------|-------|-------|---|

|                                  |             | 0KB SRAM                                   | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   |                                          | 0.225 |       |       |   |

|                                  |             | retained, retention regulator disabled     | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V |                                          | 0.13  |       |       |   |

|                                  |             | 20KB SRAM                                  | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   |                                          | 1.256 |       |       |   |

|                                  |             | retained                                   | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V |                                          | 0.507 |       |       |   |

| V <sub>CORE</sub> Fixed Current, |             | t,                                         | 40KB SRAM                                               | $V_{DDIO} = 3.3V$ ,<br>$V_{CORE} = 1.1V$ |       | 2.243 |       | ^ |

| BACKUP Mode                      | CORE_FBKUD  | retained                                   | $V_{DDIO} = 3.3V$ ,<br>$V_{CORE} = 0.855V$              |                                          | 0.877 |       | μΑ    |   |

|                                  |             | 80KB SRAM                                  | $V_{DDIO} = 3.3V$ ,<br>$V_{CORE} = 1.1V$                |                                          | 3.97  |       |       |   |

|                                  |             | retained                                   | $V_{DDIO} = 3.3V$ ,<br>$V_{CORE} = 0.855V$              |                                          | 1.49  |       |       |   |

|                                  |             | 160KB SRAM                                 | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   |                                          | 7.22  |       |       |   |

|                                  |             | retained                                   | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V |                                          | 2.61  |       |       |   |

|                                  |             | 0KB SRAM                                   | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   |                                          | 0.34  |       |       |   |

|                                  |             | retained, retention regulator disabled     | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V |                                          | 0.34  |       |       |   |

|                                  |             | 20KB SRAM retained                         | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   |                                          | 0.32  |       |       |   |

|                                  |             |                                            | $V_{DDIO} = 3.3V$ ,<br>$V_{CORE} = 0.855V$              |                                          | 0.32  |       |       |   |

| V <sub>DDIO</sub> Fixed Current, |             | 40KB SRAM                                  | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   |                                          | 0.32  |       |       |   |

| BACKUP Mode                      | IDD_FBKUD   | retained                                   | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V |                                          | 0.108 |       | μA    |   |

|                                  |             | 80KB SRAM                                  | $V_{DDIO} = 3.3V$ ,<br>$V_{CORE} = 1.1V$                |                                          | 0.32  |       |       |   |

|                                  |             | retained                                   | $V_{DDIO} = 3.3V$ ,<br>$V_{CORE} = 0.855V$              |                                          | 0.32  |       |       |   |

|                                  |             | 160KB SRAM                                 | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   |                                          | 0.32  |       |       |   |

|                                  |             | retained                                   | V <sub>DDIO</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V |                                          | 0.32  |       |       |   |

| V <sub>CORE</sub> Fixed Current, | loops       | $V_{DDIO}$ = 3.3V, $V_{COF}$               | RE = 1.1V                                               |                                          | 0.226 |       |       |   |

| STORAGE Mode                     | ICORE_FSTOD | V <sub>DDIO</sub> = 3.3V, V <sub>COF</sub> | RE = 0.855V                                             |                                          | 0.112 |       | μA    |   |

| V <sub>DDIO</sub> Fixed Current, | lon sores   | V <sub>DDIO</sub> = 3.3V; V <sub>COF</sub> | RE = 1.1V                                               |                                          | 0.335 |       | μΑ    |   |

| STORAGE Mode                     | IDD_FSTOD   | $V_{DDIO}$ = 3.3V; $V_{COF}$               | RE = 0.855V                                             |                                          | 0.335 |       | μΛ    |   |

## **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                       | SYMBOL                 | CONDITIONS                                                     | MIN                        | TYP  | MAX                        | UNITS |

|-------------------------------------------------|------------------------|----------------------------------------------------------------|----------------------------|------|----------------------------|-------|

| SLEEP Mode Resume<br>Time                       | t <sub>SLP_OND</sub>   |                                                                |                            | 2.1  |                            | μs    |

| DEEPSLEEP Mode                                  | <b>4</b>               | fast_wk_en = 1                                                 |                            | 81   |                            |       |

| Resume Time                                     | t <sub>DSL_OND</sub>   | fast_wk_en = 0                                                 |                            | 129  |                            | μs    |

| BACKUP Mode Resume<br>Time                      | t <sub>BKU_OND</sub>   | Includes system initialization and ROM execution time          |                            | 1.25 |                            | ms    |

| STORAGE Mode<br>Resume Time                     | tsto_ond               | Includes system initialization and ROM execution time          |                            | 1.5  |                            | ms    |

| GENERAL-PURPOSE I/O                             | )                      |                                                                |                            |      |                            | •     |

| Input Low Voltage for All GPIO, RSTN            | V <sub>IL_GPIO</sub>   | Pin configured as GPIO                                         |                            |      | 0.3 ×<br>V <sub>DDIO</sub> | V     |

| Input High Voltage for All GPIO, RSTN           | V <sub>IH_GPIO</sub>   | Pin configured as GPIO                                         | 0.7 ×<br>V <sub>DDIO</sub> |      |                            | V     |

| Output Low Voltage for                          |                        | V <sub>DDIO</sub> = 2.7V, I <sub>OL</sub> = 1mA, DS[1:0] = 00  |                            | 0.2  | 0.4                        |       |

| All GPIO Except P0.6,                           | V                      | V <sub>DDIO</sub> = 2.7V, I <sub>OL</sub> = 2mA, DS[1:0] = 10  |                            | 0.2  | 0.4                        |       |

| P0.7, P0.13, P0.18,                             | V <sub>OL_GPIO</sub>   | V <sub>DDIO</sub> = 2.7V, I <sub>OL</sub> = 4mA, DS[1:0] = 01  |                            | 0.2  | 0.4                        | V     |

| P0.19                                           |                        | V <sub>DDIO</sub> = 2.7V, I <sub>OL</sub> = 6mA, DS[1:0] = 11  |                            | 0.2  | 0.4                        |       |

| Output Low Voltage for                          |                        | V <sub>DDIO</sub> = 2.7V, I <sub>OL</sub> = 2mA, DS = 0        |                            | 0.2  | 0.4                        |       |

| GPIO P0.6, P0.7, P0.13,<br>P0.18, P0.19         | V <sub>OL_I2C</sub>    | V <sub>DDIO</sub> = 2.7V, I <sub>OL</sub> = 10mA, DS = 1       |                            | 0.2  | 0.4                        | V     |

|                                                 |                        | V <sub>DDIO</sub> = 2.7V, I <sub>OH</sub> = -1mA, DS[1:0] = 00 | V <sub>DDIO</sub> - 0.4    |      |                            |       |

| Output High Voltage for All GPIO Except P0.6,   | V <sub>OH_GPIO</sub>   | V <sub>DDIO</sub> = 2.7V, I <sub>OH</sub> = -2mA, DS[1:0] = 10 | V <sub>DDIO</sub> - 0.4    |      |                            | V     |

| P0.7, P0.13, P0.18,<br>P0.19                    |                        | V <sub>DDIO</sub> = 2.7V, I <sub>OH</sub> = -4mA, DS[1:0] = 01 | V <sub>DDIO</sub> - 0.4    |      |                            | V     |

|                                                 |                        | V <sub>DDIO</sub> = 2.7V, I <sub>OH</sub> = -6mA, DS[1:0] = 11 | V <sub>DDIO</sub> - 0.4    |      |                            |       |

| Output High Voltage for GPIO P0.6, P0.7, P0.13, | V <sub>OH_I2C</sub>    | V <sub>DDIO</sub> = 2.7V, I <sub>OH</sub> = -2mA, DS = 0       | V <sub>DDIO</sub> - 0.4    |      |                            | V     |

| P0.18, and P0.19                                | VOH_I2C                | V <sub>DDIO</sub> = 2.7V, I <sub>OH</sub> = -10mA, DS = 1      | V <sub>DDIO</sub> - 0.4    |      |                            | V     |

| Combined I <sub>OL</sub> , All GPIO             | I <sub>OL_TOTAL</sub>  |                                                                |                            |      | 100                        | mA    |

| Combined I <sub>OH</sub> , All GPIO             | I <sub>OH_</sub> TOTAL |                                                                | -100                       |      |                            | mA    |

| Input Hysteresis<br>(Schmitt)                   | V <sub>IHYS</sub>      |                                                                |                            | 300  |                            | mV    |

| Input/Output Pin<br>Capacitance for All Pins    | C <sub>IO</sub>        |                                                                |                            | 4    |                            | pF    |

| Input Leakage Current<br>Low                    | I <sub>IL</sub>        | V <sub>IN</sub> = 0V, internal pullup disabled                 | -500                       |      | +500                       | nA    |

| Input Leakage Current<br>High                   | I <sub>IH</sub>        | V <sub>IN</sub> = 3.6V, internal pulldown disabled             | -500                       |      | +500                       | nA    |

#### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A = +25^{\circ}$ C and  $T_A = +105^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                               | SYMBOL               | CONDITIONS                                                                                                                                                | MIN | TYP                        | MAX | UNITS   |

|-----------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------|-----|---------|

| Input Pullup Resistor to                | В                    | Pullup to V <sub>DDIO</sub> = V <sub>RST</sub> , RSTN at V <sub>IH</sub>                                                                                  |     | 18.7                       |     | kΩ      |

| RSTN                                    | $R_{PU\_VDD}$        | Pullup to V <sub>DDIO</sub> = 3.63V, RSTN at V <sub>IH</sub>                                                                                              |     | 10.0                       |     |         |

| Input Pullup Resistor for               | D                    | Device pin configured as GPIO, pullup to $V_{DDIO} = V_{RST}$ , device pin at $V_{IH}$                                                                    |     | 18.7                       |     | kΩ      |

| All GPIO                                | R <sub>PU</sub>      | Device pin configured as GPIO, pullup to $V_{DDIO}$ = 3.63V, device pin at $V_{IH}$                                                                       |     | 10.0                       |     | _ K12   |

| Input Pulldown Resistor                 | Pag                  | Device pin configured as GPIO, pulldown to $V_{SS}$ , $V_{DDIO}$ = $V_{RST}$ , device pin at $V_{IL}$                                                     |     | 17.6                       |     | kΩ      |

| for All GPIO                            | R <sub>PD</sub>      | Device pin configured as GPIO, pulldown to $V_{SS}$ , $V_{DDIO}$ = 3.63V, device pin at $V_{IL}$                                                          |     | 8.8                        |     | K\$2    |

| CLOCKS                                  |                      |                                                                                                                                                           |     |                            |     |         |

| System Clock<br>Frequency               | fsys_clk             |                                                                                                                                                           |     |                            | 100 | MHz     |

| System Clock Period                     | tsys_clk             |                                                                                                                                                           |     | 1/f <sub>SYS_C</sub><br>LK |     | μs      |

| Internal Primary<br>Oscillator (IPO)    | f <sub>IPO</sub>     | Default OVR = [10]                                                                                                                                        |     | 100                        |     | MHz     |

| External RF Oscillator (ERFO)           | fERFO                | Required crystal characteristics: $C_L$ = 12pF, ESR $\leq$ 50 $\Omega$ , $C_0 \leq$ 7pF, temperature stability $\pm$ 20ppm, initial tolerance $\pm$ 20ppm | 16  |                            | 32  | MHz     |

| Internal Baud Rate<br>Oscillator (IBRO) | f <sub>IBRO</sub>    |                                                                                                                                                           |     | 7.3728                     |     | MHz     |

| Internal NanoRing<br>Oscillator (INRO)  | f <sub>INRO</sub>    | Measured at V <sub>DDIO</sub> = 2.7V                                                                                                                      |     | 70                         |     | kHz     |

| External Clock                          | fEXT_CLK             | External clock selected (P0.10)                                                                                                                           |     |                            | 25  | MHz     |

| FLASH MEMORY                            |                      |                                                                                                                                                           |     |                            |     |         |

| Flash Erase Time                        | t <sub>M_ERASE</sub> | Mass erase                                                                                                                                                |     | 30                         |     |         |

| I Idoli Eldot IIIIt                     | tp_ERASE             | Page erase                                                                                                                                                |     | 30                         |     | ms      |

| Flash Programming<br>Time Per Word      | t <sub>PROG</sub>    | 32-bit programming mode,<br>f <sub>FLC_CLK</sub> = 1MHz                                                                                                   |     | 42                         |     | μs      |

| Flash Endurance                         |                      |                                                                                                                                                           | 10  |                            |     | kcycles |

| Data Retention                          | t <sub>RET</sub>     | T <sub>A</sub> = +125°C                                                                                                                                   | 10  |                            |     | years   |

#### Electrical Characteristics—16-/24-Bit Δ-Σ ADC with PGA

$(V_{DDA} = +3.3V, REFP - REFN = V_{DDA}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. } T_A = +25^{\circ}\text{C} \text{ for typical specifications, unless otherwise noted. Limits are 100% production tested at } T_A = +25^{\circ}\text{C}. \text{ Limits over the operating temperature range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.)}$

| PARAMETER                | SYMBOL | CONDITIONS | MIN | TYP                         | MAX | UNITS |

|--------------------------|--------|------------|-----|-----------------------------|-----|-------|

| ANALOG INPUTS            |        |            |     |                             |     |       |

| Full-Scale Input Voltage | FS     |            |     | ±V <sub>REF</sub> /<br>Gain |     |       |

#### Electrical Characteristics—16-/24-Bit $\Delta$ - $\Sigma$ ADC with PGA (continued)

$(V_{DDA} = +3.3V, REFP - REFN = V_{DDA}, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.  $T_A = +25^{\circ}C$  for typical specifications, unless otherwise noted. Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.)

| PARAMETER                    | SYMBOL   | CONDITIONS                   | MIN                                                           | TYP      | MAX                                                           | UNITS |  |

|------------------------------|----------|------------------------------|---------------------------------------------------------------|----------|---------------------------------------------------------------|-------|--|

| Absolute Input Voltage       |          | Buffers disabled             | V <sub>SSA</sub> -<br>30mV                                    |          | V <sub>DDA</sub> +<br>30mV                                    | V     |  |

| Innut Voltage Dange          |          | Unipolar                     | 0                                                             |          | $V_{REF}$                                                     | V     |  |

| Input Voltage Range          |          | Bipolar                      | -V <sub>REF</sub>                                             |          | $V_{REF}$                                                     | V     |  |

|                              |          | AIN buffers/PGA disabled     | V <sub>SSA</sub>                                              |          | $V_{DDA}$                                                     |       |  |

|                              |          | Buffers enabled              | V <sub>SSA</sub> + 0.1                                        |          | V <sub>DDA</sub> -<br>0.1                                     |       |  |

| Common-Mode Voltage<br>Range | $V_{CM}$ | PGA gain = 1 to 16           | V <sub>SSA</sub> +<br>0.1 +<br>(V <sub>IN</sub> )(Ga<br>in)/2 |          | V <sub>DDA</sub> -<br>0.1 -<br>(V <sub>IN</sub> )(Ga<br>in)/2 | V     |  |

|                              |          | PGA gain = 32 to 128         | V <sub>SSA</sub> +<br>0.2 +<br>(V <sub>IN</sub> )(Ga<br>in)/2 |          | V <sub>DDA</sub> -<br>0.2 -<br>(V <sub>IN</sub> )(Ga<br>in)/2 |       |  |

|                              |          | Buffer disabled              |                                                               | ±1       |                                                               | μA/V  |  |

| Differential Input Current   |          | Buffer enabled               |                                                               | 0 to 50  |                                                               | nA    |  |

|                              |          | PGA enabled                  |                                                               | ±1       |                                                               |       |  |

|                              |          | Buffer disabled              |                                                               | ±1       |                                                               | μΑ/V  |  |

| Absolute Input Current       |          | Buffer enabled               |                                                               | 20 to 80 |                                                               | A     |  |

|                              |          | PGA enabled, -40°C to +105°C | -2                                                            |          | 2                                                             | nA    |  |

| Input Capacitance            |          | Bypass mode                  |                                                               | 10       |                                                               | pF    |  |

| SYSTEM PERFORMANCE           | <u> </u> |                              |                                                               |          |                                                               |       |  |

| Resolution                   |          |                              |                                                               | 24       |                                                               | bits  |  |

#### Electrical Characteristics—16-/24-Bit $\Delta$ - $\Sigma$ ADC with PGA (continued)

$(V_{DDA} = +3.3V, REFP - REFN = V_{DDA}, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.  $T_A = +25^{\circ}C$  for typical specifications, unless otherwise noted. Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.)