### **General Description**

The MAX3346E bidirectional transceiver converts logiclevel signals to USB signals, and USB signals to logiclevel signals. The MAX3346E includes the 1.5k $\Omega$  USB pullup resistor internally, and supports both full-speed (12Mbps) and low-speed (1.5Mbps) USB operation. The device has built-in ±15kV ESD protection circuitry to guard the USB I/O pins, D+ and D-.

The MAX3346E operates with V<sub>L</sub> voltages as low as 1.65V, ensuring compatibility with low-voltage ASICs. The device features a logic-selectable suspend mode that lowers current draw to less than 40µA. The MAX3346E has an enumerate function that allows devices to logically disconnect while plugged in. The MAX3346E is fully compliant with USB specification 1.1, and the full-speed and low-speed operation under USB specification 2.0.

The MAX3346E is available in the miniature 4 x 4 chipscale package (UCSPTM), as well as the small 14-pin TSSOP, and is rated for the -40°C to +85°C extended temperature range.

### **Applications**

Cell Phones

PC Peripherals

**Data Cradles**

**PDAs**

MP3 Players

## **Features**

- ♦ ±15kV ESD Protection on D+ and D-

- ♦ Internal Linear Regulator Allows Direct Powering from the USB Cable

- ♦ Internal 1.5kΩ Pullup Resistor for Low/Full-Speed Operation

- ♦ Supports Low-Speed and Full-Speed USB Communications

- ♦ Complies with USB Specification Revision 1.1 and 2.0 (Low Speed and Full Speed)

- **♦ Three-State Outputs**

- ♦ Enumerate Input—Allows USB Connection through Software

- ♦ No Power-Supply Sequencing Required

- ♦ Operates with V<sub>L</sub> of 1.65V to 3.6V, Ensuring Compatibility with Low-Voltage ASICs

- **♦** Available in Miniature Chip-Scale Package

## **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAX3346EEUD   | -40°C to +85°C | 14 TSSOP    |

| MAX3346EEBE-T | -40°C to +85°C | 4 x 4 UCSP  |

UCSP is trademark of Maxim Integrated Products, Inc.

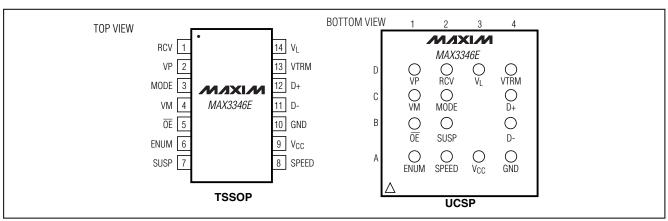

## **Pin Configurations**

NIXIN

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND, unless otherwise noted.)           |

|---------------------------------------------------------------------|

| Supply Voltage (V <sub>CC</sub> )0.3V to +6V                        |

| Output of Internal Regulator (VTRM)0.3V to (V <sub>CC</sub> + 0.3V) |

| Input Voltage (D+, D-)0.3V to +6V                                   |

| System Supply Voltage (V <sub>L</sub> )0.3V to +6V                  |

| RCV, SUSP, VM, VP, MODE,                                            |

| $\overline{\text{OE}}$ , SPEED, ENUM0.3V to (V <sub>L</sub> + 0.3V) |

| Short-Circuit Current (D+, D-)                                      |

| to V <sub>CC</sub> or GND (Note 1)Continuous                        |

| Maximum Continuous Current (all other pins)±15mA                    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

|-------------------------------------------------------|---------------|

| 4 x 4 UCSP (derate 7.4mW/°C above +70°C)              | 589mW [B16-2] |

| 14-Pin TSSOP (derate 9.1mW/°C above +70°C)            | 727mW [U14-1] |

| Operating Temperature Range                           | 40°C to +85°C |

| Junction Temperature                                  | +150°C        |

| Storage Temperature Range                             |               |

| Lead Temperature (soldering, 10s)                     |               |

| Bump Temperature (soldering) Reflow                   | +235°C        |

**Note 1:** External 23.7 $\Omega$  resistors connected to D+ and D-.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +4V \text{ to } +5.5V, \text{GND} = 0, \text{VTRM} = +3.0V \text{ to } +3.6V, \text{V}_L = +1.65V \text{ to } +3.6V, \text{T}_A = \text{T}_{MIN} \text{ to T}_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V, \text{V}_L = +2.5V, \text{T}_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                     | SYMBOL               | CONDITIONS                                                                      | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------------|----------------------|---------------------------------------------------------------------------------|------|-----|------|-------|

| SUPPLY INPUTS (VCC, VTRM, V                   | 'L)                  |                                                                                 |      |     |      |       |

| Regulated Supply Voltage                      | V <sub>VTRM</sub>    | Internal regulator                                                              | 3.0  | 3.3 | 3.6  | V     |

| V <sub>L</sub> Input Range                    |                      |                                                                                 | 1.65 |     | 3.60 | V     |

| V <sub>CC</sub> Input Range                   |                      |                                                                                 | 4.0  |     | 5.5  | V     |

| Operating V <sub>CC</sub> Supply Current      | Ivcc                 | Full-speed transmitting/receiving at 12Mbps, C <sub>L</sub> = 50pF on D+ and D- |      |     | 8    | mA    |

| Operating V <sub>L</sub> Supply Current       | IVL                  | Full-speed transmitting/receiving at 12Mbps                                     |      |     | 6    | mA    |

| Full-Speed Idle and SE0 Supply                | l                    | Full-speed idle: $V_{D+} > 2.7V$ , $V_{D-} < 0.3V$                              |      | 340 | 450  |       |

| Current                                       | IVCC(IDLE)           | SE0: $V_{D+} < 0.3V$ , $V_{D-} < 0.3V$                                          |      | 390 | 500  | μΑ    |

| Static V <sub>L</sub> Supply Current          | IVL(STATIC)          | Full-speed idle, SE0, or suspend mode                                           |      |     | 5    | μΑ    |

| Suspend Supply Current                        | IVCC(SUSP)           | $SUSP = \overline{OE} = high$                                                   |      |     | 40   | μΑ    |

| Disable-Mode Supply Current                   | Ivcc(DIS)            | V <sub>L</sub> = GND or open                                                    |      |     | 20   | μΑ    |

| D+/D- Disable-Mode<br>Load Current            | I <sub>D_(DIS)</sub> | $V_L = GND \text{ or open, } V_{D} = 0 \text{ or } +5.5V$                       |      |     | 5    | μΑ    |

| Sharing-Mode V <sub>L</sub> Supply<br>Current | IVL(SHARING)         | $V_{CC} = GND$ or open, $\overline{OE} = low$ , $SUSP = high$                   |      |     | 20   | μΑ    |

| D+/D- Sharing-Mode<br>Load Current            | ID_(SHARING)         | V <sub>CC</sub> = GND or open, V <sub>D</sub> _ = 0 or +5.5V                    |      |     | 20   | μΑ    |

| LINEAR REGULATOR                              |                      |                                                                                 |      |     |      |       |

| External Capacitor                            | Cout                 | Compensation of linear regulator                                                | 1    |     |      | μF    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +4V \text{ to } +5.5V, \text{GND} = 0, \text{VTRM} = +3.0V \text{ to } +3.6V, \text{V}_L = +1.65V \text{ to } +3.6V, \text{T}_A = \text{T}_{MIN} \text{ to T}_{MAX}, \text{ unless otherwise noted. Typical values are at V}_{CC} = +5V, \text{V}_L = +2.5V, \text{T}_A = +25^{\circ}\text{C.})$  (Note 2)

| PARAMETER                       | SYMBOL           | CONDITIONS                                                            | MIN                    | TYP | MAX   | UNITS |

|---------------------------------|------------------|-----------------------------------------------------------------------|------------------------|-----|-------|-------|

| ESD PROTECTION (D+, D-)         |                  |                                                                       |                        |     |       |       |

| Human Body Model                |                  |                                                                       |                        | ±15 |       | kV    |

| IEC 1000-4-2 Air-Gap Discharge  |                  |                                                                       |                        | ±10 |       | kV    |

| IEC 1000-4-2 Contact Discharge  |                  |                                                                       |                        | ±8  |       | kV    |

| LOGIC-SIDE I/O                  |                  |                                                                       |                        |     |       |       |

| Input High Voltage              | V <sub>IH</sub>  | VP, VM, SUSP, SPEED, $\overline{\text{OE}}$ , MODE, ENUM              | (2/3) x V <sub>L</sub> |     |       | V     |

| Input Low Voltage               | VIL              | VP, VM, SUSP, SPEED, $\overline{\text{OE}}$ , MODE, ENUM              |                        |     | 0.4   | V     |

| Output High Voltage             | VoH              | ISOURCE = +2mA, RCV, VP, VM                                           | V <sub>L</sub> - 0.4   |     |       | V     |

| Output Low Voltage              | V <sub>OL</sub>  | I <sub>SINK</sub> = -2mA, RCV, VP, VM                                 |                        |     | 0.4   | V     |

| Input Leakage Current           |                  | $VP$ , $VM$ , $SUSP$ , $ENUM$ , $\overline{OE}$ , $MODE = 0$ or $V_L$ |                        |     | ±1    | μΑ    |

| USB-SIDE I/O                    |                  |                                                                       |                        |     |       |       |

| Output-Voltage Low              | V <sub>OLD</sub> | $R_L = 1.5k\Omega$ from D+ or D- to 3.6V                              |                        |     | 0.3   | V     |

| Output-Voltage High             | V <sub>OHD</sub> | $R_L = 15k\Omega$ from D+ and D- to GND                               | 2.8                    |     | 3.6   | V     |

| Input Impedance                 | Z <sub>IN</sub>  | V <sub>D</sub> _ = 0 or +3.6V, ENUM = 0,<br>three-state driver        | 1                      |     |       | МΩ    |

| Single-Ended Input-Voltage High | V <sub>IH</sub>  |                                                                       | 2.0                    |     |       | V     |

| Single-Ended Input-Voltage Low  | VIL              |                                                                       |                        |     | 0.8   | V     |

| D+, D- Receiver Hysteresis      |                  |                                                                       |                        | 200 |       | mV    |

| Driver Output Impedance         | Rout             |                                                                       | 4.6                    |     | 16.0  | Ω     |

| Internal Resistor               | Rpullup          |                                                                       | 1.410                  | 1.5 | 1.540 | kΩ    |

| Input Common-Mode Voltage       |                  |                                                                       | 0.8                    |     | 2.5   | V     |

| Differential Input Sensitivity  |                  |                                                                       | 200                    |     |       | mV    |

#### **TIMING CHARACTERISTICS**

$(V_{CC} = +4V \text{ to } +5.5V, \text{GND} = 0, \text{ VTRM} = +3.0V \text{ to } +3.6V, \text{ V}_{L} = +1.65V \text{ to } +3.6V, \text{ T}_{A} = \text{T}_{MIN} \text{ to T}_{MAX}, \text{ unless otherwise noted. Typical values are at V}_{CC} = +5V, \text{V}_{L} = +2.5V, \text{T}_{A} = +25^{\circ}\text{C.})$  (Note 2)

| PARAMETER                                     | SYMBOL           | CONDITIONS                              | MIN | TYP | MAX | UNITS |  |

|-----------------------------------------------|------------------|-----------------------------------------|-----|-----|-----|-------|--|

| SPEED INDEPENDENT TIMING CHARACTERISTICS      |                  |                                         |     |     |     |       |  |

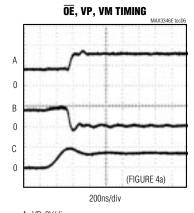

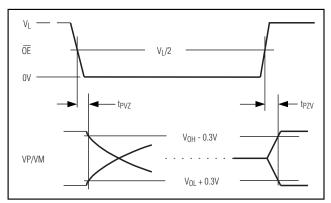

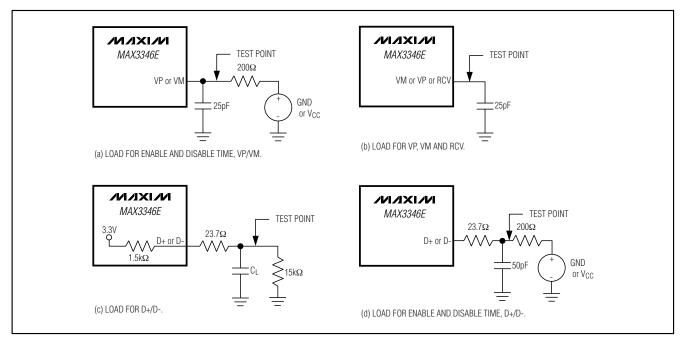

| OE to VP/VM Three-State Delay<br>Disable Time | t <sub>PVZ</sub> | Figures 1a and 4a                       |     |     | 20  | ns    |  |

| OE to VP/VM Delay<br>Enable Time              | tPZV             | Figures 1a and 4a                       |     |     | 25  | ns    |  |

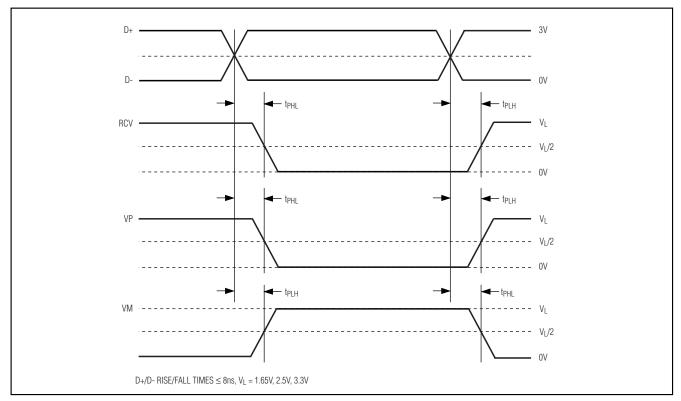

| D+/D- to RCV Propagation Delay                | tpLH             | C <sub>L</sub> = 25pF, Figures 4b and 5 |     |     | 18  | ns    |  |

| D+/D- to RCV Propagation Delay                | tphL             | C <sub>L</sub> = 25pF, Figures 4b and 5 |     |     | 18  | ns    |  |

#### **TIMING CHARACTERISTICS (continued)**

$(V_{CC} = +4V \text{ to } +5.5V, \text{ GND} = 0, \text{ VTRM} = +3.0V \text{ to } 3.6V, \text{ } V_{L} = +1.65V \text{ to } +3.6V, \text{ } T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +5V, \text{ } V_{L} = +2.5V, \text{ } T_{A} = +25^{\circ}\text{C.}) \text{ (Note 2)}$

| PARAMETER                                      | SYMBOL                         | CONDITIONS                                       | MIN | TYP | MAX | UNITS |  |

|------------------------------------------------|--------------------------------|--------------------------------------------------|-----|-----|-----|-------|--|

| D+/D- to VP/VM Propagation                     | tpLH                           | C <sub>L</sub> = 25pF, Figures 4b and 5          |     |     | 18  | 20    |  |

| Delay                                          | tphl                           | C <sub>L</sub> = 25pF, Figures 4b and 5          |     |     | 18  | ns    |  |

| FULL-SPEED TIMING CHARACT                      | ERISTICS                       |                                                  |     |     |     |       |  |

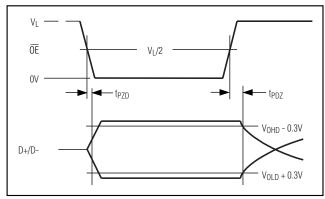

| OE to Transmit Delay Enable<br>Time            | t <sub>PZD</sub>               | (Figures 1b, 4d)                                 |     |     | 20  | ns    |  |

| OE to Driver Three-State Delay<br>Disable Time | tPDZ                           | (Figures1b, 4d)                                  |     |     | 20  | ns    |  |

| VP/VM to D+/D- Propagation                     | tpLH                           | (Figures 3, 4c)                                  |     |     | 18  |       |  |

| Delay (MODE = 1)                               | tphl                           | (Figures 3, 4c)                                  |     |     | 18  | ns    |  |

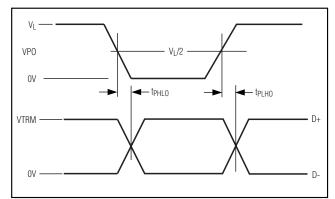

| VP to D+/D- Propagation Delay                  | t <sub>PHL0</sub>              | C <sub>L</sub> = 50pF (Figures 2, 4c)            |     |     | 20  | ns l  |  |

| (MODE = 0)                                     | t <sub>PLH0</sub>              | C <sub>L</sub> = 50pF (Figures 2, 4c)            |     |     | 20  |       |  |

| D+, D- Rise Time                               | t <sub>R</sub>                 | $C_L = 50pF$ , 10% to 90% of $IV_{OH} - V_{OL}I$ | 4   |     | 20  | ns    |  |

| D+, D- Fall Time                               | tF                             | $C_L = 50$ pF, 90% to 10% of $IV_{OH} - V_{OL}I$ | 4   |     | 20  | ns    |  |

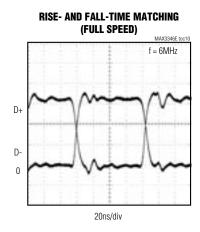

| Rise- and Fall-Time Matching (Note 3)          | t <sub>R</sub> /t <sub>F</sub> | C <sub>L</sub> = 50pF                            | 90  |     | 110 | %     |  |

| Output-Signal Crossover Voltage (Note 3)       | VCRS                           | C <sub>L</sub> = 50pF                            | 1.3 |     | 2.0 | V     |  |

| LOW-SPEED TIMING CHARACTI                      | ERISTICS                       |                                                  | •   |     |     | •     |  |

| VP/VM to D+/D- Propagation                     | tpLH                           | Figures 3 and 4c, C <sub>L</sub> = 50pF to 600pF | 30  |     | 250 | 20    |  |

| Delay (MODE = 1)                               | tphL                           | Figures 3 and 4c, C <sub>L</sub> = 50pF to 600pF | 30  |     | 250 | ns    |  |

| VP to D+/D- Propagation Delay                  | t <sub>PHL0</sub>              | Figures 2 and 4c, C <sub>L</sub> = 50pF to 600pF | 30  |     | 250 |       |  |

| (MODE = 0)                                     | t <sub>PLH0</sub>              | Figures 2 and 4c, C <sub>L</sub> = 50pF to 600pF | 30  |     | 250 | ns    |  |

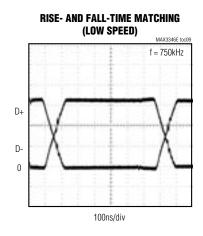

| D+/D- Rise Time                                | t <sub>R</sub>                 | C <sub>L</sub> = 50pF to 600pF                   | 75  |     | 300 | ns    |  |

| D+/D- Fall Time                                | tF                             | C <sub>L</sub> = 50pF to 600pF                   | 75  |     | 300 | ns    |  |

| Rise- and Fall-Time Matching                   | t <sub>R</sub> /t <sub>F</sub> | $C_L = 50pF$ to $600pF$                          | 80  |     | 125 | %     |  |

| Output-Signal Crossover Voltage                | VCRS                           | $C_L = 50pF$ to $600pF$                          | 1.3 |     | 2.0 | V     |  |

Note 2: Parameters are 100% production tested at +25°C, limits over temperature are guaranteed by design.

Note 3: Guaranteed by design, not production tested.

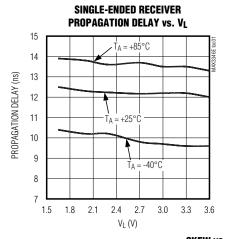

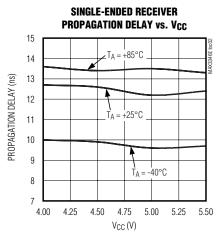

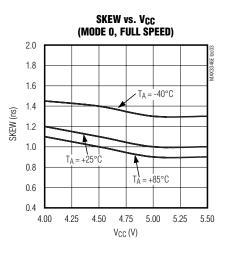

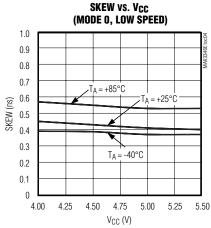

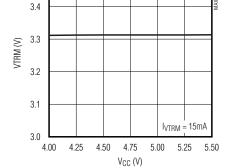

## Typical Operating Characteristics

( $V_{CC}$  = +5V,  $V_L$  =+3.3V,  $T_A$  = +25°C, unless otherwise noted.)

3.5

A: VP, 2V/div B: VM, 2V/div C: OE, 5V/div

## **Typical Operating Characteristics (continued)**

$(V_{CC} = +5V, V_L = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

A: SUSP, 2V/div B: RCV, 2V/div

## **Pin Description**

| Р     | IN   | NAME | INPUT/           | FUNCTION                                                                                                                                                                                                                                                                   |  |

|-------|------|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TSSOP | UCSP | NAME | OUTPUT           | FUNCTION                                                                                                                                                                                                                                                                   |  |

| 1     | D2   | RCV  | Output           | Receiver Output. Single-ended CMOS output. RCV responds to the differential input on D+ and D- (see Table 3).                                                                                                                                                              |  |

| 2     | D1   | VP   | Input/<br>Output | put Drive OE low to make VP a driver input (see Table 3).                                                                                                                                                                                                                  |  |

| 3     | C2   | MODE | Input            | Mode Control Input. Selects single-ended (mode zero) or differential (mode of input for the system side when converting logic-level signals to USB-level signals. If MODE is forced high, mode one is selected. If MODE is forced low mode zero is selected (see Table 3). |  |

| 4     | C1   | VM   | Input/<br>Output | System-Side Data Input/Output. Drive $\overline{OE}$ high to make VM a receiver output. Drive $\overline{OE}$ low to make VM a driver input (see Table 3).                                                                                                                 |  |

| 5     | B1   | ŌĒ   | Input            | Output Enable. Drive $\overline{\text{OE}}$ high to enable the receiver. Drive $\overline{\text{OE}}$ low to enable the driver input.                                                                                                                                      |  |

| 6     | A1   | ENUM | Input            | Enumerate Input. Drive ENUM low to disconnect the internal $1.5 k\Omega$ resistor, and enumerate the USB. With ENUM high, the internal $1.5 k\Omega$ resistor is connected to either D+ or D-, depending on the state of SPEED.                                            |  |

## **Pin Description (continued)**

| Р     | IN     | NAME  | INPUT/           | FUNCTION                                                                                                                                                                                                                                                                                  |  |

|-------|--------|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TSSOP | UCSP   | NAME  | OUTPUT           | FUNCTION                                                                                                                                                                                                                                                                                  |  |

| 7     | B2     | SUSP  | Input            | Suspend Input. Drive SUSP low for normal operation. Force SUSP high for low-power state. In low-power state RCV is low, D+/D- are high impedance if $\overline{OE}$ is floating, and VP/VM are active outputs.                                                                            |  |

| 8     | A2     | SPEED | Input            | USB Transmission Speed Select Input. If SPEED is forced high, full speed (12Mbps) is selected and the internal 1.5k $\Omega$ pullup resistor is connected to D+. If SPEED is forced low, low speed (1.5Mbps) is selected and the internal 1.5k $\Omega$ pullup resistor is connected to D |  |

| 9     | АЗ     | VCC   | Power            | USB-Side Power-Supply Input. Connect V <sub>CC</sub> to the incoming USB power suppl Bypass V <sub>CC</sub> to GND with a 1µF ceramic capacitor.                                                                                                                                          |  |

| 10    | A4     | GND   | Power            | Ground                                                                                                                                                                                                                                                                                    |  |

| 11    | B4     | D-    | Input/<br>Output | USB Differential Data Input/Output. Connect to the USB's D- signal through a $24.3\Omega$ ±1% resistor.                                                                                                                                                                                   |  |

| 12    | C4     | D+    | Input/<br>Output | USB Differential Data Input/Output. Connect to the USB's D+ signal through a $24.3\Omega$ ±1% resistor.                                                                                                                                                                                   |  |

| 13    | D4     | VTRM  | Power            | Regulated Output Voltage. 3.3V output derived from the $V_{CC}$ input. Bypass VTRM to GND with a 1 $\mu$ F (or more) low-ESR capacitor, such as ceramic or plastic film types.                                                                                                            |  |

| 14    | D3     | VL    | Power            | System-Side Power-Supply Input. Connect to the system's logic-level power supply, 1.65V to 3.6V. Bypass to GND with a 0.1µF capacitor.                                                                                                                                                    |  |

| _     | B3, C3 | _     | _                | Not populated. The solder sphere is omitted from these locations (see the <i>Package Information</i> ).                                                                                                                                                                                   |  |

#### **Detailed Description**

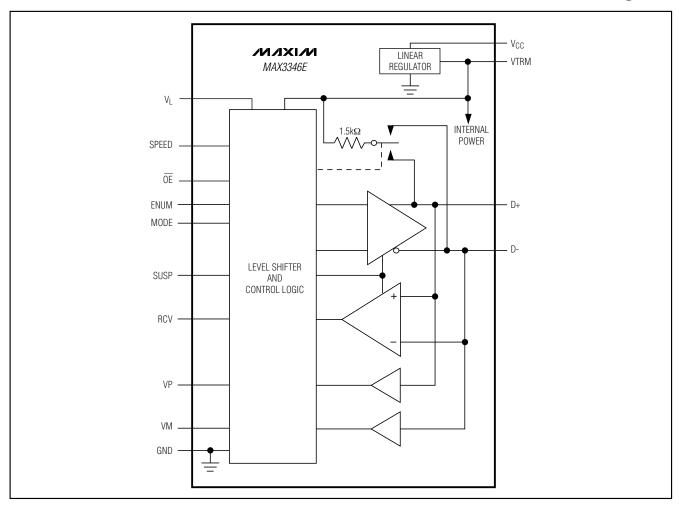

The MAX3346E is a bidirectional transceiver that converts single-ended or differential logic-level signals to differential USB signals, and converts differential USB signals to single-ended or differential logic-level signals. The MAX3346E includes an internal  $1.5k\Omega$  pullup resistor that can be connected to either D+ or D- for full-speed or low-speed operation (see the *Functional Diagram*). The MAX3346E can be energized without concern about power-supply sequencing. Additionally, the USB I/O, D+ and D-, are ESD protected to  $\pm 15kV$ . The MAX3346E can get its USB-side power, VCC,

directly from the USB connection, and can operate with system-side power,  $V_L$ , down to 1.65V and still meet the USB physical layer specifications. The MAX3346E supports both full-speed (12Mbps) and low-speed (1.5Mbps), USB specification 1.1 operation.

The MAX3346E has an enumerate feature that works when power is on. Driving ENUM low disconnects the internal 1.5k $\Omega$  pullup resistor from both D+ and D-, reenumerating the USB. This is useful if changes in communication protocol are required while power is applied, and while the USB cable is connected.

## Applications Information

#### **Power-Supply Configurations**

#### Normal Operating Mode

Connect  $V_L$  and  $V_{CC}$  to system power supplies (Table 1). Connect  $V_L$  to a +1.65V to +3.6V supply. Connect  $V_{CC}$  to a +4.0V to +5.5V supply. Alternatively, the MAX3346E can derive power from a single Li+ battery. Connect the battery to  $V_{CC}$ . VTRM remains above +3.0V for  $V_{CC}$  as low as +3.1V.

Additionally, the MAX3346E can derive power from a 3.3V ±10% voltage regulator. Connect V<sub>CC</sub> and VTRM to an external +3.3V voltage regulator.

#### Disable Mode

Connect V<sub>CC</sub> to a system power supply and leave V<sub>L</sub> unconnected or connect to GND. D+ and D- enter a tristate mode and V<sub>CC</sub> consumes less than 20µA of supply current. D+ and D- withstand external signals up to +5.5V in disable mode (Table 2).

#### Sharing Mode

Connect  $V_L$  to a system power supply and leave  $V_{CC}$  (or  $V_{CC}$  and  $V_{VTRM}$ ) unconnected or connect to GND. D+ and D- enter a tri-state mode, allowing other circuitry to share the USB D+ and D- lines, and  $V_L$  consumes less than  $20\mu A$  of supply current. D+ and D- withstand external signals up to +5.5V in sharing mode (Table 2).

#### **Device Control**

0E

OE controls the direction of communication through the device. With OE low, the MAX3346E transfers data from the system side to the USB side. With OE high, the MAX3346E transfers data from the USB side to the system side.

#### **ENUM**

The MAX3346E allows software control of USB enumeration. USB specification 1.1 requires a  $1.5 k\Omega$  pullup resistor to D+ or D- to set the transmission speed (see the SPEED section). Enumerating the USB requires removing the  $1.5 k\Omega$  resistor from the circuit, and is accomplished with the MAX3346E by driving ENUM low. With ENUM high, the voltage at SPEED determines how the internal resistor is connected (see the  $Functional\ Diagram$ ).

#### MODE

MODE is a control input that selects whether differential or single-ended logic signals are recognized by the system side of the MAX3346E (Table 3).

If MODE is forced high, differential input is selected. With differential input selected, outputs D+ and D- follow the differential inputs at VP and VM. If VP and VM are both forced low, an SE0 condition is forced on the USB.

Drive MODE and VM low for single-ended input mode. With single-ended input selected, the differential signal on D+ and D- is controlled by VP. If VM is high when MODE is low, D- and D+ are both low, forcing an SE0 condition.

**Table 1. Power-Supply Configurations**

| V <sub>CC</sub> (V) | VTRM (V)           | V <sub>L</sub> (V) | CONFIGURATION            | NOTES   |

|---------------------|--------------------|--------------------|--------------------------|---------|

| +4.0 to +5.5        | +3.3 Output        | +1.65 to +3.6      | Normal mode              | _       |

| +3.1 to +4.5        | +3.3 Output        | +1.65 to +3.6      | Battery supply           | _       |

| +3.0 to +3.6        | +3.0 to +3.6 Input | +1.65 to +3.6      | Voltage regulator supply | _       |

| GND or floating     | Output             | +1.65 to +3.6      | Sharing mode             | Table 2 |

| +3.0 to +5.5        | Output             | GND or floating    | Disable mode             | Table 2 |

Table 2. Disable-Mode and Sharing-Mode Configurations

| INPUTS/OUTPUTS        | DISABLE MODE                                                                                                   | SHARING MODE                 |

|-----------------------|----------------------------------------------------------------------------------------------------------------|------------------------------|

| Vcc/VTRM              | <ul> <li>+5V input/+3.3V output</li> <li>+3.3V input/+3.3V output</li> <li>+3.7V input/+3.3V output</li> </ul> | Floating or connected to GND |

| VL                    | Floating or connected to GND                                                                                   | +1.65V to +3.6V input        |

| D+ and D-             | High impedance                                                                                                 | High impedance               |

| SPEED, SUSP, OE, ENUM | High impedance                                                                                                 | High impedance               |

### **Timing Diagrams**

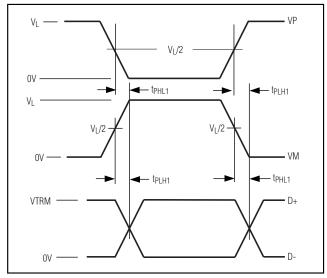

Figure 1a. Enable and Disable Timing, Receiver

Figure 1b. Enable and Disable Timing, Transmitter

#### SUSP

SUSP, or suspend, is a control input. When SUSP is forced high the MAX3346E enters a low-power state. In this state, the quiescent supply current into VCC is less than  $40\mu A$ . In this mode, RCV is forced low, and D+ and D- are high-impedance inputs (Table 3d).

In suspend mode, data can only be transmitted with full-speed slope control.

#### **SPEED**

SPEED is a control input that selects between low-speed (1.5Mbps) and full-speed (12Mbps) USB transmission. Internally, it selects whether the 1.5k $\Omega$  pullup resistor is connected to D+ (full-speed) or D- (low-speed) (*Functional Diagram*). Force SPEED high to select full speed, or force SPEED low to select low speed.

#### **VTRM**

VTRM is the 3.3V output of the internal linear voltage regulator. The regulator is used to power the internal portions of the USB side of the MAX3346E. The VTRM

Figure 2. Mode 0 Timing

Figure 3. Mode 1 Timing

regulator's supply input is VCC. Connect a 1.0 $\mu$ F (or greater) ceramic or plastic capacitor from VTRM to GND, as close to VTRM as possible. Do not use VTRM to provide power to external circuitry.

#### D+ and D-

D+ and D- are the transceiver I/O connections, and are ESD protected to  $\pm 15 \mathrm{kV}$  using the Human Body Model, making the MAX3346E ideal for applications where a robust transmitter is required.

#### VCC

Bypass VCC to GND with a  $1\mu F$  capacitor. Place the  $1\mu F$  capacitor as close as possible to the MAX3346E.

Figure 4. Test Circuits

Figure 5. D+/D- to RCV, VP, VM Propagation Delays

Table 3a. Truth Table, Transmit (MODE = 0)

| $\overline{\text{OE}} = 0 \text{ (TRANSMIT)}$ |    |         |    |      |         |  |  |

|-----------------------------------------------|----|---------|----|------|---------|--|--|

| IN                                            |    | DECLU T |    |      |         |  |  |

| VP                                            | VM | D+      | D- | RCV  | RESULT  |  |  |

| 0                                             | 0  | 0       | 1  | 0    | Logic 0 |  |  |

| 0                                             | 1  | 0       | 0  | RCV* | SE0     |  |  |

| 1                                             | 0  | 1       | 0  | 1    | Logic 1 |  |  |

| 1                                             | 1  | 0       | 0  | X    | SE0     |  |  |

<sup>\*</sup>RCV denotes the signal level on output RCV just before SE0 state occurs. This level is stable during the SE0 period.

### **Table 3b. Truth Table, Transmit (MODE = 1)**

| $\overline{\text{OE}} = 0 \text{ (TRANSMIT)}$ |    |        |    |      |           |  |  |  |

|-----------------------------------------------|----|--------|----|------|-----------|--|--|--|

| INPUT                                         |    | ОИТРИТ |    |      | DECLUT    |  |  |  |

| VP                                            | VM | D+     | D- | RCV  | RESULT    |  |  |  |

| 0                                             | 0  | 0      | 0  | RCV* | SE0       |  |  |  |

| 0                                             | 1  | 0      | 1  | 0    | Logic 0   |  |  |  |

| 1                                             | 0  | 1      | 0  | 1    | Logic 1   |  |  |  |

| 1                                             | 1  | 1      | 1  | X    | Undefined |  |  |  |

<sup>\*</sup>RCV denotes the signal level on output RCV just before SE0 state occurs. This level is stable during the SE0 period.

### **Table 3c. Truth Table, Receive**

| DE = 1 (RECEIVE) |    |    |        |      |           |  |  |  |

|------------------|----|----|--------|------|-----------|--|--|--|

| INPUT            |    |    | DECLUT |      |           |  |  |  |

| D+               | D- | VP | VM     | RCV  | RESULT    |  |  |  |

| 0                | 0  | 0  | 0      | RCV* | SE0       |  |  |  |

| 0                | 1  | 0  | 1      | 0    | Logic 0   |  |  |  |

| 1                | 0  | 1  | 0      | 1    | Logic 1   |  |  |  |

| 1                | 1  | 1  | 1      | Х    | Undefined |  |  |  |

<sup>\*</sup>RCV denotes the signal level on output RCV just before SE0 state occurs. This level is stable during the SE0 period.

#### **Table 3d. Function Select**

| SUSP | ENUMERATE | ŌĒ     | D+/D-   | RCV    | VP/VM  | FUNCTION                               |

|------|-----------|--------|---------|--------|--------|----------------------------------------|

| 0    | 0         | 0      | Driving | Active | High-Z | Normal driving                         |

| 0    | 0         | 1      | High-Z  | Active | Active | Normal receiving, RPULLUP disconnected |

| 0    | 1         | 0      | Driving | Active | High-Z | Normal driving                         |

| 0    | 1         | 1      | High-Z  | Active | Active | Normal receiving, RPULLUP connected    |

| 1    | 0         | 0 or 1 | High-Z  | 0      | Active | Suspend mode, RPULLUP disconnected     |

| 1    | 1         | 0 or 1 | High-Z  | 0      | Active | Suspend mode, RPULLUP connected        |

#### **External Components**

#### External Resistors

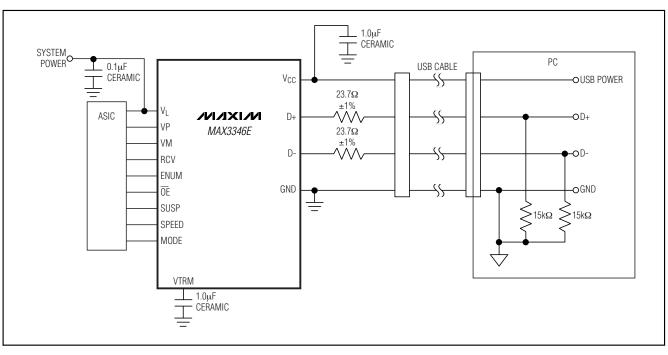

Two external resistors are required for USB connection, each of them from  $23.7\Omega$  ±1% to  $27.4\Omega$  ±1%, 1/2W (or greater). Place one resistor in series between D+ of the MAX3346E and D+ of the USB connector. Place the other resistor in series between D- of the MAX3346E and D- of the USB connector. The *Typical Operating Circuit* shows these connections.

#### External Capacitors

Four external capacitors are recommended for proper operation. Use a 0.1  $\mu F$  ceramic for decoupling  $V_{CC}$ , and a 1.0  $\mu F$  (or greater) ceramic or plastic filter capacitor on VTRM. Return all capacitors to GND.

#### Receiving Data from the USB

Data received from the USB are output to VP/VM and RCV in either of two ways, differentially or single ended. To receive data from the USB, force  $\overline{OE}$  high, and force SUSP low. Differential data arriving at D+/D- appears as differential logic signals at VP/VM, and as a single-ended logic signal at RCV. If both D+ and D- are low, then VP and VM are low, signaling an SEO condition on the bus; RCV retains the last state before SEO (see Table 3).

#### Transmitting Data to the USB

The MAX3346E outputs data to the USB differentially on D+ and D-. The logic driving the signals may be either differential or single ended. For sending differential logic, force MODE high, force  $\overline{\text{OE}}$  and SUSP low, and apply data to VP and VM. If sending single-ended logic, force MODE, SUSP,  $\overline{\text{OE}}$ , and VM low, and apply data to VP. With VP low, D+ is low and D- high, resulting in a logic 0 state. With VP high, D+ is high and D-low, resulting in a logic 1 state (see Table 3).

#### **ESD** protection

To protect the MAX3346E against ESD, D+ and D- have extra protection against static electricity to protect the device up to  $\pm 15$ kV. The ESD structures withstand high ESD in all states; normal operation, suspend, and powered down. For the 15kV ESD structures to work correctly, a 1 $\mu$ F or greater capacitor must be connected from VTRM to GND.

ESD protection can be tested in various ways; the D+ and D- input/output pins are characterized for protection to the following limits:

- 1) ±15kV using the Human Body Model.

- 2) ±8kV using the Contact Discharge method specified in IEC 1000-4-2.

- 3) ±10kV using the IEC 1000-4-2 Air-Gap method.

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

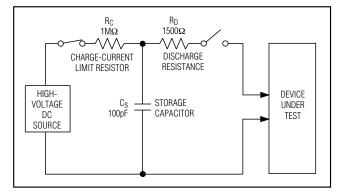

#### **Human Body Model**

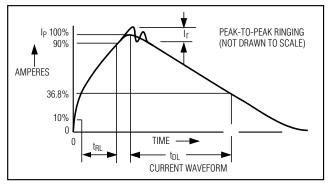

Figure 6a shows the Human Body Model, and Figure 6b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a  $1.5 \mathrm{k}\Omega$  resistor.

Figure 6a. Human Body ESD Test Models

Figure 6b. Human Body Model Current Waveform

#### IEC 1000-4-2

The IEC 1000-4-2 standard covers ESD testing and performance of finished equipment; it does not specifically refer to integrated circuits. The MAX3346E helps to design equipment that meets Level 2 of IEC 1000-4-2, without the need for additional ESD-protection components.

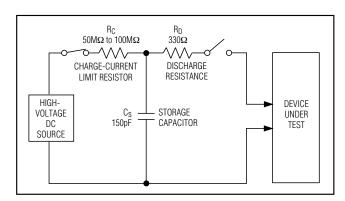

The major difference between tests done using the Human Body Model and IEC 1000-4-2 is a higher peak current in IEC 1000-4-2, because series resistance is lower in the IEC 1000-4-2 model. Hence, the ESD withstand voltage measured to IEC 1000-4-2 is generally lower than that measured using the Human Body Model. Figure 7a shows the IEC 1000-4-2 model.

The Air-Gap Discharge test involves approaching the device with a charged probe. The Contact Discharge method connects the probe to the device before the probe is energized.

#### Machine Model

The Machine Model for ESD tests all pins using a 200pF storage capacitor and zero discharge resistance. Its objective is to emulate the stress caused by contact that occurs with handling and assembly during manufacturing. Of course, all pins require this protection during manufacturing, not just USB inputs and outputs. Therefore, after PC board assembly, the Machine Model is less relevant to I/O ports.

Figure 7a. IEC 1000-4-2 ESD Test Model

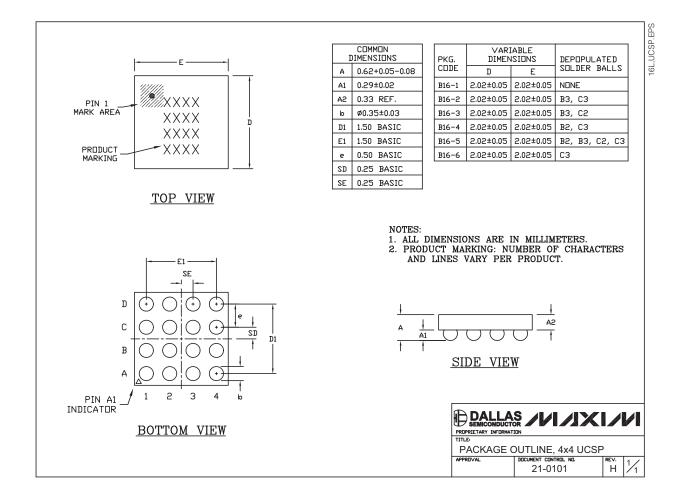

## **UCSP Applications Information**

For the latest application details on UCSP construction, dimensions, tape carrier information, printed circuit board techniques, bump-pad layout, and recommended reflow temperature profile as well as the latest information on reliability testing results, go to the Maxim website at www.maxim-ic.com/ucsp for the Application Note, "UCSP—A Wafer-Level Chip-Scale Package."

## **Typical Operating Circuit**

## Functional Diagram

**Chip Information**

TRANSISTOR COUNT: 2162 PROCESS: BICMOS

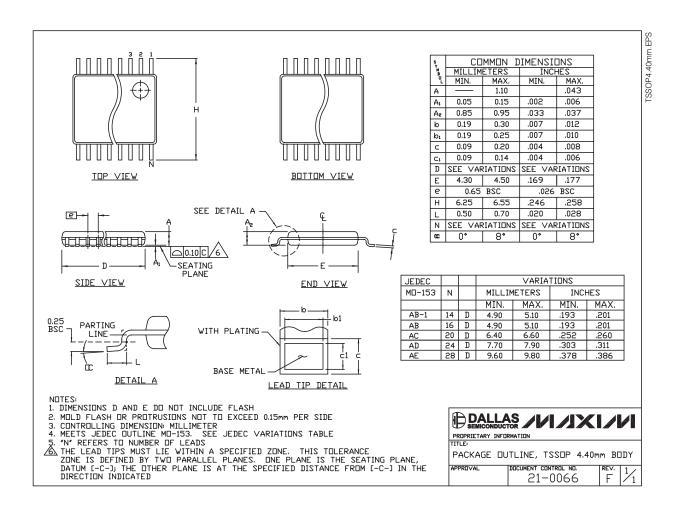

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for USB Interface IC category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

CY7C69356-48LTXC USB3319C-GJ-TR USB3370B-EZK-TR CYPD2120-24LQXI CYPD2122-20FNXIT CYPD2122-24LQXIT LIF-UC120-SWG36ITR50 UPD360-A/6HX CP2102NP1174GM DPO2039DABQ-13 CY7C68034-56LTXC TUSB212RWBT TUSB213IRGYT TUSB213RGYT USB3503T-I/ML CY7C63310-SXC USB3316C-CP-TR USB3250-ABZJ MAX3107ETG+ MAX14632EZK+T LAN9514-JZX CYPD2120-24LQXIT MAX3100CEE+T USB5806/KD USB5826-I/KD USB5826/KD USB5906/KD USB5916/KD USB5926/KD TUSB215QRGYTQ1 NB7NPQ701MMTTBG TUSB213RGYR USB5926-I/KD USB5906-I/KD USB4640I-HZH-03 CY7C63813-SXC CY7C63823-SXC CY7C64215-28PVXC CY7C68013A-128AXC CY7C68013A-56LTXI CY7C68013A-56PVXC CY7C68013A-56PVXI CYPD1120-40LQXI AP43771VDKZ-13 AP43771VFBZ-13 DIO32320MP10 HT42B534-2 FT2232HPQ-TRAY FT312D-32L1C-T KTU1001AEVA-TR