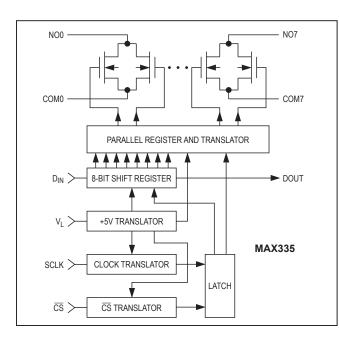

#### **General Description**

The MAX335 analog switch with serial digital interface offers eight separately controlled single-pole-single-throw (SPST) switches. All switches conduct equally in either direction, and on-resistance ( $100\Omega$ ) is constant over the analog signal range.

These CMOS switches can operate continuously with power supplies ranging from  $\pm 4.5$ V to  $\pm 20$ V and handle rail-to-rail analog signals. Upon power-up, all switches are off, and the internal serial and parallel shift registers are reset to zero. The MAX335 is equivalent to two DG211 quad switches but controlled by a serial interface.

The interface is compatible with the Motorola SPI interface standard. Functioning as a shift register, this serial interface allows data (at DIN) to be locked in synchronous with the rising edge of clock (SCLK). The shift register's output (DOUT) enables several MAX335s to be daisy chained.

#### **Applications**

- Serial Data Acquisition and Process Control

- Avionics

- Signal Routing

- Networking

#### **Features**

- 8 Separately Controlled SPST Switches

- SPI-Compatible Serial Interface

- Accepts ±15V Analog Swings

- Multiple Devices Can Be Daisy-Chained

#### **Ordering Information**

| PART      | TEMP RANGE      | PIN-PACKAGE           |

|-----------|-----------------|-----------------------|

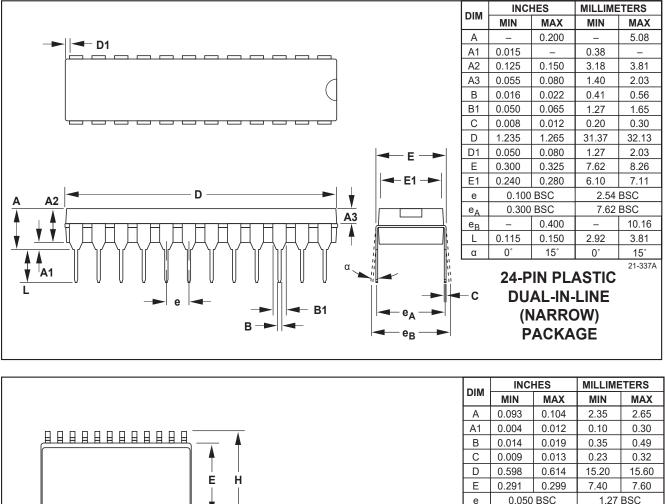

| MAX335CNG | 0°C to +70°C    | 24 Narrow Plastic DIP |

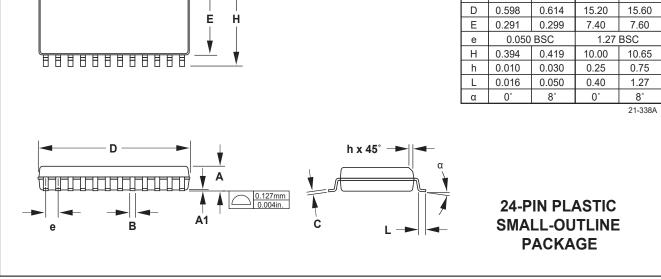

| MAX335CWG | 0°C to +70°C    | 24 Wide SO            |

| MAX335C/D | 0°C to +70°C    | Dice*                 |

| MAX335ENG | -40°C to +85°C  | 24 Narrow Plastic DIP |

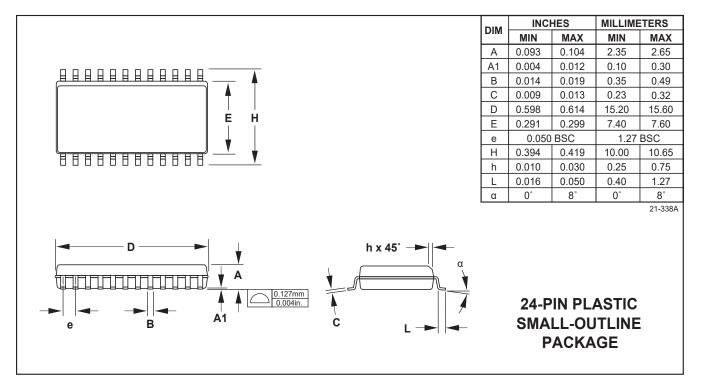

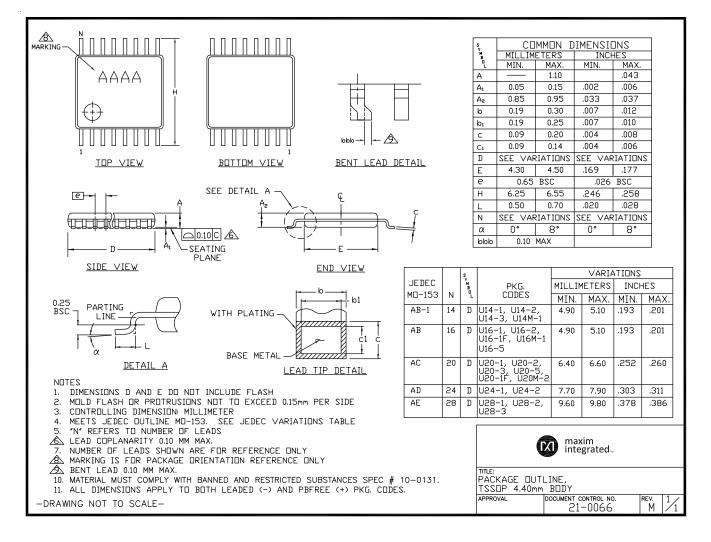

| MAX335EUG | -40°C to +85°C  | 24 TSSOP              |

| MAX335EWG | -40°C to +85°C  | 24 Wide SO            |

| MAX335MRG | -55°C to +125°C | 24 Narrow CERDIP**    |

\*Contact factory for dice specifications.

\*\*Contact factory for availability and processing to MIL-STD-883.

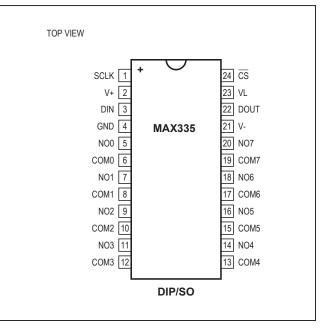

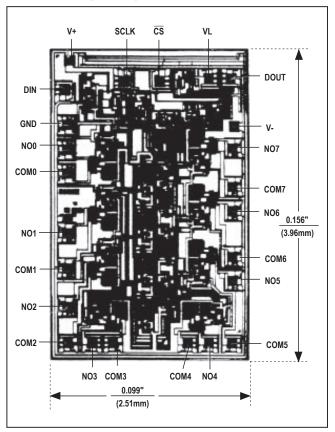

#### **Pin Configuration**

# Serial Controlled, 8-Channel SPST Switch

Lead Temperature (soldering, 10sec) .....+300°C

### **Absolute Maximum Ratings**

| Voltages Referenced to V-                  | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) (Note 1) |

|--------------------------------------------|----------------------------------------------------------------|

| V+                                         | Narrow Plastic DIP                                             |

| GND25V                                     | (derate 13.33mW/°C above +70°C)1067mW                          |

| V <sub>L</sub> (GND - 0.3V) to (V+ + 0.3V) | Wide SO (derate 11.76mW/°C above +70°C)941mW                   |

| SCLK, CS, DIN, DOUT, NO_, COMV2V to V+ +2V | Narrow CERDIP (derate 12.50mW/°C above +70°C)1000mW            |

| or 30mA, whichever occurs first            | TSSOP (derate 12.2mW/°C above +70°C)                           |

| Continuous Current (any terminal)          | Operating Temperature Ranges                                   |

| Peak Current, NO or COM                    | MAX335C0°C to +70°C                                            |

| (pulsed at 1ms, 10% duty cycle MAX)00mA    | MAX335E40°C to +85°C                                           |

|                                            | MAX335MRG55°C to +125°C                                        |

|                                            | Storage Temperature Range65°C to +160°C                        |

**Note 1:** All leads are soldered or welded to PC boards.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

(V<sub>L</sub> = +5V ±10%, V+ = 15V, V- = -15V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                         | SYMBOL               | CONDITIO                                                                   | MIN                      | TYP  | MAX   | UNITS   |      |  |

|-----------------------------------|----------------------|----------------------------------------------------------------------------|--------------------------|------|-------|---------|------|--|

| SWITCH                            |                      |                                                                            |                          |      |       |         |      |  |

| Analog Signal Range               | VANALOG              | $T_A = T_{MIN}$ to $T_{MAX}$                                               | -15                      |      | 15    | V       |      |  |

| On-Resistance                     | Davis                | V <sub>COM</sub> = ±10V,                                                   | T <sub>A</sub> = +25°C   |      | 100   | 150     | Ω    |  |

| On-Resistance                     | R <sub>ON</sub>      | I <sub>NO</sub> = 1mA                                                      |                          |      |       | 200     |      |  |

|                                   |                      | V <sub>COM</sub> = -14V,                                                   | T <sub>A</sub> = +25°C   | -1   | 0.002 | 1       |      |  |

| NO Off-Leakage Current            | hugeners             | V <sub>NO</sub> = +14V                                                     |                          | -20  |       | 20      | nA   |  |

|                                   | I <sub>NO(OFF)</sub> | V <sub>COM</sub> = -14V,                                                   | T <sub>A</sub> = +25°C   | -1   | 0.002 | 1       |      |  |

|                                   |                      | V <sub>NO</sub> = +14V                                                     |                          | -20  |       | 20      |      |  |

|                                   |                      | V <sub>COM</sub> = -14V,                                                   | T <sub>A</sub> = +25°C   | -1   | 0.002 | 1       |      |  |

| COM Off-Leakage Current           |                      | V <sub>NO</sub> = +14V                                                     |                          | -20  |       | 20      | nA   |  |

|                                   | ICOM(OFF)            | V <sub>COM</sub> = -14V,<br>V <sub>NO</sub> = +14V                         | T <sub>A</sub> = +25°C   | -1   | 0.002 | 1       |      |  |

|                                   |                      |                                                                            |                          | -20  |       | 20      |      |  |

|                                   | ICOM(ON)             | $V_{COM} = V_{NO} = +14V$                                                  | T <sub>A</sub> = +25°C   | -2   | 0.01  | 2       | - nA |  |

| COM On-Leakage Current            |                      |                                                                            |                          | -20  |       | 40      |      |  |

| COM ON-Leakage Guneni             |                      | $V_{COM} = V_{NO} = -14V$                                                  | T <sub>A</sub> = +25°C   | -2   | 0.01  | 2       |      |  |

|                                   |                      | VCOM - VNO 14V                                                             |                          | -20  |       | 40      |      |  |

| DIGITAL I/O                       |                      |                                                                            |                          |      |       |         |      |  |

| DIN, SCLK, CS Input Logic         | VIH                  | V <sub>L</sub> = +5V                                                       | 2.4                      |      |       | v       |      |  |

| Threshold High                    | VIH                  | V <sub>L</sub> = +15V                                                      | 11                       |      |       | v       |      |  |

| DIN, SCLK, CS Input Logic         | V <sub>IL</sub>      | V <sub>L</sub> = +5V                                                       |                          |      | 0.8   | v       |      |  |

| Threshold Low                     |                      | V <sub>L</sub> = +15V                                                      |                          |      | 3     | v       |      |  |

| DIN, SCLK, CS Input Current       |                      | $V_{\text{DIN}}, V_{\text{SCLK}}, V_{\overline{\text{CS}}} = 2.4 \text{V}$ |                          | -1   | 0.03  | 1       | μA   |  |

| Threshold High                    | I <sub>INH</sub>     | $V_L$ = +15V, $V_{DIN}$ , $V_{SCLK}$ , $V_{\overline{CS}}$ = 11V           |                          | -1   | 0.03  | 1       | μΛ   |  |

| DIN, SCLK, CS Input Current       | lu u                 | $V_{\text{DIN}}, V_{\text{SCLK}}, V_{\overline{\text{CS}}} = 0.8$          | -1                       | 0.03 | 1     | - μΑ    |      |  |

| Threshold Low                     | I <sub>INL</sub>     | $V_L$ = +15V, $V_{DIN}$ , $V_{SCLK}$                                       | $V_{\overline{CS}} = 3V$ | -1   | 0.03  | 1       | μΛ   |  |

| DOUT Output Voltage<br>Logic High | V <sub>DOUT</sub>    | I <sub>DOUT</sub> = 0.8mA                                                  |                          | 3.5  |       | $V_{L}$ | V    |  |

### **Electrical Characteristics (continued)**

(V<sub>L</sub> = +5V ±10%, V+ = 15V, V- = -15V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                    | SYMBOL                                | CONDITIONS                                                                                          | MIN                    | TYP  | MAX  | UNITS |        |  |

|----------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------|------|------|-------|--------|--|

| DIGITAL I/O                                  |                                       |                                                                                                     |                        |      |      |       |        |  |

| DOUT Output Voltage<br>Logic Low             | V <sub>DOUT</sub>                     | I <sub>DOUT</sub> = -1.6mA                                                                          |                        |      | 0.4  | V     |        |  |

| V <sub>L</sub> RESET Voltage                 | V <sub>LL</sub>                       | (Note 2)                                                                                            | (Note 2)               |      |      |       | V      |  |

| V <sub>L</sub> RESET Voltage                 | V <sub>LH</sub>                       |                                                                                                     | T <sub>A</sub> = +25°C |      |      | 2.4   | V      |  |

| SCLK Input Hysteresis                        | SCLK <sub>HYST</sub>                  |                                                                                                     | T <sub>A</sub> = +25°C |      | 100  |       | mV     |  |

| SWITCH DYNAMIC CHARACT                       | ERISTICS                              |                                                                                                     |                        |      |      |       |        |  |

| Turn-On Time                                 | tou                                   | From rising-edge of $\overline{CS}$                                                                 | T <sub>A</sub> = +25°C |      | 200  | 400   | ne     |  |

| Tum-On Time                                  | ton                                   | From Itsing-edge of CS                                                                              |                        |      |      | 500   | ns     |  |

| Turn-Off Time                                | torr                                  | From rising-edge of $\overline{CS}$                                                                 | T <sub>A</sub> = +25°C |      | 90   | 400   | ns     |  |

|                                              | toff                                  | From hsing-edge of CS                                                                               |                        |      |      | 500   | 115    |  |

| NO Off-Capacitance                           | C <sub>NO(OFF)</sub>                  | V <sub>S</sub> = GND, f = 1MHz                                                                      | T <sub>A</sub> = +25°C |      | 2    |       | pF     |  |

| COM Off-Capacitance                          | C <sub>COM(OFF)</sub>                 | V <sub>S</sub> = GND, f = 1MHz                                                                      | T <sub>A</sub> = +25°C |      | 2    |       | pF     |  |

| Channel On-Capacitance                       | C <sub>COM(ON)</sub>                  | $V_D = V_S = GND,$<br>f = 1MHz                                                                      | T <sub>A</sub> = +25°C |      | 8    |       | pF     |  |

| Off Isolation                                | OIRR                                  | $\begin{array}{l} R_{L} = 100\Omega,  C_{L} = 15 pF, \\ V_{S} = 1V_{RMS},  f = 100 kHz \end{array}$ | T <sub>A</sub> = +25°C |      | 90   |       | dB     |  |

| Channel-to-Channel Crosstalk                 | CCRR                                  | $R_L$ = 50Ω, $C_L$ = 15pF,<br>V <sub>S</sub> = 1V <sub>RMS</sub> , f = 100kHz                       | T <sub>A</sub> = +25°C |      | 100  |       | dB     |  |

| Break-Before-Make Delay                      | T <sub>BBM</sub>                      |                                                                                                     |                        | 15   | 25   |       | ns     |  |

| Clock Feedthrough at S, D<br>(Note 3)        | ESCLK                                 | $D_{LOAD} = S_{LOAD} = 75\Omega$ , measured at S and D                                              | T <sub>A</sub> = +25°C |      |      | 100   | nV-sec |  |

| POWER SUPPLIES                               |                                       |                                                                                                     |                        |      |      |       |        |  |

| Power-Supply Voltage Range                   | V+/V-                                 |                                                                                                     |                        | ±4.5 |      | ±20   | V      |  |

| V <sub>L</sub> Power-Supply Voltage<br>Range | VL                                    |                                                                                                     |                        | 4.5  |      | V+    | V      |  |

|                                              |                                       | $DIN = \overline{CS} = SCLK =$                                                                      | T <sub>A</sub> = +25°C |      | 150  | 300   |        |  |

| V+ Supply Current                            | Supply Current I+ DIN - CS - SCEN - N |                                                                                                     |                        |      |      | 500   | μA     |  |

| V Supply Current                             |                                       | $DIN = \overline{CS} = SCLK =$                                                                      | T <sub>A</sub> = +25°C |      | 0.01 | 10    |        |  |

| V- Supply Current                            | -                                     | 0V/5V                                                                                               |                        |      |      | 10    | μA     |  |

| V Supply Current                             |                                       | $DIN = \overline{CS} = SCLK =$                                                                      | T <sub>A</sub> = +25°C |      | 50   | 100   |        |  |

| V <sub>L</sub> Supply Current                | ۱L                                    | 0V/5V                                                                                               |                        |      |      | 200   | - μΑ   |  |

Note 2: When  $V_L$  falls below this voltage, all switches are set off and the internal shift register is cleared (all zero).

Note 3: Guaranteed, not production tested.

# Serial Controlled, 8-Channel SPST Switch

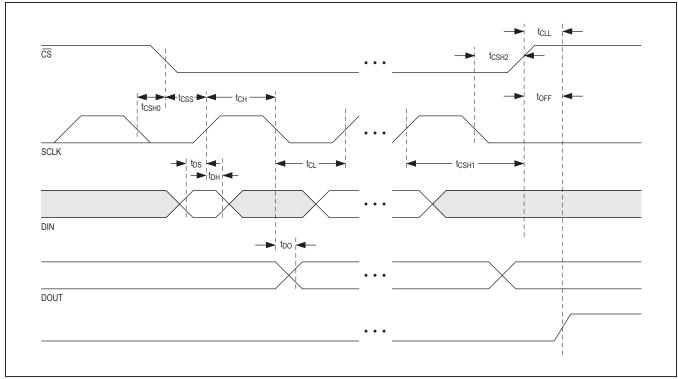

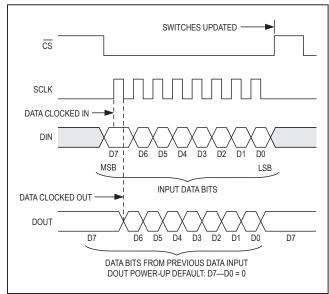

# **Timing Characteristics of Serial Digital Interface (Figure 1)**

(V<sub>L</sub> = +5V ±10%, V+ = 15V, V- = -15V, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                                                | SYMBOL                            | CONDITION                                                        | MIN                    | TYP | MAX | UNITS |     |

|----------------------------------------------------------|-----------------------------------|------------------------------------------------------------------|------------------------|-----|-----|-------|-----|

| SCLK Maximum Frequency                                   | f <sub>SCLK</sub>                 |                                                                  |                        | 2.1 |     |       | MHz |

| Cycle Time                                               | t <sub>CH</sub> + t <sub>CL</sub> |                                                                  |                        | 480 |     |       | ns  |

| CS Lead Time                                             | t <sub>CSS</sub>                  |                                                                  |                        | 240 |     |       | ns  |

| CS Lag Time                                              | t <sub>CSH2</sub>                 |                                                                  |                        | 240 |     |       | ns  |

| SCLK High Time                                           | tсн                               |                                                                  |                        | 190 |     |       | ns  |

| SCLK Low Time                                            | t <sub>CL</sub>                   |                                                                  |                        | 190 |     |       | ns  |

| Data-Setup Time                                          | t <sub>DS</sub>                   |                                                                  |                        | 200 |     |       | ns  |

| Data-Hold Time                                           | t <sub>DH</sub>                   |                                                                  |                        | 0   |     |       | ns  |

| DOUT Data Valid After<br>Falling SCLK                    | t <sub>DO</sub>                   | 50% of SCLK to 10% of<br>DOUT CL = 10pF                          | T <sub>A</sub> = +25°C |     | 240 | 400   | ns  |

| DOUT Data-Hold Time After<br>Rising SCLK (Note 4)        |                                   | C <sub>L</sub> = 10pF                                            | 1                      | 0   |     |       | ns  |

| Rise Time of DOUT (Note 3)                               |                                   | 20% V <sub>L</sub> to 70% V <sub>L</sub> , C <sub>L</sub> =      | 10pF                   |     |     | 100   | ns  |

| Allowa <u>ble</u> Rise Time at DIN,<br>SCLK, CS (Note 3) |                                   | 20% V <sub>L</sub> to 70% V <sub>L</sub> , C <sub>L</sub> = 10pF |                        |     |     | 2     | μs  |

| Fall Time of DOUT (Note 3)                               |                                   | 70% V <sub>L</sub> to 20% V <sub>L</sub> , C <sub>L</sub> =      |                        |     | 100 | ns    |     |

| Allowable Fall Time at DIN,<br>SCLK, CS (Note 3)         |                                   | 70% V <sub>L</sub> to 20% V <sub>L</sub> , C <sub>L</sub> =      | 10pF                   |     |     | 2     | μs  |

Note 4: This specification guarantees that data at  $\mathsf{D}_{\mathsf{OUT}}$  never appears before SCLK's falling edge.

# Serial Controlled, 8-Channel SPST Switch

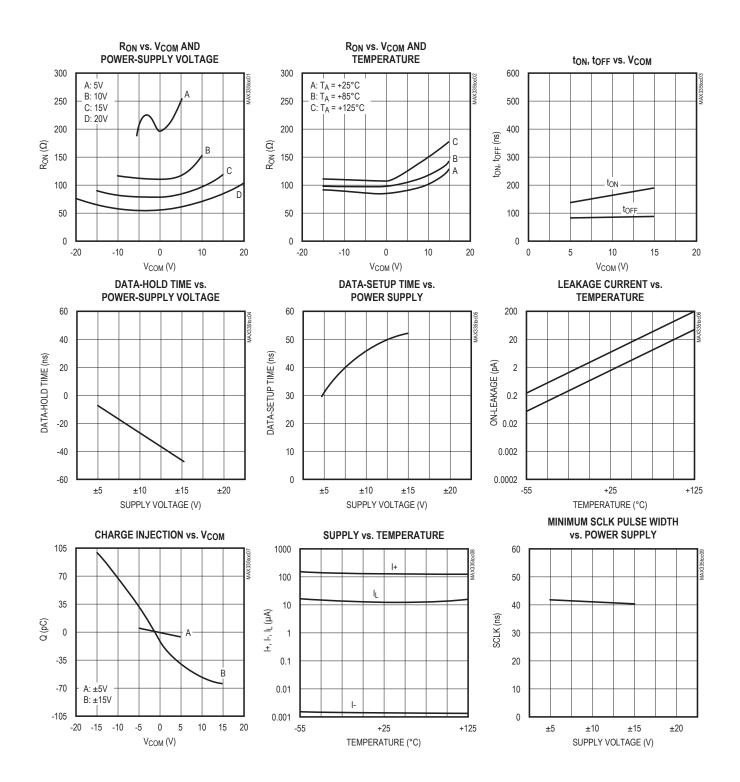

### **Typical Operating Characteristics**

(V+ = +15V, V- = -15V, V<sub>L</sub>= 5V,  $T_A$  = +25°C, unless otherwise noted.)

# Serial Controlled, 8-Channel SPST Switch

#### Pin Description

| PIN | NAME | FUNCTION                |

|-----|------|-------------------------|

| 1   | SCLK | Serial Clock Input      |

| 2   | V+   | Positive Supply Voltage |

| 3   | DIN  | Serial Data Input       |

| 4   | GND  | Ground                  |

| 5   | NOØ  | Switch 0                |

| 6   | COMØ | Switch 0                |

| 7   | NO1  | Switch 1                |

| 8   | COM1 | Switch 1                |

| 9   | NO2  | Switch 2                |

| 10  | COM2 | Switch 2                |

| 11  | NO3  | Switch 3                |

| 12  | COM3 | Switch 3                |

| 13  | COM4 | Switch 4                |

| 14  | NO4  | Switch 4                |

| 15  | COM5 | Switch 5                |

| 16  | NO5  | Switch 5                |

| 17  | COM6 | Switch 6                |

| 18  | NO6  | Switch 6                |

| 19  | COM7 | Switch 7                |

| 20  | NO7  | Switch 7                |

| 21  | V-   | Negative Supply Voltage |

| 22  | DOUT | Serial Data Output      |

| 23  | VL   | Logic Supply/Reset      |

| 24  | CS   | Chip Select             |

### **Detailed Description**

#### **Serial Digital Interface**

#### **Basic Operation**

Refer to Figure 2. The MAX335 interface can be thought of as an 8-bit shift register controlled by  $\overline{CS}$ . While  $\overline{CS}$  is low, input data appearing at DIN is clocked into the shift register synchronous with SCLK's rising edge. The data is an 8-bit word, each bit controlling one of eight switches in the MAX335 (Table 1). DOUT is the output of the shift register, with data appearing synchronous with SCLK's falling edge. Data at DOUT is simply the input data delayed by eight clock cycles.

When shifting the input data, D7 is the first bit in and out of the shift register. While shifting data, the switches remain in their original configuration. When the 8 bits of data have been shifted in,  $\overline{CS}$  is brought high. This updates the new switch configuration and inhibits further data from entering the shift register. Transitions at DIN and SCLK have no effect when  $\overline{CS}$  is high, and DOUT holds the last bit in the shift register.

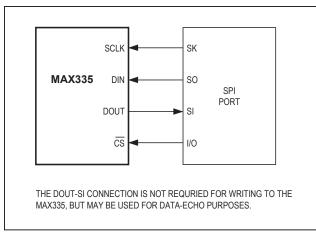

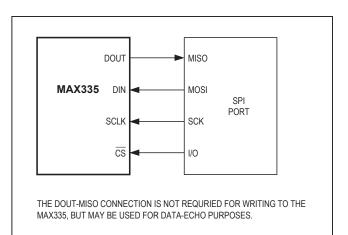

The MAX335 three-wire serial interface is compatible with the SPI<sup>M</sup> and Microwire<sup>M</sup> standards. If interfacing with a Motorola processor serial interface, set CPOL = 0. The MAX335 is considered a slave device (Figures 2 and 3). Upon power-up, the shift register contains all zeros, and all switches are off.

The latch that drives the analog switch is only updated on the rising edge of  $\overline{CS}$  when SCLK is low. If SCLK is high when  $\overline{CS}$  rises, the latch will not be updated until SCLK goes low. The CPOL = 1, CPHA = 1 SPI configuration does not update the latch correctly.

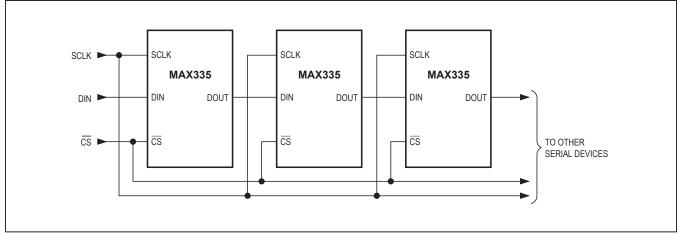

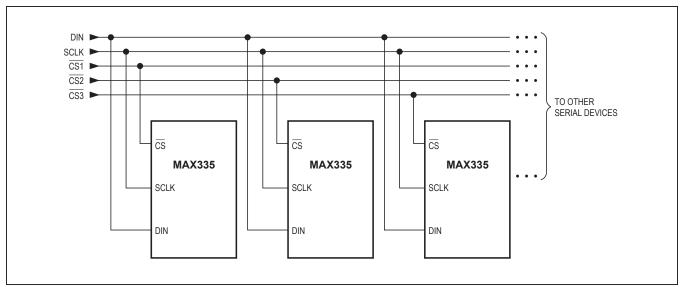

#### **Daisy Chaining**

For a simple interface using several MAX335s, "daisy chain" the shift registers as shown in Figure 5. The  $\overline{CS}$  pins of all devices are connected together, and a stream of data is shifted through the MAX335s in series. When  $\overline{CS}$  is brought high, all switches are updated simultaneously. Additional shift registers may be included anywhere in series with the MAX335 data chain.

#### Addressable Serial Interface

When several serial devices are configured as slaves, addressable by the processor, DIN pins of each MAX335 are connected together (Figure 6). Address decode logic individually controls  $\overline{CS}$  of each slave device. When a slave is selected, its  $\overline{CS}$  is brought low, data is shifted in, and  $\overline{CS}$  is brought high to latch the data. Typically, only one slave is addressed at a time. DOUT is not used.

#### **Digital Feedthrough**

Digital feedthrough energy measures 100nV-sec, which means that with no filtering at the signal channel, feedthrough from a sharply rising clock edge into an unfiltered switch channel can be measured at 1Vp-p for 100ns. However, even 100pF capacitance in the switch channel, when combined with the switch resistance, yields a filter that reduces this transient to 10mVp-p typical. To reduce digital feedthrough, hysteresis (150mV typ) was added to the SCLK input so triangle or sine waves may be used.

Figure 1. Timing Diagram

Figure 2. Three-Wire Interface Timing

# Serial Controlled, 8-Channel SPST Switch

|    |    | FUNCTION |    |    |    |    |    |                      |

|----|----|----------|----|----|----|----|----|----------------------|

| D7 | D6 | D5       | D4 | D3 | D2 | D1 | D0 | FUNCTION             |

| 0  | Х  | Х        | Х  | Х  | Х  | Х  | Х  | Switch 7 open (off)  |

| 1  | Х  | Х        | Х  | Х  | Х  | Х  | Х  | Switch 7 closed (on) |

| Х  | 0  | Х        | Х  | Х  | Х  | Х  | Х  | Switch 6 open        |

| Х  | 1  | Х        | Х  | Х  | Х  | Х  | Х  | Switch 6 closed      |

| Х  | Х  | 0        | Х  | Х  | X  | Х  | Х  | Switch 5 open        |

| Х  | Х  | 1        | Х  | Х  | Х  | Х  | Х  | Switch 5 closed      |

| Х  | Х  | Х        | 0  | Х  | Х  | Х  | Х  | Switch 4 open        |

| Х  | Х  | Х        | 1  | Х  | Х  | Х  | Х  | Switch 4 closed      |

| Х  | Х  | Х        | Х  | 0  | Х  | Х  | Х  | Switch 3 open        |

| Х  | Х  | Х        | Х  | 1  | X  | Х  | Х  | Switch 3 closed      |

| Х  | Х  | Х        | Х  | Х  | 0  | Х  | Х  | Switch 2 open        |

| Х  | Х  | Х        | Х  | Х  | 1  | Х  | Х  | Switch 2 closed      |

| Х  | Х  | Х        | Х  | Х  | Х  | 0  | Х  | Switch 1 open        |

| Х  | Х  | Х        | Х  | Х  | Х  | 1  | Х  | Switch 1 closed      |

| Х  | Х  | Х        | Х  | Х  | Х  | Х  | 0  | Switch 0 open        |

| Х  | Х  | Х        | Х  | Х  | Х  | Х  | 1  | Switch 0 closed      |

### Table 1. Serial-Interface Switch Programming

#### X = Don't care

Figure 3. Connections for Microwire

Figure 4. Connections for SPI

# Serial Controlled, 8-Channel SPST Switch

Figure 5. Daisy-Chained Connection

Figure 6. Addressable Serial Interface

### **Applications Information**

#### 8 x 1 Multiplexer

To use the MAX335 as an 8 x 1 multiplexer, tie all drains together (COM0 to COM7); the mux inputs now source each switch (NO0 to NO7). Input a single 0V to +3V pulse at DIN. As this is clocked through the register by SCLK, each switch will sequence on one at a time.

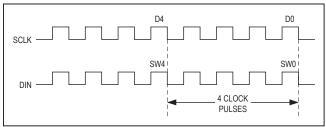

#### 4-2 Differential Multiplexer

To use the MAX335 as a 4-2 differential multiplexer, tie COM0 through COM3 together and COM4 through COM7 together. Differential inputs will be the source inputs as follows: (NO0, NO4), (NO1, NO5), (NO2, NO6), (NO3, NO7). Figure 7 shows the serial input control at DIN required to turn on two switches making a differential multiplexer.

Figure 7. Differential Multiplexer Input Control

$\overline{\text{CS}}$  is held low for four clock pulses; the first pulse is clocked into the fifth switch position as the second pulse is clocked into the first switch position.  $\overline{\text{CS}}$  is pulled high to update switches; then  $\overline{\text{CS}}$  is pulled low, and SCLK advances pulses to S1 and S5 positions, where  $\overline{\text{CS}}$  is pulled high to update, etc.

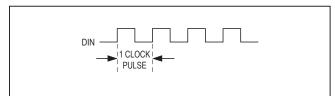

#### **SPDT Switches**

Tie COM0 to NO1 so that NO0 and COM1 are now inputs and COM0/NO1 is the common output. SP is common output. Up to four SPDT switches can be made from each MAX335. Multiples of four or more can be made by daisy chaining devices. In Figure 8, DIN is a pulse train. Again,  $\overline{CS}$  is held low to clock in pulses and  $\overline{CS}$  is pulled high to update;  $\overline{CS}$  is held low to shift pulses, then pulled high to update, etc.

Figure 8. Serial-Input Control for SPDT Switch

#### **Reset Function**

Pulsing  $V_L$  below +0.8V initiates the power-up reset function. The switches are set to the off position, and the serial shift register is reset to all zeros.

#### **Power-Supply Operation**

The MAX335 operates with V =  $\pm 4.5$ V to  $\pm 20$ V and V<sub>L</sub> = +5V. With V- tied to ground, the part operates with V+ =  $\pm 10$ V to  $\pm 30$ V.

The V<sub>L</sub> supply sets TTL input compatibility at a 1.6V switching threshold. As V<sub>L</sub> is raised, the switching threshold is raised, so the part is no longer TTL compatible. The MAX335 also operates with a single power supply: V<sub>L</sub> = V+ and V- = 0V. With V<sub>L</sub> tied to V+, the V<sub>L</sub> supply cannot be used as a reset function.

#### **Chip Topography**

TRANSISTOR COUNT: 387 SUBSTRATE CONNECTED TO V+.

## Serial Controlled, 8-Channel SPST Switch

### Package Information

# Serial Controlled, 8-Channel SPST Switch

### **Package Information (continued)**

## Serial Controlled, 8-Channel SPST Switch

### **Package Information (continued)**

# Serial Controlled, 8-Channel SPST Switch

### **Revision History**

| REVISION | REVISION | DESCRIPTION                                                                                         | PAGES   |

|----------|----------|-----------------------------------------------------------------------------------------------------|---------|

| NUMBER   | DATE     |                                                                                                     | CHANGED |

| 4        | 7/17     | Updated Min and Typ values of Break-Before-Make Delay in<br><i>Electrical Characteristics</i> table | 3       |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Analogue Switch ICs category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

FSA3051TMX NLAS4684FCTCG NLAS5223BLMNR2G NLVAS4599DTT1G NLX2G66DMUTCG 425541DB 425528R 099044FB NLAS5123MNR2G PI5A4157CEX NLAS4717EPFCT1G PI5A3167CCEX SLAS3158MNR2G PI5A392AQE PI5A4157ZUEX PI5A3166TAEX FSA634UCX XS3A1T3157GMX TC4066BP(N,F) DG302BDJ-E3 PI5A100QEX HV2605FG-G HV2301FG-G RS2117YUTQK10 RS2118YUTQK10 RS2227XUTQK10 ADG452BRZ-REEL7 MAX4066ESD+ MAX391CPE+ MAX4730EXT+T MAX314CPE+ BU4066BCFV-E2 MAX313CPE+ BU4S66G2-TR NLASB3157MTR2G TS3A4751PWR NLAS4157DFT2G NLAST4599DFT2G NLAST4599DTT1G DG419LDY+T DG300BDJ-E3 DG2503DB-T2-GE1 TC4W53FU(TE12L,F) HV2201FG-G 74HC2G66DC.125 DG3257DN-T1-GE4 ADG619BRMZ-REEL ADG1611BRUZ-REEL7 DG2535EDQ-T1-GE3 LTC201ACN#PBF