### **General Description**

The MAX3882A is a deserializer combined with clock and data recovery and limiting amplifier ideal for converting 2.488Gbps serial data to 4-bit-wide, 622Mbps parallel data for SDH/SONET applications. The device accepts serial NRZ input data as low as 10mVp-p of 2.488Gbps and generates four parallel LVDS data outputs at 622Mbps. Included is an additional high-speed serial data input for system loopback diagnostic testing. For data acquisition, the MAX3882A does not require an external reference clock. However, if needed, the loopback input can be connected to an external reference clock of 155MHz or 622MHz to maintain a valid clock output in the absence of input data transitions. Additionally, a TTL-compatible loss-of-lock output is provided. The device provides a vertical threshold adjustment to compensate for optical noise generated by EDFAs in WDM transmission systems. The MAX3882A operates from a single +3.3V supply and consumes 610mW.

The MAX3882A's jitter performance exceeds all SDH/ SONET specifications. The device is available in a 6mm × 6mm, 36-pin TQFN package.

### **Applications**

SDH/SONET Receivers and Regenerators Add/Drop Multiplexers Digital Cross-Connects SDH/SONET Test Equipment **DWDM Transmission Systems**

Typical Application Circuits appear at end of data sheet.

#### **Features**

- ♦ No Reference Clock Required for Data Acquisition

- ♦ Serial Input Rate: 2.488Gbps

- ♦ Fully Integrated Clock and Data Recovery with **Limiting Amplifier and 1:4 Demultiplexer**

- ♦ Parallel Output Rate: 622Mbps

- ♦ Differential Input Range: 10mVp-p to 1.6Vp-p without Threshold Adjust

- ◆ Differential Input Range: 50mVp-p to 600mVp-p with Threshold Adjust

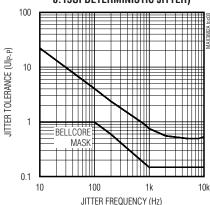

- ♦ 0.65UI High-Frequency Jitter Tolerance

- ♦ Loss-of-Lock (LOL) Indicator

- ♦ Wide Input Threshold Adjust Range: ±170mV

- ♦ Maintain Valid Clock Output in Absence of Data **Transitions**

- ♦ System Loopback Input Available for System **Diagnostic Testing**

- ♦ Operating Temperature Range -40°C to +85°C

- ♦ Low Power Dissipation: 610mW at +3.3V

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |  |  |

|--------------|----------------|-------------|--|--|

| MAX3882AETX+ | -40°C to +85°C | 36 TQFN-EP* |  |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

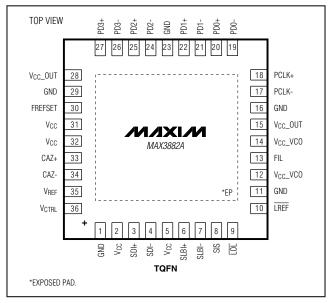

# Pin Configuration

<sup>\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>CC</sub> 0.5 to +5.0V                                   |

|--------------------------------------------------------------------------------|

| Input Voltage Levels                                                           |

| (SDI+, SDI-, SLBI+, SLBI-)(V <sub>CC</sub> - 1.0V) to (V <sub>CC</sub> + 0.5V) |

| Input Current Levels (SDI+, SDI-, SLBI+, SLBI-)±20mA                           |

| LVDS Output Voltage Levels                                                     |

| (PCLK±, PD_±)0.5V to (V <sub>CC</sub> + 0.5V)                                  |

| Voltage at LOL, SIS, LREF, VREF, FIL, CAZ+,                                    |

| CAZ-, V <sub>CTRL</sub> , FREFSET0.5V to (V <sub>CC</sub> + 0.5V)              |

| Continuous Power Dissipation (T <sub>A</sub> = - | +70°C)             |

|--------------------------------------------------|--------------------|

| 36-Pin TQFN (derate 35.7mW/°C a                  | above +70°C)2856mW |

| Operating Temperature Range                      | 40°C to +85°C      |

| Storage Temperature Range                        | 55°C to +150°C     |

| Lead Temperature (soldering, 10s)                | +300°C             |

|                                                  |                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{ to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values are at } +3.3 \text{V} \text{ and at } T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                                                                              | SYMBOL              | CONDITIONS                                                     | MIN                   | TYP | MAX                   | UNITS             |

|----------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------|-----------------------|-----|-----------------------|-------------------|

| Supply Current                                                                         | Icc                 |                                                                |                       | 185 | 230                   | mA                |

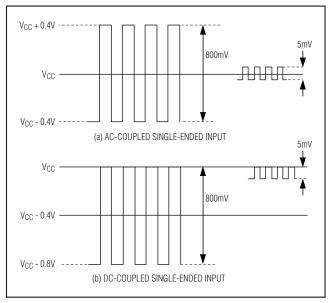

| Single-Ended Input Voltage<br>Range                                                    | VIS                 | Figure 1                                                       | V <sub>CC</sub> - 0.8 |     | V <sub>CC</sub> + 0.4 | V                 |

| Input Common-Mode Voltage<br>Range                                                     |                     | Figure 1                                                       | V <sub>CC</sub> - 0.4 |     | Vcc                   | V                 |

| Input Termination to V <sub>CC</sub>                                                   | R <sub>IN</sub>     |                                                                | 42.5                  | 50  | 57.5                  | Ω                 |

| Differential Input Voltage Range<br>with Threshold Adjust Enabled<br>SDI+, SDI-        |                     | Figure 2                                                       | 100                   |     | 600                   | mV <sub>P-P</sub> |

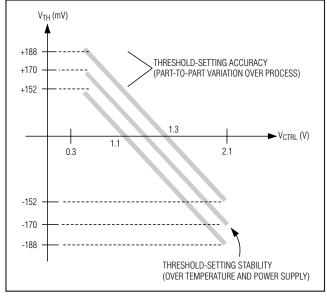

| Threshold Adjustment Range                                                             | VTH                 | Figure 2                                                       | -170                  |     | +170                  | mV                |

| Threshold-Control Voltage                                                              | VCTRL               | (Note 2)                                                       | 0.302                 |     | 2.097                 | V                 |

| Threshold-Control Linearity                                                            |                     |                                                                |                       | ±5  |                       | %                 |

| Threshold Setting Accuracy                                                             |                     | Figure 2                                                       | -18                   |     | +18                   | mV                |

| Threshold Setting Stability                                                            |                     | 15mV ≤ IV <sub>TH</sub> I ≤ 80mV                               | -6                    |     | +6                    | mV                |

| Threshold Setting Stability                                                            |                     | $80\text{mV} < \text{IV}_{\text{TH}}\text{I} \le 170\text{mV}$ | -12                   |     | +12                   | 1110              |

| V <sub>REF</sub> Voltage Output                                                        |                     | $R_L = 50k\Omega$                                              | 2.14                  | 2.2 | 2.24                  | V                 |

| LVDS Output High Voltage                                                               | VoH                 |                                                                |                       |     | 1.475                 | V                 |

| LVDS Output Low Voltage                                                                | V <sub>OL</sub>     |                                                                | 0.925                 |     |                       | V                 |

| LVDS Differential Output Voltage                                                       | IV <sub>OD</sub> I  |                                                                | 250                   |     | 400                   | mV                |

| LVDS Change in Magnitude of<br>Differential Output Voltage for<br>Complementary States | ΔIV <sub>OD</sub> I |                                                                |                       |     | 25                    | mV                |

| LVDS Offset Output Voltage                                                             |                     |                                                                | 1.125                 |     | 1.275                 | V                 |

| LVDS Change in Magnitude of<br>Output Offset Voltage for<br>Complementary States       | ΔIV <sub>OS</sub> I |                                                                |                       |     | 25                    | mV                |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0 \text{ to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values are at } +3.3 \text{V} \text{ and at } T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                          | SYMBOL          | CONDITIONS                     | MIN | TYP | MAX | UNITS |

|------------------------------------|-----------------|--------------------------------|-----|-----|-----|-------|

| LVDS Differential Output Impedance |                 |                                | 80  |     | 120 | Ω     |

| LVDS Output Current                |                 | Short together or short to GND |     |     | 12  | mA    |

| LVTTL Input High Voltage           | VIH             |                                | 2.0 |     |     | V     |

| LVTTL Input Low Voltage            | VIL             |                                |     |     | 0.8 | V     |

| LVTTL Input Current                |                 |                                | -10 |     | +10 | μΑ    |

| LVTTL Output High Voltage          | Voh             | I <sub>OH</sub> = +20μA        | 2.4 |     |     | V     |

| LVTTL Output Low Voltage           | V <sub>OL</sub> | I <sub>OL</sub> = -1mA         |     |     | 0.4 | V     |

Note 1: At -40°C, DC characteristics are guaranteed by design and characterization.

Note 2: Voltage applied to V<sub>CTRL</sub> pin is from 0.302V to 2.097V when input threshold is adjusted from +170mV to -170mV.

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{ to } +3.6 \text{ V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values are at } +3.3 \text{V} \text{ and at } T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 3)

| PARAMETER                                                             | SYMBOL                | CONDITIONS                       | MIN  | TYP   | MAX   | UNITS             |

|-----------------------------------------------------------------------|-----------------------|----------------------------------|------|-------|-------|-------------------|

| Serial Input Data Rate                                                |                       |                                  |      | 2.488 |       | Gbps              |

| Differential Input Voltage<br>Threshold Adjust Disabled<br>SDI+, SDI- | V <sub>ID</sub>       | (Note 4) Figure 1                | 10   |       | 1600  | mV <sub>P-P</sub> |

| Differential Input Voltage SLBI+,<br>SLBI-                            |                       |                                  | 50   |       | 800   | mV <sub>P-P</sub> |

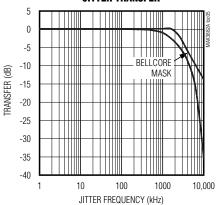

| Jitter Peaking                                                        | J <sub>P</sub>        | f ≤ 2MHz                         |      |       | 0.1   | dB                |

| Jitter Transfer Bandwidth                                             | J <sub>BW</sub>       |                                  |      | 1.7   | 2.0   | MHz               |

|                                                                       |                       | f = 100kHz                       | 3.1  | 4.1   |       | UI <sub>P-P</sub> |

| Sinusoidal Jitter Tolerance                                           |                       | f = 1MHz                         | 0.62 | 1.0   |       |                   |

|                                                                       |                       | f = 10MHz                        | 0.44 | 0.6   |       |                   |

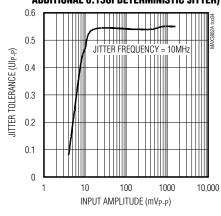

| Sinusoidal Jitter Tolerance with                                      |                       | f = 100kHz                       |      | 4.1   |       | ]                 |

| Threshold Adjust Enabled                                              |                       | f = 1MHz                         |      | 0.75  |       | UI <sub>P-P</sub> |

| (Note 5)                                                              |                       | f = 10MHz                        |      | 0.41  |       |                   |

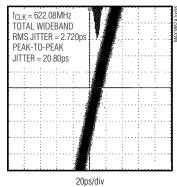

| Jitter Generation                                                     | JGEN                  | (Note 6)                         |      | 2.7   |       | psrms             |

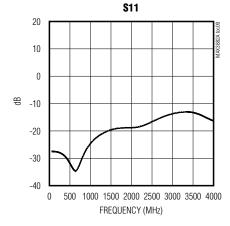

| Differential Input Return Loss                                        | 20log S <sub>11</sub> | 100kHz to 2.5GHz                 |      | 17    |       | - dB              |

| Differential input heturn coss                                        | 20109[511]            | 2.5GHz to 4.0GHz                 |      | 15    |       | UB                |

| Tolerated Consecutive Identical Digits                                |                       | BER = 10-10                      |      | 2000  |       | Bits              |

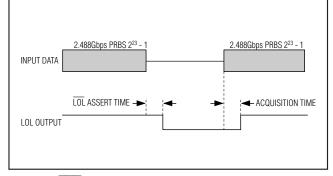

| Acquisition Time (Note 7)                                             |                       | 0011 pattern                     |      | 0.6   |       |                   |

| Figure 4                                                              |                       | PRBS 2 <sup>23</sup> - 1 pattern |      | 0.62  | 1.5   | ms                |

| LOL Assert Time                                                       |                       | Figure 4                         | 2.3  |       | 100.0 | μs                |

| Low-Frequency Cutoff for DC Offset Cancellation Loop                  |                       | CAZ = 0.1μF                      |      | 4     |       | kHz               |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0 \text{ to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values are at } +3.3 \text{V} \text{ and at } T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 3)

|                                         |                                 |                           |     |      | , , |       |

|-----------------------------------------|---------------------------------|---------------------------|-----|------|-----|-------|

| PARAMETER                               | SYMBOL                          | CONDITIONS                | MIN | TYP  | MAX | UNITS |

| Reference Clock Frequency               |                                 | FREFSET = V <sub>CC</sub> |     | 155  |     | MHz   |

| Neterence Clock Frequency               |                                 | FREFSET = GND             |     | 622  |     | IVIDZ |

| Reference Clock Accuracy                |                                 |                           |     | ±100 |     | ppm   |

| VCO Frequency Drift                     |                                 | (Note 8)                  |     | 400  |     | ppm   |

| Data Output Rate                        |                                 |                           |     | 622  |     | Mbps  |

| Clock Output Frequency                  |                                 |                           |     | 622  |     | MHz   |

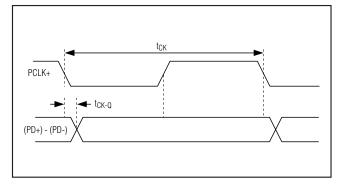

| Output Clock-to-Data Delay              | tck-q                           | (Note 9)                  | -80 |      | +80 | ps    |

| Clock Output Duty Cycle                 |                                 |                           | 45  | 50   | 55  | %     |

| Clock and Data Output Rise/Fall<br>Time | t <sub>R</sub> , t <sub>F</sub> | 20% to 80%                | 100 |      | 250 | ps    |

| LVDS Differential Skew                  | tskew1                          | Any differential pair     |     |      | 50  | ps    |

| LVDS Channel-to-Channel Skew            | tskew2                          | PD_±                      |     |      | 100 | ps    |

- **Note 3:** AC characteristics are guaranteed by design and characterization.

- Note 4: Jitter tolerance is guaranteed (BER ≤ 10<sup>-10</sup>) within this input voltage range. Input threshold adjust is disabled when V<sub>CTRL</sub> is connected to V<sub>CC</sub>.

- **Note 5:** Measured with the input amplitude set at 100mV<sub>P-P</sub> differential swing with a 20mV offset and an input edge speed of 145ps (4th-order Bessel filter with f<sub>3dB</sub> = 1.8GHz).

- **Note 6:** Measured with  $10mV_{P-P}$  OC-48 differential input with PRBS  $2^{23}$  1 and BW = 12kHz to 20MHz.

- **Note 7:** Measured at OC-48 data rate using a 0.068µF loop-filter capacitor.

- Note 8: Under LOL condition, the CDR clock output is set by the external reference clock.

- **Note 9:** Relative to the falling edge of PCLK+. See Figure 3.

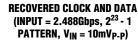

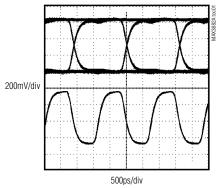

**Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

**SUPPLY CURRENT vs. TEMPERATURE**

JITTER TOLERANCE (2.48832Gbps, 2<sup>23</sup> - 1 PATTERN, VIN = 16mVP-P WITH ADDITIONAL 0.15UI DETERMINISTIC JITTER)

JITTER TOLERANCE vs. INPUT AMPLITUDE (2.48832Gbps, 2<sup>23</sup> - 1 PATTERN, WITH **ADDITIONAL 0.15UI DETERMINISTIC JITTER)**

**JITTER TRANSFER**

PARALLEL CLOCK OUTPUT JITTER

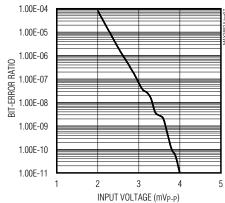

**BIT-ERROR RATE vs. INPUT AMPLITUDE**

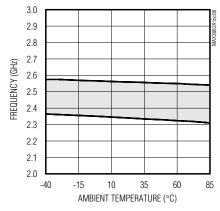

**PULLIN RANGE**

## **Pin Description**

| PIN               | NAME                 | FUNCTION                                                                                                                 |

|-------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1, 11, 16, 23, 29 | GND                  | Supply Ground                                                                                                            |

| 2, 5, 31, 32      | V <sub>C</sub> C     | +3.3V Supply Voltage                                                                                                     |

| 3                 | SDI+                 | Positive Data Input. 2.488Gbps serial data stream, CML.                                                                  |

| 4                 | SDI-                 | Negative Data Input. 2.488Gbps serial data stream, CML.                                                                  |

| 6                 | SLBI+                | Positive System Loopback Input or Positive Reference Clock Input, CML                                                    |

| 7                 | SLBI-                | Negative System Loopback Input or Negative Reference Clock Input, CML                                                    |

| 8                 | SIS                  | Signal Input Selection, LVTTL. Low for normal data, high for system loopback.                                            |

| 9                 | LOL                  | Loss-of-Lock Output, LVTTL, Active Low                                                                                   |

| 10                | LREF                 | TTL Control Input for PLL Clock Holdover. Low for PLL lock to reference clock, high for PLL lock to input data.          |

| 12, 14            | V <sub>CC</sub> _VCO | Supply Voltage for the VCO                                                                                               |

| 13                | FIL                  | PLL Loop-Filter Capacitor Input. Connect a 0.068µF loop-filter capacitor between FIL and VCC_VCO.                        |

| 15, 28            | V <sub>CC</sub> OUT  | Supply Voltage for LVDS Output Buffers                                                                                   |

| 17                | PCLK-                | Negative Clock Output, LVDS                                                                                              |

| 18                | PCLK+                | Positive Clock Output, LVDS                                                                                              |

| 19                | PD0-                 | Negative Data Output, LVDS                                                                                               |

| 20                | PD0+                 | Positive Data Output, LVDS                                                                                               |

| 21                | PD1-                 | Negative Data Output, LVDS                                                                                               |

| 22                | PD1+                 | Positive Data Output, LVDS                                                                                               |

| 24                | PD2-                 | Negative Data Output, LVDS                                                                                               |

| 25                | PD2+                 | Positive Data Output, LVDS                                                                                               |

| 26                | PD3-                 | Negative Data Output, LVDS, MSB                                                                                          |

| 27                | PD3+                 | Positive Data Output, LVDS, MSB                                                                                          |

| 30                | FREFSET              | Sets Reference Frequency. LVTTL low for 622MHz/667MHz reference, high for 155MHz/167MHz reference.                       |

| 33                | CAZ+                 | Positive Capacitor Input for DC Offset-Cancellation Loop. Connect a 0.1µF capacitor between CAZ+ and CAZ                 |

| 34                | CAZ-                 | Negative Capacitor Input for DC Offset-Cancellation Loop. Connect a 0.1µF capacitor between CAZ+ and CAZ                 |

| 35                | V <sub>REF</sub>     | 2.2V Bandgap Reference Voltage Output. Optionally used for threshold adjustment.                                         |

| 36                | VCTRL                | Analog Control Input for Threshold Adjustment. Connect to V <sub>CC</sub> to disable threshold adjust.                   |

| _                 | EP                   | Exposed Pad. The exposed pad must be soldered to the circuit board ground for proper thermal and electrical performance. |

### **Detailed Description**

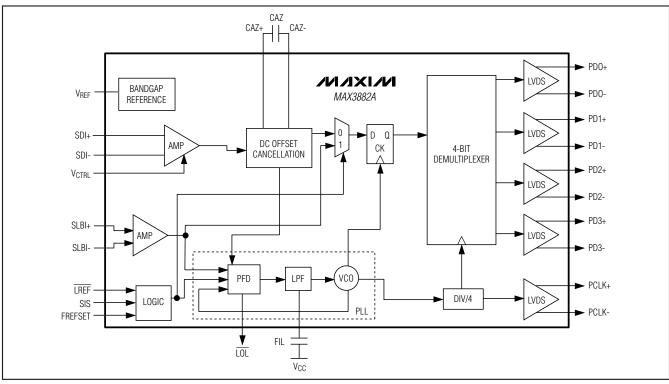

The MAX3882A deserializer with clock and data recovery and limiting amplifier converts 2.488Gbps serial data to clean 4-bit-wide, 622Mbps LVDS parallel data. The device combines a limiting amplifier with a fully integrated phase-locked loop (PLL), data retiming block, 4-bit demultiplexer, clock divider, and LVDS output buffer (Figure 5). The PLL consists of a phase/frequency detector (PFD), loop filter, and voltage- controlled oscillator (VCO). The MAX3882A is designed to deliver the best combination of jitter performance and power dissi-

pation by using a fully differential signal architecture and low-noise design techniques.

The input signal to the device (SDI) passes through a DC offset control block, which balances the input signal to a zero crossing at 50%. The PLL recovers the serial clock from the serial input data stream and produces the properly aligned data and the buffered recovered clock. The frequency of the recovered clock is divided by four and converted to differential LVDS parallel output PCLK. The demultiplexer generates 4-bit-wide 622Mbps parallel data.

Figure 1. Definition of Input Voltage Swing

Figure 2. Relationship Between Control Voltage and Threshold Voltage

Figure 3. Definition of Clock-to-Q Delay

Figure 4. LOL Assert Time and PLL Acquisition Time Measurement

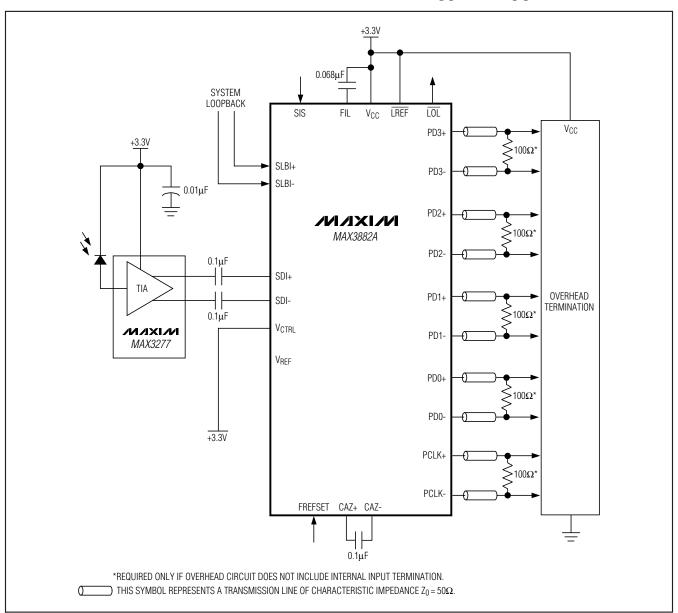

#### **Input Amplifier**

The SDI inputs of the MAX3882A accept serial NRZ data at 2.488Gbps with 10mV<sub>P-P</sub> to 1600mV<sub>P-P</sub> amplitude. The input sensitivity is 10mV<sub>P-P</sub>, at which the jitter tolerance is met for a BER of 10<sup>-10</sup> when the threshold adjust is not used. The input sensitivity is as low as 4mV<sub>P-P</sub> for a BER of 10<sup>-10</sup>. The MAX3882A is designed to directly interface with a transimpedance amplifier (MAX3277).

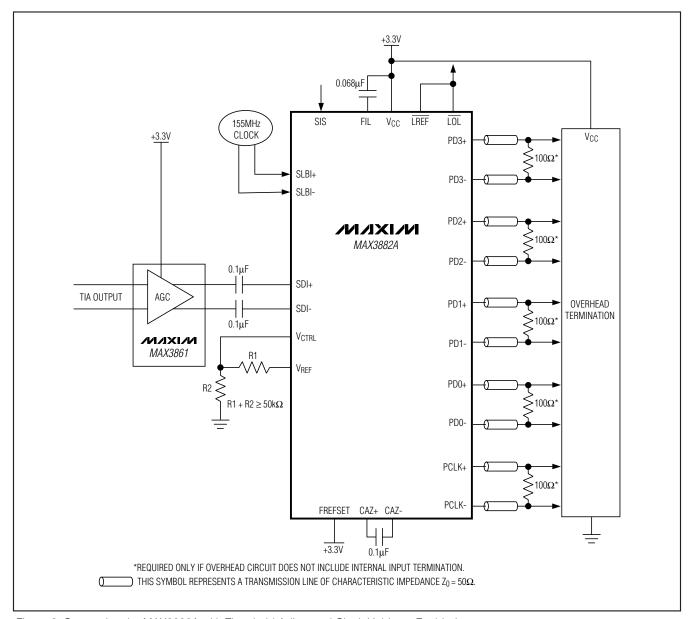

For applications when vertical threshold adjustment is needed, the MAX3882A can be connected to the output of an AGC amplifier (MAX3861). Here, the input voltage range is 50mV<sub>P-P</sub> to 600mV<sub>P-P</sub>. See the *Design Procedure* section for decision threshold adjust.

#### **Phase Detector**

The phase detector in the MAX3882A produces a voltage proportional to the phase difference between the incoming data and the internal clock. Because of its feedback nature, the PLL drives the error voltage to zero, aligning the recovered clock to the center of the incoming data eye for retiming.

#### **Frequency Detector**

The digital frequency detector (FD) acquires frequency lock without using an external reference clock. The frequency difference between the received data and the VCO clock is derived by sampling the in-phase and quadrature VCO outputs on both edges of the data input signal. Depending on the polarity of the frequency difference, the FD drives the VCO until the frequency difference is reduced to zero. Once frequency acquisition is complete, the FD returns to a neutral state. False locking is eliminated by this digital frequency detector.

#### **Loop Filter and VCO**

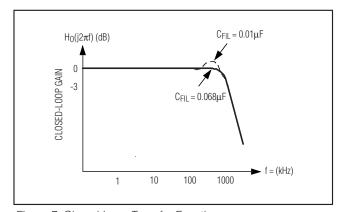

The fully integrated PLL has a second-order transfer function, with a loop bandwidth (f<sub>L</sub>) fixed at 1.7MHz. An external capacitor between V<sub>CC</sub>\_VCO and FIL sets the damping of the PLL. All jitter specifications are based on the C<sub>FIL</sub> capacitor being 0.068µF. Note that the PLL

jitter transfer bandwidth does not change as the external capacitor changes, but the jitter peaking, acquisition time, and loop stability are affected.

For an overdamped system ( $f_Z/f_L$ ) < 0.25, the jitter peaking (Jp) of a second-order system can be approximated by:

$$J_P = 20\log(1 + f_Z/f_L)$$

The PLL zero frequency (fz) is a function of the external capacitor (CFIL) and can be approximated according to:

$$f_Z = 1/2\pi(650)C_{FIL}$$

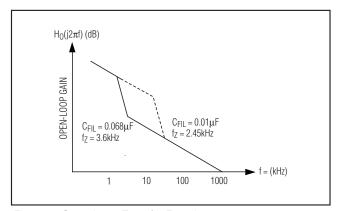

Figures 6 and 7 show the open-loop and closed-loop transfer functions. The PLL acquisition time is also directly proportional to the external capacitor CFIL.

#### **Loss-of-Lock Monitor**

The  $\overline{\text{LOL}}$  output indicates a PLL lock failure, either due to excessive jitter present at data input or due to loss of input data. In the case of loss of input data, the  $\overline{\text{LOL}}$  indicates a loss-of-signal condition. The  $\overline{\text{LOL}}$  output is asserted low when the PLL loses lock.

#### **Output LVDS Interface: PD, PCLK**

The MAX3882A's clock and data outputs are LVDS compatible to minimize power dissipation, speed transition time, and improve noise immunity. These outputs comply with the IEEE LVDS specification. The differential output signal magnitude is 250mV to 400mV.

### Design Procedure

The MAX3882A provides a differential output clock (PCLK). Table 1 shows the pin configuration for choosing the type of operation mode.

#### **Decision Threshold Adjust**

Decision threshold adjust is available for WDM applications where optical amplifiers are used, generating spontaneous optical noise at data logic high. The decision threshold adjust range is ±170mV. Use the provided 2.2V bandgap reference VREF pin or an outside source, such as an output from a DAC to control the

**Table 1. Operation Modes**

| FREFSET | LREF | SIS | OPERATION MODE DESCRIPTION                                  |  |

|---------|------|-----|-------------------------------------------------------------|--|

| X       | 1    | 0   | Normal operation: PLL locked to data input at 2.488Gbps     |  |

| X       | 1    | 1   | System loopback: PLL lock frequency at 2.488Gbps            |  |

| 1       | 0    | Х   | Clock holdover: PLL locked to reference frequency at 155MHz |  |

| 0       | 0    | Х   | Clock holdover: PLL locked to reference frequency at 622MHz |  |

Figure 5. Functional Diagram

Figure 6. Open-Loop Transfer Function

threshold voltage. The +170mV to -170mV threshold offset can be accomplished by varying the VCTRL voltage from 0.3V to 2.1V, respectively. See Figure 2. When using the VREF to generate voltage for threshold setting, see Figure 8. Connect VCTRL directly to VCC to disable threshold adjust.

Figure 7. Closed-Loop Transfer Function

#### **DC-Offset Cancellation Loop Filter**

A DC-offset cancellation loop is implemented to remove the DC offset of the limiting amplifier. To minimize the low-frequency pattern-dependent jitter associated with this DC-cancellation loop, the low-frequency cutoff is 10kHz typical with CAZ =  $0.1\mu F$ , connected across CAZ+ and CAZ-.

### **Applications Information**

#### **Clock Holdover Capability**

Clock holdover is required in some applications where a valid clock needs to be provided to the upstream device in the absence of data transitions. To provide this function, an external reference clock rate of 155MHz or 622MHz must be applied to the SLBI input. Control input FREFSET selects which reference clock rate to use. The control  $\overline{LREF}$  selects whether the PLL locks to the input data stream (SDI) or the reference clock (SLBI). When  $\overline{LREF}$  is low, the input is switched to the reference clock input. This  $\overline{LREF}$  input can be driven by connecting the  $\overline{LOL}$  output pin directly or connecting to any other power monitor signal from the system.

#### System Loopback

The MAX3882A is designed to allow system loopback testing. The user can connect the serializer output (MAX3892) directly to the SLBI± inputs of the MAX3882A for system diagnostics. See Table 1 for selecting the system loopback operation mode. During system loopback, LOL cannot be connected to LREF.

#### Interfacing the MAX3882A

To correctly interface with the MAX3882A's CML input and LVDS outputs, refer to Application Note 291: *HFAN-1.0: Introduction to LVDS, PECL, and CML*.

#### **Layout Techniques**

For best performance, use good high-frequency layout techniques. Filter voltage supplies, keep ground connections short, and use multiple vias where possible. Use controlled-impedance transmission lines to interface with the MAX3882A high-speed inputs and outputs. Power-supply decoupling should be placed as close to the VCC as possible. To reduce feedthrough, isolate input signals from output signals.

#### **Exposed-Paddle Package**

The exposed pad, 36-pin TQFN incorporates features that provide a very low thermal-resistance path for heat removal from the IC. The pad is electrical ground on the MAX3882A and should be soldered to the circuit board for proper thermal and electrical performance.

Figure 8. Connecting the MAX3882A with Threshold Adjust and Clock Holdover Enabled

## **Typical Application Circuit**

## **Package Information**

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 36 TQFN-EP   | T3666-2      | <u>21-0141</u> |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                     | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------|------------------|

| 0                  | 1/03             | Initial release (MAX3882 only). | _                |

| 1                  | 11/05            | Added the MAX3882A.             | All              |

| 2                  | 4/09             | Removed the MAX3882.            | All              |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Serializers & Deserializers - Serdes category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

MAX31953AUM DS90UR903QSQE/NOPB DS90UB925QSQ/NOPB SN65HVS881PWPR MAX9208EAI+ HG82C51N

MAX9260GCB/V+ MAX9278AGTM+ MAX9272AGTM/V+ MAX96700GTJ/V+ MAX31963AUM+ MAX3680EAI+ MAX3681EAG+

MAX3882AETX+ MAX9205EAI+ MAX9206EAI+T MAX9205EAI/V+ MAX9205EAI+T MAX9206EAI+ MAX9206EAI/V+

MAX9207EAI+ MAX9238EUM+ MAX9275GTN/V+T MAX9280AGTN/V+ MAX96708GTJ+ MAX9218ECM+T MAX9217ECM+

GS1572-IBE3 MAX3693ECJ FIN224CMLX WK2114-ISPG FM25M4AA-1AIB4R MAX9278GTM/VY+ MAX9248ECMV

MAX9268GCM/V+ DS90UB941ASRTDTQ1 DS92LX2122SQE/NOPB LMH0030VS/NOPB LMH0031VS/NOPB LMH0041SQE/NOPB

LMH0070SQ/NOPB LMH0071SQE/NOPB LMH0340SQE/NOPB LMH0341SQE/NOPB SCAN921025HSM/NOPB SN65LVDS301ZQE

SN65LVDS315RGER SN65LVDS93BIDGGTQ1 SN65LVDS93DGG SN65LVDS95DGG