# **General Description**

**Applications**

The MAX4923–MAX4926 overvoltage protection (OVP) controllers protect low-voltage systems against high-voltage faults of up to +28V with an appropriate external pFET. When the input voltage exceeds the overvoltage lockout (OVLO) threshold, or falls below the undervoltage lockout (UVLO) threshold, these devices turn off the pFET to prevent damage to protected components and issue a flag to notify the processor of a fault condition.

The typical overvoltage trip level is set to 7.18V (MAX4923), 6.16V (MAX4924), 5.65V (MAX4925), and 4.46V (MAX4926). The undervoltage trip level is set to 2.44V (typ) for all devices.

The input (IN) is ESD protected to  $\pm 15$ kV HBM when bypassed to ground with a 1µF ceramic capacitor. All devices are offered in a small, 6-pin (1.5mm x 1.0mm) µDFN package and are specified over the extended -40°C to +85°C temperature range.

> Cell Phones Digital Still Cameras PDAs and Palmtop Devices MP3 Players

### \_Features

- ♦ Overvoltage Protection Up to +28V

- Preset 7.18V, 6.16V, 5.65V, and 4.46V Typical Overvoltage Trip Levels

- Preset 2.44V Typical Undervoltage Trip Level

- ♦ ±2.5% Accurate Overvoltage/Undervoltage Trip Levels

- ♦ Low 13µA (typ) Supply Current

- Drives External pFET

- ♦ 20ms Adapter Debounce Time

- ♦ Fault Flag Indicator

- ♦ 6-Pin (1.5mm x 1.0mm) µDFN Package

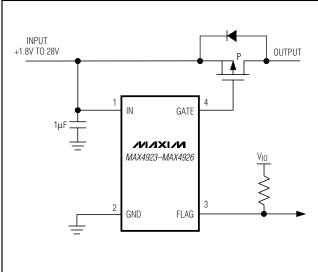

# \_Typical Operating Circuit

### **Ordering Information/Selector Guide**

| PART         | PIN-PACKAGE | OVLO (V) | UVLO (V) | TOP MARK | PKG CODE |

|--------------|-------------|----------|----------|----------|----------|

| MAX4923ELT+* | 6 µDFN      | 7.18     | 2.44     | LB       | L611-1   |

| MAX4924ELT+  | 6 µDFN      | 6.16     | 2.44     | LC       | L611-1   |

| MAX4925ELT+  | 6 µDFN      | 5.65     | 2.44     | LD       | L611-1   |

| MAX4926ELT+  | 6 µDFN      | 4.46     | 2.44     | LE       | L611-1   |

Note: All devices are specified over the -40°C to +85°C operating temperature range.

+Denotes lead-free package.

\*Future Product—contact factory for availability.

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| IN, GATE to GND                                       | 0.3V to +30V |

|-------------------------------------------------------|--------------|

| FLAG to GND                                           | 0.3V to +6V  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |              |

| 6-µDFN (derate 2.1mW/°C above 70°C)                   | 168mW        |

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300 °C        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>IN</sub> = +5V for MAX4923/MAX4924/MAX4925, V<sub>IN</sub> = +4V for MAX4926, C<sub>GATE</sub> = 500pF to IN,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 1)

| PARAMETER                       | PARAMETER SYMBOL CONDITIONS |                                                                                                                                                              | MIN     | TYP                      | MAX   | UNITS |     |  |

|---------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------|-------|-------|-----|--|

| Input Voltage Range             | VIN                         |                                                                                                                                                              |         | 1.8                      |       | 28.0  | V   |  |

| Overvoltage Lockout Level       | OVLO                        |                                                                                                                                                              | MAX4923 | 7.00                     | 7.18  | 7.36  | - V |  |

|                                 |                             | V <sub>IN</sub> rising                                                                                                                                       | MAX4924 | 6.00                     | 6.16  | 6.31  |     |  |

|                                 |                             |                                                                                                                                                              | MAX4925 | 5.50                     | 5.65  | 5.79  |     |  |

|                                 |                             |                                                                                                                                                              | MAX4926 | 4.35                     | 4.46  | 4.57  |     |  |

|                                 |                             | MAX4923                                                                                                                                                      | ·       |                          | 65    |       |     |  |

|                                 |                             | MAX4924                                                                                                                                                      |         |                          | 55    |       |     |  |

| Overvoltage Lockout Hysteresis  |                             | MAX4925                                                                                                                                                      |         |                          | 50    |       | mV  |  |

|                                 |                             | MAX4926                                                                                                                                                      |         |                          | 40    |       |     |  |

| Undervoltage Lockout Level      | UVLO                        | V <sub>IN</sub> falling                                                                                                                                      |         | 2.378                    | 2.439 | 2.500 | V   |  |

| Undervoltage Lockout Hysteresis |                             |                                                                                                                                                              |         |                          | 20    |       | mV  |  |

|                                 |                             | MAX4923/MAX4924/MAX4925                                                                                                                                      |         |                          | 14    | 25    | μA  |  |

| IN Supply Current               | lin                         | MAX4926                                                                                                                                                      |         |                          | 13    | 23    |     |  |

| GATE Voltage High               | V <sub>OH</sub>             | $V_{IN} \ge 8V$ , $I_{SOURCE} = 0.1mA$                                                                                                                       |         | V <sub>IN</sub> -<br>0.2 |       |       | V   |  |

| GATE Pulldown Current           | IPD                         | V <sub>GATE</sub> = V <sub>IN</sub>                                                                                                                          |         | 6.5                      | 12    |       | mA  |  |

| FLAG Low Voltage                | Vol                         | I <sub>SINK</sub> = 1mA                                                                                                                                      |         |                          |       | 0.4   | V   |  |

| FLAG Leakage Current            | I <sub>LKG</sub>            | V <sub>FLAG</sub> = 5.5V                                                                                                                                     |         | -1                       |       | +1    | μA  |  |

| TIMING CHARACTERISTICS          |                             |                                                                                                                                                              |         |                          |       |       |     |  |

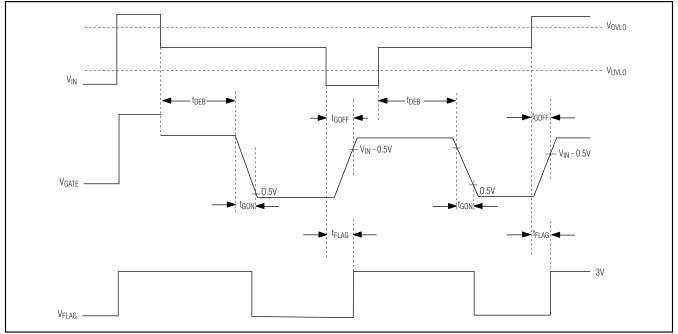

| Debounce Time                   | t <sub>DEB</sub>            | V <sub>UVLO</sub> < V <sub>IN</sub> < V <sub>OVLO</sub> , time for GATE to go<br>low (Figure 1)                                                              |         | 10                       | 20    | 34    | ms  |  |

| Gate Turn-on Time               | tgon                        | V <sub>GATE</sub> = 5V to 0.5V<br>(MAX4923/MAX4924/MAX4925) or<br>V <sub>GATE</sub> = 4V to 0.5V (MAX4926) (Figure 1)                                        |         |                          | 0.6   |       | μs  |  |

| Gate Turn-Off Time              | tgoff                       | $V_{IN}$ rising at 1V/µs from 5V to 8V<br>(MAX4923/MAX4924/MAX4925) or from 4V<br>to 7V (MAX4926) to V <sub>GATE</sub> = V <sub>IN</sub> -0.5V<br>(Figure 1) |         |                          | 5     | 20    | μs  |  |

| Flag Assertion Delay            | <sup>t</sup> FLAG           | $V_{IN}$ rising at 1V $\mu$<br>(MAX4923/MAX4<br>to 7V (MAX4926)<br>R <sub>FLAG</sub> = 10k $\Omega$ to                                                       |         | 4.5                      |       | μs    |     |  |

Note 1: All devices are 100% tested at +25°C. Electrical limits across the full temperature range are guaranteed by design and characterization.

MIXIM

# **Typical Operating Characteristics**

$(V_{IN} = +5V \text{ for MAX4923/MAX4924/MAX4925}, V_{IN} = +4V \text{ for MAX4926} (pFET = Si6991DQ), T_A = +25^{\circ}C, unless otherwise noted.)$

#### **GATE-OUTPUT LOW VOLTAGE GATE VOLTAGE vs. INPUT VOLTAGE** vs. GATE SINK CURRENT **SUPPLY CURRENT vs. INPUT VOLTAGE** 250 100 10 MAX4925 GATE OUTPUT LOW VOLTAGE (mV) 80 8 200 SUPPLY CURRENT (MA) $V_{CC} = +2.5V$ MAX4925 GATE VOLTAGE (V) 150 60 6 $V_{CC} = +3.3V$ 40 100 4 MAX4926 20 50 2 $V_{CC} = +5.5V$ 0 0 0 1000 0 4 8 16 20 24 28 2 4 6 8 0 200 400 600 12 800 INPUT VOLTAGE (V) INPUT VOLTAGE (V) GATE SINK CURRENT (µA) **SUPPLY CURRENT vs. TEMPERATURE POWER-UP RESPONSE POWER-UP RESPONSE** MAX4923 toc06 VIN 15 MAX4926 5V/div $V_{CC} = +4V$ 5V/div VIN 14 SUPPLY CURRENT (MA) VOUT 5V/div 13 5V/div 1A/div VGATE I<sub>IN</sub> 12 5V/div 5V/div 11 VFLAG VFLAG 10 -40 -15 10 35 60 85 20.0 ms 10.0ms TEMPERATURE (°C) **POWER-UP OVERVOLTAGE RESPONSE OVERVOLTAGE RESPONSE** 5V/div VIN VIN 5V/div 5V/div VGATE VGATE

10mA/div IGATE 5V/div VFLAG

20.0µs

M/IXI/M

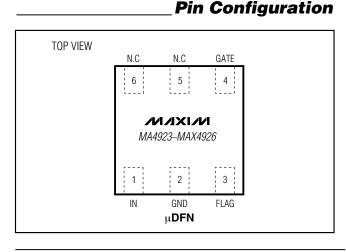

# **Pin Description**

| PIN  | NAME | FUNCTION                                                                                                                                                                                                                               |  |  |  |  |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1    | IN   | Voltage Input. IN is both the power-supply input and the overvoltage/undervoltage sense input. Bypass IN to GND with a $1\mu$ F ceramic capacitor as close as possible to the device to enable $\pm 15$ kV (HBM) ESD protection on IN. |  |  |  |  |

| 2    | GND  | Ground                                                                                                                                                                                                                                 |  |  |  |  |

| 3    | FLAG | Fault Indication Open-Drain Output. FLAG deasserts high during undervoltage and overvoltage lockout conditions. FLAG asserts low during normal operation.                                                                              |  |  |  |  |

| 4    | GATE | pFET Gate Drive Output. GATE is driven high during a fault condition to turn off the external pFET. When $V_{UVLO} < V_{IN} < V_{OVLO}$ , GATE is driven low and the external pFET is turned on.                                       |  |  |  |  |

| 5, 6 | N.C. | No Connection. Not internally connected. Leave N.C. unconnected.                                                                                                                                                                       |  |  |  |  |

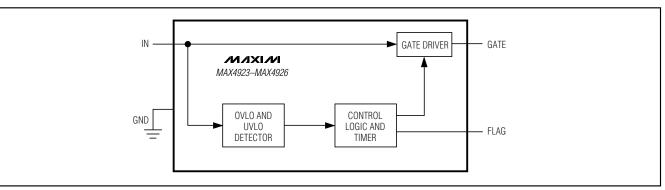

# Functional Diagram

Figure 1. Timing Diagram

MAX4923-MAX4926

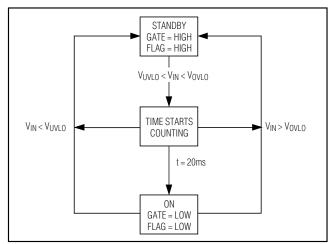

Figure 2. State Machine

### **Detailed Description**

The MAX4923–MAX4926 overvoltage protection controllers protect low-voltage systems against highvoltage faults of up to +28V when used with a -30V pFET. When the input voltage exceeds the OVLO threshold, these devices turn off the external pFET to prevent damage to protected components.

The typical overvoltage trip level is set to 7.18V (MAX4923), 6.16V (MAX4924), 5.65V (MAX4925), and 4.46V (MAX4926). When the supply drops below the UVLO threshold, the devices turn off the external pFET.

IN is ESD protected to  $\pm 15 kV$  (Human Body Model) when bypassed with a 1  $\mu F$  ceramic capacitor to ground.

#### **Undervoltage Lockout (UVLO)**

The MAX4923–MAX4926 have a fixed 2.44V (typ) UVLO level. When  $V_{\rm IN}$  is less than  $V_{\rm UVLO},$  GATE is high and FLAG is high.

#### **Overvoltage Lockout (OVLO)**

The MAX4923 has a 7.18V (typ) OVLO; the MAX4924 has a 6.16V (typ) OVLO; the MAX4925 has a 5.65V (typ) OVLO; and the MAX4926 has a 4.46V (typ) OVLO. When  $V_{IN}$  is greater than  $V_{OVLO}$ , GATE is high and FLAG is high.

#### **FLAG Output**

The open-drain FLAG output is used to signal to the host system that there is a fault with the input voltage. FLAG goes high during an overvoltage or undervoltage fault. Connect a pullup resistor from FLAG to the logic I/O voltage of the host system.

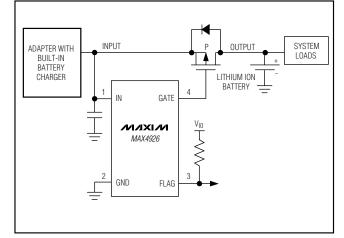

Figure 3. MAX4926 Typical Operating Circuit

#### **Device Operation**

The MAX4923–MAX4926 have an on-board state machine to control device operation. A flowchart is shown in Figure 2. At initial power up, if  $V_{IN} < V_{UVLO}$  or if  $V_{IN} > V_{OVLO}$ , both GATE and FLAG are high. When  $V_{UVLO} < V_{IN} < V_{OVLO}$ , an internal timer starts counting and the device enters its on state after a 20ms delay. At any time if  $V_{IN}$  drops below  $V_{UVLO}$  or above  $V_{OVLO}$ , both GATE and FLAG transition high.

### Application Information

#### MAX4926 Application

In a typical application for the MAX4926, an external adapter with built-in battery charger is connected to IN and a battery is connected to the drain of the external FET. When the adapter is unplugged, IN is directly connected to the battery through the external FET. Since the battery voltage is typically greater than  $V_{UVLO}$ , the GATE voltage stays low and the device remains powered by the battery.

#### **MOSFET Selection**

The MAX4923–MAX4926 are designed for use with either a single pFET or dual pFETs in parallel. MOSFETs with  $R_{DS(ON)}$  specified for a V<sub>GS</sub> of -4.5V are recommended. For input supplies near the UVLO maximum of 2.5V, use a MOSFET specified for a lower V<sub>GS</sub> voltage. Also, the V<sub>DS</sub> must be -30V and the V<sub>GS</sub> (max) must be higher than the VOVLO (max) for the MOSFET to withstand the full +28V input range of the MAX4923–MAX4926.

MAX4923-MAX4926

### Table 1. MOSFETS Suggestions

| PART     | CONFIGURATON/<br>PACKAGE | V <sub>DS</sub> MAX<br>(V) | R <sub>ON</sub> MAX (mΩ)<br>at V <sub>GS</sub> = -4.5V | MANUFACTURER     |  |

|----------|--------------------------|----------------------------|--------------------------------------------------------|------------------|--|

| Si3993DV | Dual/TSOP-6              | -30                        | 245 each                                               |                  |  |

| Si1433DH | Single/SOT-363           | -30                        | 260                                                    |                  |  |

| Si3983DV | Dual/TSOP-6              | -20                        | 110 each                                               | Vishay Siliconix |  |

| Si1413DH | Single/SOT-363           | -20                        | 115                                                    | www.vishay.com   |  |

| Si5933DC | Dual/1206-8              | -20                        | 110 each                                               |                  |  |

| Si6991DQ | Dual/TSSOP-8             | -30                        | 68 each                                                |                  |  |

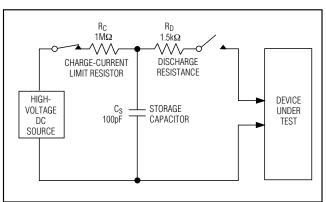

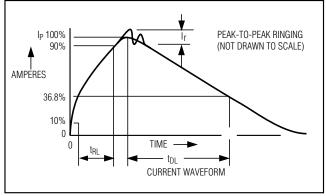

Figure 4. Human Body ESD Test Model

#### **IN Bypass Consideration**

For most applications, bypass IN to GND with a  $1\mu$ F ceramic capacitor. If the power source has significant inductance due to long lead length, take care to prevent overshoots due to the LC tank circuit and provide protection if necessary to prevent exceeding the 30V absolute maximum rating on IN.

#### **ESD Test Conditions**

The MAX4923–MAX4926 are ESD protected to  $\pm 15$ kV (typ) Human Body Model on IN when IN is bypassed to ground with a 1µF ceramic capacitor as close as possible to IN.

Figure 5. Human Body Model Current Waveform

#### Human Body Model

Figure 4 shows the Human Body Model and Figure 5 shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest that is then discharged into the device through a  $1.5k\Omega$  resistor.

\_\_\_\_\_Chip Information

MAX4923-MAX4926

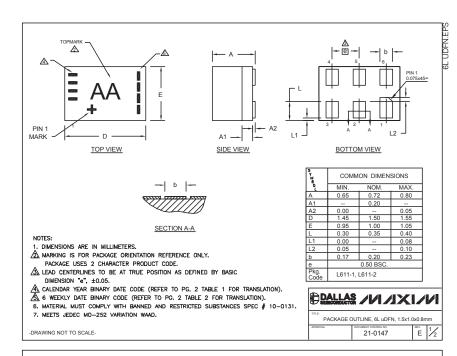

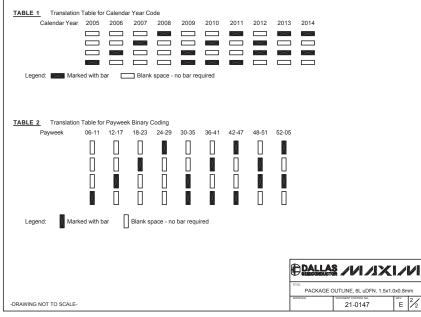

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>www.maxim-ic.com/packages</u>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

is a registered trademark of Maxim Integrated Products, Inc.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management Specialised - PMIC category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

LV5686PVC-XH FAN7710VN NCP391FCALT2G SLG7NT4081VTR SLG7NT4192VTR AP4313UKTR-G1 AS3729B-BWLM MB39C831QN-G-EFE2 MAX4940MB LV56841PVD-XH MAX77686EWE+T AP4306BUKTR-G1 MIC5164YMM PT8A3252WE NCP392CSFCCT1G TEA1998TS/1H PT8A3284WE PI3VST01ZEEX PI5USB1458AZAEX PI5USB1468AZAEX MCP16502TAC-E/S8B MCP16502TAE-E/S8B MCP16502TAA-E/S8B MCP16502TAB-E/S8B TCKE712BNL,RF ISL91211AIKZT7AR5874 ISL91211BIKZT7AR5878 MAX17506EVKITBE# MCP16501TC-E/RMB ISL91212AIIZ-TR5770 ISL91212BIIZ-TR5775 CPX200D AX-3005D-3 TP-1303 TP-1305 TP-1603 TP-2305 TP-30102 TP-4503N MIC5167YML-TR LPTM21-1AFTG237C MPS-3003L-3 MPS-3005D SPD-3606 STLUX383A TP-60052 ADN8834ACBZ-R7 LM26480SQ-AA/NOPB LM81BIMTX-3/NOPB LM81CIMT-3/NOPB