EVALUATION KIT AVAILABLE

# SAS/SATA Single Lane 2:1/1:2 Multiplexer/ Demultiplexer Plus Redriver with Equalization

## **General Description**

The MAX4986 active 2:1/1:2 multiplexer/demultiplexer equalizes and redrives SAS/SATA or SATA-only signals up to 6.0Gbps and operates from a single +3.3V supply.

The MAX4986 features independent input equalization and output preemphasis. The MAX4986 enhances signal integrity at the receiver by equalizing the signal at the input and establishing preemphasis at the output of the device. SAS/SATA and SATA-only out-of-band (OOB) signaling is supported using high-speed amplitude detection on the inputs and squelch on the corresponding outputs. Inputs and outputs are internally  $50\Omega$ terminated and must be AC-coupled to the SAS/SATA controller IC and SAS/SATA device.

The MAX4986 is available in a small (3.5mm x 9.0mm), 42-pin TQFN package optimal for simplified layout and space-saving requirements. The MAX4986C is specified over the 0°C to +70°C commercial operating temperature range. The MAX4986E is specified over the -40°C to +85°C extended temperature range.

## PC Servers Workstations

Desktops Docking Stations

#### \_Features

- Single +3.3V Supply Operation

- Low-Power, 1mA (typ) Standby Active-High Enable (EN) for Use with Power Good Active-Low Enable (EN) for Cable-Detect Function

- ♦ Supports SAS I/II/III ≤ 6.0Gbps

- Independent Programmable Input Equalization Two Levels: 0dB, 4dB

- Independent Programmable Output Preemphasis Two Levels: 0dB, 3dB

- Independent Programmable Output Level Selection

- Supports SAS/SATA OOB-Level Signaling Programmable SAS/SATA Threshold

- Cable-Detect Feature for Low Power Consumption

- On-Chip 50Ω Input/Output Terminations

- ♦ Inline Signal Traces for Simplified Layout

- Space-Saving, 3.5mm x 9.0mm TQFN Package with Exposed Pad

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX4986CTO+ | 0°C to +70°C   | 42 TQFN-EP* |

| MAX4986ETO+ | -40°C to +85°C | 42 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

**Applications**

## **ABSOLUTE MAXIMUM RATINGS**

(Voltages Referenced to GND.)

Operating Temperature Range

-40°C to +85°C

Junction Temperature Range

-40°C to +150°C

Storage Temperature Range

-65°C to +150°C

Lead Temperature (soldering, 10s)

+300°C

Soldering Temperature (reflow)

+260°C

42-Pin TQFN (derate 34.5mW/°C above +70°C) .... 2758mW

Note 1: All I/O pins are clamped by internal diodes.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0V \text{ to } +3.6V, C_{CL} = 10nF \text{ coupling capacitor on each input and output, } R_L = 50\Omega \text{ on each input and output, } T_A = 0^{\circ}C \text{ to } +70^{\circ}C \text{ (MAX4986C)}, T_A = -40^{\circ}C \text{ to } +85^{\circ}C \text{ (MAX4986E)}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +3.3V \text{ and } T_A = +25^{\circ}C.) \text{ (Note 2)}$

| PARAMETER                                   | SYMBOL             | CONDITIONS                                                                                                                                                              |             | MIN  | ТҮР | MAX  | UNITS             |  |

|---------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-----|------|-------------------|--|

| DC PERFORMANCE                              |                    |                                                                                                                                                                         |             |      |     |      |                   |  |

| Power-Supply Range                          | Vcc                |                                                                                                                                                                         |             | 3.0  |     | 3.6  | V                 |  |

| Standby Current                             | lotpy              | $EN = 0 \text{ or } \overline{EN} = 1, V_{CC} =$                                                                                                                        | = 3.6V      |      | 2.5 | 4    | — mA              |  |

| Standby Current                             | ISTBY              | $EN = 0 \text{ or } \overline{EN} = 1, VCC =$                                                                                                                           | = 3.3V      |      | 1.0 | 2    | ША                |  |

| Supply Current                              |                    | OUTPE = PEA = PEB = 0<br>INEQ = EQA = EQB = 0                                                                                                                           | ,           |      | 145 | 170  | mA                |  |

| Supply Current                              | ICC                | OUTPE = PEA = PEB =<br>INEQ = EQA = EQB = 1                                                                                                                             | 1,          |      | 185 | 230  | mA                |  |

| Input Termination, Single-Ended             | RRX-SE             | DC                                                                                                                                                                      |             | 42.5 |     | 57.5 | Ω                 |  |

| Output Termination, Single-<br>Ended        | R <sub>TX-SE</sub> | DC                                                                                                                                                                      |             | 42.5 |     | 57.5 | Ω                 |  |

| AC PERFORMANCE                              |                    |                                                                                                                                                                         |             |      |     |      |                   |  |

|                                             | SDD11              | 0.1GHz < f ≤ 0.3GHz                                                                                                                                                     |             |      |     | -10  | dB                |  |

| Input Return Loss, Differential<br>(Note 3) |                    | $0.3$ GHz < f $\leq$ $3.0$ GHz                                                                                                                                          |             |      |     | -7.9 |                   |  |

| (Note 5)                                    |                    | $3.0GHz < f \le 6.0GHz$                                                                                                                                                 |             |      |     | 0    |                   |  |

| Input Datum Laga                            | SCC11              | $\begin{array}{l} 0.1 \text{GHz} < f \leq 0.3 \text{GHz} \\ \hline 0.3 \text{GHz} < f \leq 3.0 \text{GHz} \\ \hline 3.0 \text{GHz} < f \leq 6.0 \text{GHz} \end{array}$ |             |      |     | -6   |                   |  |

| Input Return Loss,<br>Common Mode (Note 3)  |                    |                                                                                                                                                                         |             |      |     | -5   | dB                |  |

|                                             |                    |                                                                                                                                                                         |             |      |     | 0    |                   |  |

| Output Return Loss, Differential            |                    | $0.1GHz < f \le 0.3GHz$                                                                                                                                                 |             |      |     | -10  |                   |  |

| (Note 3)                                    | SDD22              | $0.3$ GHz < f $\leq$ $3.0$ GHz                                                                                                                                          |             |      |     | -7.9 | dB                |  |

|                                             |                    | $3.0GHz < f \le 6.0GHz$                                                                                                                                                 |             |      |     | 0    |                   |  |

| Output Daturn Laga                          |                    | $0.1GHz < f \le 0.3GHz$                                                                                                                                                 |             |      |     | -6   |                   |  |

| Output Return Loss,<br>Common Mode (Note 3) | SCC22              | $0.3$ GHz < f $\leq$ $3.0$ GHz                                                                                                                                          |             |      |     | -5   | dB                |  |

|                                             |                    | $3.0GHz < f \le 6.0GHz$                                                                                                                                                 |             |      |     | 0    |                   |  |

|                                             |                    | SAS 1.5Gbps, 3Gbps, N                                                                                                                                                   | 10DE_ = 0   | 275  |     | 1600 |                   |  |

| Differential Input Voltage                  | VIN-DIFF           | SAS 6Gbps, MODE_ = 0                                                                                                                                                    |             | 300  |     | 1600 | mVP-P             |  |

|                                             |                    | SATA 1.5Gbps, 3Gbps, 6Gbps, MODE_ = 1                                                                                                                                   |             | 225  |     | 1600 |                   |  |

| Input Equalization                          | EQ                 | f = 1.5GHz, INEQ = 1                                                                                                                                                    |             |      | 4   |      | dB                |  |

| Differential Output Voltage                 | Vout-diff          |                                                                                                                                                                         | OAMP_ = 0   | 700  |     | 1200 | mV <sub>P-P</sub> |  |

| Emolonital Output Voltage                   | *UUI-DIFF          | PE_ = 0                                                                                                                                                                 | $OAMP_ = 1$ | 425  |     | 700  | ····vF-F          |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0V \text{ to } +3.6V, C_{CL} = 10nF \text{ coupling capacitor on each input and output, } R_L = 50\Omega \text{ on each input and output, } T_A = 0^{\circ}C \text{ to } +70^{\circ}C \text{ (MAX4986C)},$  $(MAX4986C), T_A = -40^{\circ}C \text{ to } +85^{\circ}C \text{ (MAX4986E)},$  unless otherwise noted. Typical values are at  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C.$  (Note 2)

| PARAMETER                             | SYMBOL                | CONDITIONS                             |                     | MIN | TYP | MAX | UNITS |

|---------------------------------------|-----------------------|----------------------------------------|---------------------|-----|-----|-----|-------|

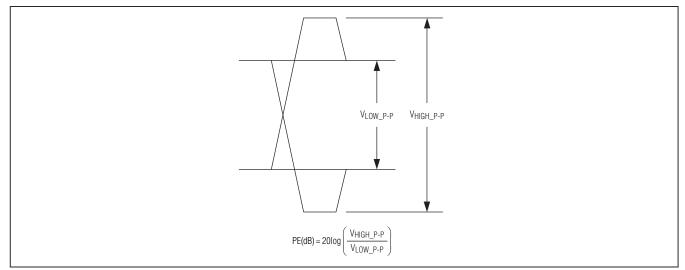

| Output Preemphasis                    | PE                    | f = 1.5GHz, PE_ = 1, Figure 1          |                     |     | 3   |     | dB    |

| Propagation Delay                     | tpD                   |                                        |                     |     | 300 |     | ps    |

| Output Transition Time                | ttx-RF                | f < 3.0GHz, PE_ = 0 (N                 | otes 3, 4)          | 40  | 60  |     | ps    |

| Differential Output Skew Same<br>Pair | tsĸ                   |                                        |                     |     | 10  |     | ps    |

| Deterministic Jitter                  | t <sub>DJ</sub>       | K28.5± pattern, PE_ =                  | 0, EQ_ = 0 (Note 3) |     |     | 20  | psp-p |

| Random Jitter                         | ttx-rj-dd             | D10.2 pattern, PE_ = 0                 | , EQ_ = 0           |     | 1   | 1.5 | psrms |

| OOR Squalab Threabald                 |                       | f 0.750Hz (Noto 2)                     | $MODE_{-} = 0$      | 120 |     | 220 |       |

| OOB Squelch Threshold                 | VSQ-DIFF              | f = 0.75GHz (Note 3)                   | MODE_ = 1           | 50  |     | 150 | mVp-p |

| OOB Squelch Time                      | toob,sq               | f = 0.75GHz (Note 3)                   |                     |     | 5   | 10  | ns    |

| OOB Exit Time                         | toob,ex               | f = 0.75GHz (Note 3)                   |                     |     | 5   | 10  | ns    |

| OOB Differential-Offset Delta         | $\Delta V_{OOB,DIFF}$ | Difference between OC<br>output offset | )B and active-mode  | -80 |     | 80  | mV    |

| OOB Common-Mode Delta                 | ΔV <sub>OOB</sub> ,CM | Difference between OC<br>output VCM    | B and active-mode   | -50 |     | 50  | mV    |

| OOB Output Disable                    | VOOB,OUT              | OOB-disabled output le                 | evel                |     |     | 30  | mVp-p |

| CONTROL LOGIC                         |                       |                                        |                     |     |     |     |       |

| Input Logic-High                      | VIH                   |                                        |                     | 1.4 |     |     | V     |

| Input Logic-Low                       | VIL                   |                                        |                     |     |     | 0.6 | V     |

| Input Logic Hysteresis                | VHYST                 |                                        |                     |     | 0.1 |     | V     |

| Pullup/Pulldown Input Resistor        | Rup/down              |                                        |                     |     | 330 |     | kΩ    |

**Note 2:** MAX4986C devices are 100% production tested at  $T_A = +70^{\circ}$ C. MAX4986E devices are 100% production tested at  $T_A = +85^{\circ}$ C. Specifications for all temperature limits are guaranteed by design.

Note 3: Guaranteed by design.

Note 4: Rise and fall times are measured using 20% and 80% levels.

Figure 1. Output Preemphasis

200

0

-200

-400

-600

-300

-200

-100

0

100ps/div

100

200

300

200mV/div

150

150

200

0

-200

-400

-600

-600

-400

-200

0

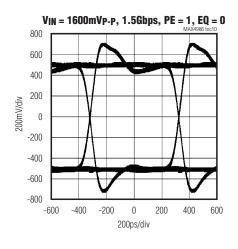

200ps/div

200

400

600

200mV/div

**MAX4986**

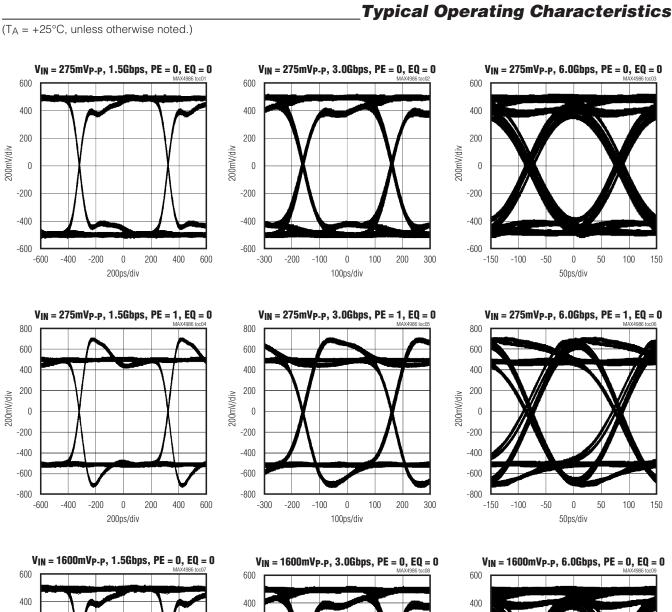

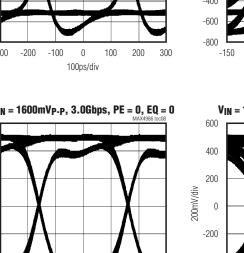

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

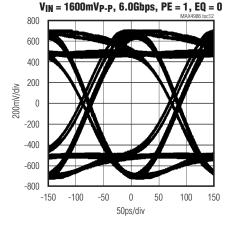

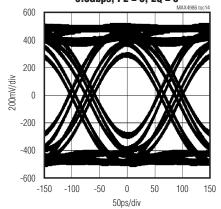

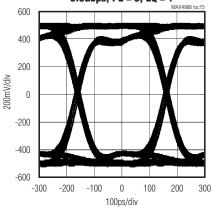

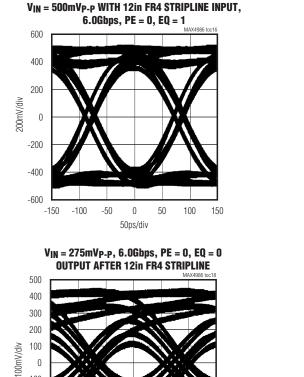

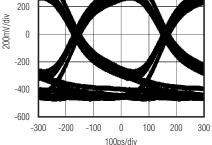

$$\label{eq:VIN} \begin{split} V_{IN} &= 500mV_{P-P} \text{ WITH 12in FR4 STRIPLINE INPUT,} \\ & 6.0Gbps, \ PE = 0, \ EQ = 0 \end{split}$$

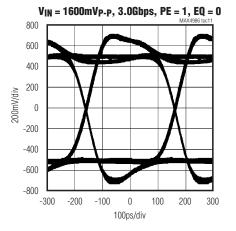

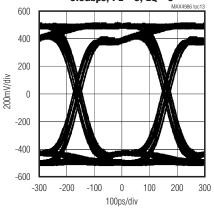

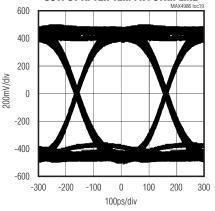

$V_{IN} = 500mV_{P-P}$  WITH 12in FR4 STRIPLINE INPUT, 3.0Gbps, PE = 0, EQ = 0

$$\label{eq:VIN} \begin{split} V_{IN} &= 500mV_{P-P} \text{ WITH 12in FR4 STRIPLINE INPUT},\\ & 3.0Gbps, \text{ PE} = 0, \text{ EQ} = 1 \end{split}$$

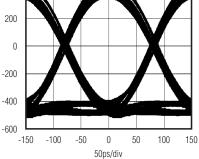

**Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

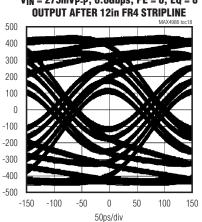

V<sub>IN</sub> = 275mV<sub>P-P</sub>, 3.0Gbps, PE = 0, EQ = 0

VIN = 275mVP-P, 3.0Gbps, PE = 1, EQ = 0 **OUTPUT AFTER 12in FR4 STRIPLINE**

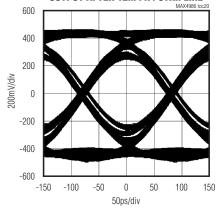

$V_{IN} = 275mV_{P-P}, 6.0Gbps, PE = 1, EQ = 0$ **OUTPUT AFTER 12in FR4 STRIPLINE**

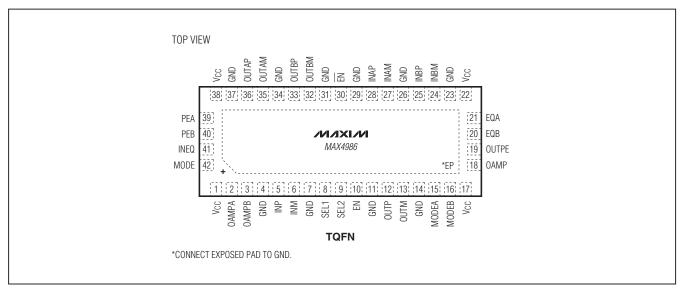

## \_Pin Configuration

## **Pin Description**

| PIN                                        | NAME                                                                                                                                                                                                                                                                  | FUNCTION                                                                                                                                                                                                                                                              |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 17, 22, 38                              | V <sub>CC</sub>                                                                                                                                                                                                                                                       | Power-Supply Input. Bypass V <sub>CC</sub> to GND with $1\mu$ F and $0.01\mu$ F capacitors in parallel as close to the device as possible; recommended for each V <sub>CC</sub> pin.                                                                                  |

| 2                                          | OAMPA                                                                                                                                                                                                                                                                 | OUTAP/OUTAM Output Level Selection. Drive OAMPA high for low output amplitude. Drive OAMPA low or leave unconnected for high output amplitude. See the <i>Electrical Characteristics</i> table. OAMPA is internally pulled down by a $330$ k $\Omega$ (typ) resistor. |

| 3                                          | OUTBP/OUTBM Output Level Selection. Drive OAMPB high for low output amplitude. Drive OAMPB low or leave unconnected for high output amplitude. See the <i>Electrical Characteristics</i> table. OAMPB is internally pulled down by a $330$ k $\Omega$ (typ) resistor. |                                                                                                                                                                                                                                                                       |

| 4, 7, 11, 14,<br>23, 26, 29,<br>31, 34, 37 | GND                                                                                                                                                                                                                                                                   | Ground                                                                                                                                                                                                                                                                |

| 5                                          | INP                                                                                                                                                                                                                                                                   | Channel 1 Noninverting Input                                                                                                                                                                                                                                          |

| 6                                          | INM                                                                                                                                                                                                                                                                   | Channel 1 Inverting Input                                                                                                                                                                                                                                             |

| 8                                          | SEL1                                                                                                                                                                                                                                                                  | Channel 1 Active-Output Selection Input. Drive SEL1 low or leave unconnected to activate A outputs. Drive SEL1 high to activate B outputs. SEL1 is internally pulled down by a 330k $\Omega$ (typ) resistor.                                                          |

| 9                                          | SEL2                                                                                                                                                                                                                                                                  | Channel 2 Active-Input Selection Input. Drive SEL2 low or leave unconnected to activate A inputs. Drive SEL2 high to activate B inputs. SEL2 is internally pulled down by a $330k\Omega$ (typ) resistor.                                                              |

|                                            |                                                                                                                                                                                                                                                                       | Enable Input. Drive EN low or leave unconnected for reduced power standby mode. Drive EN high for normal operation. See Table 1. EN is internally pulled down by a $330k\Omega$ (typ) resistor.                                                                       |

| 12                                         | OUTP                                                                                                                                                                                                                                                                  | Channel 2 Noninverting Output                                                                                                                                                                                                                                         |

| 13                                         | OUTM                                                                                                                                                                                                                                                                  | Channel 2 Inverting Output                                                                                                                                                                                                                                            |

## Pin Description (continued)

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                 |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | MODEA | INAP/INAM OOB-Mode Logic Input. Drive MODEA low or leave unconnected for SAS OOB threshold. Drive MODEA high for SATA OOB threshold. MODEA is internally pulled down by a 330k $\Omega$ (typ) resistor.                                                                  |

| 16  | MODEB | INBP/INBM OOB-Mode Logic Input. Drive MODEB low or leave unconnected for SAS OOB threshold. Drive MODEB high for SATA OOB threshold. MODEB is internally pulled down by a 330k $\Omega$ (typ) resistor.                                                                  |

| 18  | OAMP  | OUTP/OUTM Output Level Selection. Drive OAMP high for low output amplitude. Drive OAMP low or leave unconnected for high output amplitude. See the <i>Electrical Characteristics</i> table. OAMP is internally pulled down by a $330k\Omega$ (typ) resistor.             |

| 19  | OUTPE | OUTP/OUTM Output Preemphasis Logic Input. Drive OUTPE low or leave unconnected for no output preemphasis. Drive OUTPE high for 3dB (typ) output preemphasis. OUTPE is internally pulled down by a $330k\Omega$ (typ) resistor.                                           |

| 20  | EQB   | INBP/INBM Input Equalization Logic Input. Drive EQB low or leave unconnected for no input equalization. Drive EQB high for 4dB (typ) input equalization. EQB is internally pulled down by a $330k\Omega$ (typ) resistor.                                                 |

| 21  | EQA   | INAP/INAM Input Equalization Logic Input. Drive EQA low or leave unconnected for no input equalization. Drive EQA high for 4dB (typ) input equalization. EQA is internally pulled down by a $330k\Omega$ (typ) resistor.                                                 |

| 24  | INBM  | Channel 2 Inverting Input B                                                                                                                                                                                                                                              |

| 25  | INBP  | Channel 2 Noninverting Input B                                                                                                                                                                                                                                           |

| 27  | INAM  | Channel 2 Inverting Input A                                                                                                                                                                                                                                              |

| 28  | INAP  | Channel 2 Noninverting Input A                                                                                                                                                                                                                                           |

| 30  | EN    | Active-Low Enable Input. Drive $\overline{\text{EN}}$ high or leave unconnected for reduced power standby mode.<br>Drive $\overline{\text{EN}}$ low for normal operation. See Table 1. $\overline{\text{EN}}$ is internally pulled up by a 330k $\Omega$ (typ) resistor. |

| 32  | OUTBM | Channel 1 Inverting Output B                                                                                                                                                                                                                                             |

| 33  | OUTBP | Channel 1 Noninverting Output B                                                                                                                                                                                                                                          |

| 35  | OUTAM | Channel 1 Inverting Output A                                                                                                                                                                                                                                             |

| 36  | OUTAP | Channel 1 Noninverting Output A                                                                                                                                                                                                                                          |

| 39  | PEA   | OUTAP/OUTAM Output Preemphasis Logic Input. Drive PEA low or leave unconnected for no output preemphasis. Drive PEA high for 3dB (typ) output preemphasis. PEA is internally pulled down by a $330k\Omega$ (typ) resistor.                                               |

| 40  | PEB   | OUTBP/OUTBM Output Preemphasis Logic Input. Drive PEB low or leave unconnected for no output preemphasis. Drive PEB high for 3dB (typ) output preemphasis. PEB is internally pulled down by a $330k\Omega$ (typ) resistor.                                               |

| 41  | INEQ  | INP/INM Input Equalization Logic Input. Drive INEQ low or leave unconnected for no input equalization. Drive INEQ high for 4dB (typ) input equalization. INEQ is internally pulled down by a $330k\Omega$ (typ) resistor.                                                |

| 42  | MODE  | INP/INM OOB-Mode Logic Input. Drive MODE low or leave unconnected for SAS OOB threshold. Drive MODE high for SATA OOB threshold. MODE is internally pulled down by a $330k\Omega$ (typ) resistor.                                                                        |

|     | EP    | Exposed Pad. Internally connected to GND. Connect EP to a large ground plane to maximize thermal performance.                                                                                                                                                            |

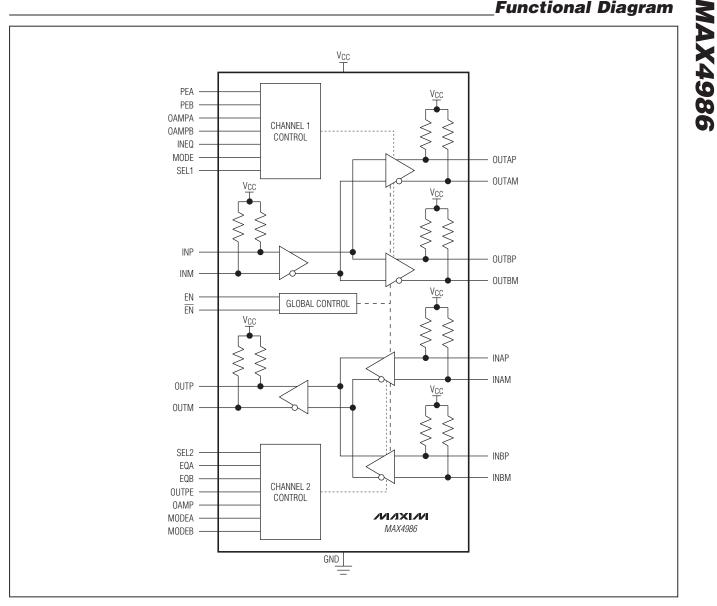

## **Functional Diagram**

# **MAX4986**

#### **Detailed Description**

The MAX4986 is an active 2:1/1:2 multiplexer/demultiplexer designed to equalize and redrive SAS/SATA (Enterprise Class, SATA \_X) or SATA-only signals up to 6.0Gbps.

#### **Input/Output Terminations**

Inputs and outputs are internally  $50\Omega$  terminated to VCC and must be AC-coupled using low-ESR, X7R, 10nF capacitors to the SAS/SATA controller IC and SAS/SATA device for proper operation.

#### Enable Inputs (EN, EN)

The MAX4986 features both an active-high enable input (EN) and an active-low enable input ( $\overline{\text{EN}}$ ). EN has an internal pulldown resistor of  $330 \text{k}\Omega$  (typ), and  $\overline{\text{EN}}$  has an internal pullup resistor of  $330 \text{k}\Omega$  (typ). When EN is driven low or left unconnected, or when  $\overline{\text{EN}}$  is driven high or

#### Table 1. Standby Mode

| EN | EN | STATUS                |  |  |  |

|----|----|-----------------------|--|--|--|

| 0  | Х  | Reduced Power Standby |  |  |  |

| Х  | 1  | Reduced Power Standby |  |  |  |

| 1  | 0  | Active                |  |  |  |

X = Don't care.

#### Table 2. Active Input/Output Select

| SEL1 | SEL2 | ACTIVE OUTPUT | ACTIVE INPUT |

|------|------|---------------|--------------|

| Х    | 0    | Х             | INAP/INAM    |

| Х    | 1    | Х             | INBP/INBM    |

| 0    | Х    | OUTAP/OUTAM   | Х            |

| 1    | Х    | OUTBP/OUTBM   | Х            |

X = Don't care.

#### **Table 3. Output Preemphasis**

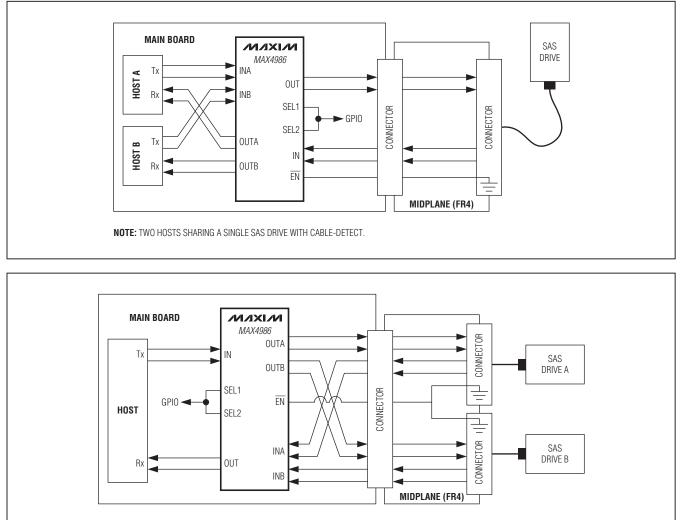

left unconnected, the MAX4986 enters reduced power standby mode and the redrivers are disabled. In standby mode, supply current is reduced to  $350\mu$ A (typ). Drive EN high and  $\overline{\text{EN}}$  low for normal operation. See Table 1.  $\overline{\text{EN}}$  is useful as an automated cable-detect. See the *Typical Application Circuits*.

#### Active Input/Output Select (SEL1, SEL2)

SEL1 selects the active output for channel 1 and SEL2 selects the active input for channel 2. Drive SEL1 or SEL2 low or leave unconnected to activate A inputs or outputs. Drive SEL1 or SEL2 high to activate B inputs or outputs. See Table 2. SEL1 and SEL2 have internal pulldown resistors of  $330k\Omega$  (typ).

#### Programmable Output Preemphasis (OUTPE, PEA, PEB)

The MAX4986 features independent output preemphasis capable of providing 3dB preemphasis on each channel. When OUTPE, PEA, or PEB are driven low or left unconnected, the corresponding output has no preemphasis. When OUTPE, PEA, or PEB are driven high, the corresponding output has 3dB preemphasis. See Table 3. OUTPE, PEA, and PEB have internal pulldown resistors of  $330k\Omega$  (typ). Output preemphasis should be used when driving long traces or cables.

#### Programmable Input Equalization (INEQ, EQA, EQB)

The MAX4986 features independent input equalization capable of providing 4dB of high-frequency equalization on each channel. When INEQ, EQA, or EQB are driven low or left unconnected, the corresponding input has no equalization. When INEQ, EQA, or EQB are driven high, the corresponding input has 4dB equalization. See Table 4. INEQ, EQA, and EQB have internal pulldown resistors of 330k $\Omega$  (typ). Input equalization should be used for long traces or cables.

| OUTPE | PEA | PEB | OUTP/OUTM | OUTAP/OUTAM | OUTBP/OUTBM |

|-------|-----|-----|-----------|-------------|-------------|

| 0     | Х   | Х   | 0dB       | Х           | Х           |

| 1     | Х   | Х   | 3dB       | Х           | Х           |

| Х     | 0   | Х   | Х         | 0dB         | Х           |

| Х     | 1   | Х   | Х         | 3dB         | Х           |

| Х     | Х   | 0   | Х         | Х           | 0dB         |

| Х     | Х   | 1   | Х         | Х           | 3dB         |

X = Don't care.

#### Table 4. Input Equalization

| INEQ | EQA | EQB | INP/INM | INAP/INAM | INBP/INBM |

|------|-----|-----|---------|-----------|-----------|

| 0    | Х   | Х   | 0dB     | Х         | Х         |

| 1    | Х   | Х   | 4dB     | Х         | Х         |

| Х    | 0   | Х   | Х       | 0dB       | Х         |

| Х    | 1   | Х   | X       | 4dB       | Х         |

| Х    | Х   | 0   | Х       | Х         | 0dB       |

| Х    | Х   | 1   | Х       | Х         | 4dB       |

X = Don't care.

#### Table 5. OOB Mode Select

| MODE | MODEA | MODEB | INP/INM | INAP/INAM | INBP/INBM |

|------|-------|-------|---------|-----------|-----------|

| 0    | Х     | Х     | SAS     | Х         | Х         |

| 1    | Х     | Х     | SATA    | Х         | Х         |

| Х    | 0     | Х     | Х       | SAS       | Х         |

| Х    | 1     | Х     | Х       | SATA      | Х         |

| X    | Х     | 0     | Х       | Х         | SAS       |

| Х    | Х     | 1     | Х       | Х         | SATA      |

X = Don't care.

## Table 6. Output Amplitude Selection

| OAMP | OAMPA | OAMPB | OUTP/OUTM | OUTAP/OUTAM | OUTBP/OUTBM |

|------|-------|-------|-----------|-------------|-------------|

| 0    | Х     | Х     | HIGH*     | Х           | Х           |

| 1    | Х     | Х     | LOW*      | Х           | Х           |

| Х    | 0     | Х     | Х         | HIGH*       | Х           |

| Х    | 1     | Х     | Х         | LOW*        | Х           |

| Х    | Х     | 0     | Х         | Х           | HIGH*       |

| Х    | Х     | 1     | Х         | Х           | LOW*        |

X = Don't care.

\*See the Electrical Characteristics table.

#### SAS/SATA Mode Inputs (MODE, MODEA, MODEB)

The MAX4986 supports both SAS and SATA OOB levels. When MODE, MODEA, or MODEB are driven low or left unconnected, the corresponding input's OOB threshold is 120mVP-P (min) (SAS mode). When MODE, MODEA, or MODEB are driven high, the corresponding input's OOB threshold is 50mVP-P (min) (SATA mode). Signals below the OOB threshold are squelched to prevent unwanted noise from being redriven at the output. See Table 5. MODE, MODEA, and MODEB have internal pull-down resistors of  $330k\Omega$  (typ).

#### Output Amplitude Selection Inputs (OAMP, OAMPA, OAMPB)

The MAX4986 features independent output amplitude selection. When OAMP, OAMPA, or OAMPB are driven high, the corresponding output amplitude is low. When OAMP, OAMPA, or OAMPB are driven low or left unconnected, the corresponding output amplitude is high. See Table 6. OAMP, OAMPA, and OAMPB have internal pulldown resistors of  $330k\Omega$  (typ).

## \_Typical Application Circuits

NOTE: SINGLE HOST WITH TWO SAS DRIVES AND CABLE-DETECT.

#### **Applications Information**

#### Layout

Circuit board layout and design can significantly affect the performance of the MAX4986. Use good, high-frequency design techniques, including minimizing ground inductance and using controlled impedance transmission lines on data signals. It is recommended to place 1 $\mu$ F and 0.01 $\mu$ F power-supply bypass capacitors in parallel as close to V<sub>CC</sub> as possible for each V<sub>CC</sub> pin. Always connect V<sub>CC</sub> to a power plane.

#### **Exposed-Pad Package**

The exposed-pad, 42-pin TQFN package incorporates features that provide a very low-thermal resistance path for heat removal from the IC. The exposed pad on the MAX4986 must be soldered to the circuit board ground plane for proper thermal performance. For more information on exposed-pad packages, refer to Maxim Application Note 862: *HFAN-08.1: Thermal Considerations of QFN and Other Exposed-Paddle Packages*.

#### **Power-Supply Sequencing**

Caution: Do not exceed the absolute maximum ratings because stresses beyond the listed ratings may cause permanent damage to the device.

Proper power-supply sequencing is recommended for all devices. Always apply GND then VCC before applying signals, especially if the signal is not current-limited.

\_\_Chip Information

PROCESS: BICMOS

#### Package Information

For the latest package outline information and land patterns (footprints), go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE   | OUTLINE        | LAND        |

|------------|-----------|----------------|-------------|

| TYPE       | CODE      | NO.            | PATTERN NO. |

| 42 TQFN-EP | T423590+1 | <u>21-0181</u> |             |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                     | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------|------------------|

| 0                  | 1/10             | Initial release                 | —                |

| 1                  | 7/12             | Added MAX4986ETO+ to data sheet | 1, 2, 3          |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

14 \_\_\_\_\_ Maxim Integrated Products, Inc. 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000

© 2012 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Multiplexer Switch ICs category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

NLV74HC4066ADR2G HEF4051BP MC74HC4067ADTG DG508AAK/883B NLV14051BDG 016400E PI3V512QE 7705201EC PI2SSD3212NCE PI3L100QE NLAS3257CMX2TCG PI5A3157BC6EX PI3V512QEX PI3DBS16213ZLEX PI3DBS16415ZHEX PS509LEX MUX36S16IRSNR 74LVC1G3157GM-Q10X TC7W53FK,LF CD4053BM96 MC74HC4053ADWR2G MAX4051AEEE+ PI3L720ZHEX ADG1404YRUZ-REEL7 ADG1208YRZ-REEL7 MAX4704EUB+T ADG1406BRUZ-REEL7 CD4053BPWRG4 ADG658TRUZ-EP 74HC4053D.653 74HCT4052PW.118 74LVC2G53DP.125 74HC4052DB.112 74HC4052PW.112 74HC4053DB.112 74HC4067DB.112 74HC4351DB.112 74HCT4052D.112 74HCT4052DB.112 74HCT4351D.112 74LV4051PW.112 FSA1256L8X\_F113 PI5V330QE PI5V331QE 5962-8771601EA 5962-87716022A ADG5249FBRUZ ADG1438BRUZ ADG5207BCPZ-RL7 ADW54003-0