##

### **High-Voltage PWM Power-Supply Controller**

#### **General Description**

The MAX5003 high-voltage switching power-supply controller has all the features and building blocks needed for a cost-effective flyback and forward voltagemode control converter. This device can be used to design both isolated and nonisolated power supplies with multiple output voltages that operate from a wide range of voltage sources. It includes a high-voltage internal start-up circuit that operates from a wide 11V to 110V input range. The MAX5003 drives an external Nchannel power MOSFET and has a current-sense pin that detects overcurrent conditions and turns off the power switch when the current-limit threshold is exceeded. The choice of external power MOSFET and other external components determines output voltage and power.

The MAX5003 offers some distinctive advantages: softstart, undervoltage lockout, external frequency synchronization, and fast input voltage feed-forward. The device is designed to operate at up to 300kHz switching frequency. This allows use of miniature magnetic components and low-profile capacitors. Undervoltage lockout, soft-start, switching frequency, maximum duty cycle, and overcurrent protection limit are all adjustable using a minimum number of external components. In systems with multiple controllers, the MAX5003 can be externally synchronized to operate from a common system clock.

Warning: The MAX5003 is designed to operate with high voltages. Exercise caution.

The MAX5003 is available in 16-pin SO and QSOP packages. An evaluation kit (MAX5003EVKIT) is also available.

### **Applications**

**Telecommunication Power Supplies** ISDN Power Supplies +42V Automobile Systems High-Voltage Power-Supply Modules **Industrial Power Supplies**

#### **Features**

- ♦ Wide Input Range: 11V to 110V

- ♦ Internal High-Voltage Startup Circuit

- **♦ Externally Adjustable Settings Output Switch Current Limit Oscillator Frequency Soft-Start Undervoltage Lockout Maximum Duty Cycle**

- **♦ Low External Component Count**

- **♦** External Frequency Synchronization

- **♦ Primary or Secondary Regulation**

- ♦ Input Feed-Forward for Fast Line-Transient Response

- ♦ Precision ±2.5% Reference over Rated **Temperature Range**

- ♦ Thermal Shutdown

### **Ordering Information**

| PART       | TEMP. RANGE               | PIN-PACKAGE  |

|------------|---------------------------|--------------|

| MAX5003CEE | 0°C to +70°C              | 16 QSOP      |

| MAX5003CSE | 0°C to +70°C 16 Narrow SO |              |

| MAX5003C/D | (Note A)                  | Dice         |

| MAX5003EEE | -40°C to +85°C            | 16 QSOP      |

| MAX5003ESE | -40°C to +85°C            | 16 Narrow SO |

**Note:** Dice are designed to operate over a -40°C to +140°C junction temperature (T<sub>i</sub>) range, but are tested and guaranteed at  $T_A = +25$ °C.

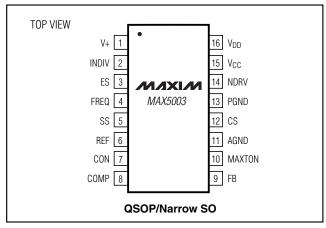

### Pin Configuration

MIXIM

#### **ABSOLUTE MAXIMUM RATINGS**

| V+ to GND                        | 0.3V to +120V                    |

|----------------------------------|----------------------------------|

| ES to GND                        | 0.3V to +40V                     |

| V <sub>DD</sub> to GND           | 0.3V to +19V                     |

| V <sub>CC</sub> to GND           | 0.3V to +12.5V                   |

| MAXTON, COMP, CS, FB, CON to GND | 0.3V to +8V                      |

| NDRV, SS, FREQ to GND            | 0.3V to (V <sub>CC</sub> + 0.3V) |

| INDIV, REF to GND                | 0.3V to +4.5V                    |

| VCC, VDD, V+, ES Current         | ±20mA                            |

| NDRV Current, Continuous         | ±25mA                            |

| NDRV Current, ≤ 1µs              | ±1A                              |

| CON and REF Current              | ±20mA                            |

| All Other Pins                   | ±20mA                            |

|                                  |                                  |

| Continuous Power Dissipation ( $T_A = +70$ °C)   |                |

|--------------------------------------------------|----------------|

| 16-Pin SO (derate 9.5mW/°C above +70°C)          | )762mW         |

| 16-Pin QSOP (derate 8.3mW/°C above +70           | °C)667mW       |

| Maximum Junction Temperature (T <sub>J</sub> )   | +150°C         |

| Operating Temperature Ranges                     |                |

| MAX5003C_E                                       | 0°C to +70°C   |

| MAX5003E_E                                       | 40°C to +85°C  |

| Operating Junction Temperature (T <sub>J</sub> ) | +125°C         |

| 16-Pin SO θ <sub>JA</sub>                        | 105°C/W        |

| 16-Pin QSOP θ <sub>JA</sub>                      | 120°C/W        |

| Storage Temperature Range                        | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                | +300°C         |

|                                                  |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V+ = VES = VDD = +12V, V_{INDIV} = 2V, V_{CON} = 0, R_{FREQ} = R_{MAXTON} = 200k\Omega, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                       | SYMBOL           | CONDITIONS                                                                         |                                                  | MIN   | TYP   | MAX   | UNITS |

|-------------------------------------------------|------------------|------------------------------------------------------------------------------------|--------------------------------------------------|-------|-------|-------|-------|

| SUPPLY CURRENT                                  | •                |                                                                                    |                                                  |       |       |       |       |

| Shutdown Current                                | l+               | V <sub>INDIV</sub> = 0, V+ = 110V, V <sub>ES</sub> = V <sub>DD</sub> = unconnected |                                                  |       | 35    | 75    | μΑ    |

| Supply Current                                  | I <sub>DD</sub>  | $V + = V_{ES}$ , $V_{DD} = 18.7$                                                   | 5                                                |       |       | 1.2   | mA    |

| PREREGULATOR/STARTUP                            | •                |                                                                                    |                                                  |       |       |       |       |

| V. Input Voltage (Note 1)                       | \/.              | E <sub>S</sub> = V <sub>DD</sub> = uncon-                                          | I <sub>NDRV</sub> = 2mA                          | 25    |       |       | V     |

| V+ Input Voltage (Note 1)                       | V+               | nected                                                                             | I <sub>NDRV</sub> = 5mA                          |       |       | 110   | V     |

| E <sub>S</sub> Input Voltage (Note 1)           | V <sub>ESI</sub> | V <sub>DD</sub> = unconnected, V                                                   | /+ = V <sub>ES</sub> , I <sub>NDRV</sub> = 7.5mA | 10.8  |       | 36    | V     |

| Es Output Voltage                               | V <sub>ESO</sub> | V+ = 110V, V <sub>DD</sub> = unc                                                   | onnected                                         |       |       | 36    | V     |

| V <sub>DD</sub> Output Voltage                  | V <sub>DD</sub>  | V+ = 36V, I <sub>DD</sub> = 0 to 7.5mA,<br>ES = unconnected                        |                                                  | 9     | 9.75  | 10.5  | ٧     |

| V <sub>DD</sub> Input Voltage Range             | V <sub>DD</sub>  | V+ = V <sub>ES</sub> = 36V, I <sub>NDRV</sub> = 7.5mA                              |                                                  | 10.75 |       | 18.75 | V     |

| V <sub>DD</sub> Regulator Turn-Off Voltage      | V <sub>TO</sub>  | V+ = 36V, I <sub>V+</sub> < 75μA,<br>ES = unconnected                              |                                                  | 10.75 |       |       | V     |

| CHIP SUPPLY (V <sub>CC</sub> )                  | 1                |                                                                                    |                                                  |       |       |       |       |

| V <sub>CC</sub> Output Voltage                  | Vcc              | V+ = 36V, ES = unconnected,<br>V <sub>DD</sub> = 18.75V                            |                                                  | 7.4   |       | 12    | V     |

| V <sub>CC</sub> Undervoltage<br>Lockout Voltage | Vcclo            | V <sub>CC</sub> falling                                                            |                                                  |       | 6.3   |       | V     |

| OUTPUT DRIVER                                   | •                |                                                                                    |                                                  |       |       |       |       |

| Peak Source Current                             |                  | V <sub>NDRV</sub> = 0, V <sub>CC</sub> supported by V <sub>CC</sub> capacitor      |                                                  |       | 570   |       | mA    |

| Peak Sink Current                               |                  | V <sub>NDRV</sub> = V <sub>CC</sub>                                                |                                                  |       | 1000  |       | mA    |

| NDRV Resistance High                            | Roh              | I <sub>NDRV</sub> = 50 mA                                                          |                                                  |       | 4     | 12    | Ω     |

| NDRV Resistance Low                             | RoL              | I <sub>NDRV</sub> = 50 mA                                                          |                                                  |       | 1     |       | Ω     |

| REFERENCE                                       |                  |                                                                                    |                                                  |       |       |       |       |

| REF Output Voltage                              | V <sub>REF</sub> | No load                                                                            |                                                  | 2.905 | 3.000 | 3.098 | V     |

| REF Voltage Regulation                          | $\Delta V_{REF}$ | I <sub>REF</sub> = 0 to 1mA                                                        |                                                  |       | 5     | 20    | mV    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+ = V_{ES} = V_{DD} = +12V, V_{INDIV} = 2V, V_{CON} = 0, R_{FREQ} = R_{MAXTON} = 200k\Omega, T_A = T_{MIN~to} T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETERS                           | SYMBOL            | CONDITIONS                                                |                            | MIN   | TYP   | MAX   | UNITS   |

|--------------------------------------|-------------------|-----------------------------------------------------------|----------------------------|-------|-------|-------|---------|

| CURRENT LIMIT                        | L                 | 1                                                         |                            |       |       |       | 1       |

| CS Threshold Voltage                 | V <sub>CS</sub>   | V <sub>CON</sub> = 1.25V                                  | 80                         | 100   | 120   | mV    |         |

| CS Input Bias Current                | Ics               | 0 < V <sub>CS</sub> < 0.1V                                |                            | -1    |       | +1    | μΑ      |

| Overcurrent Delay                    | t <sub>D</sub>    | From end of blanking                                      | time 25mV overdrive        |       | 240   |       | ns      |

| CS Blanking Time                     | tB                |                                                           |                            |       | 70    |       | ns      |

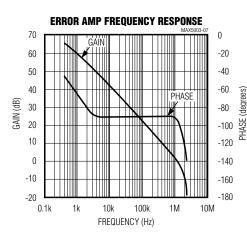

| ERROR AMPLIFIER                      |                   |                                                           |                            |       |       |       | •       |

| Voltage Gain                         | Av                | ICOMP = 5µA; VCOMP                                        | = 0.5V, 2.5V               | 60    | 80    |       | dB      |

| Unity-Gain Bandwidth                 | BW                | $R_{LOAD} = 200k\Omega$ , $C_{LOA}$                       | <sub>AD</sub> = 100pF      |       | 1.2   |       | MHz     |

| Phase Margin                         | ф                 | $A_{VOL} = 1V/V, C_{LOAD} =$                              | = 100pF                    |       | 65    |       | degrees |

| Output Clamp Low                     | VCOMPL            | At COMP                                                   |                            |       | 0.25  |       | V       |

| Output Clamp High                    | Vсомрн            | At COMP                                                   |                            |       | 3.00  |       | V       |

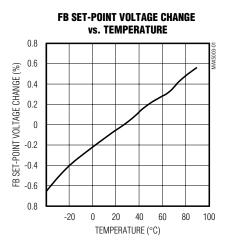

| FEEDBACK INPUT AND SET               | POINT             |                                                           |                            |       |       |       |         |

| FB Regulation Voltage                | VSET              | FB = COMP, V <sub>CON</sub> =                             | 1.5V                       | 1.448 | 1.485 | 1.522 | V       |

| FB Bias Current                      | I <sub>FB</sub>   | V <sub>FB</sub> = 1.5V                                    |                            | -1    | 0.1   | +1    | μA      |

| FB V <sub>SET</sub> Tempco           | TC <sub>FB</sub>  |                                                           |                            |       | 100   |       | ppm/°C  |

| UNDERVOLTAGE LOCKOUT                 |                   |                                                           |                            |       |       |       |         |

| INDIV Undervoltage Lockout           | VINDIVLO          | V+ = V <sub>ES</sub> = V <sub>DD</sub> = 10.8V and 18.75V | V <sub>INDIV</sub> falling | 1.15  | 1.20  | 1.25  | V       |

| INDIV Ondervoltage Lockout           |                   |                                                           | V <sub>INDIV</sub> rising  | 1.23  | 1.32  | 1.45  | ]       |

| INDIV Hysteresis                     | V <sub>HYST</sub> |                                                           |                            |       | 125   |       | mV      |

| INDIV Bias Current                   |                   | V <sub>INDIV</sub> = 1.28V                                |                            | -1    | 0.01  | +1    | μA      |

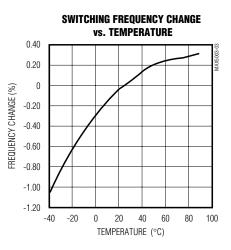

| MAIN OSCILLATOR—EXTERN               | IAL MODE          |                                                           |                            |       |       |       |         |

| FREQ Input Low                       | VIL               | V <sub>CON</sub> = 3.0V                                   |                            |       |       | 0.8   | V       |

| FREQ Input High                      | VIH               | $V_{CON} = 3.0V$                                          |                            | 2.7   |       |       | V       |

| FREQ Output Low                      | I <sub>OL</sub>   | $V_{FREQ} = 5V, V_{CON} = 3$                              | 3.0V                       |       |       | 1     | μΑ      |

| External Oscillator Maximum Low Time | text              | (Note 2)                                                  |                            | 8     | 13    |       | μs      |

| FREQ Range                           | fFREQ             |                                                           |                            | 200   |       | 1200  | kHz     |

| Frequency Range                      | fs                | fs = 1/4 fFREQ                                            |                            | 50    |       | 300   | kHz     |

| FREQ HI/LO Pulse Width               |                   | O PETITE OF                                               |                            | 150   |       |       | ns      |

| MAIN OSCILLATOR—INTERN               | AL MODE           |                                                           |                            |       |       |       |         |

| FREQ Resistor Range                  | RFREQ             |                                                           |                            | 50    |       | 500   | kΩ      |

| Oscillator Frequency                 |                   |                                                           |                            | 80    | 100   | 120   | kHz     |

| FREQ Output Current High             | Іон               | V <sub>FREQ</sub> = 0                                     |                            |       |       | 300   | μA      |

| FREQ Output Current Low              | loL               | V <sub>FREQ</sub> = 1.5V                                  |                            |       |       | 1     | μA      |

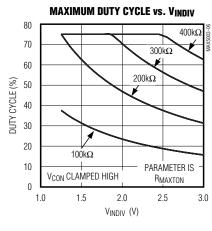

| MAXIMUM DUTY CYCLE (MAX              | (TON)             | ı                                                         |                            | 1     |       |       | 1       |

| Maximum Programmable Duty Cycle      |                   | V <sub>INDIV</sub> = 1.25V                                |                            |       | 75    |       | %       |

|                                      |                   | l .                                                       |                            |       |       |       | 1       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+ = V_{ES} = V_{DD} = +12V, V_{INDIV} = 2V, V_{CON} = 0, R_{FREQ} = R_{MAXTON} = 200k\Omega, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETERS                          | SYMBOL  | CONDITIONS                                                                     | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------|---------|--------------------------------------------------------------------------------|------|------|------|-------|

| PWM OSCILLATOR                      |         |                                                                                |      |      |      | l.    |

| MAXTON Resistor Range               | RMAXTON |                                                                                | 50   |      | 500  | kΩ    |

| Maximum On-Time Range               | ton     | RMAXTON = $200k\Omega$ , $V_{INDIV} = 1.25V$                                   |      | 7.5  |      | μs    |

| Input Voltage Feed Forward<br>Ratio |         | $V_{INDIV}$ stepped from 1.5V to 1.875V, $V_{CON} =$ 3.0V (Note 3)             | 0.72 | 0.8  | 0.88 |       |

| RAMP Voltage Low                    |         | V <sub>INDIV</sub> = 1.875V                                                    | 0.48 | 0.5  | 0.53 | V     |

| RAMP Voltage High                   |         |                                                                                |      | 2.5  |      | V     |

| Minimum On-Time                     |         |                                                                                |      | 200  |      | ns    |

| SOFT-START                          | •       |                                                                                |      |      |      |       |

| SS Source Current                   |         | V <sub>SS</sub> = 0.5V, V <sub>DD</sub> = unconnected, V <sub>CON</sub> = 1.5V | 3.4  | 5.5  | 9    | μΑ    |

| SS Sink Current                     |         | V <sub>SS</sub> = 0.4V (Note 4)                                                |      | 10   |      | mA    |

| SS Time                             |         |                                                                                |      | 0.45 |      | s/µF  |

| PWM COMPARATOR                      |         |                                                                                |      |      |      |       |

| CON Bias Current                    | ICON    | V <sub>CON</sub> = 0.5V and 2.5V                                               | -1   | 0.01 | 1    | μΑ    |

| THERMAL SHUTDOWN                    |         |                                                                                |      |      |      |       |

| Thermal Shutdown Temperature        |         |                                                                                |      | 150  |      | °C    |

| Thermal Hysteresis                  |         |                                                                                |      | 20   |      | °C    |

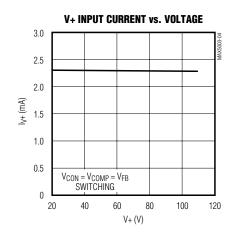

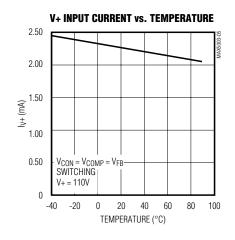

Note 1: See the Typical Operating Characteristics for preregulator current-to-voltage characteristics.

Note 2: Maximum time FREQ can be held below V<sub>IL</sub> and still remain in external mode.

Note 3: Feed-forward Ratio = Duty cycle at (V<sub>INDIV</sub> = 1.5V)/Duty cycle at (V<sub>INDIV</sub> = 1.875V)

Note 4: Occurs at start-up and until VREF is valid.

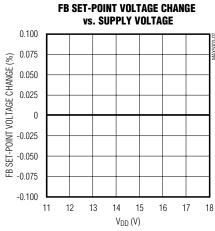

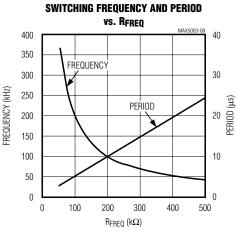

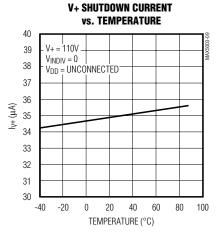

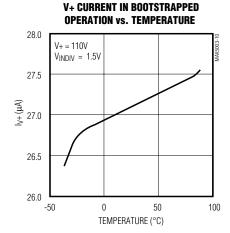

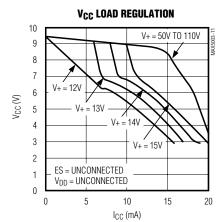

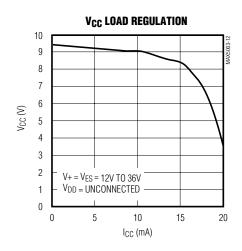

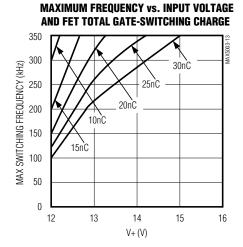

### Typical Operating Characteristics

$(V_{DD} = +12V, R_{FREQ} = 200k\Omega, R_{MAXTON} = 200k\Omega, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

$(V_{DD} = +12V, R_{FREQ} = 200k\Omega, R_{MAXTON} = 200k\Omega, T_A = +25^{\circ}C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(V_{DD} = +12V, R_{FREQ} = 200k\Omega, R_{MAXTON} = 200k\Omega, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN                                                                                                      | NAME                                                                                                                                                                                                                                                                                | FUNCTION                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                                                                                                        | V+                                                                                                                                                                                                                                                                                  | Preregulator Input. Connect to the power line for use with 25V to 110V line voltages. Bypass V+ to ground with a 0.1µF capacitor, close to the IC. Connects internally to the drain of a depletion FET preregulator.                                                                                                                       |  |  |  |

| 2                                                                                                        | Undervoltage Sensing and Feed-Forward Input. Connect to the center point of an external resistive div connected between the main power line and AGND. Undervoltage lockout takes over and shuts down the controller when V <sub>INDIV</sub> < 1.2V. INDIV bias is typically 0.01µA. |                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 3                                                                                                        | ES                                                                                                                                                                                                                                                                                  | Preregulator Output. When V+ ranges above 36V, bypass ES to AGND with a 0.1µF capacitor close to the IC. When V+ is always below 36V, connect ES to V+.                                                                                                                                                                                    |  |  |  |

| 4 FREQ pin is internally regulated to 1.25V. Connect a resistor between this pin and AGND to set the PWM |                                                                                                                                                                                                                                                                                     | Oscillator Frequency Adjust and Synchronization Input. In internal free-running mode, the voltage on this pin is internally regulated to 1.25V. Connect a resistor between this pin and AGND to set the PWM frequency. Drive between V <sub>IL</sub> and V <sub>IH</sub> at four times the desired frequency for external synchronization. |  |  |  |

| 5                                                                                                        | 5 SS Soft-Start Capacitor Connection. Ramp time to full current limit is approximately 0.5ms/nF. Limits du cycle when Vss < Vcon.                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 6                                                                                                        | REF Reference Voltage Output (3.0V). Bypass to AGND with a 0.1µF capacitor.                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 7                                                                                                        | CON                                                                                                                                                                                                                                                                                 | Control Input of the PWM Comparator                                                                                                                                                                                                                                                                                                        |  |  |  |

| 8                                                                                                        | COMP                                                                                                                                                                                                                                                                                | Compensation Connection. Output of the error amplifier, available for compensation.                                                                                                                                                                                                                                                        |  |  |  |

| 9                                                                                                        | FB                                                                                                                                                                                                                                                                                  | Feedback Input. Regulates to V <sub>FB</sub> = V <sub>REF</sub> / 2 = 1.5V.                                                                                                                                                                                                                                                                |  |  |  |

| 10                                                                                                       | MAXTON                                                                                                                                                                                                                                                                              | Maximum On-Time Programming. A resistor from MAXTON to AGND sets the PWM gain and limits the maximum duty cycle. The voltage on MAXTON tracks the voltage on the INDIV pin. Maximum on-time is proportional to the value of the programming resistor. The maximum duty cycle is limited to 75%, regardless of the programming resistor.    |  |  |  |

### **Pin Description (continued)**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                  |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | AGND            | Analog Ground. Connect to PGND close to the IC.                                                                                                                                                                                           |

| 12  | CS              | Current Sense with Blanking. Turns power switch off if V <sub>CS</sub> rises above 100mV (referenced to PGND). Connect a $100\Omega$ resistor between CS and the current-sense resistor (Figure 2). Connect CS to PGND if not used.       |

| 13  | PGND            | Power Ground. Connect to AGND.                                                                                                                                                                                                            |

| 14  | NDRV            | Gate Drive for External N-Channel Power FET                                                                                                                                                                                               |

| 15  | Vcc             | Output Driver Power-Rail Decoupling Point. Connect a capacitor to PGND with half the value used for VDD bypass very close to the pin. If synchronizing several controllers, power the fan-out buffer driving the FREQ pins from this pin. |

| 16  | V <sub>DD</sub> | 9.75V Internal Linear-Regulator Output. Drive $V_{DD}$ to a voltage higher than 10.75V to bootstrap the chip supply. $V_{DD}$ is also the supply voltage rail for the chip. Bypass to AGND with a 5µF to 10µF capacitor.                  |

#### **Detailed Description**

The MAX5003 is a PWM controller designed for use as the control and regulation core of voltage-mode control flyback converters or forward-voltage power converters. It provides the power-supply designer with maximum flexibility and ease of use. The device is specified up to 110V and will operate from as low as 11V. Its maximum operating frequency of 300kHz permits the use of miniature magnetic components to minimize board space. The range, polarity, and range of output voltages and power are limited only by design and by the external components used.

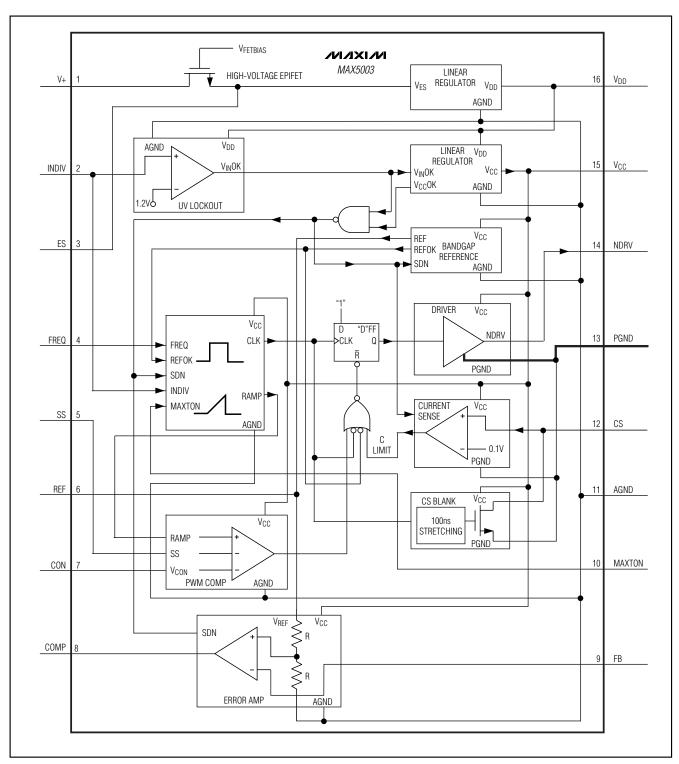

This device works in isolated and nonisolated configurations, and in applications with single or multiple output voltages. All the building blocks of a PWM voltage-mode controller are present in the MAX5003 and its settings are adjustable. The functional diagram is shown on Figure 1.

#### **Modern Voltage-Mode Controllers**

The MAX5003 offers a voltage-mode control topology and adds features such as fast input voltage feed forward, programmable maximum duty cycle, and high operating frequencies. It has all the advantages of current-mode control—good control loop bandwidth, same-cycle response to input voltage changes, and pulse-by-pulse current limiting. It eliminates disadvantages such as the need for ramp compensation, noise sensitivity, and the analytical and design difficulties of dealing with two nested feedback loops. In summary, voltage-mode control has inherent superior noise immunity and uses simpler compensation schemes.

#### **Internal Power Regulators**

The MAX5003's power stages operate over a wide range of supply voltages while maintaining low power consumption. For the high end of the range (+36V to +110V), power is fed to the V+ pin into a depletion junction FET preregulator. This input must be decoupled with a 0.1µF capacitor to the power ground pin (PGND). To decouple the power line, other large-value capacitors must be placed next to the power transformer connection.

The preregulator drops the input voltage to a level low enough to feed a first low-dropout regulator (LDO) (Figure 1). The input to the LDO is brought out at the ES pin. ES must also be decoupled with a 0.1µF capacitor.

In applications where the maximum input voltage is below 36V, connect ES and V+ together and decouple with a  $0.1\mu F$  capacitor.

The first LDO generates the power for the  $V_{DD}$  line. The  $V_{DD}$  line is available at the  $V_{DD}$  pin for decoupling. The bypass to AGND must be a  $5\mu F$  to  $10\mu F$  capacitor.

When the maximum input voltage is always below 18.75V, power may also be supplied at  $V_{DD}$ ; in this case, connect V+, ES, and  $V_{DD}$  together.

Forcing voltages at V<sub>DD</sub> above 10.75V (see *Electrical Characteristics*) disables the first LDO, typically reducing current consumption below 50µA (see *Typical Operating Characteristics*).

Following the  $V_{DD}$  LDO is another regulator that drives  $V_{CC}$ : the power bus for the internal logic, analog circuitry, and external power MOSFET driver. This regulator is needed because the  $V_{DD}$  voltage level would be too high for the external N-channel MOSFET gate. The

Figure 1. Functional Diagram

VCC regulator has a lockout line that shorts the N-channel MOSFET driver output to ground if the VCC LDO is not regulating. VCC feeds all circuits except the VCC lockout logic, the undervoltage lockout, and the power regulators.

The preferred method for powering the MAX5003 is to start with the high-voltage power source (at V+ or ES, depending on the application), then use a bootstrap source from the same converter with an output voltage higher than the VDD regulator turn-off voltage (10.75V) to power VDD. This will disable the power consumption of the VDD LDO. It is also possible to power the MAX5003 with no bootstrap source from ES or V+, but do not exceed the maximum allowable power dissipation. The current consumption of the part is mostly a function of the operating frequency and the type of external power switch used—in particular, the total charge to be supplied to the gate.

A reference output of 3V nominal is externally available at the REF pin, with a current sourcing capability of 1mA. A lockout circuit shuts off the oscillator and the output driver if REF falls 200mV below its set value.

Minimize loading at REF, since the REF voltage is the source for the FB voltage, which is the regulator set point when the error amplifier is used. Any changes in  $V_{REF}$  will be proportionally reflected in the regulated output voltage of the converter.

#### Undervoltage Lockout, Feed Forward, and Shutdown

The undervoltage lockout feature disables the controller when the voltage at INDIV is below 1.2V (120mV hysteresis). When INDIV rises higher than 1.2V plus the hysteresis (typically 1.32V), it allows the controller to start. An external resistive divider connected between the power line and AGND generates the INDIV signal. INDIV is also used as the signal for the fast input voltage feed-forward circuit.

Always connect INDIV to a voltage divider. It is not a "don't care" condition; the signal is used to set the fast feed-forward circuit (see the *Oscillator and Ramp Generator* section).

Choose R2 (Figure 2) between  $25 k\Omega$  to  $500 k\Omega$  and calculate R1 to satisfy the following equation:

$$R1 = R2 \left( \frac{V_{SUL}}{V_{INDIVLO}} - 1 \right)$$

where V<sub>SUL</sub> = system undervoltage lockout and V<sub>INDIVLO</sub> = I<sub>NDIV</sub> undervoltage lockout.

The undervoltage lockout function allows the use of the INDIV pin as a shutdown pin with an external switch to

ground. The shutdown circuit must not affect the resistive divider during normal operation.

#### **Current-Sense Comparator**

The current-sense (CS) comparator and its associated logic limit the current through the power switch. Current is sensed at CS as a voltage across a sense resistor between the external MOSFET source and PGND. Connect CS to the external MOSFET source through a  $100\Omega$  resistor or RC lowpass filter (Figures 2 and 3). See *CS Resistor* in the *Component Selection* section.

A blanking circuit shunts CS to ground when the power MOSFET switch is turned off, and keeps it there for 70ns after turn-on. This avoids false trips caused by the switching transients. The blanking circuit also resets the RC filter, if used. When  $V_{CS} > 100 \text{mV}$ , the power MOSFET is switched off. The propagation delay from the time the switch current reaches the trip level to the driver turn-off time is 240ns. If the current limit is not used, the CS pin must be connected to PGND.

#### **Error Amplifier**

The internal error amplifier is one of the building blocks that gives the MAX5003 its flexibility. Its noninverting input is biased at 1.5V, derived from the internal 3V reference. The inverting input is brought outside (FB pin) and is the regulation feedback connection point. If the error amplifier is not used, connect this pin to ground. The output is available for the frequency compensation network and for connection to the input of the PWM comparator (CON). Unity-gain frequency is 1.2MHz, open-circuit gain is 80dB, and the amplifier is unity-gain stable. To eliminate long overload recovery times, there are clamps limiting the output excursions close to the range limits of the PWM ramp. The voltage at the noninverting input of the error amplifier is the regulator set point, but is not accessible.

Set-point voltage can be measured, if needed, by connecting COMP and FB and measuring that node with respect to ground. The error amplifier is powered from the  $V_{CC}$  rail.

#### **PWM Comparator**

The pulse-width modulator (PWM) comparator stage transforms the error signal into a duty cycle by comparing the error signal with a linear ramp. The ramp levels are 0.5V min and 2.5V max. The comparator has a typical hysteresis of 5.6mV and a propagation delay of 100ns. The output of the comparator controls the external FET.

#### Soft-Start

The soft-start feature allows converters built using the MAX5003 to apply power to the load in a controllable soft ramp, thus reducing start-up surges and stresses.

It also determines power-up sequencing when several converters are used.

Upon power turn-on, the SS pin acts as a current sink to reset any capacitance attached to it. Once REF has exceeded its lockout value, SS sources a current to the external capacitor, allowing the converter output voltage to ramp up. Full output voltage is reached in approximately 0.45s/µF.

The SS pin is an overriding extra input to the PWM comparator. As long as its voltage is lower than  $V_{CON}$ , it overrides  $V_{CON}$  and SS determines the level at which the duty cycle is decided by the PWM comparator. After exceeding  $V_{CON}$ , SS no longer controls the duty cycle. Its voltage will keep rising up to  $V_{CC}$ .

#### **Oscillator and Ramp Generator**

The MAX5003 oscillator generates the ramp used by the comparator, which in turn generates the PWM digital signal. It also controls the maximum on-time feature of the controller. The oscillator can operate in two modes: free running and synchronized (sync). A single pin, FREQ, doubles as the attachment point for the frequency programming resistor and as the synchronization input. The mode recognition is automatic, based on the voltage level at the FREQ pin.

In free-running mode, a 1.25V source is internally applied to the pin; the oscillator frequency is proportional to the current out of the pin through the programming resistor, with a proportionality constant of  $16kHz/\mu A$ .

In sync mode, the signal from the external master generator must be a digital rectangular waveform running at four times the desired converter switching frequency. Minimum acceptable signal pulse width is 150ns, positive or negative, and the maximum frequency is 1.2MHz.

When the voltage at FREQ is forced above 2.7V, the oscillator goes into sync mode. If left at or below 1.5V for more than 8µs to 20µs, it enters free-running mode.

The master clock generator cannot be allowed to stop at logic zero. If the system design forces such a situation, an inverter must be used at the FREQ pin.

In sync mode, the oscillator signal is divided by four and decoded. The output driver is blocked during the last phase of the division cycle, giving a hardwired maximum on-time of 75%. In free-running mode, the oscillator duty cycle is 75% on, and the off portion also blocks the output driver. The maximum on-time is then absolutely limited to 75% in either mode. Maximum on-time can be controlled to values lower than 75% by a programming resistor at the MAXTON pin.

The PWM ramp generated goes from 0.5V min to 2.5V max, and the maximum time on is the time it takes from low to high.

MAXTON is internally driven to V<sub>INDIV</sub> and a resistor must be connected from MAXTON to AGND, to program the maximum on-time.

The ramp slope is directly proportional to V<sub>INDIV</sub> and inversely proportional to R<sub>MAXTON</sub>. Since the ramp voltage limits are fixed, controlling the ramp slope sets the maximum time on.

Changing the ramp slope while V<sub>CON</sub> remains constant also changes the duty cycle and the energy transferred to the load per cycle of the converter. The INDIV signal is a fraction of the input voltage, so the fast input voltage feedforward works by modifying the duty cycle in the same clock period, in response to an input voltage change.

Calculate the maximum duty cycle as:

$$D_{MAX} = \frac{MAXTON}{T} \times 100$$

where:

D<sub>MAX</sub> = Maximum duty cycle (%) MAXTON = Maximum on-time T = Switching period

Then:

$$D_{MAX} = 0.75 \times 100 \left( \frac{R_{MAXTON}}{200k\Omega} \right) \left( \frac{1.25V}{V_{INDIV}} \right) \left( \frac{f_{SW}}{100kHz} \right)$$

where:

RMAXTON = Resistor from the MAXTON pin to ground VINDIV = Voltage at the INDIV pin fsw = Output switching frequency MAXTON can then be calculated as:

$$\mbox{MAXTON} = \frac{0.75 \times \mbox{R}_{\mbox{MAXTON}} \times 1.25 \mbox{V}}{200 \mbox{k} \Omega \times \mbox{V}_{\mbox{NDIV}} \times 100 \mbox{kHz}}$$

## N-Channel MOSFET Output Switch Driver

The MAX5003 output drives an N-channel MOSFET transistor. The output sources and sinks relatively large currents, supplying the gate with the charge the transistor needs to switch. These are current spikes only, since after the switching transient is completed the load is a high-value resistance. The current is supplied from the V<sub>CC</sub> rail and must be sourced by a large-value

capacitor ( $5\mu\text{F}$  to  $10\mu\text{F}$ ) at the V<sub>CC</sub> pin, since the rail will not support such a load. It is this current, equivalent to the product of the total gate switching charge (from the N-channel MOSFET data sheet), times the operating frequency, that determines the bulk of the MAX5003 power dissipation.

The driver can source up to 560mA and sink up to 1A transient current with a typical on source resistance of  $4\Omega$ . The no-load output levels are V<sub>CC</sub> and PGND.

### Applications Information

#### Compensation and Loop Design Considerations

The circuit shown in Figure 2 is essentially an energy pump. It stores energy in the magnetic core and the air gap of the transformer while the power switch is on, and delivers it to the load during the off phase. It can operate in two modes: continuous and discontinuous. In discontinuous mode, all the energy is given to the load before the next cycle begins; in continuous mode, some energy is continuously stored in the core.

The system has four operating parameters: input voltage, output voltage, load current, and duty cycle. The PWM controller senses the output voltage and the input voltage, and keeps the output voltage regulated by controlling the duty cycle.

The output filter in this circuit consists of the load resistance and the capacitance on the output.

To study the stability of the feedback system and design the compensation necessary for system stability under all operating conditions, first determine the transfer function. In discontinuous mode, since there is no energy stored in the inductor at the end of the cycle, the inductor and capacitor do not show the characteristic double pole, and there is only a dominant pole defined by the filter capacitor and the load resistance. There is a zero at a higher frequency, defined by the ESR of the output filter capacitor. Such a response is easy to stabilize for a wide range of operating conditions while retaining a reasonably fast loop response.

In continuous mode, the situation is different. The inductor-capacitor combination creates a double pole, since energy is stored in the inductor at all times. In addition to the double pole, a right-half-plane zero appears in the frequency response curves. This response is not easy to compensate. It can result in conditional stability, a complicated compensation network, or very slow transient response.

To avoid the analytical and design problems of the continuous-conduction mode flyback topology and maintain

good loop response, choose a design incorporating a discontinuous-conduction mode power stage

To keep the converter in discontinuous mode at all times, the value of the power transformer's primary inductance must be calculated at minimum line voltage and maximum load, and the maximum duty cycle must be limited. The MAX5003 has a programmable duty-cycle limit function intended for this purpose.

#### **Design Methodology**

Following is a general procedure for developing a system:

- 1) Determine the requirements.

- 2) In free-running mode, choose the FREQ pin programming resistor. In synchronized mode, determine the clock frequency (fCLK).

- 3) Determine the transformer turns ratio, and check the maximum duty cycle.

- 4) Determine the transformer primary inductance.

- Complete the transformer specifications by listing the primary maximum current, the secondary maximum current, and the minimum duty cycle at full power.

- 6) Choose the MAXTON pin programming resistor.

- 7) Choose a filter capacitor.

- 8) Determine the compensation network.

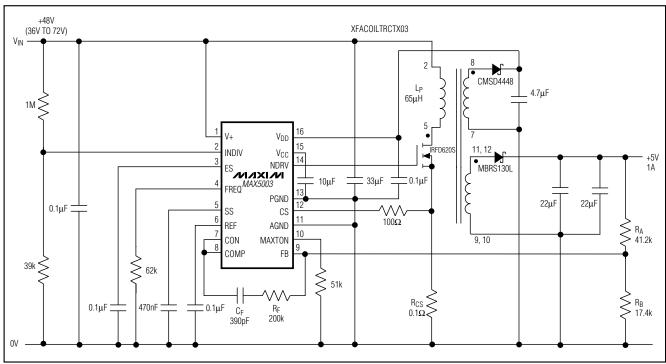

#### Design Example

- 1)  $36V < V_{IN} < 72V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 1A$ , ripple < 50mV, settling time  $\approx 0.5$ ms.

- 2) Generally, the higher the frequency, the smaller the transformer. A higher frequency also gives higher system bandwidth and faster settling time. The trade-off is lower efficiency. In this example, 300kHz switching frequency is the choice to favor for a small transformer. If the converter will be free running (not externally synchronized), use the following formula to calculate the Rereo programming resistor:

$$R_{FREQ} = \left(\frac{100 \text{kHz}}{f_{SW}}\right) 200 \text{k} = 66.7 \text{k}\Omega$$

where:

RFREQ = Resistor between FREQ and ground fsw = Switching frequency (300kHz)

If the converter is synchronized to an external clock, the input frequency will be 1.2MHz. The external clock runs at four times the desired switching frequency.

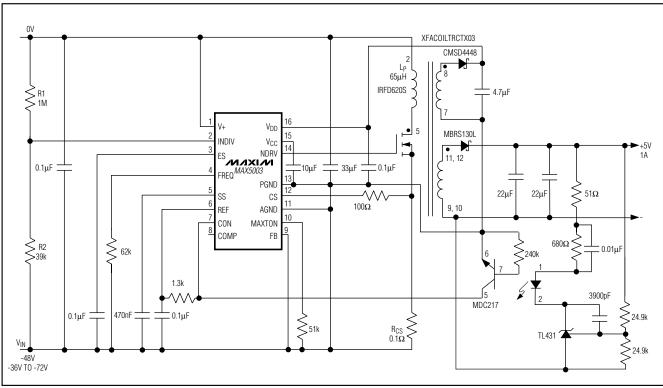

Figure 2. Application Example 1: Nonisolated +48V to +5V Converter

3) The main factors influencing the choice of the turns ratio are the switch breakdown voltage and the duty cycle. With a smaller turns ratio, the secondary reflected voltage and the maximum voltage seen by the switch during flyback are reduced, which is favorable. On the other hand, a smaller turns ratio will shorten the duty cycle and increase the primary RMS current, which can impact efficiency. A good starting figure is the ratio of the input voltage to the output voltage, rounding to the nearest integer. To keep the flyback voltage under control, choose an 8-to-1 ratio for the 48V to 5V system. The maximum duty cycle allowed without putting the device in continuous-conduction mode can be found using the following formula:

$$DC_{MAX} = \frac{1}{\left(\frac{V_{MIN}}{V_{SEC} \times N}\right) + 1}$$

where:

N = Np/Ns = Turns ratio

VSEC = Secondary voltage

DC<sub>MAX</sub> = Maximum duty cycle

V<sub>MIN</sub> = Minimum power-line voltage

For a 48V to 5V system with an 8-to-1 turns ratio, the maximum duty cycle before putting the device in discontinuous mode is 55%. Assume that  $V_{\rm IN}$  min is 36V (minimum input voltage, neglecting drops in the power switch and in the resistance of the primary coil) and VSEC is 5.4V (5V plus a Schottky diode drop). The MAX5003 maximum duty cycle is internally limited to 75%. Generally this parameter must fall between 45% to 65% to obtain a balance between efficiency and flyback voltage while staying out of continuous conduction. If the value exceeds these bounds, adjust the turns ratio.

4) Assuming 80% efficiency, a 6.25W input is needed to produce a 5W output. Set an operating duty cycle around 12% below the maximum duty cycle to allow for component variation: 55% - 12% = 43%. Use the following formula to calculate the primary inductance:

$$L_{PRI} = \frac{\left(DC \times V_{MIN}\right)^{2}}{2 \times PWR_{IN} \times f_{SW}} = \frac{\left(0.43 \times 36V\right)^{2}}{2 \times 6.25W \times 300kHz} \approx 65\mu H$$

Figure 3. Application Example 2: Isolated -48V to +5V Converter

where:

DC = Duty cycle. Set to calculated minimum duty cycle at V<sub>MIN</sub>.

$PWR_{IN}$  = Input power, at maximum output power This gives an inductance value (L<sub>PRI</sub>) of approximately 65 $\mu$ H.

5) The other parameter that defines the transformer is peak current. This is given by:

$$I_{PRI} = \sqrt{\frac{2 \times PWR_{IN}}{L_{PRI} \times f_{SW}}} = \sqrt{\frac{2 \times 6.25W}{65\mu H \times 300kHz}} = 0.8A$$

The peak secondary current is the peak primary current multiplied by the turns ratio, or  $0.8A \cdot 8 = 6.4A$ . Calculating the minimum duty cycle:

$$DC_{(MIN)} = DC_{(MAX)} \times \frac{V_{IN(MIN)}}{V_{IN(MAX)}} = 43\% \times \frac{36V}{72V} =$$

With these numbers, the transformer manufacturer can choose a core.

6) For this application, the MAX5003 must be programmed for a maximum duty cycle of 55% at 36V. The MAX5003 will automatically scale the limit with the reciprocal of the input voltage as it changes. The duty-cycle limit for an input voltage of 72V will be 27% (half of 55%). The duty cycle needed to stay out of continuous conduction at 72V is 37%, so there is a 10% margin. The maximum duty time scales with the voltage at the undervoltage lockout pin, VINDIV. The voltage at INDIV is set by selecting the power line undervoltage lockout trip point. The trip point for this system, running from 36V to 72V, is 32V. Then INDIV must be connected to the center point of a divider with a ratio of 32/1.25, connected between the power line and ground. Then RMAXTON is:

$$R_{MAXTON} = \left(\frac{V_{MIN}}{V_{UVL}}\right) \left(\frac{100kHz}{f_{SW}}\right) \left(\frac{DC_{MAX}(V_{MIN})}{75\%}\right) 200k\Omega$$

$$= \left(\frac{36V}{32V}\right) \left(\frac{100kHz}{300kHz}\right) \left(\frac{55\%}{75\%}\right) 200k\Omega = 55k\Omega$$

where:

RMAXTON = Resistor between the MAXTON pin and ground

V<sub>MIN</sub> = Minimum power-line voltage

VUVL = Power-line trip voltage

$DC_{MAX}(V_{MIN}) = Maximum duty cycle at minimum power-line voltage$

For this application circuit, a 10% margin is reasonable, so the value used is  $50k\Omega$ . This gives a maximum duty cycle of 50%. The maximum duty cycle can now be expressed as:

$$DC(V_{CON,VIN}) = \left(\frac{V_{CON} - 0.5V}{2.0V}\right) \left(\frac{V_{MIN}}{V_{IN}}\right) \left(\frac{f_{SW}}{f_{NOM}}\right) \times DC_{MAX(VMIN)}$$

$$\approx \left(\frac{V_{CON} - 0.5V}{2.0V}\right) \left(\frac{36V}{V_{IN}}\right) \left(\frac{f_{SW}}{f_{NOM}}\right) 50\%$$

where:

VCON = Voltage at the CON pin, input of the PWM comparator

$DC(V_{CON}, V_{IN}) = Duty cycle, function of V_{CON}$  and  $V_{IN}$

0.5V and 2.5V are the values at the beginning and end of the PWM ramp.

The term  $f_{\rm SW}$  /  $f_{\rm NOM}$  varies from 0.8 to 1.2 to allow for clock frequency variation. If the clock is running at 300kHz and the input voltage is fixed, then the duty cycle is a scaled portion of the maximum duty cycle, determined by  $V_{\rm CON}$ .

$$\begin{aligned} & DC(V_{CON}, V_{MIN}) = \left(\frac{V_{CON} - 0.5V}{2.0V}\right) 50\% \\ & DC(V_{CON}, V_{MAX}) = \left(\frac{V_{CON} - 0.5V}{2.0V}\right) 25\% \\ & DC(2.5V, V_{MIN}) = 50\% \\ & DC(2.5V, V_{MAX}) = 25\% \\ & DC(0.5V, V_{MIN}) = 0 \end{aligned}$$

7) Low-ESR/ESL ceramic capacitors were used in this application. The output filter is made by two 22µF ceramic capacitors in parallel. Normally, the ESR of a capacitor is a dominant factor determining the ripple, but in this case it is the capacitor value.

$DC(0.5V, V_{MAX}) = 0$

Calculating

$$\frac{I_{OUT}}{f_{SW} \times C} = \frac{1A}{300 \text{kHz} \times 44 \mu \text{F}} = 76 \text{mV}$$

the ripple will be a fraction of this depending on the duty cycle. For a 50% duty cycle, the ripple due to the capacitance is approximately 45mV.

8) The PWM gain can be calculated from:

$$\begin{split} \mathsf{A}_{\mathsf{PWM}} = \ \frac{\mathsf{dV}_{\mathsf{OUT}}}{\mathsf{dV}_{\mathsf{CON}}} &= \sqrt{\frac{\mathsf{R}_{\mathsf{L}}}{2 \times \mathsf{L}_{\mathsf{PRI}} \times f_{\mathsf{SW}}}} \bigg( \frac{\mathsf{V}_{\mathsf{MIN}}}{2.0\mathsf{V}} \bigg) \ \mathsf{DC}_{\mathsf{MAX}(\mathsf{VMI})} \\ &= \sqrt{\frac{\mathsf{R}_{\mathsf{L}}}{2 \times \mathsf{L}_{\mathsf{PRI}} \times f_{\mathsf{SW}}}} \bigg( \frac{36\mathsf{V}}{2.0\mathsf{V}} \bigg) \ \mathsf{50\%} \ \cong 3 \end{split}$$

Note that while the above formula incorporates the product of the maximum duty cycle and  $V_{IN}$ , it is independent of  $V_{IN}$ . For 1A output ( $R_L = 5\Omega$ ), the PWM gain is +3.0V/V. For a 10% load ( $R_L = 50\Omega$ ), the gain is multiplied by the square root of 10 and becomes +10V/V. The pole of the system due to the output filter is 1 /  $2\pi RC$ , where R is the load resistance and C the filter capacitor. Choosing a capacitor and calculating the pole frequency by:

$$f_{P} = \left(\frac{1}{2\pi \times R_{L} \times C_{L}}\right) = \left(\frac{1}{2\pi \times 5\Omega \times 44\mu F}\right)$$

it is 723Hz at full load. At 10% load it will be 72Hz, since the load resistor is then  $50\Omega$  instead of  $5\Omega$ . The total loop gain is equal to the PWM gain times the gain in the combination of the voltage divider and the error amplifier. The worst case for phase margin is at full load. For a phase margin of 60 degrees, this midband gain (G) must be set to be less than:

$$G < \sqrt{\frac{f_{UErrorAmp}}{tan(PM) \times A_{PWM} \times f_{P}}} = \sqrt{\frac{1 \text{ MHz}}{1.7 \times 3 \times 723 \text{Hz}}}$$

where:

$f_{IJ}$  = Unity-gain frequency of error amplifier

PM = Phase margin angle

The DC accuracy of the regulator is a function of the DC gain. For 1% accuracy, a DC gain of 20 is required. Since the maximum midband gain for a stable response is 16, an integrator with a flat midband gain given by a zero is used. The midband gain is less than 16, to preserve stability, and the DC gain is much larger than 20, to achieve high DC accuracy.

Optimization on the bench showed that a midband gain of 5 gave fast transient response and settling with no ringing. The zero was pushed as high in frequency as possible without losing stability. The zero must be a factor of two or so below the system unity-gain frequency (crossover frequency) at minimum load. With the

zero at 2kHz, the crossover frequency is 4kHz and the phase margin is 50°.

Given the above considerations, RA, RB, RF, and CF can be chosen (Figure 2). The sum of RA and RB is chosen for low current drain. In the example, RA plus RB is  $58k\Omega$  and draws  $80\mu\text{A}$ . The following ratio sets the output voltage:

$$R_B / (R_A + R_B) = V_{SET} / V_{OUT}$$

Since  $V_{SET} = 1.5V$  and  $V_{OUT} = 5V$ ,  $R_A$  is set to  $41.2k\Omega$  and  $R_B$  to  $17.4k\Omega$ .

The midband gain is the ratio of RF/RA. RB does not affect the gain because it is connected to a virtual ground. For a midband gain of 5, the feedback resistor equals  $200k\Omega$ . To set the zero at 2kHz, the capacitor value is:

$$C_F = 1 / (2\pi \times R_F \times f_Z) = 400pF$$

### **Layout Recommendations**

All connections carrying pulsed currents must be very short, be as wide as possible, and have a ground plane behind them whenever possible. The inductance of these connections must be kept to an absolute minimum due to the high di/dt of the currents in high-frequency switching power converters. In the development or prototyping process, multipurpose boards, wire wrap, and similar constructive practices are not suitable for these type of circuits; attempts to use them will fail. Instead, use milled PC boards with a ground plane, or equivalent techniques

Current loops must be analyzed in any layout proposed, and the internal area kept to a minimum to reduce radiated EMI. The use of automatic routers is discouraged for PC board layout generation in the board area where the high-frequency switching converters are located. Designers should carefully review the layout. In particular, pay attention to the ground connections. Ground planes must be kept as intact as possible. The ground for the power-line filter capacitor and the ground return of the power switch or current-sensing resistor must be close. All ground connections must resemble a star system as much as practical.

"Short" and "close" are dimensions on the order of 0.25in to 0.5in (0.5cm to about 1cm).

#### **Setting the Output Voltage**

The output voltage of the converter, if using the internal error amplifier, can easily be set by the value of the FB pin set voltage. This value is 1.5V. A resistive divider must be calculated from the output line to ground, with a dividing ratio such that when the output is at the

desired value, the center-point voltage will be 1.5V. The Thevenin equivalent of the resistors must be low enough so the error amplifier bias current will not introduce a division error. The two resistors must have similar temperature coefficients (tempcos), so the dividing ratio will be constant with temperature.

## Component Selection CS Resistor

The CS resistor is connected in series with the source of the N-channel MOSFET and ground, sensing the switch current. Its value can be calculated from the following equation:

$$R_{CS} = \frac{100\text{mV}}{I_{LIM(PRI)}} = \frac{100\text{mV}}{\sqrt{\frac{2 \text{ PWR}_{OUT(MAX)}}{L_{PRI} \times f_{SW} \times \eta}}} \times K_{TOL}$$

where  $\eta$  = efficiency and 0.5 < KT<sub>OL</sub> < 0.75.

K<sub>TOL</sub> includes the tolerance of the sensing resistor, the dispersion of the MAX5003 CS trip point, and the uncertainties in the calculation of the primary maximum current.

The sensing resistor must be of the adequate power dissipation and low tempco. It must also be noninductive and physically short. Use standard surface-mount CS resistors. A  $100\Omega$  resistor is recommended between the CS resistor and the CS pin. If the current surge at the beginning of the conduction period is large and disrupts the MAX5003's operation, add a capacitor between the CS pin and PGND, to form an RC filter.

#### **Power Switch**

The MAX5003 will typically drive an N-channel MOSFET power switch. The maximum drain voltage, maximum RDS(ON), and total gate switching charge are the parameters involved in choosing the FET. The maximum gate switching charge is the most important factor defining the MAX5003 internal power consumption, since the product of the switching frequency and the total gate charge is the IC current consumption. RDS(ON) is the parameter that determines the total conduction power losses in the switch, and the choice depends on the expected efficiency and the cooling and mounting method. The maximum drain voltage requirements can be different depending on the topology used. In the flyback configuration, the maximum voltage is the maximum supply voltage plus the reflected secondary voltage, any ringing at the end of the conduction period, and the spike caused by the leakage inductance. In the case of the forward converter, the reset time of the core will set the maximum voltage

stress on the switch. A FET with the lowest total charge and the lowest  $R_{DS(ON)}$  for the maximum drain voltage expected (plus some safety factor) is the best choice. The choice of package is a function of the application, the total power, and the cooling methods available.

#### Transformer

Transformer parameters, once calculated in the design process, can be used to find standard parts whenever possible. The most important factors are the saturation current, primary inductance, leakage inductance turns ratio, and losses. Packaging and EMI generation and susceptibility are closely connected, and must be considered. In general, parts with exposed air gaps (not contained inside the magnetic structure) will generate the most radiated EMI, and might need external shielding. If the design is in high-voltage power supplies, the insulation specifications are also important. Pay close attention if the circuitry is galvanically connected to the mains at any point, since serious safety and regulatory issues might exist.

#### Capacitors

As in any high-frequency power circuit, the capacitors used for filtering must meet very low ESR and ESL requirements. At the 300kHz frequency (of which the MAX5003 is capable), the most favorable technologies are ceramic capacitors and organic semiconductor (OS CON) capacitors. The temperature dependence of the capacitance value and the ESR specification is important, particularly if the ESR is used as part of the compensation network for the feedback loop. If using through-hole-

mounted parts, keep lead length as short as practical. Components with specifications for switching power converters are preferred. Decoupling capacitors must be mounted close to the IC.

#### Diodes

The choice of rectifier diodes depends on the output voltage range of the particular application. For low-voltage converters, the diode drop is a significant portion of the total loss, and must be kept to a minimum. In those cases, Schottky diodes are the preferred component for the design. At higher voltages, ultra-fast recovery diodes must be used, since Schottky components will not satisfy the reverse voltage specification.

For all cases, the specifications to be determined before choosing a diode are the peak current, the average current, the maximum reverse voltage, and the maximum acceptable rectification losses. Once a type is identified, a thermal analysis of the diode losses vs. total thermal resistance (from junction to ambient) must be carried out if the total power involved is significant.

Industrial-frequency (60Hz) rectifiers are not recommended for any function in these converters, due to their high capacitance and recovery losses. If using overdimensioned rectifiers, the junction capacitance influence must be reviewed.

### \_Chip Information

TRANSISTOR COUNT: 1050 SUBSTRATE CONNECTED TO GND

**Table 1. Component Manufacturers**

| DEVICE TYPE             | MANUFACTURER            | PHONE        | FAX          |

|-------------------------|-------------------------|--------------|--------------|

| Power FETs              | International Rectifier | 310-322-3333 | 310-322-3332 |

| Power PETS              | Fairchild               | 408-822-2000 | 408-822-2102 |

| Current-Sense Resistors | Dale-Vishay             | 402-564-3131 | 402-563-6418 |

| Diodes                  | Motorola                | 303-675-2140 | 303-675-2150 |

|                         | Central Semiconductor   | 516-435-1110 | 516-435-1824 |

| Transistors             | Central Semiconductor   | 516-435-1110 | 516-435-1824 |

|                         | Sanyo                   | 619-661-6835 | 619-661-1055 |

| Capacitors              | Taiyo Yuden             | 408-573-4150 | 408-573-4159 |

|                         | AVX                     | 803-946-0690 | 803-626-3123 |

| Coils                   | Coiltronics             | 561-241-7876 | 561-241-9339 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

16 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

AZ7500EP-E1 NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81205MNTXG

SJE6600 SMBV1061LT1G SG3845DM NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG NCP81203MNTXG

NCP81206MNTXG NX2155HCUPTR UBA2051C MAX8778ETJ+ NTBV30N20T4G NCP1240AD065R2G NCP1240FD065R2G

NCP1361BABAYSNT1G NTC6600NF TC105333ECTTR NCP1230P100G NCP1612BDR2G NX2124CSTR SG2845M

NCP81101MNTXG IFX81481ELV NCP81174NMNTXG NCP4308DMTTWG NCP4308DMNTWG NCP4308AMTTWG

NCP1251FSN65T1G NCP1246BLD065R2G NTE7154 NTE7242 LTC7852IUFD-1#PBF LTC7852EUFD-1#PBF MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G MCP1633T-E/MG NCV1397ADR2G

AZ494AP-E1 UTC3843D XDPL8219XUMA1