## **General Description**

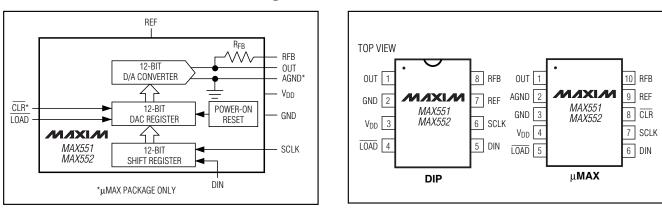

The MAX551/MAX552 are 12-bit, current-output, 4-quadrant multiplying digital-to-analog converters (DACs). These devices are capable of providing unipolar or bipolar outputs when operating from either a single +5V (MAX551) or +3V (MAX552) power supply. An internal power-on-reset circuit clears all DAC registers on power-up, setting the DAC output voltage to 0V.

The SPI™/QSPI™ and MICROWIRE™-compatible 3wire serial interface saves board space and reduces power dissipation compared with parallel-interface devices. The MAX551/MAX552 feature double-buffered interface logic with a 12-bit input register and a 12-bit DAC register. Data in the DAC register sets the DAC output voltage. Data is loaded into the input register through the serial interface. The LOAD input transfers data from the input register to the DAC register, updating the DAC output voltage.

The MAX551/MAX552 are available in an 8-pin DIP package or a space-saving 10-pin µMAX package. The µMAX package provides an asynchronous clear (CLR) input that clears all DAC registers when pulled to GND, setting the output voltage to OV.

## **Applications**

Automatic Calibration Gain Adjustment **Transducer Drivers** Process-Control I/O Boards **Digitally Controlled Filters** Motion-Controlled Systems µP-Controlled Systems Programmable Amplifiers/Attenuators

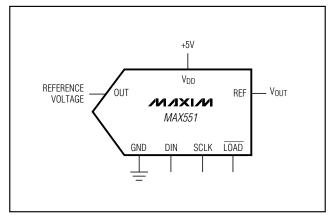

## **Functional Diagram**

SPI and QSPI are trademarks of Motorola Inc. MICROWIRE is a trademark of National Semiconductor Corp.

## M/XI/M

Maxim Integrated Products 1

**Ordering Information**

Single-Supply Operation: +4.5V to +5.25V (MAX551) +2.7V to +3.6V (MAX552)

- 12.5MHz 3-Wire Serial Interface

- SPI/QSPI and MICROWIRE Compatible

- Power-On Reset Clears DAC Output to Zero

- Asynchronous Clear Input Clears DAC Output to Zero

- Voltage Mode or Bipolar Mode Operation with a Single Power Supply

- Schmitt-Trigger Digital Inputs for Direct **Optocoupler Interface**

- 0.4µA Supply Current

- 10-Pin µMAX Package

| PART            | TEMP RANGE         | PIN-<br>PACKAGE | LINEARITY<br>(LSB) |

|-----------------|--------------------|-----------------|--------------------|

| MAX551ACPA      | 0°C to +70°C       | 8 Plastic DIP   | ±1/2               |

| MAX551BCPA      | 0°C to +70°C       | 8 Plastic DIP   | ±1                 |

| MAX551ACUB      | 0°C to +70°C       | 10 µMAX         | ±1/2               |

| MAX551BCUB      | 0°C to +70°C       | 10 µMAX         | ±1                 |

| MAX551AEPA      | -40°C to +85°C     | 8 Plastic DIP   | ±1/2               |

| MAX551BEPA      | -40°C to +85°C     | 8 Plastic DIP   | ±1                 |

| MAX551AEUB      | -40°C to +85°C     | 10 µMAX         | ±1/2               |

| MAX551BEUB      | -40°C to +85°C     | 10 µMAX         | ±1                 |

| Ordoning Inform | ation continued at | and of data ab  | a a t              |

Ordering Information continued at end of data sheet.

## **Pin Configurations**

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

Features

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND                                |  |

|-------------------------------------------------------|--|

| DIGITAL INPUTS (SOLK, DIN, LOAD, OLR)                 |  |

| to GND0.3V to 6V                                      |  |

| OUT to GND0.3V to (V <sub>DD</sub> + 0.3V)            |  |

| AGND to DGND±0.3V                                     |  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |  |

| Plastic DIP (derate 9.09mW/°C above +70°C)727mW       |  |

| µMAX (derate 5.60mW/°C above +70°C)444mW              |  |

**Operating Temperature Ranges**

| MAX55C                            | 0°C to +70°C   |

|-----------------------------------|----------------|

| MAX55E                            | 40°C to +85°C  |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS—MAX551**

(V<sub>DD</sub> = +4.5V to +5.25V, V<sub>REF</sub> = 5V, OUT = AGND = GND, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                    | SYMBOL  | CONDITIONS                                                                |                                                                                                                         | MIN | ТҮР  | MAX               | UNITS  |

|------------------------------|---------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|------|-------------------|--------|

| STATIC PERFORMANCE           | I       |                                                                           |                                                                                                                         |     |      |                   | I      |

| Resolution                   | N       |                                                                           |                                                                                                                         | 12  |      |                   | Bits   |

| Integral Nonlinearity        | INL     |                                                                           | MAX551A                                                                                                                 |     |      | ±1/2              | LSB    |

| integral Nonlineanty         |         |                                                                           | MAX551B                                                                                                                 |     |      | ±1                | LSD    |

| Differential Nonlinearity    | DNL     | Guaranteed monotonic over                                                 | MAX551A                                                                                                                 |     |      | ±1/2              | LSB    |

| Differential Norhinearity    | DINL    | temperature                                                               | MAX551B                                                                                                                 |     |      | ±1                |        |

| Gain Error                   |         | Using internal feedback                                                   | MAX551A                                                                                                                 |     |      | ±1                | LSB    |

| Gain Litor                   |         | resistor (R <sub>FB</sub> )                                               | MAX551B                                                                                                                 |     |      | ±2                | LOD    |

| Gain Tempco<br>(ΔGain/ΔTemp) |         | Using internal feedback resis<br>(Note 2)                                 | tor (R <sub>FB</sub> )                                                                                                  |     | ±0.2 | ±1                | ppm/°C |

| Power-Supply Rejection       | PSR     | ΔV <sub>DD</sub> = +5%, -10%                                              |                                                                                                                         |     |      | 2                 | ppm/%  |

|                              | Note 3) |                                                                           |                                                                                                                         |     |      |                   | 1      |

| Current Settling Time        | ts      |                                                                           | $T_A = +25^{\circ}C$ , to 1/2LSB, OUT load is<br>100 $\Omega$ II13pF, DAC register alternately loaded<br>with 1s and 0s |     |      | 1                 | μs     |

| Digital-to-Analog Glitch     |         | V <sub>REF</sub> = 0V, OUT load is 100Ω<br>register alternately loaded wi |                                                                                                                         |     | 0.65 | 20                | nV-s   |

| AC Feedthrough at OUT        |         | V <sub>REF</sub> = 5V <sub>P-P</sub> at 10kHz, DAC<br>with all 0s         |                                                                                                                         | 0.3 | 1    | mV <sub>P-P</sub> |        |

| Total Harmonic Distortion    | THD     | V <sub>REF</sub> = 6V <sub>RMS</sub> at 1kHz, DAC<br>with all 1s          |                                                                                                                         | -85 |      | dB                |        |

| Output Noise-Voltage Density |         | 10Hz to 100kHz, measured b<br>OUT                                         | etween RFB and                                                                                                          |     | 13   | 15                | nV/√Hz |

## ELECTRICAL CHARACTERISTICS—MAX551 (continued)

(V<sub>DD</sub> = +4.5V to +5.25V, V<sub>REF</sub> = 5V, OUT = AGND = GND, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                | SYMBOL           | CONDITIONS                                                                                                |                                  | MIN  | TYP   | MAX  | UNITS  |  |

|--------------------------|------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|------|-------|------|--------|--|

| REFERENCE INPUT          | I                |                                                                                                           |                                  |      |       |      | 1      |  |

| Input Resistance         | R <sub>REF</sub> | Measured between REF and OUT                                                                              |                                  | 7    | 11    | 15   | kΩ     |  |

| Input Resistance Tempco  |                  |                                                                                                           |                                  |      | 6.5   |      | ppm/°C |  |

| Reference -3dB Bandwidth | BW               | $V_{OUT} = 0.31 V_{P-P}, R_L =$                                                                           | 50 $\Omega$ , code = full-scale  |      | 725   |      | kHz    |  |

| ANALOG OUTPUT            |                  |                                                                                                           |                                  |      |       |      |        |  |

| OUT Leakage Current      |                  | DAC register loaded                                                                                       | $T_A = +25^{\circ}C$             |      | ±0.15 | ±5   | - nA   |  |

| OUT Leakage Guitent      |                  | with all 0s                                                                                               | $T_A = T_{MIN}$ to $T_{MAX}$     |      |       | ±25  |        |  |

| OUT Capacitance          | Court            | Code = zero scale (Not                                                                                    | e 2)                             |      | 14    | 20   |        |  |

| OUT Capacitance          | Cout             | Code = full scale (Note                                                                                   | 2)                               |      | 20    | 30   | - pF   |  |

| DIGITAL INPUTS           |                  |                                                                                                           |                                  |      |       |      |        |  |

| Input High Voltage       | VIH              |                                                                                                           |                                  | 2.4  |       |      | V      |  |

| Input Low Voltage        | VIL              |                                                                                                           |                                  |      |       | 0.8  | V      |  |

| Input Hysteresis         | HYST             | LOAD, CLR, DIN, and S                                                                                     | SCLK, V <sub>DD</sub> = 5V       |      | 156   |      | mV     |  |

| Input Leakage Current    |                  |                                                                                                           | $V_{\overline{CLR}} = V_{DD}$    |      |       | ±1   |        |  |

|                          | l <sub>IN</sub>  | CLR                                                                                                       | $V_{\overline{\text{CLR}}} = 0V$ |      | 18    | 100  | μA     |  |

|                          |                  | SCLK, LOAD, DIN                                                                                           | Inputs at 0V or V <sub>DD</sub>  |      |       | ±1   | -      |  |

| Input Capacitance        | CIN              | Inputs at 0V or V <sub>DD</sub> (No                                                                       | te 2)                            |      |       | 8    | pF     |  |

| SWITCHING CHARACTERIS    | TICS             |                                                                                                           | I                                |      |       |      | 4      |  |

| SCLK Pulse Width High    | tсн              |                                                                                                           |                                  | 25   |       |      | ns     |  |

| SCLK Pulse Width Low     | tCL              |                                                                                                           |                                  | 25   |       |      | ns     |  |

| DIN Data to SCLK Setup   | t <sub>DS</sub>  |                                                                                                           |                                  | 15   |       |      | ns     |  |

| DIN Data to SCLK Hold    | tDH              |                                                                                                           |                                  | 15   |       |      | ns     |  |

| LOAD Pulse Width         | tLD              |                                                                                                           |                                  | 20   |       |      | ns     |  |

| LSB SCLK to LOAD         | tsl              |                                                                                                           |                                  | 0    |       |      | ns     |  |

| LOAD High to SCLK        | tLC              |                                                                                                           |                                  | 15   |       |      | ns     |  |

| CLR Pulse Width          | tCLR             |                                                                                                           |                                  | 20   |       |      | ns     |  |

| POWER SUPPLY             | 1                | 1                                                                                                         |                                  |      |       |      | 1      |  |

| Supply Voltage           | V <sub>DD</sub>  |                                                                                                           |                                  | 4.50 |       | 5.25 | V      |  |

|                          |                  | All digital inputs at V <sub>IL</sub> or V <sub>IH</sub> , $\overline{\text{CLR}} = \text{V}_{\text{DD}}$ |                                  |      | 0.5   | 1.5  | mA     |  |

| Supply Current           | IDD              | All digital inputs at 0V or $V_{DD}$ , $\overline{CLR} = V_{DD}$                                          |                                  |      | 0.4   | 5    | μA     |  |

## **ELECTRICAL CHARACTERISTICS—MAX552**

(V<sub>DD</sub> = +2.7V to +3.6V, V<sub>REF</sub> = 2.5V, OUT = AGND = GND,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 1)

| PARAMETER                    | SYMBOL           | CONDI                                                                              | TIONS                                                                                                                   | 6                                    | MIN | TYP   | MAX  | UNITS             |

|------------------------------|------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|-------|------|-------------------|

| STATIC PERFORMANCE           | 1                |                                                                                    |                                                                                                                         | L.                                   |     |       |      |                   |

| Resolution                   | N                |                                                                                    |                                                                                                                         |                                      | 12  |       |      | Bits              |

| Integral Nonlinearity        | INL              | MAX552A                                                                            |                                                                                                                         | MAX552A                              |     |       | ±1/2 |                   |

| Integral Normineanty         | IINL             |                                                                                    |                                                                                                                         | MAX552B                              |     |       | ±1   | - LSB             |

| Differential Nonlinearity    | DNL              | Guaranteed monotonic                                                               | over                                                                                                                    | MAX552A                              |     |       | ±1/2 | LSB               |

| Binerential Noninicarity     | DINE             | temperature                                                                        | mperature MAX552B                                                                                                       |                                      |     |       | ±1   | LOD               |

| Gain Error                   |                  | Using internal feedbac                                                             | k                                                                                                                       | MAX552A                              |     |       | ±1   | LSB               |

|                              |                  | resistor (R <sub>FB</sub> )                                                        |                                                                                                                         | MAX552B                              |     |       | ±2   | LOD               |

| Gain Tempco<br>(ΔGain/ΔTemp) |                  | Using internal feedback<br>(Note 2)                                                | k resis                                                                                                                 | tor (R <sub>FB</sub> )               |     | ±0.3  | ±1   | ppm/°C            |

| Power-Supply Rejection       | PSR              | $\Delta V_{DD} = +20\%, -10\%$                                                     |                                                                                                                         |                                      |     |       | 1    | ppm/%             |

| DYNAMIC PERFORMANCE (N       | ote 3)           |                                                                                    |                                                                                                                         |                                      |     |       |      | 1                 |

| Current Settling Time        | ts               |                                                                                    | $T_A = +25^{\circ}C$ , to 1/2LSB, OUT load is<br>100 $\Omega$ II13pF, DAC register alternately loaded<br>with 1s and 0s |                                      |     | 0.12  | 1    | μs                |

| Digital-to-Analog Glitch     |                  |                                                                                    | $V_{REF} = 0V$ , OUT load is 100 $\Omega$ II13pF, DAC register alternately loaded with 1s and 0s                        |                                      |     | 0.6   | 20   | nV-s              |

| AC Feedthrough at OUT        |                  | $V_{REF} = 3V_{P-P}$ at 10kHz, with all 0s                                         | $V_{REF} = 3V_{P-P}$ at 10kHz, DAC register loaded with all 0s                                                          |                                      |     | 0.2   | 0.6  | mV <sub>P-P</sub> |

| Total Harmonic Distortion    | THD              | $V_{REF} = 6V_{RMS}$ at 1kHz, with all 1s                                          | $V_{REF} = 6V_{RMS}$ at 1kHz, DAC register loaded with all 1s                                                           |                                      |     | -85   |      | dB                |

| Output Noise-Voltage Density |                  | 10Hz to 100kHz, measu<br>OUT                                                       | ured b                                                                                                                  | etween RFB and                       |     | 13    | 15   | nV/√Hz            |

| REFERENCE INPUT              |                  |                                                                                    |                                                                                                                         |                                      |     |       |      | 1                 |

| Input Resistance             | R <sub>REF</sub> | Measured between RE                                                                | F and                                                                                                                   | OUT                                  | 7   | 11    | 15   | kΩ                |

| Input Resistance Tempco      |                  |                                                                                    |                                                                                                                         |                                      |     | 7.5   |      | ppm/°C            |

| Reference -3dB Bandwidth     | BW               | $V_{OUT} = 0.31 V_{P\text{-}P}, R_L = 50 \Omega, \text{ code} = \text{full-scale}$ |                                                                                                                         |                                      | 725 |       | kHz  |                   |

| ANALOG OUTPUT                |                  |                                                                                    |                                                                                                                         |                                      |     |       |      |                   |

| OUT Leakage Current          |                  | DAC register loaded                                                                | T <sub>A</sub> =                                                                                                        | +25°C                                |     | ±0.13 | ±5   | nA                |

| 0                            |                  | with all 0s                                                                        | T <sub>A</sub> =                                                                                                        | $T_{\mbox{MIN}}$ to $T_{\mbox{MAX}}$ |     |       | ±25  |                   |

|                              | 0.5.1.5          | Code = zero code (Not                                                              | te 2)                                                                                                                   |                                      |     | 14    | 20   |                   |

| OUT Capacitance              | COUT             | Code = full scale (Note 2)                                                         |                                                                                                                         |                                      | 20  | 30    | pF   |                   |

M/X/M

## ELECTRICAL CHARACTERISTICS—MAX552 (continued)

(V<sub>DD</sub> = +2.7V to +3.6V, V<sub>REF</sub> = 2.5V, VOUT = AGND = GND, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER              | SYMBOL          | CONDITIONS                                                             |                                  | MIN | TYP  | MAX | UNITS |

|------------------------|-----------------|------------------------------------------------------------------------|----------------------------------|-----|------|-----|-------|

| DIGITAL INPUTS         |                 |                                                                        |                                  |     |      |     | 1     |

| Input High Voltage     | VIH             |                                                                        |                                  | 2.1 |      |     | V     |

| Input Low Voltage      | VIL             |                                                                        |                                  |     |      | 0.6 | V     |

| Input Hysteresis       | HYST            | LOAD, CLR, DIN, and                                                    | SCLK, V <sub>DD</sub> = 3V       |     | 135  |     | mV    |

|                        |                 | CLR                                                                    | $V_{\overline{CLR}} = V_{DD}$    |     |      | ±1  |       |

| Input Leakage Current  | lin             | CLR                                                                    | $V_{\overline{\text{CLR}}} = 0V$ |     | 12   | 75  | μA    |

|                        |                 | SCLK, LOAD, DIN                                                        | Inputs at 0V or $V_{DD}$         |     |      | ±1  |       |

| Input Capacitance      | CIN             | Inputs at 0V or V <sub>DD</sub> (N                                     | ote 2)                           |     |      | 8   | pF    |

| SWITCHING CHARACTERIS  | STICS           |                                                                        |                                  |     |      |     |       |

| SCLK Pulse Width High  | tсн             |                                                                        |                                  | 40  |      |     | ns    |

| SCLK Pulse Width Low   | t <sub>CL</sub> |                                                                        |                                  | 40  |      |     | ns    |

| DIN Data to SCLK Setup | tDS             |                                                                        |                                  | 15  |      |     | ns    |

| DIN Data to SCLK Hold  | t <sub>DH</sub> |                                                                        |                                  | 15  |      |     | ns    |

| LOAD Pulse Width       | tLD             |                                                                        |                                  | 30  |      |     | ns    |

| LSB SCLK to LOAD       | t <sub>SL</sub> |                                                                        |                                  | 0   |      |     | ns    |

| LOAD High to SCLK      | tLC             |                                                                        |                                  | 15  |      |     | ns    |

| CLR Pulse Width        | tCLR            |                                                                        |                                  | 30  |      |     | ns    |

| POWER SUPPLY           |                 |                                                                        |                                  |     |      |     |       |

| Supply Voltage         | V <sub>DD</sub> |                                                                        |                                  | 2.7 |      | 3.6 | V     |

| Supply Current         |                 | All digital inputs at $V_{IL}$ or $V_{IH}$ , $\overline{CLR} = V_{DD}$ |                                  |     | 0.1  | 0.5 | mA    |

| Supply Current         | IDD             | All digital inputs at 0V or $V_{DD}$ , $\overline{CLR} = V_{DD}$       |                                  |     | 0.07 | 5   | μA    |

**Note 1:** AGND and  $\overline{\text{CLR}}$  are for  $\mu$ MAX only.

Note 2: Guaranteed by design. Not subject to production testing.

**Note 3:** Parametric limits are provided for design guidance, and are not production tested.

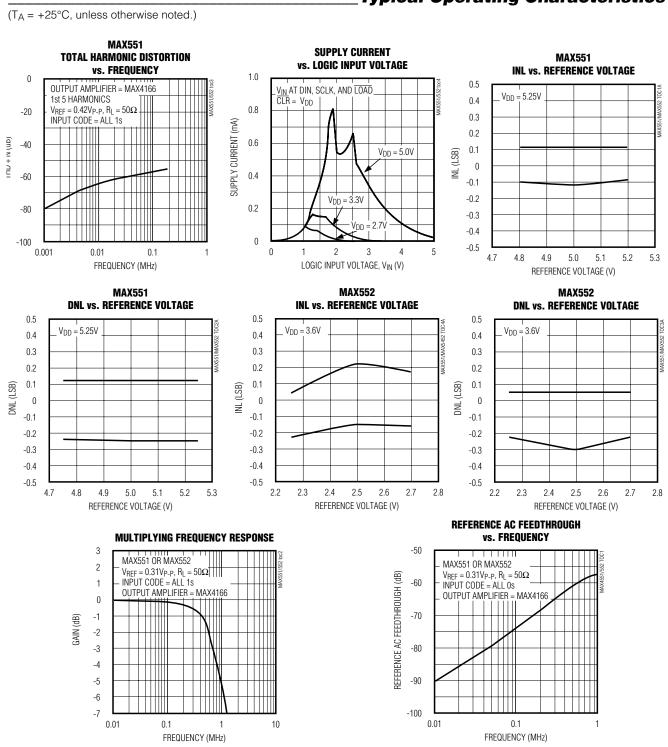

**Typical Operating Characteristics**

M/IXI/N

MAX551/MAX552

## \_Pin Description

**MAX551/MAX552**

| F   | PIN  | NAME            | FUNCTION                                                                                                                         |

|-----|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|

| DIP | μΜΑΧ |                 | FUNCTION                                                                                                                         |

| 1   | 1    | OUT             | DAC Current Output                                                                                                               |

| _   | 2    | AGND            | Analog Ground                                                                                                                    |

| 2   | 3    | GND             | Digital Ground. Also Analog Ground for DIP package.                                                                              |

| 3   | 4    | V <sub>DD</sub> | Supply Voltage                                                                                                                   |

| 4   | 5    | LOAD            | Active-Low Load DAC Input. Driving this asynchronous input low transfers the contents of the input register to the DAC register. |

| 5   | 6    | DIN             | Serial-Data Input                                                                                                                |

| 6   | 7    | SCLK            | Serial-Clock Input. The serial input data is clocked in on SCLK's rising edge.                                                   |

|     | 8    | CLR             | Clear DAC Input. Clears the DAC register. Tie to V <sub>DD</sub> or float if not used.                                           |

| 7   | 9    | REF             | Reference Input                                                                                                                  |

| 8   | 10   | RFB             | Feedback Resistor                                                                                                                |

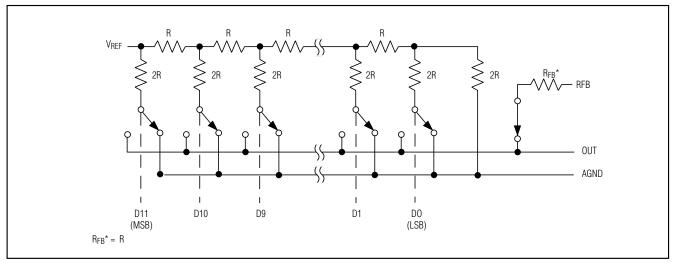

Figure 1. MAX551/MAX552 Simplified Circuit

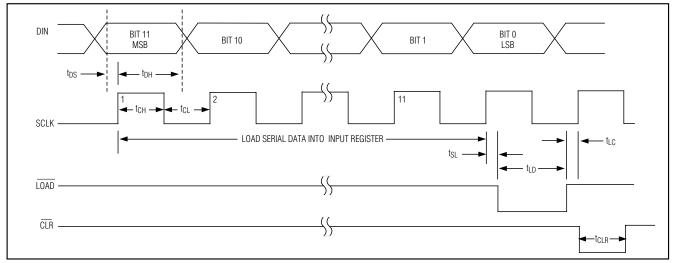

Figure 2. Write-Cycle Timing Diagram

## **Detailed Description**

The MAX551/MAX552 digital-to-analog converter (DAC) circuits consist of a laser-trimmed, thin-film R-2R resistor array with NMOS current switches (Figure 1). Binary-weighted currents are switched to either OUT or AGND, depending on the status of each input data bit. Although the currents at OUT and AGND depend on the digital input code, the sum of the two output currents is always equal to the input current at REF.

The output current (I<sub>OUT</sub>) can be converted into a voltage by adding an external output amplifier (Figure 3). The REF input accepts a wide range of signals, including fixed and time-varying voltage or current inputs. If a current source is used at the reference input, use a low-tempco, external feedback resistor in place of the

Table 1. Unipolar Binary-Code Tablefor Circuit of Figure 3

| DI<br>MSB | GITAL INF | VUT<br>LSB | ANALOG OUTPUT                                                               |

|-----------|-----------|------------|-----------------------------------------------------------------------------|

| 1111      | 1111      | 1111       | $-V_{REF}\left(\frac{4095}{4096}\right)$                                    |

| 1000      | 0000      | 0000       | $-V_{\text{REF}}\left(\frac{2048}{4096}\right) = -\frac{V_{\text{REF}}}{2}$ |

| 0000      | 0000      | 0001       | $-V_{\text{REF}}\left(\frac{1}{4096}\right)$                                |

| 0000      | 0000      | 0000       | 0                                                                           |

internal feedback resistor (RFB) to minimize gain variation with temperature.

The internal feedback resistor (RFB) is compensated with an NMOS switch that matches the NMOS switches used in the R-2R array, resulting in excellent supply rejection and gain-temperature coefficient.

The OUT pin output capacitance ( $C_{OUT}$ ) is code dependent. C<sub>OUT</sub> is typically 14pF at 000hex and 20pF at FFFhex.

## **Serial Interface**

The MAX551/MAX552 serial interface is compatible with the SPI/QSPI and MICROWIRE serial-interface standards. These devices accept serial clocks up to 12.5MHz (50% duty cycle). If the SCLK input is not

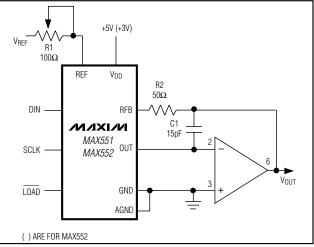

Figure 3. Unipolar Operation

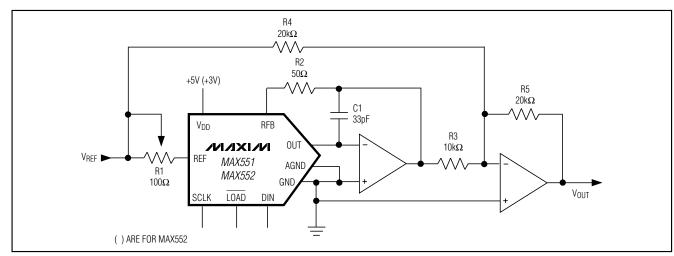

Figure 4. Bipolar Operation

# Table 2. Offset Binary-Code Tablefor Circuit of Figure 4

| DI<br>MSB | GITAL INF | PUT<br>LSB | ANALOG OUTPUT                                   |

|-----------|-----------|------------|-------------------------------------------------|

| 1111      | 1111      | 1111       | $+V_{\text{REF}}\left(\frac{2047}{2048}\right)$ |

| 1000      | 0000      | 0001       | $+V_{\text{REF}}\left(\frac{1}{2048}\right)$    |

| 1000      | 0000      | 0000       | 0                                               |

| 0111      | 1111      | 1111       | $-V_{REF}\left(\frac{1}{2048}\right)$           |

| 0000      | 0000      | 0000       | $-V_{REF}\left(\frac{2048}{2048}\right)$        |

symmetrical, then the clock signal used must meet the  $t_{CH}$  and  $t_{CL}$  requirements given in the *Electrical Characteristics*.

Figure 2 shows the MAX551/MAX552 timing diagram. The most significant bit (MSB) is always loaded first on SCLK's rising edge. When all data is shifted into the input register, the DAC register is loaded by driving the LOAD signal low. The DAC register is transparent when LOAD is low and latched when LOAD is high. The MAX551/MAX552 digital inputs are compatible with CMOS logic levels. The MAX551's inputs are also compatible with TTL logic.

## **Unipolar Operation**

MAX551/MAX552

Figure 3 shows the MAX551/MAX552's basic application. This circuit is used for unipolar operation or 2quadrant multiplication. The code table for this mode is given in Table 1. Note that the output's polarity is the opposite of the reference voltage polarity.

In many applications the gain accuracy is sufficient and gain adjustment is not necessary. In these cases, resistors R1 and R2 in Figure 3 can be omitted. If the gain is trimmed and the DAC is operated over a wide temperature range, use low-tempco (<300ppm/°C) resistors for R1 and R2. Capacitor C1 provides phase compensation and reduces overshoot and ringing when fast amplifiers are used at the DAC's output.

### **Bipolar Operation**

Figure 4 shows the MAX551/MAX552 operating in bipolar (or 4-quadrant multiplying) mode. Matched resistors R3, R4, and R5 must be of the same material (preferably metal film or wire-wound) for good temperaturetracking characteristics (<15ppm/°C) and should match to 0.01% for 12-bit performance. The output code is offset binary, as listed in Table 2.

To adjust the circuit, load the DAC with a code of 1000 0000 0000 and trim R1 for a 0V output. With R1 and R2 omitted, an alternative zero trim is needed to adjust the ratio of R3 and R4 for 0V out. Trim full scale by loading the DAC with all 0s or 1s and adjusting the V<sub>REF</sub> amplitude or varying R5 until the desired positive or negative output is obtained. In applications where gain trim is not required, omit resistors R1 and R2. If gain trim is desired and the DAC is operated over a wide temperature range, then low-tempco (<300ppm/°C) resistors should be used.

# MAX551/MAX552

## **Applications Information**

## **Output Amplifier**

For best linearity, terminate OUT and GND at exactly OV. In most applications, OUT is connected to an inverting op amp's summing junction. The amplifier's input offset voltage can degrade the DAC's linearity by causing OUT to be terminated to a nonzero voltage. The resulting error is:

Error Voltage = Vos (1 + RFB / RO)

where V<sub>OS</sub> = is the op amp's offset and R<sub>O</sub> is the DAC's output resistance, which is code dependent. The maximum error voltage (R<sub>O</sub> = R<sub>FB</sub>) is 2V<sub>OS</sub>; the minimum error voltage (R<sub>O</sub> =  $\infty$ ) is V<sub>OS</sub>. To minimize this error, use a low-offset amplifier such as the MAX4166 (unipolar output) or the MAX427 (bipolar output). Otherwise, the amplifier offset must be trimmed to zero. A good guide rule is that V<sub>OS</sub> should be no more than 1/10LSB.

The output amplifier's input bias current (I<sub>B</sub>) can also limit performance, since I<sub>B</sub> x R<sub>FB</sub> generates an offset error. Choose an op amp with an I<sub>B</sub> much less than (e.g., one-tenth) the DAC's 1LSB output current (typically 111nA when V<sub>REF</sub> = 5V, and 55.5nA when V<sub>REF</sub> = 2.5V). Offset and linearity can also be impaired if the output amplifier's noninverting input is grounded through a bias-current compensation resistor. This resistor adds to the offset at this pin and thus should not be used. For best performance, connect the noninverting input directly to ground.

In static or DC applications, the output amplifier's characteristics are not critical. In higher speed applications in which either the reference input is an AC signal or the DAC output must quickly settle to a new programmed value, the output op amp's AC parameters must be considered.

A compensation capacitor, C1, may be required when the DAC is used with a high-speed output amplifier. The purpose of the capacitor is to cancel the pole formed by the DAC output capacitance, C<sub>OUT</sub>, and the internal feedback resistor, R<sub>FB</sub>. Its value depends on the type of op amp used but typically ranges from 14pF to 30pF. Too small a value causes output ringing, while excess capacitance overdamps the output. C1's size can be minimized and the output voltage settling time improved by keeping the circuit-board trace short and stray capacitance at OUT as low as possible.

Figure 5. Single-Supply, Voltage Mode Operation

## **Single-Supply Operation**

## **Reference Voltage**

The MAX551/MAX552 are true 4-quadrant DACs, making them ideal for multiplying applications. The reference input accepts both AC and DC signals within a voltage range of  $\pm$ 6V. The R-2R ladder is implemented with thin-film resistors, enabling the use of unipolar or bipolar reference voltages with only a single power supply for the DAC. The voltage at the V<sub>REF</sub> input sets the DAC's full-scale output voltage.

If the reference is too noisy, it should be bypassed to GND (AGND on the 10-pin  $\mu$ MAX package) with a 0.1 $\mu$ F ceramic capacitor located as close to the REF pin as possible.

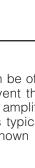

## Voltage Mode (MAX551)

The MAX551 can be conveniently used in voltage mode, single-supply operation with OUT biased at any voltage between GND and  $V_{DD}$ . OUT must not be allowed to go 0.3V lower than GND or 0.3V higher than  $V_{DD}$ . Otherwise, internal diodes turn on, causing a high current flow that could damage the device.

Figure 5 shows the MAX551 connected as a voltage output DAC. In this mode of operation, the OUT pin is connected to the reference-voltage source, and the GND pin is connected to the PCB ground plane. The DAC output now appears at the REF pin, which has a constant resistance equal to the reference input resistance (11k $\Omega$  typ). This output should be buffered with an op amp when a lower output impedance is required. The RFB pin is not used in this mode. The reference input (OUT) impedance is code dependent, and the circuit's response time depends on the reference source's behavior with changing load conditions.

Figure 6. Single-Supply, Current Mode Operation

An advantage of voltage mode operation is that a negative reference is not required for a positive output. Note that the reference input (OUT) must always be positive and is limited to no more than 2V when V<sub>D</sub> is 5V. The unipolar and bipolar circuits in Figures 3 and 4 can be converted to voltage mode.

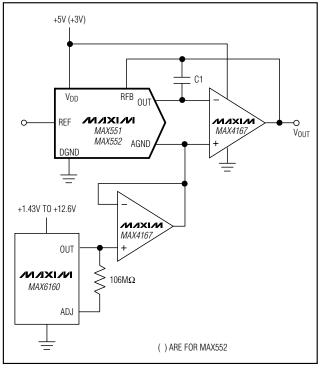

**Current Mode** Figure 6 shows the MAX551/MAX552 in a current output configuration in which the output amplifier is powered from a single supply, and AGND is biased to 1.23V. With 0V applied to the REF input, the output can be programmed from 1.23V (zero code) to 2.46V (full scale). With 2.45V applied to REF, the output can be programmed from 1.23V (zero code) to 0.01V (full scale).

The MAX4166 op amp that drives AGND maintains the 1.23V bias as AGND's impedance changes with the DAC's digital code, from high impedance (zero code) to  $7k\Omega$  minimum (full scale).

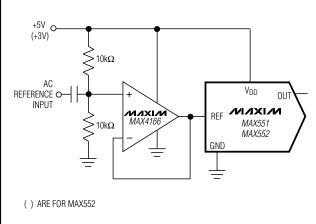

## Using an AC Reference

In applications where reference voltage has AC signal components, the MAX551/MAX552 have multiplying capability within the reference input range of ±6V. If the DAC and the output amplifier are operated with a single

Figure 7. Single-Supply AC Reference Input Circuit

supply voltage, then an AC reference input can be offset with the circuit shown in Figure 7 to prevent the DAC output voltage from exceeding the output amplifier's negative output rail. The reference input's typical -3dB bandwidth is greater than 700kHz, as shown in the Typical Operating Characteristics graphs.

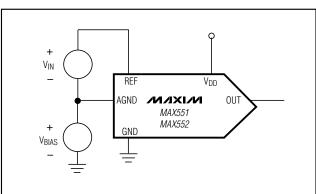

## **Offsetting AGND**

The MAX551/MAX552 provide separate AGND and GND inputs in the µMAX package. With this package, AGND can be biased above GND to provide an arbitrary nonzero output voltage for a "0" input code (Figure 8).

## Layout, Grounding, and Bypassing

Bypass V<sub>DD</sub> with a 0.1µF capacitor, located as close to VDD and GND as possible. The ground pins (AGND and GND) should be connected in a star configuration to the highest quality ground available, which should be located as close to the MAX551/MAX552 as possible.

Since OUT and the output amplifier's noninverting input are sensitive to offset voltage, nodes that are to be grounded should be connected directly to a singlepoint ground through a separate, low-resistance (less than 0.2 $\Omega$ ) connection. The current at OUT and AGND varies with input code, creating a code-dependent error if these terminals are connected to ground (or virtual ground) through a resistive path.

Parasitic coupling of the signal from REF to OUT is an error source in dynamic applications. This coupling is normally a function of board layout and pin-to-pin package capacitance. Minimize digital feedthrough with guard traces between digital inputs, REF, and OUT pins.

MAX551/MAX552

Figure 8. AGND Bias Current

MAX551/MAX552

The MAX551/MAX552 have high-impedance digital inputs. To minimize noise pickup, tie them to either V<sub>DD</sub> or GND when they are not in use. As a good practice, connect active inputs to V<sub>DD</sub> or GND through high-value resistors (1M $\Omega$ ) to prevent static charge accumulation if the pins are left floating, such as when a circuit card is left unconnected.

The  $\overline{\text{CLR}}$  input on the  $\mu$ MAX device has an internal pullup resistor with a typical value of 125k $\Omega$ . If the  $\overline{\text{CLR}}$ input is not used, tie it to V<sub>DD</sub> to minimize supply current.

## \_Ordering Information (continued)

| PART       | TEMP RANGE     | PIN-<br>PACKAGE | LINEARITY<br>(LSB) |

|------------|----------------|-----------------|--------------------|

| MAX552ACPA | 0°C to +70°C   | 8 Plastic DIP   | ±1/2               |

| MAX552BCPA | 0°C to +70°C   | 8 Plastic DIP   | ±1                 |

| MAX552ACUB | 0°C to +70°C   | 10 µMAX         | ±1/2               |

| MAX552BCUB | 0°C to +70°C   | 10 µMAX         | ±1                 |

| MAX552AEPA | -40°C to +85°C | 8 Plastic DIP   | ±1/2               |

| MAX552BEPA | -40°C to +85°C | 8 Plastic DIP   | ±1                 |

| MAX552AEUB | -40°C to +85°C | 10 µMAX         | ±1/2               |

| MAX552BEUB | -40°C to +85°C | 10 µMAX         | ±1                 |

## **Chip Information**

TRANSISTOR COUNT: 887 SUBSTRATE CONNECTED TO VDD

## **Package Information**

For the latest package outline information, go to **www.maxim-ic.com/packages**.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2002 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Digital to Analog Converters - DAC category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

5962-8876601LA PM7545FPCZ AD5311BRMZ-REEL7 AD664AJ AD7534JPZ TCC-103A-RT 057536E 5962-89657023A 702423BB TCC-202A-RT AD664BE TCC-303A-RT TCC-206A-RT AD5770RBCBZ-RL7 DAC8229FSZ-REEL AD5673RBCPZ-2 MCP48FVB24-20E/ST MCP48FVB28-E/MQ MCP48FEB18-20E/ST MCP48FEB18-E/MQ MCP48FEB24-E/MQ MCP48FEB28T-20E/ST MCP47FVB04T-E/MQ MCP48FEB28T-E/MQ MCP48FVB28T-20E/ST MCP47FVB28T-20E/ST MCP47FEB24T-E/MQ MCP48FVB18T-20E/ST MCP47FEB14T-E/MQ MCP48FEB08T-E/MQ MCP48FVB08T-20E/ST MCP47FEB04T-E/MQ MCP47FVB04T-20E/ST AD7524JRZ-REEL LTC1664CGN LTC1664IGN LTC7545ACSW MCP47DA1T-A1E/OT MCP4921-E/MC UC3910D DAC39J84IAAV DAC8218SPAG DAC8562TDGSR MAX545BCPD+ DAC7641YB/250 DAC7611PB DAC0800LCM TLV5638CDR TLC5615IDR DAC900TPWRQ1