# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

#### **General Description**

The MAX5816 4-channel, low-power, 12-bit, voltageoutput digital-to-analog converter (DAC) includes output buffers and an internal reference that is selectable to be 2.048V, 2.500V, or 4.096V. The MAX5816 accepts a wide supply voltage range of 2.7V to 5.5V with extremely low power (3mW) consumption to accommodate most lowvoltage applications. A precision external reference input allows rail-to-rail operation and presents a  $100k\Omega$  (typ) load to an external reference.

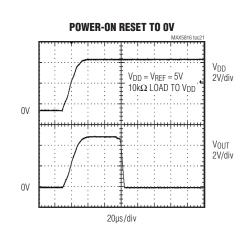

The MAX5816 has an I<sup>2</sup>C-compatible, 2-wire interface that operates at clock rates up to 400kHz. The DAC output is buffered and has a low supply current of less than 250µA per channel and a low offset error of ±0.5mV (typ). On power-up, the MAX5816 resets the DAC outputs to zero, providing additional safety for applications that drive valves or other transducers which need to be off on power-up. The internal reference is initially powered down to allow use of an external reference. The MAX5816 allows simultaneous output updates using software LOAD commands. Multiple devices can simultaneously be updated using software load command in combination with the broadcast ID.

The MAX5816 is available in a 10-pin TDFN package and is specified over the -40°C to +125°C temperature range.

### **Applications**

Programmable Voltage and Current Sources Gain and Offset Adjustment Automatic Tuning and Optical Control Power Amplifier Control and Biasing Process Control and Servo Loops Portable Instrumentation **Data Acquisition**

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- **♦ Four High-Accuracy DAC Channels**

- ♦ 12-Bit Accuracy Without Adjustment

- Conditions

- ♦ Independent Mode Settings for Each DAC

- **♦ Three Precision Selectable Internal References**

- ♦ 2.048V. 2.500V. or 4.096V

- ♦ Internal Output Buffer

- ♦ Rail-to-Rail Operation with External Reference

- ♦ 4.5µs Settling Time

- ♦ Outputs Directly Drive 2kΩ Loads

- ♦ Small 3mm x 3mm 10-Pin TDFN Package

- ♦ Wide 2.7V to 5.5V Supply Range

- ♦ Fast 400kHz I<sup>2</sup>C-Compatible, 2-Wire Serial Interface

- ♦ Power-On-Reset to Zero-Scale DAC Output

- ♦ Three Software-Selectable Power-Down Output

- $\diamond$  1k $\Omega$ , 100k $\Omega$ , or High Impedance

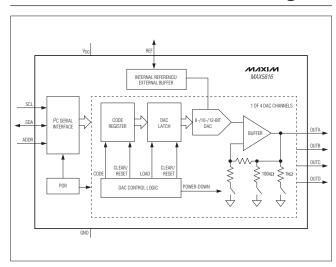

### **Functional Diagram**

For related parts and recommended products to use with this part, refer to: www.maxim-ic.com/MAX5816.related

#### **ABSOLUTE MAXIMUM RATINGS**

| ADDR to GND0.3V to the lower of (V <sub>DD</sub> + 0.3V) and +6V Lead Temperature (soldering, 10s)+300° | Continuous Power Dissipation (T <sub>A</sub> = +70°C) | Maximum Continuous Current into Any Pin |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------|

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------|

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

**TDFN**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) .......41°C/W Junction-to-Case Thermal Resistance (θ<sub>JC</sub>)......9°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD}=2.7V \text{ to } 5.5V,\ V_{GND}=0V,\ C_L=200 \text{pF},\ R_L=2k\Omega,\ T_A=-40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                          | SYMBOL | CONDITIONS                       | MIN  | TYP  | MAX                      | UNITS           |

|------------------------------------|--------|----------------------------------|------|------|--------------------------|-----------------|

| DC PERFORMANCE (Note 3)            |        |                                  |      |      |                          |                 |

| Resolution and Monotonicity        | N      |                                  | 12   |      |                          | Bits            |

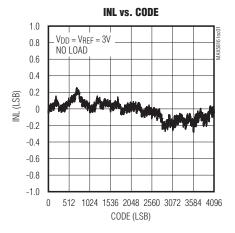

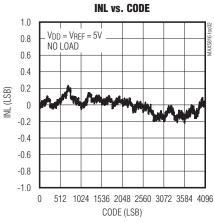

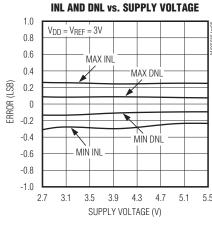

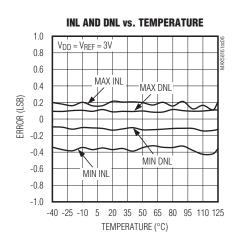

| Integral Nonlinearity (Note 4)     | INL    |                                  | -1   | ±0.5 | +1                       | LSB             |

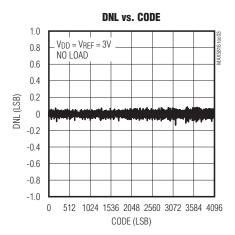

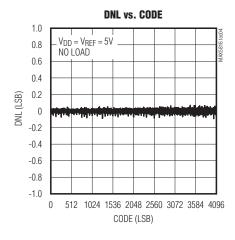

| Differential Nonlinearity (Note 4) | DNL    |                                  | -1   | ±0.2 | +1                       | LSB             |

| Offset Error (Note 5)              | OE     |                                  | -5   | ±0.5 | +5                       | mV              |

| Offset Error Drift                 |        |                                  |      | ±10  |                          | μV/°C           |

| Gain Error (Note 5)                | GE     |                                  | -1.0 | ±0.1 | +1.0                     | %FS             |

| Gain Temperature Coefficient       |        | With respect to V <sub>REF</sub> |      | ±3.0 |                          | ppm of<br>FS/°C |

| Zero-Scale Error                   |        |                                  | 0    |      | 10                       | mV              |

| Full-Scale Error                   |        | With respect to V <sub>REF</sub> | -0.5 |      | +0.5                     | %FS             |

| DAC OUTPUT CHARACTERISTI           | CS     |                                  |      |      |                          |                 |

|                                    |        | No load                          | 0    |      | V <sub>DD</sub>          |                 |

| Output Voltage Range (Note 6)      |        | $2k\Omega$ load to GND           | 0    |      | V <sub>DD</sub> -<br>0.2 | V               |

|                                    |        | $2k$ Ω load to $V_{DD}$          | 0.2  |      | $V_{DD}$                 |                 |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 2.7 \text{V to } 5.5 \text{V}, V_{GND} = 0 \text{V}, C_L = 200 \text{pF}, R_L = 2 \text{k}\Omega, T_A = -40 ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                        | SYMBOL | CON                                 | DITIONS                                         | MIN | TYP | MAX | UNITS   |

|----------------------------------|--------|-------------------------------------|-------------------------------------------------|-----|-----|-----|---------|

| Load Degulation                  |        | V V/0                               | $V_{DD} = 3V \pm 10\%,$<br>$II_{OUT}I \le 5mA$  |     | 300 |     | - μV/mA |

| Load Regulation                  |        | $V_{OUT} = V_{FS}/2$                | $V_{DD} = 5V \pm 10\%,$<br>$II_{OUT}I \le 10mA$ |     | 300 |     | ην/πΑ   |

| DC Output Impedance              |        | V // //                             | $V_{DD} = 3V \pm 10\%,$<br>$II_{OUT}I \le 5mA$  |     | 0.3 |     |         |

| DC Output impedance              |        | $V_{OUT} = V_{FS}/2$                | $V_{DD} = 5V \pm 10\%,$<br>$II_{OUT}I \le 10mA$ |     | 0.3 |     | Ω       |

| Maximum Capacitive Load Handling | CL     |                                     |                                                 |     | 500 |     | pF      |

| Resistive Load Handling          | RL     |                                     |                                                 | 2   |     |     | kΩ      |

|                                  |        | \\                                  | Sourcing (output shorted to GND)                |     | 30  |     | A       |

| Short-Circuit Output Current     |        | $V_{DD} = 5.5V$                     | Sinking (output shorted to V <sub>DD</sub> )    |     | 50  |     | - mA    |

| DC Power-Supply Rejection        |        | $V_{DD} = 3V \pm 10\% \text{ or } $ | 5V ±10%                                         |     | 100 |     | μV/V    |

| DYNAMIC PERFORMANCE              |        |                                     |                                                 |     |     |     |         |

| Voltage-Output Slew Rate         | SR     | Positive and negative               | /e                                              |     | 1.0 |     | V/µs    |

| Voltage-Output Settling Time     |        | 1/4 scale to 3/4 scale,             | to ≤ 1 LSB                                      |     | 4.5 |     | μs      |

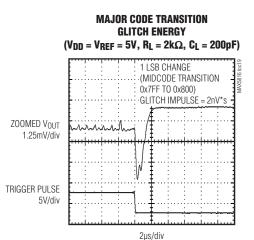

| DAC Glitch Impulse               |        | Major code transitio                | n                                               |     | 2   |     | nV*s    |

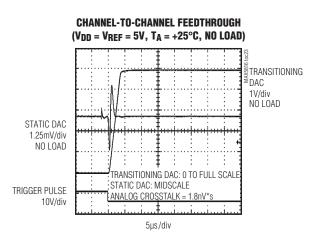

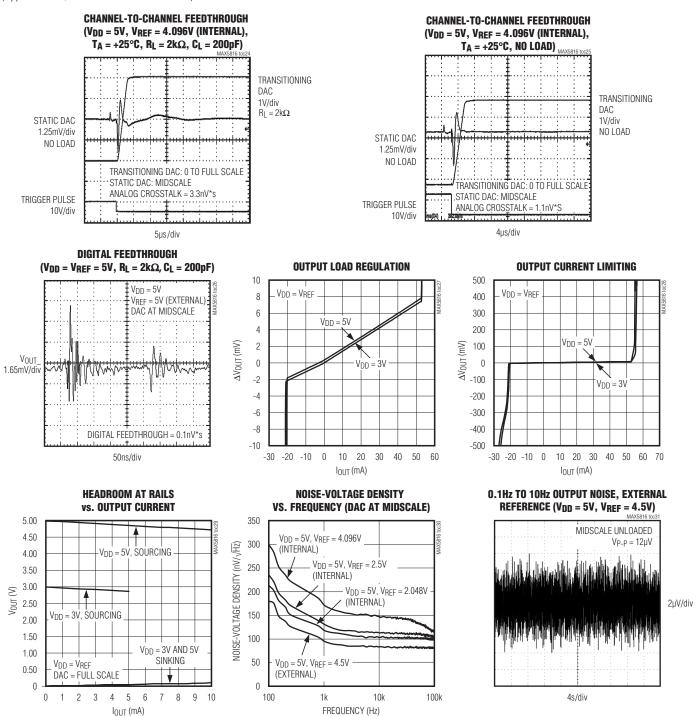

| Channel-to-Channel               |        | External reference                  |                                                 |     | 3.5 |     | nV*s    |

| Feedthrough (Note 7)             |        | Internal reference                  |                                                 |     | 3.3 |     | TIVS    |

| Digital Feedthrough              |        | Code = 0, all digital               | inputs from 0V to V <sub>DD</sub>               |     | 0.2 |     | nV*s    |

| D. II. T                         |        | Startup calibration t               | ime (Note 8)                                    |     | 200 |     | μs      |

| Power-Up Time                    |        | From power-down                     |                                                 |     | 50  |     | μs      |

|                                  |        | Estamal materials                   | f = 1kHz                                        |     | 90  |     |         |

|                                  |        | External reference                  | f = 10kHz                                       |     | 82  |     |         |

|                                  |        | 2.048V internal                     | f = 1kHz                                        |     | 112 |     |         |

| Output Voltage-Noise Density     |        | reference                           | f = 10kHz                                       |     | 102 |     | nV/√Hz  |

| (DAC Output at Midscale)         |        | 2.5V internal                       | f = 1kHz                                        |     | 125 |     |         |

|                                  |        | reference                           | f = 10kHz                                       |     | 110 |     | _       |

|                                  |        | 4.096V internal                     | f = 1kHz                                        |     | 160 |     | -       |

|                                  |        | reference                           | f = 10kHz                                       |     | 145 |     |         |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=2.7V\ to\ 5.5V,\ V_{GND}=0V,\ C_L=200pF,\ R_L=2k\Omega,\ T_A=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                    | SYMBOL           | CON                       | DITIONS               | MIN  | TYP | MAX      | UNITS             |

|------------------------------|------------------|---------------------------|-----------------------|------|-----|----------|-------------------|

|                              |                  |                           | f = 0.1Hz to 10Hz     |      | 12  |          |                   |

|                              |                  | External reference        | f = 0.1Hz to $10kHz$  |      | 76  |          |                   |

|                              |                  |                           | f = 0.1Hz to 300kHz   |      | 385 |          | ]                 |

|                              |                  | 2.048V internal reference | f = 0.1Hz to 10Hz     |      | 14  |          |                   |

|                              |                  |                           | f = 0.1Hz to $10kHz$  |      | 91  |          |                   |

| Integrated Output Noise      |                  |                           | f = 0.1Hz to 300kHz   |      | 450 |          | μν <sub>Ρ-Ρ</sub> |

| (DAC Output at Midscale)     |                  | 2.5V internal             | f = 0.1Hz to 10Hz     |      | 15  |          | μνρ-Ρ             |

|                              |                  | reference                 | f = 0.1Hz to $10kHz$  |      | 99  |          |                   |

|                              |                  |                           | f = 0.1Hz to 300kHz   |      | 470 |          |                   |

|                              |                  | 4.096V internal           | f = 0.1Hz to 10Hz     |      | 16  |          |                   |

|                              |                  | reference                 | f = 0.1Hz to $10kHz$  |      | 124 |          |                   |

|                              |                  |                           | f = 0.1Hz to $300kHz$ |      | 490 |          |                   |

|                              |                  | External reference        | f = 1kHz              |      | 114 |          |                   |

|                              |                  | External reference        | f = 10kHz             |      | 99  |          |                   |

|                              |                  | 2.048V internal           | f = 1kHz              |      | 175 |          |                   |

| Output Voltage-Noise Density |                  | reference                 | f = 10kHz             |      | 153 |          | nV/√Hz            |

| (DAC Output at Full Scale)   |                  | 2.5V internal             | f = 1kHz              |      | 200 |          |                   |

|                              |                  | reference                 | f = 10kHz             |      | 174 |          |                   |

|                              |                  | 4.096V internal           | f = 1kHz              |      | 295 |          |                   |

|                              |                  | reference                 | f = 10kHz             |      | 255 |          |                   |

|                              |                  |                           | f = 0.1Hz to 10Hz     |      | 13  |          |                   |

|                              |                  | External reference        | f = 0.1Hz to $10kHz$  |      | 94  |          |                   |

|                              |                  |                           | f = 0.1Hz to 300kHz   |      | 540 |          |                   |

|                              |                  | 0.0401/1                  | f = 0.1Hz to 10Hz     |      | 19  |          |                   |

|                              |                  | 2.048V internal reference | f = 0.1Hz to $10kHz$  |      | 143 |          |                   |

| Integrated Output Noise      |                  | reference                 | f = 0.1Hz to 300kHz   |      | 685 |          | /                 |

| (DAC Output at Full Scale)   |                  |                           | f = 0.1Hz to 10Hz     |      | 21  |          | μV <sub>P-P</sub> |

|                              |                  | 2.5V internal reference   | f = 0.1Hz to $10kHz$  |      | 159 |          |                   |

|                              |                  | Telefelice                | f = 0.1Hz to 300kHz   |      | 705 |          |                   |

|                              |                  |                           | f = 0.1Hz to 10Hz     |      | 26  |          |                   |

|                              |                  | 4.096V internal reference | f = 0.1Hz to $10kHz$  |      | 213 |          |                   |

|                              |                  | Telefelice                | f = 0.1Hz to 300kHz   |      | 750 |          |                   |

| REFERENCE INPUT              |                  |                           |                       | ,    |     |          |                   |

| Reference Input Range        | V <sub>REF</sub> |                           |                       | 1.24 |     | $V_{DD}$ | V                 |

| Reference Input Current      | I <sub>REF</sub> | $V_{REF} = V_{DD} = 5.5V$ |                       |      | 55  | 74       | μA                |

| Reference Input Impedance    | R <sub>REF</sub> |                           |                       | 75   | 100 |          | kΩ                |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=2.7V\ to\ 5.5V,\ V_{GND}=0V,\ C_L=200pF,\ R_L=2k\Omega,\ T_A=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                            | SYMBOL                            | CONI                                                     | MIN                                                                      | TYP                      | MAX   | UNITS                    |        |  |

|--------------------------------------|-----------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------|--------------------------|-------|--------------------------|--------|--|

| REFERENCE OUPUT                      |                                   |                                                          |                                                                          |                          |       |                          |        |  |

|                                      |                                   | $V_{REF} = 2.048V, T_{A} =$                              | : +25°C                                                                  | 2.043                    | 2.048 | 2.053                    |        |  |

| Reference Output Voltage             | V <sub>REF</sub>                  | $V_{REF} = 2.5V, T_A = +$                                | 25°C                                                                     | 2.494                    | 2.5   | 2.506                    | V      |  |

|                                      |                                   | $V_{REF} = 4.096V, T_{A} =$                              | 4.086                                                                    | 4.096                    | 4.106 |                          |        |  |

| Reference Temperature<br>Coefficient |                                   |                                                          |                                                                          |                          | ±10   | ±25                      | ppm/°C |  |

| Reference Drive Capacity             |                                   | External load                                            |                                                                          |                          | 25    |                          | kΩ     |  |

| Reference Capacitive Load            |                                   |                                                          |                                                                          |                          | 200   |                          | pF     |  |

| Reference Load Regulation            |                                   | I <sub>SOURCE</sub> = 0 to 500µ                          | AL                                                                       |                          | 2     |                          | mV/mA  |  |

| Reference Line Regulation            |                                   |                                                          |                                                                          |                          | 0.05  |                          | mV/V   |  |

| POWER REQUIREMENTS                   | •                                 |                                                          |                                                                          | '                        |       |                          |        |  |

| 0 - 1 1/4 11                         |                                   | V <sub>REF</sub> = 4.096V                                | 4.5                                                                      |                          | 5.5   |                          |        |  |

| Supply Voltage                       | V <sub>DD</sub>                   | All other options                                        | 2.7                                                                      |                          | 5.5   | - V                      |        |  |

|                                      |                                   |                                                          | V <sub>REF</sub> = 2.048V                                                |                          | 0.85  | 1.25                     |        |  |

|                                      |                                   | Internal reference,<br>V <sub>DD</sub> = 5.5V            | V <sub>REF</sub> = 2.5V                                                  |                          | 0.9   | 1.25                     | mA     |  |

| Supply Current (Note 9)              | I <sub>DD</sub>                   | VDD = 3.5V                                               | V <sub>REF</sub> = 4.096V                                                |                          | 1.1   | 1.40                     |        |  |

|                                      |                                   | F. dama al mafanana                                      | $V_{DD} = V_{REF} = 3V$                                                  |                          | 0.65  | 1.1                      |        |  |

|                                      |                                   | External reference                                       | $V_{DD} = V_{REF} = 5V$                                                  |                          | 0.9   | 1.25                     |        |  |

|                                      |                                   | All DACs off, interna                                    | I reference ON                                                           |                          | 140   |                          |        |  |

| Power-Down Mode Supply<br>Current    | I <sub>PD</sub>                   | All DACs off, interna<br>T <sub>A</sub> = -40°C to +85°C | All DACs off, internal reference OFF,<br>T <sub>A</sub> = -40°C to +85°C |                          | 0.5   | 1                        | μA     |  |

| Current                              |                                   | All DACs off, interna<br>T <sub>A</sub> = +125°C         |                                                                          | 1.2                      | 2.5   |                          |        |  |

| DIGITAL INPUT CHARACTERIS            | TICS (SCL, S                      | DA, ADDR)                                                |                                                                          | '                        |       |                          |        |  |

| Input High Voltage                   | V <sub>IH</sub>                   | 2.7V < V <sub>DD</sub> < 5.5V                            |                                                                          | 0.7 x<br>V <sub>DD</sub> |       |                          | V      |  |

| Input Low Voltage                    | V <sub>IL</sub>                   | 2.7V < V <sub>DD</sub> < 5.5V                            |                                                                          |                          |       | 0.3 x<br>V <sub>DD</sub> | V      |  |

| Hysteresis Voltage                   | V <sub>H</sub>                    |                                                          |                                                                          |                          | 0.15  |                          | V      |  |

| Input Leakage Current                | I <sub>IN</sub>                   | $V_{IN} = 0V \text{ or } V_{DD}$                         | ·                                                                        |                          | ±0.1  | ±1                       | μΑ     |  |

| Input Capacitance (Note 10)          | C <sub>IN</sub>                   |                                                          |                                                                          |                          |       | 10                       | pF     |  |

| ADDR Pullup/Pulldown Strength        | R <sub>PU</sub> , R <sub>PD</sub> | (Note 11)                                                |                                                                          | 30                       | 50    | 90                       | kΩ     |  |

| DIGITAL OUTPUT (SDA)                 |                                   |                                                          |                                                                          |                          |       |                          |        |  |

| Output Low Voltage                   | V <sub>OL</sub>                   | I <sub>SINK</sub> = 3mA                                  |                                                                          |                          |       | 0.2                      | V      |  |

|                                      |                                   |                                                          |                                                                          |                          |       |                          |        |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 2.7V \text{ to } 5.5V, V_{GND} = 0V, C_L = 200 \text{pF}, R_L = 2 \text{k}\Omega, T_A = -40 ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                                          | SYMBOL              | CONDITIONS | MIN                        | TYP | MAX | UNITS |  |  |  |  |  |  |

|----------------------------------------------------|---------------------|------------|----------------------------|-----|-----|-------|--|--|--|--|--|--|

| I <sup>2</sup> C TIMING CHARACTERISTICS (SCL, SDA) |                     |            |                            |     |     |       |  |  |  |  |  |  |

| SCL Clock Frequency                                | f <sub>SCL</sub>    |            |                            |     | 400 | kHz   |  |  |  |  |  |  |

| Bus Free Time Between a STOP and a START Condition | t <sub>BUF</sub>    |            | 1.3                        |     |     | μs    |  |  |  |  |  |  |

| Hold Time Repeated for a START Condition           | t <sub>HD;STA</sub> |            | 0.6                        |     |     | μs    |  |  |  |  |  |  |

| SCL Pulse Width Low                                | t <sub>LOW</sub>    |            | 1.3                        |     |     | μs    |  |  |  |  |  |  |

| SCL Pulse Width High                               | tHIGH               |            | 0.6                        |     |     | μs    |  |  |  |  |  |  |

| Setup Time for Repeated START Condition            | tsu;sta             |            | 0.6                        |     |     | μs    |  |  |  |  |  |  |

| Data Hold Time                                     | t <sub>HD;DAT</sub> |            | 0                          |     | 900 | ns    |  |  |  |  |  |  |

| Data Setup Time                                    | t <sub>SU;DAT</sub> |            | 100                        |     |     | ns    |  |  |  |  |  |  |

| SDA and SCL Receiving<br>Rise Time                 | t <sub>r</sub>      |            | 20 +<br>C <sub>B</sub> /10 |     | 300 | ns    |  |  |  |  |  |  |

| SDA and SCL Receiving Fall Time                    | t <sub>f</sub>      |            | 20 +<br>C <sub>B</sub> /10 |     | 300 | ns    |  |  |  |  |  |  |

| SDA Transmitting Fall Time                         | t <sub>f</sub>      |            | 20 +<br>C <sub>B</sub> /10 |     | 250 | ns    |  |  |  |  |  |  |

| Setup Time for STOP Condition                      | tsu;sto             |            | 0.6                        |     |     | μs    |  |  |  |  |  |  |

| Bus Capacitance Allowed                            | C <sub>B</sub>      |            | 10                         |     | 400 | pF    |  |  |  |  |  |  |

| Pulse Width of Suppressed Spike                    | t <sub>sp</sub>     |            |                            | 50  |     | ns    |  |  |  |  |  |  |

- Note 2: Limits are 100% production tested at  $T_A = +25^{\circ}$ C and/or  $T_A = +125^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are at T<sub>A</sub> = +25°C and are not guaranteed.

- Note 3: DC Performance is tested without load.

- Note 4: Linearity is tested with unloaded outputs to within 20mV of GND and VDD.

- Note 5: Gain and offset tested at code 4065 and 30, respectively with V<sub>RFF</sub> = V<sub>DD</sub>.

- Note 6: Subject to zero and full-scale error limits and V<sub>RFF</sub> settings.

- Note 7: Measured with all other DAC outputs at midscale with one channel transitioning 0 to full scale.

- Note 8: On power-up, the device initiates an internal 200µs (typ) calibration sequence. All commands issued during this time will

- Note 9: All channels active at  $V_{FS}$ , unloaded. Static logic inputs with  $V_{IL} = V_{GND}$  and  $V_{IH} = V_{DD}$ .

- Note 10: Guaranteed by design.

- Note 11:An unconnected condition on the ADDR pin is sensed via a resistive pullup and pulldown operation; for proper operation, the ADDR pin should be tied to VDD, GND, or left unconnected with minimal capacitance.

# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

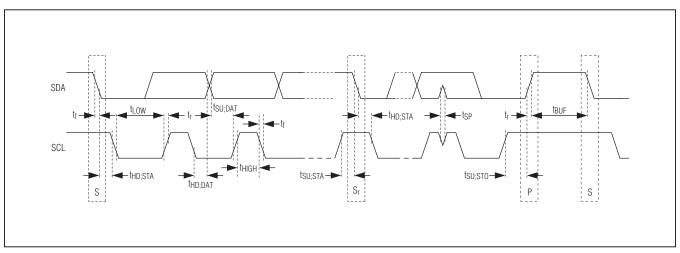

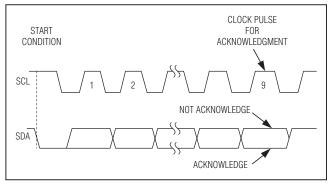

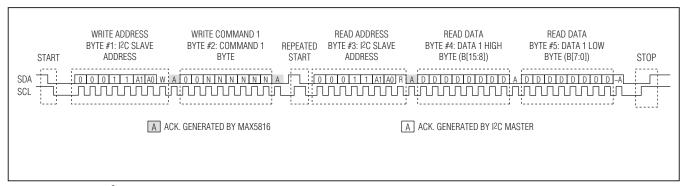

Figure 1. I<sup>2</sup>C Serial Interface Timing Diagram

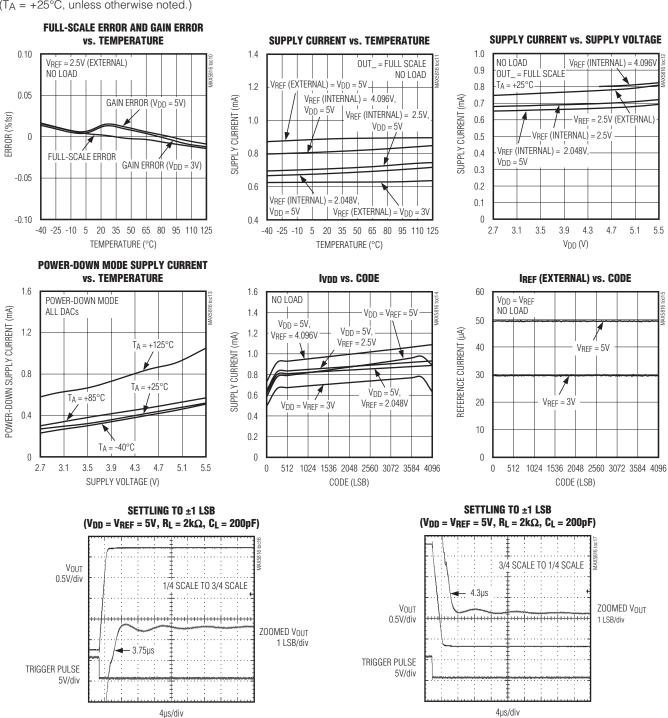

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

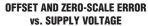

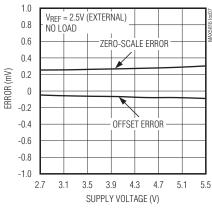

#### **OFFSET AND ZERO-SCALE ERROR** vs. TEMPERATURE

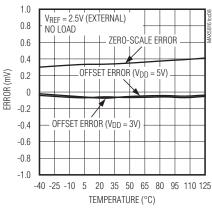

#### **FULL-SCALE ERROR AND GAIN-ERROR** vs. SUPPLY VOLTAGE

# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

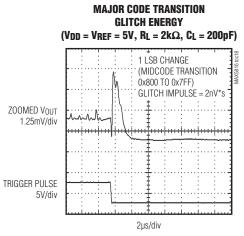

### Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

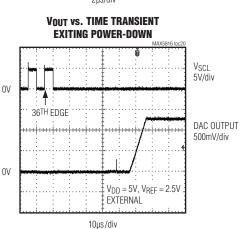

### **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

**CHANNEL-TO-CHANNEL FEEDTHROUGH**

# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

### Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

### **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

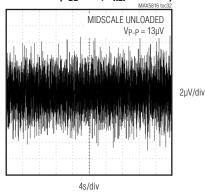

#### 0.1Hz TO 10Hz OUTPUT NOISE, INTERNAL REFERENCE (VDD = 5V, VREF = 2.048V)

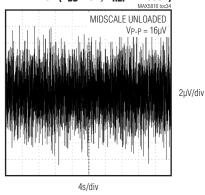

#### 0.1Hz TO 10Hz OUTPUT NOISE, INTERNAL REFERENCE (VDD = 5V, VREF = 4.096V)

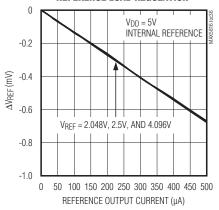

#### REFERENCE LOAD REGULATION

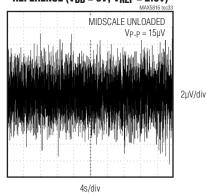

#### 0.1Hz TO 10Hz OUTPUT NOISE, INTERNAL REFERENCE ( $V_{DD} = 5V$ , $V_{REF} = 2.5V$ )

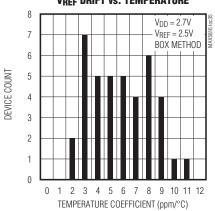

#### **VREF DRIFT vs. TEMPERATURE**

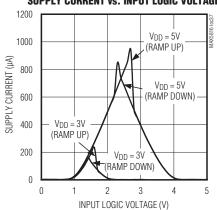

#### SUPPLY CURRENT vs. INPUT LOGIC VOLTAGE

# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

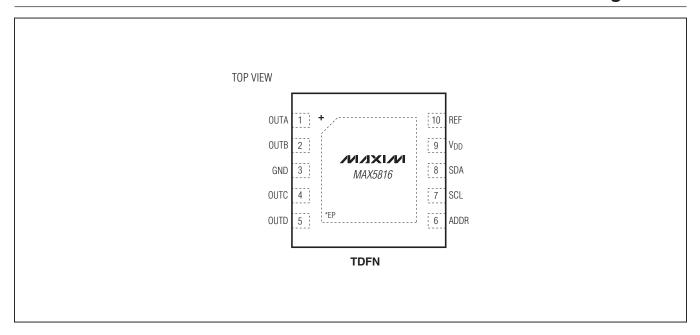

### **Pin Configuration**

### **Pin Description**

| PIN | NAME            | FUNCTION                                                                    |

|-----|-----------------|-----------------------------------------------------------------------------|

| 1   | OUTA            | Buffered Channel A DAC Output                                               |

| 2   | OUTB            | Buffered Channel B DAC Output                                               |

| 3   | GND             | Ground                                                                      |

| 4   | OUTC            | Buffered Channel C DAC Output                                               |

| 5   | OUTD            | Buffered Channel D DAC Output                                               |

| 6   | ADDR            | I <sup>2</sup> C Address Selection Input                                    |

| 7   | SCL             | Supply Voltage Input. I <sup>2</sup> C Interface Clock Input                |

| 8   | SDA             | I <sup>2</sup> C Bidirectional Serial Data                                  |

| 9   | V <sub>DD</sub> | Digital Interface Power-Supply Input. Bypass with a 0.1µF capacitor to GND. |

| 10  | REF             | Reference Voltage Input/Output                                              |

| _   | EP              | Exposed Pad. Connect the exposed pad to ground.                             |

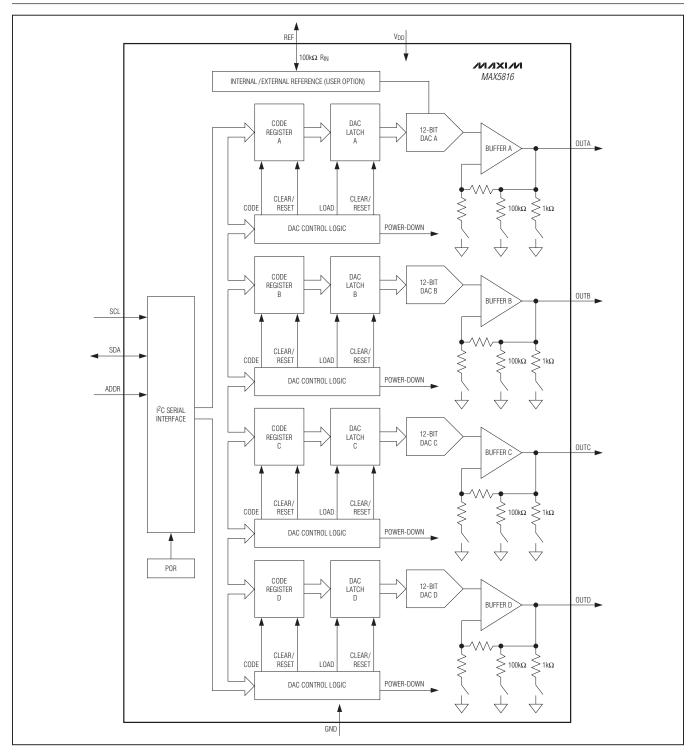

### **Detailed Description**

The MAX5816 is a 4-channel, low-power, 12-bit buffered voltage-output DAC. The 2.7V to 5.5V wide supply voltage range and low-power consumption accommodates most low-power and low-voltage applications. The device presents a  $100k\Omega$  load to the external reference. The internal output buffers allow rail-to-rail operation. An internal voltage reference is available with software selectable options of 2.048V, 2.5V, or 4.096V. The device features a fast 400kHz I2C-compatible interface. The MAX5816 includes a serial-in/parallel-out shift register, internal CODE and DAC registers, a power-on-reset (POR) circuit to initialize the DAC outputs to code zero, and control logic.

#### DAC Outputs (OUT )

The MAX5816 includes internal buffers on all DAC outputs. The internal output buffers provide improved load regulation for the DAC outputs. The output buffers slew at  $1V/\mu s$  (typ) and drive up to  $2k\Omega$  in parallel with 500pF. Under no-load conditions, the output buffers drive from GND to  $V_{DD}$ , subject to offset and gain errors. With a  $2k\Omega$ load to GND, the output buffers drive from GND to within 200mV of  $V_{DD}$ . With a  $2k\Omega$  load to  $V_{DD}$ , the output buffers drive to within 200mV of GND and VDD.

The DAC ideal output voltage is defined by:

$$V_{OUT} = V_{REF} \times \frac{D}{2^N}$$

where D = code loaded into the DAC register, V<sub>RFF</sub> = reference voltage, N = resolution.

#### **Internal Register Structure**

The user interface is separated from the DAC logic to minimize digital feedthrough. Within the serial interface is an input shift register, the contents of which can be routed to control registers, individual, or multiple DACs as determined by the user command.

Within each DAC channel there is a CODE register followed by a DAC latch register (see the Detailed Functional Diagram). The contents of the CODE register hold pending DAC output settings which can later be loaded into the DAC registers. The CODE register can be updated using both CODE and CODE\_LOAD user commands. The contents of the DAC register hold the current DAC output settings. The DAC register can be updated directly from the serial interface using the CODE\_LOAD

commands or can upload the current contents of the CODE register using LOAD commands.

The contents of both CODE and DAC registers are maintained during power-down states, so that when the DACs are powered on, they return to their previously stored output settings. Any CODE or LOAD commands issued during power-down states continue to update the register contents. SW\_CLEAR and SW\_RESET commands (both clear and reset modes) reset the contents of all CODE and DAC registers to their zero-scale defaults.

#### Internal Reference

The MAX5816 includes an internal precision voltage reference that is software selectable to be 2.048V, 2.500V, or 4.096V. When an internal reference is selected, that voltage is available on the REF pin for other external circuitry (see Figure 9) and can drive a  $25k\Omega$  load.

#### External Reference

The external reference input has a typical input impedance of  $100k\Omega$  and accepts an input voltage from +1.24Vto VDD. Connect an external voltage supply between REF and GND to apply an external reference. The MAX5816 powers up and resets to external reference mode. Visit www.maxim-ic.com/products/references for a list of available external voltage-reference devices.

#### I<sup>2</sup>C Serial Interface

The MAX5816 features an I<sup>2</sup>C-/SMBus<sup>™</sup>-compatible. 2-wire serial interface consisting of a serial data line (SDA) and a serial clock line (SCL). SDA and SCL enable communication between the MAX5816 and the master at clock rates up to 400kHz. Figure 1 shows the 2-wire interface timing diagram. The master generates SCL and initiates data transfer on the bus. The master device writes data to the MAX5816 by transmitting the proper slave address followed by the command byte and then the data word. Each transmit sequence is framed by a START (S) or Repeated START (Sr) condition and a STOP (P) condition. Each word transmitted to the MAX5816 is 8 bits long and is followed by an acknowledge clock pulse. A master reading data from the MAX5816 must transmit the proper slave address followed by a series of nine SCL pulses for each byte of data requested. The MAX5816 transmits data on SDA in sync with the master-generated SCL pulses. The master acknowledges receipt of each byte of data. Each read sequence is framed by a START or Repeated START condition, a not acknowledge, and a STOP condition. SDA operates as both an input and

an open-drain output. A pullup resistor, typically  $4.7k\Omega$  is required on SDA. SCL operates only as an input. A pullup resistor, typically  $4.7k\Omega$ , is required on SCL if there are multiple masters on the bus, or if the single master has an open-drain SCL output.

Series resistors in line with SDA and SCL are optional. Series resistors protect the digital inputs of the MAX5816 from high voltage spikes on the bus lines and minimize crosstalk and undershoot of the bus signals. The MAX5816 can accommodate bus voltages higher than Vnn up to a limit of 5.5V; bus voltages lower than Vnn are not recommended and may result in significantly increased interface currents.

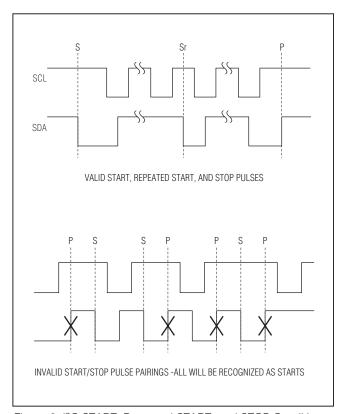

#### I<sup>2</sup>C START and STOP Conditions

SDA and SCL idle high when the bus is not in use. A master initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 2). A START condition from the master signals the beginning of a transmission to the MAX5816. The master terminates transmission and frees the bus, by issuing a STOP condition. The bus remains active if a Repeated START condition is generated instead of a STOP condition.

#### I<sup>2</sup>C Early STOP and **Repeated START Conditions**

The MAX5816 recognizes a STOP condition at any point during data transmission except if the STOP condition occurs in the same high pulse as a START condition. Transmissions ending in an early STOP condition will not impact the internal device settings. If the STOP occurs during a readback byte, the transmission is terminated and a later read mode request will begin transfer of the requested register data from the beginning (this applies to combined format I2C read mode transfers only, interface verification mode transfers will be corrupted). See Figure 2.

#### I<sup>2</sup>C Slave Address

The slave address is defined as the seven most significant bits (MSBs) followed by the R/W bit. See Figure 4. The five most significant bits are 00011 with the 2 LSBs determined by ADDR as shown in Table 1. Setting the R/W bit to 1 configures the MAX5816 for read mode.

Figure 2. I<sup>2</sup>C START, Repeated START, and STOP Conditions

Setting the R/W bit to 0 configures the MAX5816 for write mode. The slave address is the first byte of information sent to the MAX5816 after the START condition.

The MAX5816 has the ability to detect an unconnected state on the ADDR input for additional address flexibility: if leaving the ADDR input unconnected, be certain to minimize all loading on the pin (i.e. provide a landing for the pin, but do not allow any board traces).

Table 1. I<sup>2</sup>C Slave Address LSBs for **TDFN Package**

| ADDR     | A1 | A0 |

|----------|----|----|

| $V_{DD}$ | 0  | 0  |

| N.C.     | 1  | 0  |

| GND      | 1  | 1  |

#### I<sup>2</sup>C Broadcast Address

A broadcast address is provided for the purpose of updating or configuring all MAX5816 devices on a given I2C bus. All MAX5816 devices acknowledge and respond to the broadcast device address 00010000. The devices will respond to the broadcast address, regardless of the state of the address pins. The broadcast mode is intended for use in write mode only (as indicated by  $R/\overline{W} = 0$  in the address given).

#### I<sup>2</sup>C Acknowledge

In write mode, the acknowledge bit (ACK) is a clocked 9th bit that the MAX5816 uses to handshake receipt of each byte of data as shown in Figure 3. The MAX5816 pulls down SDA during the entire master-generated 9th clock pulse if the previous byte is successfully received. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master will retry communication.

In read mode, the master pulls down SDA during the 9th clock cycle to acknowledge receipt of data when the MAX5816 is in read mode. An acknowledge is sent by the master after each read byte to allow data transfer to continue. A not-acknowledge is sent when the master reads the final byte of data from the MAX5816, followed by a STOP condition.

#### I<sup>2</sup>C Command Byte and Data Bytes

A command byte follows the slave address. A command byte is typically followed by two data bytes unless it is the last byte in the transmission. If data bytes follow the command byte, the command byte indicates the address of the register that is to receive the following two data bytes. The data bytes are stored in a temporary register and then transferred to the appropriate register during the ACK periods between bytes. This avoids any glitching or digital feedthrough to the DACs while the interface is active.

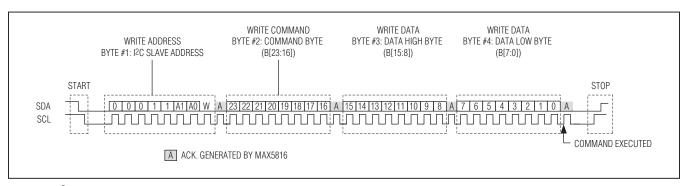

#### I<sup>2</sup>C Write Operations (Standard Protocol)

A master device communicates with the MAX5816 by transmitting the proper slave address followed by command and data words. Each transmit sequence is framed by a START or Repeated START condition and a STOP condition as described above. Each word is 8 bits long and is always followed by an acknowledge clock (ACK) pulse as shown in the Figure 4 and Figure 5. The first byte contains the address of the MAX5816 with  $R/\overline{W} = 0$  to indicate a write. The second byte contains the command (or register) to be written and the third and fourth bytes contain the data to be written. By repeating the command plus data byte pairs (Byte #2 through Byte #4 in Figure 4 and Figure 5), the user can execute multiple command writes using a single I2C write sequence. There is no limit as to how many commands the user can execute with a single write sequence. The MAX5816 supports this capability for all user-accessible write mode commands.

Figure 3. I<sup>2</sup>C Acknowledge

Figure 4. I<sup>2</sup>C Single Register Write Sequence

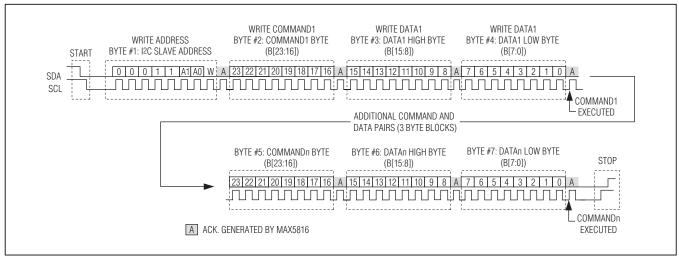

#### I<sup>2</sup>C Write Operation (Multibyte Operation)

The MAX5816 supports a multibyte transfer protocol for some commands. In multibyte mode, once a command is issued (with multibyte bit = 1), that command is continuously executed based on two byte data blocks for the duration I2C operation. Essentially, bytes 1 to 4 are processed normally, but for every two bytes of data provided after byte 4, the originally requested command is executed again with the latest byte pair provided as input data. Multibyte protocol is enforced until a STOP condition (or repeated START) is encountered, this provides a higher speed transfer mode that is useful in servo DAC applications.

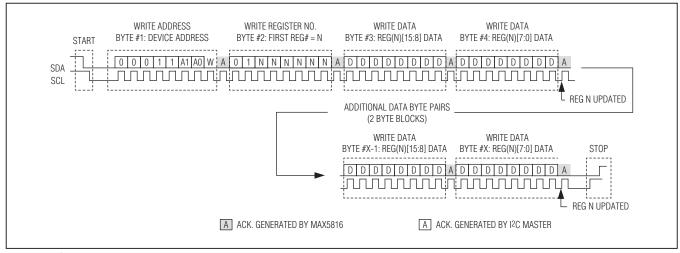

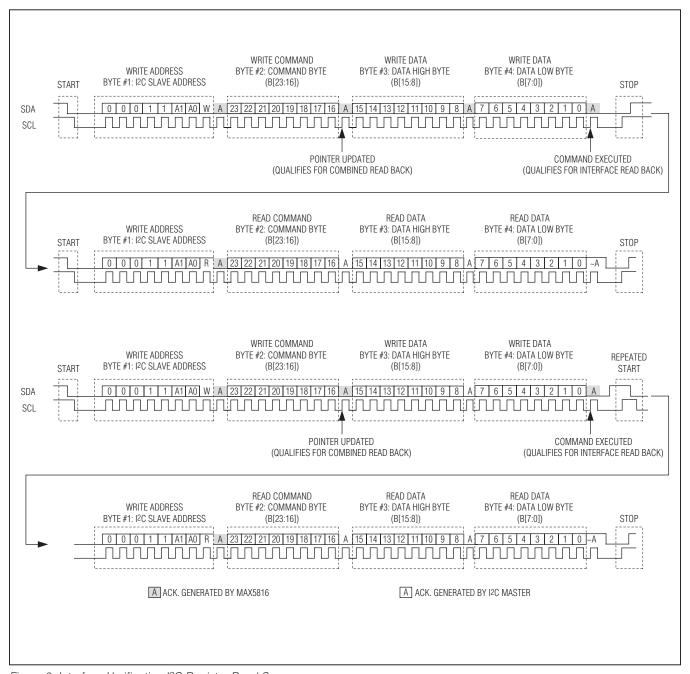

#### Combined Format I<sup>2</sup>C Readback **Operations**

Each readback sequence is framed by a START or Repeated START condition and a STOP condition. Each word is 8 bits long and is followed by an acknowledge clock pulse as shown in Figure 6. The first byte contains the address of the MAX5816 with  $R/\overline{W} = 0$  to indicate a write. The second byte contains the register that is to be read back. There is a Repeated START condition, followed by the device address with  $R/\overline{W} = 1$  to indicate a read and an acknowledge clock. The master has control of the SCL line but the MAX5816 takes over the SDA line. The final two bytes in the frame contain the register data readback followed by a STOP condition. If additional bytes beyond those required to readback the requested data are provided, the MAX5816 will continue to readback ones.

Readback of individual CODE registers is supported for all the user CODE commands. For these commands. which support a DAC address, the requested channel CODE register content will be returned; if all DACs are selected, CODE A content will be returned.

Readback of individual DAC registers is supported for all user LOAD and CODE\_LOAD commands. For these commands, which support a DAC address, the requested DAC register content will be returned. If all DACs are selected, DACA content will be returned.

Modified readback of the POWER register is supported for the POWER command. The power status of each DAC is reported in locations B[3:0], with a 1 indicating the DAC is powered down and a zero indicating the DAC is operational (see Table 2).

Readback of all other registers is not directly supported. All requests to read unsupported registers reads back the device's reference status device ID and revision information in the format is shown in Table 2.

#### Interface Verification I<sup>2</sup>C **Readback Operations**

While the MAX5816 supports standard I<sup>2</sup>C readback of selected registers, it is also capable of functioning in an interface verification mode. This mode is accessed any time a readback operation follows an executed write mode command. In this mode, the last executed threebyte command is read back in its entirety. This behavior allows verification of the interface.

Sample command sequences are shown in Figure 7. The first command transfer is given in write mode with  $R/\overline{W} =$ 0 and must be run to completion to qualify for interface verification readback. There is now a STOP/START pair or Repeated START condition required, followed by the readback transfer with  $R/\overline{W} = 1$  to indicate a read and an acknowledge clock from the MAX5816. The master still has control of the SCL line but the MAX5816 takes over the SDA line. The final three bytes in the frame contain the command and register data written in the first transfer presented for readback, followed by a STOP condition. If additional bytes beyond those required to read back the requested data are provided, the MAX5816 will continue to read back ones.

| Table 2. Standard | l I2C User | <sup>·</sup> Readback | Data |

|-------------------|------------|-----------------------|------|

|-------------------|------------|-----------------------|------|

|    | COM | MAN | D BY | BYTE (REQUEST) READBACK DATA HIGH BYTE READBACK DATA LOW BYTE |    |    |    |     |             |     |      |        |     |    | READBACK DATA HIGH BYTE |        |        |        |       |        |     |     |     |

|----|-----|-----|------|---------------------------------------------------------------|----|----|----|-----|-------------|-----|------|--------|-----|----|-------------------------|--------|--------|--------|-------|--------|-----|-----|-----|

| R7 | R6  | R5  | R4   | R3                                                            | R2 | R1 | R0 | B15 | B14         | B13 | B12  | B11    | B10 | В9 | B8                      | B7     | B6     | B5     | B4    | В3     | B2  | B1  | B0  |

| 0  | Χ   | 0   | 0    | 0                                                             | A2 | A1 | A0 |     | CODEn[11:4] |     |      |        |     |    | (                       | CODE   | n[3:0] |        | 0     | 0      | 0   | 0   |     |

| 0  | Х   | 0   | 0    | 1                                                             | A2 | A1 | A0 |     | DACn[11:4]  |     |      |        |     |    |                         | DACr   | 1[3:0] |        | 0     | 0      | 0   | 0   |     |

| 0  | Х   | 0   | 1    | 0                                                             | A2 | A1 | A0 |     | DACn[11:4]  |     |      |        |     |    | DACr                    | 1[3:0] |        | 0      | 0     | 0      | 0   |     |     |

| 0  | Х   | 0   | 1    | 1                                                             | A2 | A1 | A0 |     |             | [   | DACn | [11:4] |     |    |                         |        | DACr   | 1[3:0] |       | 0      | 0   | 0   | 0   |

| 0  | Х   | 1   | 0    | 0                                                             | X  | Χ  | Χ  | 0   | 0           | 0   | 0    | 0      | 0   | 0  | 0                       | 0      | 0      | 0      | 0     | PWD    | PWC | PWB | PWA |

| 0  | Χ   | 1   | 0    | 1                                                             | Х  | Χ  | Χ  |     |             |     |      |        |     |    |                         |        |        |        | ı     | REV_II | D   | RI  | ΞF  |

| 0  | Х   | 1   | 1    | 0                                                             | Х  | Х  | Х  | 1   | 0           | 0   | 0    | 1      | 0   | 0  | 0                       | 0      | 1      | 0      |       | [2:0]  |     | MC  | DE  |

| 0  | Χ   | 1   | 1    | 1                                                             | Х  | Χ  | Χ  |     |             |     |      |        |     |    |                         |        |        |        | (010) |        | [1  | :0] |     |

Figure 5. Multiple Register Write Sequence (Standard I<sup>2</sup>C Protocol)

Figure 6. I<sup>2</sup>C Multibyte Register Write Sequence (Multibyte Protocol)

Figure 7. Standard I<sup>2</sup>C Register Read Sequence

# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

Figure 8. Interface Verification I<sup>2</sup>C Register Read Sequences

It is not necessary for the write and read mode transfers to occur immediately in sequence. I2C transfers involving other devices do not impact the MAX5816 readback mode. Toggling between readback modes is based on the length of the preceding write mode transfer. Combined format I2C readback operation is resumed if a write command greater than two bytes but less than four bytes is supplied. For commands written using multiple register write sequences, only the last command executed is read back. For each command written, the readback sequence can only be completed one time; partial and/or multiple attempts to readback executed in succession will not yield usable data.

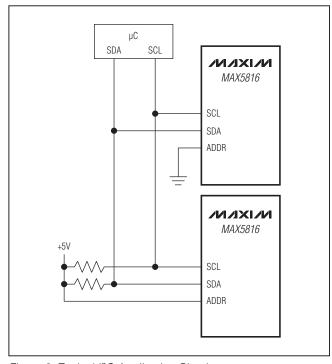

#### I<sup>2</sup>C Compatibility

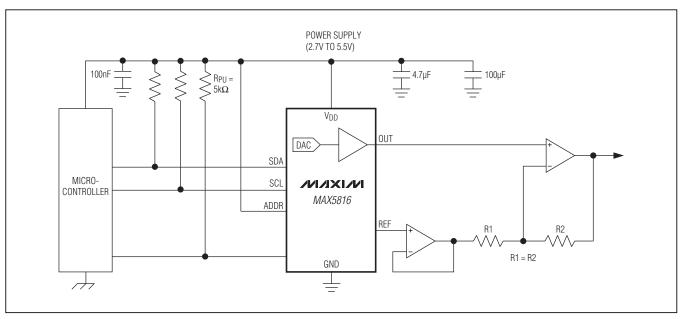

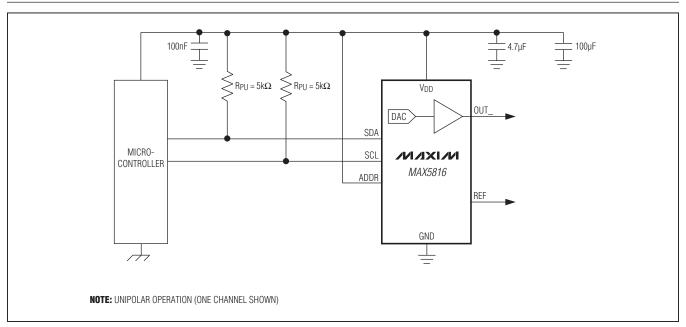

The MAX5816 is fully compatible with existing I2C systems. SCL and SDA are high-impedance inputs; SDA has an open drain which pulls the data line low to transmit data or ACK pulses. Figure 9 shows a typical I2C application.

#### I<sup>2</sup>C User-Command Register Map

This section lists the user accessible commands and registers for the MAX5816.

Table 3 provides detailed information about the Command Registers.

Figure 9. Typical I<sup>2</sup>C Application Circuit

# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

|                                            | DESCRIPTION         |              | Writes data<br>to the selected<br>CODE<br>register(s). | Transfers data from the selected CODE registers to the selected DAC register(s). | Simultaneously writes data to the selected CODE register(s) while updating all DAC registers. | Simultaneously writes data to the selected CODE register(s) while updating selected DAC register(s). |  |  |  |

|--------------------------------------------|---------------------|--------------|--------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|

|                                            | B0                  |              | ×                                                      | ×                                                                                | ×                                                                                             | ×                                                                                                    |  |  |  |

|                                            | B1                  |              | ×                                                      | ×                                                                                | ×                                                                                             | ×                                                                                                    |  |  |  |

|                                            | B2                  |              | ×                                                      | ×                                                                                | ×                                                                                             | ×                                                                                                    |  |  |  |

|                                            | B3                  |              | ×                                                      | ×                                                                                | ×                                                                                             | ×                                                                                                    |  |  |  |

|                                            | B4                  |              | H                                                      | ×                                                                                | DATA                                                                                          | H                                                                                                    |  |  |  |

|                                            | B5                  |              | GISTE<br>[3:0]                                         | ×                                                                                | STER (                                                                                        | EGISTE<br>[3:0]                                                                                      |  |  |  |

|                                            | B6                  |              | CODE REGISTER<br>DATA [3:0]                            | ×                                                                                | CODE REGISTER DATA<br>[3:0]                                                                   | CODE REGISTER<br>DATA [3:0]                                                                          |  |  |  |

|                                            | B7                  |              | 00                                                     | ×                                                                                | CODE                                                                                          | 00                                                                                                   |  |  |  |

|                                            | B8                  |              |                                                        | ×                                                                                |                                                                                               |                                                                                                      |  |  |  |

|                                            | B9                  |              |                                                        | ×                                                                                |                                                                                               |                                                                                                      |  |  |  |

|                                            | B10                 |              | H.                                                     | ×                                                                                | H.                                                                                            | E.                                                                                                   |  |  |  |

|                                            | B11                 |              | CODE REGISTER<br>DATA [11:4]                           | ×                                                                                | CODE REGISTER<br>DATA [11:4]                                                                  | CODE REGISTER<br>DATA [11:4]                                                                         |  |  |  |

|                                            | B12                 |              | ODE R                                                  | ODE R                                                                            |                                                                                               |                                                                                                      |  |  |  |

|                                            | B13                 |              | ŏ                                                      | ŏ                                                                                |                                                                                               |                                                                                                      |  |  |  |

|                                            | B14                 |              |                                                        |                                                                                  |                                                                                               |                                                                                                      |  |  |  |

| _                                          | B16 B15 B14         |              |                                                        |                                                                                  |                                                                                               |                                                                                                      |  |  |  |

| nary                                       | B16                 |              | SS                                                     | SS                                                                               | SS                                                                                            | SS                                                                                                   |  |  |  |

| umr                                        | 3 B17               |              | DAC                                                    | DAC<br>ADDRESS                                                                   | DAC                                                                                           | DAC                                                                                                  |  |  |  |

| S                                          | B19 B18             |              | ∢                                                      | ∢                                                                                | ∢                                                                                             | ∢                                                                                                    |  |  |  |

| and                                        | <b>-</b>            |              | 0                                                      | -                                                                                | 0                                                                                             | -                                                                                                    |  |  |  |

| ш                                          | B20                 |              | 0                                                      | 0                                                                                | <del>-</del>                                                                                  | -                                                                                                    |  |  |  |

| S                                          | B21                 |              | 0                                                      | 0                                                                                | 0                                                                                             | 0                                                                                                    |  |  |  |

| 2C                                         | 3 B22               | SQI          | 0                                                      | 0                                                                                | 0                                                                                             | 0                                                                                                    |  |  |  |

| ა<br>                                      | ) B23               | IMAN         | 0                                                      | 0                                                                                | 0                                                                                             | 0                                                                                                    |  |  |  |

| Table 3. I <sup>2</sup> C Commands Summary | COMMAND B23 B22 B21 | DAC COMMANDS | CODEn                                                  | LOADn                                                                            | CODEn_<br>LOAD_<br>ALL                                                                        | CODEn_                                                                                               |  |  |  |

# Ultra-Small, Quad-Channel, 12-Bit Buffered Output DAC with Internal Reference and I<sup>2</sup>C Interface

| DESCRIPTION                 |                        | Sets the Power Mode of the selected DACs (DACs selected out a 1 in the corresponding DACn bit are updated, DACs with a 0 in the corresponding DACn bit are not impacted). | Executes a software reset (all registers returned to their default values) or clear (all CODE and DAC registers cleared to their default values). | Sets the DAC Latch Mode of the corresponding DAC; 0 = DAC latch is LOAD controlled 1 = DAC latch is transparent. | Sets the reference operating mode. REF Power (B2): 0 = Internal reference is only powered if at least one DAC is powered 1 = Internal reference is always powered. |

|-----------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B0                          |                        | A DAG                                                                                                                                                                     | 0 =<br>CLR<br>1 =<br>RST                                                                                                                          | A DAG                                                                                                            | REF Mode<br>00 = EXT<br>01 = 2.5V<br>10 = 2.0V<br>11 = 4.1V                                                                                                        |

| 19                          |                        | DAC B                                                                                                                                                                     | ×                                                                                                                                                 | DAC B                                                                                                            | REF   00 = 01 = 10 = 11 = 11 = 11 = 11 = 11                                                                                                                        |

| B2                          |                        | DAC C                                                                                                                                                                     | ×                                                                                                                                                 | DAC C                                                                                                            | REF Pow-er Mode                                                                                                                                                    |

| B3                          |                        | DAC D                                                                                                                                                                     | ×                                                                                                                                                 | DAC D                                                                                                            | ×                                                                                                                                                                  |

| B4                          |                        | Power Mode 00 = 10   10   10   10   10   10   10                                                                                                                          | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B5                          |                        | Power Mode $00 = 0$ Normal $01 = PD$ $1k\Omega$ $10 = PD$ $100k\Omega$ $11 = PD$                                                                                          | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B6                          |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B7                          |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B8                          |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B9                          |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B10                         |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B11                         |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B12                         |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B13                         |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B16 B15 B14                 |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B15                         |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B16                         |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |

| B17                         |                        | ×                                                                                                                                                                         | ×                                                                                                                                                 | ×                                                                                                                | ×                                                                                                                                                                  |