#### **MAX5855**

# 16-Bit, 4.9Gsps Wideband Interpolating and Modulating RF DAC with JESD204B Interface

### **General Description**

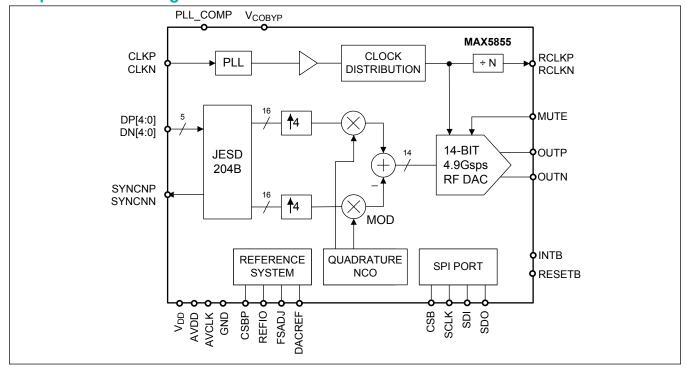

The MAX5855 high-performance, interpolating and modulating, 16-bit, 4.9Gsps RF DAC can directly synthesize up to 1000MHz of instantaneous bandwidth from DC to frequencies greater than 2.45GHz. The device is optimized for cable access and digital video broadcast applications and meets spectral emission requirements for a broad set of radio transmitters and modulators including DOC-SIS 3.1/3.0, DVB-C/C2, DVB-T2, DVB-S2X, ISDB-T, and EPoC.

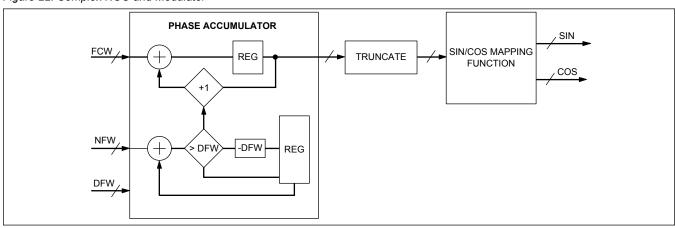

The device integrates interpolation filters, a digital quadrature modulator, a numerically controlled oscillator (NCO), clock multiplying PLL + VCO and a 14-bit RF DAC core. The 4x linear phase interpolation filter simplifies reconstruction filtering, while enhancing passband dynamic performance, and reducing the input data bandwidth required from an FPGA. The NCO allows for fully agile modulation of the input baseband signal for direct RF synthesis.

The MAX5855 input interface accepts 16-bit input data by way of a five-lane, JESD204B SerDes data input interface that is Subclass-0 compliant and operates at a data rate of 9.8304Gbps.

The MAX5855 clock input has a flexible interface that accepts a differential sine-wave or square-wave reference input clock signal at 245.75MHz, 491.52MHz, or 983.04MHz. A clock multiplying PLL and VCO is used to internally generate the 4.9152GHz sampling clock from the reference clock. The device provides a divided reference clock output to ensure synchronization between the data source and the DAC.

The integrated RF DAC uses a differential current-steering architecture that includes a differential  $50\Omega$  internal termination and can produce a 3dBm full-scale output signal level on a  $50\Omega$  external load. Operating from 1.0V and 1.8V power supplies, the device consumes 2.7W at 4.9Gsps. The device is offered in a compact 144-pin, 10mm x 10mm, FCCSP package and is specified for the extended industrial temperature range (-40°C to +85°C).

### **Applications**

- DOCSIS 3.1/3.0 Remote PHY and CCAP

- Digital Video Broadcast Modulators

- DVB-C/C2/DVB-T2/DVB-S2X/ISDB-T

- Ethernet PON Over Coax (EPoC)

- Point-to-Point Wireless

- Instrumentation

#### **Benefits and Features**

- Simplifies RF Design and Enables New Communication Architectures

- Eliminates I/Q Imbalance and LO Feedthrough

- · Enables Multi-Band RF Modulation

- Direct RF Synthesis of 1GHz Bandwidth

- 4.9152Gsps DAC Output Update Rate

- · High-Performance 14-Bit RF DAC Core

- Digital Baseband I/Q with 4x Interpolation

- Digital Quadrature Modulator + NCO for Full Agility

- Sub-1Hz NCO Resolution

- Integrated Clock Multiplying PLL + VCO

- Flexible and Configurable

- 5-Lane JESD204B Input Data Interface

- · Subclass-0 Compliant

- · 9.8304Gbps Per Lane

- · Divided Reference Clock Output

- · SPI Interface for Device Configuration

Ordering Information appears at end of data sheet.

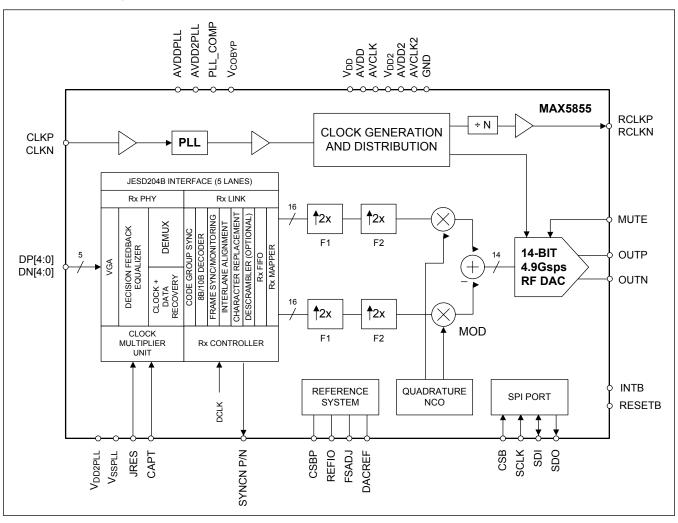

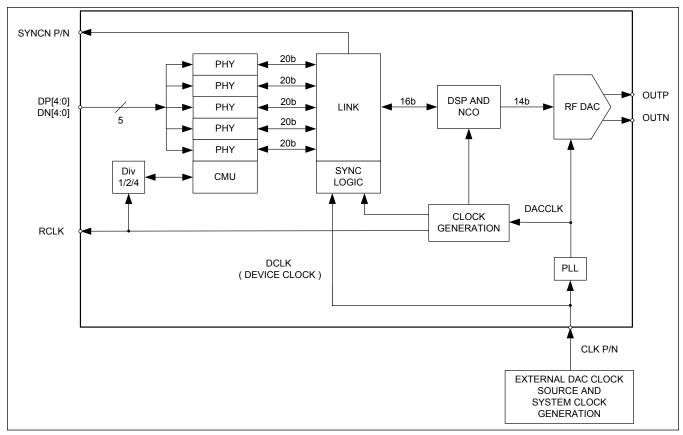

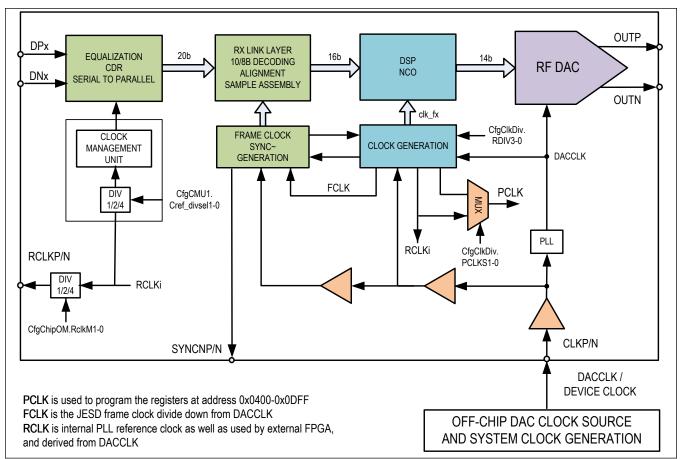

## **Simplified Block Diagram**

### **TABLE OF CONTENTS**

| General Description                               | 1  |

|---------------------------------------------------|----|

| Applications                                      | 1  |

| Benefits and Features                             | 1  |

| Simplified Block Diagram                          | 2  |

| Absolute Maximum Ratings                          | 7  |

| Package Information                               | 7  |

| 144 FCCSP                                         | 7  |

| Electrical Characteristics                        | 8  |

| Typical Operating Characteristics                 | 15 |

| Pin Configuration                                 | 17 |

| Pin Description                                   | 18 |

| Functional Diagrams                               | 20 |

| Detailed Description                              | 21 |

| Supported DAC Update Rate and JESD204B Data Rates | 22 |

| JESD204B Interface                                | 22 |

| JESD204B Data Interface Features                  | 23 |

| Mapping of Physical to Logical Channels           | 24 |

| High-Speed Input Receiver (Rx)                    | 24 |

| JESD204B Receiver Equalization                    | 26 |

| Lane Skew Requirement                             | 27 |

| Link Layer (LINK)                                 | 27 |

| Interface Timing for Subclass-0                   | 28 |

| Serial Control Interface                          | 29 |

| Interrupt Control                                 | 34 |

| Digital Control Pins                              | 35 |

| Frequency Planning                                | 36 |

| Quadrature Modulator and NCO                      | 37 |

| Analog Interface                                  | 40 |

| Reference Interface                               | 40 |

| Analog Output                                     | 41 |

| Clock Interface                                   | 42 |

| Clock Subsystem                                   | 42 |

| Overview                                          | 42 |

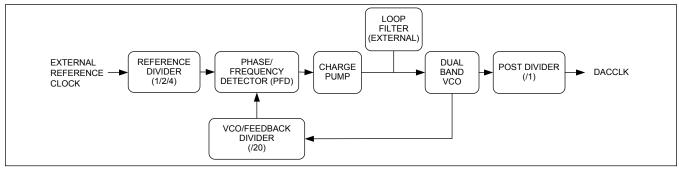

| DAC Clock PLL                                     | 43 |

| VCO Band Select                                   | 44 |

| Lock Detect                                       | 44 |

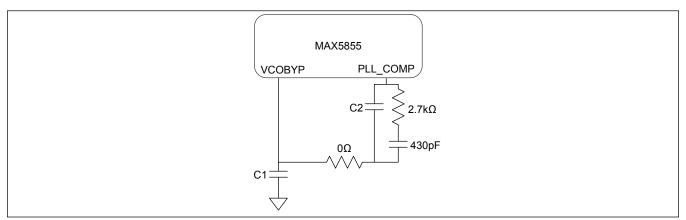

| PLL External Components                           | 44 |

## TABLE OF CONTENTS (CONTINUED)

| RCLK Description and Use                        | 44  |

|-------------------------------------------------|-----|

| Interpolation Filters                           | 45  |

| Register Definition and Description.            | 46  |

| SPI to PCLK Frequency Ratio                     | 46  |

| SPI to f <sub>DAC</sub> Frequency Ratio         | 46  |

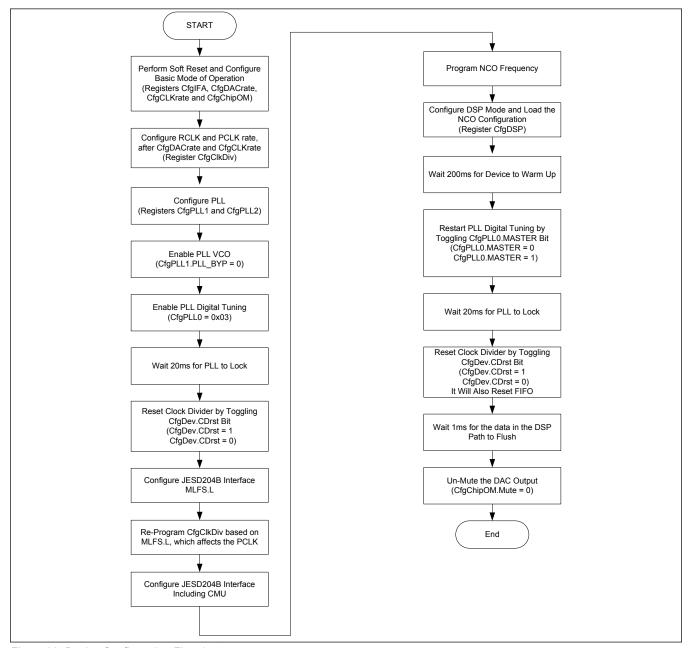

| Device Configuration                            | 46  |

| Frequency Settings and Configuration            | 48  |

| Configuration Script Tool                       | 49  |

| Register Map                                    | 51  |

| MAX5855                                         | 51  |

| Register Details                                | 64  |

| Applications Information                        | 122 |

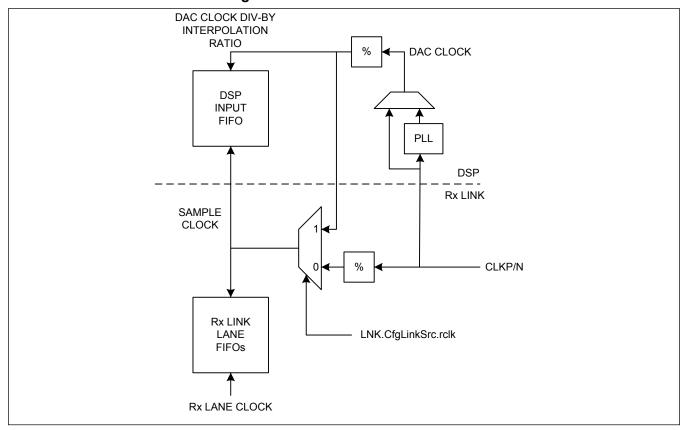

| JESD204B LINK and DSP Clocking                  | 122 |

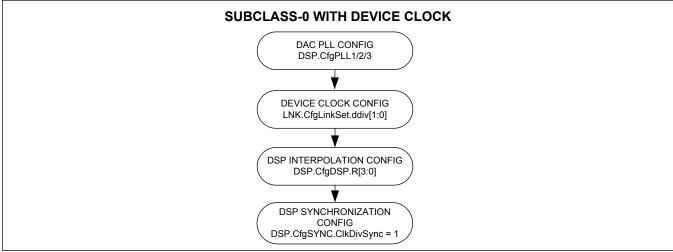

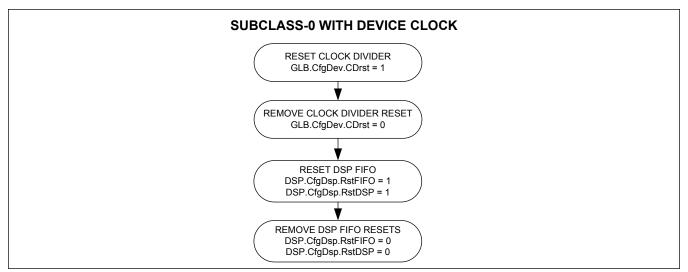

| Subclass-0 with Device Clock                    | 122 |

| Typical Configuration                           | 123 |

| Applications Guidelines                         | 124 |

| Power Sequence                                  | 124 |

| Power Supply AVCLK                              | 124 |

| Power-On RESETB and SPI Configuration           | 124 |

| Delay Time T <sub>D-DivRst</sub> Estimation     | 125 |

| Pin DACREF Consideration                        | 125 |

| DAC PLL Consideration                           | 125 |

| Pin SDO Consideration                           | 125 |

| Clock Requirement                               | 125 |

| NCO Frequency                                   | 126 |

| Latency                                         | 126 |

| PRBS Sequence                                   | 126 |

| DAC Output Impedance Model and Matching Network | 126 |

| Thermal Considerations                          | 127 |

| Ordering Information                            | 127 |

| Revision History                                | 128 |

| LI | ST | ГΟ | F | FI | GI | UI | RI | ES |

|----|----|----|---|----|----|----|----|----|

|    |    |    |   |    |    |    |    |    |

| 2.01 01 1100 110                                                                                     |     |

|------------------------------------------------------------------------------------------------------|-----|

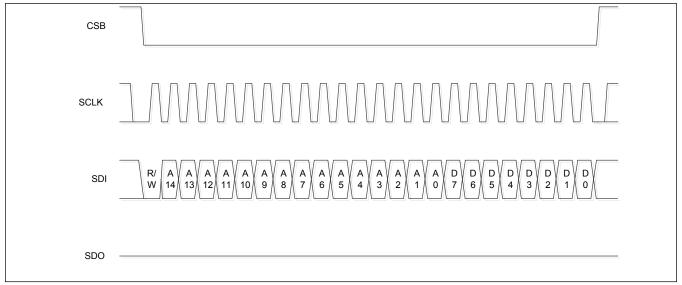

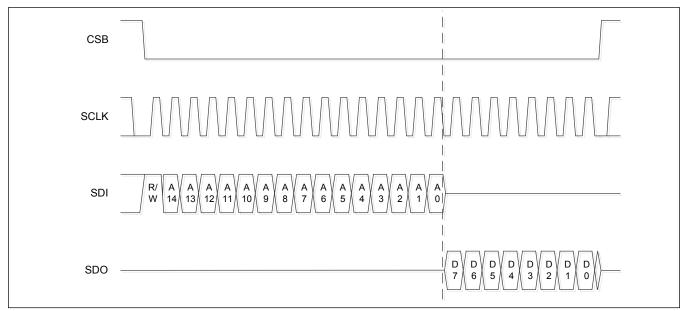

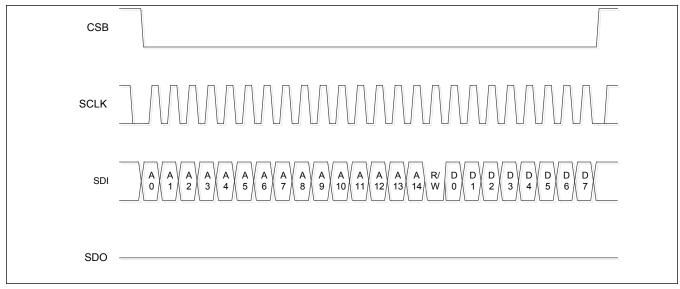

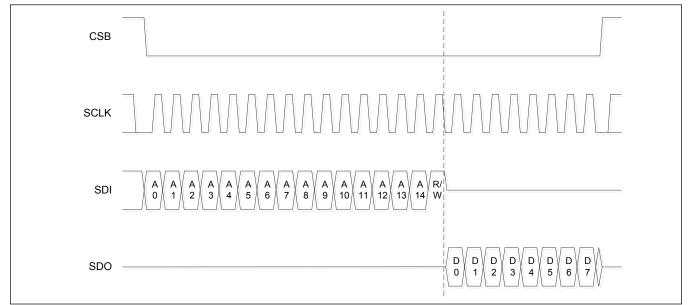

| Figure 1. Serial Interface Timing Diagram                                                            | 14  |

| Figure 2. Simplified Diagram of JESD204B Internal to MAX5855                                         | 22  |

| Figure 3. Octet-To-Sample Conversion                                                                 | 24  |

| Figure 4. JESD204B Rx Physical Layer, Simplified Block Diagram                                       | 24  |

| Figure 5. VGA Gain Range                                                                             | 25  |

| Figure 6. Receiver Equalization Eye Diagram Before and After Lane Training                           | 26  |

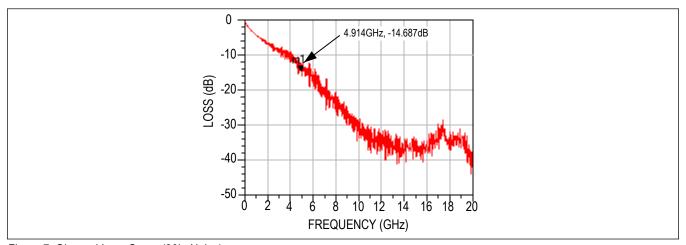

| Figure 7. Channel Loss Curve (30in Nelco)                                                            | 26  |

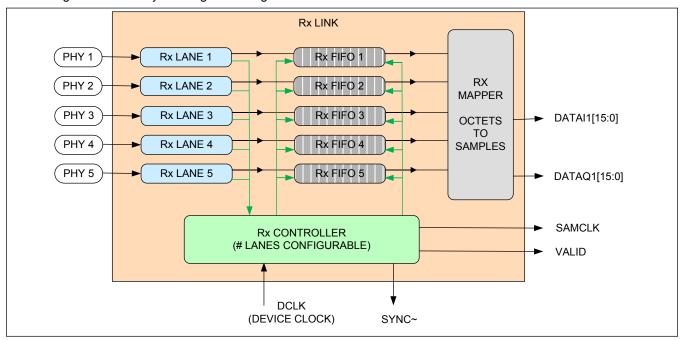

| Figure 8. JESD204B Receive Link Layer Block Diagram                                                  | 27  |

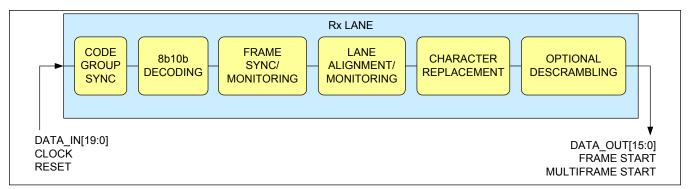

| Figure 9. JESD204B Receive Lane Block Diagram                                                        | 28  |

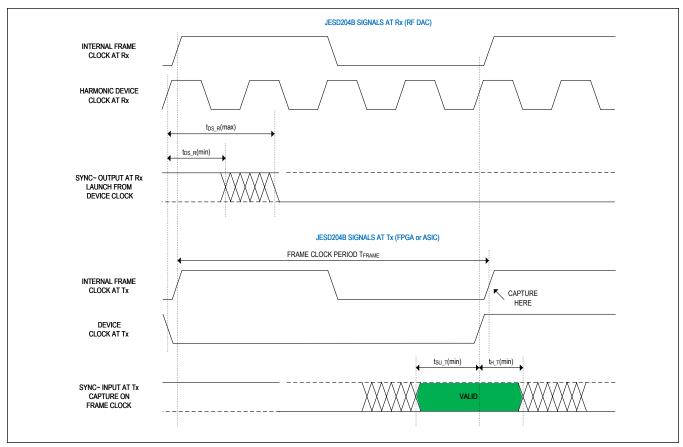

| Figure 10. Interface Timing for Subclass-0                                                           | 29  |

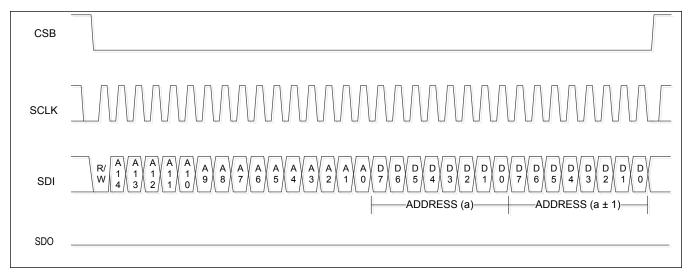

| Figure 11. SPI Single Write with MSB-First Format                                                    | 30  |

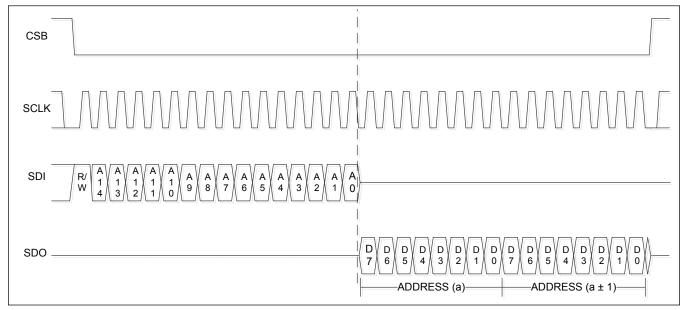

| Figure 12. SPI Single Read with MSB-First Format                                                     | 30  |

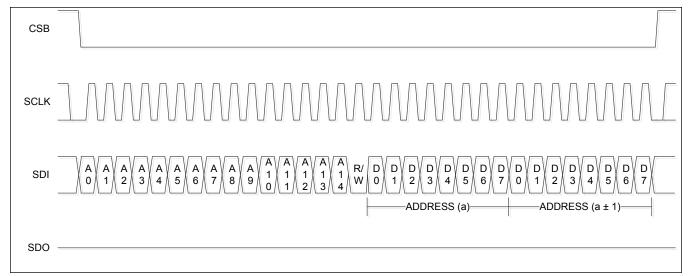

| Figure 13. SPI Single Write with LSB-First Format                                                    | 31  |

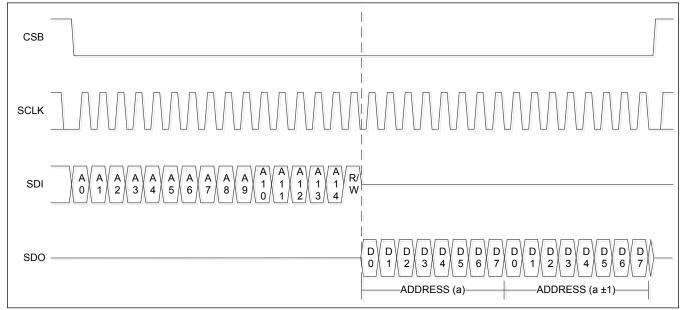

| Figure 14. SPI Single Read with LSB-First Format                                                     | 31  |

| Figure 15. SPI Burst Write with MSB-First Format                                                     | 32  |

| Figure 16. SPI Burst Read with MSB-First Format                                                      | 32  |

| Figure 17. SPI Burst Write with LSB-First Format                                                     | 33  |

| Figure 18. SPI Burst Read with LSB-First Format                                                      | 33  |

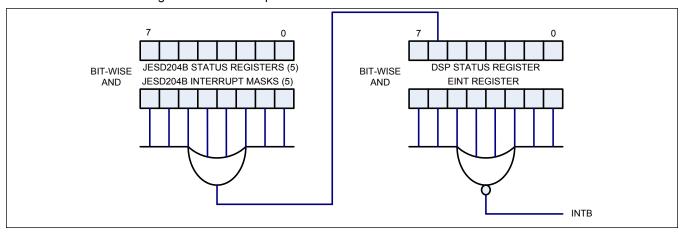

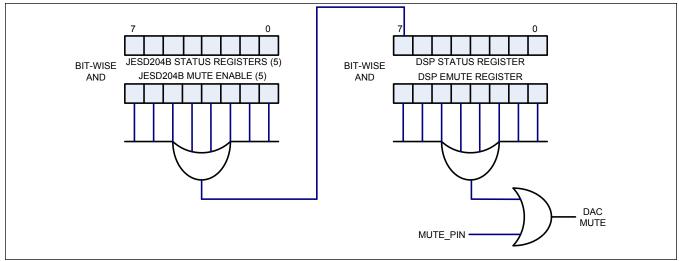

| Figure 19. Interrupt Tree                                                                            | 34  |

| Figure 20. Mute Generation Logic                                                                     | 35  |

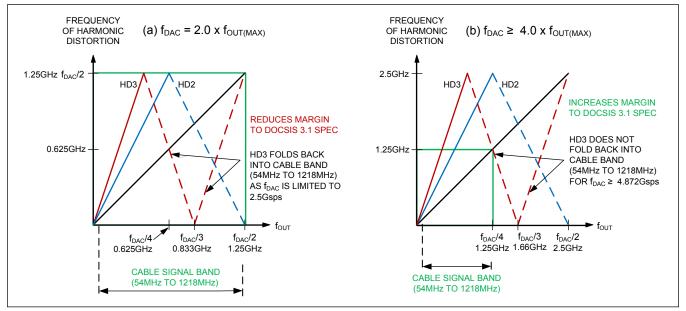

| Figure 21. Effect of DAC Update Rate on Folded HD2 and HD3                                           | 36  |

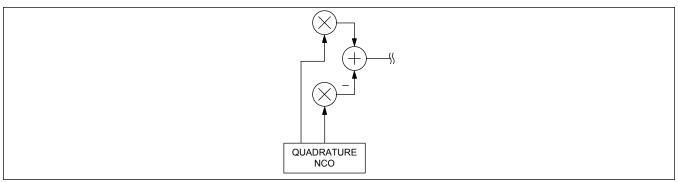

| Figure 22. Complex NCO and Modulator                                                                 | 39  |

| Figure 23. NCO Block Diagram                                                                         | 39  |

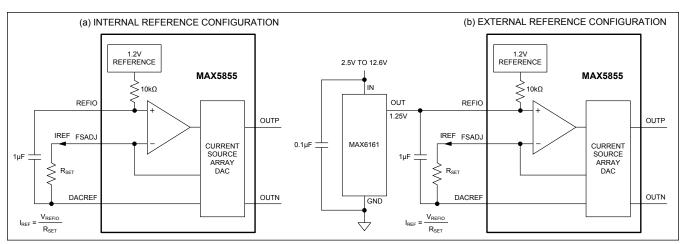

| Figure 24. Setting the DAC Output Full-Scale Using an (a) Internal or (b) External Reference Voltage | 41  |

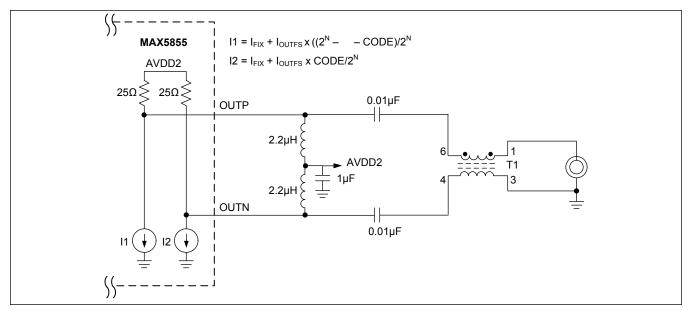

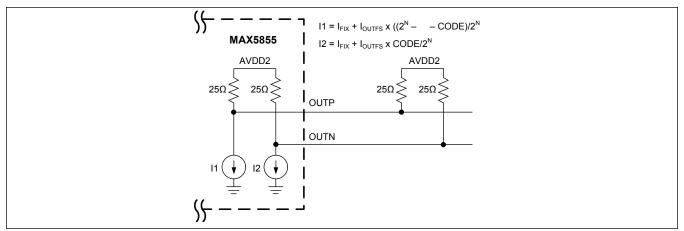

| Figure 25. Typical DAC Output Configuration                                                          | 41  |

| Figure 26. Output Configuration for Low-Frequency Operation                                          | 42  |

| Figure 27. MAX5855 Clock Subsystem                                                                   | 43  |

| Figure 28. DAC Clock PLL Functional Block Diagram                                                    | 43  |

| Figure 29. DAC Clock PLL External Components                                                         | 44  |

| Figure 30. Device Configuration Flowchart                                                            | 47  |

| Figure 31. Rx LINK and DSP Clocking                                                                  | 122 |

| Figure 32. DAC Power-Up Sequence                                                                     | 123 |

| Figure 33. DAC Configuration Sequence                                                                | 123 |

| Figure 34 DAC Reset Sequence                                                                         | 124 |

## MAX5855

# 16-Bit, 4.9Gsps Wideband Interpolating and Modulating RF DAC with JESD204B Interface

| LIST OF TABLES                                                                          |    |

|-----------------------------------------------------------------------------------------|----|

| Table 1. Complex I/Q Base Band Up-Conversion                                            | 22 |

| Table 2. Lane Rate                                                                      | 22 |

| Table 3. Status Register Bits                                                           | 34 |

| Table 4. Digital Filter Coefficients                                                    | 45 |

| Table 5. Frequency Planning and Configuration with CLKP/N Used as JESD204B Device Clock | 48 |

| Table 6. Configuration Input Parameters                                                 | 49 |

## **Absolute Maximum Ratings**

| VDD2, AVCLK2, AVDD2, AVDD2PLL, VDD2PLL0.3V to +2.1V OUTP, OUTN0.3V to (V <sub>AVDD2</sub> + 0.5)V MUTE, RESETB, CSB, SCLK, SDO, SDI, INTB,TDA0.3V to (V <sub>VDD2</sub> + 0.3, MAX 2.1)V | VSSPLL, TDC, DACREF $(V_{GND} - 0.3)V$ to $(V_{GND} + 0.3)V$ VDD, AVDD, AVCLK, AVDDPLL0.3V to +1.2V REFIO, FSADJ, CSBP0.3V to $(V_{AVDD2} + 0.3, MAX\ 2.1)V$ CLKP, CLKN0.3V to $(V_{AVDDPLL} + 0.3, MAX\ 1.2)V$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TESTP, TESTN, SYNCNP, SYNCNN, RCLKP, RCLKN0.3V to (V <sub>VDD2</sub> + 0.3, MAX 2.1)V                                                                                                    | SDO, INTB Maximum Continuous Current8mA Continuous Power Dissipation (T <sub>A</sub> = +85°C)4.0W                                                                                                               |

| DP0, DN0, DP1, DN1, DP2, DN2, DP3, DN3, DP4, DN4 -0.3V to                                                                                                                                | Thermal Characteristics                                                                                                                                                                                         |

| $(V_{VDD2} + 0.3, MAX 1.6)V$<br>JRES, CAPT, TESTEN $(V_{VSSPLI} - 0.3)V$ to $(V_{VDD2PLI} + 0.3,$                                                                                        | Operating Temperature Range (T <sub>A</sub> )40°C to +85°C<br>Operating Junction Temperature (T <sub>I</sub> )+110°C                                                                                            |

| MAX 2.1)V                                                                                                                                                                                | Maximum Junction Temperature+150°C                                                                                                                                                                              |

| VCOBYP0.3V to (V <sub>AVCLK2</sub> + 0.3, MAX 2.1)V                                                                                                                                      | Storage Temperature Range60°C to +150°C                                                                                                                                                                         |

| PLLCOMP0.3V to (V <sub>AVDD2PLL</sub> + 0.3, MAX 2.1)V                                                                                                                                   | Soldering Temperature (reflow)+260°C                                                                                                                                                                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 144 FCCSP

| Package Code                                           | X14400F+1      |

|--------------------------------------------------------|----------------|

| Outline Number                                         | <u>21-0732</u> |

| Land Pattern Number                                    | <u>90-0289</u> |

| Thermal Resistance, Four-Layer Board:                  |                |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 16.2°C/W       |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 2.5°C/W        |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

$(V_{DD} = V_{AVCLK} = V_{AVDD} = V_{AVDDPLL} = 1.0V, \ V_{DD2} = V_{AVCLK2} = V_{AVDD2} = V_{AVDD2PLL} = V_{DD2PLL} = 1.8V, \ P_{CLK} = 0dBm, \ f_{CLK} = 983.04MHz, \ f_{DAC} = 4915.2Msps, \ 4x \ interpolation, 5-lanes, 9830.4Mbps per lane, external reference at 1.206V, R_{SET} = 965\Omega \ between FSADJ \ and DACREF, I_{OUTFS} = 40mA, output \ is 50\Omega \ double-terminated \ and \ transformer \ coupled \ (see \ Figure 25), PLL \ on. \ T_A \ge -40^{\circ}C$  and  $T_J \le +110^{\circ}C$ , unless otherwise noted. Typical values are at  $T_J = +65 \pm 15^{\circ}C$ . (Note 1))

| PARAMETER                                                                                   | SYMBOL             | COND                                                                                  | ITIONS                       | MIN TYP                     | MAX    | UNITS |

|---------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------|------------------------------|-----------------------------|--------|-------|

| STATIC PERFORMANCE                                                                          | <u> </u>           |                                                                                       |                              |                             |        | •     |

| Input Data Word Width                                                                       | N                  |                                                                                       |                              | 16                          |        | Bits  |

| DAC Resolution                                                                              |                    |                                                                                       |                              | 14                          |        | Bits  |

| Differential Non-<br>Linearity                                                              | DNL                | Figure 26                                                                             | igure 26                     |                             |        | LSB   |

| Integral Non-Linearity                                                                      | INL                | Figure 26                                                                             |                              | ±3                          |        | LSB   |

| Offset Voltage Error                                                                        | os                 |                                                                                       |                              | 0.003                       |        | %FS   |

| Minimum Full-Scale<br>Output Current                                                        | loutfs             |                                                                                       |                              | 10                          |        | mA    |

| Maximum Full-Scale<br>Output Current                                                        | loutes             |                                                                                       |                              | 40                          |        | mA    |

| Output-Voltage Gain<br>Error                                                                | GE <sub>FS</sub>   | f <sub>OUT</sub> = DC, <u>Figure 2</u>                                                | <u>6</u>                     | ±3                          |        | %FS   |

| Maximum Output<br>Compliance                                                                |                    |                                                                                       |                              | V <sub>AVDD2</sub><br>+ 0.4 |        | V     |

| Minimum Output<br>Compliance                                                                |                    |                                                                                       |                              | V <sub>AVDD2</sub><br>- 0.4 |        | V     |

| Output Resistance                                                                           | R <sub>OUT</sub>   | Differential DAC output resistance                                                    |                              | 50                          |        | Ω     |

| DYNAMIC PERFORMAN                                                                           | CE                 |                                                                                       |                              |                             |        |       |

| DAC Sample Rate                                                                             | f <sub>DAC</sub>   |                                                                                       |                              |                             | 4915.2 | Msps  |

| Adjusted DAC Update Rate                                                                    | AUR <sub>DAC</sub> | (Note 2)                                                                              |                              |                             | 1228.8 | Msps  |

| Maximum Input Sample Rate                                                                   | f <sub>S_IN</sub>  | For the complex I/Q                                                                   | dataset                      | 1228.8                      |        | MHz   |

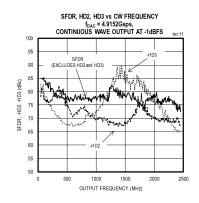

|                                                                                             |                    |                                                                                       | f <sub>OUT</sub> = 500MHz    | 73                          |        |       |

| SFDR to Nyquist                                                                             | SFDR               | CW tone, -1dBFS                                                                       | f <sub>OUT</sub> = 1000MHz   | 74                          |        | dB    |

|                                                                                             |                    |                                                                                       | f <sub>OUT</sub> = 1500MHz   | 69                          |        |       |

| Maximum HD2, HD3,<br>f <sub>DAC</sub> /2-f <sub>OUT</sub> , Measured<br>in 1st Nyquist Zone |                    | CW tone, -3dBFS                                                                       | f <sub>OUT</sub> = 1842.5MHz | -71                         |        | dBc   |

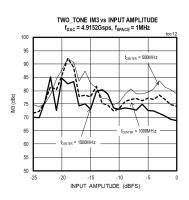

| Intermodulation                                                                             | IMD                | Two-tone signal,<br>$f_{DAC}$ = 4.9152GHz,<br>$f_1$ = 1842MHz and<br>$f_2$ = 1843MHz  | Average total power -15dBFS  | -74                         |        | dBc   |

| Distortion                                                                                  | טואוו              | Two-tone signal,<br>$f_{DAC}$ = 4.9152GHz,<br>$f_1$ = 1842MHz, and<br>$f_2$ = 1843MHz | Average total power -33dBFS  | -80                         |        | dBFS  |

## **Electrical Characteristics (continued)**

$(V_{DD} = V_{AVCLK} = V_{AVDD} = V_{AVDDPLL} = 1.0V, \ V_{DD2} = V_{AVCLK2} = V_{AVDD2} = V_{AVDD2PLL} = V_{DD2PLL} = 1.8V, \ P_{CLK} = 0dBm, \ f_{CLK} = 983.04MHz, \ f_{DAC} = 4915.2Msps, \ 4x \ interpolation, 5-lanes, 9830.4Mbps per lane, external reference at 1.206V, R_{SET} = 965\Omega \ between FSADJ \ and DACREF, I_{OUTFS} = 40mA, output \ is 50\Omega \ double-terminated \ and \ transformer \ coupled \ (see \ Figure 25), \ PLL \ on. \ T_A \ge -40^{\circ}C$  and  $T_J \le +110^{\circ}C$ , unless otherwise noted. Typical values are at  $T_J = +65 \pm 15^{\circ}C$ . (Note 1))

| PARAMETER                                                                          | SYMBOL                                       | COND                                                                 | ITIONS                                      | MIN TYP | MAX   | UNITS  |  |

|------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------|---------------------------------------------|---------|-------|--------|--|

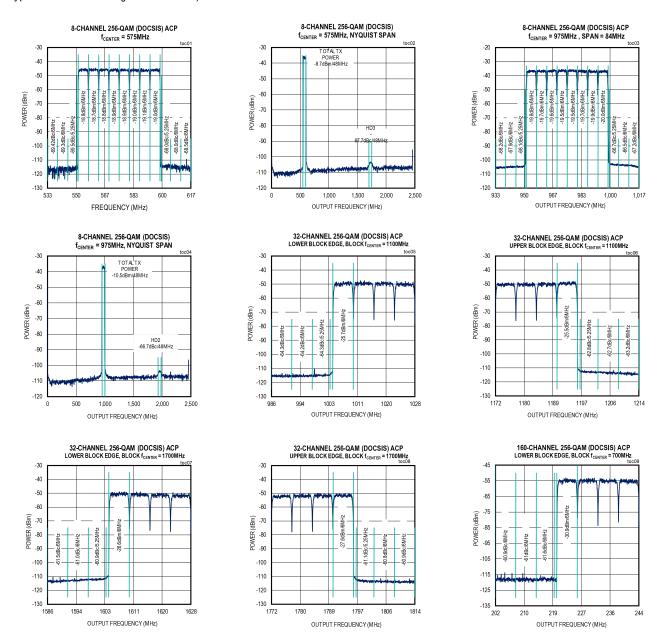

|                                                                                    |                                              |                                                                      | Adjacent channel                            | -69.8   | -62.9 |        |  |

|                                                                                    |                                              | f <sub>OUT</sub> = 575MHz<br>(Note 3, Note 4)                        | Next-adjacent channel                       | -70.5   | -63.1 |        |  |

|                                                                                    |                                              | (Note o, Note 1)                                                     | Third-adjacent channel                      | -70.9   | -64.0 |        |  |

| Out-of-Band Noise and<br>Spurious, Eight 6MHz<br>256-QAM Carriers (Note            | ACPR                                         | f <sub>OUT</sub> = 575MHz<br>(Note 3)                                | Noise in any other channel                  | -65.4   |       | dBc    |  |

|                                                                                    | ACPR                                         |                                                                      | Adjacent channel                            | -67.4   |       | UBC    |  |

| 5)                                                                                 |                                              | f <sub>OUT</sub> = 975MHz,                                           | Next-adjacent channel                       | -67.9   |       |        |  |

|                                                                                    |                                              | Average Total<br>Power =<br>-12dBFS (Note 6)                         | Third-adjacent channel                      | -68.5   |       |        |  |

|                                                                                    |                                              | ,                                                                    | Noise in any other channel                  | -63.8   |       |        |  |

|                                                                                    |                                              |                                                                      | Adjacent channel                            | -64.4   |       |        |  |

| Out-of-Band Noise and<br>Spurious, Thirty Two<br>6MHz 256-QAM<br>Carriers (Note 5) | f <sub>OUT</sub> = 1100MHz,<br>Average Total | Next-adjacent channel                                                | -64.1                                       |         |       |        |  |

|                                                                                    | ACPR                                         | ACPR Power = -15dBFS (Note 6)                                        | Third-adjacent channel                      | -64.1   |       | dBc    |  |

| , ,                                                                                |                                              |                                                                      | Noise in any other channel                  | -57.3   |       |        |  |

| Harmonic Distortion,<br>Four 6MHz 256-QAM                                          | Пр                                           | f <sub>OUT</sub> = 575MHz,<br>Average Total                          | Second Harmonic<br>Distortion               | -66.8   | -55.4 | - dBc  |  |

| Carriers                                                                           | по                                           | Power = -12dBFS<br>(Note 4, Note 6)                                  | Third Harmonic Distortion                   | -67.7   | -60.4 | ubc    |  |

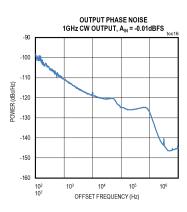

| Noise Density                                                                      | ND                                           | CW tone at 1842.5M<br>Measured at 10MHz<br>200kHz bandwidth          | Hz, -15dBFS,<br>offset from carrier, in     | -157.5  |       | dBm/Hz |  |

| DAC RESPONSE CHARA                                                                 | ACTERISTIC                                   |                                                                      |                                             |         |       |        |  |

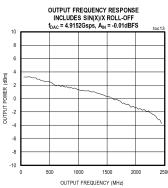

|                                                                                    |                                              | 0dBFS CW tone at                                                     | Excludes losses                             | 3.2     |       |        |  |

| Output Power (CW) (Note 7)                                                         | DAC input, f <sub>OUT</sub> = 100MHz         | DAC input, f <sub>OUT</sub> =                                        | Excludes losses, includes sin(x)/x roll-off | 3.2     |       | ]      |  |

|                                                                                    | P <sub>OUT</sub>                             | 0dBFS CW tone at                                                     | Excludes losses                             | 0.4     |       | dBm    |  |

|                                                                                    |                                              | DAC input, f <sub>DAC</sub> = 4915.2Msps, f <sub>OUT</sub> = 2140MHz | Excludes losses, includes sin(x)/x roll-off | -2.5    |       |        |  |

| Output Bandwidth                                                                   |                                              | f <sub>DAC</sub> = 4915.2Msps,<br>excludes losses (Not               |                                             | 2600    |       | MHz    |  |

## **Electrical Characteristics (continued)**

$(V_{DD} = V_{AVCLK} = V_{AVDD} = V_{AVDDPLL} = 1.0V, \ V_{DD2} = V_{AVCLK2} = V_{AVDD2} = V_{AVDD2PLL} = V_{DD2PLL} = 1.8V, \ P_{CLK} = 0dBm, \ f_{CLK} = 983.04MHz, \ f_{DAC} = 4915.2Msps, \ 4x \ interpolation, 5-lanes, 9830.4Mbps per lane, external reference at 1.206V, R_{SET} = 965\Omega \ between FSADJ \ and DACREF, I_{OUTFS} = 40mA, output \ is 50\Omega \ double-terminated \ and \ transformer \ coupled \ (see \ Figure 25), \ PLL \ on. \ T_A \ge -40^{\circ}C$  and  $T_J \le +110^{\circ}C$ , unless otherwise noted. Typical values are at  $T_J = +65 \pm 15^{\circ}C$ . (Note 1))

| PARAMETER                                               | SYMBOL             | CONDITIONS                                                      | MIN                       | TYP                          | MAX                       | UNITS                  |

|---------------------------------------------------------|--------------------|-----------------------------------------------------------------|---------------------------|------------------------------|---------------------------|------------------------|

| Output Settling Time for Full-Scale Input Step (Note 8) |                    | To ±0.024% of output full-scale in 4x interpolation mode        |                           | 20                           |                           | ns                     |

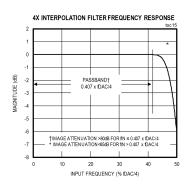

| INTERPOLATION FILTER                                    | RS                 |                                                                 |                           |                              |                           |                        |

| Interpolation Rates                                     | R                  | Complex path                                                    |                           | 4x                           |                           |                        |

| Passband Width                                          | PBW                | Ripple < 0.01dB                                                 |                           | 0.407 x<br>f <sub>S_IN</sub> |                           | MHz                    |

| Stopband Rejection                                      |                    | 4x interpolation, 0.593 x f <sub>S_IN</sub>                     |                           | 80                           |                           | dB                     |

| Data Latency (Excluding JESD204B Latency)               |                    | 4x interpolation                                                |                           | 424                          |                           | DAC<br>Clock<br>Cycles |

| NCO                                                     |                    |                                                                 |                           |                              |                           |                        |

| Maximum Frequency                                       |                    |                                                                 |                           | 2457.6                       |                           | MHz                    |

| Frequency Control Word Resolution                       |                    |                                                                 |                           | 33                           |                           | Bits                   |

| REFERENCE (REFIO)                                       |                    |                                                                 |                           |                              |                           |                        |

| Reference Input Range                                   |                    |                                                                 | 1.1                       |                              | 1.3                       | V                      |

| Reference Output<br>Voltage                             | V <sub>REFIO</sub> | Internal Reference                                              | 1.1                       | 1.2                          | 1.3                       | V                      |

| Reference Input<br>Resistance                           | R <sub>REFIO</sub> |                                                                 |                           | 10                           |                           | kΩ                     |

| Reference Voltage Drift                                 |                    |                                                                 |                           | ±110                         |                           | ppm/°C                 |

| CMOS LOGIC INPUTS/O                                     | JTPUTS (SCLK       | , CSB, MUTE, RESETB, SDI, SDO, INTB)                            |                           |                              |                           |                        |

| Input High Voltage                                      | V <sub>IH</sub>    |                                                                 | 0.7 x<br>V <sub>DD2</sub> |                              |                           | V                      |

| Input Low Voltage                                       | $V_{IL}$           |                                                                 |                           |                              | 0.3 x<br>V <sub>DD2</sub> | V                      |

| Input Current                                           | I <sub>IN</sub>    | Excluding RESETB                                                | -1                        | ±0.1                         | +1                        | μA                     |

| RESETB Input Current                                    | I <sub>INRB</sub>  |                                                                 | -1                        |                              | +55                       | μA                     |

| Input Capacitance                                       | C <sub>IN</sub>    |                                                                 |                           | 3                            |                           | pF                     |

| Output High Voltage                                     | V <sub>OH</sub>    | $I_{LOAD}$ = 200μA, INTB has a 1kΩ pullup resistor to $V_{DD2}$ | 0.8 x<br>V <sub>DD2</sub> |                              |                           | V                      |

| Output Low Voltage                                      | V <sub>OL</sub>    | $I_{SINK}$ = 200μA, INTB has a 1kΩ pullup resistor to $V_{DD2}$ |                           |                              | 0.2 x<br>V <sub>DD2</sub> | V                      |

| Output Leakage Current                                  |                    | Three-state, SDO pin                                            | -4                        | ±2.5                         | +4                        | μA                     |

| JESD204B INPUTS (DP4-                                   | -DP0, DN4-DN0      | )                                                               |                           |                              |                           |                        |

| Differential Input Return<br>Loss                       | RL <sub>DIFF</sub> |                                                                 |                           | 8                            |                           | dB                     |

## **Electrical Characteristics (continued)**

$(V_{DD} = V_{AVCLK} = V_{AVDD} = V_{AVDDPLL} = 1.0V, \ V_{DD2} = V_{AVCLK2} = V_{AVDD2} = V_{AVDD2PLL} = V_{DD2PLL} = 1.8V, \ P_{CLK} = 0dBm, \ f_{CLK} = 983.04MHz, \ f_{DAC} = 4915.2Msps, \ 4x \ interpolation, 5-lanes, 9830.4Mbps per lane, external reference at 1.206V, R_{SET} = 965\Omega \ between FSADJ \ and DACREF, I_{OUTFS} = 40mA, output \ is 50\Omega \ double-terminated \ and \ transformer \ coupled \ (see \ Figure 25), \ PLL \ on. \ T_A \ge -40^{\circ}C$  and  $T_J \le +110^{\circ}C$ , unless otherwise noted. Typical values are at  $T_J = +65 \pm 15^{\circ}C$ . (Note 1))

| PARAMETER                                                  | SYMBOL              | CONDITIONS                                                     | MIN   | TYP                       | MAX   | UNITS  |

|------------------------------------------------------------|---------------------|----------------------------------------------------------------|-------|---------------------------|-------|--------|

| Common-mode Input<br>Return Loss                           | RL <sub>CM</sub>    |                                                                |       | 6                         |       | dB     |

| Receiver Differential Resistance                           | R <sub>RxDIFF</sub> | At DC                                                          | 80    |                           | 120   | Ω      |

| Minimum Differential Input Voltage                         | V <sub>MIN_IN</sub> |                                                                |       | 110                       |       | mVp-p  |

| Maximum Differential Input Voltage                         | V <sub>MAX_IN</sub> |                                                                |       | 1050                      |       | mVp-p  |

| Discrete Serial Data<br>Rate per Lane                      | f <sub>SER_IN</sub> |                                                                |       | 9830.4                    |       | Mbps   |

| LVDS LOGIC OUTPUT (S                                       | SYNCNP, SYNCI       | NN, RCLKP, RCLKN)                                              |       |                           |       |        |

| Differential Output Logic<br>High Voltage                  | V <sub>OH</sub>     | R <sub>LOAD</sub> = 100Ω differential                          | 250   |                           | 450   | mV     |

| Differential Output Logic<br>Low Voltage                   | V <sub>OL</sub>     | R <sub>LOAD</sub> = 100Ω differential                          | -450  |                           | -250  | mV     |

| Output Common Mode<br>Voltage                              | V <sub>OCM</sub>    |                                                                | 1.125 | 1.25                      | 1.375 | V      |

| Output Maximum<br>Frequency                                | f <sub>RCLK</sub>   | $R_{LOAD}$ = 100Ω differential, $C_{LOAD}$ = 5pF               |       | 245.76                    |       | MHz    |

| CLOCK INPUT (CLKP, C                                       | LKN)                |                                                                |       |                           |       |        |

| Power Level at Differential CLKP/CLKN Clock Input (Note 6) | P <sub>CLK</sub>    | Sine-wave input,<br>PLL on                                     |       | > -3                      |       | dBm    |

| Common-Mode Voltage                                        | V <sub>COM</sub>    | AC-coupled, internally biased                                  |       | 0.5                       |       | V      |

| Differential Input<br>Resistance                           | R <sub>CLK</sub>    |                                                                |       | 100                       |       | Ω      |

| INTERNAL DAC CLOCK                                         | PLL                 |                                                                |       |                           |       | •      |

| Internal DAC Clock PLL Frequency Range                     | f <sub>PLL</sub>    |                                                                |       | 4915.2                    |       | MHz    |

| PLL Input Frequencies                                      | fCLK                | (Note 9)                                                       |       | f <sub>PLL</sub> /<br>MLT |       | MHz    |

| Minimum PLL Input<br>Frequency Multiplier                  | MLT <sub>MIN</sub>  | (Note 9)                                                       |       | 5                         |       |        |

| Maximum PLL Input Frequency Multiplier                     | MLT <sub>MAX</sub>  | (Note 9)                                                       |       | 20                        |       |        |

| Phase Noise at 6MHz<br>Offset                              |                     | Simulated at PLL output, does not include DAC core phase noise |       | -142                      |       | dBc/Hz |

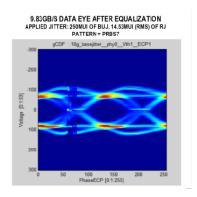

| Cycle-to-Cycle Jitter                                      |                     | Simulated at PLL output, does not include DAC core jitter      |       | 245                       |       | fs     |

## **Electrical Characteristics (continued)**

$(V_{DD} = V_{AVCLK} = V_{AVDD} = V_{AVDDPLL} = 1.0V, \ V_{DD2} = V_{AVCLK2} = V_{AVDD2} = V_{AVDD2PLL} = V_{DD2PLL} = 1.8V, \ P_{CLK} = 0dBm, \ f_{CLK} = 983.04MHz, \ f_{DAC} = 4915.2Msps, \ 4x \ interpolation, 5-lanes, 9830.4Mbps per lane, external reference at 1.206V, R_{SET} = 965\Omega \ between FSADJ \ and DACREF, I_{OUTFS} = 40mA, output \ is 50\Omega \ double-terminated \ and \ transformer \ coupled \ (see \ Figure 25), \ PLL \ on. \ T_A \ge -40^{\circ}C$  and  $T_J \le +110^{\circ}C$ , unless otherwise noted. Typical values are at  $T_J = +65 \pm 15^{\circ}C$ . (Note 1))

| PARAMETER                                                    | SYMBOL                                                                                                    | CONDITIONS                               | MIN  | TYP    | MAX  | UNITS                      |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------|------|--------|------|----------------------------|

| RESET TIMING                                                 |                                                                                                           |                                          | '    |        |      |                            |

| RESET to Ready Delay                                         | <sup>t</sup> RRDY                                                                                         |                                          |      | 350000 |      | f <sub>CLK</sub><br>Cycles |

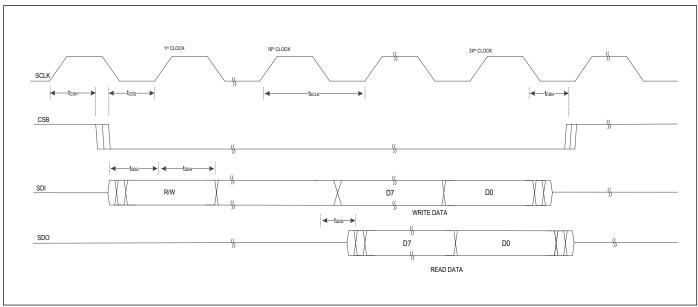

| SERIAL PORT INTERFA                                          | CE (Note 4)                                                                                               |                                          |      |        |      |                            |

| SCLK Frequency                                               | fsclk                                                                                                     | 1/t <sub>SCLK</sub>                      |      |        | 20   | MHz                        |

| SCLK to CSB Falling<br>Edge Setup Time                       | t <sub>CSS</sub>                                                                                          |                                          |      | 10     |      | ns                         |

| Minimum SCLK to CSB Falling Edge Hold Time                   | t <sub>CSH</sub>                                                                                          |                                          |      | 40     |      | ns                         |

| Minimum SCLK Falling<br>Edge to CSB Rising<br>Edge Hold Time | t <sub>CRH</sub>                                                                                          |                                          |      | 9.765  |      | ns                         |

| SDI to SCLK Hold Time                                        | tsdh                                                                                                      | Data write                               |      | 0      |      | ns                         |

| SDI to SCLK Setup<br>Time                                    | t <sub>SDS</sub>                                                                                          | Data write                               |      | 5      |      | ns                         |

| Minimum SCLK to SDO                                          |                                                                                                           | Data read, 10pF load from SDO to ground  |      | 1.5    |      |                            |

| Data Delay                                                   | t <sub>SDD_MIN</sub>                                                                                      | Data read, 100pF load from SDO to ground |      | 3.5    |      | ns                         |

| Maximum SCLK to SDO                                          |                                                                                                           | Data read, 10pF load from SDO to ground  |      | 8      |      |                            |

| Data Delay                                                   | tSDD_MAX                                                                                                  | Data read, 100pF load from SDO to ground |      | 11     |      | ns                         |

| POWER SUPPLY                                                 |                                                                                                           |                                          | -    |        |      |                            |

| 1.0V Supply Voltage<br>Range                                 | V <sub>DD</sub> , V <sub>AVDD</sub> ,<br>V <sub>AVDDPLL</sub> ,<br>V <sub>AVCLK</sub>                     |                                          | 0.95 | 1.0    | 1.05 | V                          |

| 1.8V Supply Voltage<br>Range                                 | V <sub>DD2</sub> ,<br>Vavclk2,<br>V <sub>AVDD2</sub> ,<br>V <sub>AVDD2</sub> PLL,<br>V <sub>DD2</sub> PLL |                                          | 1.71 | 1.8    | 1.89 | V                          |

| 1.0V Digital Supply<br>Current                               | I <sub>VDD</sub>                                                                                          | (Note 3)                                 |      | 550    | 750  | mA                         |

| 1.8V Digital Supply<br>Current                               | I <sub>VDD2</sub>                                                                                         | (Note 3)                                 |      | 500    | 550  | mA                         |

| 1.0V Clock Supply<br>Current                                 | IAVCLK                                                                                                    | (Note 3)                                 |      | 350    | 400  | mA                         |

| 1.8V Clock Supply<br>Current                                 | I <sub>AVCLK2</sub>                                                                                       | (Note 3)                                 |      | 51     | 60   | mA                         |

### **Electrical Characteristics (continued)**

$(V_{DD} = V_{AVCLK} = V_{AVDD} = V_{AVDDPLL} = 1.0V, V_{DD2} = V_{AVCLK2} = V_{AVDD2} = V_{AVDD2PLL} = V_{DD2PLL} = 1.8V, P_{CLK} = 0dBm, f_{CLK} = 983.04MHz, f_{DAC} = 4915.2Msps, 4x interpolation, 5-lanes, 9830.4Mbps per lane, external reference at 1.206V, R_{SET} = 965Ω between FSADJ and DACREF, I_{OUTFS} = 40mA, output is 50Ω double-terminated and transformer coupled (see <u>Figure 25</u>), PLL on. <math>T_A \ge -40^{\circ}C$  and  $T_J \le +110^{\circ}C$ , unless otherwise noted. Typical values are at  $T_J = +65 \pm 15^{\circ}C$ . (Note 1))

| PARAMETER                           | SYMBOL                | CONDITIONS | MIN | TYP  | MAX  | UNITS |

|-------------------------------------|-----------------------|------------|-----|------|------|-------|

| 1.0V Analog Supply<br>Current       | I <sub>AVDD</sub>     | (Note 3)   |     | 230  | 270  | mA    |

| 1.8V Analog Supply<br>Current       | I <sub>AVDD2</sub>    | (Note 3)   |     | 270  | 295  | mA    |

| 1.0V Clock PLL Supply<br>Current    | I <sub>AVDDPLL</sub>  | (Note 3)   |     | 7    | 15   | mA    |

| 1.8V Clock PLL Supply Current       | I <sub>AVDD2PLL</sub> | (Note 3)   |     | 28   | 35   | mA    |

| 1.8V JESD204B PLL<br>Supply Current | I <sub>VDD2PLL</sub>  | (Note 3)   |     | 27   | 35   | mA    |

| Total Power Dissipation             | PTOTAL                | (Note 3)   |     | 2700 | 3100 | mW    |

- Note 1: All specifications are guaranteed by test at T<sub>J</sub> = +60°C and T<sub>J</sub> = +115°C to an accuracy of ±10°C, unless otherwise noted. Specifications at T<sub>J</sub> < +60°C are guaranteed by design and characterization. Timing specifications are guaranteed by design and characterization.

- **Note 2:** Adjusted DAC update rate is defined as the rate at which the digital signal is converted to an analog signal and the output analog values are changed by the DAC.

- Note 3: Eight 6MHz 256-QAM carriers, f<sub>OUT</sub> = 575MHz, Average Total Power = -12dBFS, input power is referenced to a 50Ω load.

- Note 4: Specification guaranteed by design and characterization and functionally tested during production.

- Note 5: Adjacent channel is 750kHz from channel block edge to 6MHz from channel block edge. Next adjacent channel is 6MHz from channel block edge to 12MHz from channel block edge to 18MHz from channel block edge. Third adjacent channel is 12MHz from channel block edge to 18MHz from channel block edge.

- **Note 6:** Input power is referenced to a  $50\Omega$  load.

- Note 7: Excludes losses from cables and matching network at DAC output, also excludes sin(x)/x roll-off unless otherwise noted.

- **Note 8:** Settling time is dominated by the interpolation filter step response.

- Note 9: DAC PLL reference input frequency multiplier (MLT), is defined by the ratio of the PLL feedback divide value (M) and the input reference divide value (N). MLT = M ÷ N, where M is 20 and N can be 1, 2, or 4; consistent with valid configurations listed in Table 5.

Figure 1. Serial Interface Timing Diagram

### **Typical Operating Characteristics**

$(V_{DD} = V_{AVCLK} = V_{AVDD} = V_{AVDDPLL} = 1.0V, V_{DD2} = V_{AVCLK2} = V_{AVDD2} = V_{AVDD2PLL} = V_{DD2PLL} = 1.8V, P_{CLK} = 0dBm, f_{CLK} = 983.04MHz, f_{DAC} = 4915.2Msps, 4x interpolation, 5-lanes, 9830.4Mbps per lane, external reference at 1.20625V, R_{SET} = 965\Omega$  between FSADJ and DACREF,  $I_{OUTFS} = 40mA$ , output is  $50\Omega$  double-terminated and transformer coupled (see Figure 25), PLL on. Typical values are at  $T_{LI} = +65 \pm 15^{\circ}C$ .)

## **Typical Operating Characteristics (continued)**

$(V_{DD} = V_{AVDDE} = V_{AVDDE} = 1.0V, \ V_{DD2} = V_{AVCLK2} = V_{AVDD2} = V_{AVDD2PLL} = 1.8V, \ P_{CLK} = 0 dBm, \ f_{CLK} = 983.04 MHz, \ f_{DAC} = 4915.2 Msps, \ 4x \ interpolation, \ 5-lanes, \ 9830.4 Mbps \ per \ lane, \ external \ reference \ at \ 1.20625V, \ R_{SET} = 965\Omega$  between FSADJ and DACREF,  $I_{OUTFS} = 40 mA$ , output is  $50\Omega$  double-terminated and transformer coupled (see  $Figure \ 25$ ), PLL on. Typical values are at  $T_{J} = +65 \pm 15^{\circ}C$ .)

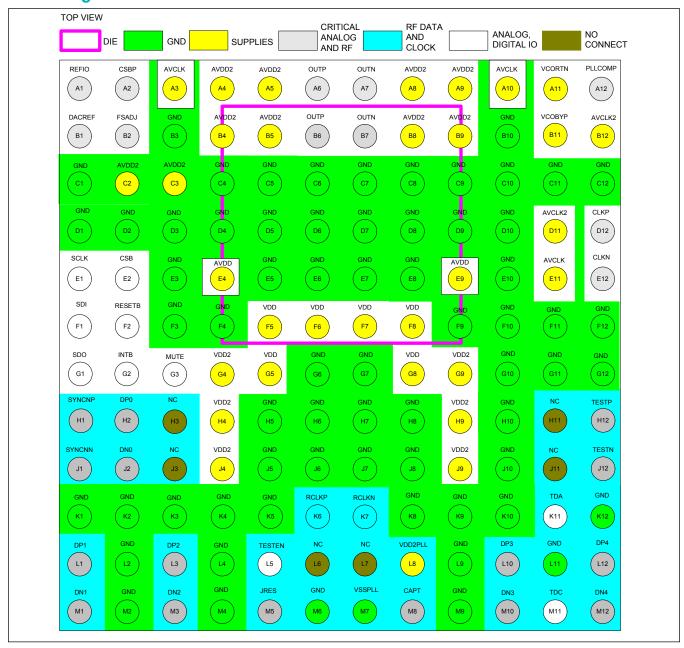

## **Pin Configuration**

## **Pin Description**

| PIN                                                                                                                                                                                                              | NAME               | FUNCTION                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1                                                                                                                                                                                                               | REFIO              | Reference Voltage Input/Output. REFIO outputs an internal 1.2V band-gap reference voltage. REFIO has a $10k\Omega$ series resistance and can be driven using an external 1.2V reference voltage. Connect a $1\mu\text{F}$ capacitor between REFIO and DACREF.                       |

| A2                                                                                                                                                                                                               | CSBP               | DAC Current Source Bypass. Connect 1.0µF capacitor between CSBP and DACREF.                                                                                                                                                                                                         |

| A3, A10                                                                                                                                                                                                          | AVCLK              | 1.0V Supply Input for Clock                                                                                                                                                                                                                                                         |

| A4-A5,<br>A8-A9,<br>B4-B5,<br>B8-B9,<br>C2-C3                                                                                                                                                                    | AVDD2              | Analog 1.8V Supply Input                                                                                                                                                                                                                                                            |

| A6, B6                                                                                                                                                                                                           | OUTP               | Positive Terminal of Differential DAC Output                                                                                                                                                                                                                                        |

| A7, B7                                                                                                                                                                                                           | OUTN               | Negative Terminal of Differential DAC Output                                                                                                                                                                                                                                        |

| A11                                                                                                                                                                                                              | V <sub>CORTN</sub> | Ground for VCO Loop Filter                                                                                                                                                                                                                                                          |

| A12                                                                                                                                                                                                              | PLLCOMP            | Analog I/O for DAC PLL Loop Filter Connection                                                                                                                                                                                                                                       |

| B1                                                                                                                                                                                                               | DACREF             | Internal DAC Reference Ground Used for DAC Current Source Bypass Ground. Do not connect to board ground (GND).                                                                                                                                                                      |

| B2                                                                                                                                                                                                               | FSADJ              | Analog Input for DAC Full-Scale Output Current Adjustment. A resistor from FSADJ to DACREF sets the full-scale output current of the DAC. To obtain a 40mA full-scale output current using the internal reference voltage, connect a $965\Omega$ resistor between FSADJ and DACREF. |

| B3, B10,<br>C1,<br>C4-C12,<br>D1-D10,<br>E3, E5-E8,<br>E10,<br>F3-F4,<br>F9-F12,<br>G6-G7,<br>G10-G12,<br>H5-H8,<br>H10,<br>J5-J8, J10,<br>K1-K5,<br>K8-K10,<br>K12, L2,<br>L4, L9,<br>L11, M2,<br>M4, M6,<br>M9 | GND                | Ground                                                                                                                                                                                                                                                                              |

| B11                                                                                                                                                                                                              | V <sub>COBYP</sub> | VCO Loop Filter Connection                                                                                                                                                                                                                                                          |

| B12                                                                                                                                                                                                              | AVCLK2             | 1.8V Supply Input for Clock                                                                                                                                                                                                                                                         |

| D11                                                                                                                                                                                                              | AVDD2PL<br>L       | 1.8V DAC Clock PLL Supply                                                                                                                                                                                                                                                           |

## **Pin Description (continued)**

| PIN                                   | NAME                | FUNCTION                                                                                                                                                                                                  |  |  |  |

|---------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                       |                     | Clock Input. Multipurpose pin that generates following internal clocks based on use case:                                                                                                                 |  |  |  |

| D12, E12                              | CLKP,<br>CLKN       | Reference clock for DAC PLL which in turn generates the DACCLK.      Powing clock (DCLK) for JESP304B interface.                                                                                          |  |  |  |

|                                       |                     | 2) Device clock (DCLK) for JESD204B interface.                                                                                                                                                            |  |  |  |

|                                       |                     | An internal 100Ω termination resistor connects CLKP to CLKN.                                                                                                                                              |  |  |  |

| E1                                    | SCLK                | Digital CMOS Input for Serial Port Interface Clock                                                                                                                                                        |  |  |  |

| E2                                    | CSB                 | Digital CMOS Input for Serial Port Interface. MAX5855 is selected when CSB = low.                                                                                                                         |  |  |  |

| E4, E9                                | AVDD                | Analog 1.0V Supply Input                                                                                                                                                                                  |  |  |  |

| E11                                   | AVDDPLL             | 1.0V DAC Clock PLL Supply                                                                                                                                                                                 |  |  |  |

| F1                                    | SDI                 | Digital CMOS Input/Output for Serial Port Interface. Data input in 4-wire SPI mode and data input/output in 3-wire SPI mode.                                                                              |  |  |  |

| F2                                    | RESETB              | Digital CMOS Input with an Internal $50k\Omega$ Pulldown Resistor. Device is reset when RESETB is low. Hold RESETB low during device startup. RESETB must be set high for normal operation after startup. |  |  |  |

| F5-F8, G5,<br>G8                      | V <sub>DD</sub>     | 1.0V Supply Input for Digital Core                                                                                                                                                                        |  |  |  |

| G1                                    | SDO                 | Digital CMOS Output for Serial Port Interface. Data output in 4-wire SPI mode.                                                                                                                            |  |  |  |

| G2                                    | INTB                | Digital CMOS Output for Interrupt                                                                                                                                                                         |  |  |  |

| G3                                    | MUTE                | Digital CMOS Input. With MUTE high the DAC output is muted and with MUTE low, the DAC output is active.                                                                                                   |  |  |  |

| G4, G9,<br>H3-H4,<br>H9, J3-J4,<br>J9 | V <sub>DD2</sub>    | 1.8V Supply Input for Digital I/O                                                                                                                                                                         |  |  |  |

| H1, J1                                | SYNCNP,<br>SYNCNN   | LVDS Output. Active-low JESD204B error reporting signal (SYNC~) from Rx device (DAC) to Tx device (FPGA/ASIC).                                                                                            |  |  |  |

| H2, L1, L3,<br>L10, L12               | DP0-DP4             | Analog Input. JESD204B Serial Data Positive Input Lanes 0-4.                                                                                                                                              |  |  |  |

| H3, H11,<br>J3, J11,<br>L6, L7        | NC                  | No Connect                                                                                                                                                                                                |  |  |  |

| H12, J12                              | TESTP,<br>TESTN     | Factory Use Only. Connect to GND.                                                                                                                                                                         |  |  |  |

| J2, M1,<br>M3, M10,<br>M12            | DN0-DN4             | Analog Input. JESD204B Serial Data Negative Input Lanes 0-4.                                                                                                                                              |  |  |  |

| K6-K7                                 | RCLKP,<br>RCLKN     | LVDS Reference Clock Output for Sample Rate Synchronization to DAC Clock. If not used, terminate differential with a $100\Omega$ resistor.                                                                |  |  |  |

| K11                                   | TDA                 | Temperature Sensor Diode Anode. Connect TDC and TDA to ground if not used.                                                                                                                                |  |  |  |

| L5                                    | TESTEN              | Factory Use Only. Connect to GND.                                                                                                                                                                         |  |  |  |

| L8                                    | V <sub>DD2PLL</sub> | JESD204B PLL 1.8V Power Supply                                                                                                                                                                            |  |  |  |

| M5                                    | JRES                | Analog Input. JESD204B Current Biasing.                                                                                                                                                                   |  |  |  |

| M7                                    | V <sub>SSPLL</sub>  | Clock Multiplier Unit (CMU) PLL Ground                                                                                                                                                                    |  |  |  |

## **Pin Description (continued)**

| PIN | NAME | FUNCTION                                                                     |  |

|-----|------|------------------------------------------------------------------------------|--|

| M8  | CAPT | Analog Input. JESD204B PLL Loop Filter Input.                                |  |

| M11 | TDC  | Temperature Sensor Diode Cathode. Connect TDC and TDA to ground if not used. |  |

## **Functional Diagrams**

### **Detailed Description**

The MAX5855 is a high-performance, interpolating and modulating, 14-bit, 4.9Gsps RF DAC designed for DOCSIS 3.1/3.0 remote PHY devices, CCAP, digital video broadcast modulators, point-to-point wireless, and instrumentation. The device can synthesize up to 1GHz of instantaneous bandwidth at frequencies up to the Nyquist bandwidth (f<sub>DAC</sub>/2) of the DAC. The major functional blocks of the device include a five-lane JESD204B interface which accepts 16-bit input data, interpolation filters, a digital quadrature modulator and NCO, clock multiplying PLL + VCO and a 14-bit, 4.9Gsps RF DAC core. The supporting functional blocks include the clock distribution system, reference system, and SPI interface. See the detailed *Functional Diagram*.

The 16-bit input data enhances the accuracy of the interpolation and modulation functions and ensures true 14-bit data is presented to the RF DAC core. The 16-bit input baseband data is supplied to the device using a five lane JESD204B (DP[4:0]/DN[4:0]) interface operating at 9.8304Gbps.

The five-lane JESD204B interface has the following major components:

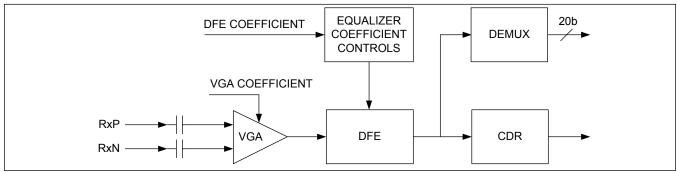

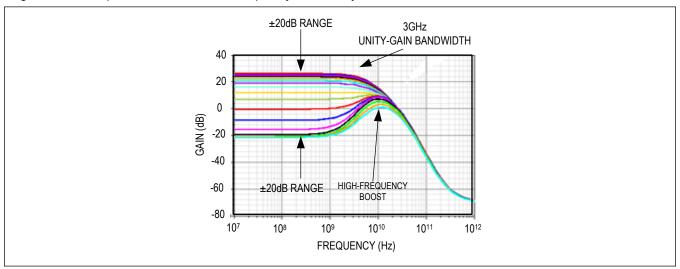

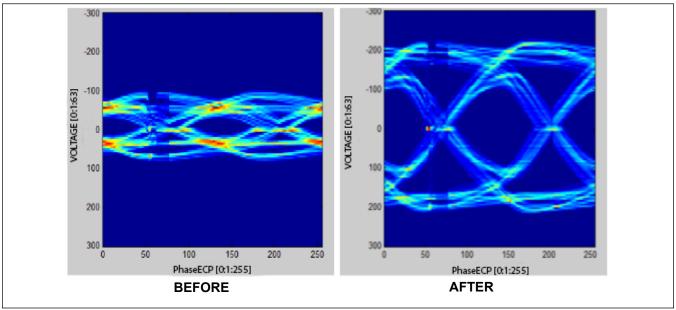

- A high-speed input receiver (Rx) consisting of a physical (PHY) layer for each of the five lanes and a common clock multiplier unit (CMU). The PHY layer contains a variable gain amplifier (VGA) which receives the incoming signal and decision feedback equalizer (DFE) to suppress inter-symbol interference. The PHY layer also includes a clock and data recovery (CDR) unit to latch the incoming single-bit data and a de-serializer (DEMUX) to convert the data to a 20-bit parallel data bus.

- A receiver link layer (Rx Link) takes the 20 bits from the PHY and restores the 16-bit DAC data for each of the I and Q channels. The Rx link consists of five Rx lanes, five Rx FIFOs, a Rx mapper and a Rx controller. The five Rx lanes perform code group synchronization, 8b/10b decoding, frame synchronization and monitoring, interlane alignment and monitoring, character replacement, and optional descrambling. The five lanes are fed into Rx FIFOs where data is aligned by the Rx controller. Using the Rx mapper, data from each physical channel is mapped to a logical channel.

The DSP path consists of 4x linear phase interpolation filters for each of the I and Q channels. Interpolation reduces the required input data rate to the device, relaxing the requirements on the FPGA or ASIC. In addition, interpolation increases the separation between the desired signal and its aliased image easing filter design requirements.

After passing through the 4x interpolation stage, the complex signal is modulated using the LO signal generated by the NCO and the digital quadrature modulator. The NCO allows for fully agile modulation of the input baseband signal for direct RF synthesis with 32 bits of frequency-setting resolution. Placing the modulator at the output of the interpolator chain allows for fully agile placement of the output carrier frequency within the Nyquist band of the DAC. The quadrature modulator produces a real signal at its output, which is fed into the 14-bit DAC core where it is converted to an analog RF signal. The analog output produces a full-scale current between 10mA and 40mA, driving  $50\Omega$  differential loads.

The clock distribution system provides a low-noise differential input buffer for the external master DAC clock (CLKP/CLKN) and delivers all the necessary clocks to the internal blocks. The master DAC clock input accepts a differential sine-wave or square-wave signal. A clock multiplying PLL and VCO is used to internally generate the 4915.2MHz sampling clock using reference frequencies of 245.76MHz, 491.52MHz or 983.04MHz. The device provides a divided reference clock (RCLKP/RCLKN) to ensure synchronization between the data source (FPGA or ASIC) and the DAC. The SYNCN output can be used for error reporting from the DAC to the data source.

The reference system delivers the reference current to the DAC current source array and all bias currents necessary for circuit operation. The reference system also includes a bypassable band-gap reference, which can be used as a reference for the DAC full-scale current.

The SPI port is a bidirectional interface used for reading and writing status and control registers to configure the device.

The device operates from 1.0V and 1.8V power-supply voltages and consumes 2.7W at 4.9Gsps.

### Supported DAC Update Rate and JESD204B Data Rates

## Table 1. Complex I/Q Base Band Up-Conversion

| DAC Update Rate: DACCLK (Msps)         | 4915.20 |  |

|----------------------------------------|---------|--|

| Input Sample Rate – I and Q each (MHz) | 1228.8  |  |

| Instantaneous Bandwidth (MHz)          | 1000    |  |

#### **Table 2. Lane Rate**

| DACCLK (Msps)            | 4915.20 |

|--------------------------|---------|

| Number of JESD204B Lanes | 5       |

| Lane Rate (Mbps)         | 9830.4  |

#### JESD204B Interface

The JESD204B interface consists of five PHY lanes with one CMU. Each lane takes a 1-bit stream and converts it to a 20-bit bus. The link layer (LINK) takes the 20-bit bus from the PHY and restores the original 16-bit DAC data for each of the I and Q channels (<u>Figure 2</u>).

The JESD204B receiver specifications are compliant with LV-OIF-6G-SR and LV-OIF-11G-SR specifications from the JEDEC standard.

Figure 2. Simplified Diagram of JESD204B Internal to MAX5855

### MAX5855

## 16-Bit, 4.9Gsps Wideband Interpolating and Modulating RF DAC with JESD204B Interface

#### **JESD204B Data Interface Features**

A summary of the MAX5855 PHY and LINK features is provided below:

#### **Rx PHY Features**

Programmable gain

#### **LINK Features**

- 8b/10b decoding

- Code group synchronization

- Inter Lane Alignment (ILA)

- 1 + x<sup>14</sup> + x<sup>15</sup> polynomial scrambling

- Character replacement

- Multiple Converter Device Alignment-Multiple Lanes (MCDA-ML) compliant

- Subclass-0 support