19-5328; Rev 0; 7/10

EVALUATION KIT AVAILABLE

# 0 to 16V, Hot-Swap Controller with 10-Bit Current, Voltage Monitor, and 4 LED Drivers

#### **General Description**

The MAX5978 hot-swap controller provides complete protection for systems with a supply voltage from 0 to 16V. The device includes four programmable LED outputs.

The IC provides two programmable levels of overcurrent circuit-breaker protection: a fast-trip threshold for a fast turn-off, and a lower slow-trip threshold for a delayed turn-off. The maximum overcurrent circuitbreaker threshold range is set with a trilevel logic input (IRNG), or by programming through the I<sup>2</sup>C interface.

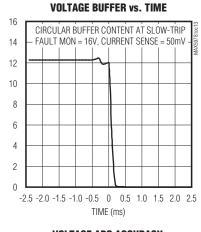

The IC is an advanced hot-swap controller that monitors voltage and current with an internal 10-bit ADC, which is continuously multiplexed to convert the output voltage and current at 10ksps. Each 10-bit sample is stored in an internal circular buffer so that 50 past samples of each signal can be read back through the I<sup>2</sup>C interface at any time or after a fault condition.

The device includes five user-programmable digital comparators to implement overcurrent warning and two levels of overvoltage/undervoltage detection. When measured values violate the programmable limits, an external ALERT output is asserted. In addition to the ALERT signal, the IC can be programmed to deassert the powergood signal and/or turn off the external MOSFET.

The IC features four I/Os that can be independently configured as general-purpose input/outputs (GPIOs) or as open-drain LED drivers with programmable blinking. These four I/Os can be configured for any mix of LED driver or GPIO function.

The device is available in a 32-pin thin QFN-EP package and operates over the -40°C to +85°C extended temperature range.

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX5978ETJ+ | -40°C to +85°C | 32 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

#### \_Features

- Hot-Swap Controller Operates from 0 to 16V

- 10-Bit ADC Monitors Load Voltage and Current

- Circular Buffers Store 5ms of Current and Voltage Measurements

- Internal Charge Pump Generates n-Channel MOSFET Gate Drive

- Internal 500mA Gate Pulldown Current for Fast Shutdown

- ◆ VariableSpeed/Bilevel<sup>™</sup> Circuit-Breaker Protection

- Precision-Voltage Enable Input

- Alert Output Indicates Fault and Warning Conditions

- Open-Drain Power-Good Output with Programmable Polarity

- Open-Drain Fault Output

- Four Open-Drain General-Purpose Outputs Sink 25mA to Directly Drive LEDs

- Programmable LED Flashing Function

- Latched-Off Fault Management

- 400kHz I<sup>2</sup>C Interface

- Small, 5mm x 5mm, 32-Pin TQFN-EP Package

## **Applications**

Blade Servers DC Power Metering Disk Drives/DASD/Storage Systems Soft-Switch for ASICs, FPGAs, and Microcontrollers Network Switches/Routers

VariableSpeed/Bilevel is a trademark of Maxim Integrated Products, Inc.

####

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| IN, SENSE, MON, GATE to AGND              |                    |

|-------------------------------------------|--------------------|

| PG, ON, ALERT, FAULT, SDA, SCL to AGND    |                    |

| REG, DREG, IRNG, MODE, PROT, A_ to AGND0. | .3V to +4V         |

| REG to DREG0.3                            | V to +0.3V         |

| HWEN, POL to AGND0.3V to (VRE             | <u>=</u> G + 0.3V) |

| GATE to MON0                              | .3V to +6V         |

| GND, DGND to AGND0.3                      | V to +0.3V         |

| SDA, ALERT Current20mA                    | to +50mA           |

| LED_ Current20mA to                       | o +100mA           |

| GATE, MON, GND Current                    | 750mA              |

\*As per JEDEC51 Standard (Multilayer Board).

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 2.7V \text{ to } 16V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{IN} = 3.3V \text{ and } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                          | SYMBOL            |             | CONDITIONS                         | MIN    | ТҮР   | MAX   | UNITS  |

|------------------------------------|-------------------|-------------|------------------------------------|--------|-------|-------|--------|

| Supply Input Voltage Range         | VIN               |             |                                    | 2.7    |       | 16    | V      |

| Hot-Swap Voltage Range             |                   |             |                                    | 0      |       | 16    | V      |

| Supply Current                     | lin               |             |                                    |        | 2.5   | 4     | mA     |

| Internal LDO Output Voltage        | REG               | IREG = 0 to | 5mA, V <sub>IN</sub> = 2.7V to 16V | 2.49   | 2.53  | 2.6   | V      |

| Undervoltage Lockout               | UVLO              | VIN rising  |                                    |        |       | 2.6   | V      |

| Undervoltage-Lockout<br>Hysteresis | UVLOHYS           |             |                                    |        | 100   |       | mV     |

| CURRENT-MONITORING FUI             | NCTION            |             |                                    |        |       |       |        |

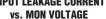

| MON, SENSE Input Voltage<br>Range  |                   |             |                                    | 0      |       | 16    | V      |

| SENSE Input Current                |                   | VSENSE, VM  | ON = 16V                           |        | 32    | 75    | μA     |

| MON Input Current                  |                   | VSENSE, VM  | ON = 16V                           |        | 180   | 280   | μA     |

|                                    |                   | 25mV range  |                                    |        | 24.34 |       | μV     |

| Current Measurement LSB<br>Voltage |                   | 50mV range  |                                    | 48.39  |       |       |        |

| vollage                            |                   | 100mV rang  |                                    | 96.77  |       |       |        |

|                                    |                   |             | VSENSE - VMON = 5mV                | -6.57  |       | +6.22 | -      |

| Current Measurement Error          |                   | VMON = 0V   | VSENSE - VMON = 20mV               | -6.71  |       | +6.82 |        |

| (25mV Range)                       |                   | VMON =      | VSENSE - VMON = 5mV                | -9.71  |       | +8.92 | %FS    |

|                                    |                   | 2.5V to 16V | VSENSE - VMON = 20mV               | -10.24 |       | +9.36 |        |

|                                    |                   | VMON = 0V   | VSENSE - VMON = 10mV               | -4.24  |       | +3.78 | 1      |

| Current Measurement Error          | Measurement Error |             | VSENSE - VMON = 40mV               | -4.53  |       | +5.36 | - %FS  |

| (50mV Range)                       |                   | VMON =      | VSENSE - VMON = 10mV               | -4.50  |       | +4.00 | ] /°F3 |

|                                    |                   | 2.5V to 16V | VSENSE - VMON = 40mV               | -4.20  |       | +4.50 |        |

M/XI/M

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 2.7V \text{ to } 16V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{IN} = 3.3V \text{ and } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                          | SYMBOL               |                                                            | CONDITIONS                 | MIN     | TYP | MAX     | UNITS |

|----------------------------------------------------|----------------------|------------------------------------------------------------|----------------------------|---------|-----|---------|-------|

|                                                    |                      |                                                            | VSENSE - VMON = 20mV       | -2.70   |     | +2.43   |       |

| Current Measurement Error                          |                      | VMON = 0V                                                  | VSENSE - VMON = 80mV       | -3.63   |     | +4.56   |       |

| (100mV Range)                                      |                      | V <sub>MON</sub> =                                         | VSENSE - VMON = 20mV       | -3.14   |     | +3.19   | %FS   |

|                                                    |                      | 2.5V to 16V                                                | VSENSE - VMON = 80mV       | -3.80   |     | +3.93   |       |

|                                                    |                      |                                                            | Circuit breaker, DAC = 102 | -2.106  |     | +0.888  |       |

| Fast Current-Limit Threshold                       |                      | VMON = 0V                                                  | Circuit breaker, DAC = 255 | -2.986  |     | +0.641  |       |

| Error (25mV Range)                                 |                      | V <sub>MON</sub> =                                         | Circuit breaker, DAC = 102 | -3.000  |     | +1.000  | mV    |

|                                                    |                      | 2.5V to 16V                                                | Circuit breaker, DAC = 255 | -3.500  |     | +1.500  |       |

|                                                    |                      | V/1.0.1                                                    | Circuit breaker, DAC = 102 | -3.1188 |     | +0.926  |       |

| Fast Current-Limit Threshold                       |                      | V <sub>MON</sub> = 0V                                      | Circuit breaker, DAC = 255 | -4.873  |     | +0.3421 |       |

| Error (50mV Range)                                 |                      | VMON =                                                     | Circuit breaker, DAC = 102 | -3.2668 |     | +0.9228 | mV    |

|                                                    |                      | 2.5V to 16V                                                | Circuit breaker, DAC = 255 | -4.7    |     | +1.0212 |       |

|                                                    |                      | V/                                                         | Circuit breaker, DAC = 102 | -4.7987 |     | +1.1812 |       |

| Fast Current-Limit Threshold                       |                      | VMON = 0V                                                  | Circuit breaker, DAC = 255 | -8.9236 |     | +0.202  |       |

| Error (100mV Range)                                |                      | VMON =                                                     | Circuit breaker, DAC = 102 | -4.9991 |     | +0.6374 | mV    |

|                                                    |                      | 2.5V to 16V                                                | Circuit breaker, DAC = 255 | -8.262  |     | +1      |       |

| Slow Current-Limit Threshold<br>Error (25mV Range) |                      | V <sub>MON</sub> = 0V<br>V <sub>MON</sub> =<br>2.5V to 16V | Circuit breaker, DAC = 102 | -1.7965 |     | +1.5496 | mV    |

|                                                    |                      |                                                            | Circuit breaker, DAC = 255 | -1.86   |     | +1.5916 |       |

|                                                    |                      |                                                            | Circuit breaker, DAC = 102 | -2.149  |     | +1.9868 |       |

|                                                    |                      |                                                            | Circuit breaker, DAC = 255 | -2.2285 |     | +1.9982 |       |

|                                                    |                      | V <sub>MON</sub> = 0V<br>V <sub>MON</sub> =<br>2.5V to 16V | Circuit breaker, DAC = 102 | -2.3992 |     | +1.8723 | mV    |

| Slow Current-Limit Threshold                       |                      |                                                            | Circuit breaker, DAC = 255 | -2.5146 |     | +2.1711 |       |

| Error (50mV Range)                                 |                      |                                                            | Circuit breaker, DAC = 102 | -2.4716 |     | +2.181  |       |

|                                                    |                      |                                                            | Circuit breaker, DAC = 255 | -2.7421 |     | +2.1152 |       |

|                                                    |                      | V/1.10.1 0\/                                               | Circuit breaker, DAC = 102 | -3.3412 |     | +2.989  | mV    |

| Slow Current-Limit Threshold                       |                      | VMON = 0V                                                  | Circuit breaker, DAC = 255 | -3.8762 |     | +3.6789 |       |

| Error (100mV Range)                                |                      | VMON =                                                     | Circuit breaker, DAC = 102 | -3.2084 |     | +2.7798 |       |

|                                                    |                      | 2.5V to 16V                                                | Circuit breaker, DAC = 255 | -3.8424 |     | +2.6483 |       |

| Fast Circuit-Breaker<br>Response Time              | tFCB                 | Overdrive =                                                | 10% of current-sense range |         | 2   |         | μs    |

|                                                    |                      | Overdrive =                                                | 4% of current-sense range  |         | 2.4 |         |       |

| Slow Current-Limit Response                        | tSCB                 |                                                            | 8% of current-sense range  |         | 1.2 |         | ms    |

| Time                                               | .000                 |                                                            | 16% of current-sense range |         | 0.8 |         |       |

| THREE-STATE INPUTS                                 |                      | ororanio                                                   |                            |         | 0.0 |         |       |

| A1, A0, IRNG, MODE, PROT<br>Low Current            | IIN_LOW              | Input voltage = 0.4V                                       |                            | -40     |     |         | μΑ    |

| A1, A0, IRNG, MODE, PROT<br>High Current           | I <sub>IN_HIGH</sub> | Input voltage                                              |                            |         | 40  | μA      |       |

| A1, A0, IRNG, MODE, PROT<br>Open Current           | IFLOAT               | Maximum so<br>state                                        | -4                         |         | +4  | μA      |       |

| A1, A0, IRNG, MODE, PROT<br>Low Voltage            |                      | Relative to A                                              | AGND                       |         |     | 0.4     | V     |

## ELECTRICAL CHARACTERISTICS (continued)

$(V_{IN} = 2.7V \text{ to } 16V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{IN} = 3.3V \text{ and } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                  | SYMBOL   | CONDITIONS                                | MIN        | TYP   | MAX   | UNITS |

|--------------------------------------------|----------|-------------------------------------------|------------|-------|-------|-------|

| A1, A0, IRNG, MODE, PROT<br>High Voltage   |          | Relative to V <sub>REG</sub>              | -0.24      |       |       | V     |

| TWO-STATE INPUTS                           |          |                                           |            |       |       |       |

| HWEN, POL Input Logic Low<br>Voltage       |          |                                           |            |       | 0.4   | V     |

| HWEN, POL Input Logic High<br>Voltage      |          |                                           | VREG - 0.4 |       |       | V     |

| HWEN, POL Input Current                    |          |                                           | -1         |       | +1    | μA    |

| ON Input Voltage                           | Von      |                                           | 0.582      | 0.592 | 0.602 | V     |

| ON Input Hysteresis                        | Vonhys   |                                           |            | 4     |       | %     |

| ON Input Current                           |          |                                           | -100       |       | +100  | nA    |

| TIMING                                     |          |                                           |            |       |       |       |

|                                            |          |                                           |            | 50    |       |       |

| MON to DO Dolov                            |          | Register configurable (see Tables 30a and |            | 100   |       | 1     |

| MON-to-PG Delay                            |          | 30b)                                      |            | 200   |       | ms    |

|                                            |          |                                           |            | 400   |       | ]     |

| CHARGE PUMP (GATE)                         |          |                                           |            |       |       |       |

| Charge-Pump Output Voltage                 |          | Relative to VMON, IGATE = 0V              | 4.5        | 5.3   | 5.5   | V     |

| Charge-Pump Output Source<br>Current       |          |                                           | 4          | 5     | 6     | μA    |

| GATE Discharge Current                     |          | VGATE - VMON = 2V                         |            | 500   |       | mA    |

| OUTPUT (FAULT, PG, ALERT                   | )        | 1                                         | 1          |       |       |       |

| Output-Voltage Low                         |          | Isink = 3.2mA                             |            |       | 0.2   | V     |

| Output Leakage Current                     |          |                                           |            |       | 1     | μA    |

| LED INPUT/OUTPUT                           |          |                                           |            |       |       |       |

| LED_ Input Threshold Low<br>Level          | VIL      |                                           |            |       | 0.4   | V     |

| LED_ Input Threshold High<br>Level         | ViH      |                                           | 1.4        |       |       | V     |

| LED_ Output Low                            | Voh      | I <sub>LED_</sub> = 25mA                  |            |       | 0.7   | V     |

| LED_ Input Leakage Current<br>(Open Drain) | IGPIO_IX | V <sub>LED</sub> = 16V                    | -1         |       | +1    | μA    |

| LED_ Weak Pullup Current                   | IPU_WEAK | VLED_ = VIN - 0.65V                       | 2          |       |       | μA    |

| ADC PERFORMANCE                            |          |                                           |            |       |       |       |

| Resolution                                 |          |                                           |            | 10    |       | Bits  |

| Maximum Integral<br>Nonlinearity           | INL      |                                           |            | 1     |       | LSB   |

| ADC Total Monitoring Cycle<br>Time         |          |                                           | 95         | 100   | 110   | μs    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 2.7V \text{ to } 16V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{IN} = 3.3V \text{ and } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                          | SYMBOL  | CONDITIONS                    | MIN   | TYP   | MAX   | UNITS |  |

|----------------------------------------------------|---------|-------------------------------|-------|-------|-------|-------|--|

|                                                    |         | 16V range                     | 15.23 | 15.49 | 15.69 |       |  |

|                                                    |         | 8V range                      | 7.655 | 7.743 | 7.811 | mV    |  |

| MON LSB Voltage                                    |         | 4V range                      | 3.811 | 3.875 | 3.933 |       |  |

|                                                    |         | 2V range                      | 1.899 | 1.934 | 1.966 |       |  |

|                                                    |         | 16V range                     | 10    | 25    | 41    |       |  |

| MON Code 000H to 001H<br>Transition Voltage        |         | 8V range                      | 4.7   | 12    | 21    |       |  |

|                                                    |         | 4V range                      | 2     | 6     | 12    | mV    |  |

|                                                    |         | 2V range                      | 0.5   | 3     | 5.5   | 1     |  |

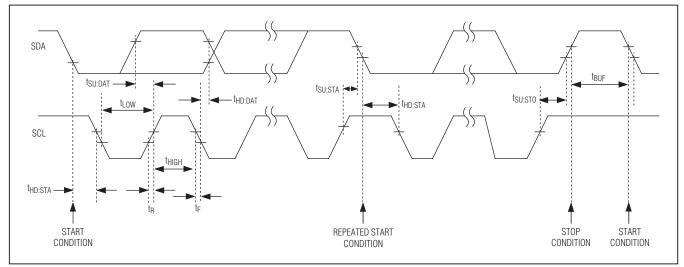

| I <sup>2</sup> C INTERFACE                         | -       |                               |       |       |       |       |  |

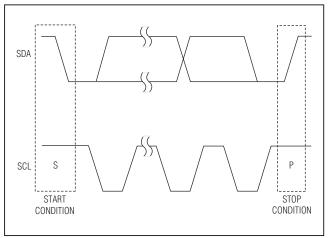

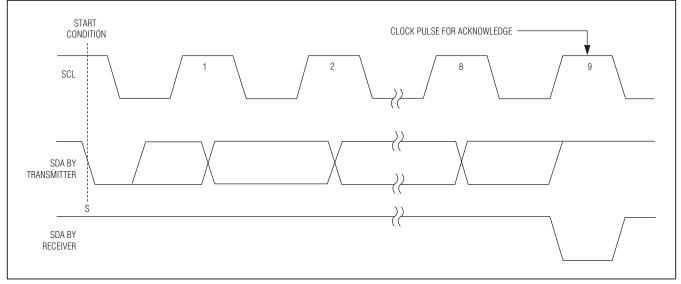

| Serial-Clock Frequency                             | fscl    |                               |       |       | 400   | kHz   |  |

| Bus Free Time Between<br>STOP and START Conditions | tBUF    |                               | 1.3   |       |       | μs    |  |

| START Condition Setup Time                         | tsu:sta |                               | 0.6   |       |       | μs    |  |

| START Condition Hold Time                          | thd:Sta |                               | 0.6   |       |       | μs    |  |

| STOP Condition Setup Time                          | tsu:sto |                               | 0.6   |       |       | μs    |  |

| Clock High Period                                  | thigh   |                               | 0.6   |       |       | μs    |  |

| Clock Low Period                                   | tLOW    |                               | 1.3   |       |       | μs    |  |

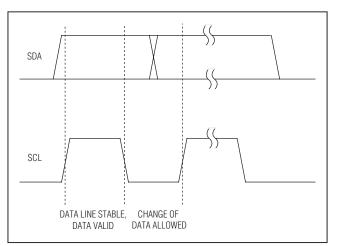

| Data Setup Time                                    | tsu:dat |                               | 100   |       |       | ns    |  |

| Data Hold Time                                     |         | Transmit                      | 100   |       |       |       |  |

|                                                    | thd:dat | Receive                       | 300   |       | 900   | ns    |  |

| Output Fall Time                                   | toF     | $C_{BUS} = 10 pF$ to $400 pF$ |       |       | 250   | ns    |  |

| Pulse Width of Spike<br>Suppressed                 | tSP     |                               |       | 50    |       | ns    |  |

| SDA, SCL Input High Voltage                        | Vih     |                               | 1.8   |       |       | V     |  |

| SDA, SCL Input Low Voltage                         | VIL     |                               |       |       | 0.8   | V     |  |

| SDA, SCL Input Hysteresis                          | VHYST   |                               |       | 0.22  |       | V     |  |

| SDA, SCL Input Current                             |         |                               | -1    |       | +1    | μA    |  |

| SDA, SCL Input Capacitance                         |         |                               |       | 15    |       | pF    |  |

| SDA Output Voltage                                 | Vol     | ISINK = 4mA                   |       |       | 0.4   | V     |  |

Note 2: All devices 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the temperature range are guaranteed by design.

**SUPPLY CURRENT SUPPLY CURRENT vs. TEMPERATURE** vs. SUPPLY VOLTAGE **GATE-DRIVE VOLTAGE vs. VMON** 2.50 3.0 5.20 VGATE REFERRED TO VMON 2.9 5.15 2.8 2.45 2.40 CURRENT (mA) 2.40 2.35 ≥ 5.10 SUPPLY CURRENT (mA) 2.7 GATE-DRIVE VOLTAGE ( 5.05 2.6 HOT-SWAP CHANNEL ON 2.5 5.00 2.4 4.95 2.3 2.35 4.90 HOT-SWAP CHANNEL OFF 2.2 4.85 2.1 2.0 2.30 4.80 2 4 12 14 16 0 6 8 10 -40 -15 10 35 60 85 0 2 4 6 8 10 12 14 16 SUPPLY VOLTAGE (V) TEMPERATURE (°C) V<sub>MON</sub> (V) **GATE-DRIVE CURRENT GATE-DRIVE DISCHARGE CURRENT GATE-DRIVE VOLTAGE vs. VIN** vs. (Vgate - Vmon) vs. (Vgate - Vmon) 10 10 5.10 9 0.9 GATE-DRIVE DISCHARGE CURRENT (A) 8 0.8 5.05 GATE-DRIVE CURRENT (µA) 7 0.7 (VGATE - VMON) (V)  $V_{MON} = 3.3V$ 5.00 6 0.6 5 0.5 4 0.4 4.95 3 0.3  $V_{MON} = 12V$ 2 0.2 4.90 0.1 1 0 0 4.85 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 2 4 10 12 14 0 0 6 8 16 (VGATE - VMON) (V) (VGATE - VMON) (V) V<sub>IN</sub> (V) SLOW-COMPARATOR TURN-OFF TIME **SLOW-COMPARATOR THRESHOLD ON THRESHOLD VOLTAGE** vs. VOLTAGE OVERDRIVE **VOLTAGE ERROR vs. TEMPERATURE** vs. TEMPERATURE 3.00 10 0.60 25mV SENSE RANGE. 8 0.59 DAC = 191, V<sub>TH,ST</sub> = 9.36mV 2.50 (V) 39200 0.57 0.56 0.55 0.55 0.54 0.53 RISING **THRESHOLD VOLTAGE ERROR (%)** 6 (in 2.00 1.50 1.50 4 FALLING 2 0 50mV SENSE RANGE 100mV SENSE RANGE -2 -4 0.53 N 0.52 -6 0.50 25mV SENSE RANGE -8 0.51 0 -10 0.50 0 2 3 4 5 -40 -15 10 35 85 -40 -15 10 85 60 35 60 (VSENSE - VMON) - VTH,ST (mV) TEMPERATURE (°C) TEMPERATURE (°C)

#### **Typical Operating Characteristics**

**MAX5978**

$(V_{IN} = 3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

**Typical Operating Characteristics (continued)**

(VIN = 3.3V,  $T_A$  = +25°C, unless otherwise noted.)

SLOW-COMPARATOR FAULT EVENT

400µs/div

**VOLTAGE BUFFER (V)**

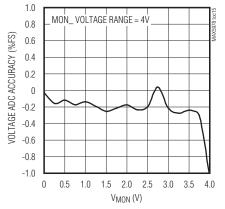

#### VOLTAGE ADC ACCURACY vs. Mon Voltage

$(V_{IN} = 3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$ **CURRENT ADC ACCURACY** vs. (Vsense - Vmon) **CURRENT BUFFER vs. TIME VOLTAGE BUFFER vs. TIME** 5 0.5 10 VOLTAGE DATA AT SHORT CIRCUIT ON DEFAULT SETTING 4 9 0.4 POWER-UP DEFAULT SETTING VMON = 16V CURRENT ADC ACCURACY (%FS) 3 8 0.3 2 E 7 0.2 VOLTAGE BUFFER (V) CURRENT BUFFER 1 6 0.1 0 5 0 -1 4 -0.1 3 -2 -0.2 -3 2 -0.3 -4 1 -0.4 -5 0 -0.5 -2.5 -2.0 -1.5 -1.0 -0.5 0 0.5 1.0 1.5 2.0 2.5 2.5 5.0 7.5 10.0 12.5 15.0 17.5 20.0 22.5 25.0 0 -2.5 -2.0 -1.5 -1.0 -0.5 0 0.5 1.0 1.5 2.0 2.5 (VSENSE - VMON) (mV) TIME (ms) TIME (ms) **INPUT LEAKAGE CURRENT**

**STARTUP INTO SHORT LOAD**

4ms/div

.....

Ö

Von

5V/div

ILOAD

5A/div

VGATE

2V/div

VMON

1V/div

V<sub>FAULT</sub> 5V/div

**Typical Operating Characteristics (continued)**

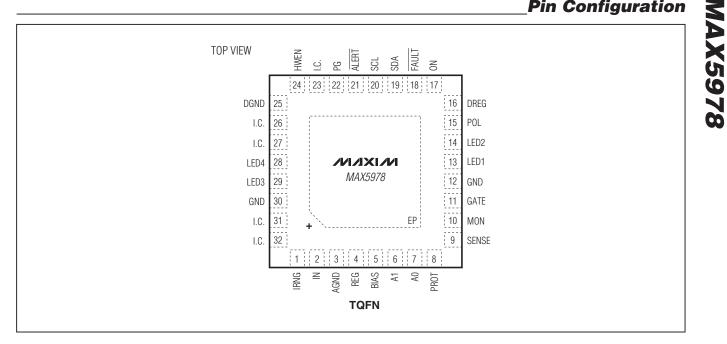

#### **Pin Configuration**

## **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                     |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IRNG  | Three-State Current-Sense Range Selection Input. Set the circuit-breaker threshold range by connecting to DGND, DREG, or leave unconnected.                                  |

| 2   | IN    | Power-Supply Input. Connect to a voltage from 2.7V to 16V. Bypass IN to AGND with a $1\mu F$ ceramic capacitor.                                                              |

| 3   | AGND  | Analog Ground. Connect all GND and DGND to AGND externally using a star connection.                                                                                          |

| 4   | REG   | Internal Regulator Output. Bypass REG to ground with a 1µF ceramic capacitor. Connect only to DREG and logic-input pullup resistors. Do not use to power external circuitry. |

| 5   | BIAS  | BIAS Input. Connect BIAS to REG.                                                                                                                                             |

| 6   | A1    | Three-State I <sup>2</sup> C Address Input 1                                                                                                                                 |

| 7   | AO    | Three-State I <sup>2</sup> C Address Input 0                                                                                                                                 |

| 8   | PROT  | Protection Behavior Input. Three-state input sets one of three different response options for undervoltage and overvoltage events.                                           |

| 9   | SENSE | Current-Sense Input. Connect SENSE to the source of an external MOSFET and to one end of RSENSE.                                                                             |

| 10  | MON   | Voltage-Monitoring Input                                                                                                                                                     |

| 11  | GATE  | Gate-Drive Output. Connect to the gate of an external n-channel MOSFET.                                                                                                      |

| 12  | GND   | Gate-Discharge Current Ground Return. Connect all GND and DGND to AGND externally using a star connection.                                                                   |

| 13  | LED1  | LED1 Driver                                                                                                                                                                  |

| 14  | LED2  | LED2 Driver                                                                                                                                                                  |

| PIN                   | NAME  | FUNCTION                                                                                                                                                                                                                               |

|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15                    | POL   | Polarity Select Input. Connect POL to DREG for an active-high power-good (PG) output, or con-<br>nect POL to GND for active-low PG output.                                                                                             |

| 16                    | DREG  | Logic Power-Supply Input. Connect to REG externally through a $10\Omega$ resistor and bypass to DGND with a 1µF ceramic capacitor.                                                                                                     |

| 17                    | ON    | Precision Turn-On Input                                                                                                                                                                                                                |

| 18                    | FAULT | Active-Low Open-Drain Fault Output. FAULT asserts low if an overcurrent event occurs.                                                                                                                                                  |

| 19                    | SDA   | I <sup>2</sup> C Serial Data Input/Output                                                                                                                                                                                              |

| 20                    | SCL   | I <sup>2</sup> C Serial Clock Input                                                                                                                                                                                                    |

| 21                    | ALERT | Open-Drain Alert Output. ALERT goes low during a fault to notify the system of an impending failure.                                                                                                                                   |

| 22                    | PG    | Open-Drain Power-Good Output                                                                                                                                                                                                           |

| 23, 26, 27,<br>31, 32 | I.C.  | Internally Connected. Connect to ground.                                                                                                                                                                                               |

| 24                    | HWEN  | Hardware Enable Input. Connect to REG or DGND. State is read upon power-up as V <sub>IN</sub> crosses the UVLO threshold and sets enable register bits with this value. After UVLO, this input becomes inactive until power is cycled. |

| 25                    | DGND  | Digital Ground. Connect all GND and DGND to AGND externally using a star connection.                                                                                                                                                   |

| 28                    | LED4  | LED Driver 4                                                                                                                                                                                                                           |

| 29                    | LED3  | LED Driver 3                                                                                                                                                                                                                           |

| 30                    | GND   | Ground                                                                                                                                                                                                                                 |

| _                     | EP    | Exposed Pad. EP is internally grounded. Connect EP to the ground plane using a star connection.                                                                                                                                        |

## Pin Description (continued)

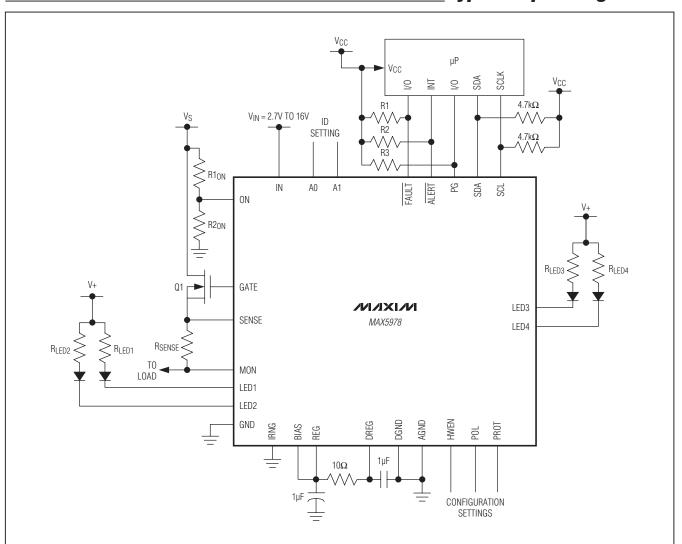

**Typical Operating Circuit**

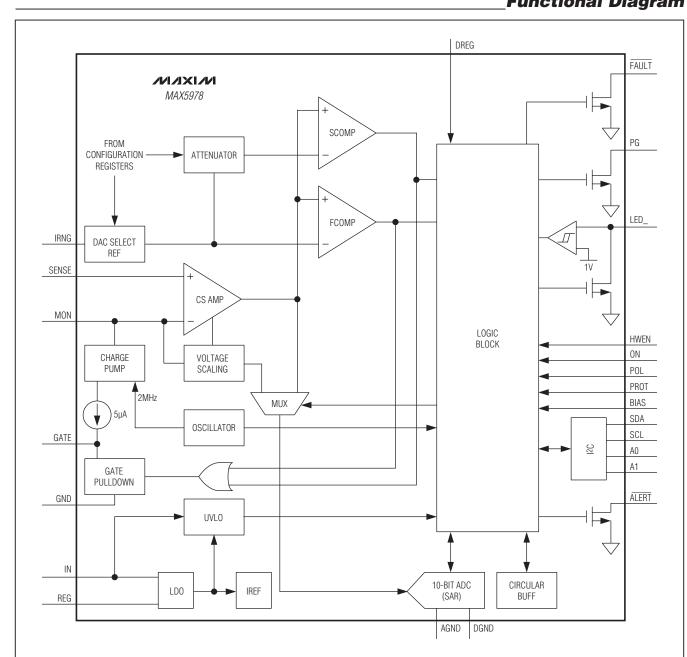

**Functional Diagram**

#### **Detailed Description**

The MAX5978 includes a set of registers that are accessed through the  $I^2C$  interface. Some of the registers are read only and some of the registers are read and write registers that can be updated to configure the device for a specific operation. See Tables 1a and 1b for the register maps.

#### Hot-Swap Channel On-Off Control

Depending on the configuration of the EN1 and EN2 bits, when VIN is above the VUVLO threshold and the ON input reaches its internal threshold, the device turns on the external n-channel MOSFET for the hot-swap channel, allowing power to flow to the load. The channel is enabled depending on the output of a majority function.

EN1, EN2, and ON are the inputs to the majority function and the channel is enabled when two or more of these inputs are 1:

$(Channel enabled) = (EN1 \times EN2) + (EN1 \times ON) + (EN2 \times ON)$

Inputs ON and EN2 can be set externally; the initial state of the EN2 bit in register chxen is set by the state of the HWEN input when VIN rises above VUVLO. The ON input connects to an internal precision analog comparators with a 0.6V threshold. Whenever VON is above 0.6V, the ON bit in register status1[0] is set to 1. Inputs EN1 and EN2 can be set using the I<sup>2</sup>C interface; the EN1 bit has a default value of 0. This makes it possible to enable or disable the hot-swap channel with or without using the I<sup>2</sup>C interface (see Tables 2, 3a, and 3b).

| REGISTER<br>NAME | DESCRIPTION                                                         | REGISTER<br>NUMBER | RESET<br>VALUE | READ/<br>WRITE |

|------------------|---------------------------------------------------------------------|--------------------|----------------|----------------|

| adc_cs_msb       | High 8 bits ([9:2]) of latest current-signal ADC result             | 0x00               | 0x00           | R              |

| adc_cs_lsb       | Low 2 bits ([1:0]) of latest current-signal ADC result              | 0x01               | 0x00           | R              |

| adc_mon_msb      | High 8 bits ([9:2]) of latest voltage-signal ADC result             | 0x02               | 0x00           | R              |

| adc_mon_lsb      | Low 2 bits ([1:0]) of latest voltage-signal ADC result              | 0x03               | 0x00           | R              |

| min_cs_msb       | High 8 bits ([9:2]) of current-signal minimum value                 | 0x08               | 0xFF           | R              |

| min_cs_lsb       | Low 2 bits ([1:0]) of current-signal minimum value                  | 0x09               | 0x03           | R              |

| max_cs_msb       | High 8 bits ([9:2]) of current-signal maximum value                 | 0x0A               | 0x00           | R              |

| max_cs_lsb       | Low 2 bits ([1:0]) of current-signal maximum value                  | 0x0B               | 0x00           | R              |

| min_mon_msb      | High 8 bits ([9:2]) of voltage-signal minimum value                 | 0x0C               | 0xFF           | R              |

| min_mon_lsb      | Low 2 bits ([1:0]) of voltage-signal minimum value                  | 0x0D               | 0x03           | R              |

| max_mon_msb      | High 8 bits ([9:2]) of voltage-signal maximum value                 | 0x0E               | 0x00           | R              |

| max_mon_lsb      | Low 2 bits ([1:0]) of voltage-signal maximum value                  | 0x0F               | 0x00           | R              |

| uv1th_msb        | High 8 bits ([9:2]) of undervoltage warning (UV1) threshold         | 0x1A               | 0x00           | R/W            |

| uv1th_lsb        | Low 2 bits ([1:0]) of undervoltage warning (UV1) threshold          | 0x1B               | 0x00           | R/W            |

| uv2th_msb        | High 8 bits ([9:2]) of undervoltage critical (UV2) threshold        | 0x1C               | 0x00           | R/W            |

| uv2th_lsb        | Low 2 bits ([1:0]) of undervoltage critical (UV2) threshold         | 0x1D               | 0x00           | R/W            |

| ov1thr_msb       | High 8 bits ([9:2]) of overvoltage warning (OV1) threshold          | 0x1E               | 0xFF           | R/W            |

| ov1thr_lsb       | Low 2 bits ([1:0]) of overvoltage warning (OV1) threshold           | 0x1F               | 0x03           | R/W            |

| ov2thr_msb       | High 8 bits ([9:2]) of overvoltage critical (OV2) threshold         | 0x20               | 0xFF           | R/W            |

| ov2thr_lsb       | Low 2 bits ([1:0]) of overvoltage critical (OV2) threshold          | 0x21               | 0x03           | R/W            |

| oithr_msb        | High 8 bits ([9:2]) of overcurrent warning threshold                | 0x22               | 0xFF           | R/W            |

| oithr_lsb        | Low 2 bits ([1:0]) of overcurrent warning threshold                 | 0x23               | 0x03           | R/W            |

| dac_fast         | Fast-comparator threshold DAC setting                               | 0x2E               | 0xBF           | R/W            |

| cbuf_ba_v        | Base address for block read of 50-sample voltage-signal data buffer | 0x46               |                | R              |

| cbuf_ba_i        | Base address for block read of 50-sample current-signal data buffer | 0x47               |                | R              |

#### Table 1a. Register Address Map (Channel Specific)

| REGISTER<br>NAME | DESCRIPTION                                                                                          | ADDRESS<br>(HEX CODE) | RESET<br>VALUE | READ/<br>WRITE |

|------------------|------------------------------------------------------------------------------------------------------|-----------------------|----------------|----------------|

| mon_range        | MON input range setting                                                                              | 0x18                  | 0x00           | R/W            |

| cbuf_chx_store   | Selective enabling of circular buffer                                                                | 0x19                  | 0x0F           | R/W            |

| ifast2slow       | Current threshold fast-to-slow ratio setting                                                         | 0x30                  | 0x0F           | R/W            |

| status0          | Slow-trip and fast-trip comparators status register                                                  | 0x31                  | 0x00           | R              |

| status1          | PROT, MODE, and ON inputs status register                                                            | 0x32                  | _              | R              |

| status2          | Fast-trip threshold maximum range setting bits, from IRNG three-<br>state input                      | 0x33                  | _              | R/W            |

| status3          | LATCH, POL, ALERT, and PG status register                                                            | 0x34                  | _              | R              |

| fault0           | Status register for undervoltage detection (warning or critical)                                     | 0x35                  | 0x00           | R/C            |

| fault1           | Status register for overvoltage detection (warning or critical)                                      | 0x36                  | 0x00           | R/C            |

| fault2           | Status register for overcurrent detection (warning)                                                  | 0x37                  | 0x00           | R/C            |

| pgdly            | Delay setting between MON measurement and PG assertion                                               | 0x38                  | 0x00           | R/W            |

| fokey            | Load register with 0xA5 to enable force-on function                                                  | 0x39                  | 0x00           | R/W            |

| foset            | Register that enables force-on function                                                              | 0x3A                  | 0x00           | R/W            |

| chxen            | Channel enable bits                                                                                  | 0x3B                  | _              | R/W            |

| dgl_i            | OC deglitch enable bits                                                                              | 0x3C                  | 0x00           | R/W            |

| dgl_uv           | UV deglitch enable bits                                                                              | 0x3D                  | 0x00           | R/W            |

| dgl_ov           | OV deglitch enable bits                                                                              | 0x3E                  | 0x00           | R/W            |

| cbufrd_hibyonly  | Circular buffers readout mode: 8 bit or 10 bit                                                       | 0x3F                  | 0x0F           | R/W            |

| cbuf_dly_stop    | Circular buffer stop delay; number of samples recorded to the circular buffer after channel shutdown | 0x40                  | 0x19           | R/W            |

| peak_log_rst     | Reset control bits for peak-detection registers                                                      | 0x41                  | 0x00           | R/W            |

| peak_log_hold    | Hold control bits for peak-detection registers                                                       | 0x42                  | 0x00           | R/W            |

| LED_flash        | LED flash/GPIO enable register                                                                       | 0x43                  | 0x0F           | R/W            |

| LED_ph_pu        | LED phase/weak pullup enable register                                                                | 0x44                  | 0x00           | R/W            |

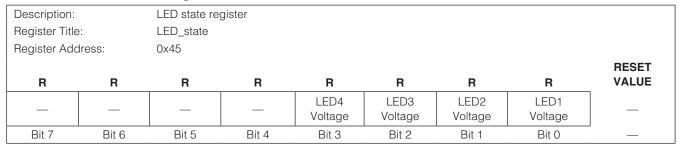

| LED_state        | LED pins voltage state register (LED pins set open)                                                  | 0x45                  |                | R              |

## Table 1b. Register Address Map (General)

## Table 2. chxen Register Format

| Description:   | Description: |       | able bits |        |        |       |       |            |

|----------------|--------------|-------|-----------|--------|--------|-------|-------|------------|

| Resister Title | :            | chxen |           |        |        |       |       |            |

| Register Add   | ress:        | 0x3B  |           |        |        |       |       |            |

|                |              |       |           |        |        |       |       | RESET      |

| R              | R            | R     | R         | R/W    | R/W    | R/W   | R/W   | VALUE      |

|                | —            | —     | _         | Unused | Unused | EN2   | EN1   | $\neg -  $ |

| Bit 7          | Bit 6        | Bit 5 | Bit 4     | Bit 3  | Bit 2  | Bit 1 | Bit 0 |            |

| REGISTER<br>ADDRESS | BIT RANGE | DESCRIPTION                                                               |  |  |  |  |  |

|---------------------|-----------|---------------------------------------------------------------------------|--|--|--|--|--|

|                     |           | ON input state                                                            |  |  |  |  |  |

|                     |           | 1 = ON above 600mV channel enable threshold                               |  |  |  |  |  |

|                     | [1:0]     | 0 = ON below 600mV channel enable threshold                               |  |  |  |  |  |

|                     |           | Bit 0: ON input state                                                     |  |  |  |  |  |

|                     |           | Bit 1: unused                                                             |  |  |  |  |  |

| 0x32                | [4]       | Unused                                                                    |  |  |  |  |  |

|                     |           | Voltage critical behavior (PROT input)                                    |  |  |  |  |  |

|                     |           | 00 = Assert ALERT upon UV/OV critical (same as UV/OV warning behavior)    |  |  |  |  |  |

|                     | [7:6]     | 01 = Assert ALERT and deassert PG upon UV/OV critical                     |  |  |  |  |  |

|                     |           | 10 = Assert ALERT, deassert PG, and shut down channel upon UV/OV critical |  |  |  |  |  |

|                     |           | 11 = (Not possible)                                                       |  |  |  |  |  |

#### Table 3a. Register Function

#### Table 3b. status1 Register Format

| Description:    |         | Fault-dete | Fault-detection behavior (three-state PROT input) and ON input status register |       |       |        |       |       |  |  |

|-----------------|---------|------------|--------------------------------------------------------------------------------|-------|-------|--------|-------|-------|--|--|

| Resister Title: |         | status1    |                                                                                |       |       |        |       |       |  |  |

| Register Addr   | ess:    | 0x32       |                                                                                |       |       |        |       |       |  |  |

|                 |         |            |                                                                                |       |       |        |       | RESET |  |  |

| R               | R       | R          | R                                                                              | R     | R     | R      | R     | VALUE |  |  |

| prot[1]         | prot[0] | _          | Unused                                                                         | —     | —     | Unused | ON    | ] _   |  |  |

| Bit 7           | Bit 6   | Bit 5      | Bit 4                                                                          | Bit 3 | Bit 2 | Bit 1  | Bit 0 |       |  |  |

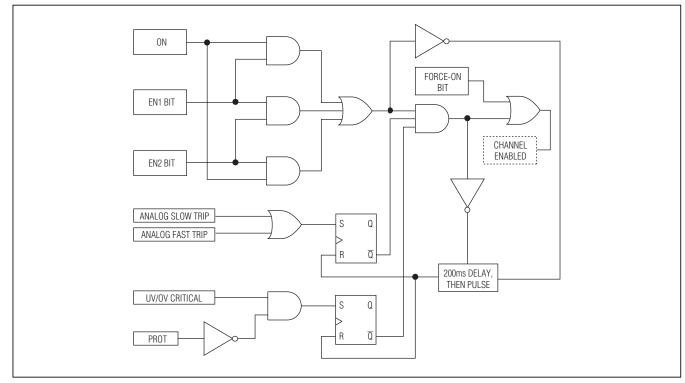

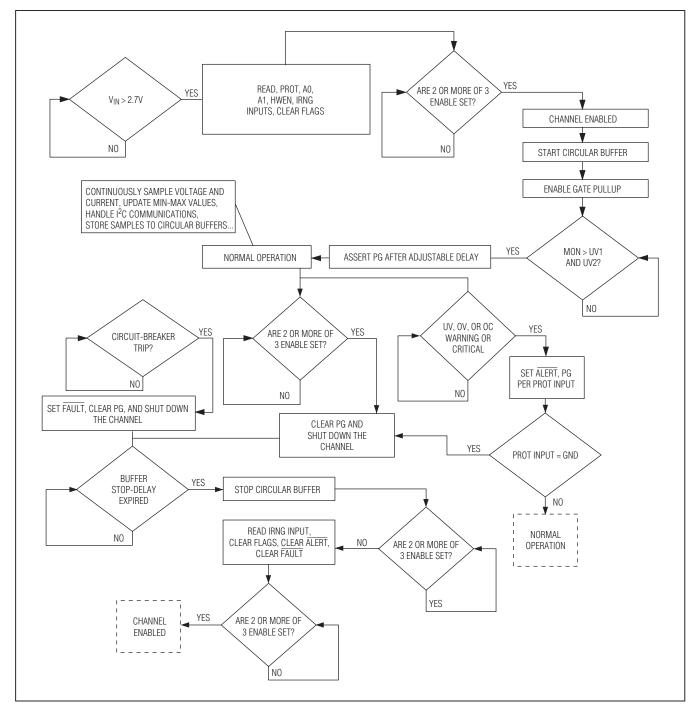

Figure 1 shows the detailed logic operation of the hotswap enable signals EN1, EN2, and ON, as well as the effect of various fault conditions.

An input undervoltage threshold control for enabling the hot-swap channel can be implemented by placing a resistive divider between the drain of the hot-swap MOSFET and ground, with the midpoint connected to ON. The turn-on threshold voltage for the channel is then:

#### $V_{EN} = 0.6V \times (R1 + R2)/R2$

The maximum rating for the ON input is 6V; do not exceed this value.

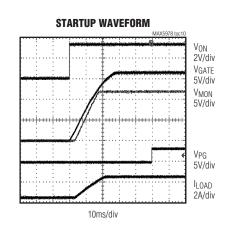

#### Startup

When all conditions for channel turn-on are met, the external n-channel MOSFET switch is fully enhanced with a typical gate-to-source voltage of 5V to ensure a low drain-to-source resistance. The charge pump at the GATE driver sources  $5\mu$ A to control the output voltage turn-on voltage slew rate. An external capacitor can be added from GATE to GND to further reduce the

voltage slew rate. Placing a  $1k\Omega$  resistor in series with this capacitance prevents the added capacitance from increasing the gate turn-off time. Total inrush current is the load current summed with the product of the gate-voltage slew rate dV/dt and the load capacitance.

To determine the output dV/dt during startup, divide the GATE pullup current  $I_G(UP)$  by the gate-to-ground capacitance. The voltage at the source of the external MOSFET follows the gate voltage, so the load dV/dt is the same as the gate dV/dt. Inrush current is the product of the dV/dt and the load capacitance. The time to start up t<sub>SU</sub> is the hot-swap voltage V<sub>S</sub> divided by the output dV/dt.

Be sure to choose an external MOSFET that can handle the power dissipated during startup. The inrush current is roughly constant during startup and the voltage drop across the MOSFET (drain to source) decreases linearly as the load capacitance charges. The resulting power dissipation is, therefore, roughly equivalent to a single pulse of magnitude (V<sub>S</sub> x inrush current)/2 and

Figure 1. Channel On-Off Control Logic Functional Schematic

duration tsU. Refer to the thermal resistance charts in the MOSFET data sheet to determine the junction temperature rise during startup, and ensure that this does not exceed the maximum junction temperature for worstcase ambient conditions.

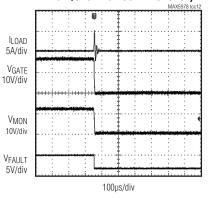

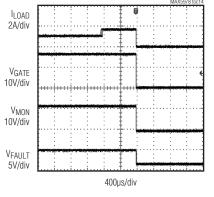

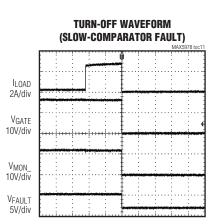

#### **Circuit-Breaker Protection**

As the channel is turned on and during normal operation, two analog comparators are used to detect an overcurrent condition by sensing the voltage across an external resistor connected between SENSE and MON. If the voltage across the sense resistor is less than the slow-trip and fast-trip circuit-breaker thresholds, the GATE output remains high. If either of the thresholds is exceeded due to an overcurrent condition, the gate of the MOSFET is pulled down to MON by an internal 500mA current source.

The higher of the two comparator thresholds, the fast trip, is set by an internal 8-bit DAC (see Table 7), within one of three configurable full-scale current-sense

ranges: 25mV, 50mV, or 100mV (see Tables 6a and 6b). The 8-bit fast-trip threshold DAC can be programmed from 40% to 100% of the selected full-scale currentsense range. The slow-trip threshold follows the fast-trip threshold as one of four programmable ratios, set by the ifast2slow register (see Tables 4a and 4b).

The fast-trip threshold is always higher than the slow-trip threshold, and the fast-trip comparator responds very quickly to protect the system against sudden, severe overcurrent events. The slower response of the slowtrip comparator varies depending upon the amount of overdrive beyond the slow-trip threshold. If the overdrive is small and short lived, the comparator will not shut down the affected channel. As the overcurrent event increases in magnitude, the response time of the slowtrip comparator decreases. This scheme provides good noise rejection and spurious overcurrent transients near the slow-trip threshold, while aggressively protecting the system against larger overcurrent events that occur as a result of a load fault.

#### Table 4a. ifast2slow Register Format

| Description:   |        | Current thre | Current threshold fast-to-slow setting bits |        |        |       |       |       |  |  |

|----------------|--------|--------------|---------------------------------------------|--------|--------|-------|-------|-------|--|--|

| Resister Title | :      | ifast2slow   | ifast2slow                                  |        |        |       |       |       |  |  |

| Register Add   | lress: | 0x30         |                                             |        |        |       |       |       |  |  |

|                |        |              |                                             |        |        |       |       | RESET |  |  |

| R              | R      | R            | R                                           | R/W    | R/W    | R/W   | R/W   | VALUE |  |  |

| _              | _      |              | _                                           | Unused | Unused | FS1   | FS0   | 0x0F  |  |  |

| Bit 7          | Bit 6  | Bit 5        | Bit 4                                       | Bit 3  | Bit 2  | Bit 1 | Bit 0 |       |  |  |

#### Table 4b. Setting Fast-Trip to Slow-Trip Threshold Ratio

| FS1 | FS0 | FAST-TRIP TO SLOW-TRIP RATIO (%) |

|-----|-----|----------------------------------|

| 0   | 0   | 125                              |

| 0   | 1   | 150                              |

| 1   | 0   | 175                              |

| 1   | 1   | 200                              |

#### **Setting Circuit-Breaker Thresholds**

To select and set the device slow-trip and fast-trip comparator thresholds, use the following procedure:

- Select one of four ratios between the fast-trip threshold and the slow-trip threshold: 200%, 175%, 150%, or 125%. A system that experiences brief but large transient load currents should use a higher ratio, whereas a system that operates continuously at higher average load currents might benefit from a smaller ratio to ensure adequate protection. The ratio is set by writing to the ifast2slow register. (The default setting on power-up is 200%.)

- 2) Determine the slow-trip threshold VTH,ST based on the anticipated maximum continuous load current during normal operation, and the value of the current-sense resistor. The slow-trip threshold should include some margin (possibly 20%) above the maximum load current to prevent spurious circuit-breaker shutdown and to accommodate passive component tolerances:

VTH,ST = RSENSE × ILOAD,MAX × 120%

3) Calculate the necessary fast-trip threshold VTH,FT based on the ratio set in step 1:

VTH,FT = VTH,ST x (ifast2slow ratio)

4) Select one of the three maximum current-sense ranges: 25mV, 50mV, or 100mV. The current-sense

range is initially set upon power-up by the state of the IRNG input, but can be altered at any time by writing to the status2 register. For maximum accuracy and best measurement resolution, select the lowest current-sense range that is larger than the VTH,FT value calculated in step 3.

5) Program the fast-trip and slow-trip thresholds by writing an 8-bit value to the dac\_fast register. This 8-bit value is determined from the desired V<sub>TH,ST</sub> value that was calculated in step 2, the threshold ratio from step 1, and the current-sense range from step 4:

The device provides a great deal of system flexibility because the current-sense range, DAC setting, and threshold ratio can be changed "on the fly" for systems that must protect a wide range of interchangeable load devices, or for systems that control the allocation of power to smart loads. Table 5 shows the specified ranges for the fast-trip and slow-trip thresholds for all combinations of current-sense range and threshold ratio.

When an overcurrent event causes the device to shut down the power channel, the open-drain FAULT output alerts the system. Figure 2 shows the operation and faultmanagement flowchart.

## Table 5. Specified Current-Sense and Circuit-Breaker Threshold Ranges

| IRNG<br>INPUT | DAC OUTPUT RANGE<br>(DEFAULT = FULL<br>SCALE) (mV) | FAST-TRIP<br>THRESHOLD RANGE<br>(mV) | GAIN (2 BIT) (VFAST/<br>VsLOW)<br>ifast2slow<br>(DEFAULT = 11) | SLOW-TRIP<br>THRESHOLD RANGE<br>(mV) |

|---------------|----------------------------------------------------|--------------------------------------|----------------------------------------------------------------|--------------------------------------|

|               |                                                    |                                      | 00 (125%)                                                      | 8.00 to 20.00                        |

| Low           | 10 to 25                                           | 10 to 25                             | 01 (150%)                                                      | 6.67 to 16.67                        |

| LOW           | 10 10 25                                           | 10 10 25                             | 10 (175%)                                                      | 5.71 to 14.29                        |

|               |                                                    |                                      | 11 (200%)                                                      | 5.00 to 12.50                        |

|               |                                                    |                                      | 00 (125%)                                                      | 16.00 to 40.00                       |

| Llieb         | 20 to 50                                           | 20 to 50                             | 01 (150%)                                                      | 13.33 to 33.33                       |

| High          | 20 to 50                                           | 201050                               | 10 (175%)                                                      | 11.48 to 28.57                       |

|               |                                                    |                                      | 11 (200%)                                                      | 10.00 to 25.00                       |

|               |                                                    |                                      | 00 (125%)                                                      | 32.00 to 80.00                       |

| Linconnected  | 40 to 100                                          | 40 to 100                            | 01 (150%)                                                      | 26.67 to 66.67                       |

| Unconnected   | 40 to 100                                          | 40 to 100                            | 10 (175%)                                                      | 22.86 to 57.14                       |

|               |                                                    |                                      | 11 (200%)                                                      | 20.00 to 50.00                       |

#### Table 6a. IRNG Input Status Register Format

| Description:   |       | Fast-trip th | Fast-trip threshold maximum range-setting bits, from IRNG three-state input |        |        |       |       |       |  |  |  |

|----------------|-------|--------------|-----------------------------------------------------------------------------|--------|--------|-------|-------|-------|--|--|--|

| Resister Title |       | status2      |                                                                             |        |        |       |       |       |  |  |  |

| Register Add   | ress: | 0x33         |                                                                             |        |        |       |       |       |  |  |  |

|                |       |              |                                                                             |        |        |       |       | RESET |  |  |  |

| R              | R     | R            | R                                                                           | R/W    | R/W    | R/W   | R/W   | VALUE |  |  |  |

|                | _     | _            |                                                                             | Unused | Unused | IRNG1 | IRNG0 |       |  |  |  |

| Bit 7          | Bit 6 | Bit 5        | Bit 4                                                                       | Bit 3  | Bit 2  | Bit 1 | Bit 0 |       |  |  |  |

#### Table 6b. Setting Current-Sense Range

| IRNG PIN STATE | IRNG1 | IRNG0 | MAXIMUM CURRENT-SENSE SIGNAL (mV) |

|----------------|-------|-------|-----------------------------------|

| Low            | 1     | 0     | 25                                |

| High           | 0     | 1     | 50                                |

| Open           | 0     | 0     | 100                               |

#### Table 7. dac\_ch\_ Register Format

| Description:             |        | Fast-compara | ator threshold D | AC setting |        |        |        |       |

|--------------------------|--------|--------------|------------------|------------|--------|--------|--------|-------|

| Register Title: dac_fast |        |              |                  |            |        |        |        |       |

| Register Addr            | esses: | 0x2E         |                  |            |        |        |        |       |

|                          |        |              |                  |            |        |        |        | RESET |

| R/W                      | R/W    | R/W          | R/W              | R/W        | R/W    | R/W    | R/W    | VALUE |

| DAC[7]                   | DAC[6] | DAC[5]       | DAC[4]           | DAC[3]     | DAC[2] | DAC[1] | DAC[0] | 0xBF  |

| Bit 7                    | Bit 6  | Bit 5        | Bit 4            | Bit 3      | Bit 2  | Bit 1  | Bit 0  | _     |

Figure 2. Operation and Fault-Management Flowchart for Hot-Swap Channel

#### **Digital Current Monitoring**

The current-sense signal is sampled by the internal 10-bit, 10ksps ADC, and the most recent results are stored in registers for retrieval through the I<sup>2</sup>C interface. The current conversion values are 10 bits wide, with the 8 high-order bits written to one 8-bit register and the 2 low-order bits written to the next-higher 8-bit register address (Tables 8 and 9). This allows use of just the high-order byte in applications where 10-bit precision is not required. This split 8-bit/2-bit storage scheme is used

throughout the device for ADC conversion results and digital comparator thresholds.

Once the PG output is asserted, the current-sense samples are continuously compared to the programmable overcurrent warning register value. If the measured current value exceeds the warning level, the ALERT output is asserted. The device response to this digital comparator is not altered by the setting of the PROT input (Tables 10 and 11).

## Table 8. ADC Current-Conversion Results Register Format (High-Order Bits)

| Description:    |        | Most recent c | Most recent current-conversion result, high-order bits [9:2] |        |        |        |        |       |  |  |

|-----------------|--------|---------------|--------------------------------------------------------------|--------|--------|--------|--------|-------|--|--|

| Register Title: |        | adc_cs_msb    |                                                              |        |        |        |        |       |  |  |

| Register Addr   | esses: | 0x00          |                                                              |        |        |        |        |       |  |  |

|                 |        |               |                                                              |        |        |        |        | RESET |  |  |

| R               | R      | R             | R                                                            | R      | R      | R      | R      | VALUE |  |  |

| inew_9          | inew_8 | inew_7        | inew_6                                                       | inew_5 | inew_4 | inew_3 | inew_2 | 0x00  |  |  |

| Bit 7           | Bit 6  | Bit 5         | Bit 4                                                        | Bit 3  | Bit 2  | Bit 1  | Bit 0  | —     |  |  |

#### Table 9. ADC Current-Conversion Results Register Format (Low-Order Bits)

| Description:   |         | Most recent c | Most recent current-conversion result, low-order bits [0:1] |       |       |        |        |       |  |

|----------------|---------|---------------|-------------------------------------------------------------|-------|-------|--------|--------|-------|--|

| Register Title |         | adc_cs_ lsb   |                                                             |       |       |        |        |       |  |

| Register Add   | resses: | 0x01          | Ix01                                                        |       |       |        |        |       |  |

|                |         |               |                                                             |       |       |        |        | RESET |  |

| R              | R       | R             | R                                                           | R     | R     | R      | R      | VALUE |  |

|                |         |               | —                                                           |       | —     | inew_1 | inew_0 | 0x00  |  |

| Bit 7          | Bit 6   | Bit 5         | Bit 4                                                       | Bit 3 | Bit 2 | Bit 1  | Bit 0  |       |  |

#### Table 10. Overcurrent Warning Threshold Register Format (High-Order Bits)

| Description:   |         | Overcurrent warning threshold high-order bits [9:2] |       |       |       |       |       |       |

|----------------|---------|-----------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Register Title | :       | oithr_msb                                           |       |       |       |       |       |       |

| Register Add   | resses: | 0x22                                                |       |       |       |       |       |       |

|                |         |                                                     |       |       |       |       |       | RESET |

| R/W            | R/W     | R/W                                                 | R/W   | R/W   | R/W   | R/W   | R/W   | VALUE |

| oi_9           | oi_8    | oi_7                                                | oi_6  | oi_5  | oi_4  | oi_3  | oi_2  | 0xFF  |

| Bit 7          | Bit 6   | Bit 5                                               | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |       |

#### Table 11. Overcurrent Warning Threshold Register Format (Low-Order Bits)

| Description:    |        | Overcurrent warning threshold low-order bits [1:0] |       |       |       |       |       |       |

|-----------------|--------|----------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Register Title: |        | oithr_lsb                                          |       |       |       |       |       |       |

| Register Addr   | esses: | 0x23                                               |       |       |       |       |       |       |

|                 |        |                                                    |       |       |       |       |       | RESET |

| R/W             | R/W    | R/W                                                | R/W   | R/W   | R/W   | R/W   | R/W   | VALUE |

|                 | —      | —                                                  | —     |       | —     | oi_1  | oi_0  | 0x03  |

| Bit 7           | Bit 6  | Bit 5                                              | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |       |

#### Minimum and Maximum Value Detection for Current-Measurement Values

Current-sense measurement values from the ADC are continuously compared with the contents of minimumand maximum-value registers, and if the most recent measurement exceeds the stored maximum, or is less than the stored minimum, the corresponding register is updated with the new value. These "peak-detection" registers are read/write accessible through the I<sup>2</sup>C interface (Tables 12–15). The minimum-value registers are reset to 0xFF and the maximum-value registers are reset to 0x00. These reset values are loaded upon startup of the channel or at any time as commanded by register peak\_log\_rst (Table 35).

## Table 12. ADC Minimum Current-Conversion Register Format (High-Order Bits)

| Description:    |                            | Minimum current-conversion result high-order bits [9:2] |        |        |        |        |        |       |

|-----------------|----------------------------|---------------------------------------------------------|--------|--------|--------|--------|--------|-------|

| Register Title: | Register Title: min_cs_msb |                                                         |        |        |        |        |        |       |

| Register Addre  | esses:                     | 80x0                                                    |        |        |        |        |        |       |

|                 |                            |                                                         |        |        |        |        |        | RESET |

| R               | R                          | R                                                       | R      | R      | R      | R      | R      | VALUE |

| imin_9          | imin_8                     | imin_7                                                  | imin_6 | imin_5 | imin_4 | imin_3 | imin_2 | 0xFF  |

| Bit 7           | Bit 6                      | Bit 5                                                   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |       |

## Table 13. ADC Minimum Current-Conversion Register Format (Low-Order Bits)

| Description:    |        | Minimum curr | Minimum current-conversion result low-order bits [1:0] |       |       |        |        |       |  |

|-----------------|--------|--------------|--------------------------------------------------------|-------|-------|--------|--------|-------|--|

| Register Title: |        | min_cs_ lsb  |                                                        |       |       |        |        |       |  |

| Register Addr   | esses: | 0x09         |                                                        |       |       |        |        |       |  |

|                 |        |              |                                                        |       |       |        |        | RESET |  |

| R               | R      | R            | R                                                      | R     | R     | R      | R      | VALUE |  |

| _               | _      | _            | —                                                      | _     | _     | imin_1 | imin_0 | 0x03  |  |

| Bit 7           | Bit 6  | Bit 5        | Bit 4                                                  | Bit 3 | Bit 2 | Bit 1  | Bit 0  |       |  |

## Table 14. ADC Maximum Current-Conversion Register Format (High-Order Bits)

| Description:    |        | Maximum cur | Maximum current-conversion result high-order bits [9:2] |        |        |        |        |       |  |

|-----------------|--------|-------------|---------------------------------------------------------|--------|--------|--------|--------|-------|--|

| Register Title: |        | max_cs_msb  | max_cs_msb                                              |        |        |        |        |       |  |

| Register Addr   | esses: | 0x0A        | AOX                                                     |        |        |        |        |       |  |

|                 |        |             |                                                         |        |        |        |        | RESET |  |

| R               | R      | R           | R                                                       | R      | R      | R      | R      | VALUE |  |

| imax_9          | imax_8 | imax_7      | imax_6                                                  | imax_5 | imax_4 | imax_3 | imax_2 | 0x00  |  |

| Bit 7           | Bit 6  | Bit 5       | Bit 4                                                   | Bit 3  | Bit 2  | Bit 1  | Bit 0  |       |  |

## Table 15. ADC Maximum Current-Conversion Register Format (Low-Order Bits)

| Description:   |         | Maximum cur | Maximum current-conversion result low-order bits [1:0] |       |       |        |        |       |  |  |

|----------------|---------|-------------|--------------------------------------------------------|-------|-------|--------|--------|-------|--|--|

| Register Title |         | max_cs_lsb  | max_cs_lsb                                             |       |       |        |        |       |  |  |

| Register Add   | resses: | 0x0B        |                                                        |       |       |        |        |       |  |  |

|                |         |             |                                                        |       |       |        |        | RESET |  |  |

| R              | R       | R           | R                                                      | R     | R     | R      | R      | VALUE |  |  |

| —              | —       | _           | —                                                      | —     | _     | imax_1 | imax_0 | 0x00  |  |  |

| Bit 7          | Bit 6   | Bit 5       | Bit 4                                                  | Bit 3 | Bit 2 | Bit 1  | Bit 0  |       |  |  |

# **MAX5978**

#### Digital Voltage Monitoring and Power-Good Output

The voltage at the load (MON input) is sampled by the internal ADC. The MON full-scale voltage can be set to 16V, 8V, 4V, or 2V by writing to register mon\_range. The default range is 16V (Tables 16 and 17).

The most recent voltage-conversion results can be read from the adc\_mon\_msb and adc\_mon\_lsb registers (see Tables 18 and 19).

#### Digital Undervoltage- and Overvoltage-Detection Thresholds

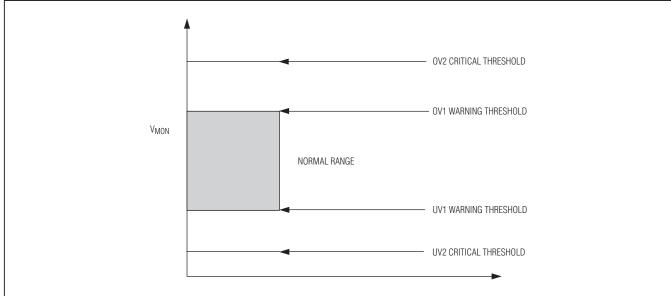

The most recent voltage values are continuously compared to four programmable limits, comprising two undervoltage (UV) levels (see Tables 20 to 23) and two overvoltage (OV) levels (see Tables 24 to 27).

If PG is asserted and the voltage is outside the warning limits, the ALERT output is asserted low. Depending on the status of the prot[] bits in register status1[7:6], the

## Table 16. ADC Voltage Monitor Settings Register Format

| Description:    |         | ADC voltage | monitor full-sc | ale range settir | ngs (for MON i | nput)    |          |       |

|-----------------|---------|-------------|-----------------|------------------|----------------|----------|----------|-------|

| Register Title: |         | mon_range   | mon_range       |                  |                |          |          |       |

| Register Add    | resses: | 0x18        | IX18            |                  |                |          |          |       |

|                 |         |             |                 |                  |                |          |          | RESET |

| R/W             | R/W     | R/W         | R/W             | R/W              | R/W            | R/W      | R/W      | VALUE |