## **Energy Measurement AFE**

## **General Description**

The MAX71020A is a single-chip analog front-end (AFE) for use in embedded energy measurement applications. It contains the compute engine (CE) found in Maxim Integrated's fourth-generation meter system-on-chip (SoC) and an improved analog-to-digital converter (ADC). It interfaces to a host controller of choice over a SPI interface.

The MAX71020A comes in a 28-pin TQFN package.

## **Applications**

- Grid-Friendly Appliances and Smart Plugs

- Power Distribution Units

- Building Automation Systems

Ordering Information appears at end of data sheet.

### **Benefits and Features**

- Best-in-Class Embedded Algorithms Support Highly Accurate Electricity Measurements

- · Voltage, Current, and Frequency

- · Active, Reactive, and Apparent Power/Energy

- Digital Temperature Compensation

- 40Hz–70Hz Line Frequency Range and Phase Compensation (±10°)

- Advanced AFE with Exceptional Accuracy and Temperature Stability

- Voltage Reference Temperature Coefficient: 40ppm/°C (max)

- · On-Chip Digital Temperature Sensor

- 24-Bit 2nd Order Delta-Sigma ADCs with Differential and Single-Ended Inputs

- ±0.1% Wh Accuracy over 2000:1 Current Range

- Highly Integrated Features Support Compact Design Cycles and Reduced Bill of Materials

- Small, 28-Pin TQFN Package

- Digital Temperature Compensation

- Low Power Consumption

- Less Than 5mA (typ) Consumption at 3.3V

- · Simple Host Interface

- · SPI Slave

- · Atomic Measurements Outputs

- · DIO or SPI-Based Status Signals

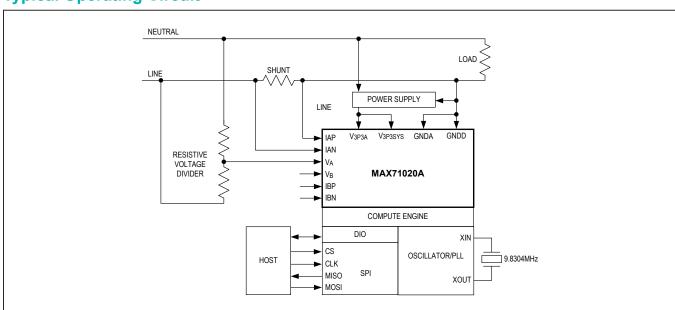

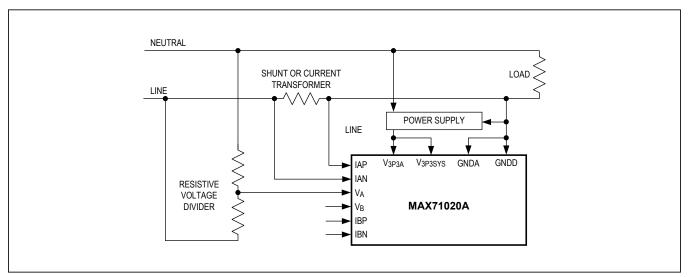

## **Typical Operating Circuit**

Soldering Temperature (reflow) .....+250°C

## **Absolute Maximum Ratings**

| (All voltages with respect to GNDA.)                  | Digital Pins                                                     |

|-------------------------------------------------------|------------------------------------------------------------------|

| Voltage and Current Supplies and Ground Pins          | Inputs(-10mA to +10mA), (-0.5V to +6V)                           |

| V <sub>3P3SYS</sub> , V <sub>3P3A</sub> 0.5V to +4.6V | Outputs (-10mA to +10mA), (-0.5V to (V <sub>3P3SYS</sub> + 0.5V) |

| GNDD0.1V to +0.1V                                     | Temperature and ESD Stress                                       |

| Analog Input Pins                                     | Operating Junction Temperature (peak, 100ms)+140°C               |

| AP, IAN, IBP, IBN,                                    | Operating Junction Temperature (continuous)+125°C                |

| VA, VB(-10mA to +10mA), (-0.5V to +0.5V)              | Storage Temperature Range45°C to +165°C                          |

| XIN, XOUT(-10mA to +10mA), (-0.5V to +3.0V)           | ESD Stress on All Pins±4kV, HBM                                  |

|                                                       | Lead Temperature (soldering, 10s)+300°C                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Thermal Characteristics (Note 1)**

**TQFN**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......35°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......3°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maximintegrated.com/thermal-tutorial**.

## **Electrical Characteristics**

| PARAMETER                                                       | CONDITIONS                                       | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------------|--------------------------------------------------|-----|-----|-----|-------|

| RECOMMENDED OPERATING                                           | CONDITIONS                                       |     |     |     |       |

| V <sub>3P3SYS</sub> and V <sub>3P3A</sub> Supply                | Precision metering operation                     | 3.0 |     | 3.6 | V     |

| Voltage                                                         | Digital operation (Notes 2, 3)                   | 2.8 |     | 3.6 | \ \ \ |

| Operating Temperature                                           |                                                  | -40 |     | +85 | °C    |

| INPUT LOGIC LEVELS                                              |                                                  |     |     |     |       |

| Digital High-Level Input<br>Voltage (V <sub>IH</sub> )          |                                                  |     | 2   |     | V     |

| Digital Low-Level Input Voltage (V <sub>IL</sub> )              |                                                  |     | 0.8 |     | V     |

| Input Pullup Current (I <sub>IL</sub> )<br>RESETZ               | V <sub>3P3SYS</sub> = 3.6V, V <sub>IN</sub> = 0V | 41  | 78  | 115 | μA    |

| Input Pullup Current (I <sub>IL</sub> )<br>Other Digital Inputs | V <sub>3P3SYS</sub> = 3.6V, V <sub>IN</sub> = 0V | -1  | 0   | +1  | μA    |

| Input Pulldown Current (I <sub>IH</sub> ) All Pins              | V <sub>IN</sub> = V <sub>3P3SYS</sub>            | -1  | 0   | +1  | μA    |

| PARAMETER                                                          | CONDITIONS                                                          | MIN                          | TYP       | MAX       | UNITS |  |

|--------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------|-----------|-----------|-------|--|

| OUTPUT LOGIC LEVELS                                                |                                                                     |                              |           |           |       |  |

| Digital High-Level Output                                          | I <sub>LOAD</sub> = 1mA                                             | V <sub>3P3SYS</sub><br>- 0.4 |           |           | V     |  |

| Voltage (V <sub>OH</sub> )                                         | I <sub>LOAD</sub> = 15mA (Note 3)                                   | V <sub>3P3SYS</sub><br>- 1.1 |           |           | V     |  |

| Digital Low-Level Output                                           | I <sub>LOAD</sub> = 1mA                                             | 0                            |           | 0.4       | V     |  |

| Voltage (V <sub>OL</sub> )                                         | I <sub>LOAD</sub> = 15mA (Note 3)                                   | 0                            |           | 0.96      | \ \ \ |  |

| TEMPERATURE MONITOR                                                |                                                                     |                              |           |           |       |  |

| TNOM (Nominal value at 22°C)                                       | V <sub>3P3A</sub> = 3.3V                                            |                              | 956       |           | LSB   |  |

| Temperature Measurement Equation                                   |                                                                     | Temp = 0.3                   | 3 x STEMF | P + 21.77 | °C    |  |

| Tomorotura France (Noto 4)                                         | T <sub>A</sub> = -40°C to +85°C                                     | -6                           |           | +6        | - °C  |  |

| Temperature Error (Note 4)                                         | T <sub>A</sub> = -20°C to +60°C                                     | -4.8                         |           | +4.8      |       |  |

| Duration of Temperature<br>Measurement After Setting<br>TEMP_START | TEMP_PER = 0                                                        | 15                           |           | 60        | ms    |  |

| SUPPLY CURRENT PERFORMA                                            | NCE SPECIFICATIONS                                                  |                              |           |           | 1     |  |

| V <sub>3P3A</sub> + V <sub>3P3SYS</sub> Current<br>(Note 4)        | V <sub>3P3A</sub> = V <sub>3P3SYS</sub> = 3.3V, CE_E = 1, ADC_E = 1 |                              | 3         | 4.3       | mA    |  |

| INTERNAL POWER-FAULT COM                                           | PARATOR SPECIFICATIONS                                              |                              |           |           |       |  |

| Overall Beanance Time                                              | 100mV overdrive, falling                                            | 20                           |           | 200       |       |  |

| Overall Response Time                                              | 100mV overdrive, rising                                             | 8                            |           | 200       | μs    |  |

|                                                                    | 3.0V comparator                                                     | 2.83                         | 2.93      | 3.03      | V     |  |

| Falling Threshold                                                  | 2.8V comparator                                                     | 2.75                         | 2.81      | 2.89      | V     |  |

|                                                                    | Difference 3.0V and 2.8V comparators                                | 50                           | 136       | 220       | mV    |  |

| Hysteresis (Rising Threshold                                       | 3.0V comparator, T <sub>A</sub> = +22°C                             | 17                           | 45        | 74        | mV    |  |

| Falling Threshold)                                                 | 2.8V comparator, T <sub>A</sub> = +22°C                             | 15                           | 42        | 70        | IIIV  |  |

| PLL PERFORMANCE SPECIFIC                                           | ATIONS                                                              |                              |           |           |       |  |

| PLL Power-Up Settling Time                                         | $V_{3P3A}$ = 0 to 3.3V step, measured from first edge of MCK        |                              | 75        |           | μs    |  |

| PLL_FAST Settling Time                                             | V <sub>3P3A</sub> = 3.3V, PLL_FAST rise                             |                              | 10        |           | μs    |  |

| T LL_I AGT Gettilly Tille                                          | V <sub>3P3A</sub> = 3.3V, PLL_FAST fall                             |                              | 10        |           | μs    |  |

| PLL Lock Frequency at XOUT                                         | V <sub>3P3A</sub> = 3.3V, MCK frequency error < 1%                  | 7                            | 9.8       | 13        | MHz   |  |

| PARAMETER                                                                                                                                | CONDITION                                                                       | S                          | MIN    | TYP                                      | MAX    | UNITS              |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------|--------|------------------------------------------|--------|--------------------|--|--|

| V <sub>REF</sub> PERFORMANCE SPECIFIC                                                                                                    | CATIONS                                                                         | ,                          |        | -                                        |        |                    |  |  |

| V <sub>REF</sub> Output Voltage, V <sub>REF</sub> (22)                                                                                   | T <sub>A</sub> = +22°C                                                          |                            | 1.200  | 1.205                                    | 1.210  | V                  |  |  |

| V <sub>REF</sub> Power-Supply Sensitivity (DVREF/DV3P3A)                                                                                 | V <sub>3P3A</sub> = 3.0V to 3.6V                                                |                            | -1.5   |                                          | +1.5   | mV/V               |  |  |

| V <sub>NOM</sub> Definition                                                                                                              |                                                                                 |                            |        | ) = V <sub>REF(22)</sub><br>2) + TC2(T - |        | V                  |  |  |

| V <sub>NOM</sub> Temperature<br>Coefficient TC1                                                                                          |                                                                                 |                            | 29.32  | ? - 1.05 x TR                            | IMT    | μV/°C              |  |  |

| V <sub>NOM</sub> Temperature<br>Coefficient TC2                                                                                          |                                                                                 |                            | -0.56  | - 0.004 x TR                             | RIMT   | μV/°C <sup>2</sup> |  |  |

| VREF(T) Deviation from VNOM(T):  VREF(T) – VNOM(T)10 6 VNOM(T) 62                                                                        | (Note 4)                                                                        |                            | -40    |                                          | +40    | ppm/°C             |  |  |

| ADC CONVERTER PERFORMAN                                                                                                                  | ICE SPECIFICATIONS                                                              |                            |        |                                          |        |                    |  |  |

| Recommended Input Range (with Respect to GNDA)                                                                                           | V <sub>A</sub> , V <sub>B</sub> , IBP, IBN                                      |                            | -250   |                                          | +250   | mV <sub>PK</sub>   |  |  |

| Recommended Input Range                                                                                                                  | IAP, IAN: preamplifier enabled                                                  |                            | -27.78 |                                          | +27.78 | mVpk               |  |  |

| (with Respect to GNDA)                                                                                                                   | IAP, IAN: preamplifier disabled                                                 |                            | -250   |                                          | +250   | Пітрк              |  |  |

| Input Impedance, No<br>Preamplifier                                                                                                      | f <sub>IN</sub> = 65Hz                                                          |                            | 50     |                                          | 100    | kΩ                 |  |  |

| ADC Gain Error Vs. % of Supply Variation $\frac{10^6 \Delta \text{NOUT}_{PK} 357 \text{nV/V}_{IN}}{100  \Delta \text{V}_{3P3A}  /  3.3}$ | V <sub>IN</sub> = 200mV peak, 65Hz; V <sub>3P</sub>                             | <sub>3A</sub> = 3.0V, 3.6V |        |                                          | 81     | ppm/%              |  |  |

| Input Offset                                                                                                                             | IAP = IAN = GNDA                                                                |                            | -10    |                                          | +10    | mV                 |  |  |

| Total Harmonic Distortion at 250mV <sub>PK</sub>                                                                                         | V <sub>IN</sub> = 55Hz, 250mV <sub>PK</sub> , 64kpts<br>Blackman-Harris window  | FFT,                       |        | -85                                      |        | dB                 |  |  |

| Total Harmonic Distortion at 20mV <sub>PK</sub>                                                                                          | V <sub>IN</sub> = 55Hz, 20mV <sub>PK</sub> , 64kpts F<br>Blackman-Harris window | FT,                        |        | -90                                      |        | dB                 |  |  |

|                                                                                                                                          |                                                                                 | FIRLEN = 15                |        | 120.46                                   |        |                    |  |  |

|                                                                                                                                          |                                                                                 | FIRLEN = 14                | 146.20 |                                          |        |                    |  |  |

| LSB Size (LSB Values Do Not Include the 9-Bit Left Shift at the                                                                          | V <sub>IN</sub> = 55Hz, 20mV <sub>PK</sub> ,<br>64kpts FFT, Blackman-Harris     | FIRLEN = 13                |        | 179.82                                   |        | nV                 |  |  |

| CE Input)                                                                                                                                | window, 10MHz ADC clock                                                         | FIRLEN = 12                |        | 224.59                                   |        | nv                 |  |  |

|                                                                                                                                          |                                                                                 | FIRLEN = 11                |        | 285.54                                   |        |                    |  |  |

|                                                                                                                                          |                                                                                 | FIRLEN = 10                |        | 370.71                                   |        |                    |  |  |

| PARAMETER                                                                                  | CONDITIO                                            | NS                   | MIN | TYP      | MAX | UNITS  |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------|-----|----------|-----|--------|

|                                                                                            |                                                     | FIRLEN = 15          |     | ±2621440 |     |        |

|                                                                                            |                                                     | FIRLEN = 14          |     | ±2160000 |     |        |

| Digital Full Scale                                                                         | V <sub>IN</sub> = 55Hz, 400mV <sub>PK</sub> ,       | FIRLEN = 13          |     | ±1756160 |     |        |

| Digital Full Scale                                                                         | 10MHz ADC clock                                     | FIRLEN = 12          |     | ±1406080 |     | - LSB  |

|                                                                                            |                                                     | FIRLEN = 11          |     | ±1105920 |     |        |

|                                                                                            |                                                     | FIRLEN = 10          |     | ±851840  |     |        |

| PREAMPLIFIER PERFORMANC                                                                    | E SPECIFICATIONS                                    |                      |     |          |     |        |

| Differential Gain (V <sub>IN</sub> = 28mV Differential)                                    | $T_A = +25^{\circ}C$ , $V_{3P3A} = 3.3V$ , p        | preamplifier enabled |     | 8.9      |     |        |

| Differential Gain<br>(V <sub>IN</sub> = 15mV Differential)                                 | T <sub>A</sub> = +25°C, V <sub>3P3A</sub> = 3.3V, p | oreamplifier enabled |     | 8.9      |     | V/V    |

| Gain Variation vs. V <sub>3P3A</sub> (V <sub>IN</sub> = 28mV Differential)                 | V <sub>3P3A</sub> = 3.0V, 3.6V                      |                      |     | -72      |     | ppm/%  |

| Gain Variation vs. Temperature (V <sub>IN</sub> = 28mV Differential)                       | T <sub>A</sub> = -40°C to +85°C                     |                      |     | -45      |     | ppm/°C |

| Phase Shift (V <sub>IN</sub> = 28mV<br>Differential)                                       | $T_A = +25^{\circ}C$ , $V_{3P3A} = 3.3V$ (I         | Note 4)              | 0   |          | 8   | m°     |

| Preamplifier Input Current (I <sub>IAP</sub> )                                             | Droomplifier enabled 1                              | = L = CNDA           | 9   | 15       | 20  |        |

| Preamplifier Input Current (I <sub>IAN</sub> )                                             | Preamplifier enabled, I <sub>ADC0</sub>             | - IADC1 - GINDA      | 9   | 15       | 20  | μA     |

| Preamplifier and ADC Total<br>Harmonic<br>(V <sub>IN</sub> = 28mV Differential)            | $T_A = +25^{\circ}C; V_{3P3A} = 3.3V, F$            | PRE_E = 1            |     | -80      |     | dB     |

| Preamplifier and ADC Total<br>Harmonic Distortion<br>(V <sub>IN</sub> = 15mV Differential) | T <sub>A</sub> = +25°C; V <sub>3P3A</sub> = 3.3V, F | PRE_E = 1            |     | -85      |     | dB     |

| SPI SLAVE TIMING SPECIFICAT                                                                | TIONS                                               |                      |     |          |     |        |

| SPI Setup Time                                                                             | SPI_DI to SPI_CK rise                               |                      | 10  |          |     | ns     |

| SPI Hold Time                                                                              | SPI_CLK rise to SPI_DI                              |                      | 10  |          |     | ns     |

| SPI Output Delay                                                                           | SPI_CLK fall to SPI_D0                              |                      |     |          | 40  | ns     |

| SPI Recovery Time                                                                          | SPI_CSZ fall to SPI_CLK                             |                      | 10  |          |     | ns     |

| SPI Removal Time                                                                           | SPI_CLK to SPI_CSZ rise                             |                      | 15  |          |     | ns     |

| SPI Clock High                                                                             |                                                     |                      | 40  |          |     | ns     |

| SPI Clock Low                                                                              |                                                     |                      | 40  |          |     | ns     |

| SPI Clock Frequency                                                                        |                                                     |                      |     |          | 10  | MHz    |

| SPI Transaction Space (SPI_<br>CSZ Rise to SPI_CSZ Fall)                                   |                                                     |                      | 1   |          |     | μs     |

| PARAMETER                                                                  | CONDITIONS               | MIN                 | TYP                                                                                           | MAX | UNITS |

|----------------------------------------------------------------------------|--------------------------|---------------------|-----------------------------------------------------------------------------------------------|-----|-------|

| RESET TIMING                                                               |                          |                     |                                                                                               |     |       |

| Reset Pulse Width                                                          | Following power-on       | 1                   |                                                                                               |     | ms    |

| Reset Fulse Width                                                          | At all other times       | 5                   |                                                                                               |     | μs    |

| Reset Pulse Rise Time                                                      | (Note 4)                 |                     |                                                                                               | 1   | μs    |

| VOLTAGE MONITOR                                                            |                          |                     |                                                                                               |     |       |

| Nominal Value at +22°C (V <sub>NOM</sub> )                                 | V <sub>3P3A</sub> = 3.3V |                     | 130                                                                                           |     | LSB   |

| Voltage Measurement<br>Equation                                            |                          | (V <sub>SENSI</sub> | V <sub>3P3SYS(CALC)</sub> = 3.29V +<br>(V <sub>SENSE</sub> - 130) x 0.025V +<br>STEMP x 242μV |     |       |

| Voltage Error $100 \left( \frac{V_{3P3SYS}(CALC)}{V_{3P3SYS}} - 1 \right)$ |                          | -4                  |                                                                                               | +4  | %     |

Note 4: Guaranteed by design, not production tested.

## **Recommended External Components**

| NAME | FROM                | то   | FUNCTION                                                                                                               | VALUE      | UNITS |

|------|---------------------|------|------------------------------------------------------------------------------------------------------------------------|------------|-------|

| C1   | V <sub>3P3A</sub>   | GNDA | Bypass capacitor for 3.3V supply                                                                                       | ≥ 0.1 ±20% | μF    |

| CSYS | V <sub>3P3SYS</sub> | GNDD | Bypass capacitor for V <sub>3P3SYS</sub>                                                                               | ≥ 1.0 ±30% | μF    |

| C1P8 | V <sub>DD</sub>     | GNDD | Bypass capacitor for V <sub>1P8</sub> regulator                                                                        | 0.1 ±20%   | μF    |

| XTAL | XIN                 | XOUT | Crystal                                                                                                                | 9.8304     | MHz   |

| cxs  | XIN                 | GNDA | Load capacitor values for crystal depend on crystal specifications                                                     | 32 ±10%    | pF    |

| CXL  | XOUT                | GNDA | and board parasitics. Nominal values are based on 4pF board capacitance and include an allowance for chip capacitance. | 32 ±10%    | pF    |

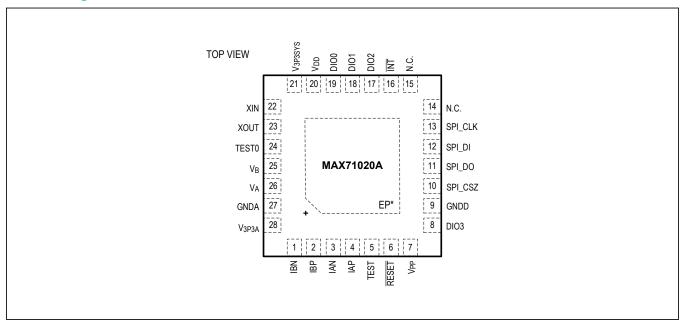

# **Pin Configuration**

# **Pin Description**

| PIN    | SIGNAL          | TYPE | FUNCTION                                                                              |

|--------|-----------------|------|---------------------------------------------------------------------------------------|

| 1      | IBN             | 1    | Negative Current Input Channel B. Not used. Connect to GNDA.                          |

| 2      | IBP             | I    | Positive Current Input Channel B. Not used. Connect to GNDA.                          |

| 3      | IAN             | 1    | Negative Current Input Channel A                                                      |

| 4      | IAP             | I    | Positive Current Input Channel A                                                      |

| 5      | TEST            | I    | Test Input. Connect to GNDD.                                                          |

| 6      | RESET           | I    | Active-Low Reset Input                                                                |

| 7      | $V_{PP}$        | I    | Programming Voltage. Not used; connect to GNDD.                                       |

| 8      | DIO3            | I/O  | Multiple-Use Pins. Configurable as DIO.                                               |

| 9      | GNDD            | Р    | Digital Ground. GNDD should be connected directly to the ground plane.                |

| 10     | SPI_CSZ         | I    | SPI Slave Select                                                                      |

| 11     | SPI_DO          | 0    | SPI Serial Data Master Input Slave Output                                             |

| 12     | SPI_DI          | I    | SPI Serial Data Master Output Slave Input                                             |

| 13     | SPI_CLK         | I    | SPI Serial Clock                                                                      |

| 14, 15 | N.C.            | I    | No Connection                                                                         |

| 16     | ĪNT             | I/O  | Active-Low Interrupt Request                                                          |

| 17     | DIO2            | I/O  | Multiple-Use Pins. Configurable as DIO.                                               |

| 18     | DIO1            | I/O  | Multiple-Use Pins. Configurable as DIO.                                               |

| 19     | DIO0            | I/O  | Multiple-Use Pins. Configurable as DIO.                                               |

| 20     | V <sub>DD</sub> | I/O  | Output of the 1.8V Regulator. Connect a 0.1µF bypass capacitor to ground to this pin. |

|     | op                  |          | ~/                                                                                                                     |

|-----|---------------------|----------|------------------------------------------------------------------------------------------------------------------------|

| PIN | SIGNAL              | TYPE     | FUNCTION                                                                                                               |

| 21  | V <sub>3P3SYS</sub> | Р        | System 3.3V Supply. Connect V <sub>3P3SYS</sub> to a 3.3V power supply.                                                |

| 22  | XIN                 | I        | Crystal Input                                                                                                          |

| 23  | XOUT                | 0        | Crystal Output                                                                                                         |

| 24  | TEST0               | I        | Test Input. Connect to GNDD.                                                                                           |

| 25  | V <sub>B</sub>      | I        | Line Voltage Sense Input VB. Unused, connect to GNDA.                                                                  |

| 26  | V <sub>A</sub>      | I        | Line Voltage Sense Inputs V <sub>A</sub>                                                                               |

| 27  | GNDA                | Р        | Analog Ground. Connect GNDA directly to the ground plane.                                                              |

| 28  | V <sub>3P3A</sub>   | Р        | Analog Power Supply. Connect a 3.3V power supply to $V_{3P3A}$ . $V_{3P3A}$ must be the same voltage as $V_{3P3SYS}$ . |

| _   | _                   | <u> </u> | Exposed Pad. On bottom.                                                                                                |

## **Pin Description (continued)**

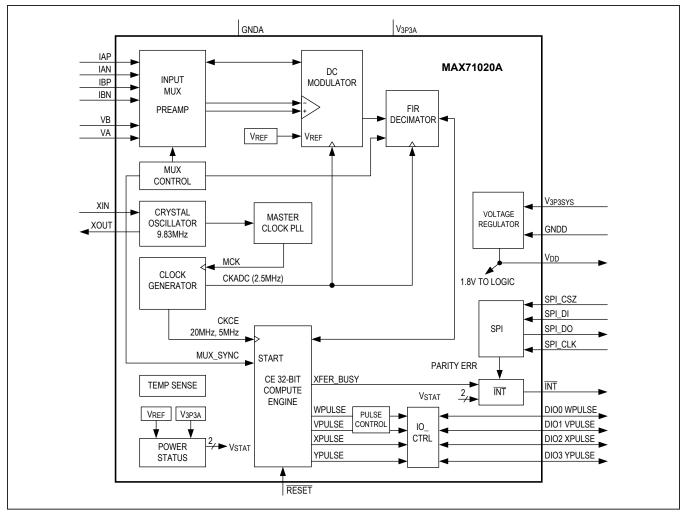

## **Detailed Description**

### **Hardware Description**

The MAX71020A analog front-end (AFE) integrates the functional blocks required to implement accurate energy measurement functions. Included on the chip are:

- An analog front-end (AFE) featuring a 22-bit second order delta-sigma ADC

- An independent 32-bit digital computation engine (CE) implementing DSP functions

- A precision voltage reference (VREF)

- A temperature sensor for digital temperature sensing and compensation

- Four I/O pins

- A zero-crossing detector with interrupt output

- Resistive shunt and current transformers are supported

- · A SPI slave for connection to a host controller

In a typical application, the 32-bit compute engine (CE) of the MAX71020A sequentially processes ADC samples from the Voltage and Current inputs and performs calculations to measure voltage and current RMS, power, active energy (Wh) and reactive energy (VARh), as well as A2h, and V2h for four-quadrant metering. These measurements are then accessed by the host processor. In addition to the temperature-trimmed ultra-precision voltage reference, the on-chip digital temperature compensation mechanism includes a temperature sensor and associated controls for correction of unwanted temperature effects on measurement. Temperature-dependent external components such as crystal oscillator, resistive shunts, current transformers (CTs) and their corresponding signal conditioning circuits can be characterized and their correction factors can be

programmed to further improve system's accuracy. The MAX71020A features an SPI (slave) interface for communication with the host processor. The communication protocol between the host and the MAX71020A provides a redundant information transfer ensuring the correctness of commands transferred from the host to the AFE, and of data transferred from the AFE to the host.

In addition, the MAX71020A has one pin dedicated as an interrupt output to the host. This pin notifies the host of asynchronous events.

## **ADC Description**

#### **Analog Inputs**

The MAX71020A has four analog inputs: two single-ended inputs for voltage measurement, and two differential inputs for current measurement.

The IAP, IAN, IBP, and IBN pins are current sensor inputs. IBP/IBN input are not used and should be connected to GNDA. The differential inputs feature preamplifiers with a selectable gain of 1 or 9, and are intended for direct connection to a shunt resistor sensor or a current transformer (CT).

The voltage inputs in the MAX71020A are single-ended, and are intended for sensing the line voltage via resistive dividers. These single-ended inputs are referenced to the GNDA pin..

All analog signal input pins measure voltage. In the case of shunt current sensors, currents are sensed as a voltage drop in the shunt resistor sensor. In the case of current transformers (CT), the current is measured as a voltage across a burden resistor that is connected to the secondary winding of the CT. Meanwhile, line voltages are sensed through resistive voltage dividers.

Figure 1. Functional Diagram

#### **ADC Preamplifier**

The ADC preamplifier is a low-noise differential amplifier with a fixed gain of 8.9 available on the IAP and IAN current-sensor input pins. When using a device with the preamplifier enabled, the input signal amplitude cannot be greater than 27.78mV peak. The preamplifier can be enabled/disabled through register settings.

### Analog-to-Digital Converter (ADC)

A single second-order delta-sigma ADC digitizes the voltage and current inputs to the device. The resolution of the ADC is dependent on several factors. Initiation of each ADC conversion is automatically controlled by logic internal to the MAX71020A. At the end of each ADC conversion, the FIR filter output data is stored into the

register determined by the multiplexer selection. FIR data is stored LSB justified, but shifted left 9 bits.

#### **FIR Filter**

The finite impulse response filter is an integral part of the ADC and it is optimized for use with the multiplexer. The purpose of the FIR filter is to decimate the ADC output to the desired resolution. At the end of each ADC conversion, the output data is stored into the register determined by the multiplexer selection.

#### **Voltage References**

A bandgap circuit provides the reference voltage ( $V_{REF}$ ) to the ADC. Since the  $V_{REF}$  bandgap amplifier is chopper stabilized, the DC offset voltage, which is the most significant long-term drift mechanism in the voltage reference ( $V_{REF}$ ), is automatically removed by the chopper circuit.

### **Digital Computation Engine (CE)**

The CE, a dedicated 32-bit signal processor, performs the precision computations necessary to accurately measure energy. The CE calculations and processes include:

- Multiplication of each current sample with its associated voltage sample to obtain the energy per sample (when multiplied with the constant sample time)

- Frequency-insensitive delay cancellation on all four channels (to compensate for the delay between samples caused by the multiplexing scheme)

- 90° phase shifter (for VAR calculations)

- Monitoring of the input signal frequency (for frequency and phase information)

- Monitoring of the input signal amplitude (for sag detection)

- Scaling of the processed samples based on calibration coefficients

- Scaling of samples based on temperature compensation information

- Gain and phase compensation

### **Temperature Sensor**

The MAX71020A includes an on-chip temperature sensor for determining the temperature of its bandgap reference. The primary use of the temperature data is to determine the magnitude of compensation required to offset the thermal drift in the system for the compensation of current, voltage, and energy measurement. The temperature sensor is awakened on command from the host controller by setting the TEMP START control bit. The host controller must wait for the TEMP START bit to clear before reading STEMP[15:0] and before setting the TEMP START bit once again. The result of the temperature measurement can be read from the STEMP[15:0] register. The 16-bit value is in two's complement form and ranges from -1024 to +1023 (decimal). The sensed temperature can be computed from the 16-bit STEMP[15:0] reading using the following formula:

Temp (

$$^{\circ}$$

C) = 0.33 x STEMP + 21.77

An additional register, VSENSE[7:0], senses the level of the supply voltage. <u>Table 1</u> shows the registers used for temperature measurement.

**Table 1. Temperature Measurement Registers**

| NAME          | RST | DIR  | DESCRIPTION                                                                                                   |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|---------------|-----|------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|               |     |      | Sets the period betwe                                                                                         | en temperature measurements.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|               |     |      | TEMP_PER                                                                                                      | TIME                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TEMP DEDIA:01 | 0   | R/W  | 0                                                                                                             | Manual updates (see TEMP_START description)                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| TEMP_PER[1:0] |     | H/VV | 1                                                                                                             | Every accumulation cycle                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|               |     |      | 2                                                                                                             | Continuous                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|               |     |      | 3                                                                                                             | No updates                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TEMP_START    | 0   | R/W  | PER[1:0] = 0, then set<br>Hardware clears TEM<br>The host controller mu                                       | TEMP_PER[1:0] must be zero in order for TEMP_START to function. If TEMP_PER[1:0] = 0, then setting TEMP_START starts a temperature measurement. Hardware clears TEMP_START when the temperature measurement is complete. The host controller must wait for TEMP_START to clear before reading STEMP[10:0] and before setting TEMP_START again. |  |  |  |  |

| STEMP[15:0]   | _   | R    | The result of the temperature measurement.                                                                    |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| VSENSE[7:0]   | _   | R    | The result of the temperature measurement. See the formula listed in the<br>Electrical Characteristics table. |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

## Digital I/O

On reset or power-up, all DIO pins are configured as high impedance. DIO pins can be configured independently by the host controller by manipulating the D0, D1, D2, and D3 bit fields.

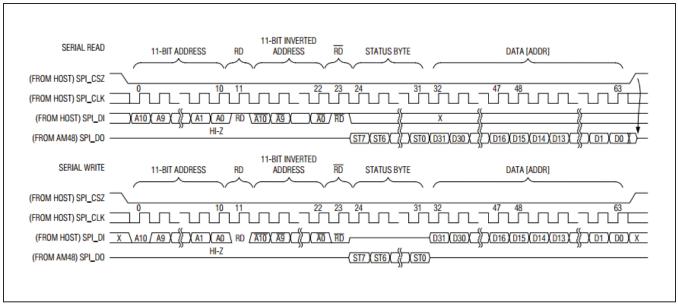

#### **SPI Slave Port**

The slave SPI port communicates directly with the host controller and allows it to read and write the device control registers. The interface to the slave port consists of the SPI\_CSZ, SPI\_CLK, SPI\_DI, and SPI\_DO pins. The host can also reset the MAX71020A through the SPI port by writing a data pattern to the RESET register.

#### **SPI Transactions**

SPI transactions are configured to provide immunity to electrical noise through redundancy in the command segment and error checking in the data field. The MAX71020A SPI transaction is exactly 64 bits; transactions of any other length are rejected. Each SPI transaction has the following fields (Table 2):

- A 24-bit setting packet, consisting of:

- · 11-bit address, MSB first

- 1-bit direction (1 means read)

- · 11-bit inverted address, MSB first

- · 1-bit inverted direction

- An 8-bit status, consisting of the following bits concerning the last transaction, starting from bit 7:

- Parity of the status byte (0 or 1 could be correct)

- FIFO overflow status bit (1 means error)

- FIFO underrun status bit (1 means error)

- Read or write data parity (0 or 1 could be correct)

(never both read and write; address is not included in the parity)

- Address or direction mismatch error bit (1 means error) (1: error, 0: no error)

- A bit indicating whether or not the bit count was exactly 64 (1 means error)

- Out of bounds address, most likely due to SPI safe bit or the memory manager (1 means error)

- A 32-bit packet of data, MSB first

If extra clocks are provided at the end during a read, all zero is output and the status continues to be updated, signaling an error. If extra clocks are provided at the end during a write, the write is aborted and the status is updated to signal an error.

- None of the fields above are optional.

- If an error is detected during the address or direction phase, no action is taken.

- SPI\_DO is high-Z while SPI\_CSZ is high.

- SPI safe mode is supported, and SPI is not locked out of this bit during SPI safe.

A typical SPI transaction is as follows. While SPI\_CSZ is high, the port is held in an initialized/reset state. During this state, SPI\_DO is held in high-Z state and all transitions on SPI\_CLK and SPI\_DI are ignored. When SPI\_CSZ falls, the port begins the transaction on the first rising edge of SPI\_CLK. A transaction consists of the fields shown in Table 2.

Note that the status byte indicates the status of the previous SPI transaction except for the status byte parity.

## **Table 2. SPI Transaction (64 Bits)**

| 24-B       | 24-BIT SETTING FIELD |              |         | 8-BIT STATUS     |                                               |                  |                |                     |          | 32-BIT DATA   |                |            |

|------------|----------------------|--------------|---------|------------------|-----------------------------------------------|------------------|----------------|---------------------|----------|---------------|----------------|------------|

| Address    | Dir                  | Inv Address  | Inv Dir |                  | Status from Previous Transaction: Status[7:0] |                  |                |                     |          | Data          |                |            |

| addr[10:0] | RD                   | addr_b[10:0] | RD_b    | Status<br>Parity |                                               | FIFO<br>UnderRun | Data<br>Parity | Setting<br>Mismatch | Reserved | Bad<br>CK Cnt | Bad<br>Address | data[31:0] |

Figure 2. SPI Slave Port—Typical Read and Write Operations

#### **SPI Safe Mode**

Sometimes it is desirable to prevent the SPI interface from writing to arbitrary registers and possibly disturbing the CE operation. For this reason, the SPI\_SAFE mode was created. In this mode, all SPI writes are disabled except to the word containing the SPI\_SAFE bit. This affords the host one more layer of protection from inadvertent writes.

#### **Fault and Reset Behavior**

Events at power-down power fault detection is performed by internal comparators that monitor the voltage at the  $V_{3P3A}$  pin and also monitor the internally generated  $V_{DD}$  pin voltage (1.8V DC).  $V_{3P3SYS}$  and  $V_{3P3A}$  must be connected together at the PCB level so that the comparators, which are internally connected only to the  $V_{3P3A}$  pin, are able to simultaneously monitor the common  $V_{3P3SYS}$  and  $V_{3P3A}$  voltage. The following discussion assumes that  $V_{3P3A}$  and  $V_{3P3SYS}$  are connected together at the PCB level. See Table 3.

During a power failure, as  $V_{3P3A}$  falls, two thresholds are detected. The first threshold, at 3.0V, warns the host controller that the analog modules are no longer accurate. The second threshold, at 2.8V, warns the host controller that a serious reduction in supply voltage has occurred and that the reliability of OTP reads may be affected.

#### **Reset Sequence**

The MAX71020A does not provide automatic reset generation. The reset needs to be generated by the host controller or by external circuitry connected to the RESET pin. When the MAX71020A receives a reset signal, either from the RESET pin or from the SPI (using a write to the RESET register at address 0x322), it asynchronously halts what it was doing. It then clears the RAM and invokes the load engine (LE). The LE initializes RAM and hardware control registers from the CE code image that is stored in OTP memory. Only RAM cells and hardware registers that need not change dynamically are loaded. All other RAM cells and registers have to be loaded by

**Table 3. VSTAT[1:0]**

| VSTAT[1:0] | DESCRIPTION                                                                            |

|------------|----------------------------------------------------------------------------------------|

| 00         | System Power-OK. V <sub>3P3A</sub> > 3.0V. Analog modules are functional and accurate. |

| 01         | System Power is low. 2.8V < V <sub>3P3A</sub> < 3.0V. Analog modules not accurate.     |

| 11         | System power below 2.8V. Ability to monitor power is about to fail.                    |

the host controller. The LE automatically refreshes the values of the registers it is tasked with loading during the operation of the MAX71020A. This refresh happens in increments of one register at a time and at a rate of one register per second. An errant reset can occur during EMI events. If this happens, the host controller is notified. This is accomplished by the holding the  $\overline{\text{INT}}$  pin low until the host clears the event (the F\_RESET bit in the M\_STAT register is set to indicate that a reset has occurred).

## **Connecting to a Host Processor**

Host connections include the  $\overline{\text{INT}}$  pin, the  $\overline{\text{RESET}}$  pin. In the host processor, the DIO pin connected to  $\overline{\text{INT}}$  should generate an interrupt. This interrupt signals to the host that an accumulation cycle has been completed and the calculations performed during it, are available in the relevant transfer registers. They remain constant throughout each accumulation interval.

#### **Sensors Connection**

Figure 3 shows a typical MAX71020A configuration. The IAP-IAN current channel can be directly connected to either a shunt resistor or a CT. The voltage input  $V_A$  is connected to a resistive voltage divider. The IBP-IBN channel, as well as  $V_B$  are not used and should be connected to GNDA.

### **Signal Flow Description**

This section reviews the signal processing calculations performed by the compute engine (CE) processor. The sample ADC sample rate is 2520 samples/s. Most of the calculations are performed over a fixed accumulation interval of 2520 samples corresponding to approximately 1s.

Figure 3. Typical Connection Diagram

## **Current Input Calculations**

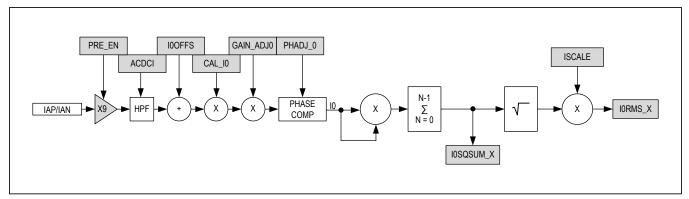

The calculation of the current is performed only on the IAN/IAP differential input. Figure 4 shows the signal processing relevant to the current input. In the darker boxes are represented the register accessible through the SPI interface.

The value of N represents the number of samples (SUM SAMP) in an accumulation interval and it is fixed.

I0SQSUM\_X is the sum of the squared voltage samples acquired during the last accumulation interval:

$$losqsum\_x = \sum_{n=0}^{N-1} lon^2$$

The host processor can complete the RMS calculation as follows:

$$IRMS = \frac{\sqrt{I0SQSUM\_X}}{N}$$

or simply access the IORMS X register where the RMS is calculated by the compute engine.

$$IORMS\_X = \sqrt{IOSQSUM\_X} \times \frac{IOSCALE}{2^{14}}$$

### **Voltage Input Calculations**

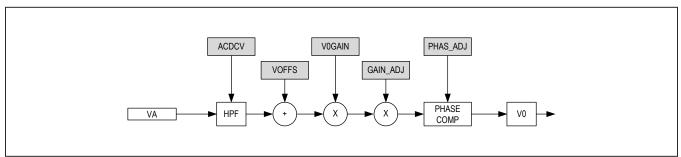

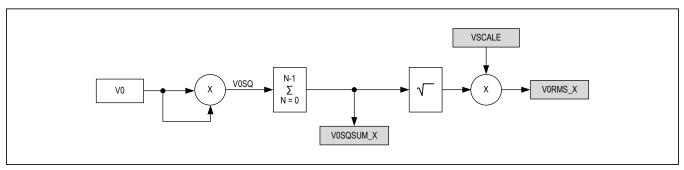

The calculation of the current is performed only on the VA single ended input. Figure 5 and Figure 6 show the signal processing relevant to the voltage input. The darker boxes represent the registers that are accessible through the SPI interface.

The value of N represents the number of samples (SUM SAMP) in an accumulation interval and it is fixed.

V0SQSUM X is the sum of the squared voltage samples acquired during the last accumulation interval:

$$V0SQSUM\_X = \sum_{n=0}^{N-1} V0n^2$$

The host processor can complete the RMS calculation as follows:

$$VRMS = \frac{\sqrt{V0SQSUM\_X}}{N}$$

or simply access the V0RMS X register where the RMS is calculated by the compute engine.

$$VORMS\_X = \sqrt{VOSQSUM\_X} \times \frac{VOSCALE}{2^{14}}$$

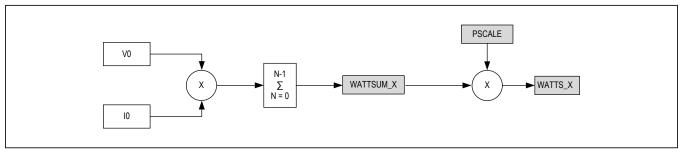

#### **Power Calculation**

Active power is calculated as the product of the voltage and current waveforms (Figure 7). The resulting waveform is the instantaneous power signal, and it is equal to the rate of energy flow at every instant of time. The instantaneous power is available as WATTSUM X as:

$$WATTSUM\_X = \sum_{n=0}^{N-1} V0n \times 10n$$

$$WATTS\_X = WATTSUM\_X \times \left(\frac{PSCALE}{2^{14}}\right)$$

### **Reactive Power Calculation Energy**

All variables are signed 32-bit integers. Accumulated variables such as WSUM are internally scaled so that internal values are no more than 50% of the full-scale range when the integration time is 1s. Additionally, the hardware does not permit output values to fold back upon overflow. WSUM X and VARSUM X are the Watt hour and VAR hour signed sum of Phase-A and Phase-B Wh or VARh values according to the metering equation implemented by the CE code. WxSUM X (x = 0 or 1, registers 0x085 and 0x086) is the watt-hour value accumulated for phase x in the last accumulation interval and can be computed based on the specified LSB value.

### Compute Engine (CE) Status and Control

The CE Status Word, CESTATUS, is useful for generating early warnings to the host controller. It contains sag warnings for phase A and B, as well as F0, the derived clock operating at the line frequency. The host controller can read the CE status word at every CE\_BUSY interrupt.

CESTATUS provides information about the status of voltage and input AC signal frequency that are useful for generating an early power-fail warning to initiate necessary data storage. CESTATUS represents the status flags for the preceding CE code pass (CE BUSY interrupt). The CE is initialized by the host controller using CECONFIG. This register contains the SAG CNT, PULSE SLOW, and PULSE FAST fields. The CECONFIG bit. When the SAG INT bit (register 0x020[20]) is set to 1, a sag event generates.

Figure 4. RMS Current Data Path

Figure 5. Voltage Signal Data Path

Figure 6. Voltage RMS Data Path

Figure 7. Power Data Path

## **Register Map**

All words are 4 bytes. Unless specified otherwise, they are in 32-bit two's complement format (-1 = 0xFFFFFFF). Calibration parameters are copied to CE data memory by the host controller before enabling the CE. Internal variables are used in internal CE calculations. Input variables allow the MPU to control the behavior of the CE code.

The registers can be read (R), write (W), or read/write (R/W) accessible by the host. The register output register (O) are measurement registers and can only be read by the host processor.

**Table 4. Register Map**

| NAME     | BYTE<br>ADDRESS | R/W | DEFAULT<br>VALUE | DESCRIPTION                                                                                                               | LOADED<br>BY |

|----------|-----------------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------|--------------|

| CAL_I0   | 0x010           | R/W | 0x0000 4000      | Calibration coefficient for current channel A.                                                                            | Host         |

| CAL_V0   | 0x011           | R/W | 0x0000 4000      | Calibration coefficient for voltage channel A.                                                                            | Host         |

| PHADJ_0  | 0x012           | R/W | 0x0000 0000      | Phase adjust coefficient for channel A.                                                                                   | Host         |

| I0OFFS   | 0x013           | R/W | 0x0000 4000      | DC offset constant current channel A                                                                                      | Host         |

| V00FFS   | 0x014           | R/W | 0x0000 4000      | DC offset constant voltage channel A                                                                                      | Host         |

| TEMP22   | 0x015           | R/W | 0x0000024D       | Device temperature default reading                                                                                        | Host         |

| I_SCALE  | 0x016           | R/W | 0x00000f6b       | Current-scaling constant. See the User Scaling section.                                                                   | Host         |

| V_SCALE  | 0x017           | R/W | 0x0000766C       | Current-scaling constant. See the <i>User Scaling</i> section.                                                            | Host         |

| P_SCALE  | 0x018           | R/W | 0x0000490A       | Current-scaling constant. See the <i>User Scaling</i> section.                                                            | Host         |

| DEGSCALE | 0x01A           | R/W | 0x0000 6A8F      | Device temperature scaling (internal constant)                                                                            | LE           |

| PPMC1    | x01B0           | R/W | 0x000 0000       | Linear coefficient for temperature compensation. A default coefficient can be established by copying PPMCATE into PPMC.   | Host         |

| PPMC2    | x01C            | R/W | 0x00000000       | Quadratic coefficient for temperature compensation. A default coefficient can be obtained by copying PPMC2ATE into PPMC2. | Host         |

| PPMCATE1 | 0x01D           | R   | N/A              | Linear coefficient for temperature compensation populated at reset.                                                       | LE           |

| PPMCATE2 | 0x01E           | R   | N/A              | Quadratic coefficient for temperature compensation populated at reset.                                                    | LE           |

**Table 4. Register Map (continued)**

| NAME     | BYTE<br>ADDRESS | R/W | DEFAULT<br>VALUE |               | DES                                                                       | CRIPTION                                                         | LOADED<br>BY |

|----------|-----------------|-----|------------------|---------------|---------------------------------------------------------------------------|------------------------------------------------------------------|--------------|

|          |                 |     |                  | Configurati   | on Register fo                                                            | CE Operation                                                     |              |

|          |                 |     |                  | BIT           | NAME                                                                      | DESCRIPTION                                                      |              |

|          |                 |     |                  | 31            | Reserved                                                                  |                                                                  |              |

|          |                 |     |                  | 30            | ACDCV                                                                     | Voltage HPF controls<br>1 = enable, 0 = disable                  |              |

|          |                 |     |                  | 29            | ACDCV                                                                     | Current HPF controls<br>1 = enable, 0 = disable                  |              |

|          |                 |     | 28               | DGNDM         | Ground reference<br>measurement<br>1 = enable, 0 = disable                |                                                                  |              |

|          |                 |     |                  | 27:2324       | Reserved                                                                  | 1 = enable, 0 = disable                                          |              |

| CECONFIG | ECONFIG 0x020 R | R/W | 0x0030 3301      | 2             |                                                                           |                                                                  | Host         |

|          |                 |     |                  | 22            | EXT_TEMP                                                                  | External control of GAIN_ADJn if set                             |              |

|          |                 |     |                  | 21            | EDGE_INT                                                                  | Enables zero-crossing output on XPULSE 1 = enabled, 0 = disabled |              |

|          |                 |     |                  | 20            | SAG_INT                                                                   | Enables a sag detect output on YPULSE 1 = enabled, 0 = disabled  |              |

|          |                 |     | 19:8             | SAG_CNT       | Number of consecutive samples below SAG_THR before a sag even is declared |                                                                  |              |

|          |                 |     |                  | 7:0           | Reserved                                                                  |                                                                  |              |

| WRATE    | 0x021           | R/W | 0x00001227       | Sets the me   | ter constant for                                                          | pulses.                                                          | Host         |

| KVAR     | 0x022           | R/W | 0x00001929       | Internal scal | ing factor for VA                                                         | Rh measurements.                                                 | LE           |

| SUM_PRE  | 0x023           | 0   | 0x00000800       |               | h of Accumulation<br>y the CE. (Inform                                    | on interval in samples as<br>mation Only)                        | Host         |

| SAG_THR  | 0x024           | R/W | 0x016D 2490      | Voltage thre  | shold for sag wa                                                          | arnings.                                                         | Host         |

| QUANT_V0 | 0x025           | R/W | 0x0000 0000      | Truncation/r  | oise compensa                                                             | tion for voltage in phase A                                      | Host         |

| QUANT_I0 | 0x026           | R/W | 0x0000 0000      | Truncation/r  | oise compensa                                                             | tion for current in phase A                                      | Host         |

| QUANT_P0 | 0x027           | R/W | 0x0000 00000     | Truncation/r  | oise compensa                                                             | tion for real power in phase A                                   | Host         |

**Table 4. Register Map (continued)**

| NAME        | BYTE<br>ADDRESS | R/W | DEFAULT<br>VALUE |                                                                                                | DESCRIPTION                                           | LOADED<br>BY |

|-------------|-----------------|-----|------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------|

| QUANT_QA    | 0x028           | R/W | 0x0000 0000      | Truncation/noise comp                                                                          | pensation for reactive power in phase A               | Host         |

| CREEP_THR   | 0x029           | R/W | 0x0000 9C40      | WSUM threshold below                                                                           | w which the device squelches outputs                  | Host         |

| GAINADJ_V0  | 0x040           | R/W | 0x0000 4000      | Adjusts the amplitude to compensation. Default                                                 | for voltage input VA for temperature<br>= unity gain. | Host         |

| GAINADJ_I0  | 0x041           | R/W | 0x0000 4000      | Adjusts the amplitude t gain.                                                                  | for current input IA. Default = unity                 | Host         |

| Reserved    | 0x042-0x043     | R/W | 0x0000 00000     | Reserved register                                                                              |                                                       | Host         |

| Reserved    | 0x044           | R/W | 0x0000 00000     | Reserved register                                                                              |                                                       | Host         |

| WPULSE_CTR  | 0x045           | R   | _                | Pulse counter for Wh (                                                                         | real power)                                           | _            |

| WPULSE_FRAC | 0x046           | R   | _                | Pulse generator numer                                                                          | rator for Wh (real power)                             | _            |

| Reserved    | 0x047           | R/W | 0x0000 00000     | Reserved register                                                                              |                                                       | Host         |

| Reserved    | 0x048           | R/W | 0x0000 00000     | Reserved register                                                                              |                                                       | Host         |

| VPULSE_CTR  | 0x049           |     | _                | Pulse counter for VARh (real power)                                                            |                                                       | _            |

| VPULSE_FRAC | 0x04A           |     | _                | Pulse generator numerator for VARh (real power)                                                |                                                       | _            |

| Reserved    | 0x04B           |     | 0x0000 00000     | Reserved register                                                                              |                                                       | Host         |

|             | 0x04C-0x07F     |     | _                | Used by CE for internal variables                                                              |                                                       | _            |

|             |                 |     |                  | Status of Compute E                                                                            | ngine                                                 |              |

|             |                 |     |                  | BIT                                                                                            | _                                                     |              |

| CESTATUS    | 0x080           | R   | _                | 0                                                                                              | _                                                     | _            |

|             |                 |     |                  | 1 R                                                                                            | Reserved                                              |              |

|             |                 |     |                  | 2 R                                                                                            | Reserved                                              |              |

|             |                 |     |                  | 3 S                                                                                            | Square wave at exact line frequency                   |              |

|             |                 |     |                  | 31:4 R                                                                                         | Reserved                                              |              |

| TEMP_X      | 0x81            | R   |                  | Temperature deviation                                                                          | from TEMP22                                           | _            |

| FREQ_X      | 0x82            | R   |                  | Fundamental line frequ                                                                         | uency (LSB = 2520.6/232Hz)                            |              |

| MAINEDGE_X  | 0x83            | R   |                  | Number of voltage zero crossings of either direction during the previous accumulation interval |                                                       | _            |

| _           | _               | _   | _                | Reserved                                                                                       |                                                       | _            |

| W0SUM_X     | 0x85            | R   | _                | Signed sum of real end                                                                         | ergy (Wh) from wattmeter element A                    | _            |

| _           |                 | _   | _                | Reserved                                                                                       |                                                       | _            |

| _           | _               | _   | _                | Reserved                                                                                       |                                                       | _            |

|             |                 |     |                  |                                                                                                |                                                       |              |

**Table 4. Register Map (continued)**

| NAME      | BYTE<br>ADDRESS | R/W | DEFAULT<br>VALUE | DESCRIPTION                                                   | LOADED<br>BY |

|-----------|-----------------|-----|------------------|---------------------------------------------------------------|--------------|

| VAR0SUM_X | 0x89            | R   |                  | Signed sum of reactive energy (VARh) from wattmeter element A | _            |

| _         | _               |     | _                | Reserved                                                      |              |

| I0SQSUM_X | 0x8C            | R   |                  | Sum of squared samples from current sensor in phase A         |              |

| _         | _               |     | _                | Reserved                                                      | <u> </u>     |

| V0SQSUM_X | 0x90            | R   |                  | Sum of squared samples from voltage sensor in phase A         | _            |

| V1SQSUM_X | 0x91            | R   |                  | Sum of squared samples from voltage sensor in phase B         | <u> </u>     |

| I0SQRES_X | 0x96            | R   |                  | Residual current from current sensor in phase A               |              |

| VB_AVG_X  | 0x97            | R   |                  | Average DC value of VB input sensor                           |              |

| I0RMS_X   | 0x098           | R   |                  | Scaled current RMS                                            |              |

| V0RMS_X   | 0x099           | R   |                  | Scaled voltage RMS                                            |              |

| P0_X      | 0x09A           | R   |                  | Scaled active power                                           |              |

| Q0_X      | 0x09B           | R   |                  | Scaled reactive power                                         |              |

| I0_RAW_DC | 0x09C           | R   |                  | RAW DC offset/level of current input                          |              |

| V0_RAW_DC | 0x09D           | R   |                  | RAW DC offset/Level of voltage input                          |              |

# **Table 5. Hardware Control Register Map**

| NAME     | BYTE<br>ADDRESS | R/W | DEFAULT<br>VALUE*      | DESCRIPTION                                                                                                                                   |

|----------|-----------------|-----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| DEVICEID | 0x301           | R   | 0x0000(H)<br>0x1100(L) | Contains identifying information for the device. Loaded by the LE.                                                                            |

| STEMP    | 0x30A           | R   | _                      | Result of the temperature measurement. Only bits 26:16 are significant; all other bits return zero.                                           |

| VSENSE   | 0x30B           | R   | _                      | Result of the device V <sub>3</sub> P <sub>3</sub> S <sub>Y</sub> S measurement. Only bits 23:16 are significant; all other bits return zero. |

**Table 5. Hardware Control Register Map (continued)**

| NAME      | BYTE<br>ADDRESS | R/W | DEFAULT<br>VALUE* |        |                                                           | DESCRIPTION                                                                     |  |  |  |

|-----------|-----------------|-----|-------------------|--------|-----------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|

|           | ADDRESS         |     |                   | Contai | Contains the Characteristics of the Four Digital I/O Pins |                                                                                 |  |  |  |

|           |                 |     |                   | BIT    | NAME                                                      | DESCRIPTION                                                                     |  |  |  |