#### **MAX77812**

## 20A User-Configurable Quad-Phase Buck Converter

### **General Description**

The MAX77812 is a quad-phase high-efficiency stepdown (buck) converter capable of delivering up to 20A of maximum current. Programmable startup/shutdown sequence and user-selectable phase configurations make the MAX77812 ideal for powering the latest generations of processors. With high-efficiency and small solution size, the MAX77812 is optimized for space constrained single-cell battery powered applications.

The MAX77812 uses an adaptive on-time PWM control scheme and it has SKIP and low-power SKIP modes for improved light-load efficiency. A programmable current limit reduces the overall solution footprint by optimizing inductors size. Differential sensing provides high output voltage accuracy, while enhanced transient response (ETR) allows fast output voltage adjustments to load transients. Programmable soft-start/stop and ramp-up/down slew rate provides control over an inrush current as the regulator transitions between operating states.

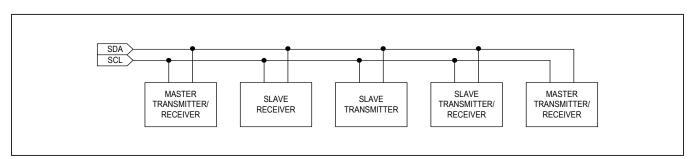

A 3.4MHz high-speed I<sup>2</sup>C or 30MHz SPI interface with dedicated logic inputs provide full configurability and control for system power optimization.

The MAX77812 is available in 3.408mm x 3.368mm, 64-bump 0.4mm pitch wafer-level package (WLP).

#### **Benefits and Features**

- 20A Maximum Output Current (5A per Phase)

- V<sub>IN</sub> Range: 2.5V to 5.5V

- V<sub>OUT</sub> Range: 0.250V to 1.525V with 5mV Steps

- ±0.5% Initial Output Accuracy with Differential Sensing

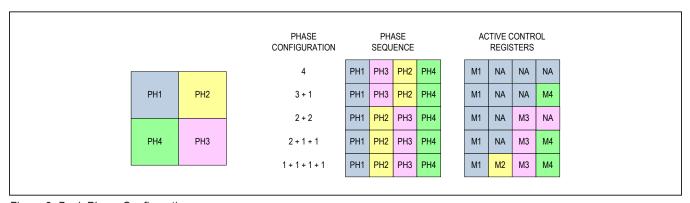

- 5 User-Selectable Phase Configurations

- 91% Peak Efficiency (V<sub>IN</sub> = 3.8V, V<sub>OUT</sub> = 1.1V)

- Auto (SKIP/PWM) and Forced PWM Modes

- Enhanced Load Transient Response

- Programmable Ramp-Up/Down Slew Rates

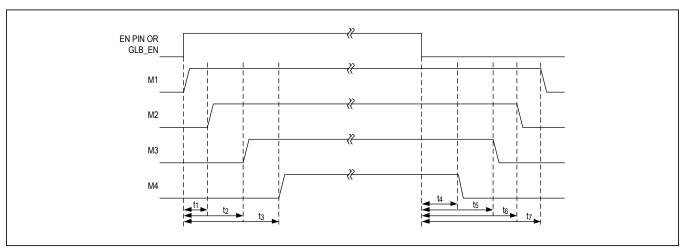

- Programmable Startup/Shutdown Sequence

- UVLO, Short-Circuit, and Thermal Protections

- 2 User-Programmable General-Purpose Inputs

- 3.4MHz High Speed I<sup>2</sup>C and 30MHz SPI Interface

- 3.408mm x 3.368mm, 64-Bump WLP Package

#### **Applications**

- CPU/GPU, FPGAs, and DSPs Power Supply

- AR/VR Headsets and Game Consoles

- Li-ion Battery Powered Equipment

- Space Constrained Portable Electronics

<u>Ordering Information</u> appears at end of data sheet.

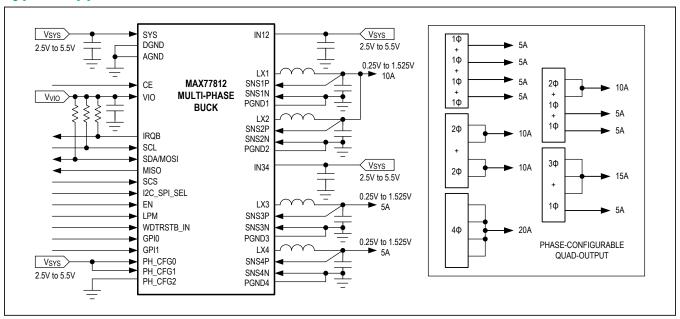

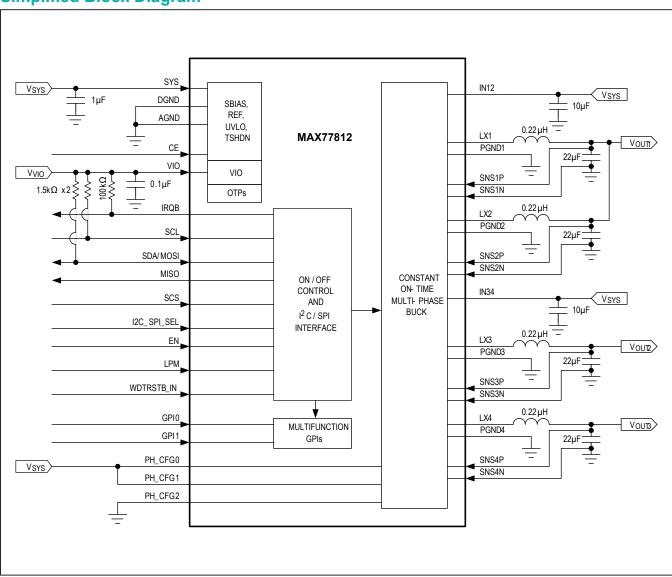

## **Typical Application Circuit**

## **Absolute Maximum Ratings**

| SYS, VIO to AGND                 | 0.3V to +6.0V                     |

|----------------------------------|-----------------------------------|

| DGND to AGND                     | 0.3V to +0.3V                     |

| SCL, SDA/MOSI, MISO, SCS, IRQB   | , CE, EN, LPM, GPI0, GPI1,        |

| WDTRSTB_IN to DGND               | 0.3V to (V <sub>VIO</sub> + 0.3V) |

| PH_CFG0, PH_CFG1, PH_CFG2,       |                                   |

| I2C_SPI_SEL to AGND              | 0.3V to $(V_{SYS} + 0.3V)$        |

| IN12, IN34 to PGNDx              | 0.3V to $(V_{SYS} + 0.3V)$        |

| LX1/2/3/4 to PGNDx               | 0.3V to $(V_{IN} + 0.3V)$         |

| LX1/2/3/4 to PGNDx (Pulsed <10ns | Voltage)3.0V to +7.0V             |

| PGND1/2/3/4 to AGND                                  | 0.3V to +0.3V                   |

|------------------------------------------------------|---------------------------------|

| SNS1P, SNS2P, SNS3P, SNS4P to AGND0.3                | $V \text{ to } (V_{IN} + 0.3V)$ |

| SNS1N, SNS2N, SNS3N, SNS4N to AGND                   | 0.3V to +0.3V                   |

| Continuous Power Dissipation at $T_A = +70^{\circ}C$ |                                 |

| (derate 26.17mW/°C above +70°C)                      | 2094mW                          |

| Junction Temperature                                 | +150°C                          |

| Storage Temperature Range                            | -65°C to +150°C                 |

| Soldering Temperature (reflow)                       | +260°C                          |

|                                                      |                                 |

**Note 1:** LXx node has internal clamp diodes to PGNDx and INx. Applications that give forward bias to these diodes should ensure that the total power loss does not exceed the power dissipation limit of IC package.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Recommended Operating Conditions**

| PARAMETER                     | SYMBOL          | CONDITION                                                                                                                                                                                                                   | TYPICAL<br>RANGE | UNITS |

|-------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|

| Input Voltage Range           | V <sub>IN</sub> |                                                                                                                                                                                                                             | 2.5 to 5.5       | V     |

| Output Current Range          | Іоит            | For continuous operation at 5A (per phase), the junction temperature (T <sub>J</sub> ) is limited to +115°C. If the junction temperature is higher than +115°C, the expected lifetime at 5A continuous operation is reduced | 0 to 5           | А     |

| Junction Temperature<br>Range | TJ              |                                                                                                                                                                                                                             | -40 to +125      | °C    |

Note: These limits are not guaranteed.

## **Package Thermal Characteristics (Note 2)**

WLP

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) ......33.2°C/W

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

### **Electrical Characteristics**

#### **Top-Level Electrical Characteristics**

$(V_{SYS} = V_{INX} = +3.8V, V_{VIO} = +1.8V, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , typical values are at  $T_A = T_J = +25^{\circ}C$ )

| PARAMETER               | SYMBOL            | CONDITIONS                                                   | MIN | TYP | MAX | UNITS |

|-------------------------|-------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| GLOBAL INPUT SUPPLY     |                   |                                                              |     |     |     |       |

| Operating Voltage Range | V <sub>SYS</sub>  |                                                              | 2.5 |     | 5.5 | V     |

| Shutdown Supply Current | I <sub>SHDN</sub> | CE = low, T <sub>A</sub> = +25°C                             |     | 2   | 5   | μA    |

| Standby Current         | ISTBY             | CE = high and all outputs are off,<br>T <sub>A</sub> = +25°C |     | 25  |     | μA    |

## **Top-Level Electrical Characteristics (continued)**

$(V_{SYS} = V_{INX} = +3.8V, \ V_{VIO} = +1.8V, \ T_A = T_J = -40^{\circ}C \ to \ +125^{\circ}C, \ typical \ values \ are \ at \ T_A = T_J = +25^{\circ}C)$

| PARAMETER                                        | SYMBOL                | CONDITIONS                                                       | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------------------|-----------------------|------------------------------------------------------------------|-------|------|-------|-------|

|                                                  | I <sub>LP_SKIP1</sub> | 4-phase configuration (no switching)                             |       | 120  |       |       |

|                                                  | I <sub>LP_SKIP2</sub> | 3 + 1-phase configuration (no switching)                         |       | 190  |       |       |

| No Load Supply Current in Low<br>Power Skip Mode | I <sub>LP_SKIP3</sub> | 2 + 2-phase configuration (no switching)                         |       | 190  |       | μA    |

|                                                  | I <sub>LP_SKIP4</sub> | 2 + 1 + 1-phase configuration<br>(no switching)                  |       | 265  |       |       |

|                                                  | I <sub>LP_SKIP5</sub> | 1 + 1 + 1 + 1-phase configuration (no switching)                 |       | 340  | 510   |       |

|                                                  | I <sub>SKIP1</sub>    | 4-phase configuration (no switching)                             |       | 150  |       |       |

|                                                  | I <sub>SKIP2</sub>    | 3 + 1-phase configuration (no switching)                         |       | 250  |       |       |

| No Load Supply Current in Skip<br>Mode           | I <sub>SKIP3</sub>    | 2 + 2-phase configuration (no switching)                         |       | 250  |       | μA    |

|                                                  | I <sub>SKIP4</sub>    | 2 + 1 + 1-phase configuration (no switching)                     |       | 350  |       |       |

|                                                  | I <sub>SKIP5</sub>    | 1 + 1 + 1 + 1-phase configuration (no switching)                 |       | 460  | 690   |       |

|                                                  | ISKIP_ETR1            | 4-phase configuration (no switching, ETR enabled)                |       | 180  |       |       |

|                                                  | ISKIP_ETR2            | 3 + 1-phase configuration<br>(no switching, ETR enabled)         |       | 310  |       |       |

| No Load Supply Current in Skip<br>Mode with ETR  | ISKIP_ETR3            | 2 + 2-phase configuration<br>(no switching, ETR enabled)         |       | 310  |       | μA    |

|                                                  | ISKIP_ETR4            | 2 + 1 + 1-phase configuration<br>(no switching, ETR enabled)     |       | 440  |       |       |

|                                                  | ISKIP_ETR5            | 1 + 1 + 1 + 1-phase configuration<br>(no switching, ETR enabled) |       | 580  | 870   |       |

| V <sub>SYS</sub> UNDERVOLTAGE LOCKOL             | IT                    |                                                                  |       |      |       |       |

| V <sub>SYS</sub> Undervoltage Lockout            | V <sub>UVLO_R</sub>   | V <sub>SYS</sub> rising                                          | 2.375 | 2.50 | 2.625 | V     |

| Threshold                                        | V <sub>UVLO_F</sub>   | V <sub>SYS</sub> falling (default)                               |       | 2.15 |       |       |

| THERMAL PROTECTION                               |                       |                                                                  |       |      |       |       |

| Thermal Protection Threshold                     | T <sub>SHDN</sub>     | T <sub>J</sub> rising, 15°C hysteresis                           |       | 165  |       | °C    |

| Thermal Interrupt at 120°C                       | T <sub>INT120</sub>   | T <sub>J</sub> rising, 15°C hysteresis                           |       | 120  |       | °C    |

| Thermal Interrupt at 140°C                       | T <sub>INT140</sub>   | T <sub>J</sub> rising, 15°C hysteresis                           |       | 140  |       | °C    |

## **Top-Level Electrical Characteristics (continued)**

$(V_{SYS} = V_{INX} = +3.8V, \ V_{VIO} = +1.8V, \ T_A = T_J = -40^{\circ}C \ to \ +125^{\circ}C, \ typical \ values \ are \ at \ T_A = T_J = +25^{\circ}C)$

| PARAMETER                                  | SYMBOL             | CONDITIONS                                                                                                  | MIN                       | TYP    | MAX                       | UNITS |

|--------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------|---------------------------|--------|---------------------------|-------|

| LOGIC AND CONTROL INPUTS                   |                    |                                                                                                             |                           |        |                           |       |

| Input Low Level                            | V <sub>IL</sub>    | PH_CFG0, PH_CFG1, PH_CFG2, I2C_SPI_SEL, $V_{SYS} \le 5.5V$ , $T_A = +25^{\circ}C$                           |                           |        | 0.4                       | V     |

|                                            |                    | CE, EN, LPM, GPI0, GPI1,<br>WDTRSTB_IN, T <sub>A</sub> = +25°C                                              |                           |        | 0.3 x<br>V <sub>VIO</sub> |       |

| Input High Level                           | V <sub>IH</sub>    | PH_CFG0, PH_CFG1, PH_CFG2, I2C_SPI_SEL, $V_{SYS} \le 5.5V$ , $T_A = +25^{\circ}C$                           | 1.2                       |        |                           | V     |

|                                            |                    | CE, EN, LPM, GPI0, GPI1,<br>WDTRSTB_IN, T <sub>A</sub> = +25°C                                              | 0.7 x<br>V <sub>VIO</sub> |        |                           |       |

|                                            | I <sub>LK</sub>    | PH_CFG0, PH_CFG1, PH_CFG2,<br>I2C_SPI_SEL, V <sub>SYS</sub> = 5.5V,<br>CE = 1.8V, T <sub>A</sub> = +25°C    | -1                        | +0.001 | +1                        |       |

| Logic Input Lookogo Current                |                    | CE, EN, LPM, GPI0, GPI1,<br>CE = 1.8V, T <sub>A</sub> = +25°C                                               | -1                        | +0.001 | +1                        |       |

| Logic Input Leakage Current                |                    | PH_CFG0, PH_CFG1, PH_CFG2, I2C_SPI_SEL, V <sub>SYS</sub> = 5.5V, CE = 1.8V, T <sub>A</sub> = +85°C (Note 4) |                           | 0.1    |                           | - μΑ  |

|                                            |                    | CE, EN, LPM, GPI0, GPI1,<br>CE = 1.8V, T <sub>A</sub> = +85°C (Note 4)                                      |                           | 0.1    |                           |       |

| IRQ Output Low Voltage                     | V <sub>OL</sub>    | I <sub>SINK</sub> = 1mA                                                                                     |                           |        | 0.4                       | V     |

| IDO Output High Lookage                    | I                  | T <sub>A</sub> = +25°C                                                                                      | -1                        | 0.001  | +1                        |       |

| IRQ Output High Leakage                    | I <sub>LK</sub> OH | T <sub>A</sub> = +85°C (Note 4)                                                                             |                           | 0.1    |                           | μA    |

| INTERNAL PULL-UP/DOWN RESI                 | STANCE             |                                                                                                             |                           |        |                           |       |

| WDTRSTB_IN Pullup Resistance               | R <sub>PU</sub>    | Pullup resistance to VIO                                                                                    | 400                       | 800    | 1600                      | kΩ    |

| GPI0, GPI1, EN, LPM Pulldown<br>Resistance | R <sub>PD</sub>    | Pulldown resistance to DGND                                                                                 | 400                       | 800    | 1600                      | kΩ    |

## **Quad-Phase Buck Electrical Characteristics**

$(V_{SYS} = V_{INX} = +3.8V, \ V_{OUTX} = 0.85V, \ T_A = T_J = -40^{\circ}C \ to \ +125^{\circ}C, \ typical \ values \ are \ at \ T_A = T_J = +25^{\circ}C$

| PARAMETER               | SYMBOL                | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                        | MIN    | TYP    | MAX       | UNITS |

|-------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-----------|-------|

| POWER SUPPLY            |                       |                                                                                                                                                                                                                                                                                                                                                                                                                   |        |        |           |       |

| Input Voltage Range     | V <sub>INx</sub>      |                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.5    |        | $V_{SYS}$ | V     |

| Output Voltage Range    | V <sub>OUT</sub>      | Programmable with 8-bit resolution, 5mV/LSB                                                                                                                                                                                                                                                                                                                                                                       | 0.25   |        | 1.525     | V     |

| DC OUTPUT VOLTAGE ACCUR | ACY                   |                                                                                                                                                                                                                                                                                                                                                                                                                   |        |        |           |       |

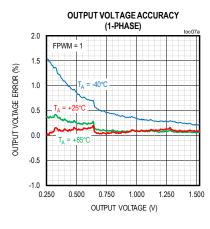

| Output Voltage Accuracy | V                     | Force PWM mode, differential remote sensing, $V_{OUT} \ge 0.65V$ , $I_{OUT} = 0mA$ , $C_{OUT(EFF)} = 64\mu F$ , $T_A = +25^{\circ}C$                                                                                                                                                                                                                                                                              | -0.5   |        | +0.5      | %     |

|                         | V <sub>ACC_INIT</sub> | Force PWM mode,<br>differential remote sensing,<br>$0.45V \le V_{OUT} < 0.6V$ , $I_{OUT} =$<br>$0mA$ , $C_{OUT(EFF)} = 64\mu F$ ,<br>$T_A = +25^{\circ}C$                                                                                                                                                                                                                                                         | -6     |        | +6        | mV    |

| Load Regulation         |                       | Forced PWM mode,<br>differential remote sensing,<br>I <sub>OUT</sub> = 0A to 5A,<br>C <sub>OUT(EFF)</sub> = 64µF (Note 5)                                                                                                                                                                                                                                                                                         |        | -0.001 |           | V/A   |

| Line Regulation         |                       | Forced PWM mode,<br>differential remote sensing,<br>V <sub>INx</sub> = 2.5V to 5.5V, V <sub>OUT</sub><br>= Default, I <sub>OUT</sub> = 0mA,<br>C <sub>OUT(EFF)</sub> = 64µF                                                                                                                                                                                                                                       | -0.005 |        | +0.005    | V/V   |

| AC OUTPUT VOLTAGE ACCUR | ACY                   |                                                                                                                                                                                                                                                                                                                                                                                                                   |        |        |           |       |

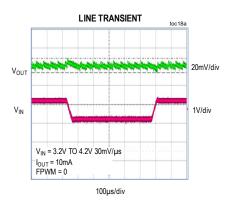

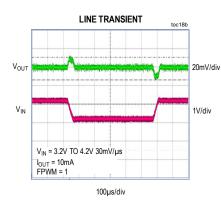

| Line Transient Response | V <sub>DROOP</sub>    | $\begin{split} &V_{\text{INx}} = 3.4 \text{V to } 2.9 \text{V to } 3.4 \text{V,} \\ &t_{\text{RISE}} = t_{\text{FALL}} = 10 \mu \text{s, } V_{\text{OUT}} \\ &= 1.1 \text{V, } I_{\text{OUT}} = 2 \text{A,} \\ &L = 220 \text{nH (DCR} = 9 \text{m}\Omega), \\ &C_{\text{OUT(EFF)}} = 16 \mu \text{F} \\ &(\text{ESR} = 5 \text{m}\Omega, \text{ ESL} = 300 \text{pH}) \\ &\text{per phase (Note 5)} \end{split}$ |        | 15     |           | mV    |

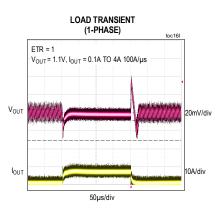

| Load Transient Response | V <sub>DROOP</sub>    | SKIP/PWM mode, differential remote sensing, $V_{OUT}$ = 1.1V, $I_{OUT}$ = 0.1A to 4A (100A/ $\mu$ s), L = 220nH (DCR = 9m $\Omega$ ), COUT(EFF) = 16 $\mu$ F (ESR = 5m $\Omega$ , ESL = 300pH) per Phase (Note 5)                                                                                                                                                                                                 |        | 45     |           | mV    |

## **Quad-Phase Buck Electrical Characteristics (continued)**

$(V_{SYS} = V_{INx} = +3.8V, V_{OUTx} = 0.85V, T_A = T_J = -40^{\circ}C$  to +125°C, typical values are at  $T_A = T_J = +25^{\circ}C$

| PARAMETER            | SYMBOL        | CONDITIONS                                | MIN TYP | MAX | UNITS |

|----------------------|---------------|-------------------------------------------|---------|-----|-------|

| RAMP RATE            |               |                                           |         |     |       |

|                      |               | B_SS_SR[2:0] = 000b<br>(Note 6)           | 1.25    |     |       |

|                      |               | B_SS_SR[2:0] = 001b<br>(Note 6)           | 2.5     |     |       |

|                      |               | B_SS_SR[2:0] = 010b<br>(Note 6)           | 5       |     |       |

| Soft-Start Slew Rate |               | B_SS_SR[2:0] = 011b<br>(Note 6)           | 10      |     | mV/μs |

|                      |               | B_SS_SR[2:0] = 100b<br>(default) (Note 6) | 20      |     |       |

|                      |               | B_SS_SR[2:0] = 101b<br>(Note 6)           | 40      |     |       |

|                      |               | B_SS_SR[2:0] = 110b or<br>111b (Note 6)   | 60      |     |       |

|                      |               | B_SD_SR[2:0] = 000b<br>(Note 6)           | 1.25    |     |       |

|                      |               | B_SD_SR[2:0] = 001b<br>(Note 6)           | 2.5     |     |       |

|                      |               | B_SD_SR[2:0] = 010b<br>(default) (Note 6) | 5       |     |       |

| Shutdown Slew Rate   |               | B_SD_SR[2:0] = 011b<br>(Note 6)           | 10      |     | mV/μs |

|                      |               | B_SD_SR[2:0] = 100b<br>(Note 6)           | 20      |     |       |

|                      | (Note<br>B_SD | B_SD_SR[2:0] = 101b<br>(Note 6)           | 40      |     |       |

|                      |               | B_SD_SR[2:0] = 110b or 111b (Note 6)      | 60      |     |       |

## **Quad-Phase Buck Electrical Characteristics (continued)**

$(V_{SYS} = V_{INx} = +3.8V, V_{OUTx} = 0.85V, T_A = T_J = -40^{\circ}C$  to +125°C, typical values are at  $T_A = T_J = +25^{\circ}C$

| PARAMETER               | SYMBOL                  | CONDITIONS                                             | MIN TYP | MAX | UNITS |  |

|-------------------------|-------------------------|--------------------------------------------------------|---------|-----|-------|--|

|                         |                         | B_RU_SR[2:0] = 000b<br>(Note 6)                        | 1.25    |     |       |  |

|                         |                         | B_RU_SR[2:0] = 001b<br>(Note 6)                        | 2.5     |     |       |  |

|                         |                         | B_RU_SR[2:0] = 010b<br>(Note 6)                        | 5       |     |       |  |

| DVS Ramp-Up Slew Rate   |                         | B_RU_SR[2:0] = 011b<br>(Note 6)                        | 10      |     | mV/μs |  |

|                         |                         | B_RU_SR[2:0] = 100b<br>(default) (Note 6)              | 20      |     |       |  |

|                         |                         | B_RU_SR[2:0] = 101b<br>(Note 6)                        | 40      |     |       |  |

|                         |                         | B_RU_SR[2:0] = 110b or 111b (Note 6)                   | 60      |     |       |  |

|                         |                         | B_RD_SR[2:0] = 000b<br>(Note 6)                        | 1.25    |     |       |  |

|                         |                         | B_RD_SR[2:0] = 001b<br>(Note 6)                        | 2.5     |     |       |  |

|                         |                         | B_RD_SR[2:0] = 010b<br>(default) (Note 6)              | 5       |     |       |  |

| DVS Ramp-Down Slew Rate |                         | B_RD_SR[2:0] = 011b<br>(Note 6)                        | 10      |     | mV/μs |  |

|                         |                         | B_RD_SR[2:0] = 100b<br>(Note 6)                        | 20      |     |       |  |

|                         |                         | B_RD_SR[2:0] = 101b<br>(Note 6)                        | 40      |     |       |  |

|                         |                         | B_RD_SR[2:0] = 110b or<br>111b (Note 6)                | 60      |     |       |  |

| Turn-On Delay Time      | <sup>t</sup> ON_DLY1    | From EN signal to LXB switching with bias on (Note 6)  | 30      |     |       |  |

|                         | On Delay Time to N_DLY2 | From EN signal to LXB switching with bias off (Note 5) | 85      |     | - µs  |  |

## **Quad-Phase Buck Electrical Characteristics (continued)**

$(V_{SYS} = V_{INx} = +3.8V, V_{OUTx} = 0.85V, T_A = T_J = -40^{\circ}C$  to +125°C, typical values are at  $T_A = T_J = +25^{\circ}C$

| PARAMETER                       | SYMBOL                  | CONDITIONS                                                       | MIN   | TYP   | MAX   | UNITS |

|---------------------------------|-------------------------|------------------------------------------------------------------|-------|-------|-------|-------|

| POWER STAGE                     |                         |                                                                  |       |       |       | ,     |

|                                 | I <sub>OUT(MAX)</sub>   | RMS current per phase,<br>V <sub>IN</sub> < 3.2V (Note 5)        |       | 4000  |       |       |

| Maximum Output Current          | lout(max)               | RMS current per phase,<br>3.2V ≤ V <sub>IN</sub> ≤ 5.5V (Note 5) |       | 5000  |       | mA    |

|                                 | I <sub>PLIM</sub>       | Mx_ILIM[2:0] = 000b                                              |       | 3000  |       |       |

|                                 | I <sub>PLIM</sub>       | Mx_ILIM[2:0] = 001b                                              |       | 3600  |       |       |

|                                 | I <sub>PLIM</sub>       | Mx_ILIM[2:0] = 010b                                              |       | 4200  |       |       |

|                                 | I <sub>PLIM</sub>       | Mx_ILIM[2:0] = 011b                                              |       | 4800  |       |       |

| PMOS Peak Current Limit         | I <sub>PLIM</sub>       | Mx_ILIM[2:0] = 100b                                              |       | 5400  |       | mA    |

|                                 | I <sub>PLIM</sub>       | Mx_ILIM[2:0] = 101b<br>(default)                                 | 4800  | 6000  | 7200  |       |

|                                 | I <sub>PLIM</sub>       | Mx_ILIM[2:0] = 110b                                              |       | 6600  |       |       |

|                                 | I <sub>PLIM</sub>       | Mx_ILIM[2:0] = 111b                                              | 5200  | 7200  | 9200  |       |

|                                 | $I_{VLIM}$              | Mx_ILIM[2:0] = 000b                                              |       | 2000  |       | _     |

|                                 | $I_{VLIM}$              | Mx_ILIM[2:0] = 001b                                              |       | 2400  |       |       |

|                                 | $I_{VLIM}$              | Mx_ILIM[2:0] = 010b                                              |       | 2800  |       |       |

|                                 | $I_{VLIM}$              | Mx_ILIM[2:0] = 011b                                              |       | 3200  |       |       |

| NMOS Valley Current Limit       | $I_{VLIM}$              | Mx_ILIM[2:0] = 100b                                              |       | 3600  |       | mA    |

|                                 | $I_{VLIM}$              | Mx_ILIM[2:0] = 101b<br>(default)                                 | 3200  | 4000  | 4800  |       |

|                                 | I <sub>VLIM</sub>       | Mx_ILIM[2:0] = 110b                                              |       | 4400  |       |       |

|                                 | $I_{VLIM}$              | Mx_ILIM[2:0] = 111b                                              | 3800  | 4800  | 5800  |       |

| NMOS Negative Current Limit     | I <sub>NLIM</sub>       | Per phase                                                        | -2000 | -1500 | -1000 | mA    |

| Switching Frequency             | $f_{\sf SW}$            | V <sub>OUT</sub> = default, Forced<br>PWM mode                   | 1.6   | 2.0   | 2.8   | MHz   |

| High-Side PMOS<br>On-Resistance | R <sub>DSON(PMOS)</sub> | INx to LXx, I <sub>LXx</sub> = -150mA                            |       | 32    | 70    | mΩ    |

| Low-Side NMOS<br>On-Resistance  | R <sub>DSON(NMOS)</sub> | LXx to PGNDx, I <sub>LXx</sub> = 150mA                           |       | 15    | 29    | mΩ    |

| LX Active Discharge Resistance  | R <sub>AD_LX</sub>      | Resistance from LXx to PGNDx, per phase, output disabled         |       | 100   | 200   | Ω     |

## **Quad-Phase Buck Electrical Characteristics (continued)**

$(V_{SYS} = V_{INx} = +3.8V, V_{OUTx} = 0.85V, T_A = T_J = -40^{\circ}C$  to +125°C, typical values are at  $T_A = T_J = +25^{\circ}C$

| PARAMETER                            | SYMBOL                    | CONDITIONS                                                                                                                                                                  | MIN | TYP | MAX | UNITS             |  |

|--------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------------------|--|

| LX Leakage Current                   | I <sub>LKG_LX</sub>       | V <sub>LXx</sub> = 0V or 5.5V,<br>T <sub>A</sub> = +25°C                                                                                                                    | -1  | 0.1 | +1  | - µA              |  |

| LA Leakage Current                   | I <sub>LKG_LX</sub>       | V <sub>LXx</sub> = 0V or 5.5V,<br>T <sub>A</sub> = +85°C (Note 4)                                                                                                           |     | 1   |     | μΑ                |  |

| Nominal Inductance                   | L <sub>NOM</sub>          | (Note 5)                                                                                                                                                                    |     | 220 |     | nH                |  |

| Minimum Effective Output Capacitance | C <sub>OUT(EFF_MIN)</sub> | 0μA < I <sub>OUT</sub> < 5000mA per<br>phase (Note 5)                                                                                                                       |     | 16  |     | μF                |  |

| EFFICIENCY AND OUTPUT RIF            | PPLE                      |                                                                                                                                                                             |     |     |     |                   |  |

| Peak Efficiency                      | <b>ПРК</b>                | L = 220nH (DCR = $9m\Omega$ ),<br>COUT(EFF) = $16\mu$ F<br>(ESR = $5m\Omega$ , ESL = $300$ pH)<br>per Phase (Note 5)                                                        |     | 90  |     | %                 |  |

| Heavy Load Efficiency                | <sup>П</sup> НЕАVY        | $I_{OUT}$ = 5A, L = 220nH<br>(DCR = 9mΩ), C <sub>OUT</sub> (EFF) =<br>16μF (ESR = 5mΩ,<br>ESL = 300pH) per Phase<br>(Note 5)                                                |     | 75  |     | %                 |  |

| Skip Mode Output Ripple              | V <sub>RIP_</sub> SKIP    | Skip mode, $I_{OUT}$ = 0.1A,<br>L = 220nH (DCR = 9m $\Omega$ ),<br>$C_{OUT(EFF)}$ = 16 $\mu$ F (ESR<br>= 5m $\Omega$ , ESL = 300pH) per<br>phase (Note 7)                   |     | 10  |     | mV <sub>P-P</sub> |  |

| FPWM Mode Output Ripple              | V <sub>RIP_</sub> FPWM    | Forced PWM mode, differential remote sensing, IOUT = 0.1A, L = 220nH (DCR = $9m\Omega$ ), $C_{OUT(EFF)}$ = $16\mu F$ (ESR = $5m\Omega$ , ESL = $300pH$ ) per phase (Note 7) |     | 5   |     | mV <sub>P-P</sub> |  |

| POWER OK COMPARATOR                  |                           |                                                                                                                                                                             |     |     |     |                   |  |

| Output POK Trip Level                |                           | Rising threshold                                                                                                                                                            |     | 90  |     | %                 |  |

| Catpact Oil trip Lovoi               |                           | Falling threshold                                                                                                                                                           |     | 85  | 90  | ,,,               |  |

## I<sup>2</sup>C Electrical Characteristics

$(V_{SYS} = V_{INX} = +3.8V, \ V_{VIO} = +1.8V, \ T_A = T_J = -40^{\circ}C \ to \ +125^{\circ}C, \ typical \ values \ are \ at \ T_A = T_J = +25^{\circ}C)$

| PARAMETER                                      | SYMBOL               | CONDITIONS                                 | MIN                           | TYP                        | MAX                       | UNITS |

|------------------------------------------------|----------------------|--------------------------------------------|-------------------------------|----------------------------|---------------------------|-------|

| POWER SUPPLY                                   | 1                    | 1                                          | ı                             |                            |                           |       |

| VIO Supply Voltage Range                       | V <sub>VIO</sub>     |                                            | 1.65                          | 1.8                        | V <sub>SYS</sub>          | V     |

| VIO Dynamic Supply Current                     | I <sub>VIO</sub>     | f <sub>SCL</sub> = f <sub>SDA</sub> = 1MHz |                               | 50                         |                           | μA    |

| V <sub>SYS</sub> Dynamic Supply Current        | I <sub>SYS</sub>     |                                            |                               | 5                          |                           | μA    |

| SDA AND SCL I/O STAGES                         |                      |                                            |                               |                            |                           |       |

| SCL, SDA Input High Voltage                    | V <sub>IH</sub>      |                                            | 0.7 x<br>V <sub>VIO</sub>     |                            |                           | V     |

| SCL, SDA Input Low Voltage                     | V <sub>IL</sub>      |                                            |                               |                            | 0.3 x<br>V <sub>VIO</sub> | V     |

| SCL, SDA Input Hysteresis                      | V <sub>HYS</sub>     |                                            |                               | 0.05 x<br>V <sub>VIO</sub> |                           | V     |

| SCL, SDA Input Hysteresis in HS<br>Mode        | V <sub>HYS_HS</sub>  |                                            |                               | 0.1 x<br>V <sub>VIO</sub>  |                           | V     |

| SDA Output Low Voltage                         | V <sub>OL</sub>      | I <sub>SINK</sub> = 5mA                    |                               |                            | 0.4                       | V     |

| SCL, SDA Input Capacitance                     | C <sub>I</sub>       |                                            |                               | 10                         |                           | pF    |

| SCL, SDA Input Leakage Current                 | l                    | T <sub>A</sub> = +25°C                     | -1                            | +0.001                     | +1                        | μA    |

| OCL, ODA IIIput Leakage Current                | l <sub>LK</sub>      | $T_A = +85^{\circ}C \text{ (Note 4)}$      |                               | 0.1                        |                           | μΛ    |

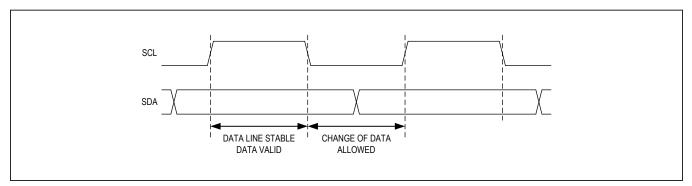

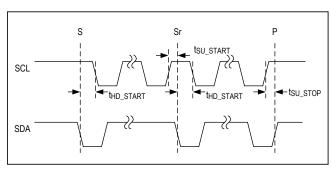

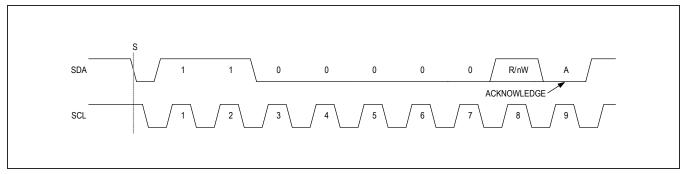

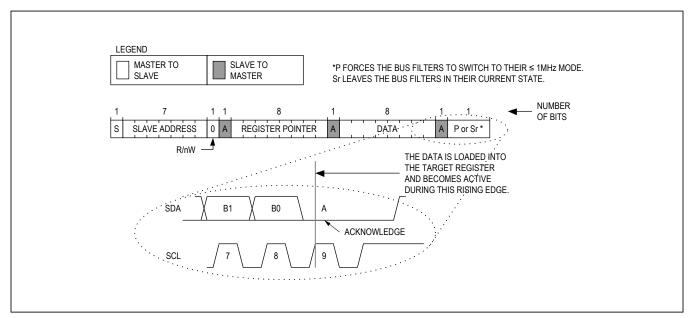

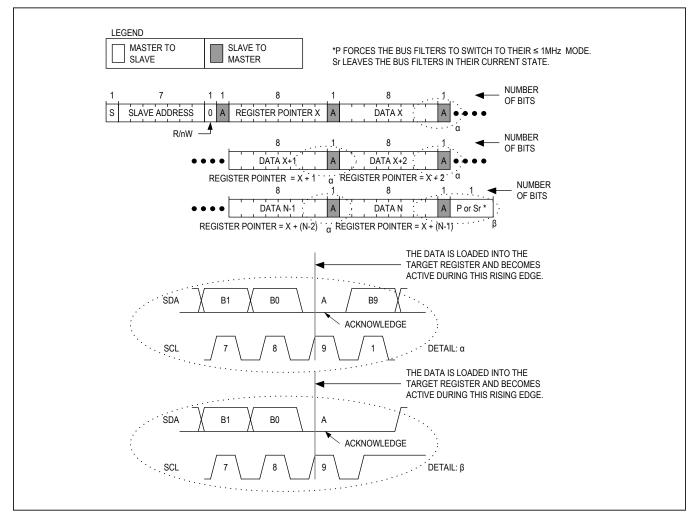

| I <sup>2</sup> C-COMPATIBLE INTERFACE TIL      | MING (STANDA         | RD, FAST AND FAST MODE PLUS                | S) (Note 5)                   |                            |                           |       |

| Clock Frequency                                | f <sub>SCL</sub>     |                                            | 0                             |                            | 1000                      | kHz   |

| Bus Free Time between STOP and START Condition | t <sub>BUSF</sub>    |                                            | 0.5                           |                            |                           | μs    |

| Hold Time (REPEATED) START Condition           | tHD_START            |                                            | 0.26                          |                            |                           | μs    |

| SCL Low Period                                 | t <sub>LOW</sub>     |                                            | 0.5                           |                            |                           | μs    |

| SCL High Period                                | tHIGH                |                                            | 0.26                          |                            |                           | μs    |

| Setup Time REPEATED START Condition            | tsu_start            |                                            | 0.26                          |                            |                           | μs    |

| Data Hold Time                                 | t <sub>HD_DATA</sub> | Transmit mode                              | 0                             |                            | 450                       | ns    |

| Data Setup Time                                | t <sub>SU_DATA</sub> |                                            | 50                            |                            |                           | ns    |

| SCL, SDA Receiving Rise Time                   | t <sub>R_REV</sub>   |                                            |                               |                            | 120                       | ns    |

| SCL, SDA Receiving Fall Time                   | t <sub>F_REV</sub>   |                                            | 20 x<br>V <sub>VIO</sub> /5.5 |                            | 120                       | ns    |

## I<sup>2</sup>C Electrical Characteristics (continued)

$(V_{SYS} = V_{INX} = +3.8V, \ V_{VIO} = +1.8V, \ T_A = T_J = -40^{\circ}C \ to \ +125^{\circ}C, \ typical \ values \ are \ at \ T_A = T_J = +25^{\circ}C)$

| PARAMETER                                                                    | SYMBOL                | CONDITIONS                                 | MIN                           | TYP | MAX | UNITS |

|------------------------------------------------------------------------------|-----------------------|--------------------------------------------|-------------------------------|-----|-----|-------|

| SCL, SDA Transmitting Fall Time                                              | t <sub>F_TRA</sub>    |                                            | 20 x<br>V <sub>VIO</sub> /5.5 |     | 120 | ns    |

| Setup Time for STOP Condition                                                | tsu_stop              |                                            | 0.26                          |     |     | μs    |

| Data Valid Time                                                              | t <sub>VD_DATA</sub>  |                                            |                               |     | 450 | ns    |

| Data Valid Acknowledge Time                                                  | t <sub>VD_ACK</sub>   |                                            |                               |     | 450 | ns    |

| Bus Capacitance                                                              | C <sub>B</sub>        |                                            |                               |     | 550 | pF    |

| Pulse Width of Suppressed<br>Spikes                                          | t <sub>SP</sub>       |                                            |                               |     | 50  | ns    |

| I <sup>2</sup> C-COMPATIBLE INTERFACE TI                                     | MING (HIGH-SP         | EED MODE, C <sub>B</sub> = 100pF) (Note 5) |                               |     |     |       |

| Clock Frequency                                                              | f <sub>SCL</sub>      |                                            |                               |     | 3.4 | MHz   |

| Hold Time (REPEATED) START Condition                                         | t <sub>HD_START</sub> |                                            | 160                           |     |     | ns    |

| SCL LOW Period                                                               | t <sub>LOW</sub>      |                                            | 160                           |     |     | ns    |

| SCL HIGH Period                                                              | tHIGH                 |                                            | 60                            |     |     | ns    |

| Setup Time REPEATED START Condition                                          | t <sub>SU_START</sub> |                                            | 160                           |     |     | ns    |

| Data Hold Time                                                               | t <sub>HD DATA</sub>  |                                            | 0                             |     | 70  | ns    |

| Data Setup Time                                                              | tsu data              |                                            | 10                            |     |     | ns    |

| SCL Rise Time                                                                | t <sub>R_SCL</sub>    | T <sub>A</sub> = +25°C                     | 10                            |     | 40  | ns    |

| SCL Rise Time after REPEATED<br>START Condition and after<br>Acknowledge Bit | <sup>t</sup> R_SCL1   | T <sub>A</sub> = +25°C                     | 10                            |     | 40  | ns    |

| SCL Fall Time                                                                | t <sub>F SCL</sub>    | T <sub>A</sub> = +25°C                     | 10                            |     | 40  | ns    |

| SDA Rise Time                                                                | t <sub>R SDA</sub>    | T <sub>A</sub> = +25°C                     | 10                            |     | 40  | ns    |

| SDA Fall Time                                                                | t <sub>F_SDA</sub>    | T <sub>A</sub> = +25°C                     |                               |     | 40  | ns    |

| Setup Time for STOP Condition                                                | t <sub>SU_STOP</sub>  |                                            | 160                           |     |     | ns    |

| Bus Capacitance                                                              | C <sub>B</sub>        |                                            |                               |     | 100 | pF    |

| Pulse Width of Suppressed<br>Spikes                                          | t <sub>SP</sub>       |                                            | 0                             |     | 10  | ns    |

## I<sup>2</sup>C Electrical Characteristics (continued)

$(V_{SYS} = V_{INX} = +3.8V, \ V_{VIO} = +1.8V, \ T_A = T_J = -40^{\circ}C \ to \ +125^{\circ}C, \ typical \ values \ are \ at \ T_A = T_J = +25^{\circ}C)$

| PARAMETER                                                                    | SYMBOL                | CONDITIONS                                 | MIN | TYP | MAX | UNITS |

|------------------------------------------------------------------------------|-----------------------|--------------------------------------------|-----|-----|-----|-------|

| I <sup>2</sup> C-COMPATIBLE INTERFACE TI                                     | MING (HIGH-SP         | EED MODE, C <sub>B</sub> = 400pF) (Note 5) |     |     |     |       |

| Clock Frequency                                                              | f <sub>SCL</sub>      |                                            |     |     | 1.7 | MHz   |

| Hold Time (REPEATED) START Condition                                         | t <sub>HD_START</sub> |                                            | 160 |     |     | ns    |

| SCL Low Period                                                               | t <sub>LOW</sub>      |                                            | 320 |     |     | ns    |

| SCL High Period                                                              | tHIGH                 |                                            | 120 |     |     | ns    |

| Setup Time REPEATED START Condition                                          | tsu_start             |                                            | 160 |     |     | ns    |

| DATA Hold Time                                                               | t <sub>HD_DATA</sub>  |                                            | 0   |     | 150 | ns    |

| DATA Setup Time                                                              | t <sub>SU_DATA</sub>  |                                            | 10  |     |     | ns    |

| SCL Rise Time                                                                | t <sub>R</sub> scl    | T <sub>A</sub> = +25°C                     | 20  |     | 80  | ns    |

| SCL Rise Time after REPEATED<br>START Condition and after<br>Acknowledge Bit | <sup>t</sup> R_SCL1   | T <sub>A</sub> = +25°C                     | 20  |     | 80  | ns    |

| SCL Fall Time                                                                | t <sub>F_SCL</sub>    | T <sub>A</sub> = +25°C                     | 20  |     | 80  | ns    |

| SDA Rise Time                                                                | t <sub>R_SDA</sub>    | T <sub>A</sub> = +25°C                     | 20  |     | 80  | ns    |

| SDA Fall Time                                                                | t <sub>F_SDA</sub>    | T <sub>A</sub> = +25°C                     |     |     | 80  | ns    |

| Setup Time for STOP Condition                                                | t <sub>SU_STOP</sub>  |                                            | 160 |     |     | ns    |

| Bus Capacitance                                                              | C <sub>B</sub>        |                                            |     |     | 400 | pF    |

| Pulse Width of Suppressed<br>Spikes                                          | t <sub>SP</sub>       |                                            | 0   |     | 10  | ns    |

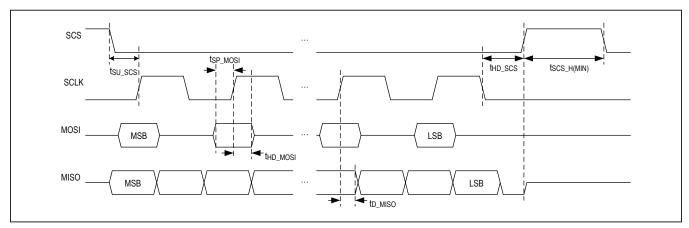

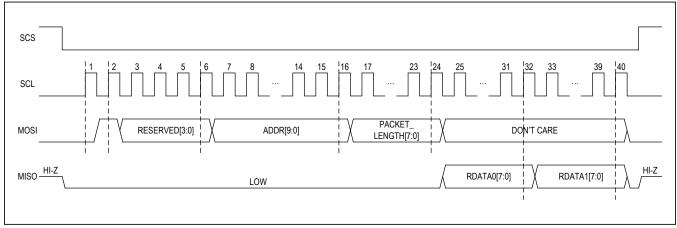

#### **SPI Electrical Characteristics**

$(V_{SYS} = V_{INx} = +3.8V, \ V_{VIO} = +1.8V, \ T_A = T_J = -40^{\circ}C \ to \ +125^{\circ}C, \ typical \ values \ are \ at \ T_A = T_J = +25^{\circ}C)$

| PARAMETER                              | SYMBOL                          | CONDITIONS                                               | MIN                       | TYP                       | MAX                       | UNITS |  |

|----------------------------------------|---------------------------------|----------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------|--|

| POWER SUPPLY AND I/O STAGE             | S                               |                                                          |                           |                           |                           |       |  |

| VIO Supply Voltage Range               | V <sub>VIO</sub>                |                                                          | 1.65                      | 1.8                       | V <sub>SYS</sub>          | V     |  |

| Input Leakage Current                  | I <sub>IH SPI</sub> ,           | T <sub>A</sub> = +25°C                                   | -1                        | +0.001                    | +1                        | μA    |  |

| (SCS, SCL, MOSI)                       | l <sub>IL_</sub> SPI            | T <sub>A</sub> = +85°C (Note 4)                          |                           | 0.1                       |                           | μΛ    |  |

| Input Capacitance<br>(SCS, SCL, MOSI)  | Cl                              |                                                          |                           | 10                        |                           | pF    |  |

| Input LOW Voltage<br>(SCS, SCL, MOSI)  | V <sub>IL</sub>                 |                                                          |                           |                           | 0.3 x<br>V <sub>VIO</sub> | ٧     |  |

| Input HIGH Voltage<br>(SCS, SCL, MOSI) | V <sub>IH</sub>                 |                                                          | 0.7 x<br>V <sub>VIO</sub> |                           |                           | V     |  |

| Input Hysteresis<br>(SCS, SCL, MOSI)   | V <sub>HYS</sub>                |                                                          |                           | 0.1 x<br>V <sub>VIO</sub> |                           |       |  |

| MISO Output Low Voltage                | V <sub>OL</sub>                 | I <sub>OL</sub> = 1mA                                    |                           |                           | 0.2                       | V     |  |

| MISO Output High Voltage               | V <sub>OH</sub>                 | I <sub>OH</sub> = 1mA                                    | V <sub>VIO</sub> - 0.2    |                           |                           | V     |  |

| MISO Lookaga Current                   | 1                               | High-impedance state,<br>T <sub>A</sub> = +25°C          | -1                        | +0.001                    | +1                        |       |  |

| MISO Leakage Current                   | I <sub>LK_HIZ</sub>             | High-impedance state,<br>T <sub>A</sub> = +85°C (Note 4) |                           | 0.1                       |                           | μA    |  |

| SPI INTERFACE TIMING (Note 5)          |                                 |                                                          |                           |                           |                           |       |  |

| SPI Operating Frequency                | f <sub>SCL</sub>                |                                                          |                           | 26                        | 30                        | MHz   |  |

| MOSI Input Valid to SCL Rising Edge    | tsu_mosi                        |                                                          | 10                        |                           |                           | ns    |  |

| MOSI Input Valid from SCL Rising Edge  | tHD_MOSI                        |                                                          | 10                        |                           |                           | ns    |  |

| MISO Valid from SCL Rising<br>Edge     | t <sub>D_MISO</sub>             | C <sub>L</sub> = 50pF                                    |                           | 9                         |                           | ns    |  |

| MISO Rising/Falling Time               | t <sub>R</sub> , t <sub>F</sub> | C <sub>L</sub> = 20pF                                    |                           |                           | 10                        | ns    |  |

| SCS Setup Time                         | t <sub>SU_SCS</sub>             |                                                          | 20                        |                           |                           | ns    |  |

| SCS Hold Time                          | t <sub>HD_</sub> scs            |                                                          | 20                        |                           |                           | ns    |  |

| Minimum SCS High Pulse Width           | tscs_H(MIN)                     |                                                          | 50                        |                           |                           | ns    |  |

Note 3: Limits are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed through correlation using statistical quality control methods.

Note 4: Guaranteed by ATE characterization. Not directly tested in production.

Note 5: Guaranteed by design. Not production tested.

Note 6: Guaranteed by design. Production tested through scan.

Note 7: Internal design target.

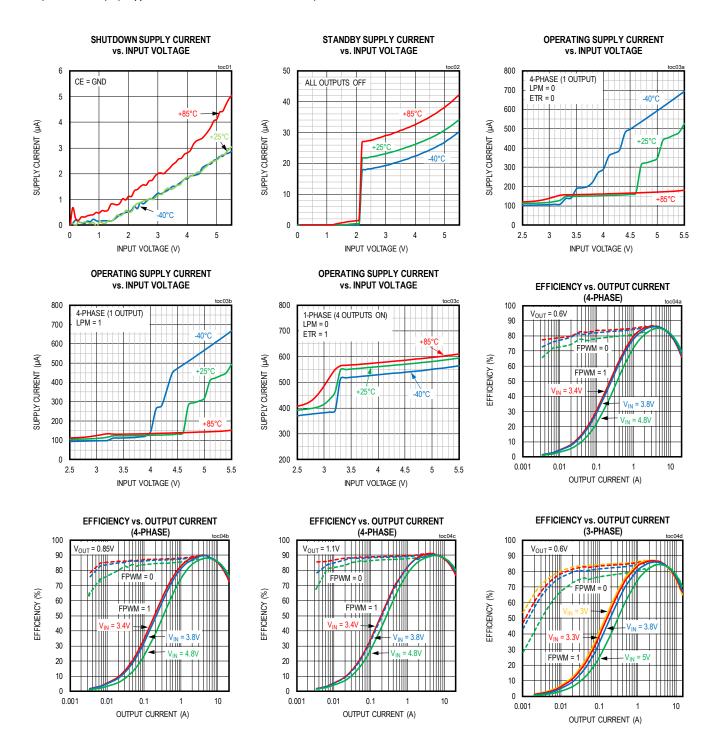

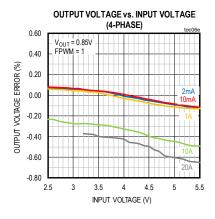

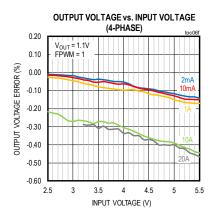

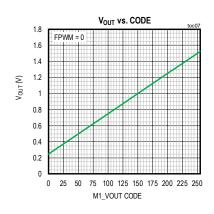

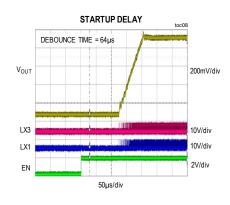

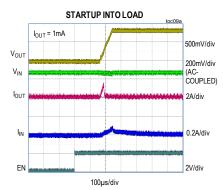

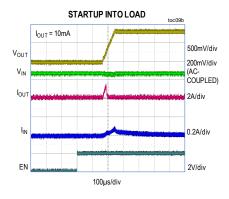

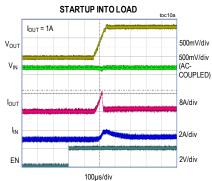

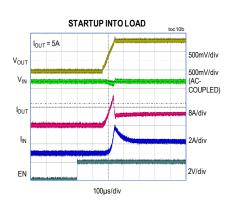

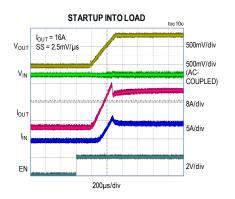

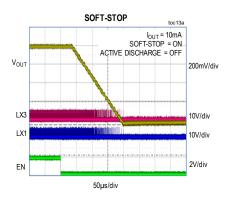

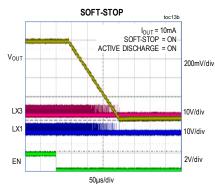

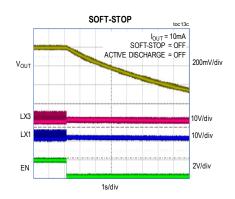

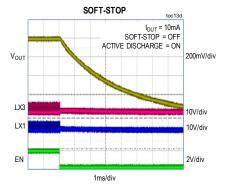

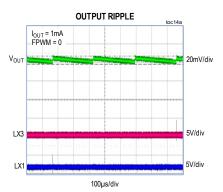

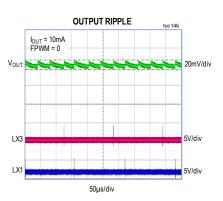

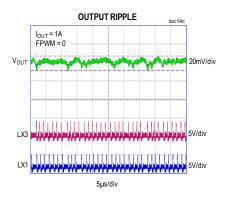

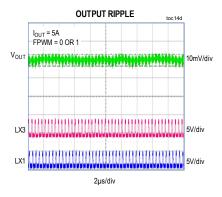

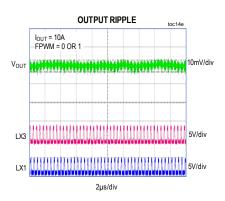

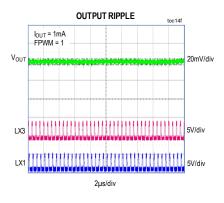

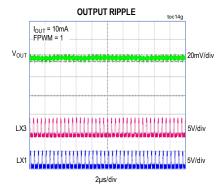

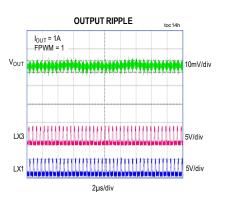

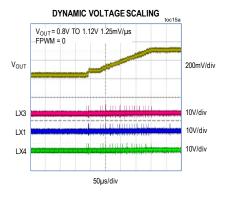

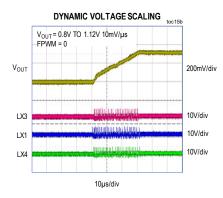

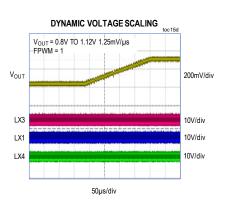

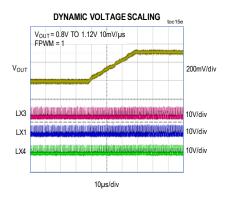

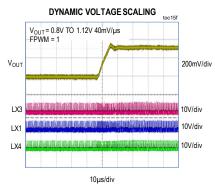

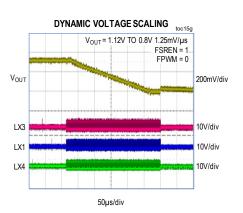

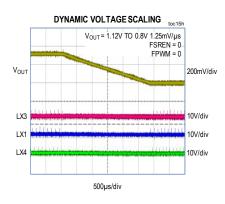

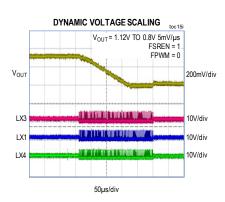

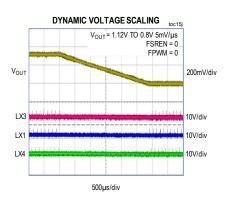

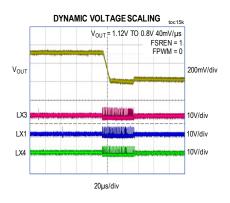

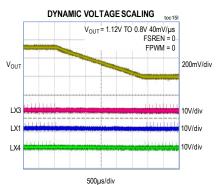

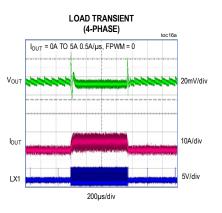

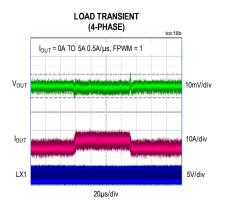

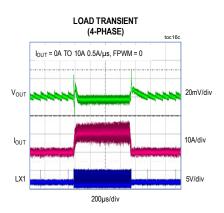

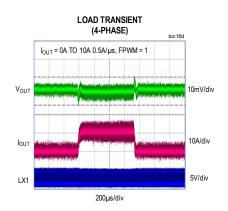

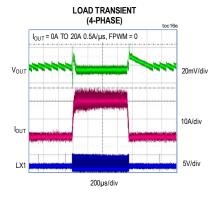

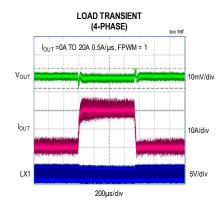

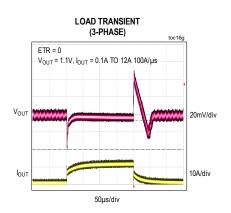

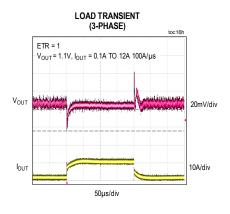

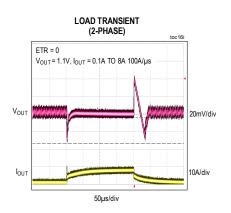

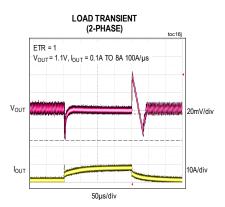

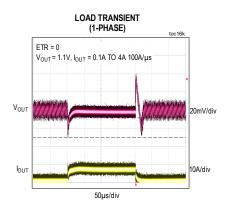

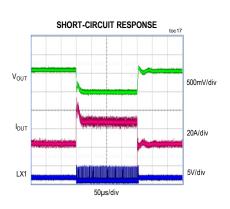

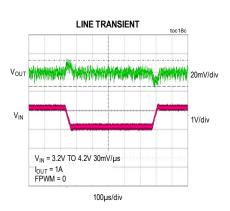

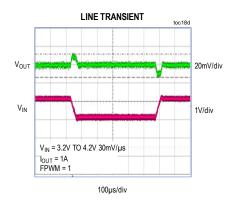

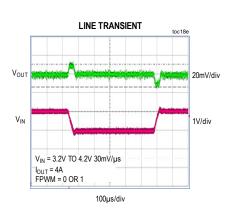

## **Typical Operating Characteristics**

$(V_{SYS} = 3.8V, V_{OUT} = 0.85V, I_{OUT} = 0A, CE = high, 4-Phase (1 Output), FPWM = 0, LPM = 0, ETR = 0, L = 220nH, C_{OUT} = (22\mu F + 0.1\mu F + 2 \times 4.3\mu F), T_A = +25^{\circ}C$ , unless otherwise noted.)

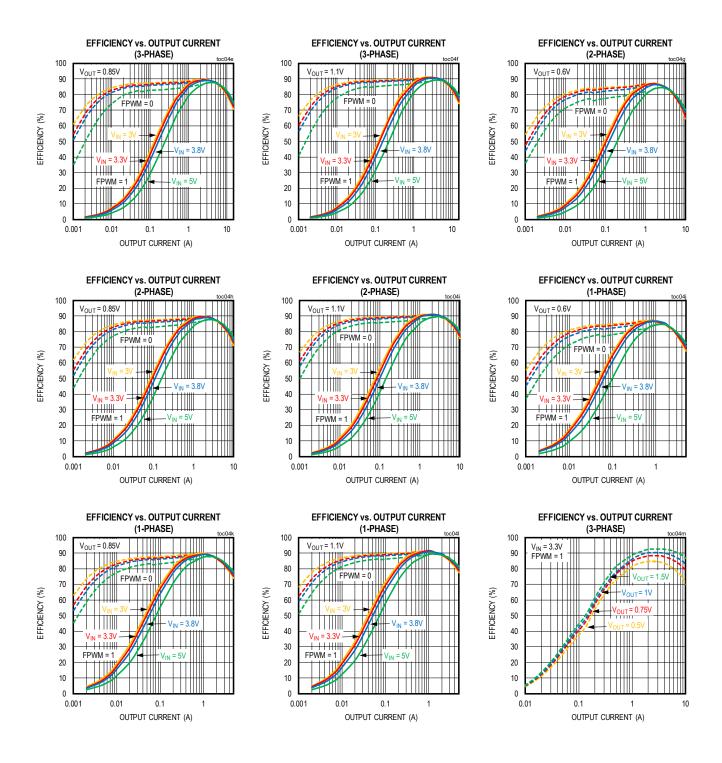

### **Typical Operating Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{OUT} = 0.85V, I_{OUT} = 0A, CE = high, 4-Phase (1 Output), FPWM = 0, LPM = 0, ETR = 0, L = 220nH, C_{OUT} = (22\mu F + 0.1\mu F + 2 \times 4.3\mu F), T_A = +25^{\circ}C$ , unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{OUT} = 0.85V, I_{OUT} = 0A, CE = high, 4-Phase (1 Output), FPWM = 0, LPM = 0, ETR = 0, L = 220nH, C_{OUT} = (22\mu F + 0.1\mu F + 2 \times 4.3\mu F), T_A = +25^{\circ}C$ , unless otherwise noted.)

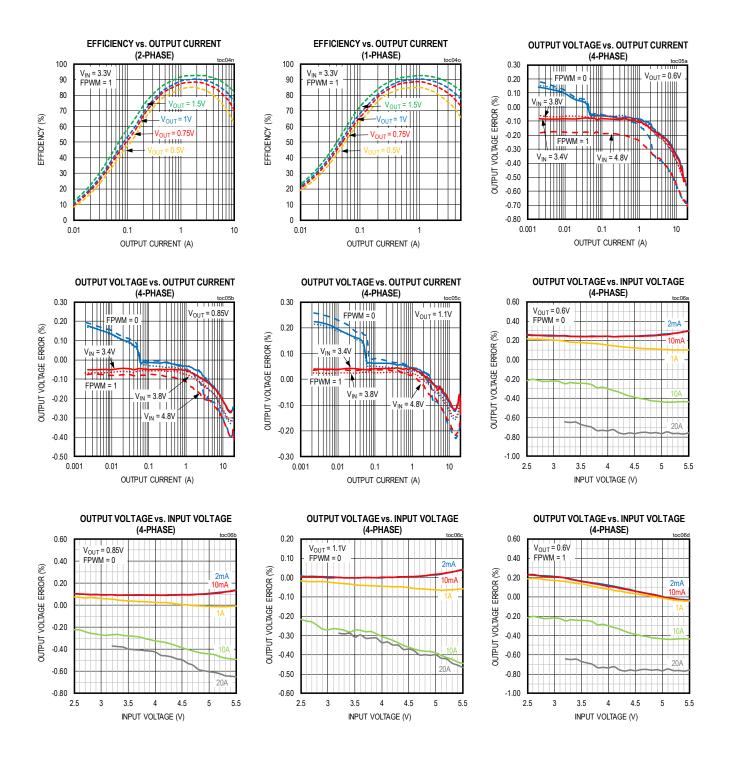

## **Typical Operating Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{OUT} = 0.85V, I_{OUT} = 0A, CE = high, 4-Phase (1 Output), FPWM = 0, LPM = 0, ETR = 0, L = 220nH, C_{OUT} = (22\mu F + 0.1\mu F + 2 \times 4.3\mu F), T_A = +25^{\circ}C$ , unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{OUT} = 0.85V, I_{OUT} = 0A, CE = high, 4-Phase (1 Output), FPWM = 0, LPM = 0, ETR = 0, L = 220nH, C_{OUT} = (22\mu F + 0.1\mu F + 2 \times 4.3\mu F), T_A = +25^{\circ}C$ , unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{OUT} = 0.85V, I_{OUT} = 0A, CE = high, 4-Phase (1 Output), FPWM = 0, LPM = 0, ETR = 0, L = 220nH, C_{OUT} = (22\mu F + 0.1\mu F + 2 \times 4.3\mu F), T_A = +25^{\circ}C$ , unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{OUT} = 0.85V, I_{OUT} = 0A, CE = high, 4-Phase (1 Output), FPWM = 0, LPM = 0, ETR = 0, L = 220nH, C_{OUT} = (22\mu F + 0.1\mu F + 2 \times 4.3\mu F), T_A = +25^{\circ}C$ , unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{OUT} = 0.85V, I_{OUT} = 0A, CE = high, 4-Phase (1 Output), FPWM = 0, LPM = 0, ETR = 0, L = 220nH, C_{OUT} = (22\mu F + 0.1\mu F + 2 \times 4.3\mu F), T_A = +25^{\circ}C$ , unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

$(V_{SYS} = 3.8V, V_{OUT} = 0.85V, I_{OUT} = 0A, CE = high, 4-Phase (1 Output), FPWM = 0, LPM = 0, ETR = 0, L = 220nH, C_{OUT} = (22\mu F + 0.1\mu F + 2 \times 4.3\mu F), T_A = +25^{\circ}C$ , unless otherwise noted.)

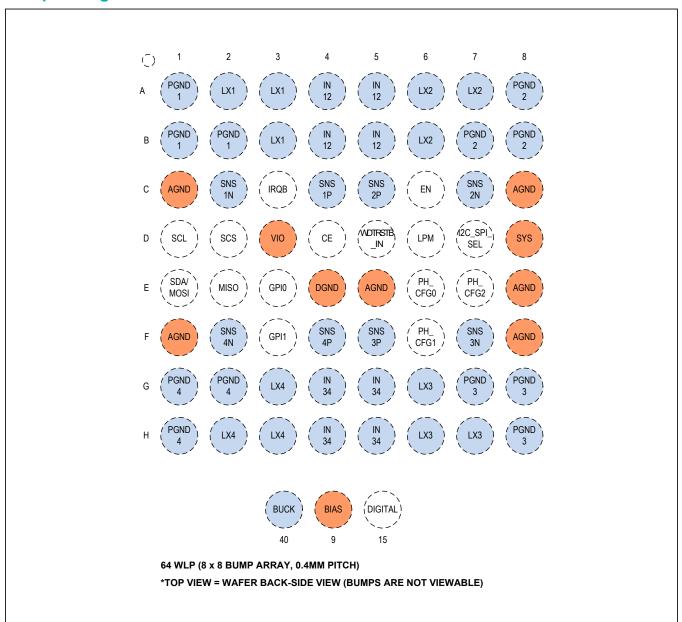

# **Bump Configuration**

# **Bump Description**

| BUMP                      | NAME        | FUNCTION                                                                                                                                                                                                                                               |  |  |  |

|---------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A1, B1, B2                | PGND1       | Phase1 Power Ground                                                                                                                                                                                                                                    |  |  |  |

| A2, A3, B3                | LX1         | Phase1 Switch Node                                                                                                                                                                                                                                     |  |  |  |

| A4, A5, B4, B5            | IN12        | Phase1/2 Input. Bypass to PGND1/2 with a 10µF capacitor.                                                                                                                                                                                               |  |  |  |

| A6, A7, B6                | LX2         | Phase 2 Switch Node                                                                                                                                                                                                                                    |  |  |  |

| A8, B7, B8                | PGND2       | Phase2 Power Ground                                                                                                                                                                                                                                    |  |  |  |

| C1, C8, E5, E8,<br>F1, F8 | AGND        | Analog Ground                                                                                                                                                                                                                                          |  |  |  |

| C2                        | SNS1N       | Phase1 Differential Negative Remote Sense Input                                                                                                                                                                                                        |  |  |  |

| C3                        | ĪRQ         | Interrupt Output. A $100k\Omega$ external pullup resistor to VIO is required. High impedance when CE = low.                                                                                                                                            |  |  |  |

| C4                        | SNS1P       | Phase 1 Differential Positive Remote Sense Input                                                                                                                                                                                                       |  |  |  |

| C5                        | SNS2P       | Phase 2 Differential Positive Remote Sense Input                                                                                                                                                                                                       |  |  |  |

| C6                        | EN          | Global Enable Input (Active-High, Logically ORed with GLB_EN Function of GPIs). An $800k\Omega$ internal pulldown resistance to DGND. If this pin is not used, leave it unconnected.                                                                   |  |  |  |

| C7                        | SNS2N       | Phase 2 Differential Negative Remote Sense Input                                                                                                                                                                                                       |  |  |  |

| D1                        | SCL         | I <sup>2</sup> C Clock Input. High impedance in off state. A 1.5k $\Omega$ ~2.2k $\Omega$ of pullup resistor to VIO is required.                                                                                                                       |  |  |  |

| D2                        | SCS         | Active-Low SPI Chip Select                                                                                                                                                                                                                             |  |  |  |

| D3                        | VIO         | IO Supply Voltage Input. Bypass to DGND with a 0.1µF capacitor.                                                                                                                                                                                        |  |  |  |

| D4                        | CE          | Active-High Chip Enable Input. CE = High (standby), I <sup>2</sup> C interface is enabled and regulators are ready to be turned on. CE = Low (shutdown), all regulators are turned off and all Type-O registers are reset to their POR default values. |  |  |  |

| D5                        | WDTRSTB_IN  | Active-Low Watchdog Timer Reset Input. An $800k\Omega$ internal pullup resistance to VIO. If this pin is not used, leave it unconnected.                                                                                                               |  |  |  |

| D6                        | LPM         | Global Low Power Mode Input (Active-High, Logically ORed with GLB_LPM Function of GPIs). An $800k\Omega$ internal pulldown resistance to DGND. If this pin is not used, leave it unconnected.                                                          |  |  |  |

| D7                        | I2C_SPI_SEL | Serial Interface Selection Input. Latches at V <sub>SYS</sub> POR.  I2C_SPI_SEL = Low: I <sup>2</sup> C  I2C_SPI_SEL = High (V <sub>SYS</sub> ): SPI                                                                                                   |  |  |  |

| D8                        | SYS         | System (Battery) Voltage Input. Bypass to AGND with a 1µF capacitor.                                                                                                                                                                                   |  |  |  |

| E1                        | SDA/MOSI    | I <sup>2</sup> C Data I/O. High Impedance in Off State. A 1.5k $\Omega$ ~2.2k $\Omega$ of pullup resistor to VIO is required. Configured as MOSI when SPI mode is selected.                                                                            |  |  |  |

| E2                        | MISO        | SPI Data Output. High impedance in off state.                                                                                                                                                                                                          |  |  |  |

| E3                        | GPI0        | Active-High, General-Purpose Input. An $800k\Omega$ internal pulldown resistance to DGND. If this pin is not used, leave it unconnected.                                                                                                               |  |  |  |

| E4                        | DGND        | Digital Ground                                                                                                                                                                                                                                         |  |  |  |

# **Bump Description (continued)**

| BUMP           | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E6             | PH_CFG0 | Phase Configuration Selection Input. Latches at $V_{SYS}$ POR.<br>PH_CFG2 = low, PH_CFG1 = low, PH_CFG0 = low: 4 phase PH_CFG2 = low, PH_CFG1 = low, PH_CFG0 = high $(V_{SYS})$ : 3 + 1 phase PH_CFG2 = low, PH_CFG1 = high $(V_{SYS})$ , PH_CFG0 = low: 2 + 2 phase PH_CFG2 = low, PH_CFG1 = high $(V_{SYS})$ , PH_CFG0 = high $(V_{SYS})$ : 2 + 1 + 1 phase PH_CFG2 = high $(V_{SYS})$ , PH_CFG1 = X, PH_CFG0 = X: 1 + 1 + 1 + 1 phase   |

| E7             | PH_CFG2 | Phase Configuration Selection Input. Latches at $V_{SYS}$ POR.<br>PH_CFG2 = low, PH_CFG1 = low, PH_CFG0 = low: 4 phase PH_CFG2 = low, PH_CFG1 = low, PH_CFG0 = high $(V_{SYS})$ : 3 + 1 phase PH_CFG2 = low, PH_CFG1 = high $(V_{SYS})$ , PH_CFG0 = low: 2 + 2 phase PH_CFG2 = low PH_CFG1 = high $(V_{SYS})$ , PH_CFG0 = high $(V_{SYS})$ : 2 + 1 + 1 phase PH_CFG2 = high $(V_{SYS})$ , PH_CFG1 = X, PH_CFG0 = X: 1 + 1 + 1 + 1 phase    |

| F2             | SNS4N   | Phase 4 Differential Negative Remote Sense Input                                                                                                                                                                                                                                                                                                                                                                                           |

| F3             | GPI1    | Active-High, General-Purpose Input. An $800k\Omega$ internal pulldown resistance to DGND. If this pin is not used, leave it unconnected.                                                                                                                                                                                                                                                                                                   |

| F4             | SNS4P   | Phase 4 Differential Positive Remote Sense Input                                                                                                                                                                                                                                                                                                                                                                                           |

| F5             | SNS3P   | Phase 3 Differential Positive Remote Sense Input                                                                                                                                                                                                                                                                                                                                                                                           |

| F6             | PH_CFG1 | Phase Configuration Selection Input. Latches at $V_{SYS}$ POR. PH_CFG2 = low, PH_CFG1 = low, PH_CFG0 = low: 4 phase PH_CFG2 = low, PH_CFG1 = low, PH_CFG0 = high ( $V_{SYS}$ ): 3 + 1 phase PH_CFG2 = low, PH_CFG1 = high ( $V_{SYS}$ ), PH_CFG0 = low: 2 + 2 phase PH_CFG2 = low, PH_CFG1 = high ( $V_{SYS}$ ), PH_CFG0 = high ( $V_{SYS}$ ): 2 + 1 + 1 phase PH_CFG2 = high ( $V_{SYS}$ ), PH_CFG1 = X, PH_CFG0 = X: 1 + 1 + 1 + 1 phase |

| F7             | SNS3N   | Phase 3 Differential Negative Remote Sense Input                                                                                                                                                                                                                                                                                                                                                                                           |

| G1, G2, H1     | PGND4   | Phase 4 Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                       |

| G3, H2, H3     | LX4     | Phase 4 Switch Node                                                                                                                                                                                                                                                                                                                                                                                                                        |

| G4, G5, H4, H5 | IN34    | Phase 3/4 Input. Bypass to PGND3/4 with a 10µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                  |

| G6, H6, H7     | LX3     | Phase 3 Switch Node                                                                                                                                                                                                                                                                                                                                                                                                                        |

| G7, G8, H8     | PGND3   | Phase 3 Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                       |

### **Detailed Description**

### **Top-Level System Management**

#### **System Faults**

The MAX77812 monitors the system for the following faults:

- Undervoltage lockout

- VIO fault

#### **Undervoltage Lockout**

When the  $V_{SYS}$  voltage falls below  $V_{UVLO\_F}$  (2.15V typ), the MAX77812 enters into a shutdown state and UVLO forces the MAX77812 to a dormant state until  $V_{SYS}$  voltage rises above the UVLO rising threshold (typically 2.5V). Once the  $V_{SYS}$  voltage is higher than the UVLO rising threshold, the MAX77812 comes out of shutdown mode to be securely functional. The UVLO falling threshold is programmable through I<sup>2</sup>C, but it must be set lower than UVLO rising threshold to avoid unexpected behaviors.

#### **VIO Fault**

When the VIO supply falls below  $V_{TH\_VIO\_OK}$  (1.0V typ), the MAX77812 immediately goes into a shutdown state and stays in this mode until IO supply rises beyond  $V_{TH\_VIO\_OK}$  threshold.

#### **Thermal Protection**

The MAX77812 has a centralized thermal protection circuit which monitors temperature on the die. If the die temperature exceeds +165°C ( $T_{SHDN}$ ), the MAX77812 initiates a soft-stop for all the output(s) and all Type-O registers are reset to their POR default values. However, the MAX77812 should be able to communicate with the host processor through the serial interface as long as  $V_{SYS}$  and  $V_{VIO}$  supplies are within the operating range.

In case the die temperature drops by 15°C after the thermal protection occurs, the MAX77812 recovers to the normal state and the output(s) can be turned on again.

In addition to  $+165^{\circ}$ C threshold, there are two additional comparators which trip at  $+120^{\circ}$ C and  $+140^{\circ}$ C. Interrupts are generated in the event the die temperature reaches  $+120^{\circ}$ C or  $+140^{\circ}$ C.

#### **Reset Conditions**

#### Power-On Reset (POR)

When a valid system supply voltage is applied to the device, the MAX77812 goes into shutdown mode and

stay there until CE goes high. As the V<sub>SYS</sub> voltage rises above POR threshold ( $\approx$  1.60V), the internal reference and the integrated supply are enabled and the MAX77812 starts loading the default register values from the OTPs.

#### **System Reset**

When  $V_{SYS}$  voltage drops below its POR threshold ( $\approx$  1.50V), all Type-S1 registers are reset to their POR default values.

#### **Off Reset**

Off reset occurs by any power-off or shutdown events. This condition resets all Type-O registers to their POR default values.

#### **Software Reset**

All Type-O registers can be reset by writing '1' to SW\_RST bit in REG\_RESET register. This bit clears to '0' upon reset.

#### Watchdog Timeout Reset (WDTRSTB\_IN)

In case the host processor fails to reset its watchdog timer for any system issues, WDTRSTB\_IN signal goes low for about 100ms. When the MAX77812 detects that WDTRSTB\_IN is low longer than its debounce timer (programmable by WDT\_DEB[2:0]), the output voltage setting registers of all phases (Mx\_VOUT[7:0]) reset to their POR default values and the output voltages return to their POR default values with given ramp-up/down slew rates.

#### Chip Enable (CE)

When  $V_{SYS}$  and  $V_{VIO}$  supplies are valid, a logic-high on CE pin puts the MAX77812 into standby mode (enabled). In standby mode, all user registers are accessible through I<sup>2</sup>C/SPI so that the host processor can overwrite the default output voltages of regulators and each regulator can be enabled by either I<sup>2</sup>C/SPI or GPI input if applicable.