#

## ±1%, Ultra-Low Output Voltage, Dual and Triple Linear n-FET Controllers

## **General Description**

The MAX8563/MAX8564/MAX8564A ultra-low-output dual and triple LDO controllers allow flexible and inexpensive point-of-load voltage conversion in motherboards, desknotes, notebooks, and other applications.

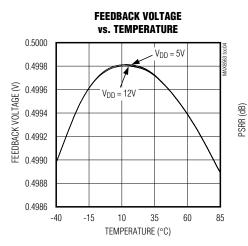

These parts feature a 0.5V reference voltage with  $\pm 1\%$  accuracy providing tight regulation of the output voltage. The MAX8563 has three n-channel MOSFET controller outputs, and the MAX8564/MAX8564A has two controller outputs.

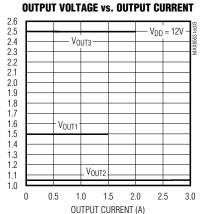

Each controller output is adjustable from 0.5V to 3.3V when  $V_{DD}$  = 12V and between 0.5V and 1.8V when  $V_{DD}$  = 5V. Each output is independently enabled and asserts a POK signal when the output reaches 94% of the set value. Each output is protected against a soft short-circuit condition by an undervoltage comparator that disables the output when it drops to under 80% of the set voltage for more than 50µs. For a catastrophic short condition, the regulators are shut down immediately if the output drops below 60% of the set voltage.

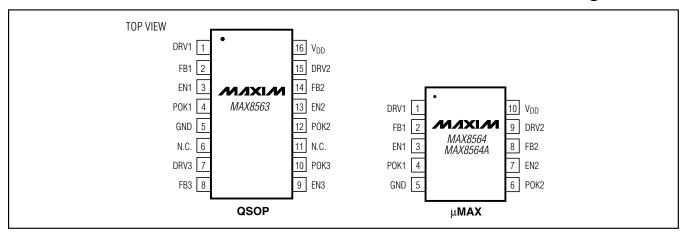

The MAX8563 is available in a 16-pin QSOP package, and the MAX8564/MAX8564A are available in a 10-pin  $\mu\text{MAX}^{(\!R\!)}$  package.

## **Applications**

Motherboards Dual/Triple Power Supplies Desknotes and Notebooks Graphic Cards Ultra-Low-Dropout Voltage Regulators Low-Voltage DSP, µP, and Microcontroller Power Supplies

### \_Features

- MAX8563: 3 Outputs

- MAX8564/MAX8564A: 2 Outputs

- ♦ ±1% Feedback Regulation

- ♦ Adjustable Output Voltage Down to 0.5V

- Can Use Ceramic Output Capacitors

- Wide Supply Voltage Range Permits Operation from 5V or 12V Rails

- Individual Enable Control and POK Signal Allows Sequencing

- Overload Protection Against Soft Short-Circuit Condition

- Undervoltage Short-Circuit Protection

- Drive n-Channel MOSFETs

### \_Ordering Information

| PART         | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|--------------|----------------|-----------------|-------------|

| MAX8563EEE   | -40°C to +85°C | 16 QSOP         | E16-1       |

| MAX8564EUB   | -40°C to +85°C | 10 µMAX         | U10-2       |

| MAX8564AEUB+ | -40°C to +85°C | 10 µMAX         | U10-2       |

|              | ,              |                 |             |

+Denotes lead-free package

#### Pin Configurations appear at end of data sheet.

µMAX is a registered trademark of Maxim Integrated Products, Inc.

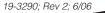

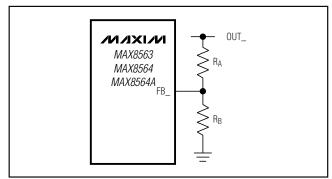

## **Typical Operating Circuit**

###

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

V<sub>DD</sub> to GND.....-0.3V to +14V DRV1, DRV2, DRV3, EN1, EN2, EN3 to GND.....-0.3V to (V<sub>DD</sub> + 0.3V) FB1, FB2, FB3, POK1, POK2, POK3 to GND.....-0.3V to +6V

Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) 10-Pin  $\mu$ MAX (derate 5.6mW/°C above +70°C)......444.4mW

16-Pin QSOP (derate 8.3mW/°C above +70°C).......666.7mW

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{EN1} = V_{EN2} = V_{EN3} = 5V, V_{GND} = 0V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                      | CONDITIONS                                                                                                                   |                         | MIN                    | ТҮР   | МАХ   | UNITS |    |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|-------|-------|-------|----|--|

| GENERAL                                        |                                                                                                                              |                         |                        |       |       |       |    |  |

| V <sub>DD</sub> Voltage Range                  |                                                                                                                              |                         |                        | 4.5   |       | 13.2  | V  |  |

| V <sub>DD</sub> Undervoltage-Lockout Threshold | Rising, 200mV hy                                                                                                             | /steresis (typ          | )                      | 3.56  | 3.76  | 4.00  | V  |  |

|                                                | $V_{EN} = V_{DD} = 12$                                                                                                       | V (MAX8563              | )                      |       | 930   | 1600  | μΑ |  |

| V <sub>DD</sub> Quiescent Current              | $V_{EN} = V_{DD} = 12$                                                                                                       | V (MAX8564              | /MAX8564A)             |       | 660   | 1200  |    |  |

| V <sub>DD</sub> Shutdown Current               | EN1 = EN2 = EN                                                                                                               | 3 = GND, V <sub>D</sub> | D = 12V                |       |       | 25    | μA |  |

| LDOs                                           |                                                                                                                              |                         |                        |       |       |       |    |  |

|                                                | $T_{A} = 0^{\circ}C \text{ to } +85^{\circ}$                                                                                 | C                       |                        | 0.494 | 0.5   | 0.504 | V  |  |

| FB_ Accuracy                                   | $T_A = -40^{\circ}C \text{ to } +8$                                                                                          | 5°C                     |                        | 0.489 |       | 0.509 | v  |  |

| ED Japant Diag Coursent                        | $T_A = +25^{\circ}C$                                                                                                         |                         |                        | -100  |       | +100  | nA |  |

| FB_ Input Bias Current                         | $T_A = +85^{\circ}C$                                                                                                         |                         |                        |       | -8    |       |    |  |

| DBV Soft Start Charging Current                | MAX8563, MAX8                                                                                                                | 564                     |                        |       | 100   |       |    |  |

| DRV_Soft-Start Charging Current                | MAX8564A                                                                                                                     |                         |                        |       | 10    |       | μA |  |

| DBV Max Sourcing Current                       | $V_{FR} = () 45V$                                                                                                            | $T_A = 0^{\circ}C$      | to +85°C               | 4     |       |       | mA |  |

| DRV_Max Sourcing Current                       |                                                                                                                              | $T_{A} = -40^{\circ}$   | °C to +85°C            | 3     | 7     |       |    |  |

| DRV_Max Sinking Current                        | $V_{FB_{-}} = 0.6V \qquad \frac{T_{A} = 0^{\circ}C \text{ to } +85^{\circ}C}{T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C}$ | $T_A = 0^{\circ}C$      | to +85°C               | 3     |       |       | m۸ |  |

| DRV_ Max Sinking Current                       |                                                                                                                              | °C to +85°C             | 1.8                    | 7     |       | mA    |    |  |

| DRV_Max Voltage                                | $V_{DD} = 5V, V_{FB_{-}} = 0.46V$                                                                                            |                         | 4.7                    |       |       | V     |    |  |

|                                                | V <sub>DD</sub> = 13.2V, V <sub>FB</sub> = 0.46V                                                                             |                         |                        | 8.0   |       | 10.9  | V  |  |

| FB_ Slow Short-Circuit Threshold               | Measured at FB_                                                                                                              | (falling)               |                        |       | 400   |       | mV |  |

| FB_Fast Short-Circuit Threshold                | Measured at FB_                                                                                                              | (falling)               |                        |       | 300   |       | mV |  |

| Slow Short-Circuit Timer                       |                                                                                                                              |                         |                        |       | 50    |       | μs |  |

| FB_ to DRV_ Transconductance                   |                                                                                                                              |                         | 0.115                  | 0.24  | 0.460 | Mho   |    |  |

| LOGIC                                          |                                                                                                                              |                         |                        |       |       |       |    |  |

| EN_ Input Low Level                            |                                                                                                                              |                         |                        |       |       | 0.7   | V  |  |

| EN_ Input High Level                           |                                                                                                                              |                         | 1.3                    |       |       | V     |    |  |

| EN Input Lookage Current                       | $V_{EN} = 0$ and $V_{D}$                                                                                                     | D,                      | $T_A = +25^{\circ}C$   | -0.1  |       | +0.1  |    |  |

| EN_ Input Leakage Current                      | _                                                                                                                            |                         | T <sub>A</sub> = +85°C |       | 0.001 |       | μA |  |

### ELECTRICAL CHARACTERISTICS (continued)

(VDD = VEN1 = VEN2 = VEN3 = 5V, VGND = 0V, TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)

| PARAMETER                        | CONDI                       | CONDITIONS                                    |  |       | MAX | UNITS |

|----------------------------------|-----------------------------|-----------------------------------------------|--|-------|-----|-------|

| POK_ Threshold Falling           | Measured at FB_ (fallir     | Measured at FB_ (falling)                     |  |       | 455 | mV    |

| POK_ Threshold Rising at Startup | Measured at FB_ (risin      | Measured at FB_ (rising)                      |  |       | 485 | mV    |

| POK_ Output Low Level            | Sinking 1mA, $V_{DD} = 4$ . | Sinking 1mA, $V_{DD}$ = 4.5V, $V_{FB}$ = 0.4V |  |       | 0.1 | V     |

|                                  |                             | $T_A = +25^{\circ}C$                          |  |       | 0.1 |       |

| POK_ Output High Leakage         | $V_{DD} = 5.5V$             | T <sub>A</sub> = +85°C                        |  | 0.001 |     | μA    |

Note 1: Specifications are production tested at  $T_A = +25^{\circ}C$ . Maximum and minimum specifications over temperature are guaranteed by design.

VOUT2

V<sub>OUT1</sub>

$V_{DD} = 5V$

1.6

1.5

1.4

1.3

1.2

1.1

10

OUTPUT VOLTAGE (V)

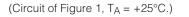

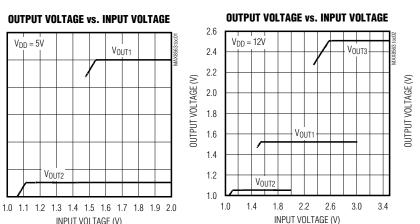

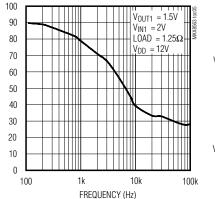

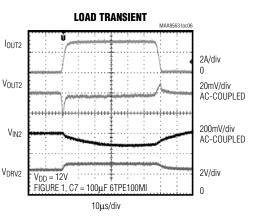

**Typical Operating Characteristics**

INPUT VOLTAGE (V)

///XI//

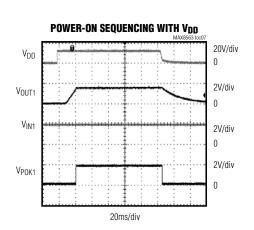

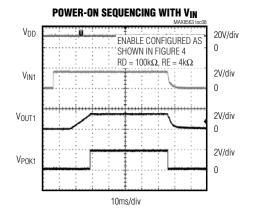

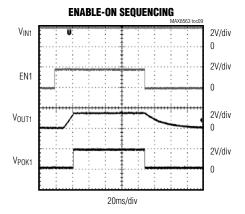

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $T_A = +25^{\circ}C$ .)

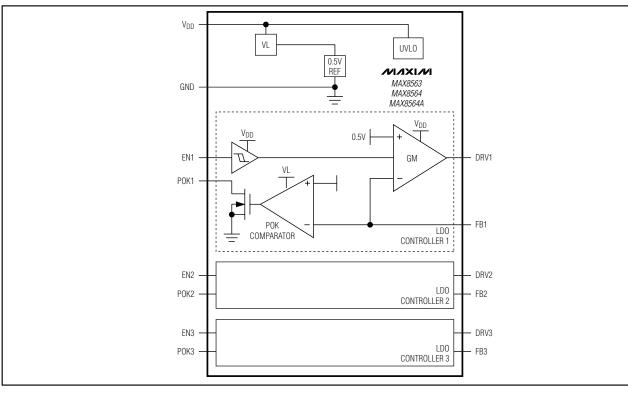

### **Functional Diagram**

### Pin Description

|     | NAME    |                      |                                                                                                                                                                                                                                                                |

|-----|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | MAX8563 | MAX8564/<br>MAX8564A | FUNCTION                                                                                                                                                                                                                                                       |

| 1   | DRV1    | DRV1                 | Output n-MOSFET Drive. Drives the gate of an external n-channel MOSFET to regulate output 1. DRV1 is internally pulled to ground when EN1 is logic low. Connect an external series RC circuit for compensation. See the <i>Stability Compensation</i> section. |

| 2   | FB1     | FB1                  | Feedback Input for Output 1. Connect to the center of a resistor-divider between output 1 and GND to set the output voltage of output 1. The feedback regulation voltage is 0.500V. See the <i>Output Voltage Setting</i> section.                             |

| 3   | EN1     | EN1                  | Enable Control for Output 1. Drive logic high to enable output 1, or logic low to disable the output. Connect to $V_{DD}$ for always-on operation.                                                                                                             |

| 4   | POK1    | POK1                 | Output 1 Power-Good Signal. Open-drain output pulls low when output 1 is 12% below the nominal regulated voltage.                                                                                                                                              |

| 5   | GND     | GND                  | Ground                                                                                                                                                                                                                                                         |

| 6   | _       | POK2                 | Output 2 Power-Good Signal. Open-drain output pulls low when output 2 is 12% below the nominal regulated voltage.                                                                                                                                              |

|     | N.C.    |                      | No Internal Connection                                                                                                                                                                                                                                         |

###

## Pin Description (continued)

| NAME |                                                                                                                                                                | AME                  |                                                                                                                                                                                                                                                                   |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN  | MAX8563                                                                                                                                                        | MAX8564/<br>MAX8564A | FUNCTION                                                                                                                                                                                                                                                          |  |  |  |  |

|      |                                                                                                                                                                |                      | Enable Control for Output 2. Drive logic high to enable output 2, or logic low to disable the output. Connect to $V_{DD}$ for always-on operation.                                                                                                                |  |  |  |  |

| 7    | DRV3                                                                                                                                                           | _                    | Output 3 n-MOSFET Drive. Drives the gate of an external n-channel MOSFET to regulate output 3. DRV3 is internally pulled to ground when EN3 is logic low. Connect an external series RC circuit for compensation. See the <i>Stability Compensation</i> section.  |  |  |  |  |

| 0    | _                                                                                                                                                              | FB2                  | Feedback Input for Output 2. Connect to the center of a resistor-divider between output 2 and GND to set the output voltage of output 2. The feedback regulation voltage is 0.500V. See the <i>Output Voltage Setting</i> section.                                |  |  |  |  |

| 8    | FB3                                                                                                                                                            | —                    | Feedback Input for Output 3. Connect to the center of a resistor-divider between output 3 and GND to set the output voltage of output 3. The feedback regulation voltage is 0.500V. See the <i>Output Voltage Setting</i> section.                                |  |  |  |  |

| 9    | 9 DRV2                                                                                                                                                         |                      | Output 2 n-MOSFET Drive. Drives the gate of the external n-channel MOSFET to regulate output 2. DRV2 is internally pulled to ground when EN2 is logic low. Connect an external series RC circuit for compensation. See the <i>Stability Compensation</i> section. |  |  |  |  |

|      | EN3 —                                                                                                                                                          |                      | Enable Control for Output 3. Drive logic high to enable output 3, or logic low to disable the output. Connect to $V_{DD}$ for always-on operation.                                                                                                                |  |  |  |  |

| 10   | - VDD ceramic or larger capacitor.                                                                                                                             |                      | +5V or +12V Supply Input. Connect to external +5V or +12V supply rail. Bypass with a 0.1 $\mu$ F ceramic or larger capacitor.                                                                                                                                     |  |  |  |  |

| 10   | POK3                                                                                                                                                           | _                    | Output 3 Power-Good Signal. Open-drain output pulls low when output 3 is 12% below the nominal regulated voltage.                                                                                                                                                 |  |  |  |  |

| 11   | N.C.                                                                                                                                                           | —                    | No Internal Connection                                                                                                                                                                                                                                            |  |  |  |  |

| 12   | POK2 — Output 2 Power-Good Signal. Open-drain output pulls low when output 2 is 12% below nominal regulated voltage.                                           |                      | Output 2 Power-Good Signal. Open-drain output pulls low when output 2 is 12% below the nominal regulated voltage.                                                                                                                                                 |  |  |  |  |

| 13   | 13 EN2 — Enable Control for Output 2. Drive logic high to enable output 2, or logic low to disab output. Connect to a V <sub>DD</sub> for always-on operation. |                      | Enable Control for Output 2. Drive logic high to enable output 2, or logic low to disable the output. Connect to a $V_{DD}$ for always-on operation.                                                                                                              |  |  |  |  |

| 14   | FB2                                                                                                                                                            | _                    | Feedback Input for Output 2. Connect to the center of a resistor-divider between output 2 and GND to set the output voltage of output 2. The feedback regulation voltage is 0.500V. See the <i>Output Voltage Setting</i> section.                                |  |  |  |  |

| 15   | DRV2                                                                                                                                                           | _                    | Output 2 n-MOSFET Drive. Drives the gate of the external n-channel MOSFET to regulate output 2. DRV2 is internally pulled to ground when EN2 is logic low. Connect an external series RC circuit for compensation. See the <i>Stability Compensation</i> section. |  |  |  |  |

| 16   | V <sub>DD</sub>                                                                                                                                                |                      | +5V or +12V Supply Input. Connect to an external +5V or +12V supply rail. Bypass with a 0.1µ ceramic or larger capacitor.                                                                                                                                         |  |  |  |  |

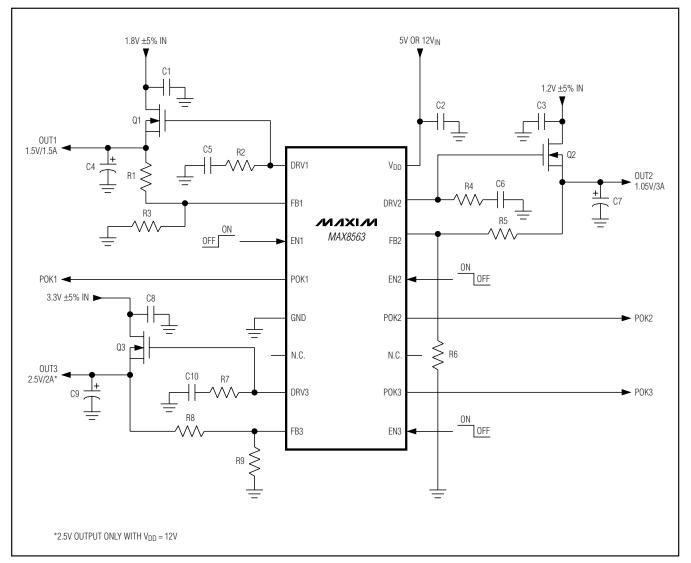

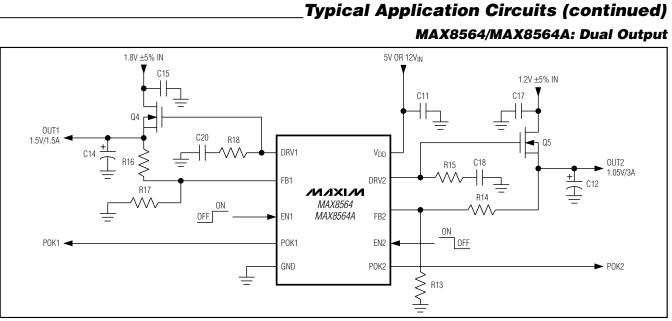

## **Typical Application Circuits**

MAX8563: Triple Output

Figure 1. MAX8563 Typical Application Circuit

Figure 2. MAX8564/MAX8564A Typical Application Circuit

### MAX8563 External Component List

| COMPONENTS     | QTY | DESCRIPTION                                                                                                                |  |

|----------------|-----|----------------------------------------------------------------------------------------------------------------------------|--|

| C1, C3, C8     | 3   | 2.2μF, 10V X5R ceramic capacitors<br>(optional 100μF, 18mΩ, 6.3V<br>aluminum electrolytic, Sanyo<br>GTPE100MI in parallel) |  |

| C2             | 1   | 0.1µF, 16V X7R ceramic capacitor                                                                                           |  |

| C4, C7, C9 3   |     | 100μF, 18mΩ, 6.3V aluminum<br>electrolytic capacitors<br>Sanyo GTPE100MI                                                   |  |

| C5, C6, C10    | 3   | 1µF, 16V X7R ceramic capacitors                                                                                            |  |

| Q1/Q2 (dual) 1 |     | Dual n-channel MOSFETs, 30V, 18m $\Omega$<br>Vishay Si4922DY                                                               |  |

| Q3 1           |     | n-channel MOSFET, 30V, 50m $\Omega$<br>Fairchild Semiconductor FDD6630A                                                    |  |

| R1             | 1   | $665\Omega \pm 1\%$ resistor                                                                                               |  |

| R2             | 1   | $620\Omega \pm 5\%$ resistor                                                                                               |  |

| R3             | 1   | $332\Omega \pm 1\%$ resistor                                                                                               |  |

| R4             | 1   | $390\Omega \pm 5\%$ resistor                                                                                               |  |

| R5 1           |     | $182\Omega \pm 1\%$ resistor                                                                                               |  |

| R6 1           |     | 165 $\Omega$ ±1% resistor                                                                                                  |  |

| R7 1           |     | 910 $\Omega$ ±5% resistor                                                                                                  |  |

| R8             | 1   | 1k $\Omega$ ±1% resistor                                                                                                   |  |

| R9             | 1   | 249 $\Omega$ ±1% resistor                                                                                                  |  |

### MAX8564/MAX8564A External Component List

| COMPONENTS QTY |   | DESCRIPTION                                                                                                                |

|----------------|---|----------------------------------------------------------------------------------------------------------------------------|

| C11            | 1 | 0.1µF, 16V X7R ceramic capacitor                                                                                           |

| C12, C14       | 2 | 100μF, 18mΩ, 6.3V aluminum<br>electrolytic capacitors<br>Sanyo GTPE100MI                                                   |

| C15, C17       | 2 | 2.2μF, 10V X5R ceramic capacitors<br>(optional 100μF, 18mΩ, 6.3V<br>aluminum electrolytic, Sanyo<br>GTPE100MI in parallel) |

| C18, C20       | 2 | 1µF, 16V X7R ceramic capacitors                                                                                            |

| Q4/Q5 (dual)   | 1 | Dual n-channel MOSFETs, 30V, 18m $\Omega$<br>Vishay Si4922DY                                                               |

| R13            | 1 | $165\Omega \pm 1\%$ resistor                                                                                               |

| R14            | 1 | $182\Omega \pm 1\%$ resistor                                                                                               |

| R15            | 1 | $390\Omega \pm 5\%$ resistor                                                                                               |

| R16            | 1 | $665\Omega \pm 1\%$ resistor                                                                                               |

| R17            | 1 | $332\Omega \pm 1\%$ resistor                                                                                               |

| R18            | 1 | $620\Omega \pm 5\%$ resistor                                                                                               |

### \_Detailed Description

The MAX8563/MAX8564/MAX8564A triple and dual LDO controllers allow flexible and inexpensive voltage conversion by controlling the gate of an external n-MOSFET in a source-follower configuration. The MAX8563/MAX8564/MAX8564A consist of multiple identical LDO controllers. Each LDO controller features an enable input (EN\_) and a power-OK output (POK\_). The MAX8563/MAX8564/MAX8564A also include a 0.5V reference, an internal regulator, and an undervoltage lockout (UVLO). The transconductance amplifier measures the feedback voltage on FB\_ and compares it to an internal 0.5V reference connected to the positive input. If the voltage on FB\_ is lower than 0.5V, the current output on the gate-drive output DRV is increased. If the voltage on FB\_ is higher than 0.5V, the current output on the gate-drive output is decreased.

**Bias Voltage (Vpp), UVLO, and Soft-Start** The MAX8563/MAX8564/MAX8564A bias current for internal circuitry is supplied by Vpp. The Vpp voltage range is from 4.5V to 13.2V. If Vpp drops below 3.76V (typ), the MAX8563/MAX8564/MAX8564A assume that the supply and reference voltages are too low and activate the UVLO circuitry. During UVLO, the internal regulator (VL) and the internal bandgap reference are forced off, DRV\_ is pulled to GND, and POK\_ is pulled low.

Before any internal startup circuitry is activated, V<sub>DD</sub> must be above the UVLO threshold. After UVLO indicates that V<sub>DD</sub> is high enough, the internal VL regulator, the internal bandgap reference, and the bias currents are activated. If EN\_ is logic-high after the internal reference and bias currents are activated, then the corresponding DRV\_ output initiates operation in soft-start mode. Once the voltage on FB\_ reaches 94% of the regulation threshold, the full output current of the LDO controller is permitted.

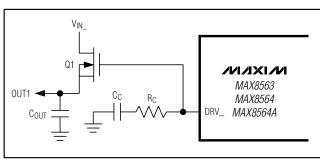

When an LDO is activated, the respective DRV\_ is pulled up from GND with a typical soft-start current of DRV soft-start. The soft-start current limits the slew of the output voltage and limits the initial spike of current that the drain of the external n-MOSFET receives. The size of the compensation capacitor (Cc) limits the slew rate (see Figure 3). This output voltage slew rate is equal to (DRV\_soft-start /C<sub>C</sub>)mV/ms, where C<sub>C</sub> is in µF. The maximum startup drain current is the ratio of C<sub>OUT</sub> to C<sub>C</sub> multiplied by the soft-start current.

#### Input Voltage (Drain Voltage of the External n-MOSFET)

The minimum input voltage to the drain of the n-MOSFET is a function of the desired output voltage and the dropout voltage of the n-MOSFET. Details on calculating

Figure 3. Soft-Start and Compensation Schematic

this value are covered in the *Power MOSFET Selection* section.

The maximum input voltage to the drain of the n-MOSFET is a function of the breakdown voltage and the thermal conditions during operation. The breakdown voltage from drain to source is normally provided in the MOSFET data sheet. The theoretical maximum input voltage is the set output voltage plus the breakdown voltage. The thermal constraint is usually the largest concern when discussing maximum input voltage. Details on calculating this value are covered in the Power MOSFET Selection section. The MOSFET package and thermal relief on the board are the largest contributors to removing heat from the n-MOSFET. Since output voltage is normally set and maximum output current is fixed, the input voltage becomes the only variable that determines the maximum power dissipated. Thus, the maximum input voltage is limited by the power capability of the n-MOSFET, if it is less than the breakdown voltage, which is most often the case. Ensure input capacitors handle the maximum input voltage.

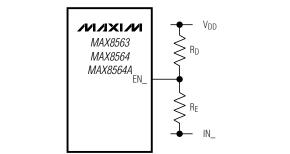

During a power-up sequence where V<sub>DD</sub> and EN\_ rise before the input to the drain of the n-MOSFET, the MAX8563/MAX8564/MAX8564A drive DRV\_ high but the output does not rise. As DRV\_ rails and V<sub>FB</sub>\_ is still below 80% of the regulation voltage, the MAX8563/MAX8564/ MAX8564A assume that an output short-circuit fault is present and shut down that regulator. To avoid this error condition, connect a resistor-divider from V<sub>DD</sub> to IN\_ with the middle node connected to the respective EN\_ (see Figure 4). Use the following equations to calculate the resistor values.

When VIN\_ is off or at a low-voltage state:

$$0.7 > \left(\frac{R_E}{R_E + R_D}\right) \times \left(V_{DD} - V_{IN_-}\right) + V_{IN_-}$$

When  $V_{IN}$  is on or at a high-voltage state:

Figure 4. Voltage-Divider on EN\_

$$1.3 < \left(\frac{R_E}{R_E + R_D}\right) \times \left(V_{DD} - V_{IN_-}\right) + V_{IN_-}$$

Set  $R_D = 100k\Omega$ . The above equations also assume that  $V_{DD} > V_{IN} > 1V$  when  $V_{IN}$  is on or at a high-voltage state, and that  $V_{DD} > 3V$ .

Example: Connect 100k $\Omega$  from EN to VDD and 4k $\Omega$  from EN\_ to IN\_. Thus, when VDD = 12V and VIN\_ = 0V, then VEN\_ = 0.46V. When VDD = 12V and VIN\_ = 1.2V, then VEN\_ = 1.6V.

Alternately, to avoid fault shutdown due to the delay of  $V_{IN}$  relative to  $V_{DD}$ , pull EN\_ low with a separate control logic and only drive high when  $V_{IN}$  reaches a steady-state value.

#### **Output Voltage**

The output voltage range at the source of the n-MOSFET is from 0.5V to 3.3V when  $V_{DD}$  is 12V and from 0.5V to 1.8V when  $V_{DD}$  is 5V. The maximum output voltage is a function of the minimum gate-to-source voltage (VGS) of the MOSFET and  $V_{DD}$ .

The external n-MOSFET contains a parasitic diode from source to drain. If the output is ever anticipated to exceed the input, current flows from source to drain. If this is undesirable, external protection is needed. A simple solution is the placement of a diode in series, from IN\_ to the drain of the n-MOSFET, so that reverse current is not possible. Due to the forward-voltage drop of the diode, the maximum output voltage is reduced and additional power is consumed in the diode.

#### **Enable and POK**

The MAX8563/MAX8564/MAX8564A have independent enable control inputs (EN1, EN2, and EN3). Drive EN1 high to enable output 1. Drive EN2 high to enable output 2. Drive EN3 high to enable output 3. When EN\_ is driven low, the corresponding DRV\_ is internally pulled to GND and POK\_ is internally pulled low. The POK\_ is an open-drain output that provides the status of the output voltage and pulls low depending upon circuit conditions. During startup, once the FB\_ reaches the POK\_ threshold, the POK\_ signal goes high. The POK\_ threshold has 30mV of hysteresis. When the output voltage drops 12% below the nominal regulated voltage, POK\_ pulls low. All POK\_ outputs pull low when UVLO is activated or when the internal VL regulator and reference are not ready.

#### Output Undervoltage and Overload Protection

When an overload event or short circuit occurs, the device that is most vulnerable is the external n-MOSFET. The MAX8563/MAX8564/MAX8564A monitor the output voltage to protect the MOSFET. When DRV\_ is at its maximum voltage and the output voltage drops below 80% but is still greater than 60% of its nominal voltage for more than 50µs, the MAX8563/MAX8564/MAX8564A shut down that particular regulator output by pulling DRV\_ to GND. Note that there is an additional inherent delay in turning off the MOSFET. The delay is a function of the compensation capacitor and the MOSFET. If the output recovers to greater than 80% within 50µs, it is not considered to be in overload and no action is taken. When the output voltage drops below 60% of its nominal voltage, the MAX8563/MAX8564/MAX8564A immediately shut down that particular regulator output by pulling DRV\_ to GND. To restart that particular LDO, V<sub>DD</sub> must be recycled below the UVLO or the corresponding EN\_ must be recycled. The overload protection is shown in the Typical Operating Characteristics.

#### Design Procedure

#### **Output Voltage Setting**

The minimum output voltage for each controller of the MAX8563/MAX8564/MAX8564A is typically 0.5V. The maximum output voltage is adjustable up to 3.3V with  $V_{DD} = 12V$ , and up to 1.8V with  $V_{DD} = 5V$ . To set the output voltage, connect the FB\_ pin to the center of a voltage-divider between OUT\_ and GND (Figure 5). The resistor-divider current should be at least 1mA per 1A of maximum output current; i.e., for a 3A maximum output current, set the resistor-divider bias current to  $\geq$  3mA:

$$I_{OUT(MIN)} \ge \frac{I_{OUT(MAX)}}{1000}$$

$R_B \le \frac{V_{FB}}{I_{OUT(MIN)}} = 1000 \times \frac{V_{FB}}{I_{OUT(MAX)}} = \frac{500}{I_{OUT(MAX)}}$

$$R_{A} = R_{B} \times \left[ \left( \frac{V_{OUT}}{V_{FB}} \right) - 1 \right] = R_{B} \times \left( 2 \times V_{OUT} - 1 \right)$$

To set the output voltage to 0.5V, disconnect RB from FB\_ and connect it to OUT\_; this change maintains the minimum load requirement on the output. In this case, RA can vary from 1k $\Omega$  to 10k $\Omega$ .

#### Input and Output Capacitor Selection

The input filter capacitor aids in providing low input impedance to the regulator and also reduces peak currents drawn from the power source during transient conditions. Use a minimum 2.2µF ceramic capacitor from IN\_ (drain of the external pass n-MOSFET) to GND (see Figures 1 and 2). If large line transients or load transients are expected, increase the input capacitance to help minimize output voltage changes.

The output filter capacitor and its equivalent series resistance (ESR) contribute to the stability of the regulator (see the *Stability Compensation* section) and affect the load-transient response. If large step loads (no load to full load) are expected, and a very fast response (less than a few microseconds) is required, use a 100µF, 18m $\Omega$  POSCAP for the output capacitor. If a larger capacitance is desired, keep the capacitance ESR product (COUT x RESR) in the 1µs to 5µs range.

If the application expects smaller load steps (less than 50% of full load), then use a 6.8µF ceramic capacitor or larger per ampere of maximum output current. This option reduces the size and cost of the regulator circuit. Note that some ceramic dielectrics exhibit large capacitance variation with temperature. Use X7R or X5R dielectrics to ensure sufficient capacitance at all operating temperatures. Tantalum and aluminum capacitors are not recommended.

#### **Power MOSFET Selection**

The MAX8563/MAX8564/MAX8564A use an n-channel MOSFET as the series pass transistor instead of a p-channel MOSFET to reduce cost. The selected MOS-FET must have a gate threshold voltage that meets the following criteria:

#### VGS\_MAX ≤ VDD - VOUT\_

where  $V_{DD}$  is the controller bias voltage, and  $V_{GS_MAX}$  is the maximum gate voltage required to yield the onresistance ( $R_{DS_ON}$ ) specified by the manufacturer's data sheet.  $R_{DS_ON}$  multiplied by the maximum output

Figure 5. Adjustable Output Voltage

current (load current) is the maximum voltage dropout across the MOSFET, V<sub>DS\_MIN</sub>. Make sure that V<sub>DS\_MIN</sub> meets the condition below to avoid entering dropout, where output voltage starts to decrease and any ripple on the input also passes through to the output:

#### VIN\_MIN > VDS\_MIN + VOUT

where  $V_{IN\_MIN}$  is the minimum input voltage at the drain of the MOSFET.  $V_{DS\_MIN}$  has a positive temperature coefficient; therefore, the value of  $V_{DS\_MIN}$  at the highest operating junction temperature should be used.

For thermal management, the maximum power dissipation in the MOSFET is calculated by:

$$P_D = (V_{IN}MAX - V_{OUT}) \times I_{OUT}MAX$$

The MOSFET is typically in an SMT package. Refer to the MOSFET data sheet for the PC board area needed to meet the maximum operating junction temperature required.

#### **Stability Compensation**

Connect a resistor, RC, and a capacitor, CC, in series from the DRV\_ pin to GND. The values of the compensation network depend upon the external MOSFET characteristics, the output current range, and the programmed output voltage. The following parameters are needed from the MOSFET data sheet: the input capacitance (C<sub>ISS</sub> at V<sub>DS</sub> = 1V), the typical forward transconductance (gFS), and the current at which gFS was measured (I<sub>DFS</sub>). Calculate the transconductance of the FET at the maximum load current (I<sub>OUT MAX</sub>):

$$g_{C(MAX)} = g_{FS} \times \sqrt{\frac{I_{OUT}_{MAX}}{I_{DFS}}}$$

M/XI/M

For the best transient response in applications with large step loads (see the *Input and Output Capacitor Selection* section for output capacitance requirements), use the following equations to select the compensation components:

$$C_{C} = \frac{\begin{bmatrix} 0.16 \times V_{OUT} \times C_{OUT} \times \\ g_{C(MAX)} \times (g_{C(MAX)} \times R_{ESR} + 1) \end{bmatrix}}{(g_{C(MAX)} \times V_{OUT} + I_{OUT} M_{AX})^{2}} - C_{ISS}$$

$$R_{C} = 59 \times \frac{V_{OUT} \times C_{OUT}(g_{C(MAX)} \times R_{ESR} + 1)}{C_{C} \times (g_{C(MAX)} \times V_{OUT} + I_{OUT} M_{AX})}$$

where  $C_{\mbox{OUT}}$  is the output capacitance and  $R_{\mbox{ESR}}$  is the ESR of  $C_{\mbox{OUT}}.$

To use a low-cost ceramic capacitor (see the *Input and Output Capacitor Selection* section for load-transient response characteristics), use the following equations to select the compensation components:

$$C_{C} = \frac{C_{OUT} \times g_{C(MAX)}}{(g_{C(MAX)} \times V_{OUT} + I_{OUT}MAX)} - C_{ISS}$$

$$R_{C} = 15 \times \frac{C_{OUT}}{C_{C} \times g_{C(MAX)}}$$

#### Example

OUTPUT 1 of Figure 1 is used in this example. Table 1 shows the values required to calculate the compensation. The values were taken from the appropriate data sheets and Figure 1.

## Table 1. Parameters Required toCalculate Compensation

| PARAMETER                 | CONDITIONS                                   | VALUE | UNITS |

|---------------------------|----------------------------------------------|-------|-------|

| MOSFET CISS               | MOSFET C <sub>ISS</sub> V <sub>DS</sub> = 1V |       | pF    |

| MOSFET GFS                | 10SFET GFS IDFS = 8.8A 30                    |       | S     |

| V <sub>OUT1</sub>         | Figure 1                                     | 1.5   | V     |

| IOUT_MAX Figure 1         |                                              | 1.5   | А     |

| COUT1                     | Figure 1                                     | 100   | μF    |

| R <sub>ESR</sub> Figure 1 |                                              | 18    | mΩ    |

$$\begin{array}{rcl} g_{C(MAX)} &=& 30S \ \times \ \sqrt{\frac{1.5A}{8.8A}} = 12.4S \\ C_{C} &=& 0.16 \ \times \frac{1.5V \ \times \ 100\mu F \ \times \ 12.4S \ \times \ \left(\frac{12.4S \ \times \ 18m\Omega + 1}{18m\Omega + 1}\right)}{\left(12.4S \ \times \ 1.5V \ + \ 1.5A\right)^{2}} - \\ &=& 2500pF = \ 0.90\mu F, \ \text{use} \ 1\mu F. \\ R_{C} &=& 59 \ \times \frac{1.5V \ \times \ 100\mu F \ \times \ (12.4S \ \times \ 18m\Omega \ + 1)}{1\mu F (12.4S \ \times \ 1.5V \ + \ 1.5A)} \\ &=& 599.4\Omega, \ \text{use} \ 620\Omega. \end{array}$$

#### **PC Board Layout Guidelines**

Due to the high-current paths and tight output accuracy required by most applications, careful PC board layout is required. An evaluation kit (MAX8563EVKIT) is available to speed design.

It is important to keep all traces as short as possible to maximize the high-current trace dimensions to reduce the effect of undesirable parasitic inductance. The MOSFET dissipates a fair amount of heat due to the high currents involved, especially during large input-to-output voltage differences. To dissipate the heat generated by the MOSFET, make power traces very wide with a large amount of copper area. An efficient way to achieve good power dissipation on a surface-mount package is to lay out copper areas directly under the MOSFET package on multiple layers and connect the areas through vias. Use a ground plane to minimize impedance and inductance. In addition to the usual high-power considerations, here are four tips to ensure high output accuracy:

- Ensure that the feedback connection to C<sub>OUT</sub> is short and direct.

- Place the feedback resistors next to the FB pin.

- Place R<sub>C</sub> and C<sub>C</sub> next to the DRV\_pin.

- Ensure FB\_ and DRV\_ traces are away from noisy sources to ensure tight accuracy.

## **Pin Configurations**

## \_Chip Information

TRANSISTOR COUNT: 1801 PROCESS: BICMOS

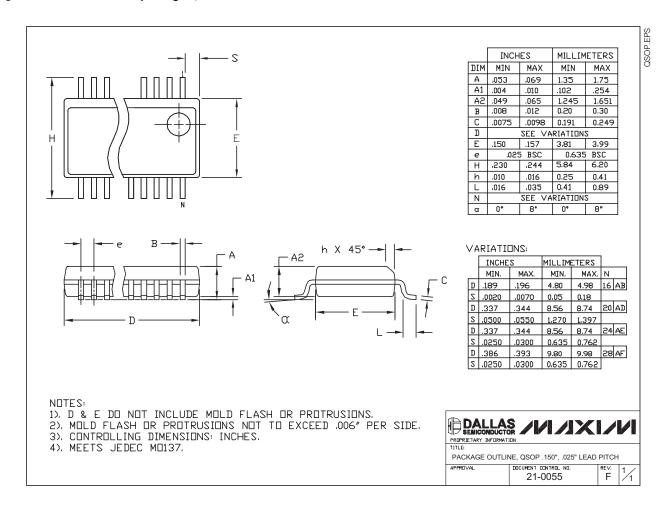

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

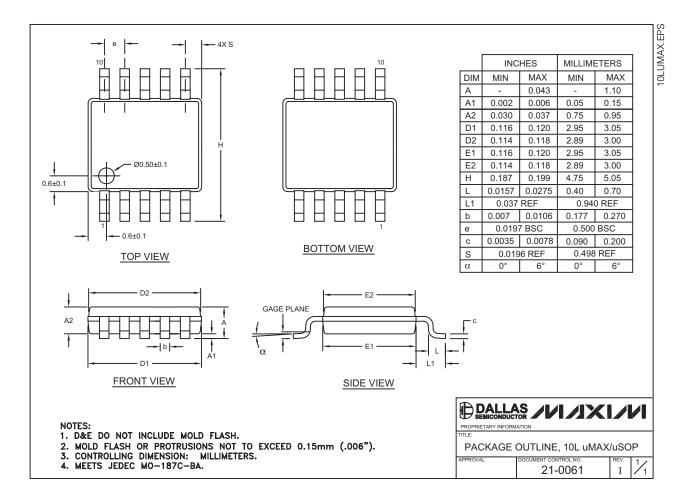

### \_Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

### **Revision History**

Pages changes at Rev 2: 1, 12, 14, 15

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2006 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LDO Voltage Controllers category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

AS1360-18-T MIC5156-5.0YN MIC5191YML-T5 MIC5191YMM LT3150CGN#PBF MAX1649CPA+ MIC5158YM MIC5157YM MIC5158YM TR MAX8563EEE+ MAX8564AEUB+ MAX8564EUB+ MIC5156YN MIC5190YMM MIC5156-5.0YM MIC5156YM MIC5156-3.3YN MIC5157YN MIC5159-1.8YM6-TR MIC5159YM6 TR NCV33269DR2G MAX1651ESA+ MAX1651CSA+ MAX1649ESA+ RN5RF33BA-TR-FE BD00IC0WEFJ-E2 BD12IC0WEFJ-E2 BD33GA3WEFJ-E2 BD33IA5WEFJ-E2 BD33IC0WEFJ-E2 BD50GA3WEFJ-E2 UC2834DW TLV717185PDQNR UC2832TDWEP UC2833DW UC2835D UC2836D UC3832DW UC3833DW UC3834DW UC3836D UCC2837D MIC5156-3.3YM UC2834DWG4 UC2836DG4 LFC789D25CDR