### **MAX8790**

## Six-String White LED Driver with Active Current Balancing for LCD Panel Applications

## **General Description**

The MAX8790 is a high-efficiency driver for white light-emitting diodes (LEDs). It is designed for large liquid-crystal displays (LCDs) that employ an array of LEDs as the light source. A current-mode step-up controller drives up to six parallel strings of multiple series-connected LEDs. Each string is terminated with ballast that achieves ±1.5% current regulation accuracy, ensuring even brightness for all LEDs. The MAX8790 has a wide input voltage range from 4.5V to 26V, and provides a fixed 20mA or adjustable 15mA to 25mA full-scale LED current.

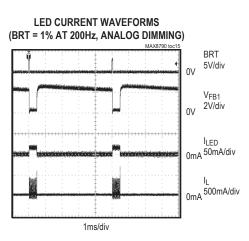

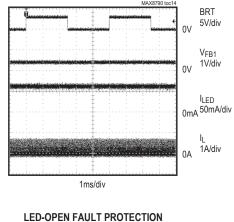

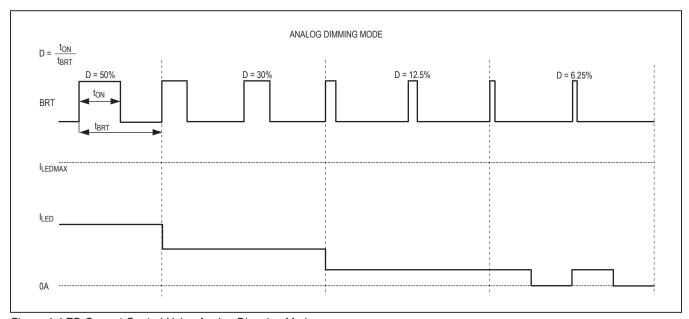

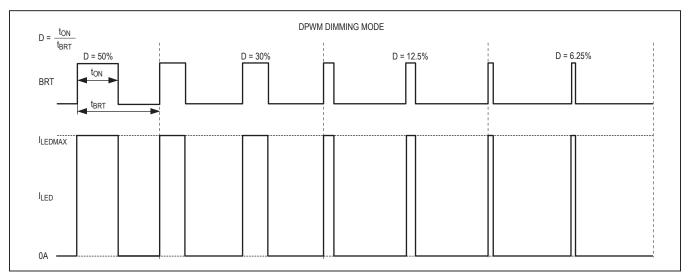

The MAX8790 has two dimming-control modes to enable a wide variety of applications. In direct DPWM mode, the LED current is directly turned on and off by a PWM signal. In analog dimming mode, an internal phase-locked loop (PLL) circuit translates the PWM signal into an analog signal and linearly controls the LED current down to 12.5%. Below 12.5%, digital dimming is added to allow lower average LED current down to 1%. Both control methods provide 100:1 dimming range.

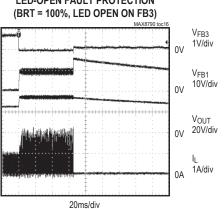

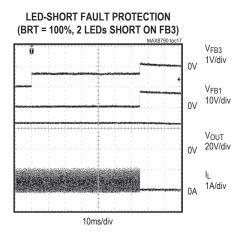

The MAX8790 has multiple features to protect the controller from fault conditions. Separate feedback loops limit the output voltage if one or more LEDs fail open or short. The controller features cycle-by-cycle current limit to provide consistent operation and soft-start capability. A thermal-shutdown circuit provides another level of protection.

The step-up controller uses an external MOSFET, which provides good efficiency and allows for scalable output power and maximum operating voltage. Low feedback voltage at each LED string (450mV) helps reduce power loss. The MAX8790 features selectable switching frequency (500kHz, 750kHz, or 1MHz), which allows trade-offs between external component size and operating efficiency.

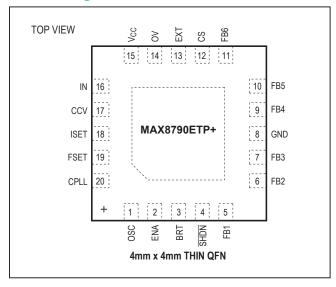

The MAX8790 is available in a thermally enhanced, lead(Pb)-free, 20-pin, 4mm x 4mm, TQFN package.

## **Applications**

- Notebook, Subnotebook, and Tablet Computer Displays

- Handy Terminals

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE                | PKG<br>CODE |

|-------------|----------------|----------------------------|-------------|

| MAX8790ETP+ | -40°C to +85°C | 20 Thin QFN<br>(4mm x 4mm) | T2044-3     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

#### **Features**

- Drives Six Parallel Strings with Multiple Series-Connected LEDs per String

- ±1.5% Current Regulation Accuracy Between Strings

- Low 450mV Feedback Voltage at Full Current Improves Efficiency

- Step-Up Controller Regulates the Output Just Above the Highest LED String Voltage

- Full-Scale LED Current Adjustable from 15mA to 25mA, or Preset 20mA

- Wide 100:1 Dimming Range

- Programmable Dimming Control: Direct DPWM or Analog Dimming

- Built-In PLL for Synchronized Dimming Control

- Open and Short LED Protections

- Output-Overvoltage Protection

- Wide Input Voltage Range from 4.5V to 26V

- External MOSFET Allows a Large Number of LEDs per String

- 500kHz/750kHz/1MHz Switching Frequency

- Small, 20-Pin, 4mm x 4mm TQFN Package

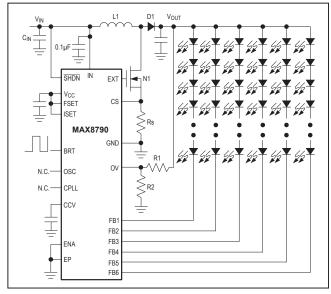

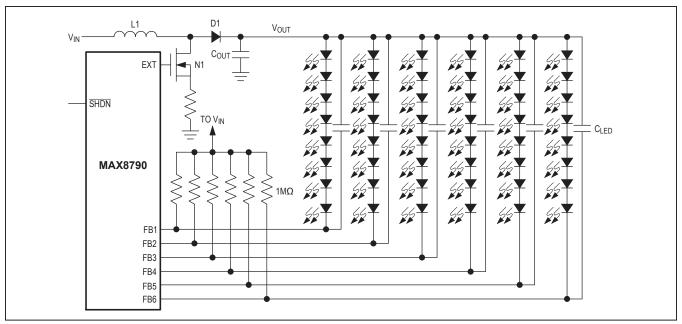

## Simplified Operating Circuit

Pin Configuration appears at end of data sheet.

## **Absolute Maximum Ratings**

| IN, SHDN, to GND0.3V to +28V                                          | Operating Temperature Range40°C to +85°C |

|-----------------------------------------------------------------------|------------------------------------------|

| FB_ to GND0.3V to +28V                                                | Junction Temperature+150°C               |

| V <sub>CC</sub> , BRT, ENA, OSC, OV to GND0.3V to +6V                 | Storage Temperature Range60°C to +150°C  |

| ISET, CCV, CS, FSET, CPLL, EXT to GND0.3V to (V <sub>CC</sub> + 0.3V) | Lead Temperature (soldering, 10s)+300°C  |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)                 |                                          |

| 20-Pin Thin OFN (derate 16.9mW/°C above +70°C) 1349mW                 |                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Electrical Characteristics**

(Circuit of Figure 1.  $V_{IN}$  = 12V,  $V_{\overline{SHDN}}$  =  $V_{IN}$ , CCV = 0.1 $\mu$ F,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                             |                                | CONDITIONS                                         | MIN                   | TYP             | MAX                   | UNITS  |

|---------------------------------------|--------------------------------|----------------------------------------------------|-----------------------|-----------------|-----------------------|--------|

| IN Innut Voltage Dange                | $V_{IN} = V_{CC}$              |                                                    | 4.5                   |                 | 5.5                   | V      |

| IN Input Voltage Range                | V <sub>CC</sub> = bypassed to  | GND through 1µF capacitor                          | 5.5                   |                 | 26.0                  | ] V    |

|                                       | \/                             | V <sub>IN</sub> = 26V                              |                       | 1               | 2                     | ^      |

| IN Quiescent Current                  | V <sub>SHDN</sub> = high       | $V_{IN} = V_{CC} = 5V$                             |                       | 1               | 2                     | mA mA  |

|                                       | SHDN = GND                     | ·                                                  |                       |                 | 10                    | μA     |

| V <sub>CC</sub> Output Voltage        | V <sub>SHDN</sub> = 5V, 6V < V | V <sub>IN</sub> < 26V, 0 < I <sub>VCC</sub> < 10mA | 4.7                   | 5.0             | 5.3                   | V      |

| V <sub>CC</sub> Short-Circuit Current |                                |                                                    | 15                    | 56              | 130                   | mA     |

| V <sub>CC</sub> UVLO Threshold        | Rising edge, hyster            | resis = 20mV                                       | 4.00                  | 4.25            | 4.45                  | V      |

| STEP-UP CONVERTER                     |                                |                                                    | '                     |                 |                       |        |

| EXT High Level                        | 10mA from EXT to               | GND                                                | V <sub>CC</sub> - 0.1 | V <sub>CC</sub> |                       | V      |

| EXT Low Level                         | -10mA from EXT to              | V <sub>CC</sub>                                    |                       | 0               | 0.1                   | V      |

| EXT On-Resistance                     | EXT high or low                |                                                    |                       | 2               | 5                     | Ω      |

| EXT Sink/Source Current               | EXT forced to 2V               |                                                    |                       | 1               |                       | Α      |

| OSC High-Level Threshold              |                                |                                                    | V <sub>CC</sub> - 0.4 |                 |                       | V      |

| OSC Midlevel Threshold                |                                |                                                    | 1.5                   |                 | V <sub>CC</sub> - 2.0 | V      |

| OSC Low-Level Threshold               |                                |                                                    |                       |                 | 0.4                   | V      |

|                                       | $V_{OSC} = V_{CC}$             |                                                    | 0.9                   | 1.0             | 1.1                   | MHz    |

| Operating Frequency                   | V <sub>OSC</sub> = open        |                                                    | 675                   | 750             | 825                   | lel I= |

|                                       | V <sub>OSC</sub> = GND         |                                                    | 450                   | 500             | 550                   | - kHz  |

| Minimum Duty Conta                    | PWM mode                       |                                                    |                       | 10              |                       | - %    |

| Minimum Duty Cycle                    | Pulse skipping, no load        |                                                    |                       | 0               |                       |        |

| Maximum Duty Cycle                    |                                |                                                    | 94                    | 95              |                       | %      |

| CS Trip Voltage                       | Duty cycle = 75%               |                                                    | 85                    | 100             | 115                   | mV     |

| CONTROL INPUT                         |                                |                                                    |                       |                 |                       |        |

| SHDN Logic-Input High Level           |                                |                                                    | 2.1                   |                 |                       | V      |

| SHDN Logic-Input Low Level            |                                |                                                    |                       |                 | 0.8                   | V      |

| BRT, ENA Logic-Input High Level       |                                |                                                    | 2.1                   | -               |                       | V      |

| BRT, ENA Logic-Input Low Level        |                                |                                                    |                       |                 | 0.8                   | V      |

## **Electrical Characteristics (continued)**

(Circuit of Figure 1.  $V_{IN}$  = 12V,  $V_{\overline{SHDN}}$  =  $V_{IN}$ , CCV = 0.1 $\mu$ F,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                      | CONDITIONS                                                  | MIN                    | TYP                   | MAX                       | UNITS             |  |

|--------------------------------|-------------------------------------------------------------|------------------------|-----------------------|---------------------------|-------------------|--|

| INPUT LEAKAGE                  |                                                             | '                      |                       |                           |                   |  |

| SHDN Leakage Current           | V <sub>SHDN</sub> = 26V                                     |                        |                       | +35                       | μA                |  |

| CS Leakage Current             | V <sub>CS</sub> = GND                                       |                        | +40                   | +50                       | μΑ                |  |

| OSC Leakage Current            |                                                             | -3                     |                       | +3                        | μΑ                |  |

| BRT, ENA Leakage Current       |                                                             | -1                     |                       | +1                        | μΑ                |  |

| FSET, ISET Leakage Current     | FSET = ISET = V <sub>CC</sub>                               | -1                     |                       | +1                        | μΑ                |  |

| OV Leakage Current             |                                                             | -0.1                   |                       | +0.1                      | μΑ                |  |

| LED CURRENT                    |                                                             |                        |                       |                           |                   |  |

|                                | ISET = V <sub>CC</sub> , BRT = 100%                         | 19.40                  | 20.00                 | 20.60                     |                   |  |

| Full-Scale FB_ Output Current  | $R_{ISET}$ = 80kΩ to GND, BRT = 100%                        | 24.25                  | 25.00                 | 25.75                     | mA                |  |

|                                | $R_{ISET}$ = 133kΩ to GND, BRT = 100%                       | 14.40                  | 15.00                 | 15.60                     |                   |  |

| ISET High-Level Threshold      | Default setting for 20mA full-scale LED current             | V <sub>CC</sub> - 0.4  |                       |                           | V                 |  |

| ISET Voltage                   |                                                             | 1.12                   | 1.19                  | 1.26                      | V                 |  |

| 20% Output Current             | ISET = V <sub>CC</sub> , BRT = 20%                          | 3.84                   | 4.00                  | 4.16                      | mA                |  |

| Current Regulation Between     | ISET = V <sub>CC</sub> , BRT = 100%                         | -1.5                   |                       | +1.5                      | %                 |  |

| Strings                        | ISET = V <sub>CC</sub> , BRT = 20%                          | -2.0                   |                       | +2.0                      | %                 |  |

|                                | $R_{ISET}$ = 80kΩ to GND, BRT = 100%                        | 300                    | 500                   | 800                       |                   |  |

| Minimum FB_ Regulation Voltage | ISET = V <sub>CC</sub> , BRT = 100%                         | 270                    | 450                   | 720                       | mV                |  |

|                                | ISET = V <sub>CC</sub> , 12.5%                              | 150                    | 275                   | 500                       |                   |  |

| Maximum FB_ Ripple             | ISET = $V_{CC}$ , COUT = 1 $\mu$ F, OSC = $V_{CC}$ (Note 1) |                        | 120                   | 200                       | mV <sub>P-P</sub> |  |

| FB_ On-Resistance              | V <sub>FB</sub> _ = 50mV                                    |                        | 13                    | 20                        | Ω                 |  |

| FB_ Leakage Current            | SHDN = GND, VFB_ = 26V                                      |                        |                       | 1                         | μΑ                |  |

|                                | $V_{\overline{SHDN}} = V_{IN}$ , BRT = GND, $V_{FB}$ = 15V  |                        | 10                    | 28                        |                   |  |

| BRT Input Frequency            |                                                             | 100                    |                       | 500                       | Hz                |  |

| Minimum BRT Duty Cycle         | PLL active                                                  |                        | 12.5                  |                           | %                 |  |

| FAULT PROTECTION               |                                                             |                        |                       |                           |                   |  |

| OV Threshold Voltage           |                                                             | 1.16                   | 1.23                  | 1.30                      | V                 |  |

| FB_ Overvoltage Threshold      |                                                             | V <sub>CC</sub> + 0.20 | V <sub>CC</sub> + 0.6 | V <sub>CC</sub> +<br>1.45 | V                 |  |

| FAULT Shutdown Timer           | V <sub>FB</sub> _ > 5.6V (typ)                              | 50                     | 65                    | 80                        | ms                |  |

| Thermal-Shutdown Threshold     | (Note 1)                                                    |                        | 170                   |                           | °C                |  |

| PHASE-LOCKED LOOP              |                                                             |                        |                       |                           |                   |  |

| FSET High-Level Threshold      | PLL disabled                                                | V <sub>CC</sub> - 0.4  |                       |                           | V                 |  |

| DDT Fraguanay Cantura Dange    | R <sub>FSET</sub> = 500kΩ                                   | 150                    | 200                   | 250                       | LI-               |  |

| BRT Frequency Capture Range    | $R_{FSET}$ = 250k $\Omega$                                  | 300                    | 400                   | 500                       | - Hz              |  |

## **Electrical Characteristics**

(Circuit of Figure 1.  $V_{IN}$  = 12V,  $V_{\overline{SHDN}}$  =  $V_{IN}$ , CCV = 0.1 $\mu$ F,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                             | CONDITIONS                         |                                                    | MIN                   | TYP | MAX                     | UNITS |

|---------------------------------------|------------------------------------|----------------------------------------------------|-----------------------|-----|-------------------------|-------|

| IN Innut Voltage Dange                | $V_{IN} = V_{CC}$                  |                                                    | 4.5                   |     | 5.5                     | V     |

| IN Input Voltage Range                | V <sub>CC</sub> bypassed to 0      | V <sub>CC</sub> bypassed to GND through 1μF cap    |                       |     | 26.0                    | V     |

|                                       | \/   hinh                          | V <sub>IN</sub> = 26V                              |                       |     | 2                       | A     |

| IN Quiescent Current                  | V <sub>SHDN</sub> = high           | V <sub>IN</sub> = V <sub>CC</sub> = 5V             |                       |     | 2                       | - mA  |

|                                       | SHDN = GND                         |                                                    |                       |     | 10                      | μA    |

| V <sub>CC</sub> Output Voltage        | V <sub>SHDN</sub> = 5V, 6V <       | V <sub>IN</sub> < 26V, 0 < I <sub>VCC</sub> < 10mA | 4.7                   |     | 5.3                     | V     |

| V <sub>CC</sub> Short-Circuit Current |                                    |                                                    | 12                    |     | 130                     | mA    |

| V <sub>CC</sub> UVLO Threshold        | Rising edge, hyste                 | resis = 20mV                                       | 4.00                  |     | 4.45                    | V     |

| STEP-UP CONVERTER                     |                                    |                                                    |                       |     |                         |       |

| EXT High Level                        | 10mA from EXT to                   | GND                                                | V <sub>CC</sub> - 0.1 |     |                         | V     |

| EXT Low Level                         | -10mA from EXT to                  | V <sub>CC</sub>                                    |                       |     | 0.1                     | V     |

| EXT On-Resistance                     | EXT high or low                    |                                                    |                       |     | 5                       | Ω     |

| OSC High-Level Threshold              |                                    |                                                    | V <sub>CC</sub> - 0.4 |     |                         | V     |

| OSC Midlevel Threshold                |                                    |                                                    | 1.5                   |     | V <sub>CC</sub><br>-2.0 | V     |

| OSC Low-Level Threshold               |                                    |                                                    |                       |     | 0.4                     | V     |

|                                       | V <sub>OSC</sub> = V <sub>CC</sub> |                                                    | 0.9                   |     | 1.1                     | MHz   |

| Operating Frequency                   | V <sub>OSC</sub> = open            |                                                    | 675                   |     | 825                     | kHz   |

|                                       | V <sub>OSC</sub> = GND             |                                                    | 450                   |     | 550                     | KIIZ  |

| Maximum Duty Cycle                    |                                    |                                                    | 94                    |     |                         | %     |

| CS Trip Voltage                       | Duty cycle = 75%                   |                                                    | 85                    |     | 115                     | mV    |

| CONTROL INPUT                         |                                    |                                                    |                       |     |                         |       |

| SHDN Logic-Input High Level           |                                    |                                                    | 2.1                   |     |                         | V     |

| SHDN Logic-Input Low Level            |                                    |                                                    |                       |     | 0.8                     | V     |

| BRT, ENA Logic-Input High Level       |                                    |                                                    | 2.1                   |     |                         | V     |

| BRT, ENA Logic-Input Low Level        |                                    |                                                    |                       |     | 0.8                     | V     |

| INPUT LEAKAGE                         |                                    |                                                    |                       |     |                         |       |

| SHDN Leakage Current                  | V <sub>SHDN</sub> = 26V            |                                                    |                       |     | +35                     | μA    |

| CS Leakage Current                    | V <sub>CS</sub> = GND              |                                                    |                       |     | +50                     | μA    |

| OSC Leakage Current                   |                                    |                                                    | -3                    |     | +3                      | μA    |

| BRT, ENA Leakage Current              |                                    |                                                    | -1                    |     | +1                      | μA    |

| FSET, ISET Leakage Current            | FSET = ISET = V <sub>CC</sub>      |                                                    | -1                    |     | +1                      | μA    |

| OV Leakage Current                    |                                    |                                                    | -0.1                  |     | +0.1                    | μA    |

## **Electrical Characteristics (continued)**

(Circuit of Figure 1.  $V_{IN}$  = 12V,  $V_{\overline{SHDN}}$  =  $V_{IN}$ , CCV = 0.1 $\mu$ F,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                      | CONDITIONS                                                 | MIN                   | TYP MAX              | UNITS             |

|--------------------------------|------------------------------------------------------------|-----------------------|----------------------|-------------------|

| LED CURRENT                    |                                                            |                       |                      |                   |

|                                | ISET = V <sub>CC</sub> , BRT = 100%                        | 19.2                  | 20.8                 |                   |

| Full-Scale FB_ Output Current  | $R_{ISET}$ = 80kΩ to GND, BRT = 100%                       | 24.0                  | 26.0                 | mA                |

|                                | $R_{ISET}$ = 133kΩ to GND, BRT = 100%                      | 14.4                  | 15.6                 |                   |

| ISET High-Level Threshold      | Default setting for 20mA full-scale LED current            | V <sub>CC</sub> - 0.4 |                      | V                 |

| ISET Voltage                   |                                                            | 1.12                  | 1.26                 | V                 |

| 20% Output Current             | ISET = V <sub>CC</sub> , BRT = 20%                         | 3.8                   | 4.2                  | mA                |

| Current Regulation Between     | ISET = V <sub>CC</sub> , BRT = 100%                        | -2                    | +2                   | - %               |

| Strings                        | ISET = V <sub>CC</sub> , BRT = 20%                         | -3                    | +3                   | 70                |

|                                | $R_{ISET}$ = 80kΩ to GND, BRT = 100%                       | 280                   | 840                  |                   |

| Minimum FB_ Regulation Voltage | ISET= V <sub>CC</sub> , BRT = 100%                         | 250                   | 760                  | mV                |

|                                | ISET = V <sub>CC</sub> , BRT = 12.5%                       | 140                   | 530                  |                   |

| Maximum FB_ Ripple             | ISET= $V_{CC}$ , COUT = 1 $\mu$ F, OSC = $V_{CC}$ (Note 1) |                       | 200                  | mV <sub>P-P</sub> |

| FB_ On-Resistance              | V <sub>FB</sub> _ = 50mV                                   |                       | 20                   | Ω                 |

| ED Lookees Current             | SHDN = GND, V <sub>FB</sub> = 26V                          |                       | 1                    |                   |

| FB_ Leakage Current            | SHDN = V <sub>IN</sub> , BRT = GND, V <sub>FB</sub> = 15V  |                       | 28                   | μA                |

| BRT Input Frequency            | _                                                          | 100                   | 500                  | Hz                |

| FAULT PROTECTION               |                                                            |                       |                      |                   |

| OV Threshold Voltage           |                                                            | 1.16                  | 1.30                 | V                 |

| FB_ Overvoltage Threshold      |                                                            | V <sub>CC</sub> + 0.2 | V <sub>CC</sub> 1.45 |                   |

| FAULT Shutdown Timer           | V <sub>FB</sub> > 5.6V (typ)                               | 50                    | 80                   | ms                |

| PHASE-LOCKED LOOP              |                                                            |                       |                      |                   |

| FSET High-Level Threshold      | PLL disabled                                               | V <sub>CC</sub> - 0.4 |                      | V                 |

| DDT F                          | $R_{FSET} = 500k\Omega$                                    | 150                   | 250                  | Hz                |

| BRT Frequency Capture Range    | $R_{FSET} = 250k\Omega$                                    | 300                   | 500                  | Hz                |

$\textbf{Note 1:} \ \ \textbf{Specifications are guaranteed by design, not production tested.}$

Note 2: Specifications to -40°C are guaranteed by design, not production tested.

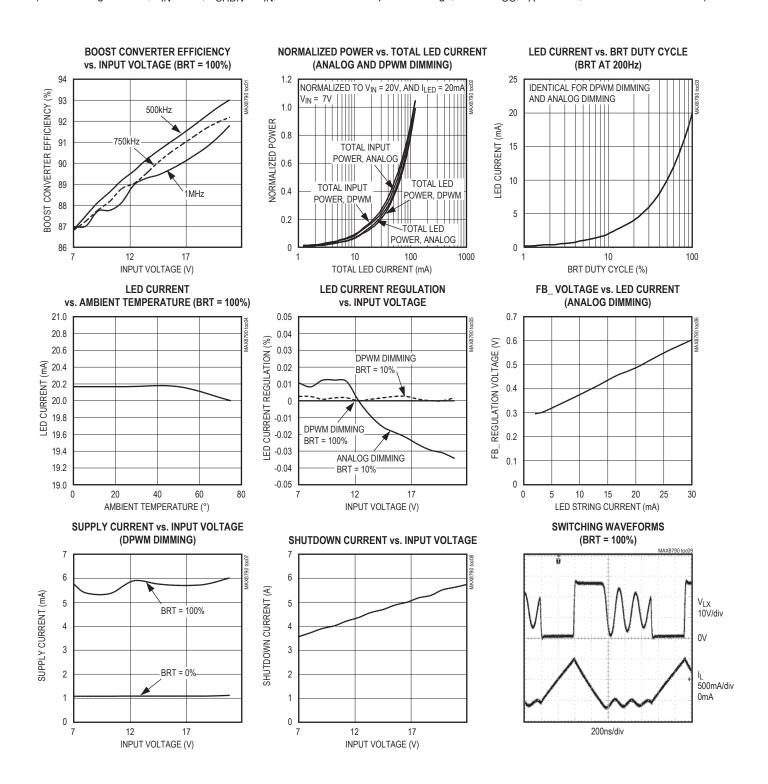

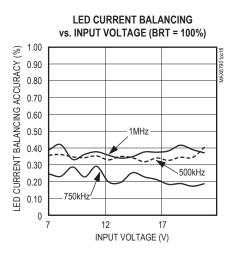

## **Typical Operating Characteristics**

(Circuit configuration 1,  $V_{IN}$  = 12V,  $V_{SHDN}$  =  $V_{IN}$ , LEDs = 8 series x 6 parallel strings, ISET =  $V_{CC}$ ,  $T_A$  = +25°C, unless otherwise noted.)

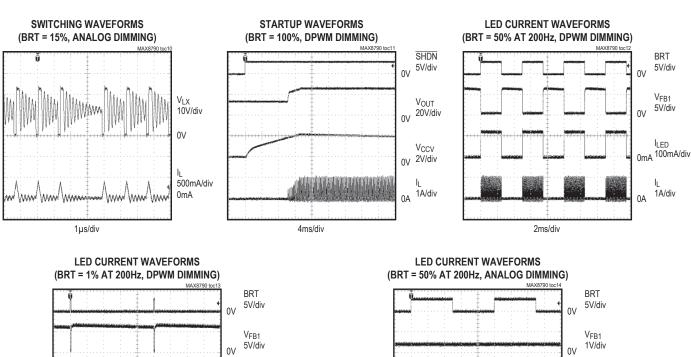

## **Typical Operating Characteristics (continued)**

(Circuit configuration 1,  $V_{IN}$  = 12V,  $V_{SHDN}$  =  $V_{IN}$ , LEDs = 8 series x 6 parallel strings, ISET =  $V_{CC}$ ,  $T_A$  = +25°C, unless otherwise noted.)

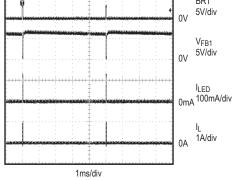

## **Typical Operating Characteristics (continued)**

(Circuit configuration 1,  $V_{IN}$  = 12V,  $V_{SHDN}$  =  $V_{IN}$ , LEDs = 8 series x 6 parallel strings, ISET =  $V_{CC}$ ,  $T_A$  = +25°C, unless otherwise noted.)

## **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | osc  | Oscillator Frequency Selection Pin. Connect OSC to $V_{CC}$ to set the step-up converter's oscillator frequency to 1MHz. Connect OSC to GND to set the frequency to 500kHz. Float OSC to set the frequency to 750kHz.                                                                                                                                                                                              |

| 2   | ENA  | Analog Dimming Enable. ENA sets the PWM control mode. Set ENA LOW to enable direct DPWM dimming. Set ENA HIGH to enable analog dimming. In both modes, the duty cycle of the PWM signal at the BRT input controls the LED current characteristics. See the <i>Dimming Control</i> section for a complete description.                                                                                              |

| 3   | BRT  | Brightness Control Input. The duty cycle of this digital input signal controls the LED current characteristics. The allowable frequency range is 100Hz to 500Hz in analog dimming mode. The duty cycle can be 100% to 1%. The BRT frequency can go above 500Hz in direct DPWM mode as long as the BRT pulse width is greater than 50µs minimum. See the <i>Dimming Control</i> section for a complete description. |

| 4   | SHDN | Shutdown Control Input. The MAX8790 shuts down when \$\overline{SHDN}\$ is less than 0.8V. Pulling \$\overline{SHDN}\$ above 2.1V enables the MAX8790. \$\overline{SHDN}\$ can be connected to the input voltage if desired.                                                                                                                                                                                       |

| 5   | FB1  | LED String 1 Cathode Connection. FB1 is the open-drain output of an internal regulator, which controls current through FB1. FB1 can sink up to 25mA. If unused, connect FB1 to GND.                                                                                                                                                                                                                                |

| 6   | FB2  | LED String 2 Cathode Connection. FB2 is the open-drain output of an internal regulator, which controls current through FB2. FB2 can sink up to 25mA. If unused, connect FB2 to GND.                                                                                                                                                                                                                                |

| 7   | FB3  | LED String 3 Cathode Connection. FB3 is the open-drain output of an internal regulator, which controls current through FB3. FB3 can sink up to 25mA. If unused, connect FB3 to GND.                                                                                                                                                                                                                                |

| 8   | GND  | Ground                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9   | FB4  | LED String 4 Cathode Connection. FB4 is the open-drain output of an internal regulator, which controls current through FB4. FB4 can sink up to 25mA. If unused, connect FB4 to GND.                                                                                                                                                                                                                                |

| 10  | FB5  | LED String 5 Cathode Connection. FB5 is the open-drain output of an internal regulator, which controls current through FB5. FB5 can sink up to 25mA. If unused, connect FB5 to GND.                                                                                                                                                                                                                                |

# **Pin Description (continued)**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | FB6             | LED String 6 Cathode Connection. FB6 is the open-drain output of an internal regulator, which controls current through FB6. FB6 can sink up to 25mA. If unused, connect FB6 to GND.                                                                                                                                                                                                                                                                                                       |

| 12  | CS              | Step-Up Controller Current-Sense Input. Connect the CS input to a ground-referenced sense resistor to measure the current in the external MOSFET switch.                                                                                                                                                                                                                                                                                                                                  |

| 13  | EXT             | External MOSFET Gate-Drive Output                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 14  | OV              | Overvoltage Sense. Connect OV to the center tap of a resistive voltage-divider from V <sub>OUT</sub> to ground. The detection threshold for voltage limiting at OV is 1.23V (typ).                                                                                                                                                                                                                                                                                                        |

| 15  | V <sub>CC</sub> | 5V Linear Regulator Output. $V_{CC}$ provides power to the MAX8790 and is also used to bias the gate driver for the external MOSFET. Bypass $V_{CC}$ to GND with a ceramic capacitor of 1µF or greater. If $V_{IN}$ is less than or equal to 5.5V, connect $V_{CC}$ to IN to the disable the internal LDO and use the external 5V supply to $V_{CC}$ . When $\overline{SHDN}$ is low, the internal linear regulator is disabled.                                                          |

| 16  | IN              | Supply Input. V <sub>IN</sub> biases the internal 5V linear regulator that powers the device. Bypass IN to GND directly at the pin with a 0.1µF or greater ceramic capacitor.                                                                                                                                                                                                                                                                                                             |

|     |                 | Step-Up Converter Compensation Pin. Connect a 0.1µF ceramic capacitor and 1.2-free                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17  | CCV             | $\Omega$ resistor from CCV to GND. When the MAX8790 shuts down, CCV is discharged to 0V through an internal 20k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                        |

| 18  | ISET            | Full-Scale LED Current Adjustment Pin. The resistance from ISET to GND controls the full-scale current in each LED string: $I_{\text{LEDmax}} = 20\text{mA} \times 100\text{k}\Omega/R_{\text{ISET}}$ The acceptable resistance range is $80\text{k}\Omega < R_{\text{ISET}} < 133\text{k}\Omega,$ which corresponds to full-scale LED current of $25\text{mA} > I_{\text{LEDmax}} > 15\text{mA}.$ Connect ISET to $V_{\text{CC}}$ for a default full-scale LED current of $20\text{mA}.$ |

| 19  | FSET            | PLL Free-Running Frequency Control Pin. The resistance from FSET to GND controls the PLL oscillator's free-running frequency, $f_{PLL}$ : $f_{PLL} = 1 / (10 \times R_{FSET} \times 800 pF)$ The capture range is $0.6 \times f_{PLL}$ to $f_{PLL}$ . The acceptable resistance range for FSET is $250 k\Omega < R_{FSET} < 754 k\Omega$ , which corresponds to a frequency range of $500 Hz > f_{PLL} > 166 Hz$ . The resulting capture frequency range is $100 Hz$ to $500 Hz$ .        |

| 20  | CPLL            | Phase-Locked Loop-Compensation Capacitor Pin. The capacitance at CPLL compensates the PLL loop response. Connect a 0.1µF ceramic capacitor from CPLL to GND.                                                                                                                                                                                                                                                                                                                              |

| EP  | EP              | Exposed Backside Pad. Solder to the circuit board ground plane with sufficient copper connection to ensure low thermal resistance. See the <i>PCB Layout Guidelines</i> section.                                                                                                                                                                                                                                                                                                          |

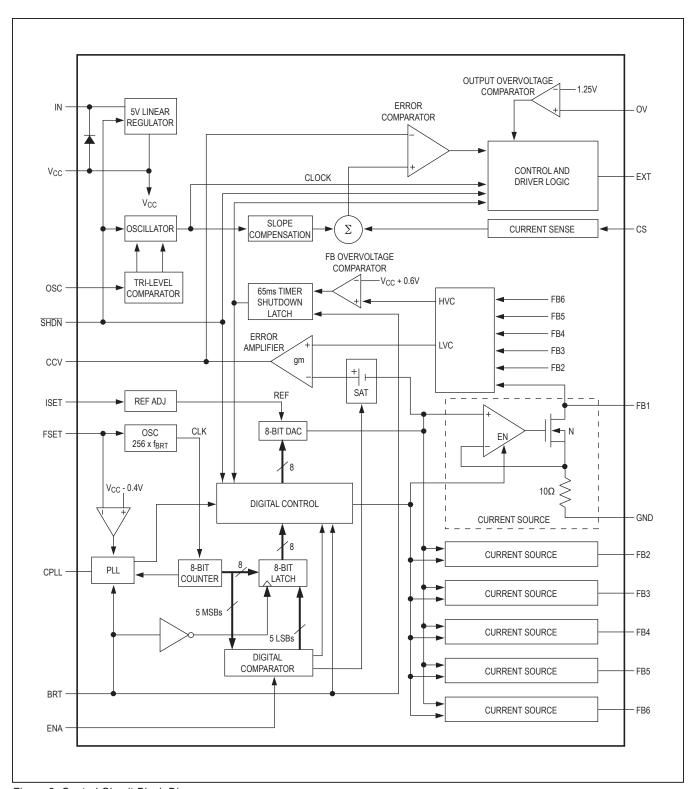

## **Detailed Description**

The MAX8790 is a high-efficiency driver for arrays of white LEDs. It contains a fixed-frequency, current-mode, PWM step-up controller, 5V linear regulator, dimming control circuit, and six regulated current sources (see Figure 2). When enabled, the step-up controller boosts the output voltage to provide sufficient headroom for the current sources to regulate their respective string currents. The MAX8790 features selectable switching frequency (500kHz, 750kHz, or 1MHz), which allows trade-offs between external component size and operating efficiency. The control architecture automatically skips pulses at light loads to improve efficiency and prevents overcharging the output capacitor.

A PWM logic input signal, BRT, controls the LED brightness. The MAX8790 supports both analog and digital control of the LED current, and achieves 100:1 dimming range. The MAX8790's dimming control circuit consists of a PLL, a digital comparator, and a DAC. In direct DPWM mode, the step-up controller and current source are directly turned on and off by the PWM signal. In analog

dimming mode, an internal PLL, digital comparator, and DAC circuit translate the PWM signal into an analog signal that linearly controls the LED current, down to a PWM duty factor of 12.5%.

The MAX8790 has multiple features to protect the controller from fault conditions. Separate feedback loops limit the output voltage if one or more LEDs fail open or short. During operation, if one of the feedback string voltages exceeds the  $V_{CC}$  to 0.6V (typ) protection threshold, the controller shuts down and latches off after an internal timer expires. The controller features cycle-by-cycle current limit to provide consistent operation and soft-start capability. A thermal-shutdown circuit provides another level of protection.

The MAX8790 includes a 5V linear regulator that provides the internal bias and gate drive for the step-up controller. When an external 5V is available, the internal LDO can be overdriven to decrease power dissipation. Otherwise, connect the IN pin to an input greater than 5.5V. The internal LDO is disabled when  $\overline{\text{SHDN}}$  is low.

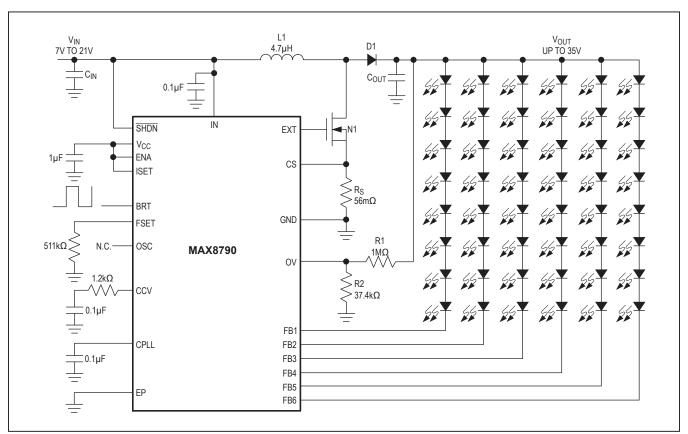

Figure 1. Typical Operating Circuit

Figure 2. Control Circuit Block Diagram

## **Fixed-Frequency Step-Up Controller**

The MAX8790's fixed-frequency, current-mode, step-up controller automatically chooses the lowest active FB\_voltage to regulate the feedback voltage. Specifically, the difference between the lowest FB\_voltage and the current source-control signal plus an offset ( $V_{SAT}$ ) is integrated at the CCV output. The resulting error signal is compared to the external switch current plus slope compensation to terminate the switch on-time. As the load changes, the error amplifier sources or sinks current to the CCV output to adjust the required peak inductor current. The slope-compensation signal is added to the current-sense signal to improve stability at high duty cycles.

At light loads, the MAX8790 automatically skips pulses to improve efficiency and prevent overcharging the output capacitor. In SKIP mode, the inductor current ramps up for a minimum on-time of approximately 150ns, then discharges the stored energy to the output. The switch remains off until another pulse is needed to boost the output voltage.

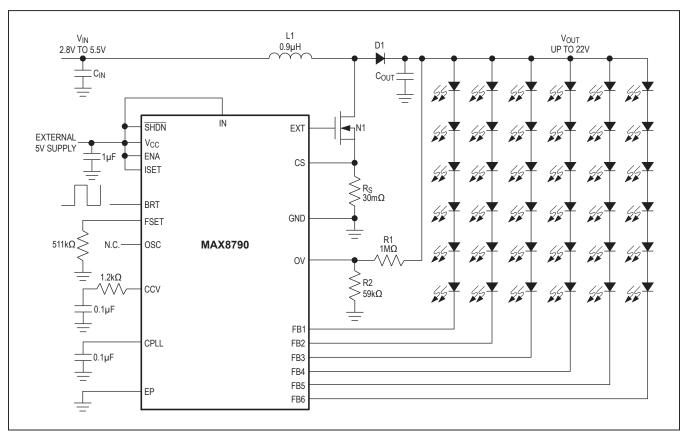

### Internal 5V Linear Regulator V<sub>CC</sub> and UVLO

The MAX8790 includes an internal low-dropout linear regulator ( $V_{CC}$ ). When  $V_{IN}$  is higher than 5.5V and  $\overline{SHDN}$  is high, this linear regulator generates a 5V supply to power an internal PWM controller, control logic, and MOSFET driver. This linear regulator can deliver at least 10mA of total additional load current. If  $V_{IN}$  is less than or equal to 5.5V,  $V_{CC}$  and IN can be connected together and powered from an external 5V supply. There is an internal diode from  $V_{CC}$  to IN, so  $V_{IN}$  must be greater than  $V_{CC}$  (see Figure 2).

The MAX8790 includes UVLO protection. The controller is disabled until  $V_{CC}$  exceeds the UVLO threshold of 4.25V (typ). Hysteresis on UVLO is approximately 20mV.

The  $V_{CC}$  pin should be bypassed to GND with a 1 $\mu F$  or greater ceramic capacitor.

Figure 3. Low-Input-Voltage Application Circuit

### Startup

At startup, the MAX8790 checks each FB\_ pin to determine if the respective current string is enabled. Each FB\_ pin is internally pulled up with a 10 $\mu$ A current source. If an FB\_ pin is connected to GND, the corresponding string current source is disabled. This feedback scan takes approximately 264 $\mu$ s, after which the step-up converter begins switching.

#### **Shutdown**

When the SHDN pin is less than 0.8V, the MAX8790 shuts down the internal LDO, the reference, current sources, and all control circuitry. The resulting supply current is less than  $10\mu A$ . While the n-channel MOSFET is turned off, the step-up regulator's output is connected to IN through the external inductor and rectifier diode.

## **Frequency Selection**

A tri-level OSC input sets the internal oscillator frequency for the step-up converter, as shown in Table 1. High-frequency (1MHz) operation optimizes the regulator for the smallest component size, at the expense of efficiency due to increased switching losses. Low-frequency (500kHz) operation offers the best overall efficiency, but requires larger components and PCB area.

**Table 1. Frequency Selection**

| osc             | SWITCHING FREQUENCY (kHz) |  |  |  |

|-----------------|---------------------------|--|--|--|

| GND             | 500                       |  |  |  |

| Open            | 750                       |  |  |  |

| V <sub>CC</sub> | 1000                      |  |  |  |

### **Overvoltage Protection**

To protect the step-up converter when the load is open, or the output voltage becomes excessive for any reason, the MAX8790 features a dedicated overvoltage feedback input (OV). The OV pin is connected to the center tap of a resistive voltage-divider from the highvoltage output (see Figure 1). When the MAX8790 is powered up, if none of the LED strings on FB1–FB6 are connected to the step-up converter output, the step-up converter regulates the output voltage to  $V_{OUT}$  = 1.23V(1 + R1 / R2). When  $V_{OV}$  exceeds 1.23V, a comparator turns off N1. The step-up converter switch is reenabled after the output voltage drops below the protection threshold.

### **LED Current Sources**

Maintaining uniform LED brightness and dimming capability are critical for LCD backlight applications. The MAX8790 is equipped with a bank of six matched current sources. These specialized current sources are accurate

to within  $\pm 1.5\%$  and can be switched on and off within 10µs, enabling PWM frequencies of up to 2kHz. All LED full-scale currents are identical and are set through the ISET pin (15mA <  $I_{I,ED}$  < 25mA).

The minimum voltage drop across each current source is approximately 450mV at 20mA. The low voltage drop helps reduce dissipation while maintaining sufficient compliance to control the LED current within the required tolerances.

The LED current sources can be disabled by grounding the respective FB\_ pin at startup. When the IC is powered up, the controller scans settings for all FB\_ pins. If an FB\_ pin is not grounded, an internal circuit pulls this pin high, and the controller enables the corresponding current source to regulate the string current. If the FB\_ pin is grounded, the controller disables the corresponding current regulator. The current regulator cannot be disabled by grounding any of the FB\_ pins after the IC is powered up.

All FB\_ pins in use are measured and the highest signal (HVC) and the lowest signal (LVC) are extracted for two feedback loops. HVC is used to identify excessive dissipation across the current-source inputs. When HVC is greater than  $V_{CC}+0.6V$  (typ) for greater than 65ms (see the *Current-Source Fault Protection* section), a fault latch is set and the MAX8790 is shut down. The LDO output is not affected by the fault latch. LVC is fed into the step-up converter's error amplifier to regulate the step-up converter's output voltage.

### **Current-Source Fault Protection**

The LED current sources are protected against string open, short, and gross mismatch faults, using overvoltage detection circuitry on each FB\_ pin. If any of these three fault conditions persists for a preset duration, the MAX8790 is latched off. The duration of the fault time depends on the dimming mode and the duty cycle of the BRT input ( $D_{BRT}$ ). In the DPWM mode, the timeout interval is:

tTIMEOUT DPWM = 65ms/DBRT

In analog dimming mode, the fault time is fixed at 65ms for DBRT greater than 12.5%. When DBRT is less than 12.5%, the timeout interval is:

$t_{TIMEOUT\_ANALOG} = 8.125 ms/D_{BRT}$

The fault latch can be cleared by cycling the power or toggling the shutdown pin  $\overline{\text{SHDN}}$ .

### **Open-Current Source Protection**

The MAX8790 step-up converter output voltage is regulated according to the minimum value of the enable FB\_voltages. If an individual LED string is open, the respective FB\_ is pulled down to near ground. In this situation, the step-up converter output voltage increases but is

clamped to a level set with the OV feedback input. When this elevated output voltage is applied to the undamaged strings, excessive voltage drop develops across the FB pins. If the resulting HVC signal exceeds V<sub>CC</sub> + 0.6V for greater than 65ms, the fault latch is triggered to protect the circuit.

### **LED-Short and String Mismatch Protection**

Normally, white LEDs have variations in forward-voltage drop of 3.1V to 3.6V. The MAX8790 can tolerate slight mismatches between LED strings. When the sum of the LED forward voltages creates a mismatch in the strings so the HVC signal exceeds  $V_{CC}$  + 0.6V for greater than 65ms, the fault latch is triggered in much the same way as the circuit responds to open string faults. Similar protection is activated when an LED is shorted.

The larger the number of series-connected LEDs (N), the smaller the tolerable mismatch between LEDs:

$$\sum_{N} \text{Error} < V_{CC} + 0.6V - V_{SAT}$$

$$V_{SAT} \approx 450 \text{mV} \text{ and } V_{CC} = 5V$$

$$\sum_{N} \text{Error} < 5.150V$$

Average Error Per LED =  $\frac{5.150V}{N}$

For N = 8, the average error per LED = 644mV.

For N = 10, the average error per LED = 510mV.

The larger the total mismatch, the larger the voltage drop required across each current source to correct for the error, and therefore the larger the dissipation within the MAX8790.

## **Dimming Control**

The MAX8790 features both analog and digital dimming control. Analog dimming can provide potentially higher converter efficiency because of low voltage drop across each WLED when the current is low. Digital dimming (DPWM) provides less WLED color distortion since the WLED current is held at full scale when the WLED is on.

The MAX8790's dimming control circuit consists of a PLL, a digital comparator, and a DAC. The controller provides 100:1 dimming range through either analog or digital control methods. Both methods translate the duty cycle of the BRT input into a control signal for the LED current sources. In analog dimming mode, the current-source outputs are DC and the BRT duty cycle (12.5% < D<sub>BRT</sub> < 100%) modulates the amplitude of the currents. For DBRT < 12.5%, the LED current is digitally modulated to reduce the average LED current down to 1% of full scale. The PLL detects the BRT frequency and phase, and adjusts the current-source amplitude and duty cycle synchronously (see Figure 4).

Figure 4. LED Current Control Using Analog Dimming Mode

In digital dimming mode, the step-up controller and current source are directly turned on and off by the PWM signal. The current pulse magnitude, or full-scale current, is set by ISET and is independent of PWM duty factor. The current-source outputs are PWM signals synchronized to the BRT input signal (see Figure 5).

The full-scale current in both methods is specified by resistance from the ISET pin to ground:

$$I_{LEDmax} = \frac{20mA \times 100k\Omega}{R_{ISET}}$$

The acceptable resistance range is  $80 k\Omega$  <  $R_{ISET}$  <  $133 k\Omega$ , which corresponds to full-scale LED current of 25 mA >  $I_{LEDmax}$  > 15 mA. Connect ISET to  $V_{CC}$  for a default full-scale LED current of 20 mA. When ENA is high, the analog dimming is enabled, when ENA is low, digital dimming is enabled.

When the current-source output is pulse-width modulated, current-source turn-on is synchronized with the BRT signal. Synchronization and low jitter in the PWM signals help

reduce flicker noise in the display. The current through each FB\_ pin is controlled only during the step-up converter's on-time. During the converter's off-time, the current sources are turned off. The output voltage does not discharge and stays high. Each FB\_ pin can withstand 28V, which is the pin's maximum rated voltage.

Table 2 summarizes the characteristics of both analog and digital dimming methods.

A PLL translates the duty cycle of the BRT input into a reference for the MAX8790's current sources. A resistor from the FSET pin to ground controls the PLL's freerunning frequency:

$$f_{PLL} = \frac{1}{10 \times R_{FSFT} \times 800pF}$$

The PLL's loop filter bandwidth is set with a capacitor from the CPLL pin to ground. This filter integrates the phase difference between the BRT input signal and the PLL oscillator. The filter bandwidth determines the PLL's dynamic response to frequency changes in the BRT signal. For

Figure 5. LED Current Control Using DPWM Dimming Mode

## **Table 2. Dimming Mode**

| MODE          | ENA    | PLL FREQUENCY                                            | CPLL  | DESCRIPTION                                                                                                                                 |

|---------------|--------|----------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Analog + DPWM | > 2.1V | 250kΩ < R <sub>FSET</sub> < 754kΩ                        | 0.1µF | Analog dimming from 100% to 12.5% brightness. From 12.5% to 1% brightness, DPWM dimming is employed. BRT frequency range is 100Hz to 500Hz. |

| Direct DPWM   | < 0.8V | V <sub>FSET</sub> > V <sub>CC</sub> - 0.4V, disables PLL | OPEN  | Direct dimming by BRT signal. BRT frequency can be 100Hz to 2kHz; 50µs minimum BRT on-time limits the minimum brightness.                   |

most applications, a  $0.1\mu F$  capacitor is adequate for oscillator frequencies in the 166Hz <  $f_{PLL}$  < 500Hz range. The PLL frequency capture window is  $0.6 \times f_{PLL}$  to  $f_{PLL}$ .

The PLL is disabled in DPWM mode; consequently, the BRT frequency is not limited by  $f_{PLL}$ . The maximum BRT frequency is determined by the minimum BRT ontime of 50µs and the minimum acceptable dimming factor. If a 1% dimming factor is needed, the maximum BRT frequency is 200Hz. If a 10% dimming factor is acceptable, the maximum BRT frequency is 2kHz.

In analog dimming mode, load-current transients can occur when the BRT duty cycle abruptly changes on the fly. Large regulation transients induce a flash on the LED load that is observable with the naked eye and should therefore be avoided. Such annoying flashes can be eliminated by dynamically changing the ENA pin setting. When a capacitor is connected to the CPLL pin and the ENA pin is grounded, the PLL continues to run but does not affect the dimming. When fast PLL lockup transitions are required, the ENA pin can be momentarily pulled to ground; after the PLL is locked up, ENA can be pulled high to reenable PLL in dimming control.

**Table 3. Component List**

| CIRCUIT                  | FIGURE 1                                                                | FIGURE 1                                                                                                           | FIGURE 1                                                                         | FIGURE 3                                                                |

|--------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Switching<br>Frequency   | 1MHz                                                                    | 750kHz                                                                                                             | 500kHz                                                                           | 750kHz                                                                  |

| White LED                | 3.2V (typ), 3.5V (max) at<br>20mA<br>Nichia NSSW008C                    | 3.2V (typ), 3.5V (max) at<br>20mA<br>Nichia NSSW008C                                                               | 3.2V (typ), 3.5V (max) at<br>20mA<br>Nichia NSSW008C                             | 3.2V (typ), 3.5V (max) at<br>20mA<br>Nichia NSSW008C                    |

| Number of<br>White LEDs  | 6 series x 6 parallel,<br>20mA (max)                                    | 8 series x 6 parallel,<br>20mA (max)                                                                               | 10 series x 6 parallel, 25mA (max)                                               | 6 series x 6 parallel,<br>20mA (max)                                    |

| Input Voltage            | 4.5V to 5.5V, V <sub>CC</sub> = IN                                      | 7V to 21V                                                                                                          | 7V to 21V                                                                        | 2.8V to 5.5V, V <sub>CC</sub> = 5V                                      |

| Inductor L1              | 2.2µH, 2.5A power inductor<br>Sumida CDRH5D16-2R2                       | 4.7µH, 2.05A power inductor Sumida CDRH5D16-4R7                                                                    | 4.7μH, 3.6A power inductor<br>Sumida CDRH8D28-4R7                                | 0.9µH, 4.7A power inductor<br>Sumida CDRH5D16-0R9                       |

| Input<br>Capacitors      | 10µF ±10%, 10V X5R<br>ceramic capacitor (1206)<br>Murata GRM31MR61A106K | 10µF ±10%, 25V X5R<br>ceramic capacitor (1206)<br>Murata<br>GRM31CR61E106KA                                        | 10μF ±10%, 25V X5R<br>ceramic capacitor (1206)<br>Murata<br>GRM31CR61E106KA      | 10µF ±10%, 10V X5R<br>ceramic capacitor (1206)<br>Murata GRM31MR61A106K |

| COUT Output<br>Capacitor | 2.2µF ±10%, 50V X7R<br>ceramic capacitor (1x)<br>Murata GRM31CR71H225K  | 2.2µF ±10%, 50V X7R<br>ceramic capacitor (1206)<br>(1x)<br>Murata GRM31CR71H225K                                   | 4.7µF ±10%, 50V X7R<br>ceramic capacitor (1210)<br>(1x)<br>Murata GRM32ER71H475K | 2.2µF ±10%, 50V X7R<br>ceramic capacitor (1x)<br>Murata GRM31CR71H225K  |

| MOSFET N1                | 30V, 3A n-channel MOSFET<br>(6-pin SC70)<br>Vishay Si1402DH             | 60V, 2.8A n-channel<br>MOSFET (6-pin TSOP)<br>Fairchild Semiconductor<br>FDC5612<br>Sanyo Semiconductor<br>CPH6424 | 60V, 6A n-channel<br>MOSFET (PowerPAK 1212-<br>8)<br>Vishay Si7308DN             | 30V, 4.9A n-channel<br>MOSFET (6-pin TSOP)<br>Vishay Si3456BDV          |

| Diode<br>Rectifier D1    | 2A, 30V Schottky diode<br>Nihon EC21QS03L                               | 2A, 40V Schottky diode<br>Toshiba CMS11<br>Nihon EC21QS04                                                          | 3A, 60V Schottky diode<br>Nihon EC31QS06                                         | 3A, 30V Schottky diode<br>Nihon EC31QS03L                               |

| Sense<br>Resistor        | 50mΩ ±1%, 1/2W<br>IRC LRC-LRF-1206LF-01-<br>R050-F                      | 56mΩ ±1%, 1/2W<br>IRC LRC-LRF-1206LF-01-<br>R056-F                                                                 | 40mΩ ±1%, 1/2W<br>IRC LRC-LRF-1206LF-01-<br>R040-F                               | 30mΩ ±1%, 1/2W<br>IRC LRC-LRF-1206LF-01-<br>R030-F                      |

**Table 4. Component Suppliers**

| SUPPLIER | PHONE        | WEBSITE              |

|----------|--------------|----------------------|

| Murata   | 770-436-1300 | www.murata.com       |

| Nichia   | 248-352-6575 | www.nichia.com       |

| Sumida   | 847-545-6700 | www.sumida.com       |

| Toshiba  | 949-455-2000 | www.toshiba.com/taec |

| Vishay   | 203-268-6261 | www.vishay.com       |

### **Thermal Shutdown**

The MAX8790 includes a thermal-protection circuit. When the local IC temperature exceeds +170°C (typ), the controller and current sources shut down and do not restart until the die temperature drops by 15°C.

## **Design Procedure**

All MAX8790 designs should be prototyped and tested prior to production. Table 3 provides a list of power components for the typical applications circuit. Table 4 lists component suppliers. External component value choice is primarily dictated by the output voltage and the maximum load current, as well as maximum and minimum input voltages. Begin by selecting an inductor value. Once L is known, choose the diode and capacitors.

### **Inductor Selection**

The inductance, peak current rating, series resistance, and physical size should all be considered when selecting an inductor. These factors affect the converter's operating mode, efficiency, maximum output load capability, transient response time, output voltage ripple, and cost.

The maximum output current, input voltage, output voltage, and switching frequency determine the inductor value. Very high inductance minimizes the current ripple, and therefore reduces the peak current, which decreases core losses in the inductor and I2R losses in the entire power path. However, large inductor values also require more energy storage and more turns of wire, which increases physical size and I2R copper losses in the inductor. Low inductor values decrease the physical size, but increase the current ripple and peak current. Finding the best inductor involves the compromises among circuit efficiency, inductor size, and cost.

When choosing an inductor, the first step is to determine the operating mode: continuous conduction mode (CCM) or discontinuous conduction mode (DCM). The MAX8790 has a fixed internal slope compensation, which requires a minimum inductor value. When CCM mode is chosen, the ripple current and the peak current of the inductor can be minimized. If a small-size inductor is required, DCM mode can be chosen. In DCM mode, the inductor value and size can be minimized but the inductor ripple current and peak current are higher than those in CCM. The controller can be stable, independent of the internal slope compensation mode, but there is a maximum inductor value requirement to ensure the DCM operating mode.

The equations used here include a constant LIR, which is the ratio of the inductor peak-to-peak ripple current to the average DC inductor current at the full-load current. The controller operates in DCM mode when LIR is higher than 2.0, and it switches to CCM mode when LIR is lower than 2.0. The best trade-off between inductor size and converter efficiency for step-up regulators generally has an LIR between 0.3 and 0.5. However, depending on the AC characteristics of the inductor core material and ratio of inductor resistance to other power-path resistances, the best LIR can shift up or down. If the inductor resistance is relatively high, more ripple can be accepted to reduce the number of required turns and increase the wire diameter. If the inductor resistance is relatively low, increasing inductance to lower the peak current can reduce losses throughout the power path. If extremely thin high-resistance inductors are used, as is common for LCD panel applications, LIR higher than 2.0 can be chosen for DCM operating mode.

Once a physical inductor is chosen, higher and lower values of the inductor should be evaluated for efficiency improvements in typical operating regions. The detail design procedure can be described as follows:

Calculate the approximate inductor value using the typical input voltage ( $V_{IN}$ ), the maximum output current ( $I_{OUT(MAX)}$ ), the expected efficiency ( $\eta_{TYP}$ ) taken from an appropriate curve in the *Typical Operating Characteristics*, and an estimate of LIR based on the above discussion:

$$L = \left(\frac{V_{IN\_MIN}}{V_{OUT}}\right)^2 \left(\frac{V_{OUT} - V_{IN\_MIN}}{I_{OUT(MAX)} \times f_{OSC}}\right) \left(\frac{\eta_{TYP}}{LIR}\right)$$

The MAX8790 has a minimum inductor value limitation for stable operation in CCM mode at low input voltage because of the internal fixed slope compensation. The minimum inductor value for stability is calculated by the following equation:

$$L_{CCM(MIN)} = \frac{\left(V_{OUT(MAX)} + V_{DIODE} - 2 \times V_{IN(MIN)}\right) \times R_{S}}{51 \text{mV} \times f_{OSC(MIN)}}$$

where 51mV is a scale factor based on slope compensation, and R<sub>S</sub> is the current-sense resistor. To determine the minimum inductor value, the RS can be temporarily calculated using the following equation:

$$R_{S\_TMP} = \frac{100mV}{1.2 \times I_{IN(DC, MAX)}}$$

where 100mV is the current-limit sense voltage.

The minimum inductor value should be recalculated after the Rs is determined (see the Sense-Resistor Selection section).

Choose an available inductor value from an appropriate inductor family. Calculate the maximum DC input current at the minimum input voltage V<sub>IN(MIN)</sub>, using conservation of energy and the expected efficiency at that operating point  $(\eta_{\mbox{\scriptsize MIN}})$  taken from an appropriate curve in the Typical Operating Characteristics:

$$I_{IN(DC, MAX)} = \frac{I_{OUT(MAX)} \times V_{OUT}}{V_{IN(MIN)} \times \eta_{MIN}}$$

Calculate the ripple current at that operating point and the peak current required for the inductor:

$$I_{RIPPLE} = \frac{V_{IN(MIN)} \times \left(V_{OUT(MAX)} - V_{IN(MIN)}\right)}{L \times V_{OUT(MAX)} \times f_{OSC}}$$

$$I_{PEAK} = I_{IN(DC, MAX)} + \frac{I_{RIPPLE}}{2}$$

When DCM operating mode is chosen to minimize the inductor value, the calculations are different from that in the above CCM mode. The maximum inductor value for DCM mode is calculated by the following equation:

$$\begin{split} L_{DCM(MAX)} = & \left(1 - \frac{V_{IN(MIN)}}{V_{OUT(MAX)} + V_{DIODE}}\right) \times \\ & \frac{V_{IN(MIN)}^2 \times \eta}{2 \times f_{OSC(MAX)} \times V_{OUT(MAX)} \times I_{OUT(MAX)}} \end{split}$$

The peak inductor current in DCM mode is calculated using the following equation:

$$I_{PEAK} = \sqrt{\frac{I_{OUT(max)} \times 2 \times V_{OUT(MAX)} \times \left(V_{OUT(MAX)} + V_{DIODE} - V_{IN(MIN)}\right)}{L \times f_{OSC(MIN)} \times \eta \times \left(V_{OUT(MAX)} + V_{DIODE}\right)}}$$

The inductor's saturation current rating should exceed IPFAK and the inductor's DC current rating should exceed I<sub>IN(DC,MAX)</sub>. For good efficiency, choose an inductor with less than  $0.1\Omega$  series resistance.

Considering the typical operating circuit, the maximum load current (IOUT(MAX)) is 120mA with a 28.72V output and a minimal input voltage of 7V. Choosing a DCM operating mode and estimating efficiency of 90% at this operating point:

$$\begin{split} L_{DCM(MAX)} = & \left(1 - \frac{7V}{28.72V + 0.4V}\right) \times \\ & \frac{(7V)^2 \times 0.9}{2 \times 0.825 \text{MHz} \times 28.72V \times 120 \text{mA}} = 5.8 \mu \text{H} \end{split}$$

An inductance less than LDCM(MAX) is required, so a 4.7µH inductor is chosen. The peak inductor current at minimum input voltage is calculated as follows:

$$I_{PEAK} = \sqrt{\frac{120mA \times 2 \times 28.72V \times \left(28.72V + 0.4V - 7V\right)}{4.7\mu H \times 0.675MHz \times 0.9 \times \left(28.72V + 0.4V\right)}} = 1.35A$$

#### **Sense-Resistor Selection**

The detected signal is fed into the step-up converter control compensation loop through the CS pin.

The MAX8790's current-mode step-up converter senses the switch current from CS to GND with an external resistor, R<sub>S</sub>. The current-limit sense voltage is a fixed 100mV. The required resistance is calculated based upon the peak inductor current at the end of the switch on-time:

$$R_S < \frac{V_{CS\_EC} + 25.6mV \times \left(0.75 - D_{MAX}\right)}{I_{PEAK}}$$

where 25.6mV is a scale factor from slope compensation, V<sub>CS</sub> <sub>FC</sub> is the current-sense voltage listed in the Electrical Characteristics table (85mV), and the D<sub>MAX</sub> is the maximum duty cycle at minimum input voltage and maximum output voltage. In DCM operating mode, it is calculated by the following equation:

$$D_{MAX} = \frac{L \times I_{LIM} \times f_{OSC}}{V_{IN(MIN)}}$$

For the typical operating circuit as Figure 1:

$$D_{MAX} = \frac{4.7 \mu H \times 1.35 A \times 0.75 MHz}{7 V} = 0.68$$

$$R_S < \frac{85mV + 25.6mV \times \left(0.75 - 0.68\right)}{1.35A} = 64m\Omega$$

Again,  $R_{\mbox{\scriptsize S}}$  is calculated as a maximum, so a  $56m\Omega$  current-sense resistor is chosen.

### **Output Capacitor Selection**

The total output voltage ripple has two components: the capacitive ripple caused by the charging and discharging on the output capacitor, and the ohmic ripple due to the capacitor's equivalent series resistance (ESR):

$$\begin{split} &V_{RIPPLE} = V_{RIPPLE(C)} + V_{RIPPLE(ESR)} \\ &V_{RIPPLE(C)} \approx \frac{I_{OUT(MAX)}}{C_{OUT}} \Bigg( \frac{V_{OUT(MAX)} - V_{IN(MIN)}}{V_{OUT(MAX)} f_{OSC}} \Bigg) \end{split}$$

and:

$$V_{RIPPLE(ESR)} \approx I_{PEAK}R_{ESR(COUT)}$$

where I<sub>PEAK</sub> is the peak inductor current (see the *Inductor Selection* section).

The output voltage-ripple voltage should be low enough for the FB\_ current-source regulation. The ripple voltage should be less than  $200\text{mV}_{P-P}$ . For ceramic capacitors, the output-voltage ripple is typically dominated by  $V_{RIPPLE(C)}$ . The voltage rating and temperature characteristics of the output capacitor must also be considered.

### **External MOSFET Selection**

The MAX8790's step-up converter uses an external MOSFET to enable applications with scalable output voltage and output power. The boost switching architecture is simple and ensures that the controller is never exposed to high voltage. Only the external MOSFET, diode, and inductor are exposed to the output voltage plus one Schottky diode forward voltage:

$$V_{BV} = N \times V_{F\_LED} + V_{F\_SCHOTTKY} + V_{FB\_}$$

The MOSFET's breakdown ratings should be higher than  $V_{BV}$  with sufficient margin to ensure long-term reliability. A conservative rule of thumb, a minimum 30% margin would be recommended for MOSFET breakdown voltage. The external MOSFET should have a current rating of no less than the  $I_{PEAK}$  derived from the *Inductor Selection* section. To improve efficiency, choose a MOSFET with low  $R_{DS(ON)}$ . The MAX8790's gate-drive linear regulator can provide 10mA. Select the external MOSFET with a total

gate charge so the average current to drive the MOSFET at maximum switching frequency is less than 10mA:

$$Q_{g(MAX)} \times f_{OSC} < 10mA$$

For example, the Si3458DV is specified with 16nC of max total gate charge at Vg = 10V. For 5V of gate drive, the required gate charge is 8nC, which equates to 8mA at 1MHz.

The MOSFET conduction loss or resistive loss is caused by the MOSFET's on-resistance ( $R_{DS(ON)}$ ). This power loss can be estimated as:

$$PD_{RES(MAX)} = \frac{R_{DS(ON)} \times L \times f_{OSC} \times I_{PEAK}^{3}}{3 \times V_{IN(MIN)}}$$

For the above Si3458DV, the estimated conduction loss is:

$$PD_{RES(MAX)} = \frac{0.1\Omega \times 4.7 \mu H \times 750 k Hz \times 1.35 A^{3}}{3 \times 7 V} = 0.04 W$$

The approximate maximum switching loss can be calculated as:

$$PD_{SW(MAX)} = \frac{t_{turn-off} \times I_{PEAK} \times V_{OUT} \times f_{OSC}}{2}$$

For the above Si3458DV, the approximate switching loss is:

$$PD_{SW(MAX)} = \frac{10ns \times 1.35A \times 28.72V \times 750kHz}{2} = 0.145W$$

### **Rectifier Diode Selection**

The MAX8790's high switching frequency demands a high-speed rectifier. Schottky diodes are recommended for most applications because of their fast recovery time and low forward voltage. The diode should be rated to handle the output voltage and the peak switch current. Make sure that the diode's peak current rating is at least IPEAK calculated in the Inductor Selection section and that its breakdown voltage exceeds the output voltage.

## **Setting the Overvoltage Protection Limit**

The OV protection circuit should ensure the circuit safe operation; therefore, the controller should limit the output voltage within the ratings of all MOSFET, diode, and output capacitor components, while providing sufficient output voltage for LED current regulation. The OV pin is connected to the center tap of a resistive voltagedivider (R1 and R2 in Figure 1) from the high-voltage output. When the controller detects the OV pin voltage reaching the threshold  $V_{\rm OV}$  TH, typically 1.23V, OV protection is

activated. Hence, the step-up converter output overvoltage protection point is:

$$V_{OUT(OVP)} = V_{OV\_TH} \times (1 + \frac{R1}{R2})$$

In Figure 1, the output OVP voltage is set to:

$$V_{OUT(OVP)} = 1.23 \text{V} \times (1 + \frac{1 \text{ M}\Omega}{37.4 \text{k}\Omega}) = 34.1 \text{V}$$

## **Input Capacitor Selection**

The input capacitor ( $C_{IN}$ ) filters the current peaks drawn from the input supply and reduces noise injection into the IC. A  $10\mu F$  ceramic capacitor is used in the typical operating circuit (Figure 1) because of the high source impedance seen in typical lab setups. Actual applications usually have much lower source impedance since the step-up regulator often runs directly from the output of another regulated supply. In some applications,  $C_{IN}$  can be reduced below the values used in the typical operating circuit. Ensure a low noise supply at IN by using adequate  $C_{IN}$ . Alternatively, greater voltage variation can be tolerated on  $C_{IN}$  if IN is decoupled from  $C_{IN}$  using an RC lowpass filter.

Select  $C_{IN}$ 's RMS ripple current rating to ensure that its thermal rise is less than approximately 10 $^{\circ}$ C:

$$I_{RMS} = \frac{dI_L}{2 \times \sqrt{3}}$$

#### **LED Selection and Bias**

The series/parallel configuration of the LED load and the full-scale bias current have a significant effect on regulator performance. LED characteristics vary significantly from manufacturer to manufacturer. Consult the respective LED data sheets to determine the range of output voltages for a given brightness and LED current. In general, brightness increases as a function of bias current. This suggests that the number of LEDs could be decreased if higher bias current is chosen; however, high current increases LED temperature and reduces operating life. Improvements in LED technology are resulting in devices with lower forward voltage while increasing the bias current and light output.