### **General Description**

The MAX8971 is a compact, high-frequency, high-efficiency switch-mode charger for a one-cell lithium-ion (Li+) battery. It delivers up to 1.55A of current to the battery from inputs up to 7.5V and withstands transient inputs up to 22V. The 4MHz switch-mode charger is ideally suited for small portable devices, such as Bluetooth® headsets, AR/VR glasses, and other lithium-ion powered accessories. It minimizes component size and heat.

Battery-protection features include: low-voltage prequalification, charge fault timer, die temperature monitoring, and battery temperature monitoring. The battery temperature monitoring adjusts the charge current and termination voltage for safe use of secondary lithium-ion batteries.

The IC accepts either a general DC input or USB. It has programmable automatic input-current limiting to protect upstream charging sources such as USB.

Charge parameters are easily adjustable through an I<sup>2</sup>C interface. Charge is terminated based on user-selectable minimum current level. Charge status is provided to the application processor through an interrupt pin.

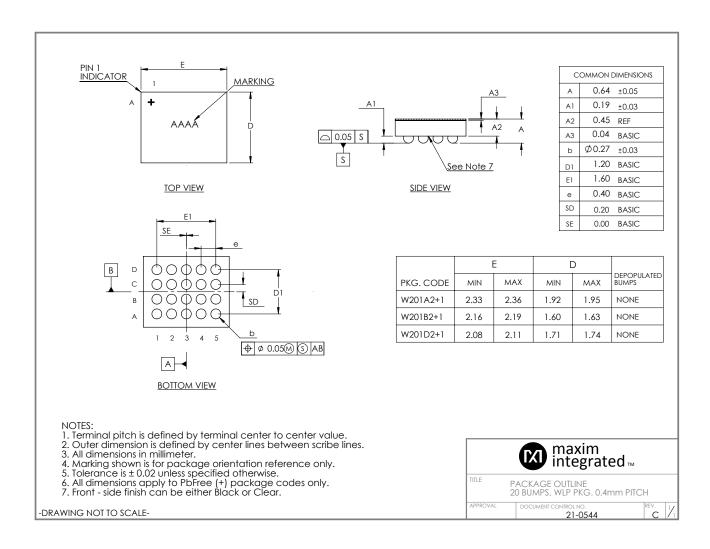

The IC is available in a space-saving, 20-bump, 2.18mm x 1.62mm WLP package.

### **Applications**

- USB Charging

- Smartphones

- Bluetooth Headsets

- AR/VR Glasses

- Hearables

- Wearables

- Portable Devices

Ordering Information and Simplified Applications Circuit appear at end of data sheet.

The Bluetooth word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. and any use of such marks by Maxim is under license.

### **Benefits and Features**

- Switch-Mode Charger

- · High-Efficiency

- Low Heat

- · Fast Charge Time

- Small and Simple

- Precise

- Up to ±5% Current Regulation and 0.5% Voltage Regulation

- Safe

- JEITA Battery Temperature Monitor

- Over/Undervoltage Protection, Safety Timers, Temperature Regulation

- USB Friendly

- Flexible

- Programmable Voltage/Current

- Status/Interrupts Through I<sup>2</sup>C

- · Automatic Input Current Limit

- I<sup>2</sup>C Interface

- Input Current Limit (100mA to 1500mA)

- Fast-Charge/Termination Current (250mA to 1550mA)

- Charge Voltage (4.1V, 4.15V, 4.2V, 4.35V)

- Termination Enable

- +22V Absolute Maximum Input Voltage Rating

- Up to 7.5V Maximum Operating Input Voltage

- 5V USB/Safeout LDO for USB PHY

- 2.3A GSM RF Test Mode (Factory Testing)

- Charge Current to Voltage Conversion (V<sub>ICHG</sub>) for Baseband ADC

- Reverse Battery Leakage Protection

- Input/Output Overvoltage Protection

- Interrupt Status Output

### **TABLE OF CONTENTS**

| General Description                   | 1  |

|---------------------------------------|----|

| Applications                          | 1  |

| Benefits and Features                 | 1  |

| Absolute Maximum Ratings              | 5  |

| Package Thermal Characteristics       | 5  |

| Electrical Characteristics            | 5  |

| Typical Operating Characteristics     | 10 |

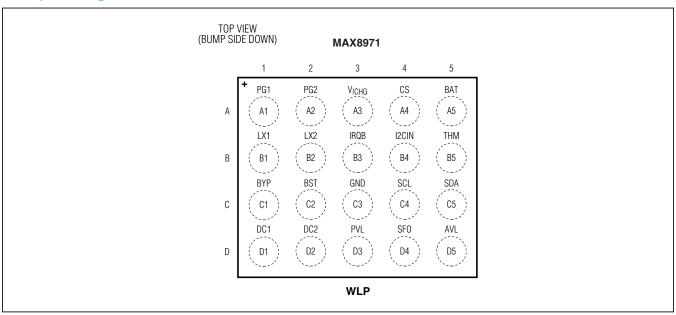

| Bump Configuration                    | 15 |

| Bump Description                      | 15 |

| Detailed Description                  | 17 |

| DC Input—Fast-Hysteretic              |    |

| Step-Down Regulator                   |    |

| Soft-Start                            |    |

| PVL and AVL                           |    |

| Thermistor Input (THM)                |    |

| Thermal Foldback                      |    |

| Charger States                        |    |

| Charger-Disabled State                |    |

| Dead-Battery State                    |    |

| Dead-Battery + Prequalification State |    |

| Prequalification State                | 21 |

| Fast-Charge Constant-Current State    | 21 |

| Fast-Charge Constant Voltage State    |    |

| Top-Off State                         | 21 |

| Done State                            | 21 |

| Timer Fault State                     |    |

| Overvoltage and Protection            |    |

| Automatic Input Current               |    |

| Limit Protection                      |    |

| VICHG Charging Current Monitor        |    |

| SAFEOUT                               |    |

| JEITA Description                     |    |

| Maxim Model Gauge M3 Support          |    |

| Factory-Mode GSM Test Mode Support    | 23 |

# **TABLE OF CONTENTS (continued)**

| Applications Information                                           | 24 |

|--------------------------------------------------------------------|----|

| Inductor Selection                                                 | 24 |

| Input Capacitor Selection                                          | 24 |

| Output Capacitor Selection                                         | 24 |

| Charge Current Resistor Selection                                  | 24 |

| Serial Interface                                                   | 25 |

| System Configuration                                               | 25 |

| Bit Transfer                                                       | 25 |

| START and STOP Conditions                                          | 26 |

| Acknowledge                                                        | 26 |

| Slave Address                                                      | 27 |

| Clock Stretching                                                   | 27 |

| General Call Address                                               | 27 |

| Communication Speed                                                | 27 |

| Communication Protocols                                            | 27 |

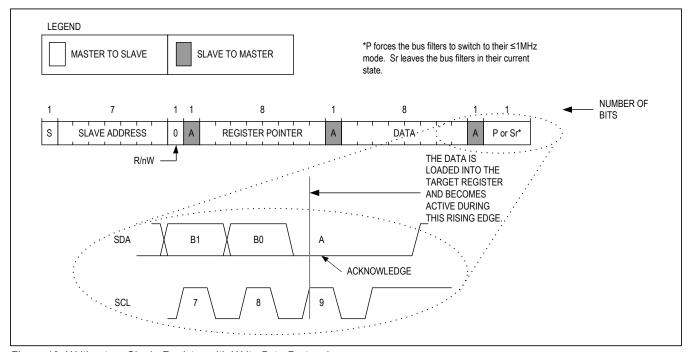

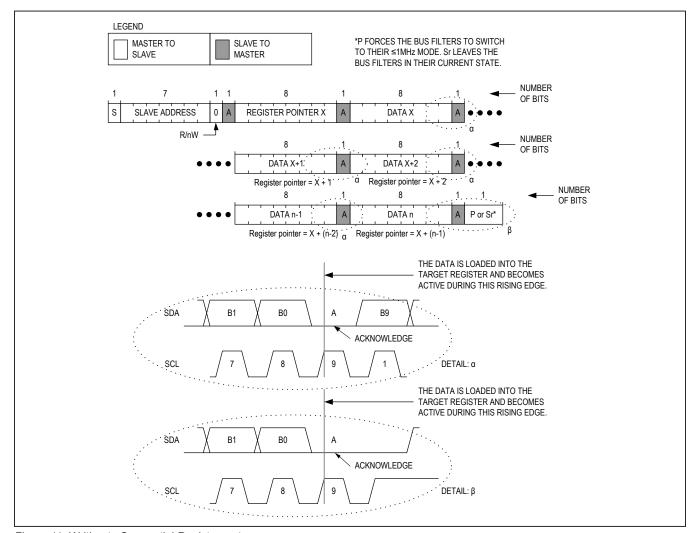

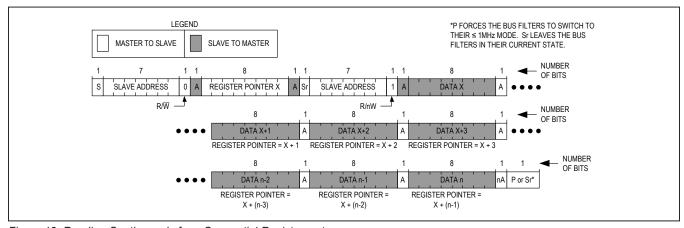

| Writing to a Single Register                                       | 28 |

| Writing to a Sequential Register                                   | 29 |

| Reading from a Single Register                                     | 30 |

| Reading from a Sequential Register                                 | 30 |

| I <sup>2</sup> C Registers                                         | 32 |

| Charger Interrupt Requests                                         | 32 |

| Charger Interrupt Masks                                            | 33 |

| Charger Status                                                     | 34 |

| DETAILS1                                                           |    |

| DETAILS2                                                           | 36 |

| Input Voltage Disable and USB Suspend                              | 37 |

| Fast-Charge Current and Timer Control                              |    |

| Input-Current Limit and Charger Restart Threshold                  | 38 |

| Done Current, Timer, GSM Test Mode, and Battery Regulation Voltage | 41 |

| Temperature Regulation                                             | 42 |

| Charger Protection                                                 |    |

| Simplified Applications Circuit                                    |    |

| Ordering Information                                               |    |

| Chip Information                                                   |    |

| Package Information                                                |    |

| Revision History                                                   |    |

### MAX8971

# Industry's Smallest 1.55A 1-Cell Li+ DC-DC Charger

| LIST OF TABLES                                                                    |    |

|-----------------------------------------------------------------------------------|----|

| Table 1. Trip Temperatures for Different Thermistors                              |    |

| Table 2. Suggested Inductors                                                      |    |

| Table 3. Charge Current Settings for $47m\Omega$ and $68m\Omega$ Sense Resistors  |    |

| Table 4. Top-Off Current Settings for $47m\Omega$ and $68m\Omega$ Sense Resistors |    |

| Table 5. High-Level I <sup>2</sup> C Register Map                                 |    |

| Table 6. CHGCC[4:0] Decoding                                                      |    |

| Table 7. DCILMT[5:0] Bit Code                                                     |    |

|                                                                                   |    |

| LIST OF FIGURES                                                                   |    |

| Figure 4. Topical Application Circuit                                             | 40 |

| Figure 1. Typical Application Circuit.                                            |    |

| Figure 2. Li/Li-Poly Charge Profile.                                              |    |

| Figure 3. Functional State Diagram                                                |    |

| Figure 4. JEITA Safety Region.                                                    |    |

| Figure 5. MAX8971 with MAX17047                                                   |    |

| Figure 6. Functional Logic Diagram for Communications Controller                  |    |

| Figure 7. I <sup>2</sup> C Bit Transfer                                           |    |

| Figure 8. START and STOP Conditions                                               |    |

| Figure 9. Slave Address Byte Example                                              |    |

| Figure 10. Writing to a Single Register with Write Byte Protocol                  |    |

| Figure 11. Writing to Sequential Registers x to n                                 | 29 |

| Figure 12. Reading Continuously from Sequential Registers x to n                  |    |

### **Absolute Maximum Ratings**

| BYP to PG                                        | 0.3V to +22V        |

|--------------------------------------------------|---------------------|

| DC_ to BYP                                       | 6V to +0.3V         |

| I2CIN, V <sub>ICHG</sub> , IRQB, SDA, SCL to GND | 0.3V to +6V         |

| BST to AVL                                       | 0.3V to +16V        |

| BST to LX                                        | 0.3V to +6V         |

| PVL, SFO, BAT, CS to PG                          | 0.3V to +6V         |

| AVL, THM to GND                                  | 0.3V to +6V         |

| PG_ to GND                                       | 0.3V to +0.3V       |

| DC_, LX_, CS, BAT, BYP Continuous Current        | 1.6A <sub>RMS</sub> |

| Continuous Power Dissipation (T <sub>A</sub> = +70° | C)             |

|-----------------------------------------------------|----------------|

| WLP derate 21.7mW/°C above +70°C .                  | 1736mW         |

| Operating Temperature Range                         | 40°C to +85°C  |

| Junction Temperature                                | +150°C         |

| Storage Temperature Range                           | 65°C to +150°C |

| Soldering Temperature (reflow)                      | +260°C         |

### Package Thermal Characteristics (Note 1)

WI F

Junction-to-Ambient Thermal Resistance (q<sub>JA</sub>) ......46°C/W

Junction-to-Case Thermal Resistance (q<sub>JC</sub>)......2°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{DC} = 5V, C_{BYP} = 1\mu F, I_{FCHG} = 500mA, C_{AVL} = 4.7\mu F, V_{THM} = AVL/2, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                     | CONDITIONS                                    |                                               |      | TYP  | MAX              | UNITS |

|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|------|------|------------------|-------|

| DC INPUT                                      |                                               |                                               |      |      |                  |       |

| DC Operating Voltage Range                    |                                               |                                               | 4.0  |      | V <sub>OVP</sub> | V     |

| DC Undervoltage Lockout (V <sub>UVLO</sub> )  | DC rising, 500mV hysteresis                   | 3                                             | 3.6  | 3.8  | 4.0              | V     |

| DC Overvoltage Threshold (V <sub>OVP</sub> )* | DC rising, 250mV hysteresis                   | 3                                             | 7.25 | 7.5  | 7.75             | V     |

| DC OVP Interrupt Delay                        |                                               |                                               |      | 16   |                  | ms    |

| DC to BAT Shutdown Threshold                  | When charging stops, V <sub>DC</sub> f        | alling, 150mV hysteresis                      | 0    | 50   | 100              | mV    |

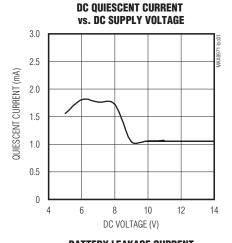

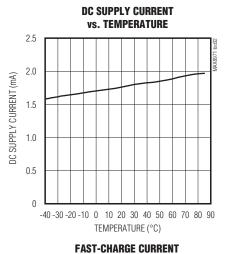

| DC Supply Current                             | Charger enabled, V <sub>DC</sub> = 5.5        | Charger enabled, V <sub>DC</sub> = 5.5V       |      | 2    |                  | mA    |

| PCT Lookaga Current                           | V <sub>BST</sub> = 5.5V, LX_ = PG_            | T <sub>A</sub> = +25°C                        |      | 0.01 | 10               |       |

| BST Leakage Current                           | V <sub>BST</sub> - 5.5V, LA PG_               | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      | 0.1  |                  |       |

| LV Lookaga Cumant                             | \\                                            | T <sub>A</sub> = +25°C                        |      | 0.01 | 10               | μA    |

| LX_ Leakage Current                           | V <sub>LX</sub> _ = 0 or 5.5V                 | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      | 0.1  |                  |       |

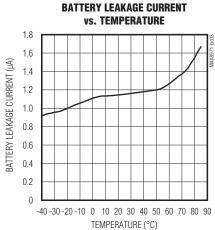

| BAT Reverse Leakage Current                   | V <sub>DC</sub> = 0V, V <sub>BAT</sub> = 4.2V |                                               |      | 1    | 5                | μA    |

| Input-Current Limit Range                     |                                               |                                               | 0.1  |      | 1.5              | А     |

<sup>\*</sup>This device is constructed using a unique set of packaging techniques that impose a limit on the thermal profile the device can be exposed to during board-level solder attach and rework. This limit permits only the use of the solder profiles recommended in the industry-standard specification, JEDEC 020A, paragraph 7.6, Table 3 for IR/VPR and Convection reflow. Preheating is required. Hand or wave soldering is not allowed.

$(V_{DC}$  = 5V,  $C_{BYP}$  = 1 $\mu$ F,  $I_{FCHG}$  = 500mA,  $C_{AVL}$  = 4.7 $\mu$ F,  $V_{THM}$  = AVL/2,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                                           | CONDITIONS                                                                                          | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|-------|

|                                                                     | DCILMT[5:0] = 0b000000 (100mA)                                                                      | 90   | 95   | 100  |       |

| Input-Current Limit Accuracy                                        | DCILMT[5:0] = 0b010100 (500mA)                                                                      | 450  | 475  | 500  | mA    |

|                                                                     | DCILMT[5:0] = 0b111100 (1500mA)                                                                     | 1350 | 1500 | 1650 |       |

| Adaptive Input-Current Limit (AICL)                                 | DC voltage where charge current is regulated                                                        |      | 4.5  |      | .,    |

| (Note 4)                                                            | DC voltage where charge current is set to 75mA                                                      |      | 4.4  |      | V     |

| Input Limit Switch                                                  | V <sub>DC</sub> = 5.5V, I <sub>BYP</sub> = 100mA                                                    |      | 35   | 80   | mΩ    |

| BUCK OPERATION                                                      |                                                                                                     |      |      |      |       |

| Switching Frequency                                                 | V <sub>BAT</sub> = 3.6V                                                                             |      | 4    |      | MHz   |

| Maximum Duty Cycle                                                  |                                                                                                     |      | 99.5 |      | %     |

| Minimum On-Time                                                     |                                                                                                     |      | 55   |      | ns    |

| Maximum On-Time                                                     |                                                                                                     |      | 10   |      | μs    |

| Minimum Off-Time                                                    |                                                                                                     |      | 65   |      | ns    |

| Soft-Start Time                                                     |                                                                                                     |      | 1.5  |      | ms    |

| High-Side Resistance                                                | I <sub>LX</sub> = 100mA, V <sub>DC</sub> = 5.5V                                                     |      | 120  | 250  | mΩ    |

| Low-Side Resistance                                                 | I <sub>LX</sub> = 100mA, V <sub>DC</sub> = 5.5V                                                     |      | 150  | 220  | mΩ    |

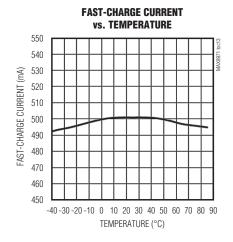

| Thermal Regulation Temperature (T <sub>REG</sub> )                  | I <sup>2</sup> C programmable with REGTEMP[1:0] to 90°C, 105°C, 120°C, and disabled (default 105°C) |      | 105  |      | °C    |

| Thermal Regulation Gain                                             | Percentage decrease in I <sub>FCHG</sub> above the thermal regulation temperature                   |      | 5    |      | %/°C  |

| BATTERY CHARGER PRECHARG                                            | E                                                                                                   |      |      |      |       |

| Battery-Prequalification Lower<br>Threshold (V <sub>PQLTH</sub> )   | V <sub>BAT</sub> rising, 130mV hysteresis                                                           |      | 2.1  |      | V     |

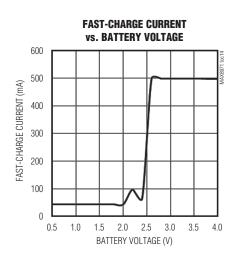

| Dead-Battery Charge Current (I <sub>DBAT</sub> )                    | 0V ≤ V <sub>BAT</sub> ≤ 2.1V                                                                        |      | 45   |      | mA    |

| Battery-Prequalification Upper<br>Threshold (V <sub>PQUTH</sub> )** | V <sub>BAT</sub> rising, 150mV hysteresis                                                           |      | 2.5  |      | V     |

| Prequalification Charge Current (I <sub>PQ</sub> )                  | Percentage of fast-charge current programmed                                                        |      | 10   |      | %     |

| CONSTANT-CURRENT MODE                                               |                                                                                                     |      |      | -    |       |

| BAT Fast-Charge Current (I <sub>FCHG</sub> )<br>Range               | 5 bits: 50mA steps, R <sub>CS</sub> = 47ml                                                          | 250  |      | 1550 | mA    |

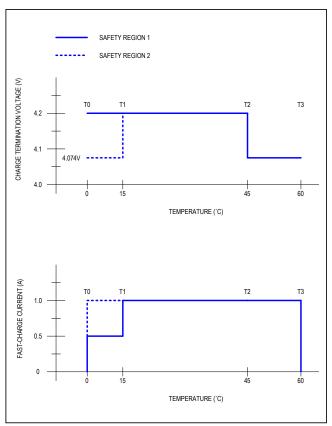

| Fact Charge Current A                                               | T <sub>A</sub> = +15°C to +45°C                                                                     | -5   |      | +5   | %     |

| Fast-Charge Current Accuracy                                        | JEITA safety region (Figure 4)                                                                      | -65  | -50  | -35  | %     |

$(V_{DC}$  = 5V,  $C_{BYP}$  = 1 $\mu$ F,  $I_{FCHG}$  = 500mA,  $C_{AVL}$  = 4.7 $\mu$ F,  $V_{THM}$  = AVL/2,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                | CONDITIONS                                                                                                         |                                                                                                                         |      | TYP   | MAX  | UNITS |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|--|

| CONSTANT VOLTAGE MODE                    |                                                                                                                    |                                                                                                                         |      |       |      |       |  |

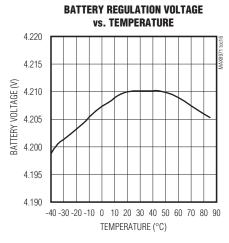

|                                          | I <sub>BAT</sub> = 100mA, operating in                                                                             | T <sub>A</sub> = +25°C                                                                                                  | -0.5 |       | +0.5 |       |  |

|                                          | voltage-regulation mode,                                                                                           | T <sub>A</sub> = -40°C to +85°C                                                                                         | -1   |       | +1   |       |  |

| Battery Regulation Voltage (VBATREG)     | I <sup>2</sup> C programmable with<br>CHGCV[1:0] to 4.1V, 4.15V,<br>4.2V, and 4.35V (default<br>4.2V)              | JEITA safety region,<br>percentage of battery<br>regulation voltage<br>(Note 6)                                         | 96   | 97    | 98   | %     |  |

| Battery Refresh Threshold                | (Below regulation point), 100n default 150mV (Note 5)                                                              | nV and 150mV selection,                                                                                                 | 120  | 150   | 185  | mV    |  |

| Battery Overvoltage Protection           |                                                                                                                    | V <sub>BAT</sub> threshold over regulation voltage to turn off charger during charge (% of regulation voltage) (Note 7) |      | 103.5 | 105  | %     |  |

|                                          | Hysteresis (V <sub>BAT</sub> falling) at 4.2                                                                       | 2V                                                                                                                      |      | 1.4   |      | 1     |  |

| Charge-Current Termination               | Programmable topoff current i functionality, default 50mA, 20                                                      |                                                                                                                         | 50   |       | 200  | mA    |  |

| Threshold (I <sub>TOPOFF</sub> )         | Deglitch time                                                                                                      |                                                                                                                         |      | 16    |      | ms    |  |

| Charge-Current Termination<br>Accuracy   | I <sub>TOPOFF</sub> = 200mA                                                                                        |                                                                                                                         | -20  |       | +20  | %     |  |

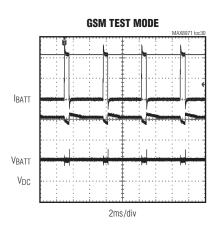

| GSM TEST MODE                            |                                                                                                                    |                                                                                                                         |      |       |      |       |  |

| GSM Test-Mode Output Pulse<br>Current    | V <sub>BAT</sub> capacitance ≥ 60μF, pea<br>frequency = 217Hz, on-duty c                                           |                                                                                                                         |      | 2.3   |      | А     |  |

| GSM Test-Mode Minimum Output             | V <sub>BAT</sub> capacitance ≥ 60μF, current pulse<br>frequency = 217Hz, on-duty cycle 12.5%<br>(Note 3)           |                                                                                                                         | 3.7  |       |      | V     |  |

| CHARGER TIMER                            |                                                                                                                    |                                                                                                                         |      |       |      |       |  |

| Prequalification Time (t <sub>PQ</sub> ) | V <sub>BAT</sub> < V <sub>BATPQ_UT</sub>                                                                           |                                                                                                                         |      | 45    |      | Mins  |  |

| Fast-Charge Time (t <sub>FC</sub> )      | I <sup>2</sup> C programmable with FCHGT[2:0] from 4 hours to 10 hours (default 5 hours)                           |                                                                                                                         |      | 5     |      | hrs   |  |

| Timer Accuracy                           | , ,                                                                                                                |                                                                                                                         |      | 20    |      | %     |  |

| Top-Off Time (t <sub>TOPOFF</sub> )      | I <sup>2</sup> C programmable with TOFFT[2:0] from 0 minutes to 70 minutes in 10-minute steps (default 30 minutes) |                                                                                                                         | 0    |       | 70   | Mins  |  |

| Top-Off Timer Accuracy                   |                                                                                                                    |                                                                                                                         |      | 20    |      | %     |  |

| Timer-Extend Current Threshold (Note 3)  | Percentage of fast-charge current below which the timer clock operates at half speed                               |                                                                                                                         |      | 50    |      | %     |  |

$(V_{DC}$  = 5V,  $C_{BYP}$  = 1 $\mu$ F,  $I_{FCHG}$  = 500mA,  $C_{AVL}$  = 4.7 $\mu$ F,  $V_{THM}$  = AVL/2,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25 $\mu$ C.) (Note 2)

| UNITS | MAX   | TYP   | MIN   | CONDITIONS                                      |                                                                             | PARAMETER                                        |

|-------|-------|-------|-------|-------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|

|       |       |       | •     |                                                 |                                                                             | THERMISTOR MONITOR                               |

| %     | 78.06 | 74.56 | 71.06 |                                                 | V <sub>THM/AVL</sub> rising, 1% hysteris (thermistor temperature falling    | THM Threshold, Cold, No Charge (0°C)             |

| %     | 63.00 | 60.00 | 57.00 |                                                 | V <sub>THM/AVL</sub> rising, 1% hysteris (thermistor temperature falling    | THM Threshold, Cold, Current<br>Foldback (+15°C) |

| %     | 36.68 | 34.68 | 32.68 |                                                 | V <sub>THM/AVL</sub> falling, 1% hysteris<br>(thermistor temperature rising | THM Threshold, Hot, Voltage<br>Foldback (+45°C)  |

| %     | 23.84 | 22.54 | 21.24 |                                                 | V <sub>THM/AVL</sub> falling, 1% hysteris<br>(thermistor temperature rising | THM Threshold, Hot, No Charge<br>(+60°C)         |

|       | +0.2  | 0.01  | -0.2  | T <sub>A</sub> = +25°C                          | \\\ =\\\ ar 0\\                                                             | TUM Innut Dies Current                           |

| μA    |       | 0.01  |       | T <sub>A</sub> = +85°C                          | $V_{THM} = V_{AVL}$ or $0V$                                                 | THM Input Bias Current                           |

|       |       | -     |       |                                                 |                                                                             | VICHG                                            |

| mV    |       | 150   |       |                                                 | I <sub>BAT</sub> = 100mA                                                    |                                                  |

| mV    | 1540  | 1400  | 1260  |                                                 | I <sub>BAT</sub> = 1000mA                                                   | V <sub>ICHG</sub> Output Voltage                 |

| mV    |       | 2100  |       | I <sub>BAT</sub> = 1500mA                       |                                                                             |                                                  |

|       |       |       |       |                                                 |                                                                             | IRQB OUTPUT                                      |

| V     | 0.4   |       |       | t                                               | I <sub>IRQB</sub> =10mA, sinking current                                    | Low-Level Output Saturation<br>Voltage           |

| μA    | +1    | 0.01  | -1    | T <sub>A</sub> = +25°C                          | \/ - 5\/                                                                    | High Loyal Lookaga Current                       |

| μA    |       | 0.1   |       | ge Current $V_{IRQB} = 5V$ $T_A = +85^{\circ}C$ | High-Level Leakage Current                                                  |                                                  |

|       |       |       |       |                                                 |                                                                             | SAFEOUT OUTPUT                                   |

| V     | 5.25  | 5     | 4.75  |                                                 | I <sub>SFO</sub> = 30mA, V <sub>DC</sub> = 5.5V                             | Regulated Output                                 |

| mV    |       | 45    |       |                                                 | I <sub>SFO</sub> = 30mA                                                     | Dropout Voltage                                  |

| mA    |       | 590   |       |                                                 |                                                                             | Current Limit                                    |

| mA    |       |       | 100   |                                                 |                                                                             | Maximum Output Current                           |

| V     |       | 2.7   |       |                                                 |                                                                             | POK Output Threshold                             |

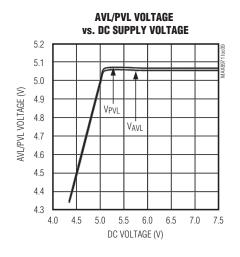

|       |       |       |       |                                                 |                                                                             | PVL/AVL OUTPUT                                   |

| V     |       | 5.05  |       |                                                 | 5.5V < V <sub>DC</sub> < 7.5V, no load                                      | PVL Output Voltage                               |

| V     |       | 5.05  |       | 5.5V < V <sub>DC</sub> < 7.5V, no load          |                                                                             | AVL Output Voltage                               |

|       |       |       |       |                                                 | RACTERISTICS (SCL, SDA)                                                     | LOGIC LEVELS AND TIMING CHA                      |

| V     | 0.4   |       |       |                                                 | I <sub>o</sub> = 3mA, sink current (SDA)                                    | Output Low Threshold                             |

| V     | 0.4   |       |       | V <sub>I2CIN</sub> = 1.8V                       |                                                                             | Input Low Threshold                              |

| V     |       |       | 1.4   |                                                 | V <sub>I2CIN</sub> = 1.8V                                                   | Input High Threshold                             |

|       | 0.4   |       | 1.4   |                                                 |                                                                             | <u>'</u>                                         |

$(V_{DC} = 5V, C_{BYP} = 1\mu F, I_{FCHG} = 500mA, C_{AVL} = 4.7\mu F, V_{THM} = AVL/2, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                                                                            | CONDITIONS                                        | MIN | TYP  | MAX | UNITS |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|------|-----|-------|

| Input Bias Current                                                                                                   | V <sub>I2CIN</sub> = 1.8V, T <sub>A</sub> = +25°C |     |      | 1   | μA    |

| SCL Clock Frequency                                                                                                  |                                                   | 100 |      | 400 | kHz   |

| Bus Free Time Between START and STOP (Note 3)                                                                        |                                                   | 1.3 |      |     | μs    |

| Hold Time REPEATED START<br>Condition (Note 3)                                                                       |                                                   | 0.6 |      |     | μs    |

| SCL Low Period (Note 3)                                                                                              |                                                   | 1.3 |      |     | μs    |

| SCL High Period (Note 3)                                                                                             |                                                   | 0.6 |      |     | μs    |

| Setup Time REPEATED START Condition (Note 3)                                                                         |                                                   | 0.6 |      |     | μs    |

| SDA Hold Time (Note 3)                                                                                               |                                                   | 0   |      |     | μs    |

| SDA Setup Time (Note 3)                                                                                              |                                                   | 100 |      |     | ns    |

| Maximum Pulse Width of Spikes<br>(must be suppressed by the input<br>filter of both SDA and SCL signals)<br>(Note 3) |                                                   |     | 50   |     | ns    |

| Setup Time for STOP Condition (Note 3)                                                                               |                                                   | 0.6 |      |     | μs    |

| THERMAL REGULATION AND SH                                                                                            | UTDOWN                                            |     |      |     |       |

| Thermal Shutdown Temperature (Note 3)                                                                                |                                                   |     | +160 |     | °C    |

| Thermal Shutdown Hysteresis (Note 3)                                                                                 |                                                   |     | 15   |     | °C    |

- **Note 2:** Parameters are production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed through correlation using statistical quality control (SQC) methods.

- Note 3: Guaranteed by design, not production tested.

- Note 4: Voltage for 4.35V battery mode increases by 100mV.

- Note 5: Refresh voltage for 4.15V increases by 50mV.

- Note 6: JEITA decreases by 1% for 4.15V termination voltage.

- Note 7: Battery overvoltage increases by 1% for 4.15V termination voltage.

<sup>\* =</sup> Contact factory for alternate thresholds (6.7V, 9.7V, and 14V available).

<sup>\*\* =</sup> Contact the factory for 3.0V.

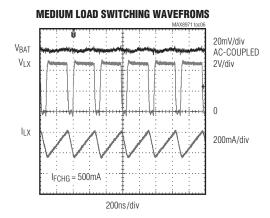

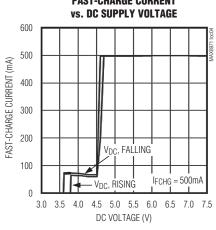

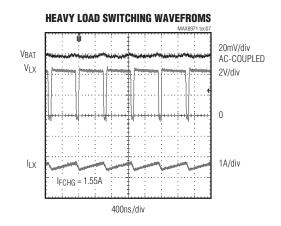

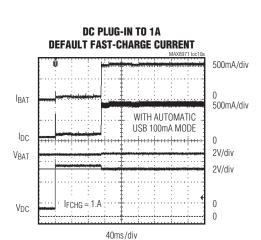

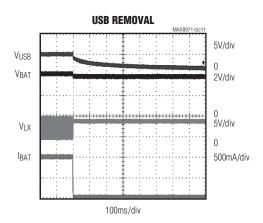

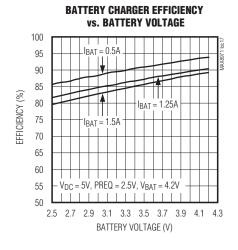

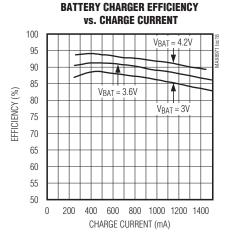

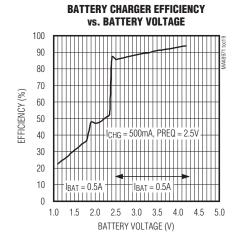

### **Typical Operating Characteristics**

$(V_{DC} = 5V, C_{BYP} = 1\mu F, C_{AVL} = 4.7\mu F, V_{THM} = 2.5V, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

$(V_{DC} = 5V, C_{BYP} = 1\mu F, C_{AVL} = 4.7\mu F, V_{THM} = 2.5V, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

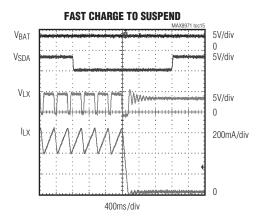

###

400µs/div

$(V_{DC} = 5V, C_{BYP} = 1\mu F, C_{AVL} = 4.7\mu F, V_{THM} = 2.5V, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

$(V_{DC} = 5V, C_{BYP} = 1\mu F, C_{AVL} = 4.7\mu F, V_{THM} = 2.5V, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

$(V_{DC} = 5V, C_{BYP} = 1\mu F, C_{AVL} = 4.7\mu F, V_{THM} = 2.5V, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

# **Bump Configuration**

# **Bump Description**

| PIN    | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2 | PG1, PG2          | Power Ground for Step-Down Low-Side FET                                                                                                                                                                                                                                                                                                                                                                        |

| A3     | V <sub>ICHG</sub> | Battery-Charging Current Monitor Output. This pin is an analog representation of the charger current at 1.4mV/mA.                                                                                                                                                                                                                                                                                              |

| A4     | CS                | Current-Sense Input Power Pin                                                                                                                                                                                                                                                                                                                                                                                  |

| A5     | BAT               | Battery Connection. Connect to a single-cell Li+ battery.                                                                                                                                                                                                                                                                                                                                                      |

| B1, B2 | LX1, LX2          | Buck Inductor Connection. Connect the inductor between LX_ and CS. The LX1 and LX2 pins must be connected together externally.                                                                                                                                                                                                                                                                                 |

| В3     | IRQB              | Open-Drain Host Processor Interrupt Pin                                                                                                                                                                                                                                                                                                                                                                        |

| B4     | I2CIN             | I <sup>2</sup> C Interface Supply                                                                                                                                                                                                                                                                                                                                                                              |

| B5     | ТНМ               | Thermistor Input. Connect a negative temperature coefficient (NTC) thermistor from THM to GND. Connect a resistor equal to the thermistor +25°C resistance from THM to AVL. Charging is suspended when the thermistor is outside the hot and cold limits. Connect THM to GND to disable the thermistor temperature sensor. If the thermistor function is disable through I <sup>2</sup> C, connect THM to GND. |

| C1     | BYP               | Connection Point Between Reverse Blocking MOSFET and High-Side Switching MOSFET. Bypass to PG_ with a minimum 1µF ceramic capacitor.                                                                                                                                                                                                                                                                           |

| C2     | BST               | High-Side FET Driver Supply. Bypass BST to LX with a 0.1µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                  |

| C3     | GND               | Analog Ground. GND is the low-noise ground connection for the internal circuitry.                                                                                                                                                                                                                                                                                                                              |

# **Bump Description (continued)**

| PIN    | NAME     | FUNCTION                                                                                                                                                                                                                  |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C4     | SCL      | I <sup>2</sup> C Interface Clock. Connect a 10kΩ resistor from SCL to I2CIN.                                                                                                                                              |

| C5     | SDA      | I <sup>2</sup> C interface Data. Connect a 10kΩ resistor from SDA to I2CIN.                                                                                                                                               |

| D1, D2 | DC1, DC2 | High-Current Charger Input Supply Pin(s). Bypass to PG_ with a 2.2µF ceramic capacitor. DC is capable of delivering up to 1.5A to BYP. DC supports both AC adapter and USB inputs. Short DC1 and DC2 together externally. |

| D3     | PVL      | Internal Bias Regulator High-Current Output Bypass Pin. Supports internal noisy and high-current gate drive loads. Bypass to PGND with a minimum 1µF ceramic capacitor. Do not use PVL to power external loads.           |

| D4     | SFO      | 5V SAFEOUT (SFO) LDO Linear Regulator Output. Bypass SFO to GND with a 1μF or larger ceramic capacitor. SFO can be used to supply low-voltage rated USB systems.                                                          |

| D5     | AVL      | Internal-Bias-Regulator Quiet Analog Bypass Pin. Internal $10\Omega$ connection between PVL and AVL forms a lowpass filter with external bypass capacitor to GND. Do not use AVL to power external loads.                 |

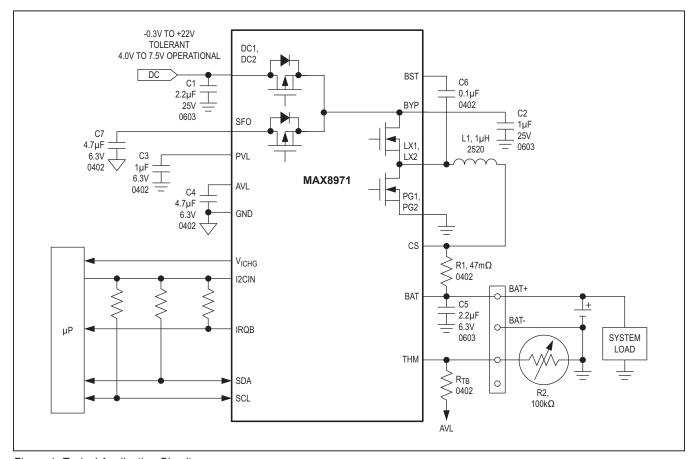

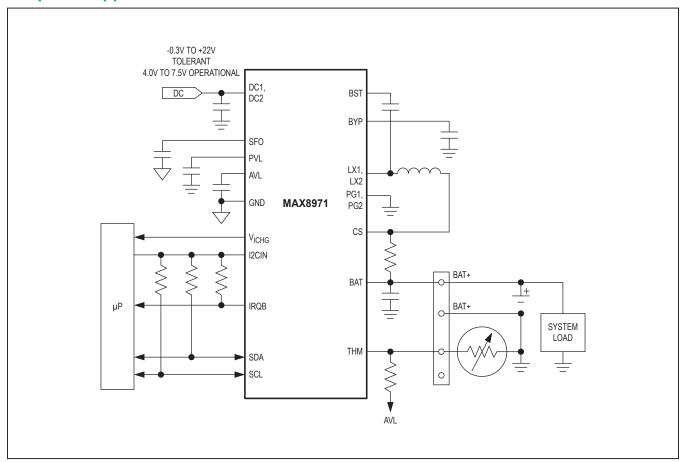

Figure 1. Typical Application Circuit

### **Detailed Description**

The MAX8971 is a JEITA-compliant Li+ switching battery charger that safely charges a single Li+ cell in accordance with JEITA specifications. The IC accepts an input supply range from 4V to 7.5V, but disables charging if the supply voltage exceeds +7.5V, protecting against unqualified or faulty AC adapters. The step-down converter supplies up to 1.5A to the battery. The IC includes charger features thermistor monitor, charger status and fault outputs. Also included are interrupt signals to the processor. Flexibility is maintained with adjustable charge current, input current limit, and a minimum battery voltage (when charging is scaled back to hold the battery voltage up) through an I<sup>2</sup>C interface.

# DC Input—Fast-Hysteretic Step-Down Regulator

If a valid DC input is present, battery charging is supplied by the high-frequency step-down regulator from DC. The step-down regulation point is then controlled by three feedback signals: maximum step-down output current programmed by the input current limit, maximum charger current programmed for the fast-charge current, and maximum die temperature. The feedback signal requiring the smallest current controls the average output current in the inductor. This scheme minimizes total power dissipation for battery charging, and allows the battery to absorb any load transients with minimum voltage disturbance.

A proprietary hysteretic current PWM control scheme ensures fast switching and physically tiny external components. The feedback control signal that requires the smallest input current, controls the center of the peak and valley currents in the inductor. The ripple current is internally set to provide 4MHz operation. When the input voltage decreases near the output voltage, very high duty cycle occurs. Due to minimum off-time, 4MHz operation is not achievable. The controller then provides minimum off-time, peak current regulation. Similarly, when the input voltage is too high to allow 4MHz operation due to the minimum off-time, the controller becomes a minimum on-time, valley current regulator. In this way, ripple current in the inductor is always as small as possible to reduce ripple voltage-on battery for a given capacitance. The ripple current is made to vary with input voltage and output voltage in a way that reduces frequency variation. However, the frequency still varies somewhat with operating conditions.

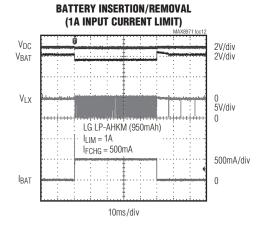

#### Soft-Start

To prevent input current transients, the rate of change of the input current (di/dt) and charge current is limited. When the input is valid the charge current ramps from 0mA to the fast-charge current value in 1.5ms. Charge current also soft-starts when transitioning from the prequalification state to the fast-charge state. There is no di/dt limiting when transitioning from the done state to the fast-charge state.

#### **PVL** and **AVL**

PVL is a 5V linear regulator that the IC uses to power the gate drivers for its step-down charger. PVL also charges the BST capacitor. The PVL linear regulator is on when DC is greater than  $\sim$ 2.5V, otherwise it is off. Bypass PVL with a 1 $\mu$ F ceramic capacitor to PG. Powering external loads from PVL is not recommended.

As shown in Figure 1, AVL is a filtered output from the PVL linear regulator that the IC uses to power its internal analog circuits. The filter consists of an internal  $10\Omega$  resistor, and the AVL external bypass capacitor (4.7µF). This filter creates a 100kHz lowpass filter that cleans the 4MHz switching noise from the analog portion of the IC. Connect a 4.7µF ceramic capacitor from AVL to GND. Powering external loads with AVL is not recommended.

### **Thermistor Input (THM)**

The THM input connects to an external negative temperature coefficient (NTC) thermistor to monitor battery or system temperature. Charging is suspended when the thermistor temperature is out of range. The charge timers are suspended and hold their state, but no fault is indicated. When the thermistor comes back into range, charging resumes and the charge timer continues from where it left.

Since the thermistor monitoring circuit employs an external bias resistor from THM to AVL, the thermistor is not limited only to  $10k\Omega$  (at +25°C). Any resistance thermistor can be used as long as the value is equivalent to the thermistors +25°C resistance. For example, with a

$10 k\Omega$  at RTB resistor, the charger enters a temperature suspend state when the thermistor resistance falls below  $3.97 k\Omega$  (too hot) or rises above  $28.7 k\Omega$  (too cold). This corresponds to the 0°C to +50°C range when using a  $10 k\Omega$  NTC thermistor with a beta of 3500. The general relation of thermistor resistance to temperature is defined by the following equation:

$$R_T = R_{25} \times e \left\{ \beta \left( \frac{1}{T + 273^{\circ}C} - \frac{1}{298^{\circ}C} \right) \right\}$$

where:

RT = the resistance in  $\Omega$  of the thermistor at temperature T in Celsius

R<sub>25</sub>= the resistance in  $\Omega$  of the thermistor at +25°C

β = the material constant of the thermistor, which typically ranges from 3000k to 5000k

T = the temperature of the thermistor in °C

Some designs might prefer other thermistor temperature limits. Threshold adjustment can be accommodated by changing RTB, connecting a resistor in series and/or in parallel with the thermistor, or using a thermistor with different  $\beta$ . For example, a +45°C hot threshold and 0°C cold threshold can be realized by using a thermistor with a  $\beta$  to 4250, and connecting 120k $\Omega$  in parallel. Since the thermistor resistance near 0°C is much higher than it is near +50°C, a large parallel resistance lowers the cold threshold, while only slightly lowering the hot threshold. Conversely, a small series resistance raises the hot threshold, while only slightly raising the cold threshold. Raising RTB, lowers both the hot and cold threshold, while lowering RTB raises both thresholds.

Note that since AVL is active whenever valid input power is connected at DC, thermistor bias current flows at all times. Using a  $10k\Omega$  thermistor and a  $10k\Omega$  pullup to AVL, results in an additional  $250\mu A$  load. This load can be reduced to  $25\mu A$  by instead using a  $100k\Omega$  thermistor and  $100k\Omega$  pullup resistor.

#### Thermal Foldback

Thermal foldback maximizes the battery charge current while regulating the IC's junction temperature. When the die temperature exceeds TREG, a thermal limiting circuit reduces the battery charge-current target until the charge current reaches 10% of the fast-charge current setting. The charger maintains 10% of the fast-charge current until the die temperature reaches TSHDN. Please note that the IC is rated for a maximum ambient temperature of +85°C. Furthermore, although the maximum die temperature of the MAX8971 is +150°C, it is common industry practice to design systems in such a way that the die temperature never exceeds +125°C. Limiting the maximum die temperature to +125°C extends long-term reliability.

### **Charger States**

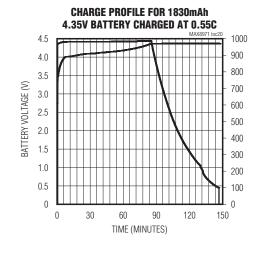

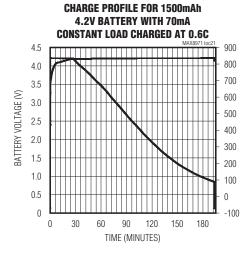

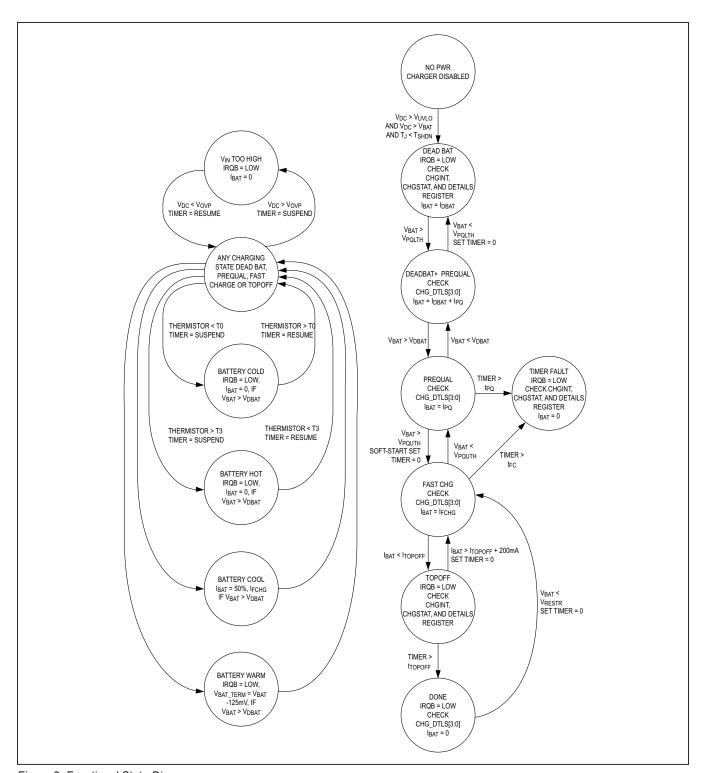

The IC utilizes several charging states to safely and quickly charge batteries as shown in Figure 3.

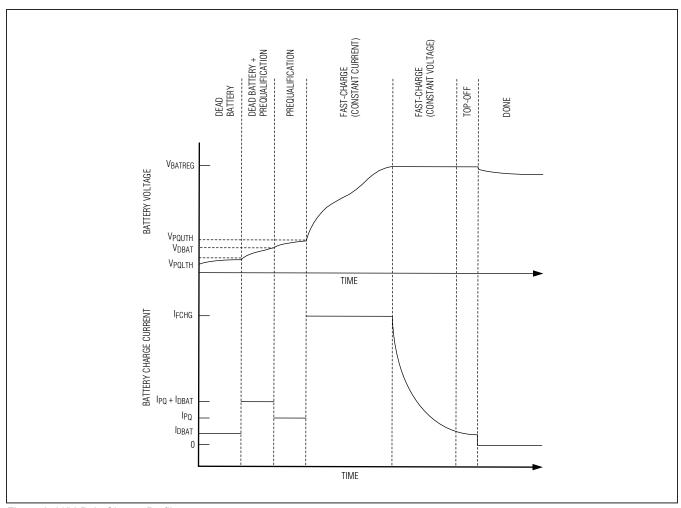

<u>Figure 2</u> shows an exaggerated view of a Li+/Li-Poly battery progressing through the following charge states when the die and battery are close to room temperature: dead battery  $\rightarrow$  prequalification  $\rightarrow$  fast charge  $\rightarrow$  top-off  $\rightarrow$  done.

**Table 1. Trip Temperatures for Different Thermistors**

|                      | R <sub>25</sub> (Ω) | 10000                         | 10000 | 47000 | 100000 |

|----------------------|---------------------|-------------------------------|-------|-------|--------|

| THERMISTOR           | Thermistor Beta (β) | 3380                          | 3940  | 4050  | 4250   |

|                      | R <sub>TB</sub> (Ω) | R <sub>TB</sub> (Ω) 10000 100 |       | 47000 | 100000 |

|                      | R <sub>15</sub> (Ω) | 14826                         | 15826 | 75342 | 164083 |

|                      | R <sub>45</sub> (Ω) | 4900                          | 4354  | 19993 | 40781  |

|                      | T0 (°C)             | -0.8                          | 2.6   | 3.2   | 4.1    |

| TRIP<br>TEMPERATURES | T1 (°C)             | 14.7                          | 16.1  | 16.4  | 16.8   |

|                      | T2 (°C)             | 42.6                          | 40.0  | 39.6  | 38.8   |

|                      | T3 (°C)             | 61.4                          | 55.7  | 54.8  | 53.2   |

Figure 2. Li/Li-Poly Charge Profile

Figure 3. Functional State Diagram

#### **Charger-Disabled State**

When DC is low or the input voltage is out of range, the IC disables the charger. To exit this state, the input voltage must be within its valid range.

#### **Dead-Battery State**

When a deeply discharged battery is inserted with a voltage of less than  $V_{PQLTH}$ , the IC disables the switching charger and linearly charges with  $I_{DBAT}$ . Once  $V_{BAT}$  increases beyond  $V_{PQLTH}$ , the IC clears the prequalification timer, and transitions to the dead battery + prequalification state. This state prevents the IC from dissipating excessive power in the event of a shorted battery. The dead-battery linear charge remains on, except when in the charger disabled state, timer fault state, thermal shutdown and  $V_{BAT} > V_{DBAT}$ .

#### **Dead-Battery + Prequalification State**

The dead battery + prequalification state occurs when the battery voltage is greater than  $V_{PQLTH}$ , and less than  $V_{DBAT}$ . In this state, both the linear dead-battery charger and the switching charger are on, delivering current to the battery. The total battery current is  $I_{DBAT}$  +  $I_{PQ}$ . If the IC remains in this state for longer than  $I_{PQ}$ , the IC transitions to the timer fault state. A normal battery typically stays in this state for several minutes or less. When the battery voltage rises above  $V_{DBAT}$  the IC transitions to the prequalification states. The dead-battery linear charger remains on except when in the charger disabled state, timer fault state, thermal shutdown and  $I_{DBAT}$  >  $I_{DBAT}$ .

#### **Pregualification State**

The prequalification state occurs when the battery voltage is greater than  $V_{DBAT}$  and less than  $V_{PQUTH}$ . In this state, the linear dead-battery charger is turned off. Only the switching charger is on and delivering current to the battery. The total battery current is  $I_{PQ}$ . If the IC remains in this state for longer than  $t_{PQ}$ , then the IC transitions to the timer fault state. A normal battery typically stays in the prequalification state for several minutes or less. When the battery voltage rises above  $V_{PQUTH}$ , the IC transitions to the fast-charge constant-current state.

### **Fast-Charge Constant-Current State**

The fast-charge constant-current state occurs when the battery voltage is greater than  $V_{PQUTH}$  and less than  $V_{BATREG}$ . In this state, the switching charger is on and delivering current to the battery. The total battery current is IFCHG. If the IC remains in this state and

the fast-charge constant voltage state for longer than  $t_{FC}$ , then the IC transitions to the timer fault state. When the battery voltage rises to  $V_{BATREG}$ , the IC transitions to the fast-charge constant voltage state. The fast-charge constant-current is set to 50% of programmed value when 0°C < THM <+15°C, and 100% of programmed value when +15°C < THM <+60°C.

The MAX8971 dissipates the most power in the fast-charge constant-current state. This power dissipation causes the internal die temperature to rise. If the die temperature exceeds  $T_{REG}$ ,  $I_{FCHG}$  is reduced.

If there is low input-voltage headroom ( $V_{IN}$  -  $V_{BAT}$ ), then I<sub>FCHG</sub> decreases due to the impedance from IN to BAT.

### **Fast-Charge Constant Voltage State**

The fast-charge constant voltage state occurs when the battery voltage is at the  $V_{BATREG}$ , and the charge current is greater than  $I_{TOPOFF}$ . In this state, the switching charge is on and delivering current to the battery. The IC maintains  $V_{BATREG}$  and monitors the charge current to detect when the battery consumes less than the TOPOFF current. When the charge current decreases below the TOPOFF threshold, the IC transitions to the top-off state. If the IC remains in the fast-charge constant-current state for longer than  $t_{FC}$ , then it transitions to the timer fault state.

#### **Top-Off State**

The top-off state occurs when the battery voltage is at  $V_{BATREG}$  and the battery current decreases below TOPOFF current. In this state, the switching charger is on and delivers current to the battery. The IC maintains  $V_{BATREG}$  for a specified time. When this time expires, the IC transitions to the DONE state. If the charging current increases to  $I_{TOPOFF}$  + 200mA before this time expires, then the charge reenters the fast-charge constant voltage state.

#### **Done State**

The IC enters its done state after the charge has been in the top-off state for  $t_{\mbox{\scriptsize TOPOFF}}.$  In this state, the switching charger is off and no current is delivered to the battery. If the system load presented to the battery is low <<  $10\mu A,$  then a typical system can remain in the done state for many days. If left in the done state long enough, the battery voltage decays below the restart threshold and the IC transitions back into the fast-charge state. There is no soft-start (di/dt limiting) during the done-to-fast-charge state transition.

#### **Timer Fault State**

The timer fault state occurs when either the prequalification or fast-charge timers expire. In this state, the charger is off. The charger can exit this timer fault state by cycling input power.

### **Overvoltage and Protection**

The IC provides for a +22V absolute maximum positive input voltage, and a -0.3V absolute maximum negative input voltage. Excursions to the absolute maximum voltage levels should be on a transient basis only, but can be withstood by the IC indefinitely.

Situations that typically require extended input voltage ratings include, but are not limited to the following:

- Inductive kick

- Charge source failure

- Power surge

- Improperly wired wall adapter

- · Improperly set universal wall adapter

- Wall adapter with the correct plug, but wrong voltage

- Home-built computer with USB wiring harness connected backwards (negative voltage)

- USB connector failure

- Excessive ripple voltage on a switch-mode wall charger

- USB-powered hub that is powered by a wall charger (typically through a barrel connector) that has any of the aforementioned issues

- Unregulated charger

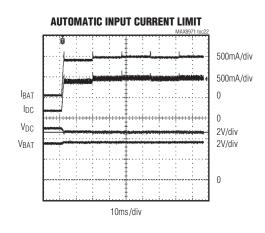

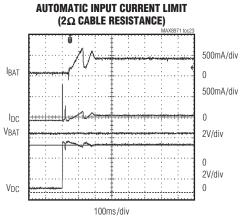

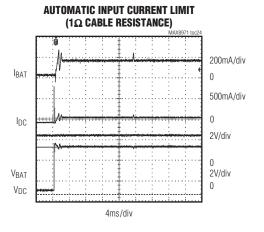

# Automatic Input Current Limit Protection

The IC includes an input-current-limiting feature. The amplifiers required for sensing the currents and associated logic circuitry for making decisions and changing the battery-charger current are fully integrated in the ICs. This not only helps in reducing cost, but also improves the speed of system response.

The IC works by monitoring the current being drawn from the AC adapter and comparing it to the programmed current limit. The current limit should be set based on the current-handling capability of the AC adapter. Generally, this limit is chosen to optimally fulfill the system-power requirements while achieving a satisfactory charging time for the batteries. If the AC-adapter current exceeds its output capability, the charger responds by cutting back on the charger current, thereby keeping the current drawn from the AC adapter within its capability. With such a battery charger, the AC adapter doesn't need to be oversized to meet maximum system and battery-charging requirements simultaneously, thereby reducing AC adapter cost.

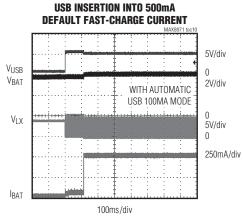

The input current limit has two control inputs, one based on voltage and one based on current. The voltage input monitors the input voltage, and when it drops below the desired input (4.5V), it generates a flag (AICL) to decrement the fast-charge current.

When the voltage comparator initially trips at 4.5V, fast-charge current decrements at a slow rate, allowing the charger output to settle until the voltage on DC returns above this voltage threshold. Once the DC voltage resolves itself, the current delivery of the adapter is maximized. In the event of a limited input current source, an example being a 500mA adaptor plugged into a 1A input current limit setting, a second voltage comparator set at 4.4V triggers and throttles the fast-charge current to a minimum of 75mA. Once the DC voltage corrects itself to above 4.5V, the fast-charge level is checked every 16ms to allow the system to recover if the available input power increases.

The current-limit input monitors the current through the input FET and generates a flag (DC\_I) to decrement the fast-charge current when the input limit is exceeded. The fast-charge current is slowly decremented until the input-limit condition is cleared. At this point, the fast-charge current is maintained for 16ms and is then sampled again.

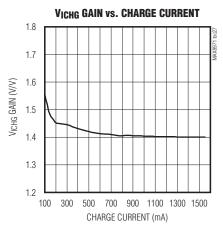

### **VICHG Charging Current Monitor**

V<sub>ICHG</sub> is a buffered output that can be interpreted to the charge current (V<sub>ICHG</sub> = 1400mV/I<sub>FCHG</sub>). See the <u>Typical</u> Operating Characteristics section for the V<sub>ICHG</sub> curve.

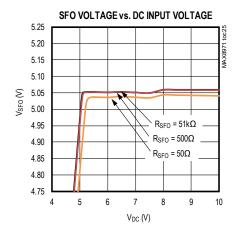

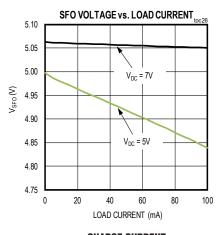

#### **SAFEOUT**

SAFEOUT (SFO) is a linear regulator that provides an output voltage of 5V and can be used to supply low-voltage rated USB systems. The SFO linear regulator turns on when  $V_{DC}$  > 2.5V.

#### **JEITA Description**

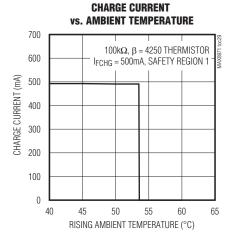

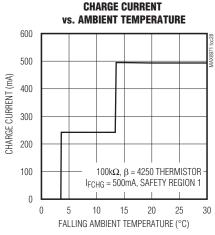

The IC JEITA-compliant switching Li+ battery charger safely charges a single Li+ cell in accordance with JEITA specifications. The IC monitors the battery temperature while charging, and automatically adjusts the fast-charge current and/or charge termination voltage as the battery temperature varies.

In safety region 1, the IC automatically reduces the fast-charging current for  $T_{BAT} < +15\,^{\circ}\text{C}$ , and reduces the charge termination voltage from 4.200V to 4.074V for  $T_{BAT} > +45\,^{\circ}\text{C}$ . The fast-charge current is reduced to 50% of the nominal fast-charge current with options for 25% and 75%. JEITA never specifically states one or the other. When battery charge current is reduced by 50%, the timer is doubled.

In safety region 2, the IC automatically reduces the charge termination voltage from 4.200V to 4.074V for  $T_{BAT} < +15^{\circ}C$  and for  $T_{BAT} > +45^{\circ}C$ . The fast-charge current is not changed in safety region 2. The safety region is programmable with the SAFETYREG bit.

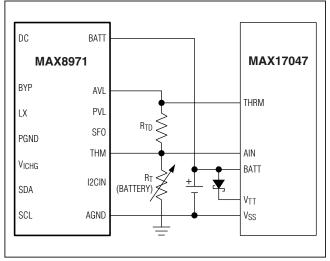

#### Maxim Model Gauge M3 Support

<u>Figure 5</u> illustrates how the IC can easily integrate with Maxim's Model gauge M3 MAX17047 chip. The user just needs to add a Schottky diode between  $V_{BATT}$  and  $V_{TT}$  on the MAX17047.

#### Factory-Mode GSM Test Mode Support

The IC supports GSM pulse programming scheme. When DC is inserted with no battery operation, the IC soft-starts and cycles through dead-battery, prequalification, and fast charge, settling at constant voltage-mode operation, and regulating to the termination voltage (4.2V default). At this time, when B4 of register 0x08 is sent, the part can now support GSM pulse. See the *Typical Operating Characteristics* section.

Figure 4. JEITA Safety Region

Figure 5. MAX8971 with MAX17047

The battery node should have enough capacitance to hold the battery voltage to some minimum acceptable system value ( $V_{SYS}$ ) during the done to fast-charge state transition time of 100 $\mu$ s ( $t_{DONE2EC}$ ).

CBAT ≥ ILOAD x tDONE2FC/(VBATREG - VSYS)

For example, if the maximum system load without a battery is 400mA ( $I_{LOAD}$ ), and the minimum acceptable system voltage is 3.4V ( $V_{SYS}$ ), then the battery node should have at least 40µF.

$C_{BAT} \ge 400 \text{mA} \times 100 \mu \text{s}/(4.2 \text{V} - 3.4 \text{V}) = 40 \mu \text{F}.$

### **Applications Information**

### **Inductor Selection**

The charger operates with a switching frequency of 4MHz and uses a  $1\mu$ H or  $2.2\mu$ H inductor. This operating frequency allows the use of physically small inductors while maintaining high efficiency.

The inductor's DC current rating only needs to match the maximum load of the application because the IC features zero current overshoot during startup and load transients. For optimum transient response and high efficiency, choose an inductor with DC series resistance in the  $40 m\Omega$  to  $120 m\Omega$  range. See <u>Table 2</u> for suggested inductors and manufacturers.

#### **Input Capacitor Selection**

The input capacitor reduces the current peaks drawn from the input power source and reduces switching noise in the IC. The impedance of the input capacitor at the switching frequency should be kept very low. Ceramic capacitors with X5R or X7R temperature characteristics are highly recommended due to their small size, low ESR, and small temperature coefficients. A 4.7µF capacitor is

recommended. For optimum noise immunity and low input ripple, the input capacitor value can be increased.

Note that some ceramic dielectrics exhibit large capacitance and ESR variation with temperature and DC bias. Ceramic capacitors with Z5U or Y5V temperature characteristics should be avoided.

### **Output Capacitor Selection**

For the charger, the output capacitor keeps the output voltage ripple small and ensures regulation loop stability. The output capacitor must have low impedance at the switching frequency. Ceramic capacitors with X5R or X7R temperature characteristics are highly recommended due to their small size, low ESR, and small temperature coefficients. A 4.7µF capacitor is recommended. For optimum load-transient performance and very low output ripple, increase the output capacitor value.

### **Charge Current Resistor Selection**

Both the top-off current range and fast-charge current range depends on the sensing resistor (R<sub>SNS</sub>). The default resistor recommended is a  $47m\Omega$ , 0.125W resistor. Select a 0.125W, $47m\Omega$  2% sense resistor, e.g., Panasonic ERJ2BWGR047. This is a standard value.

PRSNS = ICHARGE<sup>2</sup> x RSNS

$P_{RSNS} = 1.52 \times 0.047$

$P_{RSNS} = 0.105W$

The charge current step  $(I_{\mbox{CHARGE}})$  is calculated using equation below:

I<sub>CHARGE\_STEP</sub> = V<sub>(CHGCC<>)</sub>/R<sub>SNS</sub>

$\underline{\text{Table 3}}$  below shows the charge current settings for two sensing resistors.

ICHARGE CURRENT STEP = V(TOPOFF<>)/RSNS

**Table 2. Suggested Inductors**

| MANUFACTURER | SERIES        | INDUCTANCE<br>(µH) | ESR (I) | CURRENT<br>RATING (mA) | DIMENSIONS                                 |

|--------------|---------------|--------------------|---------|------------------------|--------------------------------------------|

| FDK          | MIPSA2520D1R0 | 1.0                | 0.090   | 1600                   | 2.5mm x 2.0mm x 1.2mm = 6mm <sup>3</sup>   |

| Murata       | LQM2HPN1R0MG0 | 1.0                | 0.055   | 900                    | 2.5mm x 2.0mm x 0.6mm = 3mm <sup>3</sup>   |

| Coilcraft    | ELP2014-102ML | 1.0                | 0.059   | 1680                   | 2.0mm x 2.0mm x 1.4mm = 5.6mm <sup>3</sup> |

| TDK          | MLP2520S      | 1.0                | 0.06    | 1500                   | 2.0mm x 2.5mm x 1.0mm = 5mm <sup>3</sup>   |

| Murata       | DFE252012C    | 1                  | 0.045   | 3800                   | 2.5 x 2.0 x 1.2 = 6mm <sup>3</sup>         |

| Murata       | LQM32PN1R0MG0 | 1                  | 0.06    | 1800                   | 3.2 x 2.5 x 0.9 = 7.2mm <sup>3</sup>       |

| Table 3. Charge Current Settings for $47m\Omega$ and $68m\Omega$ Sense Resistors | Table 3. Charg | e Current | Settings 1 | for 47mΩ | and 68m | Ω Sense | Resistors |

|----------------------------------------------------------------------------------|----------------|-----------|------------|----------|---------|---------|-----------|

|----------------------------------------------------------------------------------|----------------|-----------|------------|----------|---------|---------|-----------|

| ВІТ                               | VI <sub>REG</sub> (mV) | I <sub>CHARGE</sub> (mA)<br>R <sub>SNS</sub> = 47mΩ | I <sub>CHARGE</sub> (mA)<br>R <sub>SNS</sub> = 68mΩ |

|-----------------------------------|------------------------|-----------------------------------------------------|-----------------------------------------------------|

| V <sub>(CHGCC&lt;11110&gt;)</sub> | 70.5                   | 1500                                                | 1037                                                |

| V <sub>(CHGCC&lt;10100&gt;)</sub> | 47                     | 1000                                                | 691                                                 |

| V(CHGCC<01010>)                   | 23.5                   | 500                                                 | 345                                                 |

Table 4. Top-Off Current Settings for  $47m\Omega$  and  $68m\Omega$  Sense Resistors

| ВІТ                           | V(TOPOFF) | I(TOPOFF) (mA)<br>$R_{SNS} = 47m\Omega$ | I( <sub>TOPOFF</sub> ) (mA)<br>R <sub>SNS</sub> = 68mΩ |

|-------------------------------|-----------|-----------------------------------------|--------------------------------------------------------|

| V <sub>(TOPOFF&lt;&gt;)</sub> | 9.4       | 200                                     | 138.2                                                  |

| V <sub>(TOPOFF&lt;&gt;)</sub> | 4.7       | 100                                     | 69.1                                                   |

| V <sub>(TOPOFF&lt;&gt;)</sub> | 2.35      | 50                                      | 34.5                                                   |

#### **Serial Interface**

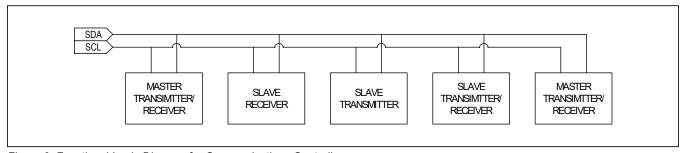

The  $I^2C$ -compatible, 2-wire serial interface is used for regulator on/off control, setting output voltages, and other functions. See the complete register map.

The I²C serial bus consists of a bidirectional serial-data line (SDA) and a serial clock (SCL). I²C is an open-drain bus. SDA and SCL require pullup resistors ( $500\Omega$  or greater). Optional  $24\Omega$  resistors in series with SDA and SCL help to protect the device inputs from high-voltage spikes on the bus lines. Series resistors also minimize crosstalk and undershoot on bus lines.

### **System Configuration**

The I<sup>2</sup>C bus is a multimaster bus. The maximum number of devices that can attach to the bus is only limited by bus capacitance.

<u>Figure 6</u> shows an example of a typical I<sup>2</sup>C system. A device on I<sup>2</sup>C bus that sends data to the bus is called a transmitter. A device that receives data from the bus is called a receiver. The device that initiates a data transfer and generates SCL clock signals to control the data transfer is a master. Any device that is being addressed by the master is considered a slave. When the MAX8971 I<sup>2</sup>C-compatible interface is operating, it is a slave on I<sup>2</sup>C bus, and it can be both a transmitter and a receiver.

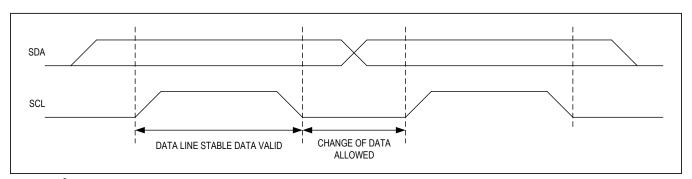

#### **Bit Transfer**

One data bit is transferred for each SCL clock cycle. The data on SDA must remain stable during the HIGH portion of SCL clock pulse. Changes in SDA while SCL is HIGH are control signals (START and STOP conditions).

Figure 6. Functional Logic Diagram for Communications Controller

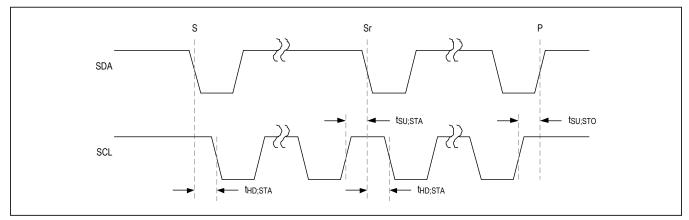

#### **START and STOP Conditions**

When the I<sup>2</sup>C serial interface is inactive, SDA and SCL idle HIGH. A master device initiates communication by issuing a START condition. A START condition is a HIGH-to-LOW transition on SDA with SCL HIGH. A STOP condition is a LOW-to-HIGH transition on SDA, while SCL is HIGH.

A START condition from the master signals the beginning of a transmission to the MAX8971. The master terminates transmission by issuing a NOT-ACKNOWLEDGE followed by a STOP condition.

A STOP condition frees the bus. To issue a series of commands to the slave, the master can issue REPEATED START (Sr) commands instead of a STOP command to maintain control of the bus. In general, a REPEATED START command is functionally equivalent to a regular START command.

When a STOP condition or incorrect address is detected, the MAX8971 internally disconnects SCL from I<sup>2</sup>C serial interface until the next START condition, minimizing digital noise and feedthrough.

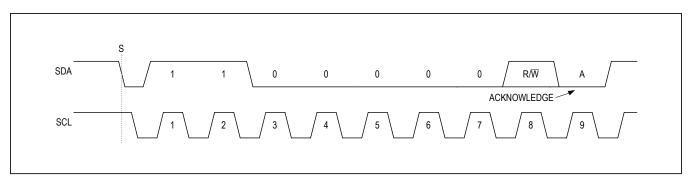

### Acknowledge

Both the I<sup>2</sup>C bus master and MAX8971 (slave) generate acknowledge bits when receiving data. The acknowledge bit is the last bit of each nine bit data packet. To generate an ACKNOWLEDGE (A), the receiving device must pull SDA LOW before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it LOW during the HIGH period of the clock pulse. To generate a NOT-ACKNOWLEDGE (nA), the receiving device allows SDA to be pulled HIGH before the rising edge of the acknowledge-related clock pulse and leaves it HIGH during the HIGH period of the clock pulse.

Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master should reattempt communication at a later time.

Figure 7. I2C Bit Transfer

Figure 8. START and STOP Conditions

#### **Slave Address**

The I<sup>2</sup>C slave address of the MAX8971 follows:

Slave Address (7 bit) 011 0101

Slave Address (Write) 0x6A 0110 1010 Slave Address (Read) 0x6B 0110 1011

#### **Clock Stretching**