### **General Description**

The MAX9324 low-skew, low-jitter, clock and data driver distributes a differential LVPECL input to four differential LVPECL outputs and one single-ended LVCMOS output. All outputs default to logic low when the differential inputs equal GND or are left open. The MAX9324 operates from 3.0V to 3.6V, making it ideal for 3.3V systems, and consumes only 25mA (max) of supply current.

The MAX9324 features low 150ps (max) part-to-part skew, low 15ps output-to-output skew, and low 1.7ps RMS jitter, making the device ideal for clock and data distribution across a backplane or board. CLK\_EN and SEOUT\_Z control the status of the various outputs. Asserting CLK EN low configures the differential (Q., Q\_) outputs to a differential low condition and SEOUT to a single-ended logic-low state. CLK\_EN operation is synchronous with the CLK\_ inputs. A logic high on SEOUT\_Z places SEOUT in a high-impedance state. SEOUT\_Z is asynchronous with the CLK (CLK) inputs.

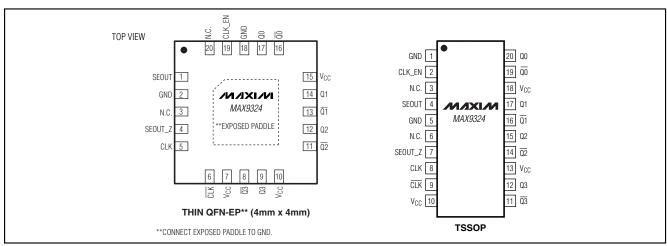

The MAX9324 is available in space-saving 20-pin TSSOP and ultra-small 20-pin 4mm x 4mm thin QFN packages and operates over the extended (-40°C to +85°C) temperature range.

### **Applications**

Precision Clock Distribution Low-Jitter Data Repeater Data and Clock Driver and Buffer Central-Office Backplane Clock Distribution **DSLAM Backplane Base Station**

#### Features

- ♦ 15ps Differential Output-to-Output Skew

- ♦ 1.7psRMS Added Random Jitter

- ◆ 150ps (max) Part-to-Part Skew

- ♦ 450ps Propagation Delay

- ♦ Synchronous Output Enable/Disable

- **♦ Single-Ended Monitor Output**

- ♦ Outputs Assert Low when CLK, CLK are Open or

- ♦ 3.0V to 3.6V Supply Voltage Range

- ♦ -40°C to +85°C Operating Temperature Range

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE      |  |  |

|-------------|----------------|------------------|--|--|

| MAX9324EUP  | -40°C to +85°C | 20 TSSOP         |  |  |

| MAX9324ETP* | -40°C to +85°C | 20 Thin QFN-EP** |  |  |

<sup>\*</sup>Future product—Contact factory for availability.

Functional Diagram and Typical Operating Circuit appear at end of data sheet.

### **Pin Configurations**

MIXIM

ATE

Maxim Integrated Products 1

<sup>\*\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND                                                  | 0.3V to +4.0V               |

|-------------------------------------------------------------------------|-----------------------------|

| $Q_{-}$ , $\overline{Q}_{-}$ , CLK, $\overline{CLK}$ , SEOUT_Z, CLK_EN, |                             |

| SEOUT to GND                                                            | $0.3V$ to $(V_{CC} + 0.3V)$ |

| CLK to CLK                                                              | ±3V                         |

| SEOUT Short to GND                                                      |                             |

| Continuous Output Current (Q_, Q_)                                      | 50mA                        |

| Surge Output Current (Q_, \overline{Q}_)                                | 100mA                       |

| Continuous Power Dissipation ( $T_A = +70^{\circ}$                      | C)                          |

| 20-Pin TSSOP (derate 11mW/°C)                                           | 879.1mW                     |

| 20-Pin 4mm × 4mm Thin QFN (derate 1)                                    | 6.9mW/°C)1349.1mW           |

| Junction-to-Ambient Thermal Resistance in St | till Air       |

|----------------------------------------------|----------------|

| 20-Pin TSSOP                                 | +91°C/W        |

| 20-Pin 4mm × 4mm Thin QFN                    | +59.3°C/W      |

| Junction-to-Case Thermal Resistance          |                |

| 20-Pin TSSOP                                 | +20°C/W        |

| 20-Pin 4mm × 4mm Thin QFN                    | +2°C/W         |

| Operating Temperature Range                  | 40°C to +85°C  |

| Junction Temperature                         | +150°C         |

| Storage Temperature Range                    | 65°C to +150°C |

| Soldering Temperature (10s)                  | +300°C         |

|                                              |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC}=3.0V\ to\ 3.6V,\ differential\ outputs\ terminated\ with\ 50\Omega\ \pm1\%\ to\ (V_{CC}\ -\ 2V),\ SEOUT\_Z=GND,\ CLK\_EN=V_{CC},\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $V_{CC}=3.3V,\ T_A=+25^{\circ}C.$ ) (Notes 1, 2, and 3)

| PARAMETER                             | SYMBOL                              | CONDITIONS                                       | MIN                   | TYP MAX                | UNITS |  |  |  |  |  |

|---------------------------------------|-------------------------------------|--------------------------------------------------|-----------------------|------------------------|-------|--|--|--|--|--|

| SINGLE-ENDED INPUTS (CLK_EN, SEOUT_Z) |                                     |                                                  |                       |                        |       |  |  |  |  |  |

| Input High Voltage                    | VIH                                 |                                                  | 2                     | Vcc                    | V     |  |  |  |  |  |

| Input Low Voltage                     | V <sub>IL</sub>                     |                                                  | 0                     | 0.8                    | V     |  |  |  |  |  |

| Janut Lligh Current                   | lo.                                 | CLK_EN = V <sub>CC</sub>                         | -5                    | +5                     | ^     |  |  |  |  |  |

| Input High Current                    | lін                                 | SEOUT_Z = V <sub>CC</sub>                        |                       | μΑ                     |       |  |  |  |  |  |

| Input Low Current                     | lu lu                               | CLK_EN = GND                                     | -150                  |                        | μA    |  |  |  |  |  |

| Imput Low Current                     | I <sub>IL</sub>                     | SEOUT_Z = GND                                    | -5                    | +5                     | μΑ    |  |  |  |  |  |

| DIFFERENTIAL INPUT (CLK, CLI          | <del>(</del> )                      |                                                  |                       |                        |       |  |  |  |  |  |

| Differential Input High Voltage       | V <sub>IHD</sub>                    | Figure 1                                         | 1.5                   | Vcc                    | V     |  |  |  |  |  |

| Differential Input Low Voltage        | V <sub>ILD</sub>                    | Figure 1                                         | 0                     | V <sub>CC</sub> - 0.15 | V     |  |  |  |  |  |

| Differential Input Voltage            | V <sub>IHD</sub> - V <sub>ILD</sub> |                                                  | 0.15                  | 1.5                    | V     |  |  |  |  |  |

| Input Current                         | ICLK                                | V <sub>IHD</sub> , V <sub>ILD</sub>              | -5                    | +150                   | μΑ    |  |  |  |  |  |

| DIFFERENTIAL OUTPUTS (Q_, 0           | <u>-</u> )                          |                                                  |                       |                        |       |  |  |  |  |  |

| Single-Ended Output High              | V <sub>OH</sub>                     | Figure 1                                         | V <sub>CC</sub> - 1.4 | V <sub>CC</sub> - 1.0  | V     |  |  |  |  |  |

| Single-Ended Output Low               | V <sub>OL</sub>                     | Figure 1                                         | V <sub>CC</sub> - 2.0 | V <sub>CC</sub> - 1.7  | V     |  |  |  |  |  |

| Differential Output Voltage           | V <sub>OH</sub> - V <sub>OL</sub>   | Figure 1                                         | 0.6                   | 0.85                   | V     |  |  |  |  |  |

| SINGLE-ENDED OUTPUT (SEOU             | T)                                  |                                                  |                       |                        |       |  |  |  |  |  |

| Output High Voltage                   | V <sub>OH</sub>                     | I <sub>OH</sub> = -4mA                           | 2.4                   |                        | V     |  |  |  |  |  |

| Output Low Voltage                    | V <sub>OL</sub>                     | I <sub>OL</sub> = 4mA                            |                       | 0.4                    | V     |  |  |  |  |  |

| Output High-Impedance Current         | loz                                 | SEOUT_Z = $V_{CC}$ , SEOUT = $V_{CC}$ or GND     | -10                   | +10                    | μΑ    |  |  |  |  |  |

| Output Short-Circuit Current          | los                                 | V <sub>CLK</sub> = V <sub>CC</sub> , SEOUT = GND |                       | 75                     | mA    |  |  |  |  |  |

| SUPPLY                                |                                     |                                                  |                       |                        |       |  |  |  |  |  |

| Supply Current                        | Icc                                 | (Note 4)                                         |                       | 25                     | mA    |  |  |  |  |  |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC}=3.0V\ to\ 3.6V,\ differential\ outputs\ terminated\ with\ 50\Omega\ \pm1\%\ to\ (V_{CC}-2V),\ f_{CLK}\le 266MHz,\ input\ duty\ cycle=50\%,\ input\ transition\ time=125ps\ (20\%\ to\ 80\%),\ V_{IHD}=1.5V\ to\ V_{CC},\ V_{ILD}=GND\ to\ (V_{CC}-0.15V),\ V_{IHD}-V_{ILD}=0.15V\ to\ 1.5V,\ CLK_EN=V_{CC},\ SEOUT_Z=GND,\ T_A=-40°C\ to\ +85°C,\ unless\ otherwise\ noted.$  Typical values are at  $V_{CC}=3.3V,\ V_{IHD}=(V_{CC}-1V),\ V_{ILD}=(V_{CC}-1.5V),\ T_A=+25°C.)$  (Note 5)

| PARAMETER                      | SYMBOL                              | CONDITIONS                                                                        | MIN | TYP | MAX | UNITS   |

|--------------------------------|-------------------------------------|-----------------------------------------------------------------------------------|-----|-----|-----|---------|

| Cuitabina Fraguenay            | f                                   | V <sub>OH</sub> - V <sub>OL</sub> ≥ 0.6V, SEOUT_Z = V <sub>CC</sub>               | 650 | 800 |     | MHz     |

| Switching Frequency            | fMAX                                | SEOUT_Z = GND, SEOUT                                                              | 125 | 200 |     | IVI□Z   |

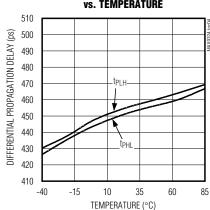

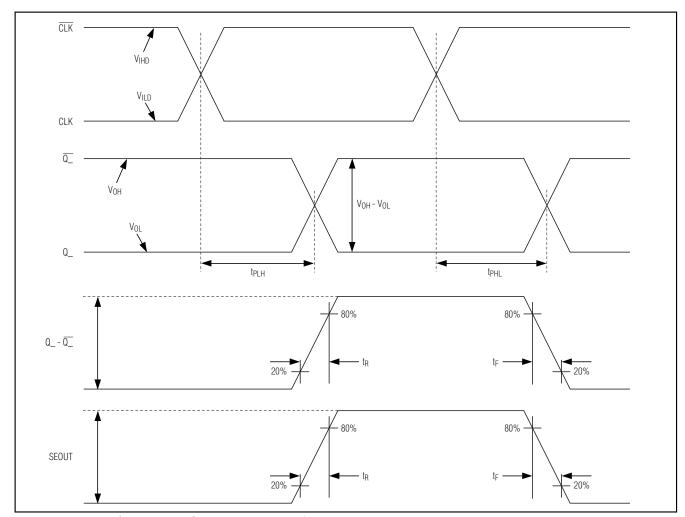

| Propagation Delay              | t <sub>PHL</sub> , t <sub>PLH</sub> | CLK, CLK to Q_, Q_, Figure 1 (Note 6)                                             | 100 | 450 | 600 | ps      |

| Output-to-Output Skew          | tskoo                               | (Note 7)                                                                          |     |     | 30  | ps      |

| Part-to-Part Skew              | tskpp                               | (Note 8)                                                                          |     |     | 150 | ps      |

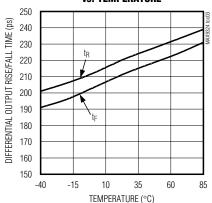

| Output Rise Time               | t <sub>R</sub>                      | 20% to 80%, Figure 1                                                              | 100 | 217 | 300 | ps      |

| Output Fall Time               | tF                                  | 80% to 20%, Figure 1                                                              | 100 | 207 | 300 | ps      |

| Output Duty Cycle              | ODC                                 |                                                                                   | 48  | 50  | 52  | %       |

| Added Random Jitter            | t <sub>RJ</sub>                     | f <sub>CLK</sub> = 650MHz (Note 9)                                                |     | 1.7 | 3   | ps(RMS) |

| Added Deterministic Jitter     | tDJ                                 | 2e <sup>23</sup> - 1 PRBS pattern, f = 650Mbps (Note 9)                           |     | 83  | 100 | ps(P-P) |

| Added Jitter                   | t <sub>A</sub> J                    | V <sub>CC</sub> = 3.3V with 25mV superimposed sinusoidal noise at 100kHz (Note 9) |     | 8.5 | 12  | ps(P-P) |

| Single-Ended Output Rise Time  | t <sub>R</sub>                      | C <sub>L</sub> = 15pF, 20% to 80%, Figure 1                                       |     | 1.6 | 2   | ns      |

| Single-Ended Output Fall Time  | tF                                  | C <sub>L</sub> = 15pF, 80% to 20%, Figure 1                                       |     | 1.6 | 2   | ns      |

| Single-Ended Output Duty Cycle | ODC                                 | (Note 10)                                                                         | 40  | 52  | 60  | %       |

- **Note 1:** Measurements are made with the device in thermal equilibrium.

- Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative.

- **Note 3:** DC parameters are production tested at  $T_A = +25^{\circ}C$  and guaranteed by design over the full operating temperature range.

- Note 4: All pins open except V<sub>CC</sub> and GND.

- Note 5: Guaranteed by design and characterization. Limits are set at ±6 sigma.

- Note 6: Measured from the differential input signal crosspoint to the differential output signal crosspoint.

- Note 7: Measured between the differential outputs of the same part at the differential signal crosspoint for a same-edge transition.

- **Note 8:** Measured between the differential outputs of different parts at the differential signal crosspoint under identical conditions for a same-edge transition.

- **Note 9:** Jitter added to the input signal.

- Note 10: Measured at 50% of V<sub>CC</sub>.

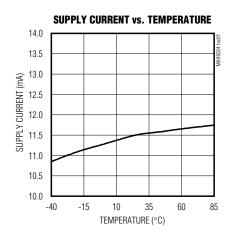

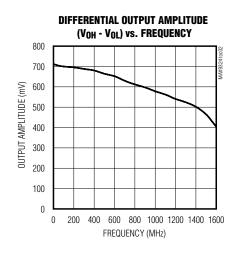

## Typical Operating Characteristics

$(V_{CC} = 3.3V, outputs terminated to (V_{CC} - 2V) through 50\Omega, SEOUT_Z = V_{CC}, CLK_EN = V_{CC}, T_A = +25^{\circ}C.)$

## Pin Description

| PIN                                                                                                      |           |                                                                                                                                                                                                                                                       | FUNCTION                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TSSOP                                                                                                    | QFN       | NAME                                                                                                                                                                                                                                                  | FUNCTION                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 1, 5                                                                                                     | 2, 18     | GND                                                                                                                                                                                                                                                   | Ground. Provide a low-impedance connection to the ground plane.                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 2 19 CLK_EN                                                                                              |           | CLK_EN                                                                                                                                                                                                                                                | Synchronous Output Enable. Connect CLK_EN to $V_{CC}$ or leave floating to enable the differential outputs. Connect CLK_EN to GND to disable the differential outputs. When disabled, Q_ asserts low, $\overline{Q}$ asserts high, and SEOUT asserts low. A 51k $\Omega$ pullup resistor to $V_{CC}$ allows CLK_EN to be left floating. |  |  |  |  |  |

| 3, 6                                                                                                     | 3, 20     | N.C.                                                                                                                                                                                                                                                  | No Connect. Not internally connected.                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 4                                                                                                        | 1         | SEOUT                                                                                                                                                                                                                                                 | LVCMOS/LVTTL Clock Output. SEOUT reproduces CLK when SEOUT_Z = GND. SEOUT goes high impedance when SEOUT_Z = $V_{CC}$ . The maximum output frequency of SEOUT is 125MHz.                                                                                                                                                                |  |  |  |  |  |

| Single-Ended Clock Output Enable/Disable. Connect SE ended clock output. Connect SEOUT_Z to Vcc to disab |           | Single-Ended Clock Output Enable/Disable. Connect SEOUT_Z to GND to enable the single-ended clock output. Connect SEOUT_Z to VCC to disable the single-ended clock output. A $51k\Omega$ pulldown resistor to GND allows SEOUT_Z to be left floating. |                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 8                                                                                                        | 5         | CLK                                                                                                                                                                                                                                                   | Noninverting Differential LVPECL Input. An internal $51k\Omega$ pulldown resistor to GND forces the outputs $(Q, \overline{Q})$ to differential low and logic low (SEOUT) when CLK and $\overline{\text{CLK}}$ are left open or at GND and the outputs are enabled.                                                                     |  |  |  |  |  |

| 9                                                                                                        | 6         | CLK                                                                                                                                                                                                                                                   | Inverting Differential LVPECL Input. An internal $51k\Omega$ pulldown resistor to GND forces the outputs $(Q, \overline{Q})$ to differential low and logic low (SEOUT) when CLK and $\overline{\text{CLK}}$ are left open or at GND and the outputs are enabled.                                                                        |  |  |  |  |  |

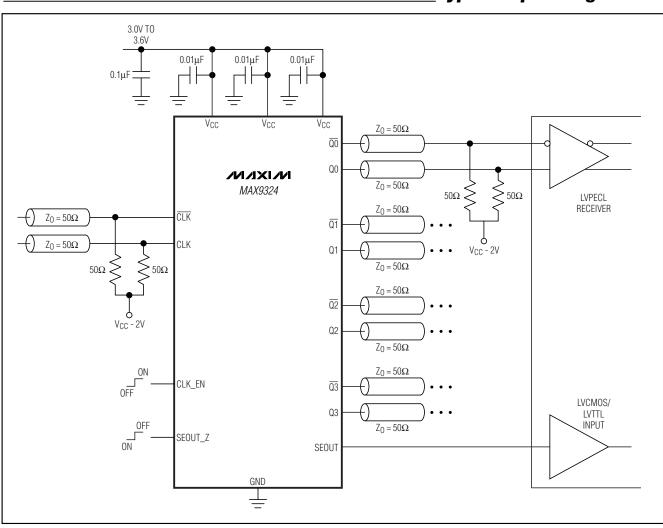

| 10, 13, 18                                                                                               | 7, 10, 15 | Vcc                                                                                                                                                                                                                                                   | Positive Supply Voltage. Bypass $V_{CC}$ to GND with three $0.01\mu F$ and one $0.1\mu F$ ceramic capacitors. Place the $0.01\mu F$ capacitors as close to each $V_{CC}$ input as possible (one per $V_{CC}$ input). Connect all $V_{CC}$ inputs together, and bypass to GND with a $0.1\mu F$ ceramic capacitor.                       |  |  |  |  |  |

| 11                                                                                                       | 8         | Q3                                                                                                                                                                                                                                                    | Inverting Differential LVPECL Output. Terminate $\overline{\rm Q3}$ to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                          |  |  |  |  |  |

| 12                                                                                                       | 9         | Q3                                                                                                                                                                                                                                                    | Noninverting Differential LVPECL Output. Terminate Q3 to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                                        |  |  |  |  |  |

| 14                                                                                                       | 11        | Q2                                                                                                                                                                                                                                                    | Inverting Differential LVPECL Output. Terminate $\overline{\rm Q2}$ to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                          |  |  |  |  |  |

| 15                                                                                                       | 12        | Q2                                                                                                                                                                                                                                                    | Noninverting Differential LVPECL Output. Terminate Q2 to (V <sub>CC</sub> - 2V) with a $50\Omega$ ±1% resistor.                                                                                                                                                                                                                         |  |  |  |  |  |

| 16 13 <u>Q1</u>                                                                                          |           | Q1                                                                                                                                                                                                                                                    | Inverting Differential LVPECL Output. Terminate $\overline{Q1}$ to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                              |  |  |  |  |  |

| 17                                                                                                       | 14        | Q1                                                                                                                                                                                                                                                    | Noninverting Differential LVPECL Output. Terminate Q1 to (V <sub>CC</sub> - 2V) with a $50\Omega \pm 1\%$ resistor.                                                                                                                                                                                                                     |  |  |  |  |  |

| 19                                                                                                       | 16        | Q0                                                                                                                                                                                                                                                    | Inverting Differential LVPECL Output. Terminate $\overline{\text{Q0}}$ to (V <sub>CC</sub> - 2V) with a 50 $\Omega$ ±1% resistor.                                                                                                                                                                                                       |  |  |  |  |  |

| 20                                                                                                       | 17        | Q0                                                                                                                                                                                                                                                    | Noninverting Differential LVPECL Output. Terminate Q0 to (V <sub>CC</sub> - 2V) with a $50\Omega \pm 1\%$ resistor.                                                                                                                                                                                                                     |  |  |  |  |  |

#### **Detailed Description**

The MAX9324 low-skew, low-jitter, clock and data driver distributes a differential LVPECL input signal to four differential LVPECL outputs and a single-ended LVC-MOS output. The differential output drivers operate at frequencies up to 800MHz. When SEOUT\_Z = GND, the single-ended LVCMOS output driver operates with frequencies as high as 200MHz. The MAX9324 operates from 3.0V to 3.6V, making the device ideal for 3.3V systems.

#### Data Inputs

#### **Differential LVPECL Inputs**

The MAX9324 accepts a differential LVPECL input. Each differential output duplicates the differential input

signal. Terminate CLK and  $\overline{\text{CLK}}$  through  $50\Omega$  to (V<sub>CC</sub> - 2V) to minimize input signal reflections. Internal  $51k\Omega$  pulldown resistors to GND ensure the outputs default to differential low (Q\_,  $\overline{\text{Q}}$ ) or logic low (SEOUT) when the CLK inputs are left open.

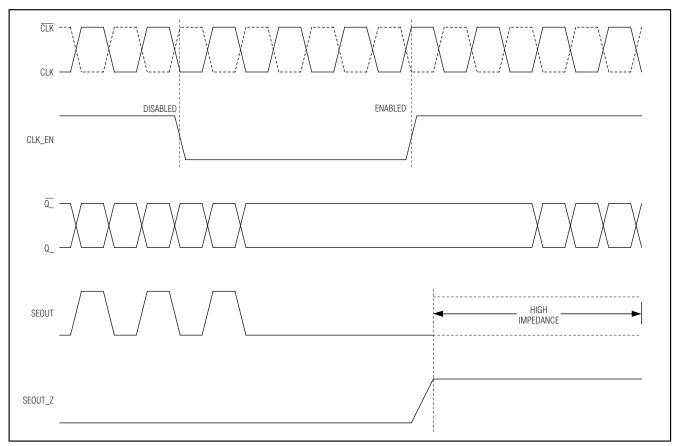

#### **CLK\_EN** Input

CLK\_EN enables/disables the differential outputs of the MAX9324. Connect CLK\_EN to V<sub>CC</sub> to enable the differential outputs. The (Q\_,  $\overline{Q}$ ) outputs are driven to a differential low condition when CLK\_EN = GND. Each differential output pair disables following successive rising and falling edges on CLK (falling and rising edges on  $\overline{C}$ LK), after CLK\_EN connects to GND. Both a rising and falling edge on CLK are required to complete the enable/disable function (Figure 2).

Figure 1. MAX9324 Clock Input-to-Output Delay and Rise/Fall Time

Figure 2. MAX9324 CLK\_EN Timing Diagram

#### SEOUT\_Z

SEOUT\_Z enables/disables the single-ended LVCMOS output (Table 1). Connect SEOUT\_Z to GND to enable the single-ended output. Connect SEOUT\_Z to  $V_{\rm CC}$  to force the single-ended output to a high-impedance state. SEOUT provides a single-ended monitor for operating frequencies as high as 200MHz.

### **Applications Information**

#### **Output Termination**

Terminate both outputs of each differential pair through  $50\Omega$  to (VCC - 2V) or use an equivalent Thevenin termination. Use identical termination on each output for the lowest output-to-output skew. Terminate both outputs when deriving a single-ended signal from a differential output. For example, using Q0 as a single-ended output requires termination for both Q0 and  $\overline{\rm Q0}$ .

**Table 1. Control Input Table**

| INPUTS         |   | OUTPUTS                       |                                |                          |  |  |  |  |  |

|----------------|---|-------------------------------|--------------------------------|--------------------------|--|--|--|--|--|

| CLK_EN SEOUT_Z |   | Q0-Q3                         | <u> Q0–Q3</u>                  | SEOUT                    |  |  |  |  |  |

| 0              | 0 | Disabled, pulled to logic low | Disabled, pulled to logic high | Enabled, logic low       |  |  |  |  |  |

| 0              | 1 | Disabled, pulled to logic low | Disabled, pulled to logic high | Disabled, high impedance |  |  |  |  |  |

| 1              | 0 | Enabled                       | Enabled                        | Enabled                  |  |  |  |  |  |

| 1              | 1 | Enabled                       | Enabled                        | Disabled, high impedance |  |  |  |  |  |

SEOUT provides a single-ended LVCMOS monitor output. SEOUT operates with a maximum output frequency of 200MHz.

Ensure that the output currents do not violate the current limits as specified in the *Absolute Maximum Ratings* table. Observe the device's total thermal limits under all operating conditions.

#### **Power-Supply Bypassing**

Bypass V<sub>CC</sub> to GND using three 0.01µF ceramic capacitors and one 0.1µF ceramic capacitor. Place the 0.01µF capacitors (one per V<sub>CC</sub> input) as close to V<sub>CC</sub> as possible (see the *Typical Operating Circuit*). Use multiple bypass vias to minimize parasitic inductance.

#### **Circuit Board Traces**

Input and output trace characteristics affect the performance of the MAX9324. Connect each input and output to a  $50\Omega$  characteristic impedance trace to minimize reflections. Avoid discontinuities in differential impedance and maximize common-mode noise immunity by maintaining the distance between differential traces and avoiding sharp corners. Minimize the number of vias to prevent impedance discontinuities. Minimize skew by matching the electrical length of the traces.

#### **Chip Information**

TRANSISTOR COUNT: 4430

PROCESS: BiCMOS

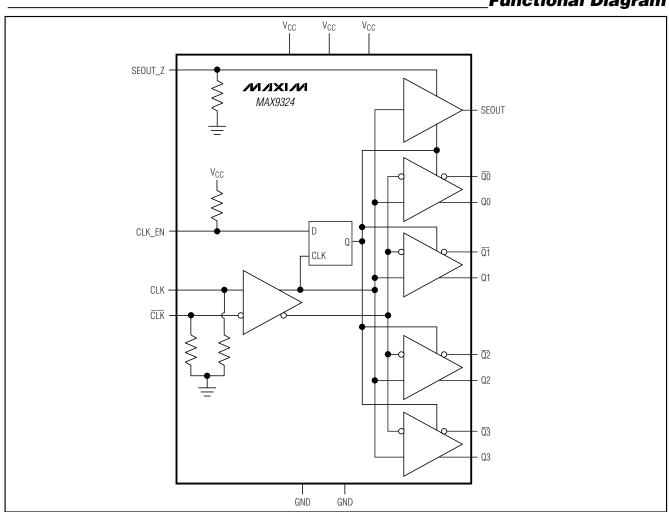

### **Functional Diagram**

### **Typical Operating Circuit**

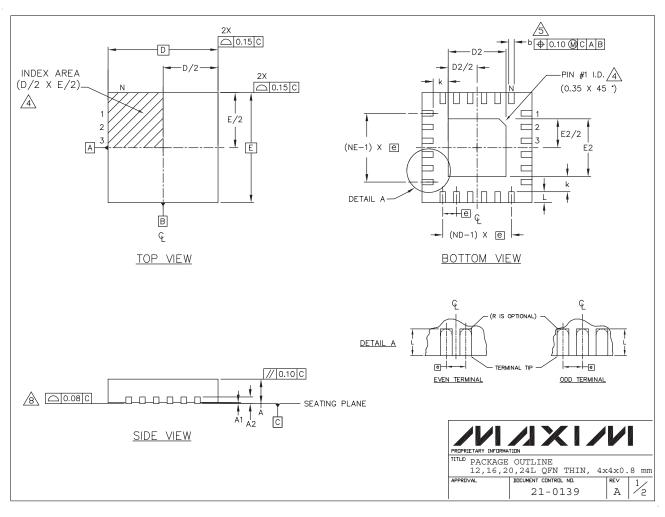

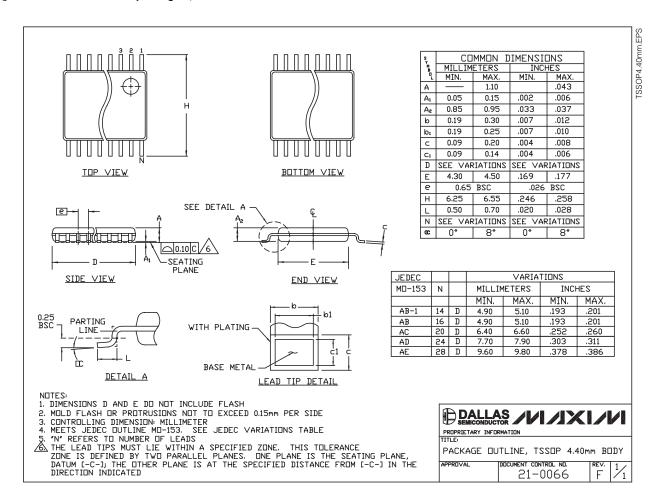

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

10 \_\_\_\_\_\_ /II/XI//I

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

|               | COMMON DIMENSIONS |          |          |           |        |           |          |           |         |          |      |      |

|---------------|-------------------|----------|----------|-----------|--------|-----------|----------|-----------|---------|----------|------|------|

| PKG 12L 4×4   |                   |          | 16L 4×4  |           |        | 20L 4×4   |          |           | 24L 4×4 |          |      |      |

| REF.          | MIN.              | N□M.     | MAX.     | MIN.      | N□M.   | MAX.      | MIN.     | N□M.      | MAX.    | MIN.     | N□M. | MAX. |

| Α             | 0.70              | 0.75     | 0.80     | 0.70      | 0.75   | 0.80      | 0.70     | 0.75      | 0.80    | 0.70     | 0.75 | 0.80 |

| A1            | 0.0               | 0.02     | 0.05     | 0.0       | 0.02   | 0.05      | 0.0      | 0.02      | 0.05    | 0.0      | 0.02 | 0.05 |

| A2            | 0.20 REF          |          |          | 0.20 REF  |        |           | 0.20 REF |           |         | 0.20 REF |      |      |

| b             | 0.25              | 0.30     | 0.35     | 0.25      | 0.30   | 0.35      | 0.20     | 0.25      | 0.30    | 0.18     | 0.23 | 0.30 |

| D             | 3.90              | 4.00     | 4.10     | 3.90      | 4.00   | 4.10      | 3.90     | 4.00      | 4.10    | 3.90     | 4.00 | 4.10 |

| E             | 3.90              | 4.00     | 4.10     | 3.90      | 4.00   | 4.10      | 3.90     | 4.00      | 4.10    | 3.90     | 4.00 | 4.10 |

| е             |                   | 0.80 B20 | <u>.</u> | 0.65 BSC. |        | 0.50 BSC. |          | 0.50 BSC. |         |          |      |      |

| k             | 0.25              | -        | -        | 0.25      | -      | -         | 0.25     | -         | -       | 0.25     | -    | -    |

| L             | 0.45              | 0.55     | 0.65     | 0.45      | 0.55   | 0.65      | 0.45     | 0.55      | 0.65    | 0.30     | 0.40 | 0.50 |

| N             | 12                |          |          | 16        |        | 20        |          | 24        |         |          |      |      |

| ND            | 3                 |          | 4        |           | 5      |           | 6        |           |         |          |      |      |

| NE            | 3                 |          | 4        |           | 5      |           | 6        |           |         |          |      |      |

| Jedec<br>Var. | WGGB              |          | WGGC     |           | WGGD−1 |           | WGGD-2   |           |         |          |      |      |

| EXPO    | DNS  |      |      |      |      |      |  |

|---------|------|------|------|------|------|------|--|

| PKG.    |      | D2   |      | E2   |      |      |  |

| CODES   | MIN. | N□M. | MAX. | MIN. | N□M. | MAX. |  |

| T1244-2 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |

| T1644-2 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |

| T2044-1 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |

| T2444-1 | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 |  |

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- 4\text{\text{THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- DIMENSION & APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- 6 ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- & COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9. DRAWING CONFORMS TO JEDEC MO220.

12,16,20,24L QFN THIN, 4x4x0.8 mm

VAL | DOCUMENT CONTROL NO. | REV | 2 21-0139 Α

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Buffer category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

MPC962309EJ-1H NB4N121KMNG IDT49FCT805ASO MK2308S-1HILF PL133-27GI-R NB3L02FCT2G NB3L03FCT2G

ZL40200LDG1 ZL40205LDG1 9FG1200DF-1LF 9FG1001BGLF PI49FCT20802QE NB7L1008MNG NB7L14MN1G PI49FCT20807QE

PI6C4931502-04LIEX ZL80002QAB1 PI6C4931504-04LIEX PI6C10806BLEX ZL40226LDG1 8T73S208B-01NLGI SY75578LMG

PI49FCT32805QEX PL133-27GC-R CDCV304PWG4 MC10LVEP11DG MC10EP11DTG MC100LVEP11DG MC100E111FNG

MC100EP11DTG NB7L14MMNG NB6L11MMNG NB6L14MMNR2G NB6L611MNG NB3N111KMNR4G ADCLK944BCPZ-R7

ZL40217LDG1 NB7LQ572MNG HMC940LC4BTR ADCLK946BCPZ-REEL7 ADCLK946BCPZ ADCLK905BCPZ-R2

ADCLK905BCPZ-R7 ADCLK907BCPZ-R2 ADCLK907BCPZ-WP ADCLK914BCPZ-R2 ADCLK914BCPZ-R7 ADCLK925BCPZ-R2

ADCLK925BCPZ-R7 ADCLK925BCPZ-WP